閉ループ光ファイバセンサのためのセグメント化された光回路駆動装置

【課題】光センサ内の光駆動回路の出力分解能を向上させる。

【解決手段】光センサ回路は、アナログ測定データを生成する光学回路10と、アナログ測定データを検出し、アナログ測定データをデジタル測定データに変換する検出器回路20と、デジタル測定データを復調し、その後、復調されたデジタル測定データに基づいてセグメント化デジタル信号を生成する信号処理回路30とを備える。光センサ回路は、セグメント化デジタル信号に基づいてアナログ駆動信号を生成する光学駆動回路40をさらに備える。そして、アナログ駆動信号が使用されて光学回路が駆動される。

【解決手段】光センサ回路は、アナログ測定データを生成する光学回路10と、アナログ測定データを検出し、アナログ測定データをデジタル測定データに変換する検出器回路20と、デジタル測定データを復調し、その後、復調されたデジタル測定データに基づいてセグメント化デジタル信号を生成する信号処理回路30とを備える。光センサ回路は、セグメント化デジタル信号に基づいてアナログ駆動信号を生成する光学駆動回路40をさらに備える。そして、アナログ駆動信号が使用されて光学回路が駆動される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、包括的にはジャイロシステムに関し、より詳細には干渉方式光ファイバジャイロ(IFOG)において光信号を変調することに関する。

【背景技術】

【0002】

回転速度又は回転軸周りの角速度における変化を測定するためにジャイロが使用されてきた。基本的な従来の光ファイバジャイロ(FOG)は、光源と、ビーム生成装置と、感知軸の周りのエリアを取り囲むビーム生成装置に結合される光ファイバのコイルとを備える。ビーム生成装置は複数の光ビームをコイル内に送る。これらの光ビームは時計回り(CW)方向及び反時計回り(CCW)方向に光ファイバのコアに沿って伝搬し、両方とも最終的には光検出器(たとえば、光検出システムに電気的に結合されるフォトダイオード)に入射する。多数のFOGが、光をファイバの中実ガラスコアに沿って伝導するガラス系光ファイバを利用する。これらの2つの反対伝搬(counter-propagating)(たとえばCW及びCCW)ビームは、1つの回転閉光路又はループを伝搬して回る間に異なる光路長を経験する。たとえば、感知軸を中心とした回転は一方の回転方向において光路長を増大し、他方の回転方向において光路長を低減する。2つの光路長における差は、両方の回転方向の光ビーム間に位相シフトを導入する(すなわちサニャック効果)。この差は、囲まれているエリアに垂直である回転速度に比例する。

【0003】

ループにおける反対伝搬光ビーム間の位相差は典型的には、バイアス信号生成器に結合される光位相変調器を使用して、回転検出に対する感度を増大するために変調される。光位相変調器は、光検出システムからのフィードバックループにおいて動作して、感知軸を中心とした回転からもたらされる、反対伝搬光ビーム間の位相シフト差を相殺するのに十分な負のフィードバックを提供することができる。一例では、位相感知検出器が光検出器出力電流を表す信号を受信し、光検出器に入射する光ビームの相対的位相の指示を提供する。変調周波数において位相感知検出器によって復元されるあらゆる重要な信号内容は回転速度に比例する。

【0004】

位相感知検出器からの信号を使用して、一方の光ビームを他方のビームに対して位相シフトし、互いに同位相の反対伝搬ビームをもたらすことができる。たとえば、位相感知検出器からの信号を、積分器のような累算器を有するサーボエレクトロニクスに供給することができる。回転中に生成された位相差に応じて、サーボエレクトロニクスは、一方の光ビームを他方のビームに対して位相シフトするための信号を供給する。フィードバックループのデジタル実装においては、(たとえば位相検波器による使用のために)アナログ/デジタル変換器(ADC)が光検出器のアナログ出力をデジタルの対応するものに変換し、デジタル/アナログ変換器(DAC)が、光位相変調器を介する位相シフトのためにサーボエレクトロニクスからのデジタル信号をアナログ信号に変換する。

【0005】

非常に低い回転速度及びほぼゼロ度(±或る所定の値)の位相の検出においては、ジャイロスコープは概して位相検出に対する感度がより低い。この領域は「不感帯」と呼ばれ、不感帯誤差は幾つかの理由から生じ得る。不感帯の1つの原因は、サーボエレクトロニクスからのデジタル信号をDACに供給する前により低いビット値に切り捨てることから生じる。この切り捨ては、振動の存在下で調整されて速度誤差となる(rectify into rate error)可能性がある非対称性を導入する可能性もある。加えて、ループ誤差が、適切な位相シフトに収束するのに著しい量の時間を要する場合があり、この収束の時間は、DACに供給される信号の切り捨てによってさらに延長される場合がある。

【0006】

上記で論じた光ファイバジャイロのような閉ループ光センサは典型的には、光学集積回路(IOC)変調構成要素を含む。この構成要素は、単一の高分解能デジタル/アナログ変換器(DAC)から受信される、12ビット〜16ビットの切り捨てられる信号によって駆動される。これらのセンサの分解能計量は実質的に、該センサのIOC駆動構成要素内の1つのみの高分解能DACの使用に関連付けられるデータ切り捨てによって制限される。高精度の用途では、これらの切り捨て信号は望ましくない不感帯誤差をもたらす可能性がある。たとえば、12ビット分解能DACの最下位ビットが数百度/時間のバイアス誤差にまでなる。長時間にわたって閉ループアーキテクチャはゼロに平均化するバイアス誤差を維持するが、角度白色雑音(angle white noise)に関しては量子化誤差が残る。

【0007】

閉ループ光ファイバジャイロにおいてビット分解能を向上させるのに利用される1つの解決策は、IOC駆動装置においてより高い分解能のDACを採用することである。残念ながら、これらの高分解能変換器は高価であり、依然として23ビット分解能をはるかに下回る切り捨てを必要とする。光ファイバジャイロのIOC駆動回路内の単一のDACの使用に関連付けられる切り捨て誤差を低減するのに利用される別の解決策は、信号処理又は駆動構成要素に雑音及び平均化を導入する技法を実施することである。残念ながら、このような技法は不可避的に、特定の望ましくない雑音を変換器構成要素にもたらす。この望ましくない雑音は、一貫性のないセンサ出力及び低減したシステムスループットを引き起こす可能性がある。

【発明の概要】

【発明が解決しようとする課題】

【0008】

したがって、閉ループ誤差を低減する閉ループ光センサを提供することが望ましい。さらに、本発明の他の望ましい特徴及び特性は、添付の図面及び本発明のこの背景技術と共に考慮される本発明の後続の詳細な説明及び添付の特許請求の範囲から明らかとなるであろう。

【課題を解決するための手段】

【0009】

本発明は、光センサシステム内の光駆動回路の出力分解能を向上させるシステム及び方法を提供する。一例の光センサシステムは、アナログ測定データを生成する光学回路と、アナログ測定データを検出し、その後アナログ測定データをデジタル測定データに変換する検出器回路と、デジタル測定データを復調し、その後、復調されたデジタル測定データに基づいてセグメント化されたデジタル信号を生成する信号処理回路と、セグメント化されたデジタル信号に基づいてアナログ駆動信号を生成する光学駆動回路とを備える。アナログ駆動信号が使用されて光学回路が駆動される。

【0010】

本発明の他の態様によれば、光学駆動構成要素は、セグメント化されたデジタル信号の第1のデジタルデータセグメントを第1のアナログデータセグメントに変換する第1の変換器と、セグメント化されたデジタル信号の第2のデジタルデータセグメントを第2のアナログデータセグメントに変換する第2の変換器とを備える。

【0011】

本発明のさらなる態様によれば、第1のデジタルデータセグメントは第2のデジタルデータセグメントよりも上位のビットのデータに対応する。

本発明のさらなる態様によれば、光駆動回路は第1のアナログデータセグメント及び第2のアナログデータセグメントを増幅し、その後、これらの増幅されたアナログデータセグメントを合成し、単一のアナログ駆動信号にする。

【0012】

本発明のさらに他の態様によれば、光駆動回路の生成されたアナログ駆動信号は第1の変換器よりも高い分解能を有する。

本発明のさらに別の態様によれば、生成されたデジタル測定データ及びアナログ駆動信号は、少なくとも16ビット分解能を有するデータに対応する。

【0013】

上記概要から容易に理解されるように、本発明は、光センサ内の光駆動構成要素の出力分解能を向上させる手段を提供する。

本発明の好ましい実施形態及び代替の実施形態を、以下の図面を参照して以下において詳細に説明する。

【図面の簡単な説明】

【0014】

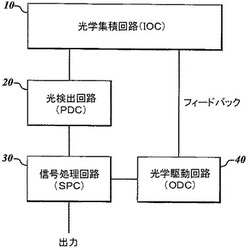

【図1】本発明の一実施形態に従って形成される閉ループ光ファイバジャイロのブロック図を示す。

【図2】本発明の一実施形態に従って形成されるIOC駆動構成要素のブロック図を示す。

【図3】本発明の一実施形態に従って形成されるIOC駆動装置内のセグメント化されたDAC構成要素のブロック図を示す。

【図4】本発明の一実施形態に従って形成されるIOC駆動装置内の利得回路を示す。

【図5】本発明の一実施形態に従って形成されるIOC駆動装置に関連付けられるプロセスのフロー図を示す。

【発明を実施するための形態】

【0015】

本発明は、光センサ装置内の光駆動回路の出力分解能を向上させるシステム及び方法に関する。少なくとも1つの実施形態によれば、光駆動回路の出力ビット分解能は、光駆動回路内の2つの別個の変換器構成要素間のデータ変換をセグメント化することによって大幅に増大することができる。

【0016】

図1は、本発明の一実施形態に従って形成される光センサ8の閉ループアーキテクチャを示している。閉ループセンサ8は、光集積回路(IOC)10と、光検出回路(PDC)20と、信号処理回路(SPC)30と、光学駆動回路(ODC)40とを備える。閉ループ光センサ8は、任意の数の異なるタイプの閉ループセンサのうちの1つ、たとえば閉ループ光ファイバセンサ及びジャイロとすることができる。

【0017】

光センサ8が閉ループ光ファイバジャイロとして実装される場合、センサ8は、IOC10の光ファイバコイルを反対方向(たとえば、時計回り方向及び反時計回り方向)に進んで回る2つの光のビーム間の位相差を求めることによって、角速度又は特定の回転軸周りの速度を測定する。IOC10のアナログ光出力はPDC20に通信される。このPDCにおいて、アナログ光出力は増幅されて、デジタル位相シフトデータに変換される。次に、PDC20のデジタル位相シフトデータはジャイロのSPC30に通信される。このSPCにおいて、デジタル位相シフトデータは復調及び検出されて、ODC40に通信される。次に、ODC40は、復調されたデジタル位相シフトデータをアナログ形式に変換し、アナログデータを増幅し、次いで、増幅されたアナログデータをフィードバックループを通じてIOC10に通信する。

【0018】

光ファイバジャイロによって測定されるビット分解能は、データ変換及び後続の信号処理の前では、23ビットにまで高くすることができる。たとえば、従来の非セグメント化IOC駆動装置は、位相シフトを23ビット分解能で測定し、次いで、SPC30において生じる切り捨て処理ステップ中にこの分解能を16ビット未満に低下させる。これらのシステムでは、ビットデータは、ODC40内の単一の高分解能DACに通信される前に切り捨てられる。この切り捨ては、データの最下位ビット(LSB)の2分の1もの大きさを有する誤差をもたらす可能性がある。ジャイロのループは、この2分の1LSBデータ誤差を補正しようと試みる場合、1つのLSBだけビット分解能を増大又は低減することしかできない。これは誤差の符号を不正確に変更してしまう。

【0019】

対照的に、本発明のSPC30は、このような切り捨て処理ステップを必要とせず、従来の非セグメント化IOC駆動装置に関連付けられる2分の1LSBデータ誤差を除去する。本発明のSPC30は、ODC40内の並列デジタル/アナログ変換器(DAC)における処理のために、23ビットデータを最上位ビット(MSB)データ部分(典型的には10ビット〜14ビットの長さの範囲を有する)及びLSBデータ部分(残りのビット分解能を含む)にセグメント化する。本発明の代替の一実施形態によれば、MSB/LSBデータセグメント化は、SPC30においてではなくODC40において生じる。次に、ODC40の並列DACは、23ビットのセグメント化されたMSB/LSBデータをアナログ信号データに変換し、次いで、IOC10を駆動するためにこの高精度信号データを増幅及び合成する。本発明の一実施形態によれば、アナログ信号データの合成は増幅ステップ前に生じる。

【0020】

図2は、本発明の一実施形態に従って形成されるODC40を示している。ODC40は、セグメント化されたビデオDAC(SVDAC)42と、利得回路46と、増幅器構成要素48とを備える。SVDAC42は、23ビットデジタル信号を表すデータをSPC30から受信する。この信号は、MSB構成部分とLSB構成部分とにセグメント化され、次いでSVDAC42によってアナログ信号に変換される。変換処理後、利得回路46を利用して、アナログのMSB信号構成部分及びLSB信号構成部分とに利得が印加される。利得処理後、アナログ信号は、増幅器48によって合成されて、IOC10に出力される。本発明の代替の一実施形態によれば、アナログ信号をIOC10に出力する前に、アナログ信号が増幅器48によって合成された後に利得が印加される。別の実施形態によれば、利得処理は、電気利得処理又は光学利得処理のいずれかを含むことができる。

【0021】

SVDAC42の中身を図3に示す。SVDAC42はMSB DAC43及びLSB DAC45を含む。MSB DAC43は、23ビットデータ信号からセグメント化された最上位ビットのデータを受信及び変換し、LSB DAC45は、同じ23ビット信号からセグメント化された最下位ビットのデータを受信及び変換する。本発明の一実施形態によれば、MSB/LSBデータセグメント化はSPC30において生じる。代替の一実施形態によれば、データセグメント化はODC40内で生じる。一実施形態では、MSB DAC及びLSB DACの両方の変換処理後に、セグメント化されたアナログ信号が利得回路46に出力される。この利得回路は図4において例示されている。代替の一実施形態によれば、セグメント化されたアナログ信号は増幅器48に出力される。

【0022】

図4は、本発明の一実施形態による利得回路46を示している。利得回路は、受動回路素子R1、R2、R5、R6、及びR9を含むMSB受動部分と、受動回路素子R3、R4、R7、R8、及びR9を含むLSB受動部分とを含む。MSB受動回路素子は、MSB DAC43のMSBアナログ出力に対する大きな信号利得(たとえば利得=3.0)を促進するために構成的に選択される。LSB受動回路素子は、LSB DAC45からのLSBアナログ出力に対するはるかにより小さい信号利得(たとえば利得=0.003)を促進するために構成的に選択される。MSB信号及びLSB信号の両方が利得回路46から増幅器48に出力される。この増幅器において、これらの信号は合成されて、(23ビット精度の)1つの高精度アナログ信号となる。

【0023】

図5は、本発明の一実施形態による、ODC40によって実行されるプロセスのフロー図を示している。23ビットデジタルデータ信号がSPC30によって処理されてMSB部分及びLSB部分にセグメント化された後、プロセスはブロック50において開始する。ブロック52において、ODC40がSPC30からセグメント化されたビット信号データを受信する。次に、ブロック54においてSVDAC42が、ブロック56における変換処理のために、MSBデータをMSB DAC43に割り当て、LSBデータをLSB DAC45に割り当てる。この変換処理中、MSB DAC43及びLSB DAC45は独立して、セグメント化されたデジタル信号をアナログ信号に変換する。次いでブロック58において、利得回路46において利得処理が実行される。これによって、MSBアナログデータの大きな利得及びLSBアナログデータのより小さな利得が促進される。ブロック60において、MSBアナログデータ及びLSBアナログデータが合成されて高精度アナログ信号になり、この高精度アナログ信号がIOC10を駆動するために使用される。ブロック62において、駆動処理が終了する。

【技術分野】

【0001】

本発明は、包括的にはジャイロシステムに関し、より詳細には干渉方式光ファイバジャイロ(IFOG)において光信号を変調することに関する。

【背景技術】

【0002】

回転速度又は回転軸周りの角速度における変化を測定するためにジャイロが使用されてきた。基本的な従来の光ファイバジャイロ(FOG)は、光源と、ビーム生成装置と、感知軸の周りのエリアを取り囲むビーム生成装置に結合される光ファイバのコイルとを備える。ビーム生成装置は複数の光ビームをコイル内に送る。これらの光ビームは時計回り(CW)方向及び反時計回り(CCW)方向に光ファイバのコアに沿って伝搬し、両方とも最終的には光検出器(たとえば、光検出システムに電気的に結合されるフォトダイオード)に入射する。多数のFOGが、光をファイバの中実ガラスコアに沿って伝導するガラス系光ファイバを利用する。これらの2つの反対伝搬(counter-propagating)(たとえばCW及びCCW)ビームは、1つの回転閉光路又はループを伝搬して回る間に異なる光路長を経験する。たとえば、感知軸を中心とした回転は一方の回転方向において光路長を増大し、他方の回転方向において光路長を低減する。2つの光路長における差は、両方の回転方向の光ビーム間に位相シフトを導入する(すなわちサニャック効果)。この差は、囲まれているエリアに垂直である回転速度に比例する。

【0003】

ループにおける反対伝搬光ビーム間の位相差は典型的には、バイアス信号生成器に結合される光位相変調器を使用して、回転検出に対する感度を増大するために変調される。光位相変調器は、光検出システムからのフィードバックループにおいて動作して、感知軸を中心とした回転からもたらされる、反対伝搬光ビーム間の位相シフト差を相殺するのに十分な負のフィードバックを提供することができる。一例では、位相感知検出器が光検出器出力電流を表す信号を受信し、光検出器に入射する光ビームの相対的位相の指示を提供する。変調周波数において位相感知検出器によって復元されるあらゆる重要な信号内容は回転速度に比例する。

【0004】

位相感知検出器からの信号を使用して、一方の光ビームを他方のビームに対して位相シフトし、互いに同位相の反対伝搬ビームをもたらすことができる。たとえば、位相感知検出器からの信号を、積分器のような累算器を有するサーボエレクトロニクスに供給することができる。回転中に生成された位相差に応じて、サーボエレクトロニクスは、一方の光ビームを他方のビームに対して位相シフトするための信号を供給する。フィードバックループのデジタル実装においては、(たとえば位相検波器による使用のために)アナログ/デジタル変換器(ADC)が光検出器のアナログ出力をデジタルの対応するものに変換し、デジタル/アナログ変換器(DAC)が、光位相変調器を介する位相シフトのためにサーボエレクトロニクスからのデジタル信号をアナログ信号に変換する。

【0005】

非常に低い回転速度及びほぼゼロ度(±或る所定の値)の位相の検出においては、ジャイロスコープは概して位相検出に対する感度がより低い。この領域は「不感帯」と呼ばれ、不感帯誤差は幾つかの理由から生じ得る。不感帯の1つの原因は、サーボエレクトロニクスからのデジタル信号をDACに供給する前により低いビット値に切り捨てることから生じる。この切り捨ては、振動の存在下で調整されて速度誤差となる(rectify into rate error)可能性がある非対称性を導入する可能性もある。加えて、ループ誤差が、適切な位相シフトに収束するのに著しい量の時間を要する場合があり、この収束の時間は、DACに供給される信号の切り捨てによってさらに延長される場合がある。

【0006】

上記で論じた光ファイバジャイロのような閉ループ光センサは典型的には、光学集積回路(IOC)変調構成要素を含む。この構成要素は、単一の高分解能デジタル/アナログ変換器(DAC)から受信される、12ビット〜16ビットの切り捨てられる信号によって駆動される。これらのセンサの分解能計量は実質的に、該センサのIOC駆動構成要素内の1つのみの高分解能DACの使用に関連付けられるデータ切り捨てによって制限される。高精度の用途では、これらの切り捨て信号は望ましくない不感帯誤差をもたらす可能性がある。たとえば、12ビット分解能DACの最下位ビットが数百度/時間のバイアス誤差にまでなる。長時間にわたって閉ループアーキテクチャはゼロに平均化するバイアス誤差を維持するが、角度白色雑音(angle white noise)に関しては量子化誤差が残る。

【0007】

閉ループ光ファイバジャイロにおいてビット分解能を向上させるのに利用される1つの解決策は、IOC駆動装置においてより高い分解能のDACを採用することである。残念ながら、これらの高分解能変換器は高価であり、依然として23ビット分解能をはるかに下回る切り捨てを必要とする。光ファイバジャイロのIOC駆動回路内の単一のDACの使用に関連付けられる切り捨て誤差を低減するのに利用される別の解決策は、信号処理又は駆動構成要素に雑音及び平均化を導入する技法を実施することである。残念ながら、このような技法は不可避的に、特定の望ましくない雑音を変換器構成要素にもたらす。この望ましくない雑音は、一貫性のないセンサ出力及び低減したシステムスループットを引き起こす可能性がある。

【発明の概要】

【発明が解決しようとする課題】

【0008】

したがって、閉ループ誤差を低減する閉ループ光センサを提供することが望ましい。さらに、本発明の他の望ましい特徴及び特性は、添付の図面及び本発明のこの背景技術と共に考慮される本発明の後続の詳細な説明及び添付の特許請求の範囲から明らかとなるであろう。

【課題を解決するための手段】

【0009】

本発明は、光センサシステム内の光駆動回路の出力分解能を向上させるシステム及び方法を提供する。一例の光センサシステムは、アナログ測定データを生成する光学回路と、アナログ測定データを検出し、その後アナログ測定データをデジタル測定データに変換する検出器回路と、デジタル測定データを復調し、その後、復調されたデジタル測定データに基づいてセグメント化されたデジタル信号を生成する信号処理回路と、セグメント化されたデジタル信号に基づいてアナログ駆動信号を生成する光学駆動回路とを備える。アナログ駆動信号が使用されて光学回路が駆動される。

【0010】

本発明の他の態様によれば、光学駆動構成要素は、セグメント化されたデジタル信号の第1のデジタルデータセグメントを第1のアナログデータセグメントに変換する第1の変換器と、セグメント化されたデジタル信号の第2のデジタルデータセグメントを第2のアナログデータセグメントに変換する第2の変換器とを備える。

【0011】

本発明のさらなる態様によれば、第1のデジタルデータセグメントは第2のデジタルデータセグメントよりも上位のビットのデータに対応する。

本発明のさらなる態様によれば、光駆動回路は第1のアナログデータセグメント及び第2のアナログデータセグメントを増幅し、その後、これらの増幅されたアナログデータセグメントを合成し、単一のアナログ駆動信号にする。

【0012】

本発明のさらに他の態様によれば、光駆動回路の生成されたアナログ駆動信号は第1の変換器よりも高い分解能を有する。

本発明のさらに別の態様によれば、生成されたデジタル測定データ及びアナログ駆動信号は、少なくとも16ビット分解能を有するデータに対応する。

【0013】

上記概要から容易に理解されるように、本発明は、光センサ内の光駆動構成要素の出力分解能を向上させる手段を提供する。

本発明の好ましい実施形態及び代替の実施形態を、以下の図面を参照して以下において詳細に説明する。

【図面の簡単な説明】

【0014】

【図1】本発明の一実施形態に従って形成される閉ループ光ファイバジャイロのブロック図を示す。

【図2】本発明の一実施形態に従って形成されるIOC駆動構成要素のブロック図を示す。

【図3】本発明の一実施形態に従って形成されるIOC駆動装置内のセグメント化されたDAC構成要素のブロック図を示す。

【図4】本発明の一実施形態に従って形成されるIOC駆動装置内の利得回路を示す。

【図5】本発明の一実施形態に従って形成されるIOC駆動装置に関連付けられるプロセスのフロー図を示す。

【発明を実施するための形態】

【0015】

本発明は、光センサ装置内の光駆動回路の出力分解能を向上させるシステム及び方法に関する。少なくとも1つの実施形態によれば、光駆動回路の出力ビット分解能は、光駆動回路内の2つの別個の変換器構成要素間のデータ変換をセグメント化することによって大幅に増大することができる。

【0016】

図1は、本発明の一実施形態に従って形成される光センサ8の閉ループアーキテクチャを示している。閉ループセンサ8は、光集積回路(IOC)10と、光検出回路(PDC)20と、信号処理回路(SPC)30と、光学駆動回路(ODC)40とを備える。閉ループ光センサ8は、任意の数の異なるタイプの閉ループセンサのうちの1つ、たとえば閉ループ光ファイバセンサ及びジャイロとすることができる。

【0017】

光センサ8が閉ループ光ファイバジャイロとして実装される場合、センサ8は、IOC10の光ファイバコイルを反対方向(たとえば、時計回り方向及び反時計回り方向)に進んで回る2つの光のビーム間の位相差を求めることによって、角速度又は特定の回転軸周りの速度を測定する。IOC10のアナログ光出力はPDC20に通信される。このPDCにおいて、アナログ光出力は増幅されて、デジタル位相シフトデータに変換される。次に、PDC20のデジタル位相シフトデータはジャイロのSPC30に通信される。このSPCにおいて、デジタル位相シフトデータは復調及び検出されて、ODC40に通信される。次に、ODC40は、復調されたデジタル位相シフトデータをアナログ形式に変換し、アナログデータを増幅し、次いで、増幅されたアナログデータをフィードバックループを通じてIOC10に通信する。

【0018】

光ファイバジャイロによって測定されるビット分解能は、データ変換及び後続の信号処理の前では、23ビットにまで高くすることができる。たとえば、従来の非セグメント化IOC駆動装置は、位相シフトを23ビット分解能で測定し、次いで、SPC30において生じる切り捨て処理ステップ中にこの分解能を16ビット未満に低下させる。これらのシステムでは、ビットデータは、ODC40内の単一の高分解能DACに通信される前に切り捨てられる。この切り捨ては、データの最下位ビット(LSB)の2分の1もの大きさを有する誤差をもたらす可能性がある。ジャイロのループは、この2分の1LSBデータ誤差を補正しようと試みる場合、1つのLSBだけビット分解能を増大又は低減することしかできない。これは誤差の符号を不正確に変更してしまう。

【0019】

対照的に、本発明のSPC30は、このような切り捨て処理ステップを必要とせず、従来の非セグメント化IOC駆動装置に関連付けられる2分の1LSBデータ誤差を除去する。本発明のSPC30は、ODC40内の並列デジタル/アナログ変換器(DAC)における処理のために、23ビットデータを最上位ビット(MSB)データ部分(典型的には10ビット〜14ビットの長さの範囲を有する)及びLSBデータ部分(残りのビット分解能を含む)にセグメント化する。本発明の代替の一実施形態によれば、MSB/LSBデータセグメント化は、SPC30においてではなくODC40において生じる。次に、ODC40の並列DACは、23ビットのセグメント化されたMSB/LSBデータをアナログ信号データに変換し、次いで、IOC10を駆動するためにこの高精度信号データを増幅及び合成する。本発明の一実施形態によれば、アナログ信号データの合成は増幅ステップ前に生じる。

【0020】

図2は、本発明の一実施形態に従って形成されるODC40を示している。ODC40は、セグメント化されたビデオDAC(SVDAC)42と、利得回路46と、増幅器構成要素48とを備える。SVDAC42は、23ビットデジタル信号を表すデータをSPC30から受信する。この信号は、MSB構成部分とLSB構成部分とにセグメント化され、次いでSVDAC42によってアナログ信号に変換される。変換処理後、利得回路46を利用して、アナログのMSB信号構成部分及びLSB信号構成部分とに利得が印加される。利得処理後、アナログ信号は、増幅器48によって合成されて、IOC10に出力される。本発明の代替の一実施形態によれば、アナログ信号をIOC10に出力する前に、アナログ信号が増幅器48によって合成された後に利得が印加される。別の実施形態によれば、利得処理は、電気利得処理又は光学利得処理のいずれかを含むことができる。

【0021】

SVDAC42の中身を図3に示す。SVDAC42はMSB DAC43及びLSB DAC45を含む。MSB DAC43は、23ビットデータ信号からセグメント化された最上位ビットのデータを受信及び変換し、LSB DAC45は、同じ23ビット信号からセグメント化された最下位ビットのデータを受信及び変換する。本発明の一実施形態によれば、MSB/LSBデータセグメント化はSPC30において生じる。代替の一実施形態によれば、データセグメント化はODC40内で生じる。一実施形態では、MSB DAC及びLSB DACの両方の変換処理後に、セグメント化されたアナログ信号が利得回路46に出力される。この利得回路は図4において例示されている。代替の一実施形態によれば、セグメント化されたアナログ信号は増幅器48に出力される。

【0022】

図4は、本発明の一実施形態による利得回路46を示している。利得回路は、受動回路素子R1、R2、R5、R6、及びR9を含むMSB受動部分と、受動回路素子R3、R4、R7、R8、及びR9を含むLSB受動部分とを含む。MSB受動回路素子は、MSB DAC43のMSBアナログ出力に対する大きな信号利得(たとえば利得=3.0)を促進するために構成的に選択される。LSB受動回路素子は、LSB DAC45からのLSBアナログ出力に対するはるかにより小さい信号利得(たとえば利得=0.003)を促進するために構成的に選択される。MSB信号及びLSB信号の両方が利得回路46から増幅器48に出力される。この増幅器において、これらの信号は合成されて、(23ビット精度の)1つの高精度アナログ信号となる。

【0023】

図5は、本発明の一実施形態による、ODC40によって実行されるプロセスのフロー図を示している。23ビットデジタルデータ信号がSPC30によって処理されてMSB部分及びLSB部分にセグメント化された後、プロセスはブロック50において開始する。ブロック52において、ODC40がSPC30からセグメント化されたビット信号データを受信する。次に、ブロック54においてSVDAC42が、ブロック56における変換処理のために、MSBデータをMSB DAC43に割り当て、LSBデータをLSB DAC45に割り当てる。この変換処理中、MSB DAC43及びLSB DAC45は独立して、セグメント化されたデジタル信号をアナログ信号に変換する。次いでブロック58において、利得回路46において利得処理が実行される。これによって、MSBアナログデータの大きな利得及びLSBアナログデータのより小さな利得が促進される。ブロック60において、MSBアナログデータ及びLSBアナログデータが合成されて高精度アナログ信号になり、この高精度アナログ信号がIOC10を駆動するために使用される。ブロック62において、駆動処理が終了する。

【特許請求の範囲】

【請求項1】

光センサシステムであって、

アナログ測定データを生成するように構成される光学回路(10)と、

前記アナログ測定データを検出し、前記アナログ測定データをデジタル測定データに変換するように構成される検出器回路(20)と、

前記デジタル測定データを復調し、前記復調されたデジタル測定データに基づいてセグメント化されたデジタル信号を生成するように構成される信号処理回路(30)と、

前記セグメント化されたデジタル信号に基づいてアナログ駆動信号を生成するように構成される光学駆動回路(40)であって、前記アナログ駆動信号が前記光学回路を駆動するために使用される、光学駆動回路(40)と、

を備える、光センサシステム。

【請求項2】

閉ループである、請求項1に記載のシステム。

【請求項3】

光センサ内の光駆動回路の出力分解能を向上させる方法であって、

光回路からアナログ測定データを受信するステップ(52)、

前記受信されたアナログ測定データをデジタル測定データに変換するステップ(54)、

前記デジタル測定データに基づいてセグメント化されたデジタル信号を生成するステップ(54)、及び

前記セグメント化されたデジタル信号に基づいてアナログ駆動信号を生成するステップであって、前記アナログ駆動信号が前記光回路を駆動するために使用される、生成するステップ(60)、

を含む、方法。

【請求項1】

光センサシステムであって、

アナログ測定データを生成するように構成される光学回路(10)と、

前記アナログ測定データを検出し、前記アナログ測定データをデジタル測定データに変換するように構成される検出器回路(20)と、

前記デジタル測定データを復調し、前記復調されたデジタル測定データに基づいてセグメント化されたデジタル信号を生成するように構成される信号処理回路(30)と、

前記セグメント化されたデジタル信号に基づいてアナログ駆動信号を生成するように構成される光学駆動回路(40)であって、前記アナログ駆動信号が前記光学回路を駆動するために使用される、光学駆動回路(40)と、

を備える、光センサシステム。

【請求項2】

閉ループである、請求項1に記載のシステム。

【請求項3】

光センサ内の光駆動回路の出力分解能を向上させる方法であって、

光回路からアナログ測定データを受信するステップ(52)、

前記受信されたアナログ測定データをデジタル測定データに変換するステップ(54)、

前記デジタル測定データに基づいてセグメント化されたデジタル信号を生成するステップ(54)、及び

前記セグメント化されたデジタル信号に基づいてアナログ駆動信号を生成するステップであって、前記アナログ駆動信号が前記光回路を駆動するために使用される、生成するステップ(60)、

を含む、方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2010−38917(P2010−38917A)

【公開日】平成22年2月18日(2010.2.18)

【国際特許分類】

【外国語出願】

【出願番号】特願2009−180986(P2009−180986)

【出願日】平成21年8月3日(2009.8.3)

【出願人】(500575824)ハネウェル・インターナショナル・インコーポレーテッド (1,504)

【Fターム(参考)】

【公開日】平成22年2月18日(2010.2.18)

【国際特許分類】

【出願番号】特願2009−180986(P2009−180986)

【出願日】平成21年8月3日(2009.8.3)

【出願人】(500575824)ハネウェル・インターナショナル・インコーポレーテッド (1,504)

【Fターム(参考)】

[ Back to top ]