除算・開平演算器

【課題】

開平演算における商決定は、除算演算の商決定より論理段数が多く複雑なので、処理性能を揃える場合、開平演算基数は除算基数より低く設定される。商決定を高速に行う為、商決定で参照する部分剰余の上位ビットを2補数で保持する回路構成では、基数に従い冗長数の部分剰余下位ビットから2補数の上位ビットへ2補数変換が必要であるが、演算基数が異なると複数の2補数変換回路と切替え回路が必要であり、回路遅延が増加し、処理速度を落す問題が発生する。

【解決手段】

低基数開平演算の基数と高基数除算演算の基数の差分だけシフトした部分剰余を生成する手段を備える事で、開平演算時に、予め部分剰余を下位側にシフトして置くことで、部分剰余計算後の2補数変換回路を高基数除算処理にあわせる事が出来、回路遅延も増加する事なく、演算処理が行える。

開平演算における商決定は、除算演算の商決定より論理段数が多く複雑なので、処理性能を揃える場合、開平演算基数は除算基数より低く設定される。商決定を高速に行う為、商決定で参照する部分剰余の上位ビットを2補数で保持する回路構成では、基数に従い冗長数の部分剰余下位ビットから2補数の上位ビットへ2補数変換が必要であるが、演算基数が異なると複数の2補数変換回路と切替え回路が必要であり、回路遅延が増加し、処理速度を落す問題が発生する。

【解決手段】

低基数開平演算の基数と高基数除算演算の基数の差分だけシフトした部分剰余を生成する手段を備える事で、開平演算時に、予め部分剰余を下位側にシフトして置くことで、部分剰余計算後の2補数変換回路を高基数除算処理にあわせる事が出来、回路遅延も増加する事なく、演算処理が行える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、除算・開平演算器に関するものであり、特に高基数型の除算器と低基数型の開平器を実装した除算・開平演算器に関する。

【背景技術】

【0002】

除算器・開平器の実装においては、アルゴリズムとして減算シフト法、あるいは減算引き離し法等を用いたものが、ハードウェア量と性能のバランスを考慮して、一般的に用いられている。このアルゴリズムは我々が通常、筆算で除算を行うのと同様に、商の決定を、余り(部分剰余)のシフトと余りからの分母(除数・部分開平値)の倍数の減算により除算を行う手法で、具体的に、n桁単位に商/開平数字が決定され、その商/開平数字の決定にもとづいて部分剰余が計算され、次の演算ステップでは、この部分剰余値がn桁シフトされ、それにもとづいて次のn桁の商/開平数字が決定され、という具合に、繰り返し演算を行うことで実行される。

【0003】

このn桁単位に商/開平数字を決定して行く方法は、2のn乗をr(これを基数と呼ぶ)とするとき、基数rの除算/開平法と呼ばれている。このようなアルゴリズムの除算処理について述べたものとして、「コンピュータの高速演算方式、1980、近代科学社、pp.214−249」(非特許文献1)には、回復型除算、非回復型除算、SRT除算、拡張SRT除算といった各種の除算手法について述べられている。

【0004】

減算シフト法を用いた除算の手順について簡単に説明する。

【0005】

演算のビット長(商/開平数字を決定していく単位桁数)をn(任意の正整数)、演算の基数をr(=2のn乗)、除数をD、被除数をR(0)、jを0以上の整数としてj回目の部分剰余をR(j)、j回目の商をq(j)とする。また、ここでは除数D、被除数R(0)は正規化されているとする。ここでは正規化浮動小数点フォーマットとして、「1.xxxx」を用いるものとし、除数、被除数共に正規化されているとする。本フォーマットに合致しないデータ形式を扱う場合でも、演算前後に適当なシフト処理を実行することで本浮動小数点フォーマットについての処理を適用可能である。

【0006】

ここで使用される商及び部分剰余は、冗長2進表現により表される。すなわち、2補数表現であれば各ビットが{0,1}で表されるところを、{−1,0,1}の3値を採ることを許し、負の値を可能としている。

【0007】

入力データが上述のように正規化されている条件の下で、次の(1)式に示される漸化式を用いて、順次、商及び部分剰余を求めることができる。

【0008】

R(j+1)=r×R(j)-q(j+1)×D・・・(1)

SRT法では、商デジットとして{0,1}に加えて{−1}をとり、部分剰余の上位数ビットで高速に商デジットを判定できる方法である。SRTアルゴリズムは、開平演算にも適用できるので、除算ハードウェアの使用が可能である。

【0009】

開平演算の手順について簡単に説明する。

【0010】

演算の基数をr、被開平数をR(0)、jを0以上の整数としてj回目の部分剰余をR(j)、部分開平値をQ(j)、j回目の商をq(j)とする。被開平数R(0)は正規化されているとする。部分開平値Q(j)は、j回目まで算出された商である。

【0011】

ここで使用される商(部分開平値も含む)及び部分剰余は、冗長2進表現により表される。すなわち、2補数表現であれば各ビットが{0,1}で表されるところを、{−1,0,1}の3値を採ることを許し、負の値を可能としている。

【0012】

入力データが上述のように正規化されている条件の下で、次の(2)、(3)式に示される漸化式を用いて、順次、商及び部分剰余を求めることができる。

【0013】

R(j+1)=r×R(j)-q(j+1)×(r×Q(j)+q(j+1)×r-(j+1))・・・(2)

Q(j+1)=Q(j)+q(j+1)×r-(j+1) ・・・(3)

開平演算では、j回目の部分剰余から部分開平値を減算する演算により、j+1回目の部分剰余算出を行うアルゴリズムとなっており、そのまま処理を行うとすると、冗長2進数表現の部分剰余と冗長2進数表現の部分開平値との演算となり、複雑な演算となってしまう。

冗長2進数表現の部分開平値が全て求まってから2補数表現に変換すると、変換に要する時間が計算時間に追加されてしまい、処理低下を招く。

【0014】

そこで、除算で実現したハードウェアを開平演算で共用する為に、オン・ザ・フライ変換と呼ばれる回路によって、商決定と同時に得られた部分開平値を2補数表現に変換して、冗長2進数表現の部分剰余と2補数表現の部分開平値の演算として処理を行う。

【0015】

オン・ザ・フライ変換は、例えば非特許文献2(On-the-fly conversion of redundant into conventional representations、エム.ディ.エルセゴバック及びティ.ラング、IEEE Transactions on Computers、第36巻第7号、1987年6月、895〜897頁)に開示されている。

【0016】

基数2の場合のオン・ザ・フライ変換について簡単に説明する。

例えば、冗長2進表現{1,-1}を2補数表現に変換すると{0,1}となる(いずれも10進数で1を表す)。冗長2進から2補数への変換を加算と減算で実現すると,-1が入力されたときにキャリー伝播するので、この例では-1が入力される前の値{1,0}以外に、{0,1}を用意しておき、-1が入力されたとき、{0,1}を選択すればキャリー伝播は発生しない。つまり、キャリーの伝播を無くし固定時間で処理するために,-1が入力された場合の答え(言い換えるなら1小さい表現)を予め内部に用意しておけば、キャリー伝播を抑止できる事になる。

【0017】

冗長2進表現で上位桁から順に求まる商Qと、2補数表現の商Z の小数点以下j桁までをそれぞれQ(j)(=.q(1)q(2)・・・q(j))とZ(j)(=.z(1)z(2)・・・z(j))とすると、上記からZ(j)は、Q(j)またはQ(j)−2-jのいずれかの2補数で表せる。従って、各演算ステップで、Q(j)およびQ(j)―2-jの2補数表現を保持しておけば、q(j)が求まった時点で、即座にZ(j)を求める事が出来る。

【0018】

演算途中のj+1回目の商デジットをq(j+1)とし、Q(j)またはQ(j)−2-jの2補数をそれぞれQP(j)、QN(j)とし、部分開平値正、部分開平値負と呼ぶ事にする。演算を基数に従い処理を行い、q(j+1)が求まれば、QP(j)、QN(j)から次のようにQP(j+1)、QN(j+1)を求める事が出来る。q(j+1)=−1の場合は、

QP(j+1)= QP(j)−2-(j+1)=QN(j)+2-j−2-(j+1)=QN(j)+2-(j+1) ・・・(4)

QN(j+1) {=QP(j+1)−2-(j+1)}=QP(j)−2-(j+1)−2-(j+1)=QP(j)−2-j=QN(j) ・・・(5)

q(j+1)=0の場合、

QP(j+1)= QP(j) ・・・(6)

QN(j+1)= QN(j) +2-(j+1) ・・・(7)

q(j+1)=1の場合、

QP(j+1)= QP(j)+2-(j+1) ・・・(8)

QN(j+1) {=QP(j+1)−2-(j+1)}=QP(j)+2-(j+1)−2-(j+1)=QP(j) ・・・(9)

式(4)と式(7)と式(8)は、Qx(j+1)=Qy(j)+2-(j+1) (演算の基数を2と仮定している)で表せる。この演算は、j桁目までの部分開平値Qy(j)の後ろに、j+1桁目の商(0または1)であるq(j+1)のビット列を連結するだけでよいので、実質的に演算は行われない。他式は、QP(j)かQN(j)を選択すればよい。これは、j回目の部分開平値正であるQP(j)、部分開平値負であるQN(j)を求めて保持しておくことにより、j+1回目の部分開平値Q(j+1)すなわちQP(j+1)は、単純なビット演算のみで、冗長2進数から2補数(通常数)を得る事が出来る。

【0019】

また、SRT法による除算演算方法については、特開2001−222410「除算器」(特許文献1)に記載されている。特許文献1には、除数を5/3≦除数<1.75の範囲にスケーリングを行うことにより、部分剰余の上位4ビットの正規化及びその4ビットの参照により、商2bitを決定(基数4の除算回路)することができるという効果が報告されている。

【0020】

除算演算の部分剰余生成は、固定値の除数Dを考慮して減算すれば実現出来るので、除数範囲をスケーリングする事で高基数を実現できるが、開平演算の部分剰余生成は、j回目の部分開平値Q(j)と商q(j)を考慮して減算する必要があり、高基数を実現するには、商生成桁の1つ前の商考慮が必要であるので、回路が複雑となり、処理にも時間を要する事になる。高基数の開平演算処理について、非特許文献3((「Radix-4 square root without initial PLA」、エム.ディ.エルセゴバック及びティ.ラング、IEEE Transactions on Computers、第39巻第8号、1990年8月、1016〜1024頁」)に部分開平値3ビットと部分剰余上位7ビットから商2ビットを決定できる例が記載されているが、このように高基数の開平演算を採用しようとすると、開平演算の商決定回路規模や論理段数が複雑となる。

【0021】

また、特開平10−187420「除算・開平演算器」(特許文献2)に除算演算器と開平演算器とを共用したものが開示されている。

【0022】

【特許文献1】特開2001−222410「除算器」

【特許文献2】特開平10−187420「除算・開平演算器」

【非特許文献1】コンピュータの高速演算方式、1980、近代科学社、pp.214−249

【非特許文献2】On-the-fly conversion of redundant into conventional representations、エム.ディ.エルセゴバック及びティ.ラング、IEEE Transactions on Computers、第36巻第7号、1987年6月、895〜897頁

【非特許文献3】Radix-4 square root without initial PLA、エム.ディ.エルセゴバック及びティ.ラング、IEEE Transactions on Computers、第39巻第8号、1990年8月、1016〜1024頁

【発明の開示】

【発明が解決しようとする課題】

【0023】

上述のように高基数の開平演算における商決定は、高基数の除算より論理段数が多く複雑なので、除算演算と開平演算で同じ基数を採用した場合、開平演算の論理段数が処理性能を決めてしまう事になり、除算処理性能が落ちてしまう問題が発生する。除算処理性能を落さない為には、開平演算の基数は除算演算より低く設定される事になる。例えば、開平演算で部分剰余上位4ビット参照の回路方式を実現するには、基数2の採用が妥当である。

【0024】

特許文献2は、低基数である基数2の除算器と除算器と同じ基数2の開平演算について開示しているが、高基数の除算と低基数の開平演算を行う除算・開平演算器については開示していない。

【0025】

本発明の目的は、このような事情に鑑みてなされたもので、除算と開平演算に多くの部分を共用でき効率的であるとともに、除算演算の基数を開平演算より高く設定でき、除算処理性能を落とすことがない除算・開平演算器を提供することにある。

【課題を解決するための手段】

【0026】

上記目的を達成するために、本発明の除算・開平演算器は、高基数の除算及び低基数の開平演算を行う除算・開平演算器において、部分剰余の上位ビットを参照して商を定める商生成手段と、前記部分剰余の前記上位ビットを2補数表現で保持し、前記部分剰余の前記上位ビット以外の下位ビットは冗長2進数表現で保持する部分剰余保持手段と、除数と部分開平値を演算種別に応じて切り替えて保持する除数・部分開平値保持手段と、前記商により前記除数・部分開平値保持手段からの除数及び部分開平値を選択する除数・部分開平値選択回路と、前記下位ビットの冗長2進数表現の部分剰余と前記除数・部分開平値選択回路の出力とを入力する桁上げ保存加算器と、前記上位ビットの2補数表現の部分剰余、前記下位ビットの冗長2進数表現の部分剰余、前記除数・部分開平値選択回路の出力、及び前記桁上げ保存加算器のキャリー信号を加算する桁上げ伝播加算器と、前記桁上げ保存加算器の出力の上位ビットから基数に基づくビット数のビットデータ及び桁上げ伝播加算器の出力を入力して2補数化し演算の基数に基づくビット数シフトして次回の部分剰余として使用する2補数化・シフト手段とを有する。

【0027】

また、前記2補数化・シフト手段は、除算と開平演算の基数の違いにより定められるビット数、前記上位ビットの2補数表現の部分剰余を下位へシフトして前記桁上げ保存加算器に入力する第1のシフタと、前記基数の違いにより定められるビット数、前記下位ビットの冗長2進数表現の部分剰余を下位へシフトして前記桁上げ伝播加算器に入力する第2のシフタと、前記桁上げ保存加算器の出力の上位ビットから前記高基数に基づいて取り出したビット数のビットデータ及び前記桁上げ伝播加算器の出力を入力して2補数化する2補数変換手段と、前記2補数変換手段の出力を次回の部分剰余として使用するよう前記高基数に基づくビット数シフトする第3のシフタとを有するものとしてもよい。

【発明の効果】

【0028】

本発明によれば、桁上げ保存加算器の出力の上位ビットから演算の基数に基づくビット数のビットデータと、桁上げ伝播加算器の出力とを入力して2補数化し、演算の基数に基づくビット数シフトして次回の部分剰余として使用する。これにより除算と開平演算において、除数と部分開平値とのレジスタ共有などの多くの部分を共用できる効率的な回路となり、除算演算の基数を開平演算より高く設定でき、除算処理性能を向上することができる。

【0029】

さらに開平演算の場合、除算演算と開平演算の基数の違いにより定められるビット数、前記上位ビットの2補数化された部分剰余及び前記下位ビットの冗長2進数の部分剰余をシフトして加算器及び桁上げ保存加算器に入力し、桁上げ保存加算器の出力の上位ビットから高基数に基づいて取り出したビット数のビットデータと加算器の出力とを入力して2補数化し、高基数に基づくビット数シフトして次回の部分剰余として使用することにより、部分剰余から除数を減算した結果を部分剰余レジスタに戻すパスの回路遅延時間が抑制し、除算演算と開平演算の処理速度を向上させることができる。

【発明を実施するための最良の形態】

【0030】

次に、本発明の構成について図面を参照して詳細に説明する。

【0031】

以下に説明する実施形態においては、除算演算の基数が4、デジット集合が{−3、−2、−1、0、1、2、3}、除数、被除数がnビット長の少数で、演算アルゴリズムに拡張SRT除算アルゴリズムを採用し、開平演算の基数が2、デジット集合が{−1、0、1}、被開平数がnビット長の少数で、演算アルゴリズムにSRT開平アルゴリズムを採用している回路について説明する。

【0032】

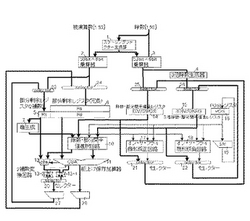

図1は、本発明の除算・開平演算器の第1の実施形態の構成を示すブロック図である。

【0033】

スケーリングファクタ生成部1は、スケーリングに用いる乗算係数を生成する。スケーリングファクタ生成部1は、除算演算では、除数から除数を5/3≦除数<1.75の範囲にスケーリングを行うための乗算係数を生成するが、開平演算では、乗算係数=1で処理を行う。53ビット×6ビット乗算器2,3が、スケーリングファクタ生成部1が出力した乗算係数を、入力された53ビットの除数、被除数に乗算して出力する。このことにより、部分剰余の上位4ビットの正規化及びその4ビットの参照により、商2bitを決定(基数4の除算回路)できる。

【0034】

基数4の除算演算は、除数範囲を5/3≦除数<1.75の範囲にスケーリングを行うことで、部分剰余上位4ビットから商2ビットを生成出来、開平演算においても、部分剰余上位4ビットだけで商生成する方式を採用出来れば、除算処理性能を落さない事が可能となる。

【0035】

除数3倍数生成部4は、53ビット×6ビット乗算器2の出力を3倍して除数3倍数を生成し、出力する。

【0036】

部分剰余レジスタ5は、2補数表現の部分剰余上位4ビットを保持する。

【0037】

部分剰余レジスタ6は、部分剰余レジスタ5で保持される上位ビット以外の下位ビットを冗長2進数表現で保持する。

【0038】

商生成回路7は、レジスタ5に保持された2補数表現の部分剰余上位4ビットから、除算においてはデジット集合{−3、−2、−1、0、1、2、3}のうちから、開平演算においてはデジット集合{−1、0、1}のうちから1つを選択し、商を生成する。

【0039】

除数・部分開平値選択回路10は、除算動作時は商生成回路7で生成された商により除数を選択する。また開平動作時は商生成回路7で生成された商とPOSITION レジスタ16のPOSITIONデータとから部分開平値を選択する。

【0040】

桁上げ保存加算器(Carry Save Adder)11は、部分剰余レジスタ6からの下位ビットの冗長2進数表現の部分剰余と除数・部分開平値選択回路10の出力を入力データとし、桁上げ伝播なく加算する。キャリー発生する場合は、キャリー信号をキャリー伝播加算器(Carry Propagate Adder)12に出力する。

【0041】

キャリー伝播加算器(Carry Propagate Adder)12は、部分剰余レジスタ5からの上位ビットの2補数表現の部分剰余と、除数・部分開平値選択回路10の出力と、加算器11のキャリー信号を加算する。

【0042】

部分剰余から除数・部分開平値選択データ減算後の部分剰余データのシフト操作で基数を考慮する必要があり、基数2である開平演算の場合、j回目の部分剰余から除数・部分開平値選択データを減算した結果を、1ビット左シフトしてj+1回目の部分剰余データとして使用する。一方、基数4である除算の場合、j回目の部分剰余から除数・部分開平値選択データを減算した結果を、2ビット左シフトしてj+1回目の部分剰余データとして使用する。加えて、部分剰余上位ビットは、商生成で参照するデータを2補数表現で保持することで、商生成を高速しているので、上記シフト処理では冗長2進数表現の下位ビットからシフトビット分だけ2補数表現のデータに変換する2補数変換回路13―1、13―2を使用しながら、シフト処理を行っている。

【0043】

2補数変換回路13―1は、桁上げ保存加算器11の出力の上位ビットから除算の基数に基づいて2補数化する必要のあるビット数、ここでは2ビットのデータを取り出し、2補数化する。2補数変換回路13−2は、桁上げ保存加算器11の出力の上位ビットから開平演算の基数に基づいて2補数化する必要のあるビット数、ここでは1ビットのデータを取り出し、2補数化する。セレクタ20は、除算においては2補数変換回路13―1の出力を、開平演算においては2補数変換回路13−2の出力を選択する。シフタ27は、除算においてはセレクタ20の出力を2ビットシフトし、開平演算においては1ビットシフトしてセレクタ23に入力する。シフタ28は、桁上げ保存加算器11の出力の2補数変換回路13―1に出力した上位ビット以外の下位ビットを、除算においては2ビットシフトし、開平演算においては1ビットシフトしてセレクタ24に入力する。

【0044】

除数・部分開平値正レジスタ14は、除算においては除数、開平演算においては部分開平値を保持する。

【0045】

3倍除数・部分開平値負レジスタ15は、除算においては3倍除数、開平演算においては部分開平値-1を保持する。

【0046】

POSITIONレジスタ16は、開平演算において商生成回路7で生成した商デジットと部分開平値を結合する為の処理ビット情報を保持する。

【0047】

オン・ザ・フライ商生成正回路17は、従来技術と同様に、商生成と並行して、冗長2進数表現のデータから2補数表現のデータへの変換を行うため、従来技術と同様に2補数表現の部分開平値データを生成する。

【0048】

オン・ザ・フライ商生成負回路18は、従来技術と同様に商生成と並行して、冗長2進数表現のデータから2補数表現のデータへの変換を行うため、従来技術と同様に2補数表現の部分開平値-1データを生成する。

【0049】

シフタ19は、POSITION レジスタ16のPOSITIONデータをサイクル毎に1ビット右シフトする。

【0050】

セレクタ21は、開平演算においてはオン・ザ・フライ商生成正回路17の出力、除算においては除数・部分開平値正レジスタ14の出力を選択する。

【0051】

セレクタ22は、開平演算においてはオン・ザ・フライ商生成負回路18の出力、除算においては3倍除数・部分開平値負レジスタ15の出力を選択する。

【0052】

セレクタ23は、1サイクル目は乗算器2の出力、2サイクル以降はシフタ27を経由した2補数変換回路13の出力を選択する。

【0053】

セレクタ24は、1サイクル目は乗算器2の出力、2サイクル以降は桁上げ保存加算器11の出力を選択する。

【0054】

セレクタ25は、1サイクル目は乗算器3の出力、2サイクル以降はセレクタ21の出力を選択する。

【0055】

セレクタ26は、1サイクル目は3倍除数生成器4の出力、2サイクル以降はセレクタ22の出力を選択する。

【0056】

次に図1の除算演算の動作について説明する。

【0057】

まず、スケーリングファクタ生成部1は、除数上位ビットから除数を5/3≦除数<1.75の範囲にスケーリングを行う乗算係数を生成する。

【0058】

生成した乗算係数を、53ビット×6ビット乗算器2,3に入力し、除数、被除数をスケーリングし、スケーリング後の除数から3倍除数を3倍除数生成器4で生成する。

【0059】

セレクタ23,24,25,26は、1サイクル目は乗算器2,3と3倍生成器4を選択し、部分剰余レジスタ5,6、除数・部分開平値正レジスタ14、3倍除数・部分開平値負レジスタ15に入力する。

【0060】

乗算器2から冗長2進数表現で部分剰余の下位ビットがセットされる部分剰余レジスタ6には、{−1}の値は生成されていないので、{0,1}の数値がセットされる。

【0061】

部分剰余の上位ビットがセットされ2補数表現で保持された部分剰余レジスタ5の内容から、商生成回路7が商2ビットを生成する。

【0062】

生成された商から除数を選択する為、除数・部分開平値選択回路10で、スケーリングされた除数の{−3倍、−2倍、−1倍、0、1倍、2倍、3倍}データから選択する。

【0063】

選択された除数の下位ビットと、冗長2進数表現で保持された部分剰余の下位ビットを入力して桁上げ伝播の無い桁上げ保存加算器11で計算を行う。

【0064】

桁上げ保存加算器11からキャリー発生する場合は、キャリー伝播加算器12にキャリー信号を送信する。

【0065】

キャリー伝播加算器12では、部分剰余レジスタ5からの部分剰余の上位ビットと、選択された除数の上位ビットと、桁上げ保存加算器11からのキャリー信号を入力して加算を行う。

【0066】

次サイクルで使用する部分剰余は、基数に従い2ビットシフトする必要があるが、部分剰余データの商生成で必要なビット数は2補数化して保持しているので、桁上げ保存加算器11からの冗長2進数表現の部分剰余下位ビットから、2補数化することが必要な2ビット分を2補数変換回路13−1で変換し、得られた2補数表現の部分剰余上位ビットを、セレクタ20、23を介し、シフタ27で2ビット左シフトして、部分剰余レジスタ5にセットし、次桁の商生成を行っていく。

【0067】

併せて、同様に、桁上げ保存加算器11の冗長2進数表現の出力のうち、2補数変換回路13―1、13−2に出力した上位ビット以外の下位ビットを、シフタ28により、除算においては2ビットシフトし、開平演算においては1ビットシフトし、セレクタ24を介して部分剰余レジスタ6にセットする。

【0068】

除算演算においては、除数、3倍除数は固定値を使用するので、除数・部分開平値正レジスタ14のデータをセレクタ21で選択し、さらにセレクタ25ではセレクタ21を選択する事で除数データを保持する。同様に、3倍除数・部分開平値負レジスタ15に保持された3倍除数データをセレクタ22で選択し、さらにセレクタ26ではセレクタ22を選択する事で保持する。

【0069】

次に図2の開平演算の動作について説明する。

【0070】

開平演算では、除数の変わりに部分開平値を用いて部分剰余計算が行われる。被演算数を乗算器2とセレクタ23、24を介して、部分剰余レジスタ5,6にセットする。

【0071】

2補数表現で保持された部分剰余レジスタ5から商1ビットを生成する。

【0072】

1回目の部分開平値R(0)=0なので、除数・部分開平値正レジスタ14と3倍除数・部分開平値負レジスタ15には0がセットされている。

【0073】

除数・部分開平値選択回路10には商生成回路7で生成された商から部分開平値が選択される。

【0074】

選択された部分開平値の下位データと、部分剰余レジスタ6からの部分剰余下位データを入力して桁上げ伝播の無い桁上げ保存加算器11で計算を行う。

【0075】

桁上げ保存加算器11からキャリー発生する場合は、キャリー伝播加算器12にキャリー信号を送信する。

【0076】

キャリー伝播加算器12では、部分剰余レジスタ5からの部分剰余上位データと、選択された部分開平値と、桁上げ保存加算器11からのキャリー信号を入力して加算を行う。

【0077】

次サイクルで使用する部分剰余は、基数に従いシフトしたデータを使用する為、1ビット左シフトする事になる。

【0078】

桁上げ保存加算器11からの冗長2進数表現の部分剰余下位ビットから2補数化するのに必要な1ビット分を2補数変換回路13−2で変換し、セレクタ20、23を使用し、シフタ27で1ビット左シフトして、レジスタ5にセットし、次桁の商生成を行っていく。

【0079】

同様に、桁上げ保存加算器11の冗長2進数表現の出力のうち、2補数変換回路13―1、13−2に出力した上位ビット以外の下位ビットを、シフタ28により、除算においては2ビットシフトし、開平演算においては1ビットシフトし、セレクタ24を介して部分剰余レジスタ6にセットする。

【0080】

除数・部分開平値選択回路10に入力される商を結合した部分開平値は、冗長2進数表現ではなく2補数表現のデータを入力させるために、商生成回路7で生成された商を考慮しながら、オン・ザ・フライ商生成正回路17と、オン・ザ・フライ商生成負回路18とで従来技術と同様に部分開平値及び部分開平値-1を生成していく。

【0081】

オン・ザ・フライ商生成正回路17は、2補数表現で生成された部分開平値を生成し、セレクタ21、25を介して、除数・部分開平値正レジスタ14に保持される。

【0082】

同様にオン・ザ・フライ商生成負回路18は、2補数表現で生成された部分開平値-1を生成し、セレクタ22、26を介して、3倍除数・部分開平値負レジスタ15に保持されて、次桁の商生成に使用される。

【0083】

POSITIONレジスタ16は、商生成桁を指示する回路であり、初期状態でMSB=1のみがセットされる。

【0084】

シフタ19では、1ビット右シフトされるので、サイクル毎に1ビット右シフトしたデータがPOSITIONレジスタ16にはセットされる事になる。

【0085】

以上説明したように、本発明の除算・開平演算器によれば、桁上げ保存加算器の出力の上位ビットから演算の基数に基づくビット数のビットデータと、加算器の出力とを入力して2補数化し、演算の基数に基づくビット数シフトして次回の部分剰余として使用する。これにより除算回路と開平演算回路において、除数と部分開平値とのレジスタ共用などの共用出来る部分が多く効率的な回路となり、除算演算の基数を開平演算より高く設定でき、除算処理性能を向上することができる。

【0086】

次に、本発明の第2の実施形態について図面を参照して詳細に説明する。

【0087】

図3は、本発明の第2の実施形態の構成を示すブロック図である。

【0088】

第1の実施形態では次回の部分剰余データを生成するには、除算演算で2ビットの2補数化処理、開平演算で1ビットの2補数化処理を行い、加えて除算演算と開平演算で回路を切り替えるセレクタを備えている。部分剰余から除数を減算した結果を部分剰余レジスタに戻すパスは、一番論理段数の多いパスであり、この部分にセレクタを追加すると、回路遅延時間が増加するので、クロックを遅くするか、レジスタ追加が必要になり、除算演算と開平演算の処理速度を低下させてしまうという問題がある。

【0089】

本発明の第2の実施形態は、上記の第1の実施形態と異なり、開平演算において2補数化された部分剰余ビットを右1ビットシフトするシフタ8、及び、開平演算において部分剰余下位ビットを右1ビットシフトするシフタ9を備え、また、2補数変換回路13―1,13−2に変えて、桁上げ保存加算器11の上位ビットから2ビットデータを取り出し、2補数化する2補数変換回路13を備え、j回目の部分剰余から除数・部分開平値選択データを減算した結果を、除算及び開平演算のどちらも、2ビット左シフトしてj+1回目の部分剰余データとして使用することにより、部分剰余から除数を減算した結果を部分剰余レジスタに戻すパスの回路遅延時間が抑制し、除算演算と開平演算の処理速度を向上させるものである。

【0090】

次に本実施形態の除算演算の動作について説明する。第1の実施形態と同様に、まずスケーリングファクタ生成部1は、スケーリングに用いる乗数係数を除数上位ビットから生成する。53ビット×6ビット乗算器2は、入力された乗算係数により、入力された被除数をスケーリングする。53ビット×6ビット乗算器3は、入力された乗算係数により、入力された除数をスケーリングする。3倍除数生成器4は、スケーリング後の除数から3倍除数を生成する。

【0091】

セレクタ23は、1サイクル目は乗算器2の出力を選択し、部分剰余レジスタ5に入力する。セレクタ24は、1サイクル目は乗算器2の出力を選択し、部分剰余レジスタ6に入力する。セレクタ25は、1サイクル目は乗算器3の出力を選択し、除数・部分開平値正レジスタ14に入力する。セレクタ26は、1サイクル目は3倍除数生成器4の生成結果を選択し、3倍除数・部分開平値負レジスタ15に入力する。

【0092】

部分剰余レジスタ5には、上位4ビットが2補数表現で保持されるセットされる。部分剰余レジスタ6には、上位4ビット以外の下位ビットが冗長2進数表現{0,1}の数値でセットされる。

【0093】

商生成回路7は、2補数表現で保持された部分剰余レジスタ5の4ビットデータから商2ビットを生成する。

【0094】

除数・部分開平値選択10は、生成された商から除数を選択する為、スケーリングされた除数の{−3倍、−2倍、−1倍、0、1倍、2倍、3倍}データから選択する。

【0095】

桁上げ保存加算器11は、選択された除数の下位ビットと、部分剰余レジスタ6に冗長2進数表現で保持された部分剰余下位ビットとを入力して、桁上げ伝播無く、部分剰余計算を行う。桁上げ保存加算器11からキャリー発生する場合は、キャリー伝播加算器12にキャリー信号を送信する。

【0096】

キャリー伝播加算器12は、部分剰余レジスタ5に保持された部分剰余の上位ビットと選択された除数の上位ビットと、桁上げ保存加算器11からのキャリー信号を入力して加算を行う。

【0097】

次サイクルで使用する部分剰余は、基数に従いシフトする必要があるが、部分剰余データの商生成で必要な上位ビットは2補数化して部分剰余レジスタ5に保持しているので、2補数変換回路13は、2補数化する必要のある上位2ビット分を部分剰余計算回路11から入力して冗長2進数表現から2補数表現に変換する。得られた2補数化部分剰余上位データを、セレクタ23を介し、シフタ27で2ビットシフトして部分剰余レジスタ5にセットし、次桁の商生成を行っていく。併せて、同様に、桁上げ保存加算器11の冗長2進数表現の出力のうち、2補数変換回路13に出力した上位ビット以外の下位ビットを、シフタ28により2ビットシフトし、セレクタ24を介して部分剰余レジスタ6にセットする。

【0098】

除算演算においては、除数は固定値を使用するので、除数・部分開平値正レジスタ14のデータをセレクタ21で選択し、さらにセレクタ25ではセレクタ21の出力を選択することで除数データを保持する。同様に、3倍除数は固定値を使用するので、3倍除数・部分開平値負レジスタ15に保持された3倍除数データをセレクタ22で選択し、さらにセレクタ26ではセレクタ22の出力を選択することで保持する。

【0099】

次に本実施形態の開平演算の動作について説明する。まず、被演算数を、乗算器2とセレクタ23、24を介して、部分剰余レジスタ5,6にセットする。

【0100】

商生成回路7は、2補数形式で保持された部分剰余レジスタ5の4ビットデータから商1ビットを生成する。

【0101】

1回目の部分開平値R(0)=0なので、除数・部分開平値正レジスタ14と3倍除数・部分開平値負レジスタ15には0がセットされる。

【0102】

除数・部分開平値選択回路10は、商生成回路7で生成された商から、部分開平値を選択する。

【0103】

シフタ8は、2補数形式で保持された部分剰余上位レジスタ5の出力を、下位側へ1ビットシフトする。

【0104】

同様に、シフタ9は、冗長形式で保持された部分剰余下位レジスタ6の出力を下位側で1ビットシフトする。

【0105】

桁上げ保存加算器11は、除数・部分開平値選択回路10が選択した部分開平値の下位データと、シフタ9で1ビット右シフトされた部分剰余下位データとを入力して、桁上げ伝播無く、部分剰余計算を行う。桁上げ保存加算器11からキャリー発生する場合は、キャリー伝播加算器12にキャリー信号を送信する。

【0106】

キャリー伝播加算器12は、シフタ8で1ビット右シフトされた部分剰余上位データと、除数・部分開平値選択回路10が選択した部分開平値の上位データと、桁上げ保存加算器11からのキャリー信号とを入力して加算を行う。

【0107】

次サイクルで使用する部分剰余は、上位ビットについては、2補数変換回路13により、桁上げ保存加算器11からの冗長2進数表現の入力の、2補数化が必要な上位2ビット分を2補数表現に変換する。演算の基数に従いシフトする必要があるが、部分剰余計算回路11及びキャリー伝播加算器12に入力する前に1ビット右シフトしているので、1ビット左シフトでなく、除算演算と同じく2ビット左シフトすることになる。シフタ27で2ビット左シフトし、セレクタ23を使用し、部分剰余レジスタ5にセットし、次桁の商生成を行っていく。

【0108】

下位ビットについては、桁上げ保存加算器11の冗長2進数表現の出力のうち、2補数変換回路13に出力した上位ビット以外の下位ビットを、シフタ28により2ビットシフトし、セレクタ24を介して部分剰余レジスタ6にセットする。

【0109】

除数・部分開平値選択回路10に入力される商を結合した部分開平値は、冗長2進数表現ではなく2補数表現であるために、オン・ザ・フライ商生成正回路17、オン・ザ・フライ商生成負回路18と、商生成回路7で生成された商を考慮しながら生成していく。オン・ザ・フライ商生成正回路17は、2補数表現で生成された部分開平値を生成し、生成された部分開平値は、セレクタ21、25を介して、除数・部分開平値正レジスタ14に保持される。同様にオン・ザ・フライ商生成負回路18は、2補数表現で生成された部分開平値-1を生成し、生成された部分開平値-1は、セレクタ22、26を介して、3倍除数・部分開平値負レジスタ15に保持されて、次桁の部分開平値生成において除数・部分開平値選択回路10に入力され使用される。

【0110】

POSITIONレジスタ16は、商生成桁を指示する回路であり、初期状態でMSB=1のみがセットされる。

【0111】

シフタ19は、1ビット右シフトされるので、サイクル毎に1ビット右シフトしたデータがPOSITIONレジスタ16にはセットされる事になる。

【0112】

以上説明したように、本実施形態では、開平演算において、予め1ビット右シフトした部分剰余を用意しておき、このシフトした部分剰余から部分開平値を演算する事で、開平演算結果のシフト数を除算演算と同じシフト数に出来るので、2補数化回路を共用化出来、余分なセレクタ追加もなく、除算・開平演算の処理速度を落さない演算器を提供することができる。

【産業上の利用可能性】

【0113】

数値計算結果の可視化で使用される座標計算などで使用される開平演算を含む高速計算分野。

【図面の簡単な説明】

【0114】

【図1】本発明の除算・開平演算器の第1の実施形態の構成を示すとともに除算の動作を説明するためのブロック図である。

【図2】本発明の除算・開平演算器の第1の実施形態の構成を示すとともに開平演算の動作を説明するためのブロック図である。

【図3】本発明の除算・開平演算器の第2の実施形態の構成を示すブロック図である。

【符号の説明】

【0115】

1 スケーリングファクタ生成部

2 53ビット×6ビット乗算器

3 53ビット×6ビット乗算器

4 除数3倍数生成部

5 部分剰余上位保持レジスタ

6 部分剰余下位保持レジスタ

7 商デジット生成回路

8 シフタ

9 シフタ

10 除数・部分開平値選択回路

11 桁上げ保存加算器(CSA)

12 キャリー伝播加算器(CPA)

13,13−1,13−2 2補数変換回路

14 除数・部分開平値正レジスタ

15 3倍除数・部分開平値負レジスタ

16 POSITIONレジスタ

17 オン・ザ・フライ商生成正回路

18 オン・ザ・フライ商生成負回路

19 シフタ

20,21,22,23,24,25,26 セレクタ

27,28 シフタ

【技術分野】

【0001】

本発明は、除算・開平演算器に関するものであり、特に高基数型の除算器と低基数型の開平器を実装した除算・開平演算器に関する。

【背景技術】

【0002】

除算器・開平器の実装においては、アルゴリズムとして減算シフト法、あるいは減算引き離し法等を用いたものが、ハードウェア量と性能のバランスを考慮して、一般的に用いられている。このアルゴリズムは我々が通常、筆算で除算を行うのと同様に、商の決定を、余り(部分剰余)のシフトと余りからの分母(除数・部分開平値)の倍数の減算により除算を行う手法で、具体的に、n桁単位に商/開平数字が決定され、その商/開平数字の決定にもとづいて部分剰余が計算され、次の演算ステップでは、この部分剰余値がn桁シフトされ、それにもとづいて次のn桁の商/開平数字が決定され、という具合に、繰り返し演算を行うことで実行される。

【0003】

このn桁単位に商/開平数字を決定して行く方法は、2のn乗をr(これを基数と呼ぶ)とするとき、基数rの除算/開平法と呼ばれている。このようなアルゴリズムの除算処理について述べたものとして、「コンピュータの高速演算方式、1980、近代科学社、pp.214−249」(非特許文献1)には、回復型除算、非回復型除算、SRT除算、拡張SRT除算といった各種の除算手法について述べられている。

【0004】

減算シフト法を用いた除算の手順について簡単に説明する。

【0005】

演算のビット長(商/開平数字を決定していく単位桁数)をn(任意の正整数)、演算の基数をr(=2のn乗)、除数をD、被除数をR(0)、jを0以上の整数としてj回目の部分剰余をR(j)、j回目の商をq(j)とする。また、ここでは除数D、被除数R(0)は正規化されているとする。ここでは正規化浮動小数点フォーマットとして、「1.xxxx」を用いるものとし、除数、被除数共に正規化されているとする。本フォーマットに合致しないデータ形式を扱う場合でも、演算前後に適当なシフト処理を実行することで本浮動小数点フォーマットについての処理を適用可能である。

【0006】

ここで使用される商及び部分剰余は、冗長2進表現により表される。すなわち、2補数表現であれば各ビットが{0,1}で表されるところを、{−1,0,1}の3値を採ることを許し、負の値を可能としている。

【0007】

入力データが上述のように正規化されている条件の下で、次の(1)式に示される漸化式を用いて、順次、商及び部分剰余を求めることができる。

【0008】

R(j+1)=r×R(j)-q(j+1)×D・・・(1)

SRT法では、商デジットとして{0,1}に加えて{−1}をとり、部分剰余の上位数ビットで高速に商デジットを判定できる方法である。SRTアルゴリズムは、開平演算にも適用できるので、除算ハードウェアの使用が可能である。

【0009】

開平演算の手順について簡単に説明する。

【0010】

演算の基数をr、被開平数をR(0)、jを0以上の整数としてj回目の部分剰余をR(j)、部分開平値をQ(j)、j回目の商をq(j)とする。被開平数R(0)は正規化されているとする。部分開平値Q(j)は、j回目まで算出された商である。

【0011】

ここで使用される商(部分開平値も含む)及び部分剰余は、冗長2進表現により表される。すなわち、2補数表現であれば各ビットが{0,1}で表されるところを、{−1,0,1}の3値を採ることを許し、負の値を可能としている。

【0012】

入力データが上述のように正規化されている条件の下で、次の(2)、(3)式に示される漸化式を用いて、順次、商及び部分剰余を求めることができる。

【0013】

R(j+1)=r×R(j)-q(j+1)×(r×Q(j)+q(j+1)×r-(j+1))・・・(2)

Q(j+1)=Q(j)+q(j+1)×r-(j+1) ・・・(3)

開平演算では、j回目の部分剰余から部分開平値を減算する演算により、j+1回目の部分剰余算出を行うアルゴリズムとなっており、そのまま処理を行うとすると、冗長2進数表現の部分剰余と冗長2進数表現の部分開平値との演算となり、複雑な演算となってしまう。

冗長2進数表現の部分開平値が全て求まってから2補数表現に変換すると、変換に要する時間が計算時間に追加されてしまい、処理低下を招く。

【0014】

そこで、除算で実現したハードウェアを開平演算で共用する為に、オン・ザ・フライ変換と呼ばれる回路によって、商決定と同時に得られた部分開平値を2補数表現に変換して、冗長2進数表現の部分剰余と2補数表現の部分開平値の演算として処理を行う。

【0015】

オン・ザ・フライ変換は、例えば非特許文献2(On-the-fly conversion of redundant into conventional representations、エム.ディ.エルセゴバック及びティ.ラング、IEEE Transactions on Computers、第36巻第7号、1987年6月、895〜897頁)に開示されている。

【0016】

基数2の場合のオン・ザ・フライ変換について簡単に説明する。

例えば、冗長2進表現{1,-1}を2補数表現に変換すると{0,1}となる(いずれも10進数で1を表す)。冗長2進から2補数への変換を加算と減算で実現すると,-1が入力されたときにキャリー伝播するので、この例では-1が入力される前の値{1,0}以外に、{0,1}を用意しておき、-1が入力されたとき、{0,1}を選択すればキャリー伝播は発生しない。つまり、キャリーの伝播を無くし固定時間で処理するために,-1が入力された場合の答え(言い換えるなら1小さい表現)を予め内部に用意しておけば、キャリー伝播を抑止できる事になる。

【0017】

冗長2進表現で上位桁から順に求まる商Qと、2補数表現の商Z の小数点以下j桁までをそれぞれQ(j)(=.q(1)q(2)・・・q(j))とZ(j)(=.z(1)z(2)・・・z(j))とすると、上記からZ(j)は、Q(j)またはQ(j)−2-jのいずれかの2補数で表せる。従って、各演算ステップで、Q(j)およびQ(j)―2-jの2補数表現を保持しておけば、q(j)が求まった時点で、即座にZ(j)を求める事が出来る。

【0018】

演算途中のj+1回目の商デジットをq(j+1)とし、Q(j)またはQ(j)−2-jの2補数をそれぞれQP(j)、QN(j)とし、部分開平値正、部分開平値負と呼ぶ事にする。演算を基数に従い処理を行い、q(j+1)が求まれば、QP(j)、QN(j)から次のようにQP(j+1)、QN(j+1)を求める事が出来る。q(j+1)=−1の場合は、

QP(j+1)= QP(j)−2-(j+1)=QN(j)+2-j−2-(j+1)=QN(j)+2-(j+1) ・・・(4)

QN(j+1) {=QP(j+1)−2-(j+1)}=QP(j)−2-(j+1)−2-(j+1)=QP(j)−2-j=QN(j) ・・・(5)

q(j+1)=0の場合、

QP(j+1)= QP(j) ・・・(6)

QN(j+1)= QN(j) +2-(j+1) ・・・(7)

q(j+1)=1の場合、

QP(j+1)= QP(j)+2-(j+1) ・・・(8)

QN(j+1) {=QP(j+1)−2-(j+1)}=QP(j)+2-(j+1)−2-(j+1)=QP(j) ・・・(9)

式(4)と式(7)と式(8)は、Qx(j+1)=Qy(j)+2-(j+1) (演算の基数を2と仮定している)で表せる。この演算は、j桁目までの部分開平値Qy(j)の後ろに、j+1桁目の商(0または1)であるq(j+1)のビット列を連結するだけでよいので、実質的に演算は行われない。他式は、QP(j)かQN(j)を選択すればよい。これは、j回目の部分開平値正であるQP(j)、部分開平値負であるQN(j)を求めて保持しておくことにより、j+1回目の部分開平値Q(j+1)すなわちQP(j+1)は、単純なビット演算のみで、冗長2進数から2補数(通常数)を得る事が出来る。

【0019】

また、SRT法による除算演算方法については、特開2001−222410「除算器」(特許文献1)に記載されている。特許文献1には、除数を5/3≦除数<1.75の範囲にスケーリングを行うことにより、部分剰余の上位4ビットの正規化及びその4ビットの参照により、商2bitを決定(基数4の除算回路)することができるという効果が報告されている。

【0020】

除算演算の部分剰余生成は、固定値の除数Dを考慮して減算すれば実現出来るので、除数範囲をスケーリングする事で高基数を実現できるが、開平演算の部分剰余生成は、j回目の部分開平値Q(j)と商q(j)を考慮して減算する必要があり、高基数を実現するには、商生成桁の1つ前の商考慮が必要であるので、回路が複雑となり、処理にも時間を要する事になる。高基数の開平演算処理について、非特許文献3((「Radix-4 square root without initial PLA」、エム.ディ.エルセゴバック及びティ.ラング、IEEE Transactions on Computers、第39巻第8号、1990年8月、1016〜1024頁」)に部分開平値3ビットと部分剰余上位7ビットから商2ビットを決定できる例が記載されているが、このように高基数の開平演算を採用しようとすると、開平演算の商決定回路規模や論理段数が複雑となる。

【0021】

また、特開平10−187420「除算・開平演算器」(特許文献2)に除算演算器と開平演算器とを共用したものが開示されている。

【0022】

【特許文献1】特開2001−222410「除算器」

【特許文献2】特開平10−187420「除算・開平演算器」

【非特許文献1】コンピュータの高速演算方式、1980、近代科学社、pp.214−249

【非特許文献2】On-the-fly conversion of redundant into conventional representations、エム.ディ.エルセゴバック及びティ.ラング、IEEE Transactions on Computers、第36巻第7号、1987年6月、895〜897頁

【非特許文献3】Radix-4 square root without initial PLA、エム.ディ.エルセゴバック及びティ.ラング、IEEE Transactions on Computers、第39巻第8号、1990年8月、1016〜1024頁

【発明の開示】

【発明が解決しようとする課題】

【0023】

上述のように高基数の開平演算における商決定は、高基数の除算より論理段数が多く複雑なので、除算演算と開平演算で同じ基数を採用した場合、開平演算の論理段数が処理性能を決めてしまう事になり、除算処理性能が落ちてしまう問題が発生する。除算処理性能を落さない為には、開平演算の基数は除算演算より低く設定される事になる。例えば、開平演算で部分剰余上位4ビット参照の回路方式を実現するには、基数2の採用が妥当である。

【0024】

特許文献2は、低基数である基数2の除算器と除算器と同じ基数2の開平演算について開示しているが、高基数の除算と低基数の開平演算を行う除算・開平演算器については開示していない。

【0025】

本発明の目的は、このような事情に鑑みてなされたもので、除算と開平演算に多くの部分を共用でき効率的であるとともに、除算演算の基数を開平演算より高く設定でき、除算処理性能を落とすことがない除算・開平演算器を提供することにある。

【課題を解決するための手段】

【0026】

上記目的を達成するために、本発明の除算・開平演算器は、高基数の除算及び低基数の開平演算を行う除算・開平演算器において、部分剰余の上位ビットを参照して商を定める商生成手段と、前記部分剰余の前記上位ビットを2補数表現で保持し、前記部分剰余の前記上位ビット以外の下位ビットは冗長2進数表現で保持する部分剰余保持手段と、除数と部分開平値を演算種別に応じて切り替えて保持する除数・部分開平値保持手段と、前記商により前記除数・部分開平値保持手段からの除数及び部分開平値を選択する除数・部分開平値選択回路と、前記下位ビットの冗長2進数表現の部分剰余と前記除数・部分開平値選択回路の出力とを入力する桁上げ保存加算器と、前記上位ビットの2補数表現の部分剰余、前記下位ビットの冗長2進数表現の部分剰余、前記除数・部分開平値選択回路の出力、及び前記桁上げ保存加算器のキャリー信号を加算する桁上げ伝播加算器と、前記桁上げ保存加算器の出力の上位ビットから基数に基づくビット数のビットデータ及び桁上げ伝播加算器の出力を入力して2補数化し演算の基数に基づくビット数シフトして次回の部分剰余として使用する2補数化・シフト手段とを有する。

【0027】

また、前記2補数化・シフト手段は、除算と開平演算の基数の違いにより定められるビット数、前記上位ビットの2補数表現の部分剰余を下位へシフトして前記桁上げ保存加算器に入力する第1のシフタと、前記基数の違いにより定められるビット数、前記下位ビットの冗長2進数表現の部分剰余を下位へシフトして前記桁上げ伝播加算器に入力する第2のシフタと、前記桁上げ保存加算器の出力の上位ビットから前記高基数に基づいて取り出したビット数のビットデータ及び前記桁上げ伝播加算器の出力を入力して2補数化する2補数変換手段と、前記2補数変換手段の出力を次回の部分剰余として使用するよう前記高基数に基づくビット数シフトする第3のシフタとを有するものとしてもよい。

【発明の効果】

【0028】

本発明によれば、桁上げ保存加算器の出力の上位ビットから演算の基数に基づくビット数のビットデータと、桁上げ伝播加算器の出力とを入力して2補数化し、演算の基数に基づくビット数シフトして次回の部分剰余として使用する。これにより除算と開平演算において、除数と部分開平値とのレジスタ共有などの多くの部分を共用できる効率的な回路となり、除算演算の基数を開平演算より高く設定でき、除算処理性能を向上することができる。

【0029】

さらに開平演算の場合、除算演算と開平演算の基数の違いにより定められるビット数、前記上位ビットの2補数化された部分剰余及び前記下位ビットの冗長2進数の部分剰余をシフトして加算器及び桁上げ保存加算器に入力し、桁上げ保存加算器の出力の上位ビットから高基数に基づいて取り出したビット数のビットデータと加算器の出力とを入力して2補数化し、高基数に基づくビット数シフトして次回の部分剰余として使用することにより、部分剰余から除数を減算した結果を部分剰余レジスタに戻すパスの回路遅延時間が抑制し、除算演算と開平演算の処理速度を向上させることができる。

【発明を実施するための最良の形態】

【0030】

次に、本発明の構成について図面を参照して詳細に説明する。

【0031】

以下に説明する実施形態においては、除算演算の基数が4、デジット集合が{−3、−2、−1、0、1、2、3}、除数、被除数がnビット長の少数で、演算アルゴリズムに拡張SRT除算アルゴリズムを採用し、開平演算の基数が2、デジット集合が{−1、0、1}、被開平数がnビット長の少数で、演算アルゴリズムにSRT開平アルゴリズムを採用している回路について説明する。

【0032】

図1は、本発明の除算・開平演算器の第1の実施形態の構成を示すブロック図である。

【0033】

スケーリングファクタ生成部1は、スケーリングに用いる乗算係数を生成する。スケーリングファクタ生成部1は、除算演算では、除数から除数を5/3≦除数<1.75の範囲にスケーリングを行うための乗算係数を生成するが、開平演算では、乗算係数=1で処理を行う。53ビット×6ビット乗算器2,3が、スケーリングファクタ生成部1が出力した乗算係数を、入力された53ビットの除数、被除数に乗算して出力する。このことにより、部分剰余の上位4ビットの正規化及びその4ビットの参照により、商2bitを決定(基数4の除算回路)できる。

【0034】

基数4の除算演算は、除数範囲を5/3≦除数<1.75の範囲にスケーリングを行うことで、部分剰余上位4ビットから商2ビットを生成出来、開平演算においても、部分剰余上位4ビットだけで商生成する方式を採用出来れば、除算処理性能を落さない事が可能となる。

【0035】

除数3倍数生成部4は、53ビット×6ビット乗算器2の出力を3倍して除数3倍数を生成し、出力する。

【0036】

部分剰余レジスタ5は、2補数表現の部分剰余上位4ビットを保持する。

【0037】

部分剰余レジスタ6は、部分剰余レジスタ5で保持される上位ビット以外の下位ビットを冗長2進数表現で保持する。

【0038】

商生成回路7は、レジスタ5に保持された2補数表現の部分剰余上位4ビットから、除算においてはデジット集合{−3、−2、−1、0、1、2、3}のうちから、開平演算においてはデジット集合{−1、0、1}のうちから1つを選択し、商を生成する。

【0039】

除数・部分開平値選択回路10は、除算動作時は商生成回路7で生成された商により除数を選択する。また開平動作時は商生成回路7で生成された商とPOSITION レジスタ16のPOSITIONデータとから部分開平値を選択する。

【0040】

桁上げ保存加算器(Carry Save Adder)11は、部分剰余レジスタ6からの下位ビットの冗長2進数表現の部分剰余と除数・部分開平値選択回路10の出力を入力データとし、桁上げ伝播なく加算する。キャリー発生する場合は、キャリー信号をキャリー伝播加算器(Carry Propagate Adder)12に出力する。

【0041】

キャリー伝播加算器(Carry Propagate Adder)12は、部分剰余レジスタ5からの上位ビットの2補数表現の部分剰余と、除数・部分開平値選択回路10の出力と、加算器11のキャリー信号を加算する。

【0042】

部分剰余から除数・部分開平値選択データ減算後の部分剰余データのシフト操作で基数を考慮する必要があり、基数2である開平演算の場合、j回目の部分剰余から除数・部分開平値選択データを減算した結果を、1ビット左シフトしてj+1回目の部分剰余データとして使用する。一方、基数4である除算の場合、j回目の部分剰余から除数・部分開平値選択データを減算した結果を、2ビット左シフトしてj+1回目の部分剰余データとして使用する。加えて、部分剰余上位ビットは、商生成で参照するデータを2補数表現で保持することで、商生成を高速しているので、上記シフト処理では冗長2進数表現の下位ビットからシフトビット分だけ2補数表現のデータに変換する2補数変換回路13―1、13―2を使用しながら、シフト処理を行っている。

【0043】

2補数変換回路13―1は、桁上げ保存加算器11の出力の上位ビットから除算の基数に基づいて2補数化する必要のあるビット数、ここでは2ビットのデータを取り出し、2補数化する。2補数変換回路13−2は、桁上げ保存加算器11の出力の上位ビットから開平演算の基数に基づいて2補数化する必要のあるビット数、ここでは1ビットのデータを取り出し、2補数化する。セレクタ20は、除算においては2補数変換回路13―1の出力を、開平演算においては2補数変換回路13−2の出力を選択する。シフタ27は、除算においてはセレクタ20の出力を2ビットシフトし、開平演算においては1ビットシフトしてセレクタ23に入力する。シフタ28は、桁上げ保存加算器11の出力の2補数変換回路13―1に出力した上位ビット以外の下位ビットを、除算においては2ビットシフトし、開平演算においては1ビットシフトしてセレクタ24に入力する。

【0044】

除数・部分開平値正レジスタ14は、除算においては除数、開平演算においては部分開平値を保持する。

【0045】

3倍除数・部分開平値負レジスタ15は、除算においては3倍除数、開平演算においては部分開平値-1を保持する。

【0046】

POSITIONレジスタ16は、開平演算において商生成回路7で生成した商デジットと部分開平値を結合する為の処理ビット情報を保持する。

【0047】

オン・ザ・フライ商生成正回路17は、従来技術と同様に、商生成と並行して、冗長2進数表現のデータから2補数表現のデータへの変換を行うため、従来技術と同様に2補数表現の部分開平値データを生成する。

【0048】

オン・ザ・フライ商生成負回路18は、従来技術と同様に商生成と並行して、冗長2進数表現のデータから2補数表現のデータへの変換を行うため、従来技術と同様に2補数表現の部分開平値-1データを生成する。

【0049】

シフタ19は、POSITION レジスタ16のPOSITIONデータをサイクル毎に1ビット右シフトする。

【0050】

セレクタ21は、開平演算においてはオン・ザ・フライ商生成正回路17の出力、除算においては除数・部分開平値正レジスタ14の出力を選択する。

【0051】

セレクタ22は、開平演算においてはオン・ザ・フライ商生成負回路18の出力、除算においては3倍除数・部分開平値負レジスタ15の出力を選択する。

【0052】

セレクタ23は、1サイクル目は乗算器2の出力、2サイクル以降はシフタ27を経由した2補数変換回路13の出力を選択する。

【0053】

セレクタ24は、1サイクル目は乗算器2の出力、2サイクル以降は桁上げ保存加算器11の出力を選択する。

【0054】

セレクタ25は、1サイクル目は乗算器3の出力、2サイクル以降はセレクタ21の出力を選択する。

【0055】

セレクタ26は、1サイクル目は3倍除数生成器4の出力、2サイクル以降はセレクタ22の出力を選択する。

【0056】

次に図1の除算演算の動作について説明する。

【0057】

まず、スケーリングファクタ生成部1は、除数上位ビットから除数を5/3≦除数<1.75の範囲にスケーリングを行う乗算係数を生成する。

【0058】

生成した乗算係数を、53ビット×6ビット乗算器2,3に入力し、除数、被除数をスケーリングし、スケーリング後の除数から3倍除数を3倍除数生成器4で生成する。

【0059】

セレクタ23,24,25,26は、1サイクル目は乗算器2,3と3倍生成器4を選択し、部分剰余レジスタ5,6、除数・部分開平値正レジスタ14、3倍除数・部分開平値負レジスタ15に入力する。

【0060】

乗算器2から冗長2進数表現で部分剰余の下位ビットがセットされる部分剰余レジスタ6には、{−1}の値は生成されていないので、{0,1}の数値がセットされる。

【0061】

部分剰余の上位ビットがセットされ2補数表現で保持された部分剰余レジスタ5の内容から、商生成回路7が商2ビットを生成する。

【0062】

生成された商から除数を選択する為、除数・部分開平値選択回路10で、スケーリングされた除数の{−3倍、−2倍、−1倍、0、1倍、2倍、3倍}データから選択する。

【0063】

選択された除数の下位ビットと、冗長2進数表現で保持された部分剰余の下位ビットを入力して桁上げ伝播の無い桁上げ保存加算器11で計算を行う。

【0064】

桁上げ保存加算器11からキャリー発生する場合は、キャリー伝播加算器12にキャリー信号を送信する。

【0065】

キャリー伝播加算器12では、部分剰余レジスタ5からの部分剰余の上位ビットと、選択された除数の上位ビットと、桁上げ保存加算器11からのキャリー信号を入力して加算を行う。

【0066】

次サイクルで使用する部分剰余は、基数に従い2ビットシフトする必要があるが、部分剰余データの商生成で必要なビット数は2補数化して保持しているので、桁上げ保存加算器11からの冗長2進数表現の部分剰余下位ビットから、2補数化することが必要な2ビット分を2補数変換回路13−1で変換し、得られた2補数表現の部分剰余上位ビットを、セレクタ20、23を介し、シフタ27で2ビット左シフトして、部分剰余レジスタ5にセットし、次桁の商生成を行っていく。

【0067】

併せて、同様に、桁上げ保存加算器11の冗長2進数表現の出力のうち、2補数変換回路13―1、13−2に出力した上位ビット以外の下位ビットを、シフタ28により、除算においては2ビットシフトし、開平演算においては1ビットシフトし、セレクタ24を介して部分剰余レジスタ6にセットする。

【0068】

除算演算においては、除数、3倍除数は固定値を使用するので、除数・部分開平値正レジスタ14のデータをセレクタ21で選択し、さらにセレクタ25ではセレクタ21を選択する事で除数データを保持する。同様に、3倍除数・部分開平値負レジスタ15に保持された3倍除数データをセレクタ22で選択し、さらにセレクタ26ではセレクタ22を選択する事で保持する。

【0069】

次に図2の開平演算の動作について説明する。

【0070】

開平演算では、除数の変わりに部分開平値を用いて部分剰余計算が行われる。被演算数を乗算器2とセレクタ23、24を介して、部分剰余レジスタ5,6にセットする。

【0071】

2補数表現で保持された部分剰余レジスタ5から商1ビットを生成する。

【0072】

1回目の部分開平値R(0)=0なので、除数・部分開平値正レジスタ14と3倍除数・部分開平値負レジスタ15には0がセットされている。

【0073】

除数・部分開平値選択回路10には商生成回路7で生成された商から部分開平値が選択される。

【0074】

選択された部分開平値の下位データと、部分剰余レジスタ6からの部分剰余下位データを入力して桁上げ伝播の無い桁上げ保存加算器11で計算を行う。

【0075】

桁上げ保存加算器11からキャリー発生する場合は、キャリー伝播加算器12にキャリー信号を送信する。

【0076】

キャリー伝播加算器12では、部分剰余レジスタ5からの部分剰余上位データと、選択された部分開平値と、桁上げ保存加算器11からのキャリー信号を入力して加算を行う。

【0077】

次サイクルで使用する部分剰余は、基数に従いシフトしたデータを使用する為、1ビット左シフトする事になる。

【0078】

桁上げ保存加算器11からの冗長2進数表現の部分剰余下位ビットから2補数化するのに必要な1ビット分を2補数変換回路13−2で変換し、セレクタ20、23を使用し、シフタ27で1ビット左シフトして、レジスタ5にセットし、次桁の商生成を行っていく。

【0079】

同様に、桁上げ保存加算器11の冗長2進数表現の出力のうち、2補数変換回路13―1、13−2に出力した上位ビット以外の下位ビットを、シフタ28により、除算においては2ビットシフトし、開平演算においては1ビットシフトし、セレクタ24を介して部分剰余レジスタ6にセットする。

【0080】

除数・部分開平値選択回路10に入力される商を結合した部分開平値は、冗長2進数表現ではなく2補数表現のデータを入力させるために、商生成回路7で生成された商を考慮しながら、オン・ザ・フライ商生成正回路17と、オン・ザ・フライ商生成負回路18とで従来技術と同様に部分開平値及び部分開平値-1を生成していく。

【0081】

オン・ザ・フライ商生成正回路17は、2補数表現で生成された部分開平値を生成し、セレクタ21、25を介して、除数・部分開平値正レジスタ14に保持される。

【0082】

同様にオン・ザ・フライ商生成負回路18は、2補数表現で生成された部分開平値-1を生成し、セレクタ22、26を介して、3倍除数・部分開平値負レジスタ15に保持されて、次桁の商生成に使用される。

【0083】

POSITIONレジスタ16は、商生成桁を指示する回路であり、初期状態でMSB=1のみがセットされる。

【0084】

シフタ19では、1ビット右シフトされるので、サイクル毎に1ビット右シフトしたデータがPOSITIONレジスタ16にはセットされる事になる。

【0085】

以上説明したように、本発明の除算・開平演算器によれば、桁上げ保存加算器の出力の上位ビットから演算の基数に基づくビット数のビットデータと、加算器の出力とを入力して2補数化し、演算の基数に基づくビット数シフトして次回の部分剰余として使用する。これにより除算回路と開平演算回路において、除数と部分開平値とのレジスタ共用などの共用出来る部分が多く効率的な回路となり、除算演算の基数を開平演算より高く設定でき、除算処理性能を向上することができる。

【0086】

次に、本発明の第2の実施形態について図面を参照して詳細に説明する。

【0087】

図3は、本発明の第2の実施形態の構成を示すブロック図である。

【0088】

第1の実施形態では次回の部分剰余データを生成するには、除算演算で2ビットの2補数化処理、開平演算で1ビットの2補数化処理を行い、加えて除算演算と開平演算で回路を切り替えるセレクタを備えている。部分剰余から除数を減算した結果を部分剰余レジスタに戻すパスは、一番論理段数の多いパスであり、この部分にセレクタを追加すると、回路遅延時間が増加するので、クロックを遅くするか、レジスタ追加が必要になり、除算演算と開平演算の処理速度を低下させてしまうという問題がある。

【0089】

本発明の第2の実施形態は、上記の第1の実施形態と異なり、開平演算において2補数化された部分剰余ビットを右1ビットシフトするシフタ8、及び、開平演算において部分剰余下位ビットを右1ビットシフトするシフタ9を備え、また、2補数変換回路13―1,13−2に変えて、桁上げ保存加算器11の上位ビットから2ビットデータを取り出し、2補数化する2補数変換回路13を備え、j回目の部分剰余から除数・部分開平値選択データを減算した結果を、除算及び開平演算のどちらも、2ビット左シフトしてj+1回目の部分剰余データとして使用することにより、部分剰余から除数を減算した結果を部分剰余レジスタに戻すパスの回路遅延時間が抑制し、除算演算と開平演算の処理速度を向上させるものである。

【0090】

次に本実施形態の除算演算の動作について説明する。第1の実施形態と同様に、まずスケーリングファクタ生成部1は、スケーリングに用いる乗数係数を除数上位ビットから生成する。53ビット×6ビット乗算器2は、入力された乗算係数により、入力された被除数をスケーリングする。53ビット×6ビット乗算器3は、入力された乗算係数により、入力された除数をスケーリングする。3倍除数生成器4は、スケーリング後の除数から3倍除数を生成する。

【0091】

セレクタ23は、1サイクル目は乗算器2の出力を選択し、部分剰余レジスタ5に入力する。セレクタ24は、1サイクル目は乗算器2の出力を選択し、部分剰余レジスタ6に入力する。セレクタ25は、1サイクル目は乗算器3の出力を選択し、除数・部分開平値正レジスタ14に入力する。セレクタ26は、1サイクル目は3倍除数生成器4の生成結果を選択し、3倍除数・部分開平値負レジスタ15に入力する。

【0092】

部分剰余レジスタ5には、上位4ビットが2補数表現で保持されるセットされる。部分剰余レジスタ6には、上位4ビット以外の下位ビットが冗長2進数表現{0,1}の数値でセットされる。

【0093】

商生成回路7は、2補数表現で保持された部分剰余レジスタ5の4ビットデータから商2ビットを生成する。

【0094】

除数・部分開平値選択10は、生成された商から除数を選択する為、スケーリングされた除数の{−3倍、−2倍、−1倍、0、1倍、2倍、3倍}データから選択する。

【0095】

桁上げ保存加算器11は、選択された除数の下位ビットと、部分剰余レジスタ6に冗長2進数表現で保持された部分剰余下位ビットとを入力して、桁上げ伝播無く、部分剰余計算を行う。桁上げ保存加算器11からキャリー発生する場合は、キャリー伝播加算器12にキャリー信号を送信する。

【0096】

キャリー伝播加算器12は、部分剰余レジスタ5に保持された部分剰余の上位ビットと選択された除数の上位ビットと、桁上げ保存加算器11からのキャリー信号を入力して加算を行う。

【0097】

次サイクルで使用する部分剰余は、基数に従いシフトする必要があるが、部分剰余データの商生成で必要な上位ビットは2補数化して部分剰余レジスタ5に保持しているので、2補数変換回路13は、2補数化する必要のある上位2ビット分を部分剰余計算回路11から入力して冗長2進数表現から2補数表現に変換する。得られた2補数化部分剰余上位データを、セレクタ23を介し、シフタ27で2ビットシフトして部分剰余レジスタ5にセットし、次桁の商生成を行っていく。併せて、同様に、桁上げ保存加算器11の冗長2進数表現の出力のうち、2補数変換回路13に出力した上位ビット以外の下位ビットを、シフタ28により2ビットシフトし、セレクタ24を介して部分剰余レジスタ6にセットする。

【0098】

除算演算においては、除数は固定値を使用するので、除数・部分開平値正レジスタ14のデータをセレクタ21で選択し、さらにセレクタ25ではセレクタ21の出力を選択することで除数データを保持する。同様に、3倍除数は固定値を使用するので、3倍除数・部分開平値負レジスタ15に保持された3倍除数データをセレクタ22で選択し、さらにセレクタ26ではセレクタ22の出力を選択することで保持する。

【0099】

次に本実施形態の開平演算の動作について説明する。まず、被演算数を、乗算器2とセレクタ23、24を介して、部分剰余レジスタ5,6にセットする。

【0100】

商生成回路7は、2補数形式で保持された部分剰余レジスタ5の4ビットデータから商1ビットを生成する。

【0101】

1回目の部分開平値R(0)=0なので、除数・部分開平値正レジスタ14と3倍除数・部分開平値負レジスタ15には0がセットされる。

【0102】

除数・部分開平値選択回路10は、商生成回路7で生成された商から、部分開平値を選択する。

【0103】

シフタ8は、2補数形式で保持された部分剰余上位レジスタ5の出力を、下位側へ1ビットシフトする。

【0104】

同様に、シフタ9は、冗長形式で保持された部分剰余下位レジスタ6の出力を下位側で1ビットシフトする。

【0105】

桁上げ保存加算器11は、除数・部分開平値選択回路10が選択した部分開平値の下位データと、シフタ9で1ビット右シフトされた部分剰余下位データとを入力して、桁上げ伝播無く、部分剰余計算を行う。桁上げ保存加算器11からキャリー発生する場合は、キャリー伝播加算器12にキャリー信号を送信する。

【0106】

キャリー伝播加算器12は、シフタ8で1ビット右シフトされた部分剰余上位データと、除数・部分開平値選択回路10が選択した部分開平値の上位データと、桁上げ保存加算器11からのキャリー信号とを入力して加算を行う。

【0107】

次サイクルで使用する部分剰余は、上位ビットについては、2補数変換回路13により、桁上げ保存加算器11からの冗長2進数表現の入力の、2補数化が必要な上位2ビット分を2補数表現に変換する。演算の基数に従いシフトする必要があるが、部分剰余計算回路11及びキャリー伝播加算器12に入力する前に1ビット右シフトしているので、1ビット左シフトでなく、除算演算と同じく2ビット左シフトすることになる。シフタ27で2ビット左シフトし、セレクタ23を使用し、部分剰余レジスタ5にセットし、次桁の商生成を行っていく。

【0108】

下位ビットについては、桁上げ保存加算器11の冗長2進数表現の出力のうち、2補数変換回路13に出力した上位ビット以外の下位ビットを、シフタ28により2ビットシフトし、セレクタ24を介して部分剰余レジスタ6にセットする。

【0109】

除数・部分開平値選択回路10に入力される商を結合した部分開平値は、冗長2進数表現ではなく2補数表現であるために、オン・ザ・フライ商生成正回路17、オン・ザ・フライ商生成負回路18と、商生成回路7で生成された商を考慮しながら生成していく。オン・ザ・フライ商生成正回路17は、2補数表現で生成された部分開平値を生成し、生成された部分開平値は、セレクタ21、25を介して、除数・部分開平値正レジスタ14に保持される。同様にオン・ザ・フライ商生成負回路18は、2補数表現で生成された部分開平値-1を生成し、生成された部分開平値-1は、セレクタ22、26を介して、3倍除数・部分開平値負レジスタ15に保持されて、次桁の部分開平値生成において除数・部分開平値選択回路10に入力され使用される。

【0110】

POSITIONレジスタ16は、商生成桁を指示する回路であり、初期状態でMSB=1のみがセットされる。

【0111】

シフタ19は、1ビット右シフトされるので、サイクル毎に1ビット右シフトしたデータがPOSITIONレジスタ16にはセットされる事になる。

【0112】

以上説明したように、本実施形態では、開平演算において、予め1ビット右シフトした部分剰余を用意しておき、このシフトした部分剰余から部分開平値を演算する事で、開平演算結果のシフト数を除算演算と同じシフト数に出来るので、2補数化回路を共用化出来、余分なセレクタ追加もなく、除算・開平演算の処理速度を落さない演算器を提供することができる。

【産業上の利用可能性】

【0113】

数値計算結果の可視化で使用される座標計算などで使用される開平演算を含む高速計算分野。

【図面の簡単な説明】

【0114】

【図1】本発明の除算・開平演算器の第1の実施形態の構成を示すとともに除算の動作を説明するためのブロック図である。

【図2】本発明の除算・開平演算器の第1の実施形態の構成を示すとともに開平演算の動作を説明するためのブロック図である。

【図3】本発明の除算・開平演算器の第2の実施形態の構成を示すブロック図である。

【符号の説明】

【0115】

1 スケーリングファクタ生成部

2 53ビット×6ビット乗算器

3 53ビット×6ビット乗算器

4 除数3倍数生成部

5 部分剰余上位保持レジスタ

6 部分剰余下位保持レジスタ

7 商デジット生成回路

8 シフタ

9 シフタ

10 除数・部分開平値選択回路

11 桁上げ保存加算器(CSA)

12 キャリー伝播加算器(CPA)

13,13−1,13−2 2補数変換回路

14 除数・部分開平値正レジスタ

15 3倍除数・部分開平値負レジスタ

16 POSITIONレジスタ

17 オン・ザ・フライ商生成正回路

18 オン・ザ・フライ商生成負回路

19 シフタ

20,21,22,23,24,25,26 セレクタ

27,28 シフタ

【特許請求の範囲】

【請求項1】

高基数の除算及び低基数の開平演算を行う除算・開平演算器において、

部分剰余の上位ビットを参照して商を定める商生成手段と、

前記部分剰余の前記上位ビットを2補数表現で保持し、前記部分剰余の前記上位ビット以外の下位ビットは冗長2進数表現で保持する部分剰余保持手段と、

除数と部分開平値を演算種別に応じて切り替えて保持する除数・部分開平値保持手段と、

前記商により前記除数・部分開平値保持手段からの除数及び部分開平値を選択する除数・部分開平値選択回路と、

前記下位ビットの冗長2進数表現の部分剰余と前記除数・部分開平値選択回路の出力とを入力する桁上げ保存加算器と、

前記上位ビットの2補数表現の部分剰余、前記下位ビットの冗長2進数表現の部分剰余、前記除数・部分開平値選択回路の出力、及び前記桁上げ保存加算器のキャリー信号を加算する桁上げ伝播加算器と、

前記桁上げ保存加算器の出力の上位ビットから基数に基づくビット数のビットデータ及び桁上げ伝播加算器の出力を入力して2補数化し演算の基数に基づくビット数シフトして次回の部分剰余として使用する2補数化・シフト手段とを有することを特徴とする除算・開平演算器。

【請求項2】

前記2補数化・シフト手段は、

前記桁上げ伝播加算器の出力と前記桁上げ保存加算器の出力の上位ビットから前記高基数に基づいて定められたビット数のビットデータとを入力して2補数化する第1の2補数変換手段と、

前記桁上げ伝播加算器の出力と前記桁上げ保存加算器の上位ビットから前記低基数に基づいて取り出したビット数のビットデータとを入力して2補数化する第2の2補数変換手段と、

除算においては第1の2補数変換回路を、開平演算においては第2の2補数変換手段の力を選択するセレクタと、

前記セレクタの出力を、次回の部分剰余として使用するよう、除算においては高基数に基づくビット数、開平演算においては低基数に基づくビット数シフトするシフタとを有することを特徴とする請求項1に記載の除算・開平演算器。

【請求項3】

前記2補数化・シフト手段は、

除算と開平演算の基数の違いにより定められるビット数、前記上位ビットの2補数表現の部分剰余を下位へシフトして前記桁上げ保存加算器に入力する第1のシフタと、

前記基数の違いにより定められるビット数、前記下位ビットの冗長2進数表現の部分剰余を下位へシフトして前記桁上げ伝播加算器に入力する第2のシフタと、

前記桁上げ保存加算器の出力の上位ビットから前記高基数に基づいて取り出したビット数のビットデータ及び前記桁上げ伝播加算器の出力を入力して2補数化する2補数変換手段と、

前記2補数変換手段の出力を次回の部分剰余として使用するよう前記高基数に基づくビット数シフトする第3のシフタとを有することを特徴とする請求項1に記載の除算・開平演算器。

【請求項1】

高基数の除算及び低基数の開平演算を行う除算・開平演算器において、

部分剰余の上位ビットを参照して商を定める商生成手段と、

前記部分剰余の前記上位ビットを2補数表現で保持し、前記部分剰余の前記上位ビット以外の下位ビットは冗長2進数表現で保持する部分剰余保持手段と、

除数と部分開平値を演算種別に応じて切り替えて保持する除数・部分開平値保持手段と、

前記商により前記除数・部分開平値保持手段からの除数及び部分開平値を選択する除数・部分開平値選択回路と、

前記下位ビットの冗長2進数表現の部分剰余と前記除数・部分開平値選択回路の出力とを入力する桁上げ保存加算器と、

前記上位ビットの2補数表現の部分剰余、前記下位ビットの冗長2進数表現の部分剰余、前記除数・部分開平値選択回路の出力、及び前記桁上げ保存加算器のキャリー信号を加算する桁上げ伝播加算器と、

前記桁上げ保存加算器の出力の上位ビットから基数に基づくビット数のビットデータ及び桁上げ伝播加算器の出力を入力して2補数化し演算の基数に基づくビット数シフトして次回の部分剰余として使用する2補数化・シフト手段とを有することを特徴とする除算・開平演算器。

【請求項2】

前記2補数化・シフト手段は、

前記桁上げ伝播加算器の出力と前記桁上げ保存加算器の出力の上位ビットから前記高基数に基づいて定められたビット数のビットデータとを入力して2補数化する第1の2補数変換手段と、

前記桁上げ伝播加算器の出力と前記桁上げ保存加算器の上位ビットから前記低基数に基づいて取り出したビット数のビットデータとを入力して2補数化する第2の2補数変換手段と、

除算においては第1の2補数変換回路を、開平演算においては第2の2補数変換手段の力を選択するセレクタと、

前記セレクタの出力を、次回の部分剰余として使用するよう、除算においては高基数に基づくビット数、開平演算においては低基数に基づくビット数シフトするシフタとを有することを特徴とする請求項1に記載の除算・開平演算器。

【請求項3】

前記2補数化・シフト手段は、

除算と開平演算の基数の違いにより定められるビット数、前記上位ビットの2補数表現の部分剰余を下位へシフトして前記桁上げ保存加算器に入力する第1のシフタと、

前記基数の違いにより定められるビット数、前記下位ビットの冗長2進数表現の部分剰余を下位へシフトして前記桁上げ伝播加算器に入力する第2のシフタと、

前記桁上げ保存加算器の出力の上位ビットから前記高基数に基づいて取り出したビット数のビットデータ及び前記桁上げ伝播加算器の出力を入力して2補数化する2補数変換手段と、

前記2補数変換手段の出力を次回の部分剰余として使用するよう前記高基数に基づくビット数シフトする第3のシフタとを有することを特徴とする請求項1に記載の除算・開平演算器。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2006−172035(P2006−172035A)

【公開日】平成18年6月29日(2006.6.29)

【国際特許分類】

【出願番号】特願2004−362300(P2004−362300)

【出願日】平成16年12月15日(2004.12.15)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成18年6月29日(2006.6.29)

【国際特許分類】

【出願日】平成16年12月15日(2004.12.15)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]