集積回路および集積回路の製造方法

【課題】トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成する方法を提供する。

【解決手段】トランジスタのゲート電極上に第1の誘電体層を形成し、第1の誘電体層上にエッチストップ層を形成し、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出し、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、トランジスタのS/D領域に接触させ、さらに金属層と接合したダマシン構造を形成する。

【解決手段】トランジスタのゲート電極上に第1の誘電体層を形成し、第1の誘電体層上にエッチストップ層を形成し、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出し、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、トランジスタのS/D領域に接触させ、さらに金属層と接合したダマシン構造を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、集積回路に関し、特に、集積回路および集積回路の製造方法に関するものである。

【背景技術】

【0002】

半導体集積回路(IC)産業は、急激な成長を遂げてきた。ICの材料および設計の技術的進歩は、各々の世代が前世代より、より小さく、より複雑な回路を有する、複数のICの世代を製造してきた。しかしながら、これらの進歩は、ICのプロセスおよび製造の複雑さを増加させてきた。そこで、これらの進歩が実現されるために、ICのプロセスおよび製造に同様の発展が必要となる。

【0003】

ICの発展過程では、機能密度(即ち、チップ単位面積あたりの相互接続される素子の数)は、一般的に増加し、幾何学的サイズ(geometry size)(即ち、製造プロセスを用いて作製され得る最小部品(またはライン))は、縮小している。この縮小化されたプロセスは、一般的に製造効率を上げ、かつ関連コストを下げることで利益を提供する。また、このような縮小化されたプロセスは、比較的高い熱放散を必要とするが、相補型金属酸化膜半導体(CMOS)デバイスなどの低消費電力デバイスを用いて対応され得る。

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の課題は、トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成するステップを含む集積回路を製造する方法を提供することである。

【課題を解決するための手段】

【0005】

本発明の集積回路の製造方法は、トランジスタのゲート電極上に第1の誘電体層を形成するステップ、第1の誘電体層上にエッチストップ層を形成するステップ、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出するステップ、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成し、トランジスタのソース/ドレイン領域に接触させるステップ、および金属層と接合したダマシン構造を形成するステップを含む。

【発明の効果】

【0006】

さまざまな実施例では、装置200は、1つのIC、いわゆる装置オンチップ(SOC)または装置オン集積回路(system on integrated circuit(SOIC))デバイスに全てのデバイスを提供し得る集積回路202を含む。これらのSOCデバイスは、単一の集積回路に、例えば、携帯電話、個人用携帯情報端末(PDA)、デジタルVCR、デジタルカムコーダー、デジタルカメラ、MP3プレーヤーなどを実装するのに必要な全ての回路を提供することが可能である。

【0007】

この開示は、添付の図面を参照して、次の詳細な説明から良く理解される。工業における標準実施に従って、種々の特徴が縮尺に描かれず、図示の目的のためだけに使用されている。実際、種々の特徴の数や寸法は、議論の明確化のために、任意に増加または減少されてもよい。

【図面の簡単な説明】

【0008】

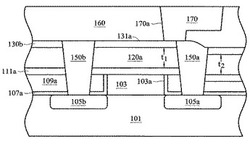

【図1A】集積回路を製造する例示的な方法を示す概略断面図である。

【図1B】集積回路を製造する例示的な方法を示す概略断面図である。

【図1C】集積回路を製造する例示的な方法を示す概略断面図である。

【図1D】集積回路を製造する例示的な方法を示す概略断面図である。

【図1E】集積回路を製造する例示的な方法を示す概略断面図である。

【図1F】集積回路を製造する例示的な方法を示す概略断面図である。

【図1G】集積回路を製造する例示的な方法を示す概略断面図である。

【図1H】集積回路を製造する例示的な方法を示す概略断面図である。

【図2】基板上に配置された例示的な集積回路を含む装置を示す概略図である。

【発明を実施するための形態】

【0009】

ビア層と接合された接触金属層を形成する既知の方法は、トランジスタの金属ゲート電極上に層間誘電体(ILD)層を形成するステップを含む。次いで、コンタクト穴がILD層に形成され、トランジスタのソース/ドレイン(S/D)領域を露出する。次いで、金属材料は、コンタクト穴およびILD層の上に形成される。化学機械研磨(CMP)プロセスは、ILD層上の金属材料を除去するように行われ、残っているILD層内に接触金属層を形成する。CMPプロセスは、残っているILD層および接触金属層の表面も平坦化することが可能なため、残っているILD層の表面が接触金属層の表面と同じ高さになる。金属ゲート電極を有する領域、および金属ゲート電極を有さない領域の上の残っているILD層の厚さは、異なることが判明されている。即ち、ゲート電極の残っているILD層の厚さは、金属ゲート電極を有さない領域の上の残っているILD層の厚さより小さい。

【0010】

残っているILD層および接触金属層の表面の平坦化の後、エッチストップ層は、残っているILD層および接触金属層の上に堆積される。次いで、金属間誘電体(IMD)層は、エッチストップ層上に堆積される。デュアルダマシン開口は、IMD層内に形成され、接触金属層を露出する。デュアルダマシン開口を形成するために、ビアエッチプロセスおよび/またはトレンチエッチプロセスが行われ、エッチストップ層を貫通してエッチングし、接触金属層を露出する。

【0011】

上述のように、ゲート電極の真上の残っているILD層は、CMPプロセスの後、薄くなる。エッチストップ層を貫通してエッチングするビアエッチプロセスおよび/またはトレンチエッチプロセスは、残っているILD層を望ましくなく陥凹させる、および/または金属ゲート電極にまで届かせる(reach)可能性がある。デュアルダマシン金属層を形成する金属材料が残っているILD層内の陥凹を充填する場合、金属材料は、金属ゲート電極に接触する。デュアルダマシン金属層は、金属ゲート電極との短絡を形成する。

【0012】

前述に基づき、集積回路の製造方法が必要である。

【0013】

次の開示は、その開示の異なる特徴を実施するための、多くの異なる実施の形態または実施例を提供することがわかる。本開示を簡素化するために、複数の要素および複数の配列の特定の実施例が以下に述べられる。これらは単に実施例であり、これらに制限されるものではないことは勿論である。また、本開示は、種々の実施例において、参照番号および/または文字を繰り返し用いている。この反復は、簡素化と明確さの目的のためであって、種々の実施の形態および/または議論された構成との間の関係を規定するものではない。また、本開示の別の特徴に接続および/または結合された特徴の形成は、続いて、特徴が直接接触で形成される複数の実施の形態を含むことができ、且つ前記特徴が直接接触でないように、付加的な特徴が前記特徴に介在するように形成された複数の実施の形態を含むこともできる。また、空間的に相対的な用語、例えば“下方”“上方”“水平”“垂直”“上の”“下の”“上”“下”“上部”“底部”などと、その派生語(例えば“水平に”“下方に”“上方に”など)は、本開示の1つの特徴と別の特徴との関係を簡略化するために用いられる。空間的に相対的な用語は、特徴を含むデバイスの異なる方向をカバーすることを意図している。

【0014】

図1A〜1Hは、集積回路を製造する例示的な方法を示す概略断面図である。図1Aでは、トランジスタ(図示されていない)のゲート電極103は、基板101上に形成されることができる。トランジスタの少なくとも1つのソース/ドレイン(S/D)領域、例えばS/D領域105aおよび105bは、基板101内に、かつゲート電極103に隣接して形成されてもよい。エッチストップ層107は、基板101上に、かつゲート電極103の側壁に隣接して形成されてもよい。誘電体層109は、エッチストップ層107上に形成され得る。エッチストップ層111は、ゲート電極103および誘電体層109の上に形成され得る。誘電体層120は、エッチストップ層111上に形成され得る。さまざまな実施の形態において、エッチストップ層107および/または誘電体層109の形成は、選択可能である。図1に関連して上述の構造は、単に例示にすぎず、本発明の範囲はこれに限定されるものではない。

【0015】

さまざまな実施の形態において、基板101は、結晶、多結晶、または非結晶構造のシリコン、またはゲルマニウムを含む元素半導体、炭化ケイ素、ガリウムヒ素、ガリウムリン、リン化インジウム、ヒ化インジウム、およびアンチモン化インジウムを含む化合物半導体、シリコンゲルマニウム(SiGe)、ガリウムヒ素リン(GaAsP)、アルミニウムインジウムヒ素(AlInAs)、アルミニウムガリウムヒ素(AlGaAs)、ヒ化ガリウムインジウム(GaInAs)、リン化ガリウムインジウム(GaInP)、およびヒ化リン化インジウムガリウム(GaInAsP)を含む合金半導体、他の任意の好適な材料、またはその組み合わせを含んでよい。1つの実施の形態では、合金半導体基板は、SiおよびGe組成が、傾斜したSiGeの特性の1つの位置の比からもう1つの位置のもう1つの比へと変化する、傾斜したSiGeの特性(gradient SiGe feature)を有し得る。もう1つの実施の形態では、SiGe基板は、歪みを受けている。また、半導体基板は、シリコンオンインシュレータ(SOI)、または薄膜トランジスタ(TFT)などの半導体オンインシュレータであり得る。いくつかの例では、半導体基板は、ドープされたエピ層または埋め込み層を含んでよい。他の例では、化合物半導体基板は、多層構造を有してもよく、または基板は、多層化合物半導体構造を含んでもよい。

【0016】

ゲート電極103は、ゲートファーストプロセス、またはゲートラストプロセスによって形成されてもよい。ゲート電極103は、ポリシリコン、シリコンゲルマニウム、例えばMo、Cu,W、Ti、Ta、TiN、TaN、NiSi、CoSi、および/または当技術分野で周知の他の好適な導電材料の金属化合物を含む金属材料を含んでよい。他の実施の形態では、ゲート電極103は、仕事関数金属層を含んで、金属ゲートのN型金属仕事関数またはP型金属仕事関数を提供し得る。P型仕事関数の材料は、ルテニウム、パラジウム、白金、コバルト、ニッケル、および導電性金属酸化物、および/または他の好適な材料などの成分を含む。N型仕事関数の材料は、ハフニウム、ジルコニウム、チタン、タンタル、アルミニウム、金属炭化物(例えば、炭化ハフニウム、炭化ジルコニウム、炭化チタン、炭化タンタル、炭化アルミニウム)、アルミナイド、および/または他の好適な材料などの成分を含む。ゲート電極103は、原子層堆積(ALD)、化学気相成長(CVD)、湿式酸化、物理気相成長(PVD)、リモートプラズマCVD(RPCVD)、プラズマCVD(PECVD)、有機金属CVD(MOCVD)、スパッタリング、蒸着、他の好適なプロセス、および/またはその組み合わせなどの任意の好適なプロセスによって形成されることができる。

【0017】

さまざまな実施の形態において、ゲート誘電体構造(図示されていない)は、ゲート電極103の下方に配置されることができる。ゲート誘電体構造は、単一層または多層構造を有してもよい。多層構造のさまざまな実施の形態において、ゲート誘電体構造は、界面層および高k誘電体層を含み得る。界面層は、酸化ケイ素、窒化ケイ素、酸窒化ケイ素、他の誘電体材料、および/またはその組み合わせなどの誘電体材料を含んでよい。高k誘電体層は、HfO2、HfSiO、HfSiON、HfTaO、HfTiO、HfZrO、他の好適な高誘電体材料、および/またはその組み合わせなどの高k誘電体材料を含んでよい。高k(誘電率:以下でも同じ)材料は、金属酸化物、金属窒化物、金属ケイ酸塩、遷移金属酸化物、遷移金属窒化物、遷移金属ケイ酸塩、金属酸窒化物、金属アルミネート、ケイ酸ジルコニウム、アルミン酸ジルコニウム、(zirconium aluminate)、酸化ケイ素、窒化ケイ素、酸窒化ケイ素、酸化ジルコニウム、酸化チタン、酸化アルミニウム、二酸化ハフニウムアルミナ(hafnium dioxide-alumina;HfO2−Al2O3)合金、他の好適な材料、および/またはその組み合わせから更に選択されてもよい。

【0018】

S/D領域105aおよび105bは、基板101内に形成される。N型トランジスタを製造するさまざまな実施の形態において、S/D領域105aおよび105bは、ヒ素(As)、リン(P)、他のV族元素、またはその任意の組み合わせなどのドーパントを有している。P型トランジスタを製造するさまざまな実施の形態において、S/D領域105aおよび105bは、例えばホウ素(B)など、他のIII族元素、またはそれらの任意の組み合わせなどのドーパントを有している。S/D領域105aおよび105bは、イオン注入および/または急速熱アニールプロセス(RTP)などの任意の好適なプロセスによって形成されて、S/D領域105aおよび105bを活性化させ得る。

【0019】

エッチストップ層107および111は、炭化ケイ素(SiC)、窒化ケイ素(SiN)、炭窒化ケイ素(SiCN)、炭酸化シリコン(SiCO)、酸窒化ケイ素(SiON)、窒化ホウ素(BN)、炭窒化ホウ素(BCN)、酸化ケイ素に対して望ましい選択比を有する他の材料、またはその任意の組み合わせなどの少なくとも1つの材料を有してもよい。エッチストップ層107および111は、原子層堆積(ALD)、化学気相成長(CVD)、湿式酸化、物理気相成長(PVD)、リモートプラズマCVD(RPCVD)、プラズマCVD(PECVD)、有機金属CVD(MOCVD)、スパッタリング、蒸着、他の好適なプロセス、および/またはその組み合わせなどの任意の好適なプロセスによって形成されることができる。

【0020】

誘電体層109および120は、例えば、高密度プラズマ(HDP)酸化物、プラズマ強化(PE)酸化物、オルトケイ酸テトラエチル(TEOS)、リンケイ酸ガラス(PSG)、ホウ素リンケイ酸ガラス(BPSG)、低k誘電体材料、超低k誘電体材料、またはその組み合わせなどの材料を含んでよい。さまざまな実施の形態において、誘電体層109および120は、例えば、高密度プラズマCVD(HDPCVD)またはプラズマCVD(PECVD)などの化学気相成長(CVD)、物理気相成長(PVD)、リモートプラズマCVD(RPCVD)、プラズマCVD(PECVD)、有機金属CVD(MOCVD)、スパッタリング、蒸着、他の好適なプロセス、および/またはその組み合わせなどの任意の好適なプロセスによって形成されてもよい。さまざまな実施の形態において、誘電体層109および120は、層間誘電体(ILD)層とも呼ばれる。

【0021】

図1Bを参照すると、エッチストップ層130が、誘電体層120上に形成されることができる。エッチストップ層130は、下記に示すように、除去プロセス、例えば、化学機械研磨(CMP)プロセスの際のエッチストップ層となり得る。エッチストップ層130は、炭化ケイ素(SiC)、窒化ケイ素(SiN)、炭窒化ケイ素(SiCN)、炭酸化シリコン(SiCO)、酸窒化ケイ素(SiON)、窒化ホウ素(BN)、炭窒化ホウ素(BCN)、酸化ケイ素のエッチング選択比より高いエッチング選択比を有する他の材料、またはその任意の組み合わせなどの少なくとも1つの材料を有してもよい。さまざまな実施の形態において、エッチストップ層130は、原子層堆積(ALD)、化学気相成長(CVD)、湿式酸化、物理気相成長(PVD)、リモートプラズマCVD(RPCVD)、プラズマCVD(PECVD)、有機金属CVD(MOCVD)、スパッタリング、蒸着、他の好適なプロセス、および/またはその組み合わせなどの任意の好適なプロセスによって形成されることができる。

【0022】

図1Cを参照すると、誘電体層140が、エッチストップ層130上に選択的に形成されている。誘電体層140は、下記に示すように、除去プロセス、例えば、化学機械研磨(CMP)プロセスの際の過剰研磨(over-polish)層となり得る。さまざまな実施の形態において、誘電体層140は、エッチストップ層130がスパッタリングプロセス、例えば、エッチングプロセスを受けることから望ましく保護し、かつエッチストップ層130から炭素ガス放出を防ぐことができる。また、他の実施の形態において、誘電体層140は、エッチストップ層130がスパッタリングプロセス、例えば、エッチングプロセスを受けることから望ましく保護し得る。エッチストップ層130の材料は、実質的に変えられることがないため、エッチおよび/またはCMPプロセスに対するエッチストップ層130のエッチング選択比は、実質的に下がることがない。

【0023】

22nm技術を用いた種々の実施の形態では、エッチストップ層130は、約250Å以上の厚さに堆積され得、誘電体層140は、約400Å以上の厚さに堆積され得る。誘電体層140は、CMPプロセス用に所望の過剰研磨マージン(margin)を提供し得る。他の実施の形態において、エッチストップ層130自体が、CMPプロセス用に所望の過剰研磨マージンを提供し得る。例えば、エッチストップ層130が約550Å以上の厚さに堆積された場合、誘電体層140は、必要でなくなる。

【0024】

さまざまな実施の形態において、誘電体層140は、例えば、高密度プラズマ(HDP)酸化物、プラズマ強化(PE)酸化物、オルトケイ酸テトラエチル(TEOS)、リンケイ酸ガラス(PSG)、ホウ素リンケイ酸ガラス(BPSG)、低k誘電体材料、超低k誘電体材料、またはその組み合わせなどの材料を含んでよい。さまざまな実施の形態において、誘電体層140は、例えば、高密度プラズマCVD(HDPCVD)またはプラズマCVD(PECVD)の化学気相成長(CVD)、物理気相成長(PVD)、リモートプラズマCVD(RPCVD)、プラズマCVD(PECVD)、有機金属CVD(MOCVD)、スパッタリング、蒸着、他の好適なプロセス、および/またはその組み合わせなどの任意の好適なプロセスによって形成されることができる。

【0025】

図1Dを参照すると、エッチプロセスは、エッチストップ層107、111、および130、並びに誘電体層109、120、および140の一部を除去して、少なくとも1つの開口、例えば、コンタクト穴145aおよび145bを形成する。コンタクト穴145aおよび145bは、エッチストップ層107a、111a、および130a、並びに誘電体層109a、120a、および140aを貫通して形成される。コンタクト穴145aおよび145bは、S/D領域105aおよび105bの少なくとも表面の部分をそれぞれ露出している。

【0026】

さまざまな実施の形態において、ケイ化物構造(図示されていない)がS/D領域105aおよび105bの露出した表面上に形成され得る。ケイ化物構造は、ニッケルシリサイド(NiSi)、ケイ化ニッケル−白金(NiPtSi)、ケイ化ニッケル−白金−ゲルマニウム(NiPtGeSi)、ケイ化ニッケル−ゲルマニウム(NiGeSi)、ケイ化イットリウム(YbSi)、ケイ化白金(PtSi)、ケイ化イリジウム(IrSi)、ケイ化エルビウム(ErSi)、ケイ化コバルト(CoSi)、他の好適な材料、および/またはその組み合わせなどの材料を含んでよい。

【0027】

図1Eを参照すると、金属材料150が、コンタクト穴145aおよび145b内、および誘電体層140a上に形成される。さまざまな実施の形態において、金属材料150は、タングステン、アルミニウム、銅、チタン、タンタル、窒化チタン、窒化タンタル、ケイ化ニッケル、ケイ化コバルト、他の好適な導電材料、および/またはその組み合わせなどの材料を含んでよい。金属材料150は、例えば、CVD、ALD、PVD、および/または好適なプロセスによって、金属材料を誘電体層140a上に堆積することで形成され得る。

【0028】

図1Fを参照すると、除去プロセス155、例えば、CMPプロセスは、エッチストップ層130a上の金属材料150の一部および誘電体層140a(図1Eに図示されている)を除去して、金属層150aおよび150bを形成し得る。除去プロセス155は、エッチストップ層130aに対する金属材料150の所望のエッチング選択比を有している。エッチング選択比は、5以上であり得る。さまざまな実施の形態において、除去プロセス155は、エッチストップ層130aの一部を除去して、エッチストップ層130bを残してもよい。エッチストップ層130bの厚さは、エッチストップ層130aの厚さより小さくてもよい。

【0029】

誘電体層140aを用いたさまざまな実施の形態において、誘電体層140aは、除去プロセス155によって完全にまたは実質的に除去され得る。エッチストップ層130bは、約150Å以上の残っている厚さを有し得る。他の実施の形態では、エッチストップ層130b自体が、CMPプロセス用に所望の過剰研磨マージンを提供し得る。例えば、エッチストップ層130(図1Bに図示されている)は、約550Å以上の厚さに堆積される。除去プロセス155の後、エッチストップ層130bは、約150Å以上の残っている厚さを有している。

【0030】

図1Fを再度参照すると、エッチストップ層130bは、上面131aおよび131bを有し得る。ゲート電極103によって生じるステップ高により、上面131aおよび131bは、互いに同じ高さでない可能性がある。さまざまな実施の形態において、金属層150aは、上面131aおよび131bの間の界面に形成される。金属層150aは、上面131aと実質的に同じ高さである表面151aを有している。金属層150aは、上面131bと実質的に同じ高さであるもう1つの表面151bを有している。金属層150bは、上面131aと実質的に同じ高さである表面152を有している。さまざまな実施の形態において、金属層150aおよび150bは、“金属0”層と呼ばれる。

【0031】

図1Gを参照すると、誘電体層160が、エッチストップ層130b上に形成される。ダマシン開口165、例えばシングルダマシン開口またはデュアルダマシン開口は、誘電体層160内に形成されて金属層150aの表面151aを露出し得る。エッチストップ層130bは、ダマシン開口165を形成するエッチストップ層となり得る。エッチストップ層130bは、ビアエッチプロセスおよび/またはトレンチプロセスによって誘電体層120aを窪まないように保護し、ダマシン開口165を形成している。ゲート電極103の真上の誘電体層120aは、ゲート電極103のない領域の誘電体層120aの厚さ“t2”に実質的に等しい厚さ“t1”を有している。

【0032】

図1Hを参照すると、ダマシン構造170、例えば、シングルダマシン構造またはデュアルダマシン構造は、ダマシン開口165内に形成され、金属層150aに接触している。さまざまな実施の形態において、ダマシン構造170のエッジ(edge)170aは、上面131aに実質的に垂直な方向で、ゲート電極103のエッジ103aと実質的に位置合わせされている。デュアルダマシン構造を形成する実施の形態では、ダマシン構造170は、ビアプラグおよび金属配線を含んでいる。ビアプラグは、“ビア0”層と呼ばれ、金属配線は“金属1”層と呼ばれる。

【0033】

さまざまな実施の形態において、ダマシン構造170は、タングステン、アルミニウム、銅、チタン、タンタル、窒化チタン、窒化タンタル、ケイ化ニッケル、ケイ化コバルト、他の好適な導電材料、および/またはその組み合わせなどの材料を含んでよい。ダマシン構造170は、例えば、CVD、ALD、PVD、および/または好適な除去プロセス、例えばCMPによって、金属材料を誘電体層160内に堆積することで形成されることができる。

【0034】

さまざまな実施の形態において、付加的な誘電材料、ビアプラグ、金属領域、および/または金属配線が相互接続用に誘電体層160上に形成される。ビアプラグ、金属領域、および/または金属配線は、タングステン、アルミニウム、銅、チタン、タンタル、窒化チタン、窒化タンタル、ケイ化ニッケル、ケイ化コバルト、他の好適な導電材料、および/またはその組み合わせなどの材料を含んでよい。ビアプラグ、金属領域、および/または金属配線は、堆積、フォトリソグラフィー、およびエッチングプロセス、および/またはその組み合わせなどの任意の好適なプロセスによって形成される。

【0035】

図2は、基板上に配置された例示的な集積回路を含む装置を示す概略図である。図2では、装置200は、基板201上に配置された集積回路202を含んでいる。基板201は、プリント回路板(PCB)、プリント配線板、および/または集積回路を搭載(carrying)できる他のキャリアでもよい。集積回路202は、図1A〜1Hに関連して上述の方法によって製造される構造を含み得る。集積回路202は、基板201と電気的に接続されている。さまざまな実施の形態において、集積回路202は、バンプ205によって基板201と電気的に接続されることができる。他の実施の形態では、集積回路202は、ワイヤボンディングによって基板201と電気的に接続されることができる。装置200は、コンピュータ、無線通信デバイス、コンピュータ周辺機器、娯楽機器などの一部であることができる。

【0036】

さまざまな実施の形態において、集積回路202を含む装置200は、単一のIC、いわゆる装置オンチップ(SOC)または集積回路装置(system on integrated circuit;SOIC)に全装置を提供し得る。これらのSOCデバイスは、単一の集積回路に、例えば、携帯電話、PDA、デジタルVCR、デジタルカムコーダー、デジタルカメラ、MP3プレーヤーなどを実行するために必要な全ての回路を提供し得る。

【0037】

以上、当業者が本開示の態様をより理解できるように幾つかの実施の形態特徴を概説した。当業者は、本開示を、ここで採用された実施の形態の、同じ目的を実行し実行しおよび/または同じ利点を達成するために他のプロセスおよび構造を設計または改変するための基礎として、容易に使用できることが分かる。本開示の精神および範囲を逸脱しない限りにおいては、当業者であればそのような等価な構成を達成することが可能であり、当業者は、本開示の精神および範囲を逸脱せずに、ここで種々の変更、代替、および改変をするだろう。

【技術分野】

【0001】

本発明は、集積回路に関し、特に、集積回路および集積回路の製造方法に関するものである。

【背景技術】

【0002】

半導体集積回路(IC)産業は、急激な成長を遂げてきた。ICの材料および設計の技術的進歩は、各々の世代が前世代より、より小さく、より複雑な回路を有する、複数のICの世代を製造してきた。しかしながら、これらの進歩は、ICのプロセスおよび製造の複雑さを増加させてきた。そこで、これらの進歩が実現されるために、ICのプロセスおよび製造に同様の発展が必要となる。

【0003】

ICの発展過程では、機能密度(即ち、チップ単位面積あたりの相互接続される素子の数)は、一般的に増加し、幾何学的サイズ(geometry size)(即ち、製造プロセスを用いて作製され得る最小部品(またはライン))は、縮小している。この縮小化されたプロセスは、一般的に製造効率を上げ、かつ関連コストを下げることで利益を提供する。また、このような縮小化されたプロセスは、比較的高い熱放散を必要とするが、相補型金属酸化膜半導体(CMOS)デバイスなどの低消費電力デバイスを用いて対応され得る。

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の課題は、トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成するステップを含む集積回路を製造する方法を提供することである。

【課題を解決するための手段】

【0005】

本発明の集積回路の製造方法は、トランジスタのゲート電極上に第1の誘電体層を形成するステップ、第1の誘電体層上にエッチストップ層を形成するステップ、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出するステップ、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成し、トランジスタのソース/ドレイン領域に接触させるステップ、および金属層と接合したダマシン構造を形成するステップを含む。

【発明の効果】

【0006】

さまざまな実施例では、装置200は、1つのIC、いわゆる装置オンチップ(SOC)または装置オン集積回路(system on integrated circuit(SOIC))デバイスに全てのデバイスを提供し得る集積回路202を含む。これらのSOCデバイスは、単一の集積回路に、例えば、携帯電話、個人用携帯情報端末(PDA)、デジタルVCR、デジタルカムコーダー、デジタルカメラ、MP3プレーヤーなどを実装するのに必要な全ての回路を提供することが可能である。

【0007】

この開示は、添付の図面を参照して、次の詳細な説明から良く理解される。工業における標準実施に従って、種々の特徴が縮尺に描かれず、図示の目的のためだけに使用されている。実際、種々の特徴の数や寸法は、議論の明確化のために、任意に増加または減少されてもよい。

【図面の簡単な説明】

【0008】

【図1A】集積回路を製造する例示的な方法を示す概略断面図である。

【図1B】集積回路を製造する例示的な方法を示す概略断面図である。

【図1C】集積回路を製造する例示的な方法を示す概略断面図である。

【図1D】集積回路を製造する例示的な方法を示す概略断面図である。

【図1E】集積回路を製造する例示的な方法を示す概略断面図である。

【図1F】集積回路を製造する例示的な方法を示す概略断面図である。

【図1G】集積回路を製造する例示的な方法を示す概略断面図である。

【図1H】集積回路を製造する例示的な方法を示す概略断面図である。

【図2】基板上に配置された例示的な集積回路を含む装置を示す概略図である。

【発明を実施するための形態】

【0009】

ビア層と接合された接触金属層を形成する既知の方法は、トランジスタの金属ゲート電極上に層間誘電体(ILD)層を形成するステップを含む。次いで、コンタクト穴がILD層に形成され、トランジスタのソース/ドレイン(S/D)領域を露出する。次いで、金属材料は、コンタクト穴およびILD層の上に形成される。化学機械研磨(CMP)プロセスは、ILD層上の金属材料を除去するように行われ、残っているILD層内に接触金属層を形成する。CMPプロセスは、残っているILD層および接触金属層の表面も平坦化することが可能なため、残っているILD層の表面が接触金属層の表面と同じ高さになる。金属ゲート電極を有する領域、および金属ゲート電極を有さない領域の上の残っているILD層の厚さは、異なることが判明されている。即ち、ゲート電極の残っているILD層の厚さは、金属ゲート電極を有さない領域の上の残っているILD層の厚さより小さい。

【0010】

残っているILD層および接触金属層の表面の平坦化の後、エッチストップ層は、残っているILD層および接触金属層の上に堆積される。次いで、金属間誘電体(IMD)層は、エッチストップ層上に堆積される。デュアルダマシン開口は、IMD層内に形成され、接触金属層を露出する。デュアルダマシン開口を形成するために、ビアエッチプロセスおよび/またはトレンチエッチプロセスが行われ、エッチストップ層を貫通してエッチングし、接触金属層を露出する。

【0011】

上述のように、ゲート電極の真上の残っているILD層は、CMPプロセスの後、薄くなる。エッチストップ層を貫通してエッチングするビアエッチプロセスおよび/またはトレンチエッチプロセスは、残っているILD層を望ましくなく陥凹させる、および/または金属ゲート電極にまで届かせる(reach)可能性がある。デュアルダマシン金属層を形成する金属材料が残っているILD層内の陥凹を充填する場合、金属材料は、金属ゲート電極に接触する。デュアルダマシン金属層は、金属ゲート電極との短絡を形成する。

【0012】

前述に基づき、集積回路の製造方法が必要である。

【0013】

次の開示は、その開示の異なる特徴を実施するための、多くの異なる実施の形態または実施例を提供することがわかる。本開示を簡素化するために、複数の要素および複数の配列の特定の実施例が以下に述べられる。これらは単に実施例であり、これらに制限されるものではないことは勿論である。また、本開示は、種々の実施例において、参照番号および/または文字を繰り返し用いている。この反復は、簡素化と明確さの目的のためであって、種々の実施の形態および/または議論された構成との間の関係を規定するものではない。また、本開示の別の特徴に接続および/または結合された特徴の形成は、続いて、特徴が直接接触で形成される複数の実施の形態を含むことができ、且つ前記特徴が直接接触でないように、付加的な特徴が前記特徴に介在するように形成された複数の実施の形態を含むこともできる。また、空間的に相対的な用語、例えば“下方”“上方”“水平”“垂直”“上の”“下の”“上”“下”“上部”“底部”などと、その派生語(例えば“水平に”“下方に”“上方に”など)は、本開示の1つの特徴と別の特徴との関係を簡略化するために用いられる。空間的に相対的な用語は、特徴を含むデバイスの異なる方向をカバーすることを意図している。

【0014】

図1A〜1Hは、集積回路を製造する例示的な方法を示す概略断面図である。図1Aでは、トランジスタ(図示されていない)のゲート電極103は、基板101上に形成されることができる。トランジスタの少なくとも1つのソース/ドレイン(S/D)領域、例えばS/D領域105aおよび105bは、基板101内に、かつゲート電極103に隣接して形成されてもよい。エッチストップ層107は、基板101上に、かつゲート電極103の側壁に隣接して形成されてもよい。誘電体層109は、エッチストップ層107上に形成され得る。エッチストップ層111は、ゲート電極103および誘電体層109の上に形成され得る。誘電体層120は、エッチストップ層111上に形成され得る。さまざまな実施の形態において、エッチストップ層107および/または誘電体層109の形成は、選択可能である。図1に関連して上述の構造は、単に例示にすぎず、本発明の範囲はこれに限定されるものではない。

【0015】

さまざまな実施の形態において、基板101は、結晶、多結晶、または非結晶構造のシリコン、またはゲルマニウムを含む元素半導体、炭化ケイ素、ガリウムヒ素、ガリウムリン、リン化インジウム、ヒ化インジウム、およびアンチモン化インジウムを含む化合物半導体、シリコンゲルマニウム(SiGe)、ガリウムヒ素リン(GaAsP)、アルミニウムインジウムヒ素(AlInAs)、アルミニウムガリウムヒ素(AlGaAs)、ヒ化ガリウムインジウム(GaInAs)、リン化ガリウムインジウム(GaInP)、およびヒ化リン化インジウムガリウム(GaInAsP)を含む合金半導体、他の任意の好適な材料、またはその組み合わせを含んでよい。1つの実施の形態では、合金半導体基板は、SiおよびGe組成が、傾斜したSiGeの特性の1つの位置の比からもう1つの位置のもう1つの比へと変化する、傾斜したSiGeの特性(gradient SiGe feature)を有し得る。もう1つの実施の形態では、SiGe基板は、歪みを受けている。また、半導体基板は、シリコンオンインシュレータ(SOI)、または薄膜トランジスタ(TFT)などの半導体オンインシュレータであり得る。いくつかの例では、半導体基板は、ドープされたエピ層または埋め込み層を含んでよい。他の例では、化合物半導体基板は、多層構造を有してもよく、または基板は、多層化合物半導体構造を含んでもよい。

【0016】

ゲート電極103は、ゲートファーストプロセス、またはゲートラストプロセスによって形成されてもよい。ゲート電極103は、ポリシリコン、シリコンゲルマニウム、例えばMo、Cu,W、Ti、Ta、TiN、TaN、NiSi、CoSi、および/または当技術分野で周知の他の好適な導電材料の金属化合物を含む金属材料を含んでよい。他の実施の形態では、ゲート電極103は、仕事関数金属層を含んで、金属ゲートのN型金属仕事関数またはP型金属仕事関数を提供し得る。P型仕事関数の材料は、ルテニウム、パラジウム、白金、コバルト、ニッケル、および導電性金属酸化物、および/または他の好適な材料などの成分を含む。N型仕事関数の材料は、ハフニウム、ジルコニウム、チタン、タンタル、アルミニウム、金属炭化物(例えば、炭化ハフニウム、炭化ジルコニウム、炭化チタン、炭化タンタル、炭化アルミニウム)、アルミナイド、および/または他の好適な材料などの成分を含む。ゲート電極103は、原子層堆積(ALD)、化学気相成長(CVD)、湿式酸化、物理気相成長(PVD)、リモートプラズマCVD(RPCVD)、プラズマCVD(PECVD)、有機金属CVD(MOCVD)、スパッタリング、蒸着、他の好適なプロセス、および/またはその組み合わせなどの任意の好適なプロセスによって形成されることができる。

【0017】

さまざまな実施の形態において、ゲート誘電体構造(図示されていない)は、ゲート電極103の下方に配置されることができる。ゲート誘電体構造は、単一層または多層構造を有してもよい。多層構造のさまざまな実施の形態において、ゲート誘電体構造は、界面層および高k誘電体層を含み得る。界面層は、酸化ケイ素、窒化ケイ素、酸窒化ケイ素、他の誘電体材料、および/またはその組み合わせなどの誘電体材料を含んでよい。高k誘電体層は、HfO2、HfSiO、HfSiON、HfTaO、HfTiO、HfZrO、他の好適な高誘電体材料、および/またはその組み合わせなどの高k誘電体材料を含んでよい。高k(誘電率:以下でも同じ)材料は、金属酸化物、金属窒化物、金属ケイ酸塩、遷移金属酸化物、遷移金属窒化物、遷移金属ケイ酸塩、金属酸窒化物、金属アルミネート、ケイ酸ジルコニウム、アルミン酸ジルコニウム、(zirconium aluminate)、酸化ケイ素、窒化ケイ素、酸窒化ケイ素、酸化ジルコニウム、酸化チタン、酸化アルミニウム、二酸化ハフニウムアルミナ(hafnium dioxide-alumina;HfO2−Al2O3)合金、他の好適な材料、および/またはその組み合わせから更に選択されてもよい。

【0018】

S/D領域105aおよび105bは、基板101内に形成される。N型トランジスタを製造するさまざまな実施の形態において、S/D領域105aおよび105bは、ヒ素(As)、リン(P)、他のV族元素、またはその任意の組み合わせなどのドーパントを有している。P型トランジスタを製造するさまざまな実施の形態において、S/D領域105aおよび105bは、例えばホウ素(B)など、他のIII族元素、またはそれらの任意の組み合わせなどのドーパントを有している。S/D領域105aおよび105bは、イオン注入および/または急速熱アニールプロセス(RTP)などの任意の好適なプロセスによって形成されて、S/D領域105aおよび105bを活性化させ得る。

【0019】

エッチストップ層107および111は、炭化ケイ素(SiC)、窒化ケイ素(SiN)、炭窒化ケイ素(SiCN)、炭酸化シリコン(SiCO)、酸窒化ケイ素(SiON)、窒化ホウ素(BN)、炭窒化ホウ素(BCN)、酸化ケイ素に対して望ましい選択比を有する他の材料、またはその任意の組み合わせなどの少なくとも1つの材料を有してもよい。エッチストップ層107および111は、原子層堆積(ALD)、化学気相成長(CVD)、湿式酸化、物理気相成長(PVD)、リモートプラズマCVD(RPCVD)、プラズマCVD(PECVD)、有機金属CVD(MOCVD)、スパッタリング、蒸着、他の好適なプロセス、および/またはその組み合わせなどの任意の好適なプロセスによって形成されることができる。

【0020】

誘電体層109および120は、例えば、高密度プラズマ(HDP)酸化物、プラズマ強化(PE)酸化物、オルトケイ酸テトラエチル(TEOS)、リンケイ酸ガラス(PSG)、ホウ素リンケイ酸ガラス(BPSG)、低k誘電体材料、超低k誘電体材料、またはその組み合わせなどの材料を含んでよい。さまざまな実施の形態において、誘電体層109および120は、例えば、高密度プラズマCVD(HDPCVD)またはプラズマCVD(PECVD)などの化学気相成長(CVD)、物理気相成長(PVD)、リモートプラズマCVD(RPCVD)、プラズマCVD(PECVD)、有機金属CVD(MOCVD)、スパッタリング、蒸着、他の好適なプロセス、および/またはその組み合わせなどの任意の好適なプロセスによって形成されてもよい。さまざまな実施の形態において、誘電体層109および120は、層間誘電体(ILD)層とも呼ばれる。

【0021】

図1Bを参照すると、エッチストップ層130が、誘電体層120上に形成されることができる。エッチストップ層130は、下記に示すように、除去プロセス、例えば、化学機械研磨(CMP)プロセスの際のエッチストップ層となり得る。エッチストップ層130は、炭化ケイ素(SiC)、窒化ケイ素(SiN)、炭窒化ケイ素(SiCN)、炭酸化シリコン(SiCO)、酸窒化ケイ素(SiON)、窒化ホウ素(BN)、炭窒化ホウ素(BCN)、酸化ケイ素のエッチング選択比より高いエッチング選択比を有する他の材料、またはその任意の組み合わせなどの少なくとも1つの材料を有してもよい。さまざまな実施の形態において、エッチストップ層130は、原子層堆積(ALD)、化学気相成長(CVD)、湿式酸化、物理気相成長(PVD)、リモートプラズマCVD(RPCVD)、プラズマCVD(PECVD)、有機金属CVD(MOCVD)、スパッタリング、蒸着、他の好適なプロセス、および/またはその組み合わせなどの任意の好適なプロセスによって形成されることができる。

【0022】

図1Cを参照すると、誘電体層140が、エッチストップ層130上に選択的に形成されている。誘電体層140は、下記に示すように、除去プロセス、例えば、化学機械研磨(CMP)プロセスの際の過剰研磨(over-polish)層となり得る。さまざまな実施の形態において、誘電体層140は、エッチストップ層130がスパッタリングプロセス、例えば、エッチングプロセスを受けることから望ましく保護し、かつエッチストップ層130から炭素ガス放出を防ぐことができる。また、他の実施の形態において、誘電体層140は、エッチストップ層130がスパッタリングプロセス、例えば、エッチングプロセスを受けることから望ましく保護し得る。エッチストップ層130の材料は、実質的に変えられることがないため、エッチおよび/またはCMPプロセスに対するエッチストップ層130のエッチング選択比は、実質的に下がることがない。

【0023】

22nm技術を用いた種々の実施の形態では、エッチストップ層130は、約250Å以上の厚さに堆積され得、誘電体層140は、約400Å以上の厚さに堆積され得る。誘電体層140は、CMPプロセス用に所望の過剰研磨マージン(margin)を提供し得る。他の実施の形態において、エッチストップ層130自体が、CMPプロセス用に所望の過剰研磨マージンを提供し得る。例えば、エッチストップ層130が約550Å以上の厚さに堆積された場合、誘電体層140は、必要でなくなる。

【0024】

さまざまな実施の形態において、誘電体層140は、例えば、高密度プラズマ(HDP)酸化物、プラズマ強化(PE)酸化物、オルトケイ酸テトラエチル(TEOS)、リンケイ酸ガラス(PSG)、ホウ素リンケイ酸ガラス(BPSG)、低k誘電体材料、超低k誘電体材料、またはその組み合わせなどの材料を含んでよい。さまざまな実施の形態において、誘電体層140は、例えば、高密度プラズマCVD(HDPCVD)またはプラズマCVD(PECVD)の化学気相成長(CVD)、物理気相成長(PVD)、リモートプラズマCVD(RPCVD)、プラズマCVD(PECVD)、有機金属CVD(MOCVD)、スパッタリング、蒸着、他の好適なプロセス、および/またはその組み合わせなどの任意の好適なプロセスによって形成されることができる。

【0025】

図1Dを参照すると、エッチプロセスは、エッチストップ層107、111、および130、並びに誘電体層109、120、および140の一部を除去して、少なくとも1つの開口、例えば、コンタクト穴145aおよび145bを形成する。コンタクト穴145aおよび145bは、エッチストップ層107a、111a、および130a、並びに誘電体層109a、120a、および140aを貫通して形成される。コンタクト穴145aおよび145bは、S/D領域105aおよび105bの少なくとも表面の部分をそれぞれ露出している。

【0026】

さまざまな実施の形態において、ケイ化物構造(図示されていない)がS/D領域105aおよび105bの露出した表面上に形成され得る。ケイ化物構造は、ニッケルシリサイド(NiSi)、ケイ化ニッケル−白金(NiPtSi)、ケイ化ニッケル−白金−ゲルマニウム(NiPtGeSi)、ケイ化ニッケル−ゲルマニウム(NiGeSi)、ケイ化イットリウム(YbSi)、ケイ化白金(PtSi)、ケイ化イリジウム(IrSi)、ケイ化エルビウム(ErSi)、ケイ化コバルト(CoSi)、他の好適な材料、および/またはその組み合わせなどの材料を含んでよい。

【0027】

図1Eを参照すると、金属材料150が、コンタクト穴145aおよび145b内、および誘電体層140a上に形成される。さまざまな実施の形態において、金属材料150は、タングステン、アルミニウム、銅、チタン、タンタル、窒化チタン、窒化タンタル、ケイ化ニッケル、ケイ化コバルト、他の好適な導電材料、および/またはその組み合わせなどの材料を含んでよい。金属材料150は、例えば、CVD、ALD、PVD、および/または好適なプロセスによって、金属材料を誘電体層140a上に堆積することで形成され得る。

【0028】

図1Fを参照すると、除去プロセス155、例えば、CMPプロセスは、エッチストップ層130a上の金属材料150の一部および誘電体層140a(図1Eに図示されている)を除去して、金属層150aおよび150bを形成し得る。除去プロセス155は、エッチストップ層130aに対する金属材料150の所望のエッチング選択比を有している。エッチング選択比は、5以上であり得る。さまざまな実施の形態において、除去プロセス155は、エッチストップ層130aの一部を除去して、エッチストップ層130bを残してもよい。エッチストップ層130bの厚さは、エッチストップ層130aの厚さより小さくてもよい。

【0029】

誘電体層140aを用いたさまざまな実施の形態において、誘電体層140aは、除去プロセス155によって完全にまたは実質的に除去され得る。エッチストップ層130bは、約150Å以上の残っている厚さを有し得る。他の実施の形態では、エッチストップ層130b自体が、CMPプロセス用に所望の過剰研磨マージンを提供し得る。例えば、エッチストップ層130(図1Bに図示されている)は、約550Å以上の厚さに堆積される。除去プロセス155の後、エッチストップ層130bは、約150Å以上の残っている厚さを有している。

【0030】

図1Fを再度参照すると、エッチストップ層130bは、上面131aおよび131bを有し得る。ゲート電極103によって生じるステップ高により、上面131aおよび131bは、互いに同じ高さでない可能性がある。さまざまな実施の形態において、金属層150aは、上面131aおよび131bの間の界面に形成される。金属層150aは、上面131aと実質的に同じ高さである表面151aを有している。金属層150aは、上面131bと実質的に同じ高さであるもう1つの表面151bを有している。金属層150bは、上面131aと実質的に同じ高さである表面152を有している。さまざまな実施の形態において、金属層150aおよび150bは、“金属0”層と呼ばれる。

【0031】

図1Gを参照すると、誘電体層160が、エッチストップ層130b上に形成される。ダマシン開口165、例えばシングルダマシン開口またはデュアルダマシン開口は、誘電体層160内に形成されて金属層150aの表面151aを露出し得る。エッチストップ層130bは、ダマシン開口165を形成するエッチストップ層となり得る。エッチストップ層130bは、ビアエッチプロセスおよび/またはトレンチプロセスによって誘電体層120aを窪まないように保護し、ダマシン開口165を形成している。ゲート電極103の真上の誘電体層120aは、ゲート電極103のない領域の誘電体層120aの厚さ“t2”に実質的に等しい厚さ“t1”を有している。

【0032】

図1Hを参照すると、ダマシン構造170、例えば、シングルダマシン構造またはデュアルダマシン構造は、ダマシン開口165内に形成され、金属層150aに接触している。さまざまな実施の形態において、ダマシン構造170のエッジ(edge)170aは、上面131aに実質的に垂直な方向で、ゲート電極103のエッジ103aと実質的に位置合わせされている。デュアルダマシン構造を形成する実施の形態では、ダマシン構造170は、ビアプラグおよび金属配線を含んでいる。ビアプラグは、“ビア0”層と呼ばれ、金属配線は“金属1”層と呼ばれる。

【0033】

さまざまな実施の形態において、ダマシン構造170は、タングステン、アルミニウム、銅、チタン、タンタル、窒化チタン、窒化タンタル、ケイ化ニッケル、ケイ化コバルト、他の好適な導電材料、および/またはその組み合わせなどの材料を含んでよい。ダマシン構造170は、例えば、CVD、ALD、PVD、および/または好適な除去プロセス、例えばCMPによって、金属材料を誘電体層160内に堆積することで形成されることができる。

【0034】

さまざまな実施の形態において、付加的な誘電材料、ビアプラグ、金属領域、および/または金属配線が相互接続用に誘電体層160上に形成される。ビアプラグ、金属領域、および/または金属配線は、タングステン、アルミニウム、銅、チタン、タンタル、窒化チタン、窒化タンタル、ケイ化ニッケル、ケイ化コバルト、他の好適な導電材料、および/またはその組み合わせなどの材料を含んでよい。ビアプラグ、金属領域、および/または金属配線は、堆積、フォトリソグラフィー、およびエッチングプロセス、および/またはその組み合わせなどの任意の好適なプロセスによって形成される。

【0035】

図2は、基板上に配置された例示的な集積回路を含む装置を示す概略図である。図2では、装置200は、基板201上に配置された集積回路202を含んでいる。基板201は、プリント回路板(PCB)、プリント配線板、および/または集積回路を搭載(carrying)できる他のキャリアでもよい。集積回路202は、図1A〜1Hに関連して上述の方法によって製造される構造を含み得る。集積回路202は、基板201と電気的に接続されている。さまざまな実施の形態において、集積回路202は、バンプ205によって基板201と電気的に接続されることができる。他の実施の形態では、集積回路202は、ワイヤボンディングによって基板201と電気的に接続されることができる。装置200は、コンピュータ、無線通信デバイス、コンピュータ周辺機器、娯楽機器などの一部であることができる。

【0036】

さまざまな実施の形態において、集積回路202を含む装置200は、単一のIC、いわゆる装置オンチップ(SOC)または集積回路装置(system on integrated circuit;SOIC)に全装置を提供し得る。これらのSOCデバイスは、単一の集積回路に、例えば、携帯電話、PDA、デジタルVCR、デジタルカムコーダー、デジタルカメラ、MP3プレーヤーなどを実行するために必要な全ての回路を提供し得る。

【0037】

以上、当業者が本開示の態様をより理解できるように幾つかの実施の形態特徴を概説した。当業者は、本開示を、ここで採用された実施の形態の、同じ目的を実行し実行しおよび/または同じ利点を達成するために他のプロセスおよび構造を設計または改変するための基礎として、容易に使用できることが分かる。本開示の精神および範囲を逸脱しない限りにおいては、当業者であればそのような等価な構成を達成することが可能であり、当業者は、本開示の精神および範囲を逸脱せずに、ここで種々の変更、代替、および改変をするだろう。

【特許請求の範囲】

【請求項1】

集積回路を製造する方法であって、前記方法は、

トランジスタのゲート電極上に第1の誘電体層を形成するステップ、

前記第1の誘電体層上にエッチストップ層を形成するステップ、

前記第1の誘電体層および前記エッチストップ層を貫通する開口を形成するステップ、

前記トランジスタのソース/ドレイン(S/D)領域を露出させるステップ、

前記開口内に、前記エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、前記トランジスタの前記ソース/ドレイン領域に接触するステップ、および

前記金属層と接合したダマシン構造を形成するステップを含む方法。

【請求項2】

前記エッチストップ層は、約550Å以上の厚さに堆積され、かつ前記開口内に前記金属層を形成するステップは、

前記開口内に、かつ前記エッチストップ層上に金属材料を形成するステップ、および

前記エッチストップ層上の前記金属材料の一部および前記エッチストップ層の一部を除去し、前記金属層を得るステップを含み、

前記除去は、前記エッチストップ層に対する前記金属材料の約5以上のエッチング選択比を有し、前記エッチストップ層は、約150Å以上の残っている厚さを有する請求項1記載の方法。

【請求項3】

前記エッチストップ層上に第2の誘電体層を形成するステップ、および

前記第2の誘電体層を貫通して前記開口を形成するステップを更に含む請求項1記載の方法。

【請求項4】

前記エッチストップ層は、約250Å以上の厚さに堆積され、かつ前記開口内に前記金属層を形成するステップは、

前記開口内に、かつ前記第2の誘電体層上に金属材料を形成するステップ、および

前記第2の誘電体層上の前記金属材料の一部および前記第2の誘電体層の少なくとも一部を除去し、前記金属層を得るステップを含み、

前記除去は、前記エッチストップ層に対する前記金属材料の約5以上のエッチング選択比を有する請求項3記載の方法。

【請求項5】

前記エッチストップ層は、第2の上面を更に有し、前記第1の上面は、前記第2の上面と同じ高さでなく、かつ前記金属層は、前記第1の上面および前記第2の上面の界面に形成され、前記ダマシン構造を形成するステップは、

前記エッチストップ層上の第3の誘電体層にダマシン開口を形成し、さらに前記エッチストップ層を用いて前記第3の誘電体層を保護するステップ、および

前記ダマシン開口に前記ダマシン構造を形成するステップを含む請求項1記載の方法。

【請求項6】

集積回路を製造する方法であって、前記方法は、

トランジスタのゲート電極上に第1の誘電体層を形成するステップ、

前記第1の誘電体層上にエッチストップ層を形成するステップ、

前記エッチストップ層上に第2の誘電体層を形成するステップ、

前記第2の誘電体層、前記エッチストップ層、および前記第1の誘電体層を貫通する開口を形成し、前記トランジスタのソース/ドレイン(S/D)領域を露出するステップ、

前記開口内に、かつ前記第2の誘電体層上に金属材料を形成するステップ、

前記第2の誘電体上の前記金属材料の一部および前記第2の誘電体層の少なくとも一部を除去し、前記開口内の金属層を得るステップ、および

前記金属層と接合したダマシン構造を形成するステップを含む方法。

【請求項7】

前記金属層は、前記トランジスタの前記ソース/ドレイン領域に接合され、前記金属層は、前記エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである、少なくとも1つの表面を有し、かつ

前記エッチストップ層は、約250Å以上の厚さに堆積され、前記除去は、前記エッチストップ層に対する前記金属材料の約5以上のエッチング選択比を有し、かつ

前記ダマシン構造を形成するステップは、

前記エッチストップ層上の第3の誘電体層にダマシン開口を形成し、さらに前記エッチストップ層を用いて前記第3の誘電体層を保護するステップ、および

前記ダマシン開口に前記ダマシン構造を形成するステップを含む請求項6記載の方法。

【請求項8】

集積回路であって、

トランジスタのゲート電極上に堆積された誘電体層、

前記誘電体層上に堆積されたエッチストップ層、

前記誘電体層および前記エッチストップ層を貫通して延伸し、かつ前記トランジスタのソース/ドレイン(S/D)領域に接触し、前記エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである少なくとも1つの表面を有する金属層、および

前記金属層と接合したダマシン構造を含む集積回路。

【請求項9】

前記エッチストップ層は、第2の上面を更に有し、前記第1の上面は、前記第2の上面と同じ高さでなく、かつ前記金属層は、前記第1の表面および前記第2の表面の界面に形成される請求項8記載の集積回路。

【請求項10】

前記ゲート電極のエッジは、前記ダマシン構造のエッジと実質的に同じレベルであり、かつ

前記ゲート電極の真上の前記誘電体層の厚さは、前記ゲート電極のない領域の前記誘電体層の厚さと実質的に等しい請求項8記載の集積回路。

【請求項1】

集積回路を製造する方法であって、前記方法は、

トランジスタのゲート電極上に第1の誘電体層を形成するステップ、

前記第1の誘電体層上にエッチストップ層を形成するステップ、

前記第1の誘電体層および前記エッチストップ層を貫通する開口を形成するステップ、

前記トランジスタのソース/ドレイン(S/D)領域を露出させるステップ、

前記開口内に、前記エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、前記トランジスタの前記ソース/ドレイン領域に接触するステップ、および

前記金属層と接合したダマシン構造を形成するステップを含む方法。

【請求項2】

前記エッチストップ層は、約550Å以上の厚さに堆積され、かつ前記開口内に前記金属層を形成するステップは、

前記開口内に、かつ前記エッチストップ層上に金属材料を形成するステップ、および

前記エッチストップ層上の前記金属材料の一部および前記エッチストップ層の一部を除去し、前記金属層を得るステップを含み、

前記除去は、前記エッチストップ層に対する前記金属材料の約5以上のエッチング選択比を有し、前記エッチストップ層は、約150Å以上の残っている厚さを有する請求項1記載の方法。

【請求項3】

前記エッチストップ層上に第2の誘電体層を形成するステップ、および

前記第2の誘電体層を貫通して前記開口を形成するステップを更に含む請求項1記載の方法。

【請求項4】

前記エッチストップ層は、約250Å以上の厚さに堆積され、かつ前記開口内に前記金属層を形成するステップは、

前記開口内に、かつ前記第2の誘電体層上に金属材料を形成するステップ、および

前記第2の誘電体層上の前記金属材料の一部および前記第2の誘電体層の少なくとも一部を除去し、前記金属層を得るステップを含み、

前記除去は、前記エッチストップ層に対する前記金属材料の約5以上のエッチング選択比を有する請求項3記載の方法。

【請求項5】

前記エッチストップ層は、第2の上面を更に有し、前記第1の上面は、前記第2の上面と同じ高さでなく、かつ前記金属層は、前記第1の上面および前記第2の上面の界面に形成され、前記ダマシン構造を形成するステップは、

前記エッチストップ層上の第3の誘電体層にダマシン開口を形成し、さらに前記エッチストップ層を用いて前記第3の誘電体層を保護するステップ、および

前記ダマシン開口に前記ダマシン構造を形成するステップを含む請求項1記載の方法。

【請求項6】

集積回路を製造する方法であって、前記方法は、

トランジスタのゲート電極上に第1の誘電体層を形成するステップ、

前記第1の誘電体層上にエッチストップ層を形成するステップ、

前記エッチストップ層上に第2の誘電体層を形成するステップ、

前記第2の誘電体層、前記エッチストップ層、および前記第1の誘電体層を貫通する開口を形成し、前記トランジスタのソース/ドレイン(S/D)領域を露出するステップ、

前記開口内に、かつ前記第2の誘電体層上に金属材料を形成するステップ、

前記第2の誘電体上の前記金属材料の一部および前記第2の誘電体層の少なくとも一部を除去し、前記開口内の金属層を得るステップ、および

前記金属層と接合したダマシン構造を形成するステップを含む方法。

【請求項7】

前記金属層は、前記トランジスタの前記ソース/ドレイン領域に接合され、前記金属層は、前記エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである、少なくとも1つの表面を有し、かつ

前記エッチストップ層は、約250Å以上の厚さに堆積され、前記除去は、前記エッチストップ層に対する前記金属材料の約5以上のエッチング選択比を有し、かつ

前記ダマシン構造を形成するステップは、

前記エッチストップ層上の第3の誘電体層にダマシン開口を形成し、さらに前記エッチストップ層を用いて前記第3の誘電体層を保護するステップ、および

前記ダマシン開口に前記ダマシン構造を形成するステップを含む請求項6記載の方法。

【請求項8】

集積回路であって、

トランジスタのゲート電極上に堆積された誘電体層、

前記誘電体層上に堆積されたエッチストップ層、

前記誘電体層および前記エッチストップ層を貫通して延伸し、かつ前記トランジスタのソース/ドレイン(S/D)領域に接触し、前記エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである少なくとも1つの表面を有する金属層、および

前記金属層と接合したダマシン構造を含む集積回路。

【請求項9】

前記エッチストップ層は、第2の上面を更に有し、前記第1の上面は、前記第2の上面と同じ高さでなく、かつ前記金属層は、前記第1の表面および前記第2の表面の界面に形成される請求項8記載の集積回路。

【請求項10】

前記ゲート電極のエッジは、前記ダマシン構造のエッジと実質的に同じレベルであり、かつ

前記ゲート電極の真上の前記誘電体層の厚さは、前記ゲート電極のない領域の前記誘電体層の厚さと実質的に等しい請求項8記載の集積回路。

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図2】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図2】

【公開番号】特開2011−101020(P2011−101020A)

【公開日】平成23年5月19日(2011.5.19)

【国際特許分類】

【外国語出願】

【出願番号】特願2010−250254(P2010−250254)

【出願日】平成22年11月8日(2010.11.8)

【出願人】(500262038)台湾積體電路製造股▲ふん▼有限公司 (198)

【氏名又は名称原語表記】Taiwan Semiconductor Manufacturing Company,Ltd.

【住所又は居所原語表記】8,Li−Hsin Rd.6,Hsinchu Science Park,Hsinchu,Taiwan 300−77,R.O.C.

【Fターム(参考)】

【公開日】平成23年5月19日(2011.5.19)

【国際特許分類】

【出願番号】特願2010−250254(P2010−250254)

【出願日】平成22年11月8日(2010.11.8)

【出願人】(500262038)台湾積體電路製造股▲ふん▼有限公司 (198)

【氏名又は名称原語表記】Taiwan Semiconductor Manufacturing Company,Ltd.

【住所又は居所原語表記】8,Li−Hsin Rd.6,Hsinchu Science Park,Hsinchu,Taiwan 300−77,R.O.C.

【Fターム(参考)】

[ Back to top ]