集積回路及び無線ICタグ

【課題】後付けでデータを書き込むことが可能な集積回路及び無線ICタグを提供する。

【解決手段】データを記憶するメモリ72と、外部装置から受信した電磁波に基づく交流信号を整流して直流電圧を生成するとともに動作電圧を生成する整流回路61と、メモリ72に記憶されているデータを読み出すロジック回路66と、ロジック回路66が読み出したデータによって反射波を変調する変調回路62と、アンテナ回路51,52が接続される端子と、照射される光信号に応じた電気信号をロジック回路に入力するフォトトランジスタ74と、前記電気信号に含まれているデータが書き込まれるヒューズROM73と、を有する集積回路2及びこれを用いた無線ICタグ1を提供する。

【解決手段】データを記憶するメモリ72と、外部装置から受信した電磁波に基づく交流信号を整流して直流電圧を生成するとともに動作電圧を生成する整流回路61と、メモリ72に記憶されているデータを読み出すロジック回路66と、ロジック回路66が読み出したデータによって反射波を変調する変調回路62と、アンテナ回路51,52が接続される端子と、照射される光信号に応じた電気信号をロジック回路に入力するフォトトランジスタ74と、前記電気信号に含まれているデータが書き込まれるヒューズROM73と、を有する集積回路2及びこれを用いた無線ICタグ1を提供する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、集積回路及び無線ICタグに関し、とくに後付けでデータの書き込みが可能な無線ICタグを提供する技術に関する。

【背景技術】

【0002】

RFIDに用いられるシート型やカード型の無線ICタグが知られている。無線ICタグは、リーダ装置等の外部装置等から送信されてくる電磁波をアンテナ回路で受信し、アンテナ回路から出力される交流電流を整流して直流電圧を生成し、この直流電圧を利用して回路を動作させることにより非接触かつ無電源で動作する。無線ICタグは、上記電磁波に対する反射波を変調することにより、メモリに格納されているデータを外部装置に応答する。

【特許文献1】特開2000−105809号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

現在流通している無線ICタグに搭載されているメモリにはROM(Read Only Memory)が用いられており、従ってメモリには出荷時等においてのみデータを書き込むことが可能である。このため、ユーザは、無線ICタグの製造発注時にメーカ等の無線ICタグの生産者に対してROMに書き込んでおきたい内容をあらかじめ伝えておく必要があった。また、例えば機密情報や流動性のあるデータ等、データを後付で書き込みたいというニーズがあるが、現行の無線ICタグはそのようなニーズに応えることができない。

【0004】

本発明はこのような事情に鑑みてなされたもので、後付けでデータを書き込むことが可能な集積回路及び無線ICタグを提供することを目的とする。

【課題を解決するための手段】

【0005】

上記目的を達成するための本発明のうちの主たる発明は、リーダ装置等の外部装置から送信される質問電波を受信して、前記質問電波の反射波を応答電波として送信する無線ICタグに用いられる集積回路であって、データを記憶するメモリと、前記外部装置から受信した電磁波に基づく交流電流を整流して直流電圧を生成するとともに、当該集積回路を動作させるための電圧を生成する整流回路と、前記メモリに記憶されているデータを読み出すロジック回路と、前記ロジック回路が読み出したデータによって前記反射波を変調する変調回路と、アンテナ回路が接続される端子と、照射される光信号に応じた電気信号を前記ロジック回路に入力するフォトトランジスタと、前記電気信号に含まれているデータが書き込まれるヒューズROMと、を有することとする。

【0006】

本発明の集積回路はこのようにフォトトランジスタとフォトトランジスタによって光電変換された電気信号に含まれるデータが書き込まれるヒューズROMとを有しており、フォトトランジスタに光信号を照射することによって、ヒューズROMにデータを書き込むことが可能である。このため、例えば機密情報や流動性のあるデータ等を後付で書き込みたいというニーズに応えることができる。

【0007】

またフォトトランジスタは無電源で動作する素子であるので、ヒューズROMへのデータの書き込みを整流回路によって生成される電圧を昇圧した電圧を用いて行うことができる。すなわち、フォトトランジスタとヒューズROMというシンプルで消費電力の少ない素子を既存の無線ICタグに付加するだけで、後付でのデータ書き込みが可能な無線ICタグを提供することができる。

【発明の効果】

【0008】

本発明によれば、後付けでデータを書き込むことができる無線ICタグを提供することができる。

【発明を実施するための最良の形態】

【0009】

以下、本発明の一実施形態につき詳細に説明する。図1は本発明の一実施形態にかかるRFID(Radio Frequency Identification)に用いられるシート型(カード型)の無線ICタグ1(RFIDタグ)の平面図であり、図2は無線ICタグ1の断面図である。本実施形態の無線ICタグ1は、素子や回路が設けられた平面矩形状の集積回路2、及び集積回路2の上面にエポキシ樹脂等からなる接着層3を介して接合される、集積回路2と同形同大のアンテナシート4からなる本体部分と、本体部分の両面を被覆する透明樹脂製のフィルム層5,6とを含んで構成されている。

【0010】

図3はアンテナシート4単体の平面図である。アンテナシート4は、PEN(ポリエチレンナフタレート)やPET(ポリエチレンテレフタレート)等の絶縁性フィルム41に、インダクタとして機能する銅(Cu)やアルミニウム(Al)等の導電材からなる配線パターン42が形成された構造からなる。配線パターン42は、絶縁性フィルム41の角隅部Aの近傍を起点とし、絶縁性フィルム41の4辺近傍に沿って一筆書きの形で渦巻状に所定回数周回させ、角隅Aに隣接する角隅Bの近傍が終点となるように形成されている。上記起点部分には、集積回路2に設けられた、断面矩形の柱状パッド(以下、「起点パッド21」と称する)の接合部分となる矩形の起点端子44が形成されている。一方、上記終点部分には、集積回路2に設けられた銅(Cu)やアルミニウム(Al)等からなる断面矩形の柱状パッド(以下、「終点パッド22」と称する)の接合部分となる矩形の終点端子45が形成されている。

【0011】

終点パッド22の近傍を通る配線パターン42部分は、終点パッド22(終点端子45)からみて絶縁性フィルム41の縁側を通ように形成されている。このように、配線パターン42が、終点パッド22(終点端子45)からみて絶縁性フィルム41の縁側を通るように形成されていることで、電流ロスやノイズ混入を生じさせる要因となりやすいクランク形状の配線パターン部分を減らすことができる。

【0012】

配線パターン42は、集積回路2に設けられる容量素子512と並列接続されて無線ICタグ1の内部アンテナ回路51を構成する。なお、容量素子512としては、実用上充分な耐圧を有する素子(例えばMIM(Metal Insulator Metal)キャパシタ)を用いることが好ましい。

【0013】

集積回路2は、内部アンテナ回路51に代えて外部アンテナ回路52を接続して用いることができる。外部アンテナ回路52は、インダクタと容量素子とを並列接続した回路を含む共振回路であって、内部アンテナ回路51とは共振周波数が異なる。すなわち、本実施形態の集積回路2は、内部アンテナ回路51に代えて外部アンテナ回路52を接続することで、RFIDの異なる周波数帯の無線ICタグとして汎用的に用いることができる。

【0014】

外部アンテナ回路52は、内部アンテナ回路51が接続される、上述した2つの端子(起点端子44と終点端子45)に接続される。すなわち、起点端子44と終点端子45は、内部アンテナ回路51を接続する端子として機能するとともに、外部アンテナ回路52を接続するための端子としても機能する。このように端子が共通化されることによって、端子の数を最小限に抑えることができ、小型の集積回路2を提供することが可能となる。

【0015】

内部アンテナ回路51や外部アンテナ回路52を構成するための容量素子は、無線ICタグ1に用いられる周波数帯によっては(例えば、2.45GHz帯)、これを起点パッド21と終点パッド22との間に存在する寄生容量で代用することができる。容量素子を寄生容量で代用した場合には、容量素子の構成を設ける必要が無い分、アンテナ回路や集積回路2を小型化することができる。寄生容量の大きさは、例えば、起点パッド21と終点パッド22との間の距離や起点パッド21と終点パッド22の面積を変えることによって調節することができる。

【0016】

図4に起点パッド21及び終点パッド22周辺の素子や配線パターンの構造を示している。終点パッド22の直近には、当該終点パッド22に隣接させて、後述する整流回路61の構成要素であるダイオード55が配置されている。このように、整流回路61を構成しているダイオード55を終点パッド22の直近に隣接させて配置することで、アンテナ回路(内部アンテナ回路51や外部アンテナ回路52)から出力される交流信号を効率よく整流回路61に取り込むことができる。またとくにアンテナ回路が受信する周波数が高周波である場合には、配線部分からの電流ロスを効果的に防ぐことができる。またこのようにダイオード55を終点パッド22の直近に隣接させて配置することで、アンテナ回路から出力される交流信号は直ちに直流電圧に変換される。このため、集積回路2上で交流信号が流れる部分が集積回路2上の一部の領域に局在化されて、集積回路2上の素子や回路には殆ど交流信号が流れなくなる。そしてその結果、交流信号が流れることに起因して生じる素子や回路におけるノイズを低減させることができる。

【0017】

一方、ダイオード55を構成している回路パターンがボトルネックとなって集積回路2に設けられている素子や回路が必要とする電流が供給不足になることがないように、ダイオード55を構成している上記回路パターンの線幅は、素子や回路において必要とされる電流を流すことが可能な幅(例えば35μm程度)に設定されている。

【0018】

図5はアンテナシート4の製造方法を説明するプロセスフローである。アンテナシート4の製造に際しては、まず樹脂製の絶縁フィルムの表面に、銅(Cu)やアルミニウム(Al)等からなる導電材を塗布してなるシート材の、導電材が塗布されている側の面(以下、「表面」と称する)に、フォトレジストを塗布する(S511)。次にフォトレジストに配線パターンに対応するパターンのフォトマスクを施した後、露光・現像を行って、レジストパターンを形成する(S512)。次にシート材をエッチング液に浸してエッチングを行うことにより、フォトマスクが施されている部分以外の部分の導電材を溶解除去する(S513)。その後は除去されずに残っているレジストパターンを除去し、導電材を露出させる(S514)。以上のプロセスを経ることによりアンテナシート4を得ることができる。

【0019】

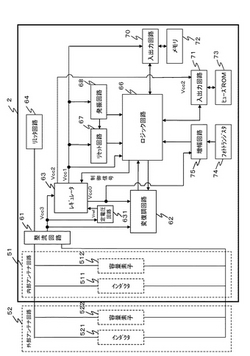

図6は集積回路2の機能を説明するブロック図である。なお、集積回路2は、シリコンウェハをベースとし、これに洗浄プロセス、スパッタやCVD、熱酸化等の製膜プロセス、リソグラフィ、不純物拡散プロセス、ボンディング、モールド、多層配線プロセス等のプロセスを施すといった、通常の半導体プロセスによって製造されたものである。集積回路2に設けられている素子や回路は、リーダ装置等の外部装置から送信されてくる電磁波(質問電波)の電力によって駆動される。アンテナ回路が電磁波(質問電波)を受信することによって生成された交流信号は、整流回路61に入力され、ここで直流電圧に変換される。整流回路61から出力される直流電圧は、変復調回路62及びレギュレータ63(レギュレータ)に電圧(Vcc3)として供給される。リミッタ回路64は、整流回路61から出力される電圧(Vcc3)が過大とならないよう上限規制するように作用する。

【0020】

変復調回路62は、整流回路61から供給される直流電圧(直流信号)を復調する。変復調回路62によって生成された復調信号は、ロジック回路66に入力される。なお、本実施形態の無線ICタグ1は、このように復調機能と変調機能の双方を備えた構成であるが、本発明は復調機能を有さずに変調回路のみを有する無線ICタグにも適用することができる。

【0021】

レギュレータ63は、整流回路61から供給される電圧(Vcc3)に基づいて、電圧(Vcc0)及び電圧(Vcc1)、及び電圧(Vcc2)を生成する。このうち電圧(Vcc0)は、変復調回路62及び増幅回路75の駆動電圧となる。電圧(Vcc1)は、リセット回路67、及び発振回路68の駆動電圧となる。また電圧(Vcc2)は、入出力回路71の駆動電圧となる。

【0022】

定電圧回路631は、電圧(Vcc3)に基づいて、レギュレータ63に定電圧(例えば1.2V)を供給する。

【0023】

リセット回路67は、レギュレータ63から出力される電圧(Vcc1)が所定の閾値以上になるとロジック回路66に入力していたリセット信号を解除するように動作する。リセット信号が解除されるとロジック回路66が初期化状態から動作状態となる。発振回路68は、例えばRC発振回路である。発振回路68は、ロジック回路66及びリセット回路67を動作させるのに必要となる100kHz〜200kHzのクロック信号を生成する。

【0024】

ここで従来の無線ICタグの製造に用いる集積回路2にあっては、アンテナ回路が受信する電磁波(質問電波)の周波数を分周することによりクロック信号を生成していたため、アンテナ回路が受信する電磁波(質問電波)の周波数が変わればクロック信号の周波数も変わってしまい、アンテナ回路のみを交換しただけでは集積回路2を異なる周波数帯の無線ICタグ用として用いることができなかった。これに対し本実施形態の集積回路2は発振回路68を内蔵するため、クロック信号の周波数はアンテナ回路が受信する電磁波(質問電波)の周波数とは無関係となり、共振周波数を有するアンテナ回路を選択することにより様々な周波数帯の無線ICタグに汎用的に用いることができる。つまり本実施形態の集積回路2によれば、RFIDに許可されている各周波数帯に対応する無線ICタグ1の製造工程を単純化することができ、製造コストも抑えることができる。

【0025】

変復調回路62から復調信号が入力されると、ロジック回路66は入出力回路70及び入出力回路71を制御して、メモリ72に記憶されているデータの読み出しと、ヒューズROM73(Fuse ROM、Fuse Prom)へのデータの書き込み、及びヒューズROM73からのデータの読み出しを行う。ここでメモリ72はEEPROM(Electrically Erasable Programmable Read Only Memory)やFRAM(Ferromagnetic Random Access Memory)等であり、例えば固定的なデータを書き込んでおく用途に利用される。一方、ヒューズROM73は、内部に設けられているヒューズ素子を電流によって焼き切ることにより、ライトアットワンス方式でデータを記憶するメモリである。ヒューズROM73には、例えば機密情報や流動性のあるデータ等、メモリ72に書き込まれるデータに比べて流動性の高いデータが書き込まれる。これらは例えば、会社名等のデータを無線ICタグ1の出荷時等においてメモリ72に書き込んでおき、無線ICタグ1を購入した後にユーザによって社員番号や氏名等のデータをヒューズROM73に書き込むといった使い分がなされる。

【0026】

このように、本実施形態の無線ICタグ1は、メモリ72に記憶される固定情報に加えてユーザが後付けでデータを書き込むことができるため、全てのデータを出荷時に書き込んでおく必要があった従来型の無線ICタグに比べ、多様なユーザニーズに柔軟に対応することができる。

【0027】

ロジック回路66は、メモリ72及びヒューズROM73から読み出したデータ(以下、「読み出しデータ」と称する)を変復調回路62に出力する。変復調回路62は、ロジック回路66から入力される読み出しデータに応じて、アンテナ回路側(リーダ装置等の外部装置側)からみた集積回路2のインピーダンスを変化させる。変復調回路62は、アンテナ回路に結合する抵抗が直列接続されたスイッチングトランジスタを含んで構成されており、読み出しデータに応じて上記スイッチングトランジスタをオンオフし、アンテナ回路側からみた半導体回路2のインピーダンスを変化させる。リーダ装置等の外部装置は、このインピーダンスの変化によって変調されて戻ってくる反射波(応答電波)を受信して復調することにより、無線ICタグ1のメモリ72に格納されているデータを読み取る。

【0028】

図6に示すフォトトランジスタ74は、ヒューズROM73にデータの書き込む際に用いられる。入射される光信号に応じてフォトトランジスタ74から出力される電気信号は、増幅回路75によって増幅されてロジック回路66に入力される。

【0029】

図7はリーダ装置等の外部装置から、メモリ72やヒューズROM73に記憶されているデータを読み出すための電磁波(質問電波)がアンテナ回路51,52に入力された場合における、無線ICタグ1の動作を説明するタイミングチャートである。同図において、「交流信号」は、電磁波(質問電波)が入力されることによりアンテナ回路51又はアンテナ回路52の出力電圧(以下、「入力電圧」と称する)である。「Vcc3」は整流回路61の出力電圧である。「Vcc0」、「Vcc1」、及び「Vcc2」は、レギュレータ63から出力される電圧の値である。「Reset」は、リセット回路67から出力されるリセット信号の波形である。「OSC」は、発振回路68から出力されるクロック信号の波形である。「メモリ」は、メモリ72又はヒューズROM73からのデータ読み出し中であるかどうかを示す信号(読み出しビジー(Busy)信号)の波形である。「変復調回路入力」は、ロジック回路66によって読み出されて変復調回路62に入力される読み出しデータの波形である。

【0030】

図7とともに無線ICタグ1の動作について説明する。電磁波(質問電波)を送信するリーダ装置等の外部装置が無線ICタグ1に近づいてくると、アンテナ回路から整流回路61に供給される交流信号の振幅は次第に増大する(T1)。ここで電圧(Vcc0)、電圧(Vcc1)、電圧(Vcc2)、及び電圧(Vcc3)は、いずれも入力電圧の振幅の増大に伴って増大する(T1〜T3)。これらの電圧は、交流電圧の振幅が閾値を超えた後はリミッタ回路65の作用によって一定に(Vcc0=3.3V、Vcc1=3.3V、Vcc2=3.3V、Vcc3=14.4V)保たれる。

【0031】

次に、電圧(Vcc1)が所定の動作電圧(例えば2.0V)以上になると、発振回路68が動作を開始し、これにより発振回路68からロジック回路66及びリセット回路67にクロック信号の入力が開始される(T2)。電圧(Vcc1)が所定の閾値(例えば3.0V)以上になると、ロジック回路66に入力されていたリセット回路67が解除され、ロジック回路66はメモリ(及び/又は)ヒューズROMに記憶されているデータの読み出しを開始する(T4)。そしてロジック回路66によって読み出されたデータが変復調回路62に入力される(T5)。変復調回路62は、ロジック回路66から入力される読み出しデータの波形に応じてスイッチングトランジスタをオンオフ制御し、アンテナ回路側(外部装置側)から見た集積回路2のインピーダンスを変化させる。以上のようにして無線ICタグ1からのデータの読み出しが行われる。

【0032】

ここでヒューズROM73へのデータの書き込み原理を図8Aとともに説明する。図8Aには2ビット分に相当するヒューズ素子を示している。このうちヒューズ素子H1には、第1のトランジスタTr1(N型MOSFET)が直列接続されている。一方、ヒューズ素子H2には第2のトランジスタTr2(N型MOSFET)が直列接続されている。第3のトランジスタTr3(P型MOSFET)及び第4のトランジスタTr4(N型MOSFET)は、レギュレータ63から供給される電圧(Vcc2)のヒューズ素子H1及びヒューズ素子H2への印加をオンオフ制御するための素子である。

【0033】

ヒューズROM73へのデータの書き込みは、ヒューズ素子H1やヒューズ素子H2を焼き切る(ショートさせる)ことにより行われる。すなわち、ヒューズROM73にデータを書き込む場合には、第3のトランジスタTr3及び第4のトランジスタTr4の夫々のゲート電極に「Low」レベルの制御電圧Aを印加して、第3のトランジスタTr3をオン、第4のトランジスタTr4をオフしてヒューズ素子H1及びヒューズ素子H2に電圧(Vcc2)を印加し、制御電圧B及び制御電圧Cを制御して、第1のトランジスタTr1又は第2トランジスタTr2をオンにする。これによりヒューズ素子H1、又はヒューズ素子H2のいずれかに電圧(Vcc2)が印加されて電圧(Vcc2)が印加されたヒューズ素子に電流が流れ込み、そのヒューズ素子がショートする。このようにしてヒューズROM73へのデータの書き込みが行われる。

【0034】

ヒューズROM73にデータを書き込む際には、入出力回路71にヒューズROM73からデータを読み出すときよりも高い電圧を印加する必要がある。図8B及び図8Cは、レギュレータ63に内蔵される回路であり、フォトトランジスタ74から上記電気信号が入力された場合に、ロジック回路66から送られてくる制御信号であるVcc2コントロールに応じて、入出力回路71に供給する電圧(Vcc2)を切り換える回路である。

【0035】

まず図8Bに示す回路であるが、この回路は、第1乃至第3の増幅器OP1,OP2,OP3と4つの抵抗素子R1,R2,R3,R4とを含んで構成されている。第1の増幅器OP1の反転入力(−)には定電圧回路631から出力される定電圧(Vref=1.2V)が入力される。第1の増幅器OP1の非反転入力(+)には第1の増幅器OP1の出力電圧が抵抗素子R1を介して帰還される。第1の増幅器OP1の出力端子は、直列接続された抵抗素子R1及びR2を介して接地されている。また抵抗素子R1,R2の抵抗値は第1の増幅器OP1の出力電圧が3.3Vになるように設定されている。一方、第2の増幅器OP2の反転入力(−)には第1の増幅器OP1の出力電圧が入力される。第2の増幅器OP2の非反転入力(+)には、第3の増幅器OP3の出力電圧が帰還される。第2の増幅器OP2の出力は、レギュレータ63の出力電圧(Vcc2)となる。

【0036】

第3の増幅器OP3の反転入力(−)には第1の増幅器OP1の出力電圧が入力される。第3の増幅器OP3の非反転入力(+)には第3の増幅器OP3の出力電圧が抵抗素子R3を介して帰還される。第3の増幅器OP3の出力端子は直列接続された抵抗素子R3及びR4を介して接地されている。抵抗素子R3,R4の抵抗値は第3の増幅器OP3の出力電圧が12.0Vになるように設定されている。

【0037】

図8Bにおいて、第1の増幅器OP1と2つの抵抗素子R1,R2とを含んで構成される回路(以下、演算増幅回路811という)は、第2及び第3の増幅器OP2,OP3に対して3.3Vのリファレンス電圧を印加している。また演算増幅回路811は、定電圧回路631から供給される定電圧(Vref=1.2V)を3.3Vのリファレンス電圧に変換し、これを第2及び第3の増幅器OP2,OP3の反転入力(−)に供給している。

【0038】

第2及び第3の増幅器OP2,OP3は、いずれもバイアス入力端子BIAS1,BIAS2を有しており、これらは夫々バイアス入力端子BIAS1,BIAS2に外部供給されるバイアス電圧によって動作状態が制御される。図8Bにおける第2及び第3の増幅器OP2,OP3と抵抗素子R3,R4とを含んで構成される回路(以下、電圧切換回路812という)は、ロジック回路66から送られてくるVcc2コントロールに応じて2種類の電圧(Vcc2=3.3V又は12.0V)を生成している。

【0039】

図8Cはロジック回路66から送られてくるVcc2コントロールに応じて、第2及び第3の増幅器OP2,OP3のバイアス入力端子BIAS1,BIAS2に入力するバイアス電圧を生成するための回路である。この回路は第5乃至第9のトランジスタTr5,Tr6,Tr7,Tr8,TR9を含んで構成されている。トランジスタTr5,Tr6,Tr7,Tr8,TR9はいずれもMOSFET(電界効果MOSトランジスタ)であり、第5及び第6のトランジスタはP型MOSFET、第7乃至第9のトランジスタはN型MOSFETである。

【0040】

第5及び第6のトランジスタTr5,Tr6のソースには、電圧(Vcc3)が供給されている。第5のトランジスタTr5のゲートは、第2の増幅器OP2のバイアス入力端子BIAS1に接続されている。第5のトランジスタTr5のゲート及びドレインは短絡されている。第6のトランジスタTr6のゲートは、第3の増幅器OP3のバイアス入力端子BIAS2に接続されている。第6のトランジスタTr6のゲート及びドレインは短絡されている。第5のトランジスタTr5のドレインは、第7のトランジスタTr7のドレインに接続されている。第6のトランジスタTr6のドレインは、第8のトランジスタTr8のドレインに接続されている。

【0041】

第7のトランジスタTr7のゲートには、定電圧回路631から供給される定電圧(例えば1.2V)が印加される。第7のトランジスタTr7のソースは第9のトランジスタTr5のドレインに接続されている。第8のトランジスタTr8のソースは、第9のトランジスタTr9のドレインに接続している。

【0042】

第8のトランジスタTr8のゲートには、ロジック回路66から送られてくるVcc2コントロールが入力される。なお、ロジック回路66から送られてくるVcc2コントロールは、入出力回路71がヒューズROM73からの読み出しを行う場合は定電圧回路631から供給される定電圧(Vref=1.2V)に対して「Low」となり、ヒューズROM73への書き込みを行う場合は「High」となる信号である。第9のトランジスタTr9のゲートには、定電圧回路631から供給される所定のバイアス電圧が印加される。また第9のトランジスタTr9のソースは接地されている。

【0043】

図9にヒューズROM73へのデータの書き込み動作を説明するタイミングチャートを示している。図9において、「Vcc1」及び「Vcc2」は、レギュレータ63から出力される電圧の値である。「Vcc2コントロール」は、ロジック回路66からレギュレータ63に送られてくるVcc2コントロールである。「光信号」は、フォトトランジスタ74に照射される光信号の波形である。「ヒューズROM」は、ヒューズROM73へのデータの書き込み中であることを示す信号(書き込みビジー(Busy)信号)の波形である。

【0044】

図9に示すヒューズROM73へのデータの書き込み処理は、電磁波をアンテナ回路に入力することにより図7のタイミングチャートに従ってロジック回路66を動作させた後、ヒューズROM73へのデータの書き込みを開始するためのコマンド(以下、「書き込み開始コマンド」と称する)を含んだ光信号をフォトトランジスタ74に照射することにより開始される。

【0045】

まずフォトトランジスタ74から当該フォトトランジスタ74に照射される光信号に応じた電気信号が出力される。増幅回路75は、フォトトランジスタ74から出力される上記電気信号を増幅してロジック回路66に出力する(T6〜T7)。なお、ヒューズROM73へのデータの書き込みは、必要な電力を有する電磁波をアンテナ回路に供給しつつ行われる。

【0046】

フォトトランジスタ74から上記電気信号が入力されると、ロジック回路66はレギュレータ63に供給しているVcc2コントロールを、「Low」から「High」に切り換える(T8)。

【0047】

ここでレギュレータ63において、ロジック回路66から送られてくるVcc2コントロールは図8Cに示す回路の第8のトランジスタTr8のゲートに入力され、Vcc2コントロールが「Low」から「High」になることにより、第8のトランジスタTr8がオンとなる。このため、第5のトランジスタTr5と第7のトランジスタTr7とによって構成される経路を通じての第9のトランジスタTr9への電流供給が停止して、第9のトランジスタTr9への電流供給はもっぱら第6のトランジスタTr6と第8のトランジスタTr8とによって構成される経路を通じてのみ行われることになる。これにより第6のトランジスタTr6のソースとゲートとの間に電位差が生じる。一方、第5のトランジスタTr5のソースとゲートとの間には電位差は生じない。

【0048】

ここで第6のトランジスタTr6のソースとゲートの間に生じた電位差は、第6のトランジスタTr6のゲートを通じて図8Bの電圧切換回路812を構成している第3の増幅器OP3のバイアス入力端子BIAS2に供給される。これにより第3の増幅器OP3が動作する。一方、図8Cの第5のトランジスタTr5のソースとゲートの間には電位差が生じないため、第2の増幅器OP2のバイアス入力端子BIAS1にはバイアス電圧が供給されず、第2の増幅器OP2は動作を停止する。以上のようにして、結局、第3の増幅器OP3のみがオンすることになり、電圧切換回路812を構成している抵抗素子R3,R4によって定まる第3の増幅器OP3の出力電圧である12.0Vが、電圧(Vcc2)としてレギュレータ63から出力される。

【0049】

なお、メモリ72又はヒューズROM73からのデータの読み出し時においては、ロジック回路66からレギュレータ63にはVcc2コントロールとして「Low」が送られてくる。このため、図8Cに示す回路における第8のトランジスタTr8のゲート電圧は「Low」となり、これにより第8のトランジスタTr8は動作を停止する。従って、第6のトランジスタTr6と第8のトランジスタTr8とによって構成される経路を通じた第9のトランジスタTr9への電流供給が停止し、第9のトランジスタTr9への電流供給はもっぱら第5のトランジスタTr5と第7のトランジスタTr7とによって構成される経路を通じてのみ行われることになり、第5のトランジスタTr5のソースとゲートとの間には電位差が生じるが、第6のトランジスタTr6のソースとゲートとの間には電位差は生じない。これにより第2の増幅器OP2は動作するが、第3の増幅器OP3は動作を停止し、電圧切換回路812を構成している第2の増幅器OP2の出力電圧である3.3Vが電圧(Vcc2)としてレギュレータ63から出力されることになる。以上のようにして電圧(Vcc=12.0V)の供給が開始される(T8)。

【0050】

次に、ヒューズROM73上のデータの書き込み位置を示すアドレスデータ及び書き込みデータを含んだ光信号が、フォトトランジスタ74に照射され(T9〜T10)、この光信号に対応する電気信号がロジック回路66に入力される。ロジック回路66は、入出力回路71を制御して、入力される電気信号に含まれるアドレスデータで指定されるヒューズROM73の所定の記憶位置に、上記電気信号に含まれる書き込みデータを書き込む(T11〜T12)。

【0051】

ヒューズROM73へのデータの書き込みが完了すると、ロジック回路66は、ヒューズROM73の所定位置のビット(以下、「書き込み済フラグ」と称する)をオンにする(T13〜T14)。以上の処理が終了した後は、アンテナ回路からの電磁波の供給が停止されて書き込み処理が終了する(T15)。なお、上記ビットは、ヒューズROM73へのデータの書き込みを行ったかどうか(書き込み済であるかどうか)を判断する際にロジック回路66によって参照される。すなわち、ロジック回路66は、上記「書き込み済フラグ」がオンであればヒューズROM73には既にデータが書き込まれているものと判断し、この場合にはフォトトランジスタ74に書き込みコマンドを含んだ光信号が照射されてもヒューズROM73へのデータの書き込み動作を開始しない。

【0052】

なお、以上に説明した処理においては、フォトトランジスタ74が光信号を確実に受信することができるように、ロジック回路66のクロック信号の周波数は、フォトトランジスタ74に照射される光信号の周波数よりも高い値に設定される。またタイミングのずれやノイズの影響によって、一度の照射で光信号を読み込めない場合も起こりうるが、このような場合には、ロジック回路66が光信号による入力を受け付けるまで、フォトトランジスタ74に繰り返し光信号を入力するようにする。

【0053】

ところで、フォトトランジスタ74に照射される光信号は、増幅回路75やロジック回路66を誤動作させる要因となる。このため、フォトトランジスタ74は、増幅回路75やロジック回路66からなるべく離れた位置に設けることが好ましい。一方、増幅回路75において増幅された電気信号を効率よくロジック回路66に伝えるためには、増幅回路75はロジック回路66に隣接させて配置することが好ましい。ここでフォトトランジスタ74と増幅回路75又はロジック回路66の位置関係は、例えば図10に示す関係から求められる。すなわち、光源(光ファイバ)81からの光が直接照射される範囲は、フォトトランジスタ74と光源との間の距離Zと、光源から照射される光の広がり角θから求められる、半径x=Z・tanθの円の範囲であるので、フォトトランジスタ74、増幅回路75、及びロジック回路66は、集積回路2上の表面の領域のうち上記円の範囲外の領域に配置することが好ましいことになる。またこの場合において、増幅回路75において増幅された電気信号を効率よくロジック回路66に伝えるために、ロジック回路66と増幅回路75とは隣接するように配置することが好ましいことになる。

【0054】

ヒューズROM73へのデータの書き込みに際しては、アンテナ回路に通常の読み出しの際に比べて強い電磁波を供給しつつフォトトランジスタ74に書き込み命令を与えてから書き込みデータを入力するといった一連のプロセスを実施する必要がある。ここでこのようなプロセスの複雑さは、無線ICタグ1のセキュリティ強度の向上に貢献する。またデータの書き込みがヒューズを焼き切るという物理的な手段で行われることもセキュリティ強度の向上に貢献する。

【0055】

以上、本発明の実施形態につき詳細に説明したが、以上の実施形態の説明は本発明の理解を容易にするためのものであり、本発明を限定するものではない。本発明はその趣旨を逸脱することなく、変更、改良され得ると共に本発明にはその等価物が含まれることは勿論である。

【図面の簡単な説明】

【0056】

【図1】本発明の一実施形態として説明する無線ICタグ1の平面図である。

【図2】本発明の一実施形態として説明する無線ICタグ1の断面図である。

【図3】本発明の一実施形態として説明するアンテナシート4単体の平面図である。

【図4】本発明の一実施形態として説明する起点パッド21及び終点パッド22周辺の素子や配線パターンの構造を示す図である。

【図5】本発明の一実施形態として説明するアンテナシート4の製造方法を説明するプロセスフローである。

【図6】本発明の一実施形態として説明する集積回路2の機能を説明するブロック図である。

【図7】本発明の一実施形態として説明するデータを読み出し時の無線ICタグ1の動作を説明するタイミングチャートである。

【図8A】本発明の一実施形態として説明するヒューズROM73へのデータの書き込み原理を説明する図である。

【図8B】本発明の一実施形態として説明するVccコントロールに応じて入出力回路71に供給する電圧(Vcc2)を切り換える回路である。

【図8C】本発明の一実施形態として説明するVccコントロールに応じて入出力回路71に供給する電圧(Vcc2)を切り換える回路である。

【図9】本発明の一実施形態として説明するヒューズROM73へのデータの書き込み動作を説明するタイミングチャートである。

【図10】本発明の一実施形態として説明するフォトトランジスタ74と増幅回路75又はロジック回路66の位置関係を説明する図である。

【符号の説明】

【0057】

1 無線ICタグ

2 集積回路

21 起点パッド

22 終点パッド

51 内部アンテナ回路

52 外部アンテナ回路

55 ダイオード

61 整流回路

62 変復調回路

63 レギュレータ

65 リミッタ回路

66 ロジック回路

67 リセット回路

68 発振回路

71 入出力回路

72 メモリ

73 ヒューズROM

74 フォトトランジスタ

【技術分野】

【0001】

この発明は、集積回路及び無線ICタグに関し、とくに後付けでデータの書き込みが可能な無線ICタグを提供する技術に関する。

【背景技術】

【0002】

RFIDに用いられるシート型やカード型の無線ICタグが知られている。無線ICタグは、リーダ装置等の外部装置等から送信されてくる電磁波をアンテナ回路で受信し、アンテナ回路から出力される交流電流を整流して直流電圧を生成し、この直流電圧を利用して回路を動作させることにより非接触かつ無電源で動作する。無線ICタグは、上記電磁波に対する反射波を変調することにより、メモリに格納されているデータを外部装置に応答する。

【特許文献1】特開2000−105809号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

現在流通している無線ICタグに搭載されているメモリにはROM(Read Only Memory)が用いられており、従ってメモリには出荷時等においてのみデータを書き込むことが可能である。このため、ユーザは、無線ICタグの製造発注時にメーカ等の無線ICタグの生産者に対してROMに書き込んでおきたい内容をあらかじめ伝えておく必要があった。また、例えば機密情報や流動性のあるデータ等、データを後付で書き込みたいというニーズがあるが、現行の無線ICタグはそのようなニーズに応えることができない。

【0004】

本発明はこのような事情に鑑みてなされたもので、後付けでデータを書き込むことが可能な集積回路及び無線ICタグを提供することを目的とする。

【課題を解決するための手段】

【0005】

上記目的を達成するための本発明のうちの主たる発明は、リーダ装置等の外部装置から送信される質問電波を受信して、前記質問電波の反射波を応答電波として送信する無線ICタグに用いられる集積回路であって、データを記憶するメモリと、前記外部装置から受信した電磁波に基づく交流電流を整流して直流電圧を生成するとともに、当該集積回路を動作させるための電圧を生成する整流回路と、前記メモリに記憶されているデータを読み出すロジック回路と、前記ロジック回路が読み出したデータによって前記反射波を変調する変調回路と、アンテナ回路が接続される端子と、照射される光信号に応じた電気信号を前記ロジック回路に入力するフォトトランジスタと、前記電気信号に含まれているデータが書き込まれるヒューズROMと、を有することとする。

【0006】

本発明の集積回路はこのようにフォトトランジスタとフォトトランジスタによって光電変換された電気信号に含まれるデータが書き込まれるヒューズROMとを有しており、フォトトランジスタに光信号を照射することによって、ヒューズROMにデータを書き込むことが可能である。このため、例えば機密情報や流動性のあるデータ等を後付で書き込みたいというニーズに応えることができる。

【0007】

またフォトトランジスタは無電源で動作する素子であるので、ヒューズROMへのデータの書き込みを整流回路によって生成される電圧を昇圧した電圧を用いて行うことができる。すなわち、フォトトランジスタとヒューズROMというシンプルで消費電力の少ない素子を既存の無線ICタグに付加するだけで、後付でのデータ書き込みが可能な無線ICタグを提供することができる。

【発明の効果】

【0008】

本発明によれば、後付けでデータを書き込むことができる無線ICタグを提供することができる。

【発明を実施するための最良の形態】

【0009】

以下、本発明の一実施形態につき詳細に説明する。図1は本発明の一実施形態にかかるRFID(Radio Frequency Identification)に用いられるシート型(カード型)の無線ICタグ1(RFIDタグ)の平面図であり、図2は無線ICタグ1の断面図である。本実施形態の無線ICタグ1は、素子や回路が設けられた平面矩形状の集積回路2、及び集積回路2の上面にエポキシ樹脂等からなる接着層3を介して接合される、集積回路2と同形同大のアンテナシート4からなる本体部分と、本体部分の両面を被覆する透明樹脂製のフィルム層5,6とを含んで構成されている。

【0010】

図3はアンテナシート4単体の平面図である。アンテナシート4は、PEN(ポリエチレンナフタレート)やPET(ポリエチレンテレフタレート)等の絶縁性フィルム41に、インダクタとして機能する銅(Cu)やアルミニウム(Al)等の導電材からなる配線パターン42が形成された構造からなる。配線パターン42は、絶縁性フィルム41の角隅部Aの近傍を起点とし、絶縁性フィルム41の4辺近傍に沿って一筆書きの形で渦巻状に所定回数周回させ、角隅Aに隣接する角隅Bの近傍が終点となるように形成されている。上記起点部分には、集積回路2に設けられた、断面矩形の柱状パッド(以下、「起点パッド21」と称する)の接合部分となる矩形の起点端子44が形成されている。一方、上記終点部分には、集積回路2に設けられた銅(Cu)やアルミニウム(Al)等からなる断面矩形の柱状パッド(以下、「終点パッド22」と称する)の接合部分となる矩形の終点端子45が形成されている。

【0011】

終点パッド22の近傍を通る配線パターン42部分は、終点パッド22(終点端子45)からみて絶縁性フィルム41の縁側を通ように形成されている。このように、配線パターン42が、終点パッド22(終点端子45)からみて絶縁性フィルム41の縁側を通るように形成されていることで、電流ロスやノイズ混入を生じさせる要因となりやすいクランク形状の配線パターン部分を減らすことができる。

【0012】

配線パターン42は、集積回路2に設けられる容量素子512と並列接続されて無線ICタグ1の内部アンテナ回路51を構成する。なお、容量素子512としては、実用上充分な耐圧を有する素子(例えばMIM(Metal Insulator Metal)キャパシタ)を用いることが好ましい。

【0013】

集積回路2は、内部アンテナ回路51に代えて外部アンテナ回路52を接続して用いることができる。外部アンテナ回路52は、インダクタと容量素子とを並列接続した回路を含む共振回路であって、内部アンテナ回路51とは共振周波数が異なる。すなわち、本実施形態の集積回路2は、内部アンテナ回路51に代えて外部アンテナ回路52を接続することで、RFIDの異なる周波数帯の無線ICタグとして汎用的に用いることができる。

【0014】

外部アンテナ回路52は、内部アンテナ回路51が接続される、上述した2つの端子(起点端子44と終点端子45)に接続される。すなわち、起点端子44と終点端子45は、内部アンテナ回路51を接続する端子として機能するとともに、外部アンテナ回路52を接続するための端子としても機能する。このように端子が共通化されることによって、端子の数を最小限に抑えることができ、小型の集積回路2を提供することが可能となる。

【0015】

内部アンテナ回路51や外部アンテナ回路52を構成するための容量素子は、無線ICタグ1に用いられる周波数帯によっては(例えば、2.45GHz帯)、これを起点パッド21と終点パッド22との間に存在する寄生容量で代用することができる。容量素子を寄生容量で代用した場合には、容量素子の構成を設ける必要が無い分、アンテナ回路や集積回路2を小型化することができる。寄生容量の大きさは、例えば、起点パッド21と終点パッド22との間の距離や起点パッド21と終点パッド22の面積を変えることによって調節することができる。

【0016】

図4に起点パッド21及び終点パッド22周辺の素子や配線パターンの構造を示している。終点パッド22の直近には、当該終点パッド22に隣接させて、後述する整流回路61の構成要素であるダイオード55が配置されている。このように、整流回路61を構成しているダイオード55を終点パッド22の直近に隣接させて配置することで、アンテナ回路(内部アンテナ回路51や外部アンテナ回路52)から出力される交流信号を効率よく整流回路61に取り込むことができる。またとくにアンテナ回路が受信する周波数が高周波である場合には、配線部分からの電流ロスを効果的に防ぐことができる。またこのようにダイオード55を終点パッド22の直近に隣接させて配置することで、アンテナ回路から出力される交流信号は直ちに直流電圧に変換される。このため、集積回路2上で交流信号が流れる部分が集積回路2上の一部の領域に局在化されて、集積回路2上の素子や回路には殆ど交流信号が流れなくなる。そしてその結果、交流信号が流れることに起因して生じる素子や回路におけるノイズを低減させることができる。

【0017】

一方、ダイオード55を構成している回路パターンがボトルネックとなって集積回路2に設けられている素子や回路が必要とする電流が供給不足になることがないように、ダイオード55を構成している上記回路パターンの線幅は、素子や回路において必要とされる電流を流すことが可能な幅(例えば35μm程度)に設定されている。

【0018】

図5はアンテナシート4の製造方法を説明するプロセスフローである。アンテナシート4の製造に際しては、まず樹脂製の絶縁フィルムの表面に、銅(Cu)やアルミニウム(Al)等からなる導電材を塗布してなるシート材の、導電材が塗布されている側の面(以下、「表面」と称する)に、フォトレジストを塗布する(S511)。次にフォトレジストに配線パターンに対応するパターンのフォトマスクを施した後、露光・現像を行って、レジストパターンを形成する(S512)。次にシート材をエッチング液に浸してエッチングを行うことにより、フォトマスクが施されている部分以外の部分の導電材を溶解除去する(S513)。その後は除去されずに残っているレジストパターンを除去し、導電材を露出させる(S514)。以上のプロセスを経ることによりアンテナシート4を得ることができる。

【0019】

図6は集積回路2の機能を説明するブロック図である。なお、集積回路2は、シリコンウェハをベースとし、これに洗浄プロセス、スパッタやCVD、熱酸化等の製膜プロセス、リソグラフィ、不純物拡散プロセス、ボンディング、モールド、多層配線プロセス等のプロセスを施すといった、通常の半導体プロセスによって製造されたものである。集積回路2に設けられている素子や回路は、リーダ装置等の外部装置から送信されてくる電磁波(質問電波)の電力によって駆動される。アンテナ回路が電磁波(質問電波)を受信することによって生成された交流信号は、整流回路61に入力され、ここで直流電圧に変換される。整流回路61から出力される直流電圧は、変復調回路62及びレギュレータ63(レギュレータ)に電圧(Vcc3)として供給される。リミッタ回路64は、整流回路61から出力される電圧(Vcc3)が過大とならないよう上限規制するように作用する。

【0020】

変復調回路62は、整流回路61から供給される直流電圧(直流信号)を復調する。変復調回路62によって生成された復調信号は、ロジック回路66に入力される。なお、本実施形態の無線ICタグ1は、このように復調機能と変調機能の双方を備えた構成であるが、本発明は復調機能を有さずに変調回路のみを有する無線ICタグにも適用することができる。

【0021】

レギュレータ63は、整流回路61から供給される電圧(Vcc3)に基づいて、電圧(Vcc0)及び電圧(Vcc1)、及び電圧(Vcc2)を生成する。このうち電圧(Vcc0)は、変復調回路62及び増幅回路75の駆動電圧となる。電圧(Vcc1)は、リセット回路67、及び発振回路68の駆動電圧となる。また電圧(Vcc2)は、入出力回路71の駆動電圧となる。

【0022】

定電圧回路631は、電圧(Vcc3)に基づいて、レギュレータ63に定電圧(例えば1.2V)を供給する。

【0023】

リセット回路67は、レギュレータ63から出力される電圧(Vcc1)が所定の閾値以上になるとロジック回路66に入力していたリセット信号を解除するように動作する。リセット信号が解除されるとロジック回路66が初期化状態から動作状態となる。発振回路68は、例えばRC発振回路である。発振回路68は、ロジック回路66及びリセット回路67を動作させるのに必要となる100kHz〜200kHzのクロック信号を生成する。

【0024】

ここで従来の無線ICタグの製造に用いる集積回路2にあっては、アンテナ回路が受信する電磁波(質問電波)の周波数を分周することによりクロック信号を生成していたため、アンテナ回路が受信する電磁波(質問電波)の周波数が変わればクロック信号の周波数も変わってしまい、アンテナ回路のみを交換しただけでは集積回路2を異なる周波数帯の無線ICタグ用として用いることができなかった。これに対し本実施形態の集積回路2は発振回路68を内蔵するため、クロック信号の周波数はアンテナ回路が受信する電磁波(質問電波)の周波数とは無関係となり、共振周波数を有するアンテナ回路を選択することにより様々な周波数帯の無線ICタグに汎用的に用いることができる。つまり本実施形態の集積回路2によれば、RFIDに許可されている各周波数帯に対応する無線ICタグ1の製造工程を単純化することができ、製造コストも抑えることができる。

【0025】

変復調回路62から復調信号が入力されると、ロジック回路66は入出力回路70及び入出力回路71を制御して、メモリ72に記憶されているデータの読み出しと、ヒューズROM73(Fuse ROM、Fuse Prom)へのデータの書き込み、及びヒューズROM73からのデータの読み出しを行う。ここでメモリ72はEEPROM(Electrically Erasable Programmable Read Only Memory)やFRAM(Ferromagnetic Random Access Memory)等であり、例えば固定的なデータを書き込んでおく用途に利用される。一方、ヒューズROM73は、内部に設けられているヒューズ素子を電流によって焼き切ることにより、ライトアットワンス方式でデータを記憶するメモリである。ヒューズROM73には、例えば機密情報や流動性のあるデータ等、メモリ72に書き込まれるデータに比べて流動性の高いデータが書き込まれる。これらは例えば、会社名等のデータを無線ICタグ1の出荷時等においてメモリ72に書き込んでおき、無線ICタグ1を購入した後にユーザによって社員番号や氏名等のデータをヒューズROM73に書き込むといった使い分がなされる。

【0026】

このように、本実施形態の無線ICタグ1は、メモリ72に記憶される固定情報に加えてユーザが後付けでデータを書き込むことができるため、全てのデータを出荷時に書き込んでおく必要があった従来型の無線ICタグに比べ、多様なユーザニーズに柔軟に対応することができる。

【0027】

ロジック回路66は、メモリ72及びヒューズROM73から読み出したデータ(以下、「読み出しデータ」と称する)を変復調回路62に出力する。変復調回路62は、ロジック回路66から入力される読み出しデータに応じて、アンテナ回路側(リーダ装置等の外部装置側)からみた集積回路2のインピーダンスを変化させる。変復調回路62は、アンテナ回路に結合する抵抗が直列接続されたスイッチングトランジスタを含んで構成されており、読み出しデータに応じて上記スイッチングトランジスタをオンオフし、アンテナ回路側からみた半導体回路2のインピーダンスを変化させる。リーダ装置等の外部装置は、このインピーダンスの変化によって変調されて戻ってくる反射波(応答電波)を受信して復調することにより、無線ICタグ1のメモリ72に格納されているデータを読み取る。

【0028】

図6に示すフォトトランジスタ74は、ヒューズROM73にデータの書き込む際に用いられる。入射される光信号に応じてフォトトランジスタ74から出力される電気信号は、増幅回路75によって増幅されてロジック回路66に入力される。

【0029】

図7はリーダ装置等の外部装置から、メモリ72やヒューズROM73に記憶されているデータを読み出すための電磁波(質問電波)がアンテナ回路51,52に入力された場合における、無線ICタグ1の動作を説明するタイミングチャートである。同図において、「交流信号」は、電磁波(質問電波)が入力されることによりアンテナ回路51又はアンテナ回路52の出力電圧(以下、「入力電圧」と称する)である。「Vcc3」は整流回路61の出力電圧である。「Vcc0」、「Vcc1」、及び「Vcc2」は、レギュレータ63から出力される電圧の値である。「Reset」は、リセット回路67から出力されるリセット信号の波形である。「OSC」は、発振回路68から出力されるクロック信号の波形である。「メモリ」は、メモリ72又はヒューズROM73からのデータ読み出し中であるかどうかを示す信号(読み出しビジー(Busy)信号)の波形である。「変復調回路入力」は、ロジック回路66によって読み出されて変復調回路62に入力される読み出しデータの波形である。

【0030】

図7とともに無線ICタグ1の動作について説明する。電磁波(質問電波)を送信するリーダ装置等の外部装置が無線ICタグ1に近づいてくると、アンテナ回路から整流回路61に供給される交流信号の振幅は次第に増大する(T1)。ここで電圧(Vcc0)、電圧(Vcc1)、電圧(Vcc2)、及び電圧(Vcc3)は、いずれも入力電圧の振幅の増大に伴って増大する(T1〜T3)。これらの電圧は、交流電圧の振幅が閾値を超えた後はリミッタ回路65の作用によって一定に(Vcc0=3.3V、Vcc1=3.3V、Vcc2=3.3V、Vcc3=14.4V)保たれる。

【0031】

次に、電圧(Vcc1)が所定の動作電圧(例えば2.0V)以上になると、発振回路68が動作を開始し、これにより発振回路68からロジック回路66及びリセット回路67にクロック信号の入力が開始される(T2)。電圧(Vcc1)が所定の閾値(例えば3.0V)以上になると、ロジック回路66に入力されていたリセット回路67が解除され、ロジック回路66はメモリ(及び/又は)ヒューズROMに記憶されているデータの読み出しを開始する(T4)。そしてロジック回路66によって読み出されたデータが変復調回路62に入力される(T5)。変復調回路62は、ロジック回路66から入力される読み出しデータの波形に応じてスイッチングトランジスタをオンオフ制御し、アンテナ回路側(外部装置側)から見た集積回路2のインピーダンスを変化させる。以上のようにして無線ICタグ1からのデータの読み出しが行われる。

【0032】

ここでヒューズROM73へのデータの書き込み原理を図8Aとともに説明する。図8Aには2ビット分に相当するヒューズ素子を示している。このうちヒューズ素子H1には、第1のトランジスタTr1(N型MOSFET)が直列接続されている。一方、ヒューズ素子H2には第2のトランジスタTr2(N型MOSFET)が直列接続されている。第3のトランジスタTr3(P型MOSFET)及び第4のトランジスタTr4(N型MOSFET)は、レギュレータ63から供給される電圧(Vcc2)のヒューズ素子H1及びヒューズ素子H2への印加をオンオフ制御するための素子である。

【0033】

ヒューズROM73へのデータの書き込みは、ヒューズ素子H1やヒューズ素子H2を焼き切る(ショートさせる)ことにより行われる。すなわち、ヒューズROM73にデータを書き込む場合には、第3のトランジスタTr3及び第4のトランジスタTr4の夫々のゲート電極に「Low」レベルの制御電圧Aを印加して、第3のトランジスタTr3をオン、第4のトランジスタTr4をオフしてヒューズ素子H1及びヒューズ素子H2に電圧(Vcc2)を印加し、制御電圧B及び制御電圧Cを制御して、第1のトランジスタTr1又は第2トランジスタTr2をオンにする。これによりヒューズ素子H1、又はヒューズ素子H2のいずれかに電圧(Vcc2)が印加されて電圧(Vcc2)が印加されたヒューズ素子に電流が流れ込み、そのヒューズ素子がショートする。このようにしてヒューズROM73へのデータの書き込みが行われる。

【0034】

ヒューズROM73にデータを書き込む際には、入出力回路71にヒューズROM73からデータを読み出すときよりも高い電圧を印加する必要がある。図8B及び図8Cは、レギュレータ63に内蔵される回路であり、フォトトランジスタ74から上記電気信号が入力された場合に、ロジック回路66から送られてくる制御信号であるVcc2コントロールに応じて、入出力回路71に供給する電圧(Vcc2)を切り換える回路である。

【0035】

まず図8Bに示す回路であるが、この回路は、第1乃至第3の増幅器OP1,OP2,OP3と4つの抵抗素子R1,R2,R3,R4とを含んで構成されている。第1の増幅器OP1の反転入力(−)には定電圧回路631から出力される定電圧(Vref=1.2V)が入力される。第1の増幅器OP1の非反転入力(+)には第1の増幅器OP1の出力電圧が抵抗素子R1を介して帰還される。第1の増幅器OP1の出力端子は、直列接続された抵抗素子R1及びR2を介して接地されている。また抵抗素子R1,R2の抵抗値は第1の増幅器OP1の出力電圧が3.3Vになるように設定されている。一方、第2の増幅器OP2の反転入力(−)には第1の増幅器OP1の出力電圧が入力される。第2の増幅器OP2の非反転入力(+)には、第3の増幅器OP3の出力電圧が帰還される。第2の増幅器OP2の出力は、レギュレータ63の出力電圧(Vcc2)となる。

【0036】

第3の増幅器OP3の反転入力(−)には第1の増幅器OP1の出力電圧が入力される。第3の増幅器OP3の非反転入力(+)には第3の増幅器OP3の出力電圧が抵抗素子R3を介して帰還される。第3の増幅器OP3の出力端子は直列接続された抵抗素子R3及びR4を介して接地されている。抵抗素子R3,R4の抵抗値は第3の増幅器OP3の出力電圧が12.0Vになるように設定されている。

【0037】

図8Bにおいて、第1の増幅器OP1と2つの抵抗素子R1,R2とを含んで構成される回路(以下、演算増幅回路811という)は、第2及び第3の増幅器OP2,OP3に対して3.3Vのリファレンス電圧を印加している。また演算増幅回路811は、定電圧回路631から供給される定電圧(Vref=1.2V)を3.3Vのリファレンス電圧に変換し、これを第2及び第3の増幅器OP2,OP3の反転入力(−)に供給している。

【0038】

第2及び第3の増幅器OP2,OP3は、いずれもバイアス入力端子BIAS1,BIAS2を有しており、これらは夫々バイアス入力端子BIAS1,BIAS2に外部供給されるバイアス電圧によって動作状態が制御される。図8Bにおける第2及び第3の増幅器OP2,OP3と抵抗素子R3,R4とを含んで構成される回路(以下、電圧切換回路812という)は、ロジック回路66から送られてくるVcc2コントロールに応じて2種類の電圧(Vcc2=3.3V又は12.0V)を生成している。

【0039】

図8Cはロジック回路66から送られてくるVcc2コントロールに応じて、第2及び第3の増幅器OP2,OP3のバイアス入力端子BIAS1,BIAS2に入力するバイアス電圧を生成するための回路である。この回路は第5乃至第9のトランジスタTr5,Tr6,Tr7,Tr8,TR9を含んで構成されている。トランジスタTr5,Tr6,Tr7,Tr8,TR9はいずれもMOSFET(電界効果MOSトランジスタ)であり、第5及び第6のトランジスタはP型MOSFET、第7乃至第9のトランジスタはN型MOSFETである。

【0040】

第5及び第6のトランジスタTr5,Tr6のソースには、電圧(Vcc3)が供給されている。第5のトランジスタTr5のゲートは、第2の増幅器OP2のバイアス入力端子BIAS1に接続されている。第5のトランジスタTr5のゲート及びドレインは短絡されている。第6のトランジスタTr6のゲートは、第3の増幅器OP3のバイアス入力端子BIAS2に接続されている。第6のトランジスタTr6のゲート及びドレインは短絡されている。第5のトランジスタTr5のドレインは、第7のトランジスタTr7のドレインに接続されている。第6のトランジスタTr6のドレインは、第8のトランジスタTr8のドレインに接続されている。

【0041】

第7のトランジスタTr7のゲートには、定電圧回路631から供給される定電圧(例えば1.2V)が印加される。第7のトランジスタTr7のソースは第9のトランジスタTr5のドレインに接続されている。第8のトランジスタTr8のソースは、第9のトランジスタTr9のドレインに接続している。

【0042】

第8のトランジスタTr8のゲートには、ロジック回路66から送られてくるVcc2コントロールが入力される。なお、ロジック回路66から送られてくるVcc2コントロールは、入出力回路71がヒューズROM73からの読み出しを行う場合は定電圧回路631から供給される定電圧(Vref=1.2V)に対して「Low」となり、ヒューズROM73への書き込みを行う場合は「High」となる信号である。第9のトランジスタTr9のゲートには、定電圧回路631から供給される所定のバイアス電圧が印加される。また第9のトランジスタTr9のソースは接地されている。

【0043】

図9にヒューズROM73へのデータの書き込み動作を説明するタイミングチャートを示している。図9において、「Vcc1」及び「Vcc2」は、レギュレータ63から出力される電圧の値である。「Vcc2コントロール」は、ロジック回路66からレギュレータ63に送られてくるVcc2コントロールである。「光信号」は、フォトトランジスタ74に照射される光信号の波形である。「ヒューズROM」は、ヒューズROM73へのデータの書き込み中であることを示す信号(書き込みビジー(Busy)信号)の波形である。

【0044】

図9に示すヒューズROM73へのデータの書き込み処理は、電磁波をアンテナ回路に入力することにより図7のタイミングチャートに従ってロジック回路66を動作させた後、ヒューズROM73へのデータの書き込みを開始するためのコマンド(以下、「書き込み開始コマンド」と称する)を含んだ光信号をフォトトランジスタ74に照射することにより開始される。

【0045】

まずフォトトランジスタ74から当該フォトトランジスタ74に照射される光信号に応じた電気信号が出力される。増幅回路75は、フォトトランジスタ74から出力される上記電気信号を増幅してロジック回路66に出力する(T6〜T7)。なお、ヒューズROM73へのデータの書き込みは、必要な電力を有する電磁波をアンテナ回路に供給しつつ行われる。

【0046】

フォトトランジスタ74から上記電気信号が入力されると、ロジック回路66はレギュレータ63に供給しているVcc2コントロールを、「Low」から「High」に切り換える(T8)。

【0047】

ここでレギュレータ63において、ロジック回路66から送られてくるVcc2コントロールは図8Cに示す回路の第8のトランジスタTr8のゲートに入力され、Vcc2コントロールが「Low」から「High」になることにより、第8のトランジスタTr8がオンとなる。このため、第5のトランジスタTr5と第7のトランジスタTr7とによって構成される経路を通じての第9のトランジスタTr9への電流供給が停止して、第9のトランジスタTr9への電流供給はもっぱら第6のトランジスタTr6と第8のトランジスタTr8とによって構成される経路を通じてのみ行われることになる。これにより第6のトランジスタTr6のソースとゲートとの間に電位差が生じる。一方、第5のトランジスタTr5のソースとゲートとの間には電位差は生じない。

【0048】

ここで第6のトランジスタTr6のソースとゲートの間に生じた電位差は、第6のトランジスタTr6のゲートを通じて図8Bの電圧切換回路812を構成している第3の増幅器OP3のバイアス入力端子BIAS2に供給される。これにより第3の増幅器OP3が動作する。一方、図8Cの第5のトランジスタTr5のソースとゲートの間には電位差が生じないため、第2の増幅器OP2のバイアス入力端子BIAS1にはバイアス電圧が供給されず、第2の増幅器OP2は動作を停止する。以上のようにして、結局、第3の増幅器OP3のみがオンすることになり、電圧切換回路812を構成している抵抗素子R3,R4によって定まる第3の増幅器OP3の出力電圧である12.0Vが、電圧(Vcc2)としてレギュレータ63から出力される。

【0049】

なお、メモリ72又はヒューズROM73からのデータの読み出し時においては、ロジック回路66からレギュレータ63にはVcc2コントロールとして「Low」が送られてくる。このため、図8Cに示す回路における第8のトランジスタTr8のゲート電圧は「Low」となり、これにより第8のトランジスタTr8は動作を停止する。従って、第6のトランジスタTr6と第8のトランジスタTr8とによって構成される経路を通じた第9のトランジスタTr9への電流供給が停止し、第9のトランジスタTr9への電流供給はもっぱら第5のトランジスタTr5と第7のトランジスタTr7とによって構成される経路を通じてのみ行われることになり、第5のトランジスタTr5のソースとゲートとの間には電位差が生じるが、第6のトランジスタTr6のソースとゲートとの間には電位差は生じない。これにより第2の増幅器OP2は動作するが、第3の増幅器OP3は動作を停止し、電圧切換回路812を構成している第2の増幅器OP2の出力電圧である3.3Vが電圧(Vcc2)としてレギュレータ63から出力されることになる。以上のようにして電圧(Vcc=12.0V)の供給が開始される(T8)。

【0050】

次に、ヒューズROM73上のデータの書き込み位置を示すアドレスデータ及び書き込みデータを含んだ光信号が、フォトトランジスタ74に照射され(T9〜T10)、この光信号に対応する電気信号がロジック回路66に入力される。ロジック回路66は、入出力回路71を制御して、入力される電気信号に含まれるアドレスデータで指定されるヒューズROM73の所定の記憶位置に、上記電気信号に含まれる書き込みデータを書き込む(T11〜T12)。

【0051】

ヒューズROM73へのデータの書き込みが完了すると、ロジック回路66は、ヒューズROM73の所定位置のビット(以下、「書き込み済フラグ」と称する)をオンにする(T13〜T14)。以上の処理が終了した後は、アンテナ回路からの電磁波の供給が停止されて書き込み処理が終了する(T15)。なお、上記ビットは、ヒューズROM73へのデータの書き込みを行ったかどうか(書き込み済であるかどうか)を判断する際にロジック回路66によって参照される。すなわち、ロジック回路66は、上記「書き込み済フラグ」がオンであればヒューズROM73には既にデータが書き込まれているものと判断し、この場合にはフォトトランジスタ74に書き込みコマンドを含んだ光信号が照射されてもヒューズROM73へのデータの書き込み動作を開始しない。

【0052】

なお、以上に説明した処理においては、フォトトランジスタ74が光信号を確実に受信することができるように、ロジック回路66のクロック信号の周波数は、フォトトランジスタ74に照射される光信号の周波数よりも高い値に設定される。またタイミングのずれやノイズの影響によって、一度の照射で光信号を読み込めない場合も起こりうるが、このような場合には、ロジック回路66が光信号による入力を受け付けるまで、フォトトランジスタ74に繰り返し光信号を入力するようにする。

【0053】

ところで、フォトトランジスタ74に照射される光信号は、増幅回路75やロジック回路66を誤動作させる要因となる。このため、フォトトランジスタ74は、増幅回路75やロジック回路66からなるべく離れた位置に設けることが好ましい。一方、増幅回路75において増幅された電気信号を効率よくロジック回路66に伝えるためには、増幅回路75はロジック回路66に隣接させて配置することが好ましい。ここでフォトトランジスタ74と増幅回路75又はロジック回路66の位置関係は、例えば図10に示す関係から求められる。すなわち、光源(光ファイバ)81からの光が直接照射される範囲は、フォトトランジスタ74と光源との間の距離Zと、光源から照射される光の広がり角θから求められる、半径x=Z・tanθの円の範囲であるので、フォトトランジスタ74、増幅回路75、及びロジック回路66は、集積回路2上の表面の領域のうち上記円の範囲外の領域に配置することが好ましいことになる。またこの場合において、増幅回路75において増幅された電気信号を効率よくロジック回路66に伝えるために、ロジック回路66と増幅回路75とは隣接するように配置することが好ましいことになる。

【0054】

ヒューズROM73へのデータの書き込みに際しては、アンテナ回路に通常の読み出しの際に比べて強い電磁波を供給しつつフォトトランジスタ74に書き込み命令を与えてから書き込みデータを入力するといった一連のプロセスを実施する必要がある。ここでこのようなプロセスの複雑さは、無線ICタグ1のセキュリティ強度の向上に貢献する。またデータの書き込みがヒューズを焼き切るという物理的な手段で行われることもセキュリティ強度の向上に貢献する。

【0055】

以上、本発明の実施形態につき詳細に説明したが、以上の実施形態の説明は本発明の理解を容易にするためのものであり、本発明を限定するものではない。本発明はその趣旨を逸脱することなく、変更、改良され得ると共に本発明にはその等価物が含まれることは勿論である。

【図面の簡単な説明】

【0056】

【図1】本発明の一実施形態として説明する無線ICタグ1の平面図である。

【図2】本発明の一実施形態として説明する無線ICタグ1の断面図である。

【図3】本発明の一実施形態として説明するアンテナシート4単体の平面図である。

【図4】本発明の一実施形態として説明する起点パッド21及び終点パッド22周辺の素子や配線パターンの構造を示す図である。

【図5】本発明の一実施形態として説明するアンテナシート4の製造方法を説明するプロセスフローである。

【図6】本発明の一実施形態として説明する集積回路2の機能を説明するブロック図である。

【図7】本発明の一実施形態として説明するデータを読み出し時の無線ICタグ1の動作を説明するタイミングチャートである。

【図8A】本発明の一実施形態として説明するヒューズROM73へのデータの書き込み原理を説明する図である。

【図8B】本発明の一実施形態として説明するVccコントロールに応じて入出力回路71に供給する電圧(Vcc2)を切り換える回路である。

【図8C】本発明の一実施形態として説明するVccコントロールに応じて入出力回路71に供給する電圧(Vcc2)を切り換える回路である。

【図9】本発明の一実施形態として説明するヒューズROM73へのデータの書き込み動作を説明するタイミングチャートである。

【図10】本発明の一実施形態として説明するフォトトランジスタ74と増幅回路75又はロジック回路66の位置関係を説明する図である。

【符号の説明】

【0057】

1 無線ICタグ

2 集積回路

21 起点パッド

22 終点パッド

51 内部アンテナ回路

52 外部アンテナ回路

55 ダイオード

61 整流回路

62 変復調回路

63 レギュレータ

65 リミッタ回路

66 ロジック回路

67 リセット回路

68 発振回路

71 入出力回路

72 メモリ

73 ヒューズROM

74 フォトトランジスタ

【特許請求の範囲】

【請求項1】

リーダ装置等の外部装置から送信される質問電波を受信して、前記質問電波の反射波を応答電波として送信する無線ICタグに用いられる集積回路であって、

データを記憶するメモリと、

前記外部装置から受信した電磁波に基づく交流電流を整流して直流電圧を生成するとともに、当該集積回路を動作させるための電圧を生成する整流回路と、

前記メモリに記憶されているデータを読み出すロジック回路と、

前記ロジック回路が読み出したデータによって前記反射波を変調する変調回路と、

アンテナ回路が接続される端子と、

照射される光信号に応じた電気信号を前記ロジック回路に入力するフォトトランジスタと、

前記電気信号に含まれているデータが書き込まれるヒューズROMと、

を有すること

を特徴とする集積回路。

【請求項2】

請求項1に記載の集積回路であって、

前記直流電圧を復調する復調回路が設けられてなること

を特徴とする集積回路。

【請求項3】

請求項1または2に記載の集積回路であって、

前記ロジック回路は、前記電気信号に含まれているデータを前記ヒューズROMに書き込むための回路を有すること

を特徴とする集積回路。

【請求項4】

請求項1または2に記載の集積回路であって、

前記ロジック回路のクロックの周波数は、前記光信号の周波数よりも高いこと

を特徴とする集積回路。

【請求項5】

請求項1または2に記載の集積回路であって、

前記ヒューズROMへのデータの読み出し及び書き込みを行う入出力回路と、

前記整流回路によって生成された電圧により前記入出力回路の前記データの読み出し及び書き込み時に必要となる電圧を前記入出力回路に供給するレギュレータとを含み、

前記ロジック回路は、前記フォトトランジスタから前記電気信号が入力されると、前記レギュレータが前記入出力回路に対して前記ヒューズROMにデータを書き込むために必要となる電圧を供給するように前記レギュレータを制御すること

を特徴とする集積回路。

【請求項6】

請求項1または2に記載の集積回路であって、

前記整流回路によって生成された電圧によって動作し、前記電気信号を増幅する増幅回路を有すること

を特徴とする集積回路。

【請求項7】

請求項1または2に記載の集積回路であって、

前記ロジック回路は、前記フォトトランジスタと前記フォトトランジスタに光を照射する光源との間の距離をZとし、前記光源から照射される光の広がり角をθとした場合に、前記集積回路の表面の領域のうち、x=Z・tanθの式から求められる半径xの円の外側の領域に配置されること

を特徴とする集積回路。

【請求項8】

請求項6に記載の集積回路であって、

前記増幅回路は、前記フォトトランジスタと前記フォトトランジスタに光を照射する光源との間の距離をZとし、前記光源から照射される光の広がり角をθとした場合に、前記集積回路の表面の領域のうち、x=Z・tanθの式から求められる半径xの円の外側の領域に配置されること

を特徴とする集積回路。

【請求項9】

請求項8に記載の集積回路であって、

前記増幅回路は、前記ロジック回路に隣接させて配置されることを特徴とする集積回路。

【請求項10】

リーダ装置等の外部装置から送信される質問電波を受信して、前記質問電波の反射波を応答電波として送信する無線ICタグであって、

データを記憶するメモリと、

前記外部装置から受信した電磁波に基づく交流電流を整流して直流電圧を生成するとともに、当該集積回路を動作させるための電圧を生成する整流回路と、

前記メモリに記憶されているデータを読み出すロジック回路と、

前記ロジック回路が読み出したデータによって前記反射波を変調する変調回路と、

前記整流回路によって生成される前記電圧によって動作し、前記ロジック回路を動作させるためのクロック信号を生成する発振回路と、

アンテナ回路が接続される端子と、

照射される光信号に応じた電気信号を前記ロジック回路に入力するフォトトランジスタと、

前記電気信号に含まれているデータが書き込まれるヒューズROMと、

が設けられてなる集積回路と、

前記内部アンテナ回路を構成する、絶縁性フィルムに導電材からなる配線パターンを渦巻状に形成した平面状のインダクタと、

を備えること

を特徴とする無線ICタグ。

【請求項11】

請求項10に記載の無線ICタグであって、

前記直流電圧を復調する復調回路が設けられてなること

を特徴とする無線ICタグ。

【請求項12】

請求項10または11に記載の無線ICタグであって、

前記集積回路には、前記整流回路によって生成された電圧を前記ヒューズROMにデータを書き込むために必要となる電圧に昇圧する昇圧回路が設けられてなること

を特徴とする無線ICタグ。

【請求項1】

リーダ装置等の外部装置から送信される質問電波を受信して、前記質問電波の反射波を応答電波として送信する無線ICタグに用いられる集積回路であって、

データを記憶するメモリと、

前記外部装置から受信した電磁波に基づく交流電流を整流して直流電圧を生成するとともに、当該集積回路を動作させるための電圧を生成する整流回路と、

前記メモリに記憶されているデータを読み出すロジック回路と、

前記ロジック回路が読み出したデータによって前記反射波を変調する変調回路と、

アンテナ回路が接続される端子と、

照射される光信号に応じた電気信号を前記ロジック回路に入力するフォトトランジスタと、

前記電気信号に含まれているデータが書き込まれるヒューズROMと、

を有すること

を特徴とする集積回路。

【請求項2】

請求項1に記載の集積回路であって、

前記直流電圧を復調する復調回路が設けられてなること

を特徴とする集積回路。

【請求項3】

請求項1または2に記載の集積回路であって、

前記ロジック回路は、前記電気信号に含まれているデータを前記ヒューズROMに書き込むための回路を有すること

を特徴とする集積回路。

【請求項4】

請求項1または2に記載の集積回路であって、

前記ロジック回路のクロックの周波数は、前記光信号の周波数よりも高いこと

を特徴とする集積回路。

【請求項5】

請求項1または2に記載の集積回路であって、

前記ヒューズROMへのデータの読み出し及び書き込みを行う入出力回路と、

前記整流回路によって生成された電圧により前記入出力回路の前記データの読み出し及び書き込み時に必要となる電圧を前記入出力回路に供給するレギュレータとを含み、

前記ロジック回路は、前記フォトトランジスタから前記電気信号が入力されると、前記レギュレータが前記入出力回路に対して前記ヒューズROMにデータを書き込むために必要となる電圧を供給するように前記レギュレータを制御すること

を特徴とする集積回路。

【請求項6】

請求項1または2に記載の集積回路であって、

前記整流回路によって生成された電圧によって動作し、前記電気信号を増幅する増幅回路を有すること

を特徴とする集積回路。

【請求項7】

請求項1または2に記載の集積回路であって、

前記ロジック回路は、前記フォトトランジスタと前記フォトトランジスタに光を照射する光源との間の距離をZとし、前記光源から照射される光の広がり角をθとした場合に、前記集積回路の表面の領域のうち、x=Z・tanθの式から求められる半径xの円の外側の領域に配置されること

を特徴とする集積回路。

【請求項8】

請求項6に記載の集積回路であって、

前記増幅回路は、前記フォトトランジスタと前記フォトトランジスタに光を照射する光源との間の距離をZとし、前記光源から照射される光の広がり角をθとした場合に、前記集積回路の表面の領域のうち、x=Z・tanθの式から求められる半径xの円の外側の領域に配置されること

を特徴とする集積回路。

【請求項9】

請求項8に記載の集積回路であって、

前記増幅回路は、前記ロジック回路に隣接させて配置されることを特徴とする集積回路。

【請求項10】

リーダ装置等の外部装置から送信される質問電波を受信して、前記質問電波の反射波を応答電波として送信する無線ICタグであって、

データを記憶するメモリと、

前記外部装置から受信した電磁波に基づく交流電流を整流して直流電圧を生成するとともに、当該集積回路を動作させるための電圧を生成する整流回路と、

前記メモリに記憶されているデータを読み出すロジック回路と、

前記ロジック回路が読み出したデータによって前記反射波を変調する変調回路と、

前記整流回路によって生成される前記電圧によって動作し、前記ロジック回路を動作させるためのクロック信号を生成する発振回路と、

アンテナ回路が接続される端子と、

照射される光信号に応じた電気信号を前記ロジック回路に入力するフォトトランジスタと、

前記電気信号に含まれているデータが書き込まれるヒューズROMと、

が設けられてなる集積回路と、

前記内部アンテナ回路を構成する、絶縁性フィルムに導電材からなる配線パターンを渦巻状に形成した平面状のインダクタと、

を備えること

を特徴とする無線ICタグ。

【請求項11】

請求項10に記載の無線ICタグであって、

前記直流電圧を復調する復調回路が設けられてなること

を特徴とする無線ICタグ。

【請求項12】

請求項10または11に記載の無線ICタグであって、

前記集積回路には、前記整流回路によって生成された電圧を前記ヒューズROMにデータを書き込むために必要となる電圧に昇圧する昇圧回路が設けられてなること

を特徴とする無線ICタグ。

【図4】

【図5】

【図6】

【図7】

【図8A】

【図8B】

【図8C】

【図9】

【図10】

【図1】

【図2】

【図3】

【図5】

【図6】

【図7】

【図8A】

【図8B】

【図8C】

【図9】

【図10】

【図1】

【図2】

【図3】

【公開番号】特開2006−293690(P2006−293690A)

【公開日】平成18年10月26日(2006.10.26)

【国際特許分類】

【出願番号】特願2005−113544(P2005−113544)

【出願日】平成17年4月11日(2005.4.11)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.FRAM

【出願人】(000001889)三洋電機株式会社 (18,308)

【Fターム(参考)】

【公開日】平成18年10月26日(2006.10.26)

【国際特許分類】

【出願日】平成17年4月11日(2005.4.11)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.FRAM

【出願人】(000001889)三洋電機株式会社 (18,308)

【Fターム(参考)】

[ Back to top ]