雑音除去装置

【課題】雑音除去フィルタとしての雑音除去処理の能力を担保しつつ、雑音除去フィルタとしてのハードウェア的な規模を縮小することが可能な雑音除去装置を提供する。

【解決手段】一定方向の走査線Lにより順次走査される複数の画素Pxにより形成されるデジタル画像における中心画素Px24の輝度と、当該中心画素Px24の周囲の複数の他の画素Pxの輝度と、を用いて、フィルタ対象領域Fにおける雑音除去処理を行う場合に、フィルタ対象領域Fにおいて走査線L上に並ぶ画素Pxの輝度を記憶し、且つフィルタ対象領域Fにおける走査線Lの数に対応した数のラインメモリを備えるとき、フィルタ対象領域Fにおける走査線L上の画素Px11乃至画素Px17の数が、走査線Lに垂直な方向の画素数より大きくされている。

【解決手段】一定方向の走査線Lにより順次走査される複数の画素Pxにより形成されるデジタル画像における中心画素Px24の輝度と、当該中心画素Px24の周囲の複数の他の画素Pxの輝度と、を用いて、フィルタ対象領域Fにおける雑音除去処理を行う場合に、フィルタ対象領域Fにおいて走査線L上に並ぶ画素Pxの輝度を記憶し、且つフィルタ対象領域Fにおける走査線Lの数に対応した数のラインメモリを備えるとき、フィルタ対象領域Fにおける走査線L上の画素Px11乃至画素Px17の数が、走査線Lに垂直な方向の画素数より大きくされている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、雑音除去装置の技術分野に属する。より詳細には、複数の画素により形成されるデジタル画像に含まれる雑音を除去する雑音除去装置の技術分野に属する。

【背景技術】

【0002】

近年、例えばデジタルカメラ等に内蔵される撮像素子(例えば、CCD(Charge-Coupled Device)等の撮像素子)においては、高密度化される等の高性能化が著しい。そしてこれに伴い、撮像素子から出力される撮像信号又は当該撮像信号を処理して得られる画像信号に含まれる雑音(ノイズ)の低減又は除去のための技術の開発も、盛んに行われている。

【0003】

ここで、上述した撮像素子から出力される撮像信号に含まれる雑音には、例えば、その撮像素子の構造上の原因から原画像(動画像又は静止画像を含む。以下、同様。)を含む撮像信号に含まれることとなる雑音がある。また撮像信号を処理して得られる画像信号に含まれる雑音には、例えば、デジタル画像生成のためのブロック符号化処理が撮像信号に施されることに起因する、いわゆるブロックノイズ等がある。

【0004】

そしてこのような各種の雑音に対して、原画像の高振幅成分(即ち、その原画像に含まれている画像構成物(被写体)の輪郭の形状等)を損なうことなく、原画像内に低振幅成分として含まれる雑音や歪みを除去する手法として、例えば下記特許文献1に開示されている手法がある。なお上記歪みとは、具体的に例えば、ブロック圧縮符号化方式に対応したブロック境界における歪みや原画像内の輪郭周辺における歪みがある。また特許文献1に開示されている手法は、いわゆるε−分離非線形デジタルフィルタを用いた雑音除去フィルタである。ε−分離非線形デジタルフィルタについては、例えば下記非特許文献1に詳細に開示されている。

【0005】

ここで、ε−分離非線形デジタルフィルタによる雑音除去処理について、その概要を説明する。当該雑音除去処理では、一般には以下の(1)から(6)までの六段階の処理により、原画像としてのデジタル画像における高振幅成分を損なうことなく、低振幅成分である雑音等を除去する。この雑音除去処理は、言い換えれば、上記高振幅成分を損なうことなく、低振幅成分を平滑化する処理である(特許文献1第4図参照)。

(1)画像信号として入力されたデジタル画像のうち、複数の画素からなる正方形の領域を「フィルタ対象領域」として設定し、そのフィルタ対象領域に含まれている画素の輝度を、画素ごとに取得する。

(2)フィルタ対象領域の中心画素の輝度を示す輝度情報を、一時的に記憶する。

(3)当該記憶されている輝度情報により示される輝度と、フィルタ対象領域の中心画素以外の複数の他の画素の輝度と、の差分を、他の画素ごとに検出する。なお一般的には、処理を簡略化すべく、上記(2)において記憶された中心画素の輝度と、フィルタ対象領域内の全ての画素(中心画素を含む)の輝度と、の差分を画一的に求める。この場合、上記(2)において記憶した中心画素の輝度と、フィルタ対象領域内の全ての画素の一部としての中心画素の輝度と、の差分は、当然ながらゼロである。

(4)他の画素との上記差分を用いて、雑音除去処理の対象となる画素を判定する。当該判定処理を、以下「雑音判定処理」と称する。即ち、他の画素各々のうち、検出された差分が予め設定されている雑音閾値以上である他の画素を、当該他の画素の輝度が上記高振幅成分に属する(即ち、当該他の画素が上記輪郭の形状等を構成する)として雑音除去処理の対象画素から除外する。一方、中心画素の輝度との差分が上記雑音閾値未満である他の画素を、当該他の画素の輝度が上記低振幅成分に属する(即ち、当該他の画素に雑音等が含まれる)として雑音除去処理の対象画素とする。

(5)雑音除去処理の対象画像についての上記差分と予め設定されているフィルタ係数とを乗算する処理を、対象画像それぞれについて行い、対象画像それぞれについての乗算結果を全て加算する。この場合、対象画素の各々に乗算されるフィルタ係数は全て同一とされる。

(6)上記の加算結果を、上記(2)において記憶した輝度情報により示される中心画素の輝度に加算し、その加算結果を、当該中心画素における雑音除去後の輝度とする。

【0006】

以上説明した(1)から(6)までの六段階の処理を、デジタル画像を構成する全ての画素を順次上記中心画素として繰り返し実行することにより、当該デジタル画像についてのε−分離非線形デジタルフィルタによる雑音除去処理が実行される。このような雑音除去処理により、原画像に含まれている画像構成物(被写体)の輪郭の形状等を損なうことなく、原画像内に低振幅成分として含まれる雑音や歪みを除去することが可能となる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2000−102020号公報(第1図、第4図等)

【非特許文献】

【0008】

【非特許文献1】原島他,“ε−分離非線形ディジタルフィルタとその応用”電子通信学会論文誌A,第65巻,NO.4,pp.297−304,Apr.1982

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、特許文献1に開示されている雑音除去フィルタでは、上記した(1)から(6)までの処理により雑音除去処理を行うことから、雑音除去フィルタとしての雑音除去効果を高めるためには、より多数の画素をフィルタ対象領域として設定する必要がある。

【0010】

ここで、ハードウェア的に特許文献1に開示されている雑音除去フィルタを実現する場合、フィルタ対象領域の輝度を取得するためには、一般には、いわゆるラインメモリ又はフレームメモリが必須である。そしてこれらのメモリは、原理上、最低でも「フィルタ対象領域における走査線数−1」の数のメモリが必要となる。このとき、「フィルタ対象領域における走査線数」とは、例えばいわゆるラスタスキャン方式に基づくデジタル画像に対する雑音除去処理においては、それに含まれる上記フィルタ対象領域を通る当該スキャンに係る走査線の数をいう。

【0011】

以上のような事情から、特許文献1に開示されている雑音除去フィルタにおいて高性能な雑音除去処理を行うためには、その回路規模が飛躍的に増大してしまうという問題点があった。このような問題点は、例えば雑音除去フィルタとしての価格の高騰や、製造工程の複雑化に繋がるものであり、解決が望まれる問題点である。

【0012】

そこで本発明は、上記の問題点等に鑑みて為されたもので、その課題は、雑音除去フィルタとしての雑音除去処理の能力を担保しつつ、雑音除去フィルタとしてのハードウェア的な規模を縮小することが可能な雑音除去装置を提供することにある。

【課題を解決するための手段】

【0013】

上記の課題を解決するために、請求項1に記載の発明は、一定方向の走査線により順次走査される複数の画素により形成されるデジタル画像における一の画素の信号と、当該一の画素の周囲の複数の他の画素の信号と、を用いて、当該一の画素と当該他の画素から構成される対象領域における雑音除去処理を行う雑音除去装置であって、前記対象領域において前記走査線上に並ぶ前記画素の前記信号を記憶し、且つ前記対象領域における前記走査線の数に対応した数のラインメモリ等の記憶手段を備える雑音除去装置において、前記対象領域における前記走査線上の画素数が、当該対象領域において前記走査線に垂直な方向の画素数より大きいように構成される。

【0014】

請求項1に記載の発明によれば、走査線の数に対応した数の信号記憶用の記憶手段を備える雑音除去装置において、対象領域における走査線上の画素数が当該走査線に垂直な方向の画素数より大きいので、走査線上の画素数と走査線に垂直な方向の画素数とが同数の場合に比して、対象領域に含まれる画素数を雑音除去処理用に十分確保しつつ、記憶手段の数を低減させることができる。

【0015】

上記の課題を解決するために、請求項2に記載の発明は、請求項1に記載の雑音除去装置において、前記雑音除去装置は、前記一の画素の前記信号と、前記他の画素各々の前記信号と、差分値を、前記記憶手段を用いてそれぞれ検出する差分演算部等の検出手段と、前記検出された各差分値と閾値とをそれぞれ比較する閾値判定部等の比較手段と、前記比較手段による比較結果に基づいて前記雑音除去処理の対象とすべき前記他の画素を特定する閾値判定部等の特定手段と、特定された前記他の画素それぞれについて、前記検出された差分値に対して予め設定されたフィルタ係数を乗算する演算部等の乗算手段と、前記乗算手段による乗算結果を前記一の画素の前記信号に加算して出力する演算部等の加算手段と、前記検出手段による検出処理、前記比較手段による比較処理、前記特定手段による特定処理、前記乗算手段による乗算処理、及び前記加算手段による加算処理を、前記デジタル画像を構成する各前記画素のそれぞれを前記一の画素として、前記デジタル画像を形成する各前記画素について繰り返す演算部等の制御手段と、を備え、前記対象領域における前記一の画素を通る前記走査線上の画素数が、当該対象領域における他の前記走査線上の画素数より大きいように構成される。

【0016】

請求項2に記載の発明によれば、請求項1に記載の発明の作用に加えて、対象領域に含まれる一の画素を通る走査線上の画素数が、当該対象領域における他の走査線上の画素数より大きいので、より効果的な雑音除去処理を実行しつつ、記憶手段の数を低減させることができる。

【0017】

上記の課題を解決するために、請求項3に記載の発明は、請求項2に記載の雑音除去装置において、前記加算手段は、前記加算処理のために前記一の画素の前記信号を記憶するレジスタ等の加算用記憶手段を備え、当該加算用記憶手段が、各前記画素の前記信号を記憶する前記記憶手段としても用いられるように構成される。

【0018】

請求項3に記載の発明によれば、請求項2に記載の発明の作用に加えて、加算処理のために一の画素の信号を記憶する加算用記憶手段が、各画素の信号を記憶する記憶手段としても用いられるので、記憶手段の数を低減させつつ、対象領域を構成する画素の数を増加させて雑音除去効果を向上させることができる。

【0019】

上記の課題を解決するために、請求項4に記載の発明は、請求項1から請求項3のいずれか一項に記載の雑音除去装置において、前記デジタル画像はデジタル静止画像であり、前記他の画素は、当該デジタル静止画像内において前記一の画素について対称の位置にある前記画素であり、前記フィルタ係数の値は、相互に前記対称の位置にある前記他の画素において同一とされるように構成される。

【0020】

請求項4に記載の発明によれば、請求項1から請求項3のいずれか一項に記載の発明の作用に加えて、他の画素がデジタル静止画像内において一の画素について対称の位置にある画素であり、相互に対称の位置にある他の画素においてフィルタ係数の値が同一とされるので、乗算手段及び加算手段を簡略化することができる。

【0021】

上記の課題を解決するために、請求項5に記載の発明は、請求項1から請求項4のいずれか一項に記載の雑音除去装置において、前記一の画素が含まれる前記対象領域を構成する前記他の画素の一部が仮想的に前記デジタル画像外となる場合において、当該デジタル画像外となった前記他の画素の前記信号として、前記デジタル画像の外縁を対称軸として当該他の画素に対して対称の位置にある前記対象領域内の前記画素の前記信号を、前記雑音除去処理に供させる端画素判定部等の画素処理手段を備える。

【0022】

請求項5に記載の発明によれば、請求項1から請求項4のいずれか一項に記載の発明の作用に加えて、対象領域を構成する他の画素の一部が仮想的にデジタル画像外となる場合に、デジタル画像外となった他の画素の信号として、デジタル画像の外縁を対称軸として当該他の画素に対して対称の位置にある対象領域内の画素の信号を雑音除去処理に供させるので、デジタル画像の端部に対象領域が設定されることで他の画素の一部が仮想的にデジタル画像外となった場合でも、それ以外の場合と同様の雑音除去効果を有する雑音除去処理を行うことができる。

【0023】

上記の課題を解決するために、請求項6に記載の発明は、請求項1から請求項4のいずれか一項に記載の雑音除去装置において、前記一の画素が含まれる前記対象領域を構成する前記他の画素の一部が仮想的に前記デジタル画像外となる場合において、当該デジタル画像外となった前記他の画素の前記信号として、前記対象領域内の前記一の画素の前記信号を前記雑音除去処理に供させる端画素判定部等の画素処理手段を備える。

【0024】

請求項6に記載の発明によれば、請求項1から請求項4のいずれか一項に記載の発明の作用に加えて、対象領域を構成する他の画素の一部が仮想的にデジタル画像外となる場合に、デジタル画像外となった他の画素の信号として、対象領域内の当該一の画素の信号を雑音除去処理に供させるので、デジタル画像の端部に対象領域が設定されることで他の画素の一部が仮想的にデジタル画像外となった場合でも、それ以外の場合と同様の雑音除去効果を有する雑音除去処理を行うことができる。

【発明の効果】

【0025】

本発明によれば、走査線の数に対応した数の信号記憶用の記憶手段を備える雑音除去装置の対象領域における走査線上の画素数が当該走査線に垂直な方向の画素数より大きいので、走査線上の画素数と走査線に垂直な方向の画素数とが同数の場合に比して、対象領域に含まれる画素数を雑音除去処理用に十分確保しつつ、記憶手段の数を低減させることができる。

【0026】

従って、雑音除去装置としての雑音除去処理の能力を担保しつつ、雑音除去装置としてのハードウェア的な規模を縮小することができる。

【図面の簡単な説明】

【0027】

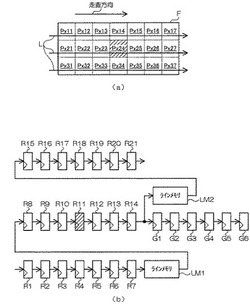

【図1】本発明の原理を説明する図であり、(a)は本発明に係るフィルタ対象領域とデジタル画像の走査方向との関係を例示する図であり、(b)は図1(a)に例示したフィルタ対象領域に対応するレジスタ及びラインメモリの構成及び動作を例示する図である。

【図2】第1実施形態に係る雑音除去フィルタを示す図であり、(a)は当該雑音除去フィルタの概要構成を示すブロック図であり、(b)は当該雑音除去フィルタにおける雑音除去処理を示すフローチャートである。

【図3】第1実施形態に係る雑音除去処理を示す図である。

【図4】第2実施形態に係るフィルタ対象領域の形状等を示す図であり、(a)は当該フィルタ対象領域の形状を例示する図であり、(b)は当該形状のフィルタ対象領域に対応するレジスタ及びラインメモリの概要構成及び動作を例示する図である。

【図5】第2実施形態に係るフィルタ対象領域の他の例を示す図であり、(a)は当該フィルタ対象領域を示す図であり、(b)は当該他の例としての各画素に対応するフィルタ係数の値の分布の第一例を示す図であり、(c)は当該フィルタ係数の値の分布の第二例を示す図であり、(d)は当該フィルタ係数の値の分布の第三例を示す図であり、(e)は当該フィルタ係数の値の分布の第四例を示す図である。

【図6】第2実施形態に係るフィルタ対象領域を更に他の例を示す図であり、(a)は当該フィルタ対象領域の形状の第五例を示す図であり、(b)は当該フィルタ対象領域の形状の第六例を示す図であり、(c)は当該フィルタ対象領域の形状の第七例を示す図である。

【図7】第3実施形態に係る端画素処理を示す図であり、(a)は第3実施形態に係るデジタル画像とフィルタ対象領域との関係を例示する図であり、(b)は第3実施形態に係る雑音除去フィルタの概要構成を示すブロック図である。

【図8】第3実施形態に係る端画素処理の第一例を示す図であり、(a)は当該端画素処理の一例を示す図であり、(b)は当該端画素処理の他の一例を示す図である。

【図9】第3実施形態に係る端画素処理の第二例を示す図であり、(a)は当該端画素処理の一例を示す図であり、(b)は当該端画素処理の他の一例を示す図である。

【発明を実施するための形態】

【0028】

次に、本発明を実施するための形態について、図面に基づいて説明する。なお、以下に説明する実施形態は、複数の画素からなるデジタル画像に含まれ雑音や歪みを除去する雑音除去フィルタに対して本発明を適用した場合の実施形態である。また本発明に係るデジタル画像は、ラスタスキャン方式により走査されるデジタル画像である。更に以下の説明では、先に述べた背景技術において説明済みの概念等については、同様の名称等を用いる。

【0029】

(I)本発明の原理

初めに、具体的な実施形態を説明する前に、本発明に係る基本的な原理について図1を用いて説明する。なお図1は、本発明の原理を説明するための図である。

【0030】

上述したように上記特許文献1に開示されている雑音除去フィルタでは、当該雑音除去フィルタとしての雑音除去効果を高めるためには、より多数の画素をフィルタ対象領域として設定する必要がある。一方上述したように、当該雑音除去処理においてフィルタ対象領域の輝度を取得する場合、一般には、ラインメモリ等が最低でも「フィルタ対象領域における走査線数−1」の数だけ必要となる。他方、上記特許文献1に開示されている雑音除去フィルタとしてのε−分離非線形デジタルフィルタでは、フィルタ対象領域全体としての形状が上記(1)の処理において述べたような正方形であることは必須の要件ではなく、正方形以外の全体形状を有するフィルタ対象領域を用いる場合でも、ε−分離非線形デジタルフィルタとして効果的な雑音除去処理を行うことが可能であるとされている。

【0031】

そこで本発明では、雑音除去フィルタとしての雑音除去処理の能力を担保しつつハードウェア的な規模を縮小させるべく、図1(a)に例示されるように、フィルタ対象領域Fが、当該フィルタ対象領域Fにおける走査線Lの方向に長い形状とされる。より具体的に本発明に係るフィルタ対象領域Fでは、フィルタ対象領域Fにおいて走査線Lに沿って配置される画素Pxの数が、フィルタ対象領域Fにおいて当該走査線Lに垂直な方向に配置される画素Pxの数よりも大きくなっている。具体的には、例えば図1(a)に例示する場合、走査線Lに沿って配置される画素Pxとは、画素Px11乃至画素Px17、画素Px21乃至画素Px27、又は画素Px31乃至画素Px37のいずれかであるから、その数は「7」である。これに対して、走査線Lに垂直な方向に配置される画素Pxの数は「3」となっており、前者の方が後者よりも大きい。

【0032】

ここで、上記処理(1)及び上記処理(2)の処理を本発明に係るフィルタ対象領域Fに対して実行するために必要なメモリ部の構成について、図1(b)を用いて例示しつつ説明する。上記処理(1)及び上記処理(2)を図1(a)に例示する21個の画素Pxからなるフィルタ対象領域Fを対象として実行する場合、各画素Pxの輝度は、図1(b)に例示するレジスタR1乃至R21に、メモリクロックごとに順次転送されて保持される。このとき、レジスタR1乃至レジスタR7がフィルタ対象領域Fの例えば画素Px11乃至画素Px17に対応し、レジスタR8乃至レジスタR14がフィルタ対象領域Fの例えば画素Px21乃至画素Px27に対応し、レジスタR15乃至レジスタR21がフィルタ対象領域Fの例えば画素Px31乃至画素Px37に対応している。ここで、レジスタR1からレジスタR7まで転送された各画素Pxの輝度はラインメモリLM1に一時的に保持されて上記処理(1)乃至処理(3)に供され、またレジスタR8からレジスタR14まで転送された各画素Pxの輝度はラインメモリLM2に一時的に保持されて上記処理(1)乃至処理(3)に供され、更にレジスタR15からレジスタR21まで転送された各画素Pxの輝度はそのまま上記処理(1)乃至処理(3)に供される。なお、図1(b)に記載されたレジスタG1乃至レジスタG6は、上記処理(1)から処理(5)が完了するまで、上記処理(1)において取得された中心画素Px24の輝度を順次転送しつつ保持しておき、その後の処理(6)に供させる為のレジスタである。

【0033】

図1(b)から明らかなように、本発明に係るフィルタ対象領域Fを用いた雑音除去処理では、例えば3画素×3画素の画素Pxからなる正方形のフィルタ対象領域に対して、同じラインメモリの数(即ち2個)を維持しつつも、フィルタ対象領域Fを構成する画素Pxを21個と倍以上とすることができる。よってこの場合、ラインメモリの数を同じとしつつもフィルタ対象領域Fを構成する画素Pxの数を多くすることができ、結果として、ラインメモリの数を同じとしつつもフィルタ対象領域Fを用いた雑音除去処理の効果を著しく向上させることができるのである。このことは即ち、同じ雑音除去処理であれば、雑音除去フィルタとしてのラインメモリの数を減らせることとなり、結果として、雑音除去フィルタとしてのハードウェア的な規模を縮小することにもなるのである。

【0034】

(II)第1実施形態

次に、上述した原理に基づく本発明に係る第1実施形態について、図2及び図3を用いて説明する。なお図2は第1実施形態に係る雑音除去フィルタを示す図であり、図3は第1実施形態に係る雑音除去処理を示す図である。また第1実施形態に係るフィルタ対象領域Fは、図1(a)に例示したフィルタ対象領域Fと同様の形状を有するフィルタ対象領域F1とされている。

【0035】

図2(a)に示すように、第1実施形態に係る雑音除去フィルタS1は、メモリ部1と、検出手段の一例としての差分演算部2と、比較手段の一例及び特定手段の一例としての閾値判定部3と、乗算手段の一例、加算手段の一例及び制御手段の一例としての演算部4と、雑音閾値設定部5と、フィルタ係数設定部6と、操作部7と、により構成されている。図1(b)において説明したレジスタR1乃至レジスタR21、加算用記憶手段の一例としてのレジスタG1乃至レジスタG6並びに記憶手段の一例としてのラインメモリLM1及びラインメモリLM2は、メモリ部1内に含まれている。

【0036】

この構成においてメモリ部1には、図2(a)及び図3に示すように、第1実施形態に係るフィルタ対象領域F1を含むデジタル画像に相当する画像信号Sinが入力される。

【0037】

この時、第1実施形態に係るフィルタ対象領域F1に含ませるべき画素Pxの数や、第1実施形態に係る形状(具体的には、図1(a)に例示した、走査線Lに沿って配置される画素Pxの数が、フィルタ対象領域F1において当該走査線Lに垂直な方向に配置される画素Pxの数よりも大きい形状)を有するフィルタ対象領域F1の具体的な当該形状(縦横それぞれの画素Pxの具体的な数)は、例えばメモリ部1に含まれる上記レジスタRの数や、上記差分演算部2、閾値判定部3及び演算部5それぞれにおける実際の処理速度等に基づいて使用者が予め固定的に設定し、その形状を示す情報を雑音除去フィルタS1内に予め記憶させておくのが好適である。なおこれ以外に例えば、メモリ部1に含まれる上記レジスタRの数や上記差分演算部2等における実際の処理速度等において許容され得る範囲内において、複数種類のフィルタ対象領域F1の形状のパターンを予め雑音除去フィルタS1内に記憶させておき、これらを、例えばデジタル画像の内容に応じて、使用者の手動により又は自動的に切り換えられるように構成することもできる。

【0038】

そしてメモリ部1は、上記各レジスタR、レジスタG及びラインメモリLMを順次用いることにより、画像信号Sinの中からデジタル画像におけるフィルタ対象領域F1を構成する各画素Px(中心画素Px24を含む)の輝度を取得して、一時的に保持する。これらの処理は上記(1)及び上記(2)にそれぞれ記載された処理に相当する(図2(b)ステップS1)。そしてメモリ部1は、保持している各画素Pxの輝度を示す輝度情報を、メモリ信号Smとして差分演算部2に出力する。なお図3においては、例えば画素Px11の輝度は「(P11)」と表記されている。

【0039】

次に差分演算部2は、中心画素Px24を含むフィルタ対象領域F内の各画素Pxの輝度を示す上記輝度情報をメモリ部1から取得し、上記(3)に相当する処理を実行する。即ち差分演算部2は、図3に模式的に示すように、中心画素Px24の輝度と、各画素Pxの輝度Pと、の差分Δを、画素Pxごとに検出し、その検出結果を画素Pxごとに差分信号Sdifとして閾値判定部3に出力する。なお図3においては、例えば画素Px11の輝度と中心画素Px24の輝度との差分Δは「Δ11」と表記されている。具体的に例えば、画素Px11について差分演算部2は、その輝度P11と、中心画素Px24の輝度P24と、差分Δ11を算出し、差分信号Sdifとして閾値判定部3に出力する。また例えば画素Px34について差分演算部2は、その輝度P34と、中心画素Px24の輝度P24と、差分Δ34を算出し、差分信号Sdifとして閾値判定部3に出力する。以上の処理を差分演算部2は、図3に示すようにフィルタ対象領域F内の全ての画素Pxについて実行する。

【0040】

そしてフィルタ係数設定部6は、例えば予め設定されているフィルタ係数を、フィルタ係数信号Scとして画素Pxごとに演算部4に出力する(図2(b)ステップS2)。なお図3においては、例えば画素Px11に対応するフィルタ係数は「C11」と表記されている。

【0041】

一方使用者は、例えばメモリ部1に入力される前の画像信号Sinに相当するデジタル画像を前もって図示しないディスプレイ上に表示させる等の処理により、そのデジタル画像の内容を把握し、上記(4)の雑音判定処理に係る雑音閾値を設定する操作を操作部7において実行する。この操作に対応する操作信号Sotは、操作部7から雑音閾値設定部5に出力される。

【0042】

これにより雑音閾値設定部5は、当該操作信号Sotに基づいて、上記(4)に相当する雑音判定処理に係る雑音閾値を設定し、閾値信号Sthとして閾値判定部3に出力する。これにより閾値判定部3は、上記(4)に相当する雑音判定処理を実行する(図2(b)ステップS3)。即ち閾値判定部3は、差分信号Sdifとして出力されてくる画素ごとの差分Δと、閾値信号Sthとして入力されてくる閾値と、を比較し、例えば閾値以上の値の差分Δに対応する画素Pxを第1実施形態に係る雑音除去処理の対象画素から除外する(図2(b)ステップS3;非雑音)。一方閾値判定部3は、例えば当該閾値未満の値の差分Δに対応する画素Pxを第1実施形態に係る雑音除去処理の対象画素とする(図2(b)ステップS3;雑音)。そして閾値判定部3は、当該対象画素とされた画素Pxについては対象画素であることを示すフラグ等を付加し、各画素Pxに対応する差分Δを、画素Pxごとに画素信号Spxとして演算部4に出力する。

【0043】

次に演算部4は、フィルタ係数信号Scとしてフィルタ係数設定部6から出力されてくるフィルタ係数Cと、上記画素信号Spxとして閾値判定部3から出力されてくる差分Δと、を用いて、上記(5)に対応する乗算/加算処理及び上記(6)に相当する加算処理を実行する(図2(b)ステップS4)。即ち演算部4は、先ず画素信号Spxとして閾値判定部3から出力されてくる差分Δのうち、対象画素であることを示すフラグ等が付加されている画素Px以外の全ての他の画素Pxに対応する差分Δ又は当該全ての他の画素Pxに対応するフィルタ係数Cのいずれか一方の値をゼロとする。次に演算部4は、図3に破線で示すように、各画素Pxに対応する差分Δとフィルタ係数Cとを画素Pxごとに乗算し、画素Pxごとの乗算結果を全て加算する。このとき演算部4は、上記背景技術とは異なり、フィルタ係数信号Scとしてフィルタ係数設定部6から出力されてくるフィルタ係数Cを用いて乗算処理を行う。この場合、雑音除去処理の対象画素である画素Px以外の全ての他の画素Pxについては、当該他の画素Pxに対応する差分Δ又はフィルタ係数Cのいずれか一方の値がゼロとされているので、結果として雑音除去処理の対象画素である画素Pxについてのみ、上記乗算結果が有意となる。

【0044】

そして演算部4は、図3に一点鎖線で示すように、全ての画素Pxについての加算結果に対して中心画素Px24の輝度を加算し、その中心画素Px24についての(換言すれば、中心画素Px24を中心とするフィルタ対象領域Fについての)第1実施形態に係る雑音除去処理後の出力信号Soutとする。なおこのとき加算される中心画素Px24の輝度は、上記ステップS1の処理により取得され、図1(b)に示すレジスタG1乃至レジスタG6を上記メモリクロックのタイミングで順次転送されつつ保持されている輝度である。この中心画素Px24の輝度は、上記ステップS1の処理により取得された後は、上記ステップS2乃至ステップS4として上記(3)から上記(5)までの処理が完了するまで、レジスタG1乃至レジスタG6により保持されることとなる。

【0045】

その後演算部4は、図2(b)に示すステップS1からステップS4の処理が、デジタル画像内の全ての画素Pxを中心画素として(換言すればデジタル画像内の全てのフィルタ対象領域Fについて)行われたか否かを確認する(図2(b)ステップS5)。ステップS5の確認において全ての画素Pxについて図2(b)に示すステップS1からステップS4の処理が完了している場合(図2(b)ステップS5;YES)、演算部4は、画像信号Sinとして入力されたデジタル画像内の全ての画素に対しての雑音除去処理が終了したとして、全てのフィルタ対象領域Fについての上記出力信号Soutを当該フィルタ対象領域Fが含まれるデジタル画像に対応する出力信号Soutとして出力し、第1実施形態に係る雑音除去処理を終了する。

【0046】

一方ステップS5の確認において図2(b)に示すステップS1からステップS4の処理が完了していない画素Pxがある場合(図2(b)ステップS5;NO)、演算部4は、当該完了していない新たな画素Pxを中心画素とした図2(b)に示すステップS1からステップS4の処理を実行すべく、当該ステップS1に戻る(ステップS6)。

【0047】

なお、上述してきたステップS1乃至ステップS6の処理は、一のフィルタ対象領域Fについての処理である。一のフィルタ対象領域Fの全てについてステップS1乃至ステップS6の処理が終了した後は、中心画素Px24に隣接する画素Px(具体的には、図1(a)に例示する画素Px13、画素Px14、画素Px15、画素Px23、画素Px25、画素Px33、画素Px34又は画素Px35のいずれか)を中心画素とした図1(a)に示す形状の新たなフィルタ対象領域Fがメモリ部1及び差分演算部2において設定され、当該新たなフィルタ対象領域Fに対して上記ステップS1乃至ステップS6の処理が改めて実行される。そして、一のデジタル画像内に設定され得る全てのフィルタ対象領域FについてステップS1乃至ステップS6の処理が全て終了することで、当該一のデジタル画像についての第1実施形態に係る雑音除去処理が終了する。

【0048】

以上説明したように、第1実施形態の雑音除去フィルタS1の構成によれば、デジタル画像の走査線Lの数に対応した数の輝度保持用のラインメモリLMを備える雑音除去フィルタS1において、フィルタ対象領域Fにおける走査線L上の画素Pxの数が、走査線Lに垂直な方向の画素Pxの数より大きいので、走査線L上の画素数と走査線Lに垂直な方向の画素数とが同数である従来の場合に比して、フィルタ対象領域Fに含まれる画素数を雑音除去処理用に十分確保しつつ、ラインメモリLMの数を低減させることができる。

【0049】

(III)第2実施形態

次に、本発明に係る他の実施形態である第2実施形態について、図4乃至図6を用いて説明する。なお図4は第2実施形態に係る雑音除去フィルタにおけるフィルタ対象領域の形状等を示す図であり、図5は第2実施形態に係るフィルタ対象領域の他の例を示す図であり、図6は第2実施形態に係るフィルタ対象領域を更に他の例を示す図である。図5(b)乃至図5(e)においては、各画素Pxにそれぞれ対応するフィルタ係数の値を( )書きの数字で示している。また第2実施形態に係る雑音除去フィルタを説明するに当たり、第1実施形態に係る雑音除去フィルタS1における部材及び処理と同一の部材及び処理については、同一の部材番号及びステップ番号を使用して、細部の説明は省略する。

【0050】

第1実施形態に係る雑音除去フィルタS1では、図1(a)及び図3に示すように、雑音除去処理に係るフィルタ対象領域Fとして、走査線Lに沿って配置される画素Pxの数がフィルタ対象領域Fにおいて当該走査線Lに垂直な方向に配置される画素Pxの数よりも大きい長方形の形状を有するフィルタ対象領域F1を用いた。これに対して第2実施形態及び後述する第3実施形態及び第4実施形態では、図4(a)に例示するように、フィルタ対象領域Fとして、その時の中心画素を通る走査線L上に並ぶ画素Pxの数が、他の走査線L上に並ぶ画素Pxの数よりも大きいフィルタ対象領域F2を用いる。なお第2実施形態及び第3実施形態に係るフィルタ対象領域F2においても、走査線Lに沿って配置される画素Pxの数がフィルタ対象領域Fにおいて当該走査線Lに垂直な方向に配置される画素Pxの数よりも大きいことに変わりはない。第2実施形態に係る雑音除去フィルタでは、上述した形状のフィルタ対象領域F2を用いることで、図1(b)にも示したレジスタG(即ち中心画素の輝度を転送しつつ保持するレジスタG)をも他のレジスタRと共に有効に活用して、ラインメモリLMの数を減らしつつ、フィルタ対象領域Fに含まれる画素Pxの数を更に増やすのである。

【0051】

即ち図4(a)に例示するように、第2実施形態に係る雑音除去フィルタでは、図4(b)に示すレジスタGの数(五つ)だけ、フィルタ対象領域F2の中心画素Px2Aを通る走査線L上に並ぶ画素Pxが、走査線Lの走査方向に画素Px2F乃至画素Px2Jとして増やされている。またこれら画素Px2F乃至画素Px2Jが増やされていることとの均衡から、中心画素Px2Aを通る走査線L上に並ぶ画素Pxが、走査線Lの走査方向と反対の方向にも、画素Px21乃至画素Px25として増やされている。

【0052】

以上のような第2実施形態に係るフィルタ対象領域F2を用いることで、これに対応するレジスタR及びレジスタG並びにラインメモリLM1及びラインメモリLM2の構成は、図4(b)に示される構成となり、レジスタR1乃至レジスタR32の合計32個のレジスタRに加えて5個のレジスタGを用いて、各画素Pxの輝度を順次転送しつつ保持する。このとき、レジスタR10乃至レジスタR23と、レジスタG1乃至レジスタG5と、が、中心画素Px2Aの輝度を含むフィルタ対象領域F2における中央の行の画素Px21乃至画素Px2Jの輝度を順保持することになる。なおレジスタG1乃至レジスタG5は、その本来の機能として中心画素Px2Aの輝度を順次転送しつつ保持するが、中心画素Px2Aの輝度の保持とその他の画素Pxの輝度の保持とではそのタイミングが異なるため、レジスタG1乃至レジスタG5のうち、空いているレジスタGを中心画素Px2Aの輝度の保持に振り向けることができるのである。

【0053】

第2実施形態に係る雑音除去フィルタは、以上説明した形状のフィルタ対象領域F2を用いて、第1実施形態に係る雑音除去フィルタS1と同様の雑音除去処理(フィルタ対象領域Fのみが第2実施形態に係るフィルタ対象領域F2とされる雑音除去処理)をデジタル画像に対して実行することになる。

【0054】

以上説明したように、第2実施形態に係る雑音除去フィルタの動作によれば、第1実施形態に係る雑音除去フィルタS1の動作による効果に加えて、フィルタ対象領域Fに含まれる中心画素Px24を通る走査線L上の画素Pxの数が、フィルタ対象領域Fにおける他の走査線L上の画素Pxの数より大きいので、より効果的な雑音除去処理を実行しつつ、ラインメモリLMの数を低減させることができる。

【0055】

また、上記(6)の加算処理のために中心画素Px2Aの輝度を保持するレジスタGが各画素Pxの輝度を保持するレジスタとしても用いられるので、ラインメモリLMの数を低減させつつ、フィルタ対象領域F2を構成する画素Pxの数を増加させて雑音除去効果を向上させることができる。

【0056】

なお、第2実施形態に係る雑音除去フィルタの演算部4において実行される上記(5)に対応する乗算処理において、各画素Pxに対応する差分Δとフィルタ係数Cとを画素Pxごとに乗算する場合(図3参照)、例えば図5(a)に例示するフィルタ対象領域F2の各画素Pxに対応するフィルタ係数Cを画素Pxごとに区別して、例えば図5(b)に例示するようにその値を全て「1」としたときには、フィルタ対象領域Fを構成する画素Pxの数(図5に例示する場合は37個)と同数の乗算器が演算部4内に必要となる。しかしながら図5(c)乃至図5(e)に例示したように、フィルタ対象領域F2において中心画素Px2Aについて対称の位置にある画素Px同士を同一の値を有するフィルタ係数Cとする場合には、値が同一のフィルタ係数Cに対応する画素Pxについての差分Δを全て加算した後に当該同一のフィルタ係数Cに乗算すれば、結果として、画素Pxごとに逐一乗算をした場合と同じ乗算結果が得られる。具体的に例えば、図5(c)に例示するように、中心画素Px2Aを含めてその上下左右に隣接する5個の画素Px15、画素Px29、画素Px2B及び画素Px35にそれぞれ対応するフィルタ係数を例えば「8」とし、中心画素Px2Aに対して更に外側にある8個の画素Px14、画素Px16、画素Px27、画素Px28、画素Px2C、画素Px2D、画素Px34及び画素Px26にそれぞれ対応するフィルタ係数を例えば「6」とする。更に、画素Px12、画素Px13、画素Px17、画素Px18、画素Px25、画素Px26、画素Px2E、画素Px2F、画素Px32、画素Px33、画素Px37及び画素Px38にそれぞれ対応するフィルタ係数を例えば「4」とし、画素Px11、画素Px19、画素Px23、画素Px24、画素Px2G、画素Px2H、画素Px31及び画素Px39にそれぞれ対応するフィルタ係数を例えば「2」とし、画素Px21、画素Px22、画素Px2I及び画素Px2Jにそれぞれ対応するフィルタ係数を例えば「1」とする。また図5(d)及び図5(e)に例示するように、同じ大文字アルファベットで示される画素Pxに対応するフィルタ係数を同一とするように構成することもできる。ここで、図5(c)に例示する場合、フィルタ係数Cとしては中心画素Px2Aに対応するフィルタ係数C2Aを入れて合計5種類であるので、乗算器も5個で済む。また同様に図5(d)に例示する場合(二つずつの画素Pxに対応するフィルタ係数を同一とする場合)には、フィルタ係数Cとしては合計19種類必要であるが、中心画素Px2Aに対応する差分Δ2Aは当然にゼロであるのでこれを考慮すると、演算部4内の乗算器は更に18個まで減らすことができることになる。更に図5(e)に例示する場合(四つずつの画素Pxに対応するフィルタ係数を同一とする場合)には、同様にフィルタ係数Cとしては合計10種類であるが、乗算器は9個で足りることとなる。

【0057】

以上図5を用いて説明したように、中心画素Px2Aについて対称の位置にある画素Pxについてフィルタ係数Cの値を同一とすれば、演算部4としての乗算器の数を大幅に削減することができ、雑音除去フィルタとしての構成を大幅に簡略化することができる。

【0058】

なお第2実施形態に係るフィルタ対象領域F2の形状は、更に種々の変形が可能である。

【0059】

即ち例えば図6(a)に示すように、上から一行目を画素Px11乃至画素Px17の7個の画素Pxにより構成し、中心画素Px28を含む中央の一行を画素Px21乃至画素Px2Fの15個の画素Pxにより構成し、更に上から三行目を画素Px31乃至画素Px37の7個の画素Pxにより構成したフィルタ対象領域F3を、第2実施形態に係る雑音除去処理に用いることが可能である。この場合の各画素Pxからの輝度の取得及び保持についての各レジスタR及びレジスタGの動作は、上記した第2実施形態に係る雑音除去フィルタと同様となる。図6(a)に例示する合計29個の画素Pxを含むフィルタ対象領域F3を用いた雑音除去処理では、当該雑音除去処理に必要なラインメモリLMの数は、図4に例示した場合と同様に2個である。なお、図6(a)に例示するフィルタ対象領域F3を用いた雑音除去処理における雑音除去能力と同等の雑音除去能力を有するフィルタ対象領域を背景技術と同様の正方形に画素Pxが配置されたフィルタ対象領域で実現しようとすると、例えば5画素×5画素の合計25個の画素Pxからなるフィルタ対象領域が必要となり、この場合に必要となるラインメモリLMの数は4個となってフィルタ対象領域F3の場合よりも多くなる。

【0060】

また例えば図6(b)に示すように、上から一行目を画素Px11乃至画素Px15の5個の画素Pxにより構成し、上から二行目を画素Px21乃至画素Px29の9個の画素Pxにより構成し、中心画素Px39を含む中央の一行を画素Px31乃至画素Px3Hの17個の画素Pxにより構成し、上から四行目を画素Px41乃至画素Px49の9個の画素Pxにより構成し、更に上から五行目を画素Px51乃至画素Px55の5個の画素Pxにより構成したフィルタ対象領域F4を、第2実施形態に係る雑音除去処理に用いることが可能である。この場合の各画素Pxからの輝度の取得及び保持についての各レジスタR及びレジスタGの動作も、上記した第2実施形態に係る雑音除去フィルタと同様となる。図6(b)に例示する合計45個の画素Pxを含むフィルタ対象領域F4を用いた雑音除去処理では、当該雑音除去処理に必要なラインメモリLMの数は4個となる。そして、図6(b)に例示するフィルタ対象領域F4を用いた雑音除去処理における雑音除去能力と同等の雑音除去能力を有するフィルタ対象領域を背景技術と同様の正方形に画素Pxが配置されたフィルタ対象領域で実現しようとすると、例えば7画素×7画素の合計49個の画素Pxからなるフィルタ対象領域が必要となり、この場合に必要となるラインメモリLMの数は6個となってフィルタ対象領域F4の場合よりも多くなる。

【0061】

最後に例えば図6(c)に示すように、上から一行目を画素Px11乃至画素Px19の9個の画素Pxにより構成し、上から二行目を画素Px21乃至画素Px29の9個の画素Pxにより構成し、中心画素Px39を含む中央の一行を画素Px31乃至画素Px3Hの17個の画素Pxにより構成し、上から四行目を画素Px41乃至画素Px49の9個の画素Pxにより構成し、更に上から五行目を画素Px51乃至画素Px59の9個の画素Pxにより構成したフィルタ対象領域F5を、第2実施形態に係る雑音除去処理に用いることが可能である。図6(c)に例示する合計53個の画素Pxを含むフィルタ対象領域F4を用いた雑音除去処理でも、当該雑音除去処理に必要なラインメモリLMの数は4個となる。そして、図6(c)に例示するフィルタ対象領域F5を用いた雑音除去処理における雑音除去能力と同等の雑音除去能力を有するフィルタ対象領域を背景技術と同様の正方形に画素Pxが配置されたフィルタ対象領域で実現しようとすると、最低でも7画素×7画素の合計49個の画素Pxからなるフィルタ対象領域が必要となり、この場合に必要となるラインメモリLMの数は6個となってフィルタ対象領域F5の場合よりも多くなる。

【0062】

このように、第2実施形態に係るフィルタ対象領域F2乃至フィルタ対象領域F5のいずれを用いる場合でも、背景技術に比してラインメモリLMの数を低減し、雑音除去フィルタとしての構成を大幅に簡略化することができる。

【0063】

(IV)第3実施形態

次に、本発明に係る他の実施形態である第3実施形態について、図7乃至図9を用いて説明する。なお図7乃至図9は第3実施形態に係る端画素処理を示す図である。なお図8及び図9においては、例えば画素Px28の輝度は「(P28)」と表記されている。更に第3実施形態に係る雑音除去フィルタを説明するに当たり、第1実施形態に係る雑音除去フィルタS1における部材及び処理と同一の部材及び処理については、同一の部材番号及びステップ番号を使用して、細部の説明は省略する。

【0064】

上述してきた第2実施形態では、フィルタ対象領域Fの形状が単純な長方形ではない。よって、図7(a)に例示するデジタル画像Gの端部にフィルタ対象領域Fが設定される場合、そのデジタル画像Gの端部の形状とフィルタ対象領域Fの外形とが一致せず、図7(a)に例示するようにフィルタ対象領域Fを構成する画素Pxの一部が仮想的にデジタル画像Gの外にはみ出すことがある。例えば図7(a)に示すデジタル画像Gの左上に設定されたフィルタ対象領域Fでは、画素Px11乃至画素Px17、画素Px21乃至画素Px27及び画素Px31乃至画素Px33が仮想的にデジタル画像Gの外にはみ出している。また当該デジタル画像Gの右辺に設定されたフィルタ対象領域Fでは、画素Px17、画素Px2B乃至画素Px2F及び画素Px37が仮想的にデジタル画像Gの外にはみ出しており、更に当該デジタル画像Gの下辺に設定されたフィルタ対象領域Fでは、画素Px31乃至画素Px37を含む一行分が仮想的にデジタル画像Gの外にはみ出している。なおこれら三つのフィルタ対象領域Fにおいても、中心画素Px28は全てデジタル画像G内にある。

【0065】

図7(a)に例示するように一部の画素Pxがデジタル画像Gの外にはみ出すように設定されたフィルタ対象領域Fであっても、それを用いた雑音除去処理では、当該はみ出した画素Pxについても(実際には存在しない)輝度を取得して上記(1)乃至上記(3)の処理に供させることが必要である。

【0066】

そこで第3実施形態に係る雑音除去フィルタにおいては、図7(a)に例示したように一部の画素Pxがデジタル画像Gから仮想的にはみ出す場合の端画素処理を実行して雑音除去処理としての能力を維持する。

【0067】

即ち図7(b)に示すように、第3実施形態に係る雑音除去フィルタS3は、第1実施形態に係る雑音除去フィルタS1に対して、画素処理手段の一例としての端画素判定部10を備えている。この構成において端画素判定部10は、画像信号Sinに基づき、フィルタ対象領域Fとデジタル画像Gとを比較し、フィルタ対象領域Fを構成する画素Pxのうち、デジタル画像Gの外にはみ出す画素Pxを検出する。これにより端画素判定部10は、当該検出結果を端画素信号Segとして差分演算部2に出力する。

【0068】

これにより差分演算部2は、第3実施形態に係る端画素処理の第一例として、デジタル画像Gの外にはみ出した画素Pxの輝度として、デジタル画像Gの外縁を対称軸として当該はみ出した画素Pxに対して対称の位置にあるフィルタ対象領域F内の画素Pxの輝度を用いて上記(3)に相当する処理を実行する。

【0069】

具体的に例えば、図8(a)に例示する場合において差分演算部2は、図8(a)に例示するように、一点鎖線で外縁が示されているデジタル画像Gの外にはみ出した画素Px25の輝度としてデジタル画像Gの左辺を対称軸として画素Px25に対して対称の位置にあるフィルタ対象領域F内の画素Px2Aの輝度(P2A)を用いて、上記(3)に相当する処理を実行する(図8(a)破線参照)。また例えば、図8(a)に例示する場合において差分演算部2は、図8(a)に例示するように、デジタル画像Gの外にはみ出した画素Px17の輝度としてデジタル画像Gの上辺を対称軸として画素Px17に対して対称の位置にあるフィルタ対象領域F内の画素Px2Bの輝度(P2B)を用いて、上記(3)に相当する処理を実行する(図8(a)破線参照)。更に例えば、図8(b)に例示する場合において差分演算部2は、図8(b)に例示するように、デジタル画像Gの外にはみ出した画素Px22の輝度としてデジタル画像Gの左辺を対称軸として画素Px22に対して対称の位置にあるフィルタ対象領域F内の画素Px29の輝度(P29)を用いて、上記(3)に相当する処理を実行する(図8(b)破線参照)。

【0070】

また差分演算部2は、第3実施形態に係る端画素処理の第二例として、デジタル画像Gの外にはみ出した全ての画素Pxの輝度として、フィルタ対象領域F内の中心画素Px28の輝度(P28)を用いて上記(3)に相当する処理を実行する。

【0071】

具体的には、図9(a)及び図9(b)に例示するいずれの場合も、デジタル画像Gの外にはみ出した全ての画素Pxの輝度としてフィルタ対象領域F内の中心画素Px28の輝度(P28)を用いて、上記(3)に相当する処理を実行する。この図9に例示する場合には、差分演算部2における上記(3)に相当する処理により、デジタル画像Gの外にはみ出した全ての画素Pxに対応する差分Δの値がゼロとなり、結果として、これらはみ出した画素Pxは第3実施形態に係る雑音除去処理の対象外となる。

【0072】

なお、上述した第3実施形態に係る端画素処理の第一例及び第二例において、デジタル画像Gの外にはみ出していないフィルタ対象領域F内の画素Pxについては、上記第1実施形態又は第2実施形態に係る雑音除去処理と同様の雑音除去処理が実行される。

【0073】

以上説明したように、第3実施形態に係る端画素処理の第一例及び第二例によれば、デジタル画像Gの端部にフィルタ対象領域Fが設定されることでそれを構成する画素Pxの一部が仮想的にデジタル画像Gの外となった場合でも、それ以外の場合と同様の雑音除去効果を有する雑音除去処理を行うことができる。

【0074】

なお、上述した各実施形態に係る雑音除去フィルタSは、デジタル画像Gを記録媒体に記録する情報記録装置において、当該デジタル画像Gに対する符号化処理の終了後且つ当該記録媒体への記録処理前の段階に挿入して備えさせるように構成することが可能である。なお当該記録媒体としては、例えば光ディスクやハードディスク等が挙げられる。更に当該雑音除去フィルタSは、デジタル画像Gを記録済みの記録媒体から当該デジタル画像Gを再生する情報再生装置において、当該デジタル画像Gに対する復号化処理の前又は後の段階に備えさせるように構成することも可能である。

【0075】

更にまた、各実施形態に係るメモリ部1、差分演算部2、閾値判定部3、演算部4、雑音閾値設定部5及びフィルタ係数設定部6等の機能に対応するプログラムを、例えば光ディスク等の記録媒体に記録しておき、或いはインターネット等のネットワークから取得して記録しておき、これらを読み出して汎用のマイクロコンピュータ等により実行させることにより、当該マイクロコンピュータ等を、各実施形態に係るメモリ部1、差分演算部2、閾値判定部3、演算部4、雑音閾値設定部5及びフィルタ係数設定部6等として機能させることも可能である。

【産業上の利用可能性】

【0076】

以上夫々説明したように、本発明は雑音除去装置の分野に利用することが可能であり、特にデジタル画像に含まれる雑音を除去する雑音除去装置の分野に適用すれば特に顕著な効果が得られる。

【符号の説明】

【0077】

1 メモリ部

2 差分演算部

3 閾値判定部

4 演算部

5 雑音閾値設定部

6 フィルタ係数設定部

10 端画素判定部

F、F1、F2、F3、F4、F5 フィルタ対象領域

L 走査線

R1〜R32、G1〜G6 レジスタ

LM1、LM2 ラインメモリ

S1、S3 雑音除去フィルタ

Sin 画像信号

Sm メモリ信号

Sdif 差分信号

Sot 操作信号

Sc フィルタ係数信号

Sth 閾値信号

Spx 画素信号

Sout 出力信号

G デジタル画像

Seg 端画素信号

【技術分野】

【0001】

本発明は、雑音除去装置の技術分野に属する。より詳細には、複数の画素により形成されるデジタル画像に含まれる雑音を除去する雑音除去装置の技術分野に属する。

【背景技術】

【0002】

近年、例えばデジタルカメラ等に内蔵される撮像素子(例えば、CCD(Charge-Coupled Device)等の撮像素子)においては、高密度化される等の高性能化が著しい。そしてこれに伴い、撮像素子から出力される撮像信号又は当該撮像信号を処理して得られる画像信号に含まれる雑音(ノイズ)の低減又は除去のための技術の開発も、盛んに行われている。

【0003】

ここで、上述した撮像素子から出力される撮像信号に含まれる雑音には、例えば、その撮像素子の構造上の原因から原画像(動画像又は静止画像を含む。以下、同様。)を含む撮像信号に含まれることとなる雑音がある。また撮像信号を処理して得られる画像信号に含まれる雑音には、例えば、デジタル画像生成のためのブロック符号化処理が撮像信号に施されることに起因する、いわゆるブロックノイズ等がある。

【0004】

そしてこのような各種の雑音に対して、原画像の高振幅成分(即ち、その原画像に含まれている画像構成物(被写体)の輪郭の形状等)を損なうことなく、原画像内に低振幅成分として含まれる雑音や歪みを除去する手法として、例えば下記特許文献1に開示されている手法がある。なお上記歪みとは、具体的に例えば、ブロック圧縮符号化方式に対応したブロック境界における歪みや原画像内の輪郭周辺における歪みがある。また特許文献1に開示されている手法は、いわゆるε−分離非線形デジタルフィルタを用いた雑音除去フィルタである。ε−分離非線形デジタルフィルタについては、例えば下記非特許文献1に詳細に開示されている。

【0005】

ここで、ε−分離非線形デジタルフィルタによる雑音除去処理について、その概要を説明する。当該雑音除去処理では、一般には以下の(1)から(6)までの六段階の処理により、原画像としてのデジタル画像における高振幅成分を損なうことなく、低振幅成分である雑音等を除去する。この雑音除去処理は、言い換えれば、上記高振幅成分を損なうことなく、低振幅成分を平滑化する処理である(特許文献1第4図参照)。

(1)画像信号として入力されたデジタル画像のうち、複数の画素からなる正方形の領域を「フィルタ対象領域」として設定し、そのフィルタ対象領域に含まれている画素の輝度を、画素ごとに取得する。

(2)フィルタ対象領域の中心画素の輝度を示す輝度情報を、一時的に記憶する。

(3)当該記憶されている輝度情報により示される輝度と、フィルタ対象領域の中心画素以外の複数の他の画素の輝度と、の差分を、他の画素ごとに検出する。なお一般的には、処理を簡略化すべく、上記(2)において記憶された中心画素の輝度と、フィルタ対象領域内の全ての画素(中心画素を含む)の輝度と、の差分を画一的に求める。この場合、上記(2)において記憶した中心画素の輝度と、フィルタ対象領域内の全ての画素の一部としての中心画素の輝度と、の差分は、当然ながらゼロである。

(4)他の画素との上記差分を用いて、雑音除去処理の対象となる画素を判定する。当該判定処理を、以下「雑音判定処理」と称する。即ち、他の画素各々のうち、検出された差分が予め設定されている雑音閾値以上である他の画素を、当該他の画素の輝度が上記高振幅成分に属する(即ち、当該他の画素が上記輪郭の形状等を構成する)として雑音除去処理の対象画素から除外する。一方、中心画素の輝度との差分が上記雑音閾値未満である他の画素を、当該他の画素の輝度が上記低振幅成分に属する(即ち、当該他の画素に雑音等が含まれる)として雑音除去処理の対象画素とする。

(5)雑音除去処理の対象画像についての上記差分と予め設定されているフィルタ係数とを乗算する処理を、対象画像それぞれについて行い、対象画像それぞれについての乗算結果を全て加算する。この場合、対象画素の各々に乗算されるフィルタ係数は全て同一とされる。

(6)上記の加算結果を、上記(2)において記憶した輝度情報により示される中心画素の輝度に加算し、その加算結果を、当該中心画素における雑音除去後の輝度とする。

【0006】

以上説明した(1)から(6)までの六段階の処理を、デジタル画像を構成する全ての画素を順次上記中心画素として繰り返し実行することにより、当該デジタル画像についてのε−分離非線形デジタルフィルタによる雑音除去処理が実行される。このような雑音除去処理により、原画像に含まれている画像構成物(被写体)の輪郭の形状等を損なうことなく、原画像内に低振幅成分として含まれる雑音や歪みを除去することが可能となる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2000−102020号公報(第1図、第4図等)

【非特許文献】

【0008】

【非特許文献1】原島他,“ε−分離非線形ディジタルフィルタとその応用”電子通信学会論文誌A,第65巻,NO.4,pp.297−304,Apr.1982

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、特許文献1に開示されている雑音除去フィルタでは、上記した(1)から(6)までの処理により雑音除去処理を行うことから、雑音除去フィルタとしての雑音除去効果を高めるためには、より多数の画素をフィルタ対象領域として設定する必要がある。

【0010】

ここで、ハードウェア的に特許文献1に開示されている雑音除去フィルタを実現する場合、フィルタ対象領域の輝度を取得するためには、一般には、いわゆるラインメモリ又はフレームメモリが必須である。そしてこれらのメモリは、原理上、最低でも「フィルタ対象領域における走査線数−1」の数のメモリが必要となる。このとき、「フィルタ対象領域における走査線数」とは、例えばいわゆるラスタスキャン方式に基づくデジタル画像に対する雑音除去処理においては、それに含まれる上記フィルタ対象領域を通る当該スキャンに係る走査線の数をいう。

【0011】

以上のような事情から、特許文献1に開示されている雑音除去フィルタにおいて高性能な雑音除去処理を行うためには、その回路規模が飛躍的に増大してしまうという問題点があった。このような問題点は、例えば雑音除去フィルタとしての価格の高騰や、製造工程の複雑化に繋がるものであり、解決が望まれる問題点である。

【0012】

そこで本発明は、上記の問題点等に鑑みて為されたもので、その課題は、雑音除去フィルタとしての雑音除去処理の能力を担保しつつ、雑音除去フィルタとしてのハードウェア的な規模を縮小することが可能な雑音除去装置を提供することにある。

【課題を解決するための手段】

【0013】

上記の課題を解決するために、請求項1に記載の発明は、一定方向の走査線により順次走査される複数の画素により形成されるデジタル画像における一の画素の信号と、当該一の画素の周囲の複数の他の画素の信号と、を用いて、当該一の画素と当該他の画素から構成される対象領域における雑音除去処理を行う雑音除去装置であって、前記対象領域において前記走査線上に並ぶ前記画素の前記信号を記憶し、且つ前記対象領域における前記走査線の数に対応した数のラインメモリ等の記憶手段を備える雑音除去装置において、前記対象領域における前記走査線上の画素数が、当該対象領域において前記走査線に垂直な方向の画素数より大きいように構成される。

【0014】

請求項1に記載の発明によれば、走査線の数に対応した数の信号記憶用の記憶手段を備える雑音除去装置において、対象領域における走査線上の画素数が当該走査線に垂直な方向の画素数より大きいので、走査線上の画素数と走査線に垂直な方向の画素数とが同数の場合に比して、対象領域に含まれる画素数を雑音除去処理用に十分確保しつつ、記憶手段の数を低減させることができる。

【0015】

上記の課題を解決するために、請求項2に記載の発明は、請求項1に記載の雑音除去装置において、前記雑音除去装置は、前記一の画素の前記信号と、前記他の画素各々の前記信号と、差分値を、前記記憶手段を用いてそれぞれ検出する差分演算部等の検出手段と、前記検出された各差分値と閾値とをそれぞれ比較する閾値判定部等の比較手段と、前記比較手段による比較結果に基づいて前記雑音除去処理の対象とすべき前記他の画素を特定する閾値判定部等の特定手段と、特定された前記他の画素それぞれについて、前記検出された差分値に対して予め設定されたフィルタ係数を乗算する演算部等の乗算手段と、前記乗算手段による乗算結果を前記一の画素の前記信号に加算して出力する演算部等の加算手段と、前記検出手段による検出処理、前記比較手段による比較処理、前記特定手段による特定処理、前記乗算手段による乗算処理、及び前記加算手段による加算処理を、前記デジタル画像を構成する各前記画素のそれぞれを前記一の画素として、前記デジタル画像を形成する各前記画素について繰り返す演算部等の制御手段と、を備え、前記対象領域における前記一の画素を通る前記走査線上の画素数が、当該対象領域における他の前記走査線上の画素数より大きいように構成される。

【0016】

請求項2に記載の発明によれば、請求項1に記載の発明の作用に加えて、対象領域に含まれる一の画素を通る走査線上の画素数が、当該対象領域における他の走査線上の画素数より大きいので、より効果的な雑音除去処理を実行しつつ、記憶手段の数を低減させることができる。

【0017】

上記の課題を解決するために、請求項3に記載の発明は、請求項2に記載の雑音除去装置において、前記加算手段は、前記加算処理のために前記一の画素の前記信号を記憶するレジスタ等の加算用記憶手段を備え、当該加算用記憶手段が、各前記画素の前記信号を記憶する前記記憶手段としても用いられるように構成される。

【0018】

請求項3に記載の発明によれば、請求項2に記載の発明の作用に加えて、加算処理のために一の画素の信号を記憶する加算用記憶手段が、各画素の信号を記憶する記憶手段としても用いられるので、記憶手段の数を低減させつつ、対象領域を構成する画素の数を増加させて雑音除去効果を向上させることができる。

【0019】

上記の課題を解決するために、請求項4に記載の発明は、請求項1から請求項3のいずれか一項に記載の雑音除去装置において、前記デジタル画像はデジタル静止画像であり、前記他の画素は、当該デジタル静止画像内において前記一の画素について対称の位置にある前記画素であり、前記フィルタ係数の値は、相互に前記対称の位置にある前記他の画素において同一とされるように構成される。

【0020】

請求項4に記載の発明によれば、請求項1から請求項3のいずれか一項に記載の発明の作用に加えて、他の画素がデジタル静止画像内において一の画素について対称の位置にある画素であり、相互に対称の位置にある他の画素においてフィルタ係数の値が同一とされるので、乗算手段及び加算手段を簡略化することができる。

【0021】

上記の課題を解決するために、請求項5に記載の発明は、請求項1から請求項4のいずれか一項に記載の雑音除去装置において、前記一の画素が含まれる前記対象領域を構成する前記他の画素の一部が仮想的に前記デジタル画像外となる場合において、当該デジタル画像外となった前記他の画素の前記信号として、前記デジタル画像の外縁を対称軸として当該他の画素に対して対称の位置にある前記対象領域内の前記画素の前記信号を、前記雑音除去処理に供させる端画素判定部等の画素処理手段を備える。

【0022】

請求項5に記載の発明によれば、請求項1から請求項4のいずれか一項に記載の発明の作用に加えて、対象領域を構成する他の画素の一部が仮想的にデジタル画像外となる場合に、デジタル画像外となった他の画素の信号として、デジタル画像の外縁を対称軸として当該他の画素に対して対称の位置にある対象領域内の画素の信号を雑音除去処理に供させるので、デジタル画像の端部に対象領域が設定されることで他の画素の一部が仮想的にデジタル画像外となった場合でも、それ以外の場合と同様の雑音除去効果を有する雑音除去処理を行うことができる。

【0023】

上記の課題を解決するために、請求項6に記載の発明は、請求項1から請求項4のいずれか一項に記載の雑音除去装置において、前記一の画素が含まれる前記対象領域を構成する前記他の画素の一部が仮想的に前記デジタル画像外となる場合において、当該デジタル画像外となった前記他の画素の前記信号として、前記対象領域内の前記一の画素の前記信号を前記雑音除去処理に供させる端画素判定部等の画素処理手段を備える。

【0024】

請求項6に記載の発明によれば、請求項1から請求項4のいずれか一項に記載の発明の作用に加えて、対象領域を構成する他の画素の一部が仮想的にデジタル画像外となる場合に、デジタル画像外となった他の画素の信号として、対象領域内の当該一の画素の信号を雑音除去処理に供させるので、デジタル画像の端部に対象領域が設定されることで他の画素の一部が仮想的にデジタル画像外となった場合でも、それ以外の場合と同様の雑音除去効果を有する雑音除去処理を行うことができる。

【発明の効果】

【0025】

本発明によれば、走査線の数に対応した数の信号記憶用の記憶手段を備える雑音除去装置の対象領域における走査線上の画素数が当該走査線に垂直な方向の画素数より大きいので、走査線上の画素数と走査線に垂直な方向の画素数とが同数の場合に比して、対象領域に含まれる画素数を雑音除去処理用に十分確保しつつ、記憶手段の数を低減させることができる。

【0026】

従って、雑音除去装置としての雑音除去処理の能力を担保しつつ、雑音除去装置としてのハードウェア的な規模を縮小することができる。

【図面の簡単な説明】

【0027】

【図1】本発明の原理を説明する図であり、(a)は本発明に係るフィルタ対象領域とデジタル画像の走査方向との関係を例示する図であり、(b)は図1(a)に例示したフィルタ対象領域に対応するレジスタ及びラインメモリの構成及び動作を例示する図である。

【図2】第1実施形態に係る雑音除去フィルタを示す図であり、(a)は当該雑音除去フィルタの概要構成を示すブロック図であり、(b)は当該雑音除去フィルタにおける雑音除去処理を示すフローチャートである。

【図3】第1実施形態に係る雑音除去処理を示す図である。

【図4】第2実施形態に係るフィルタ対象領域の形状等を示す図であり、(a)は当該フィルタ対象領域の形状を例示する図であり、(b)は当該形状のフィルタ対象領域に対応するレジスタ及びラインメモリの概要構成及び動作を例示する図である。

【図5】第2実施形態に係るフィルタ対象領域の他の例を示す図であり、(a)は当該フィルタ対象領域を示す図であり、(b)は当該他の例としての各画素に対応するフィルタ係数の値の分布の第一例を示す図であり、(c)は当該フィルタ係数の値の分布の第二例を示す図であり、(d)は当該フィルタ係数の値の分布の第三例を示す図であり、(e)は当該フィルタ係数の値の分布の第四例を示す図である。

【図6】第2実施形態に係るフィルタ対象領域を更に他の例を示す図であり、(a)は当該フィルタ対象領域の形状の第五例を示す図であり、(b)は当該フィルタ対象領域の形状の第六例を示す図であり、(c)は当該フィルタ対象領域の形状の第七例を示す図である。

【図7】第3実施形態に係る端画素処理を示す図であり、(a)は第3実施形態に係るデジタル画像とフィルタ対象領域との関係を例示する図であり、(b)は第3実施形態に係る雑音除去フィルタの概要構成を示すブロック図である。

【図8】第3実施形態に係る端画素処理の第一例を示す図であり、(a)は当該端画素処理の一例を示す図であり、(b)は当該端画素処理の他の一例を示す図である。

【図9】第3実施形態に係る端画素処理の第二例を示す図であり、(a)は当該端画素処理の一例を示す図であり、(b)は当該端画素処理の他の一例を示す図である。

【発明を実施するための形態】

【0028】

次に、本発明を実施するための形態について、図面に基づいて説明する。なお、以下に説明する実施形態は、複数の画素からなるデジタル画像に含まれ雑音や歪みを除去する雑音除去フィルタに対して本発明を適用した場合の実施形態である。また本発明に係るデジタル画像は、ラスタスキャン方式により走査されるデジタル画像である。更に以下の説明では、先に述べた背景技術において説明済みの概念等については、同様の名称等を用いる。

【0029】

(I)本発明の原理

初めに、具体的な実施形態を説明する前に、本発明に係る基本的な原理について図1を用いて説明する。なお図1は、本発明の原理を説明するための図である。

【0030】

上述したように上記特許文献1に開示されている雑音除去フィルタでは、当該雑音除去フィルタとしての雑音除去効果を高めるためには、より多数の画素をフィルタ対象領域として設定する必要がある。一方上述したように、当該雑音除去処理においてフィルタ対象領域の輝度を取得する場合、一般には、ラインメモリ等が最低でも「フィルタ対象領域における走査線数−1」の数だけ必要となる。他方、上記特許文献1に開示されている雑音除去フィルタとしてのε−分離非線形デジタルフィルタでは、フィルタ対象領域全体としての形状が上記(1)の処理において述べたような正方形であることは必須の要件ではなく、正方形以外の全体形状を有するフィルタ対象領域を用いる場合でも、ε−分離非線形デジタルフィルタとして効果的な雑音除去処理を行うことが可能であるとされている。

【0031】

そこで本発明では、雑音除去フィルタとしての雑音除去処理の能力を担保しつつハードウェア的な規模を縮小させるべく、図1(a)に例示されるように、フィルタ対象領域Fが、当該フィルタ対象領域Fにおける走査線Lの方向に長い形状とされる。より具体的に本発明に係るフィルタ対象領域Fでは、フィルタ対象領域Fにおいて走査線Lに沿って配置される画素Pxの数が、フィルタ対象領域Fにおいて当該走査線Lに垂直な方向に配置される画素Pxの数よりも大きくなっている。具体的には、例えば図1(a)に例示する場合、走査線Lに沿って配置される画素Pxとは、画素Px11乃至画素Px17、画素Px21乃至画素Px27、又は画素Px31乃至画素Px37のいずれかであるから、その数は「7」である。これに対して、走査線Lに垂直な方向に配置される画素Pxの数は「3」となっており、前者の方が後者よりも大きい。

【0032】

ここで、上記処理(1)及び上記処理(2)の処理を本発明に係るフィルタ対象領域Fに対して実行するために必要なメモリ部の構成について、図1(b)を用いて例示しつつ説明する。上記処理(1)及び上記処理(2)を図1(a)に例示する21個の画素Pxからなるフィルタ対象領域Fを対象として実行する場合、各画素Pxの輝度は、図1(b)に例示するレジスタR1乃至R21に、メモリクロックごとに順次転送されて保持される。このとき、レジスタR1乃至レジスタR7がフィルタ対象領域Fの例えば画素Px11乃至画素Px17に対応し、レジスタR8乃至レジスタR14がフィルタ対象領域Fの例えば画素Px21乃至画素Px27に対応し、レジスタR15乃至レジスタR21がフィルタ対象領域Fの例えば画素Px31乃至画素Px37に対応している。ここで、レジスタR1からレジスタR7まで転送された各画素Pxの輝度はラインメモリLM1に一時的に保持されて上記処理(1)乃至処理(3)に供され、またレジスタR8からレジスタR14まで転送された各画素Pxの輝度はラインメモリLM2に一時的に保持されて上記処理(1)乃至処理(3)に供され、更にレジスタR15からレジスタR21まで転送された各画素Pxの輝度はそのまま上記処理(1)乃至処理(3)に供される。なお、図1(b)に記載されたレジスタG1乃至レジスタG6は、上記処理(1)から処理(5)が完了するまで、上記処理(1)において取得された中心画素Px24の輝度を順次転送しつつ保持しておき、その後の処理(6)に供させる為のレジスタである。

【0033】

図1(b)から明らかなように、本発明に係るフィルタ対象領域Fを用いた雑音除去処理では、例えば3画素×3画素の画素Pxからなる正方形のフィルタ対象領域に対して、同じラインメモリの数(即ち2個)を維持しつつも、フィルタ対象領域Fを構成する画素Pxを21個と倍以上とすることができる。よってこの場合、ラインメモリの数を同じとしつつもフィルタ対象領域Fを構成する画素Pxの数を多くすることができ、結果として、ラインメモリの数を同じとしつつもフィルタ対象領域Fを用いた雑音除去処理の効果を著しく向上させることができるのである。このことは即ち、同じ雑音除去処理であれば、雑音除去フィルタとしてのラインメモリの数を減らせることとなり、結果として、雑音除去フィルタとしてのハードウェア的な規模を縮小することにもなるのである。

【0034】

(II)第1実施形態

次に、上述した原理に基づく本発明に係る第1実施形態について、図2及び図3を用いて説明する。なお図2は第1実施形態に係る雑音除去フィルタを示す図であり、図3は第1実施形態に係る雑音除去処理を示す図である。また第1実施形態に係るフィルタ対象領域Fは、図1(a)に例示したフィルタ対象領域Fと同様の形状を有するフィルタ対象領域F1とされている。

【0035】

図2(a)に示すように、第1実施形態に係る雑音除去フィルタS1は、メモリ部1と、検出手段の一例としての差分演算部2と、比較手段の一例及び特定手段の一例としての閾値判定部3と、乗算手段の一例、加算手段の一例及び制御手段の一例としての演算部4と、雑音閾値設定部5と、フィルタ係数設定部6と、操作部7と、により構成されている。図1(b)において説明したレジスタR1乃至レジスタR21、加算用記憶手段の一例としてのレジスタG1乃至レジスタG6並びに記憶手段の一例としてのラインメモリLM1及びラインメモリLM2は、メモリ部1内に含まれている。

【0036】

この構成においてメモリ部1には、図2(a)及び図3に示すように、第1実施形態に係るフィルタ対象領域F1を含むデジタル画像に相当する画像信号Sinが入力される。

【0037】

この時、第1実施形態に係るフィルタ対象領域F1に含ませるべき画素Pxの数や、第1実施形態に係る形状(具体的には、図1(a)に例示した、走査線Lに沿って配置される画素Pxの数が、フィルタ対象領域F1において当該走査線Lに垂直な方向に配置される画素Pxの数よりも大きい形状)を有するフィルタ対象領域F1の具体的な当該形状(縦横それぞれの画素Pxの具体的な数)は、例えばメモリ部1に含まれる上記レジスタRの数や、上記差分演算部2、閾値判定部3及び演算部5それぞれにおける実際の処理速度等に基づいて使用者が予め固定的に設定し、その形状を示す情報を雑音除去フィルタS1内に予め記憶させておくのが好適である。なおこれ以外に例えば、メモリ部1に含まれる上記レジスタRの数や上記差分演算部2等における実際の処理速度等において許容され得る範囲内において、複数種類のフィルタ対象領域F1の形状のパターンを予め雑音除去フィルタS1内に記憶させておき、これらを、例えばデジタル画像の内容に応じて、使用者の手動により又は自動的に切り換えられるように構成することもできる。

【0038】

そしてメモリ部1は、上記各レジスタR、レジスタG及びラインメモリLMを順次用いることにより、画像信号Sinの中からデジタル画像におけるフィルタ対象領域F1を構成する各画素Px(中心画素Px24を含む)の輝度を取得して、一時的に保持する。これらの処理は上記(1)及び上記(2)にそれぞれ記載された処理に相当する(図2(b)ステップS1)。そしてメモリ部1は、保持している各画素Pxの輝度を示す輝度情報を、メモリ信号Smとして差分演算部2に出力する。なお図3においては、例えば画素Px11の輝度は「(P11)」と表記されている。

【0039】

次に差分演算部2は、中心画素Px24を含むフィルタ対象領域F内の各画素Pxの輝度を示す上記輝度情報をメモリ部1から取得し、上記(3)に相当する処理を実行する。即ち差分演算部2は、図3に模式的に示すように、中心画素Px24の輝度と、各画素Pxの輝度Pと、の差分Δを、画素Pxごとに検出し、その検出結果を画素Pxごとに差分信号Sdifとして閾値判定部3に出力する。なお図3においては、例えば画素Px11の輝度と中心画素Px24の輝度との差分Δは「Δ11」と表記されている。具体的に例えば、画素Px11について差分演算部2は、その輝度P11と、中心画素Px24の輝度P24と、差分Δ11を算出し、差分信号Sdifとして閾値判定部3に出力する。また例えば画素Px34について差分演算部2は、その輝度P34と、中心画素Px24の輝度P24と、差分Δ34を算出し、差分信号Sdifとして閾値判定部3に出力する。以上の処理を差分演算部2は、図3に示すようにフィルタ対象領域F内の全ての画素Pxについて実行する。

【0040】

そしてフィルタ係数設定部6は、例えば予め設定されているフィルタ係数を、フィルタ係数信号Scとして画素Pxごとに演算部4に出力する(図2(b)ステップS2)。なお図3においては、例えば画素Px11に対応するフィルタ係数は「C11」と表記されている。

【0041】

一方使用者は、例えばメモリ部1に入力される前の画像信号Sinに相当するデジタル画像を前もって図示しないディスプレイ上に表示させる等の処理により、そのデジタル画像の内容を把握し、上記(4)の雑音判定処理に係る雑音閾値を設定する操作を操作部7において実行する。この操作に対応する操作信号Sotは、操作部7から雑音閾値設定部5に出力される。

【0042】

これにより雑音閾値設定部5は、当該操作信号Sotに基づいて、上記(4)に相当する雑音判定処理に係る雑音閾値を設定し、閾値信号Sthとして閾値判定部3に出力する。これにより閾値判定部3は、上記(4)に相当する雑音判定処理を実行する(図2(b)ステップS3)。即ち閾値判定部3は、差分信号Sdifとして出力されてくる画素ごとの差分Δと、閾値信号Sthとして入力されてくる閾値と、を比較し、例えば閾値以上の値の差分Δに対応する画素Pxを第1実施形態に係る雑音除去処理の対象画素から除外する(図2(b)ステップS3;非雑音)。一方閾値判定部3は、例えば当該閾値未満の値の差分Δに対応する画素Pxを第1実施形態に係る雑音除去処理の対象画素とする(図2(b)ステップS3;雑音)。そして閾値判定部3は、当該対象画素とされた画素Pxについては対象画素であることを示すフラグ等を付加し、各画素Pxに対応する差分Δを、画素Pxごとに画素信号Spxとして演算部4に出力する。

【0043】

次に演算部4は、フィルタ係数信号Scとしてフィルタ係数設定部6から出力されてくるフィルタ係数Cと、上記画素信号Spxとして閾値判定部3から出力されてくる差分Δと、を用いて、上記(5)に対応する乗算/加算処理及び上記(6)に相当する加算処理を実行する(図2(b)ステップS4)。即ち演算部4は、先ず画素信号Spxとして閾値判定部3から出力されてくる差分Δのうち、対象画素であることを示すフラグ等が付加されている画素Px以外の全ての他の画素Pxに対応する差分Δ又は当該全ての他の画素Pxに対応するフィルタ係数Cのいずれか一方の値をゼロとする。次に演算部4は、図3に破線で示すように、各画素Pxに対応する差分Δとフィルタ係数Cとを画素Pxごとに乗算し、画素Pxごとの乗算結果を全て加算する。このとき演算部4は、上記背景技術とは異なり、フィルタ係数信号Scとしてフィルタ係数設定部6から出力されてくるフィルタ係数Cを用いて乗算処理を行う。この場合、雑音除去処理の対象画素である画素Px以外の全ての他の画素Pxについては、当該他の画素Pxに対応する差分Δ又はフィルタ係数Cのいずれか一方の値がゼロとされているので、結果として雑音除去処理の対象画素である画素Pxについてのみ、上記乗算結果が有意となる。

【0044】

そして演算部4は、図3に一点鎖線で示すように、全ての画素Pxについての加算結果に対して中心画素Px24の輝度を加算し、その中心画素Px24についての(換言すれば、中心画素Px24を中心とするフィルタ対象領域Fについての)第1実施形態に係る雑音除去処理後の出力信号Soutとする。なおこのとき加算される中心画素Px24の輝度は、上記ステップS1の処理により取得され、図1(b)に示すレジスタG1乃至レジスタG6を上記メモリクロックのタイミングで順次転送されつつ保持されている輝度である。この中心画素Px24の輝度は、上記ステップS1の処理により取得された後は、上記ステップS2乃至ステップS4として上記(3)から上記(5)までの処理が完了するまで、レジスタG1乃至レジスタG6により保持されることとなる。

【0045】

その後演算部4は、図2(b)に示すステップS1からステップS4の処理が、デジタル画像内の全ての画素Pxを中心画素として(換言すればデジタル画像内の全てのフィルタ対象領域Fについて)行われたか否かを確認する(図2(b)ステップS5)。ステップS5の確認において全ての画素Pxについて図2(b)に示すステップS1からステップS4の処理が完了している場合(図2(b)ステップS5;YES)、演算部4は、画像信号Sinとして入力されたデジタル画像内の全ての画素に対しての雑音除去処理が終了したとして、全てのフィルタ対象領域Fについての上記出力信号Soutを当該フィルタ対象領域Fが含まれるデジタル画像に対応する出力信号Soutとして出力し、第1実施形態に係る雑音除去処理を終了する。

【0046】

一方ステップS5の確認において図2(b)に示すステップS1からステップS4の処理が完了していない画素Pxがある場合(図2(b)ステップS5;NO)、演算部4は、当該完了していない新たな画素Pxを中心画素とした図2(b)に示すステップS1からステップS4の処理を実行すべく、当該ステップS1に戻る(ステップS6)。

【0047】

なお、上述してきたステップS1乃至ステップS6の処理は、一のフィルタ対象領域Fについての処理である。一のフィルタ対象領域Fの全てについてステップS1乃至ステップS6の処理が終了した後は、中心画素Px24に隣接する画素Px(具体的には、図1(a)に例示する画素Px13、画素Px14、画素Px15、画素Px23、画素Px25、画素Px33、画素Px34又は画素Px35のいずれか)を中心画素とした図1(a)に示す形状の新たなフィルタ対象領域Fがメモリ部1及び差分演算部2において設定され、当該新たなフィルタ対象領域Fに対して上記ステップS1乃至ステップS6の処理が改めて実行される。そして、一のデジタル画像内に設定され得る全てのフィルタ対象領域FについてステップS1乃至ステップS6の処理が全て終了することで、当該一のデジタル画像についての第1実施形態に係る雑音除去処理が終了する。

【0048】

以上説明したように、第1実施形態の雑音除去フィルタS1の構成によれば、デジタル画像の走査線Lの数に対応した数の輝度保持用のラインメモリLMを備える雑音除去フィルタS1において、フィルタ対象領域Fにおける走査線L上の画素Pxの数が、走査線Lに垂直な方向の画素Pxの数より大きいので、走査線L上の画素数と走査線Lに垂直な方向の画素数とが同数である従来の場合に比して、フィルタ対象領域Fに含まれる画素数を雑音除去処理用に十分確保しつつ、ラインメモリLMの数を低減させることができる。

【0049】

(III)第2実施形態

次に、本発明に係る他の実施形態である第2実施形態について、図4乃至図6を用いて説明する。なお図4は第2実施形態に係る雑音除去フィルタにおけるフィルタ対象領域の形状等を示す図であり、図5は第2実施形態に係るフィルタ対象領域の他の例を示す図であり、図6は第2実施形態に係るフィルタ対象領域を更に他の例を示す図である。図5(b)乃至図5(e)においては、各画素Pxにそれぞれ対応するフィルタ係数の値を( )書きの数字で示している。また第2実施形態に係る雑音除去フィルタを説明するに当たり、第1実施形態に係る雑音除去フィルタS1における部材及び処理と同一の部材及び処理については、同一の部材番号及びステップ番号を使用して、細部の説明は省略する。

【0050】

第1実施形態に係る雑音除去フィルタS1では、図1(a)及び図3に示すように、雑音除去処理に係るフィルタ対象領域Fとして、走査線Lに沿って配置される画素Pxの数がフィルタ対象領域Fにおいて当該走査線Lに垂直な方向に配置される画素Pxの数よりも大きい長方形の形状を有するフィルタ対象領域F1を用いた。これに対して第2実施形態及び後述する第3実施形態及び第4実施形態では、図4(a)に例示するように、フィルタ対象領域Fとして、その時の中心画素を通る走査線L上に並ぶ画素Pxの数が、他の走査線L上に並ぶ画素Pxの数よりも大きいフィルタ対象領域F2を用いる。なお第2実施形態及び第3実施形態に係るフィルタ対象領域F2においても、走査線Lに沿って配置される画素Pxの数がフィルタ対象領域Fにおいて当該走査線Lに垂直な方向に配置される画素Pxの数よりも大きいことに変わりはない。第2実施形態に係る雑音除去フィルタでは、上述した形状のフィルタ対象領域F2を用いることで、図1(b)にも示したレジスタG(即ち中心画素の輝度を転送しつつ保持するレジスタG)をも他のレジスタRと共に有効に活用して、ラインメモリLMの数を減らしつつ、フィルタ対象領域Fに含まれる画素Pxの数を更に増やすのである。

【0051】

即ち図4(a)に例示するように、第2実施形態に係る雑音除去フィルタでは、図4(b)に示すレジスタGの数(五つ)だけ、フィルタ対象領域F2の中心画素Px2Aを通る走査線L上に並ぶ画素Pxが、走査線Lの走査方向に画素Px2F乃至画素Px2Jとして増やされている。またこれら画素Px2F乃至画素Px2Jが増やされていることとの均衡から、中心画素Px2Aを通る走査線L上に並ぶ画素Pxが、走査線Lの走査方向と反対の方向にも、画素Px21乃至画素Px25として増やされている。

【0052】

以上のような第2実施形態に係るフィルタ対象領域F2を用いることで、これに対応するレジスタR及びレジスタG並びにラインメモリLM1及びラインメモリLM2の構成は、図4(b)に示される構成となり、レジスタR1乃至レジスタR32の合計32個のレジスタRに加えて5個のレジスタGを用いて、各画素Pxの輝度を順次転送しつつ保持する。このとき、レジスタR10乃至レジスタR23と、レジスタG1乃至レジスタG5と、が、中心画素Px2Aの輝度を含むフィルタ対象領域F2における中央の行の画素Px21乃至画素Px2Jの輝度を順保持することになる。なおレジスタG1乃至レジスタG5は、その本来の機能として中心画素Px2Aの輝度を順次転送しつつ保持するが、中心画素Px2Aの輝度の保持とその他の画素Pxの輝度の保持とではそのタイミングが異なるため、レジスタG1乃至レジスタG5のうち、空いているレジスタGを中心画素Px2Aの輝度の保持に振り向けることができるのである。

【0053】

第2実施形態に係る雑音除去フィルタは、以上説明した形状のフィルタ対象領域F2を用いて、第1実施形態に係る雑音除去フィルタS1と同様の雑音除去処理(フィルタ対象領域Fのみが第2実施形態に係るフィルタ対象領域F2とされる雑音除去処理)をデジタル画像に対して実行することになる。

【0054】

以上説明したように、第2実施形態に係る雑音除去フィルタの動作によれば、第1実施形態に係る雑音除去フィルタS1の動作による効果に加えて、フィルタ対象領域Fに含まれる中心画素Px24を通る走査線L上の画素Pxの数が、フィルタ対象領域Fにおける他の走査線L上の画素Pxの数より大きいので、より効果的な雑音除去処理を実行しつつ、ラインメモリLMの数を低減させることができる。

【0055】

また、上記(6)の加算処理のために中心画素Px2Aの輝度を保持するレジスタGが各画素Pxの輝度を保持するレジスタとしても用いられるので、ラインメモリLMの数を低減させつつ、フィルタ対象領域F2を構成する画素Pxの数を増加させて雑音除去効果を向上させることができる。

【0056】

なお、第2実施形態に係る雑音除去フィルタの演算部4において実行される上記(5)に対応する乗算処理において、各画素Pxに対応する差分Δとフィルタ係数Cとを画素Pxごとに乗算する場合(図3参照)、例えば図5(a)に例示するフィルタ対象領域F2の各画素Pxに対応するフィルタ係数Cを画素Pxごとに区別して、例えば図5(b)に例示するようにその値を全て「1」としたときには、フィルタ対象領域Fを構成する画素Pxの数(図5に例示する場合は37個)と同数の乗算器が演算部4内に必要となる。しかしながら図5(c)乃至図5(e)に例示したように、フィルタ対象領域F2において中心画素Px2Aについて対称の位置にある画素Px同士を同一の値を有するフィルタ係数Cとする場合には、値が同一のフィルタ係数Cに対応する画素Pxについての差分Δを全て加算した後に当該同一のフィルタ係数Cに乗算すれば、結果として、画素Pxごとに逐一乗算をした場合と同じ乗算結果が得られる。具体的に例えば、図5(c)に例示するように、中心画素Px2Aを含めてその上下左右に隣接する5個の画素Px15、画素Px29、画素Px2B及び画素Px35にそれぞれ対応するフィルタ係数を例えば「8」とし、中心画素Px2Aに対して更に外側にある8個の画素Px14、画素Px16、画素Px27、画素Px28、画素Px2C、画素Px2D、画素Px34及び画素Px26にそれぞれ対応するフィルタ係数を例えば「6」とする。更に、画素Px12、画素Px13、画素Px17、画素Px18、画素Px25、画素Px26、画素Px2E、画素Px2F、画素Px32、画素Px33、画素Px37及び画素Px38にそれぞれ対応するフィルタ係数を例えば「4」とし、画素Px11、画素Px19、画素Px23、画素Px24、画素Px2G、画素Px2H、画素Px31及び画素Px39にそれぞれ対応するフィルタ係数を例えば「2」とし、画素Px21、画素Px22、画素Px2I及び画素Px2Jにそれぞれ対応するフィルタ係数を例えば「1」とする。また図5(d)及び図5(e)に例示するように、同じ大文字アルファベットで示される画素Pxに対応するフィルタ係数を同一とするように構成することもできる。ここで、図5(c)に例示する場合、フィルタ係数Cとしては中心画素Px2Aに対応するフィルタ係数C2Aを入れて合計5種類であるので、乗算器も5個で済む。また同様に図5(d)に例示する場合(二つずつの画素Pxに対応するフィルタ係数を同一とする場合)には、フィルタ係数Cとしては合計19種類必要であるが、中心画素Px2Aに対応する差分Δ2Aは当然にゼロであるのでこれを考慮すると、演算部4内の乗算器は更に18個まで減らすことができることになる。更に図5(e)に例示する場合(四つずつの画素Pxに対応するフィルタ係数を同一とする場合)には、同様にフィルタ係数Cとしては合計10種類であるが、乗算器は9個で足りることとなる。

【0057】

以上図5を用いて説明したように、中心画素Px2Aについて対称の位置にある画素Pxについてフィルタ係数Cの値を同一とすれば、演算部4としての乗算器の数を大幅に削減することができ、雑音除去フィルタとしての構成を大幅に簡略化することができる。

【0058】

なお第2実施形態に係るフィルタ対象領域F2の形状は、更に種々の変形が可能である。

【0059】

即ち例えば図6(a)に示すように、上から一行目を画素Px11乃至画素Px17の7個の画素Pxにより構成し、中心画素Px28を含む中央の一行を画素Px21乃至画素Px2Fの15個の画素Pxにより構成し、更に上から三行目を画素Px31乃至画素Px37の7個の画素Pxにより構成したフィルタ対象領域F3を、第2実施形態に係る雑音除去処理に用いることが可能である。この場合の各画素Pxからの輝度の取得及び保持についての各レジスタR及びレジスタGの動作は、上記した第2実施形態に係る雑音除去フィルタと同様となる。図6(a)に例示する合計29個の画素Pxを含むフィルタ対象領域F3を用いた雑音除去処理では、当該雑音除去処理に必要なラインメモリLMの数は、図4に例示した場合と同様に2個である。なお、図6(a)に例示するフィルタ対象領域F3を用いた雑音除去処理における雑音除去能力と同等の雑音除去能力を有するフィルタ対象領域を背景技術と同様の正方形に画素Pxが配置されたフィルタ対象領域で実現しようとすると、例えば5画素×5画素の合計25個の画素Pxからなるフィルタ対象領域が必要となり、この場合に必要となるラインメモリLMの数は4個となってフィルタ対象領域F3の場合よりも多くなる。

【0060】

また例えば図6(b)に示すように、上から一行目を画素Px11乃至画素Px15の5個の画素Pxにより構成し、上から二行目を画素Px21乃至画素Px29の9個の画素Pxにより構成し、中心画素Px39を含む中央の一行を画素Px31乃至画素Px3Hの17個の画素Pxにより構成し、上から四行目を画素Px41乃至画素Px49の9個の画素Pxにより構成し、更に上から五行目を画素Px51乃至画素Px55の5個の画素Pxにより構成したフィルタ対象領域F4を、第2実施形態に係る雑音除去処理に用いることが可能である。この場合の各画素Pxからの輝度の取得及び保持についての各レジスタR及びレジスタGの動作も、上記した第2実施形態に係る雑音除去フィルタと同様となる。図6(b)に例示する合計45個の画素Pxを含むフィルタ対象領域F4を用いた雑音除去処理では、当該雑音除去処理に必要なラインメモリLMの数は4個となる。そして、図6(b)に例示するフィルタ対象領域F4を用いた雑音除去処理における雑音除去能力と同等の雑音除去能力を有するフィルタ対象領域を背景技術と同様の正方形に画素Pxが配置されたフィルタ対象領域で実現しようとすると、例えば7画素×7画素の合計49個の画素Pxからなるフィルタ対象領域が必要となり、この場合に必要となるラインメモリLMの数は6個となってフィルタ対象領域F4の場合よりも多くなる。

【0061】

最後に例えば図6(c)に示すように、上から一行目を画素Px11乃至画素Px19の9個の画素Pxにより構成し、上から二行目を画素Px21乃至画素Px29の9個の画素Pxにより構成し、中心画素Px39を含む中央の一行を画素Px31乃至画素Px3Hの17個の画素Pxにより構成し、上から四行目を画素Px41乃至画素Px49の9個の画素Pxにより構成し、更に上から五行目を画素Px51乃至画素Px59の9個の画素Pxにより構成したフィルタ対象領域F5を、第2実施形態に係る雑音除去処理に用いることが可能である。図6(c)に例示する合計53個の画素Pxを含むフィルタ対象領域F4を用いた雑音除去処理でも、当該雑音除去処理に必要なラインメモリLMの数は4個となる。そして、図6(c)に例示するフィルタ対象領域F5を用いた雑音除去処理における雑音除去能力と同等の雑音除去能力を有するフィルタ対象領域を背景技術と同様の正方形に画素Pxが配置されたフィルタ対象領域で実現しようとすると、最低でも7画素×7画素の合計49個の画素Pxからなるフィルタ対象領域が必要となり、この場合に必要となるラインメモリLMの数は6個となってフィルタ対象領域F5の場合よりも多くなる。

【0062】

このように、第2実施形態に係るフィルタ対象領域F2乃至フィルタ対象領域F5のいずれを用いる場合でも、背景技術に比してラインメモリLMの数を低減し、雑音除去フィルタとしての構成を大幅に簡略化することができる。

【0063】

(IV)第3実施形態

次に、本発明に係る他の実施形態である第3実施形態について、図7乃至図9を用いて説明する。なお図7乃至図9は第3実施形態に係る端画素処理を示す図である。なお図8及び図9においては、例えば画素Px28の輝度は「(P28)」と表記されている。更に第3実施形態に係る雑音除去フィルタを説明するに当たり、第1実施形態に係る雑音除去フィルタS1における部材及び処理と同一の部材及び処理については、同一の部材番号及びステップ番号を使用して、細部の説明は省略する。

【0064】

上述してきた第2実施形態では、フィルタ対象領域Fの形状が単純な長方形ではない。よって、図7(a)に例示するデジタル画像Gの端部にフィルタ対象領域Fが設定される場合、そのデジタル画像Gの端部の形状とフィルタ対象領域Fの外形とが一致せず、図7(a)に例示するようにフィルタ対象領域Fを構成する画素Pxの一部が仮想的にデジタル画像Gの外にはみ出すことがある。例えば図7(a)に示すデジタル画像Gの左上に設定されたフィルタ対象領域Fでは、画素Px11乃至画素Px17、画素Px21乃至画素Px27及び画素Px31乃至画素Px33が仮想的にデジタル画像Gの外にはみ出している。また当該デジタル画像Gの右辺に設定されたフィルタ対象領域Fでは、画素Px17、画素Px2B乃至画素Px2F及び画素Px37が仮想的にデジタル画像Gの外にはみ出しており、更に当該デジタル画像Gの下辺に設定されたフィルタ対象領域Fでは、画素Px31乃至画素Px37を含む一行分が仮想的にデジタル画像Gの外にはみ出している。なおこれら三つのフィルタ対象領域Fにおいても、中心画素Px28は全てデジタル画像G内にある。

【0065】

図7(a)に例示するように一部の画素Pxがデジタル画像Gの外にはみ出すように設定されたフィルタ対象領域Fであっても、それを用いた雑音除去処理では、当該はみ出した画素Pxについても(実際には存在しない)輝度を取得して上記(1)乃至上記(3)の処理に供させることが必要である。

【0066】

そこで第3実施形態に係る雑音除去フィルタにおいては、図7(a)に例示したように一部の画素Pxがデジタル画像Gから仮想的にはみ出す場合の端画素処理を実行して雑音除去処理としての能力を維持する。

【0067】

即ち図7(b)に示すように、第3実施形態に係る雑音除去フィルタS3は、第1実施形態に係る雑音除去フィルタS1に対して、画素処理手段の一例としての端画素判定部10を備えている。この構成において端画素判定部10は、画像信号Sinに基づき、フィルタ対象領域Fとデジタル画像Gとを比較し、フィルタ対象領域Fを構成する画素Pxのうち、デジタル画像Gの外にはみ出す画素Pxを検出する。これにより端画素判定部10は、当該検出結果を端画素信号Segとして差分演算部2に出力する。

【0068】

これにより差分演算部2は、第3実施形態に係る端画素処理の第一例として、デジタル画像Gの外にはみ出した画素Pxの輝度として、デジタル画像Gの外縁を対称軸として当該はみ出した画素Pxに対して対称の位置にあるフィルタ対象領域F内の画素Pxの輝度を用いて上記(3)に相当する処理を実行する。

【0069】

具体的に例えば、図8(a)に例示する場合において差分演算部2は、図8(a)に例示するように、一点鎖線で外縁が示されているデジタル画像Gの外にはみ出した画素Px25の輝度としてデジタル画像Gの左辺を対称軸として画素Px25に対して対称の位置にあるフィルタ対象領域F内の画素Px2Aの輝度(P2A)を用いて、上記(3)に相当する処理を実行する(図8(a)破線参照)。また例えば、図8(a)に例示する場合において差分演算部2は、図8(a)に例示するように、デジタル画像Gの外にはみ出した画素Px17の輝度としてデジタル画像Gの上辺を対称軸として画素Px17に対して対称の位置にあるフィルタ対象領域F内の画素Px2Bの輝度(P2B)を用いて、上記(3)に相当する処理を実行する(図8(a)破線参照)。更に例えば、図8(b)に例示する場合において差分演算部2は、図8(b)に例示するように、デジタル画像Gの外にはみ出した画素Px22の輝度としてデジタル画像Gの左辺を対称軸として画素Px22に対して対称の位置にあるフィルタ対象領域F内の画素Px29の輝度(P29)を用いて、上記(3)に相当する処理を実行する(図8(b)破線参照)。

【0070】

また差分演算部2は、第3実施形態に係る端画素処理の第二例として、デジタル画像Gの外にはみ出した全ての画素Pxの輝度として、フィルタ対象領域F内の中心画素Px28の輝度(P28)を用いて上記(3)に相当する処理を実行する。

【0071】

具体的には、図9(a)及び図9(b)に例示するいずれの場合も、デジタル画像Gの外にはみ出した全ての画素Pxの輝度としてフィルタ対象領域F内の中心画素Px28の輝度(P28)を用いて、上記(3)に相当する処理を実行する。この図9に例示する場合には、差分演算部2における上記(3)に相当する処理により、デジタル画像Gの外にはみ出した全ての画素Pxに対応する差分Δの値がゼロとなり、結果として、これらはみ出した画素Pxは第3実施形態に係る雑音除去処理の対象外となる。

【0072】

なお、上述した第3実施形態に係る端画素処理の第一例及び第二例において、デジタル画像Gの外にはみ出していないフィルタ対象領域F内の画素Pxについては、上記第1実施形態又は第2実施形態に係る雑音除去処理と同様の雑音除去処理が実行される。

【0073】

以上説明したように、第3実施形態に係る端画素処理の第一例及び第二例によれば、デジタル画像Gの端部にフィルタ対象領域Fが設定されることでそれを構成する画素Pxの一部が仮想的にデジタル画像Gの外となった場合でも、それ以外の場合と同様の雑音除去効果を有する雑音除去処理を行うことができる。

【0074】

なお、上述した各実施形態に係る雑音除去フィルタSは、デジタル画像Gを記録媒体に記録する情報記録装置において、当該デジタル画像Gに対する符号化処理の終了後且つ当該記録媒体への記録処理前の段階に挿入して備えさせるように構成することが可能である。なお当該記録媒体としては、例えば光ディスクやハードディスク等が挙げられる。更に当該雑音除去フィルタSは、デジタル画像Gを記録済みの記録媒体から当該デジタル画像Gを再生する情報再生装置において、当該デジタル画像Gに対する復号化処理の前又は後の段階に備えさせるように構成することも可能である。

【0075】

更にまた、各実施形態に係るメモリ部1、差分演算部2、閾値判定部3、演算部4、雑音閾値設定部5及びフィルタ係数設定部6等の機能に対応するプログラムを、例えば光ディスク等の記録媒体に記録しておき、或いはインターネット等のネットワークから取得して記録しておき、これらを読み出して汎用のマイクロコンピュータ等により実行させることにより、当該マイクロコンピュータ等を、各実施形態に係るメモリ部1、差分演算部2、閾値判定部3、演算部4、雑音閾値設定部5及びフィルタ係数設定部6等として機能させることも可能である。

【産業上の利用可能性】

【0076】

以上夫々説明したように、本発明は雑音除去装置の分野に利用することが可能であり、特にデジタル画像に含まれる雑音を除去する雑音除去装置の分野に適用すれば特に顕著な効果が得られる。

【符号の説明】

【0077】

1 メモリ部

2 差分演算部

3 閾値判定部

4 演算部

5 雑音閾値設定部

6 フィルタ係数設定部

10 端画素判定部

F、F1、F2、F3、F4、F5 フィルタ対象領域

L 走査線

R1〜R32、G1〜G6 レジスタ

LM1、LM2 ラインメモリ

S1、S3 雑音除去フィルタ

Sin 画像信号

Sm メモリ信号

Sdif 差分信号

Sot 操作信号

Sc フィルタ係数信号

Sth 閾値信号

Spx 画素信号

Sout 出力信号

G デジタル画像

Seg 端画素信号

【特許請求の範囲】

【請求項1】

一定方向の走査線により順次走査される複数の画素により形成されるデジタル画像における一の画素の信号と、当該一の画素の周囲の複数の他の画素の信号と、を用いて、当該一の画素と当該他の画素から構成される対象領域における雑音除去処理を行う雑音除去装置であって、前記対象領域において前記走査線上に並ぶ前記画素の前記信号を記憶し、且つ前記対象領域における前記走査線の数に対応した数の記憶手段を備える雑音除去装置において、

前記対象領域における前記走査線上の画素数が、当該対象領域において前記走査線に垂直な方向の画素数より大きいことを特徴とする雑音除去装置。

【請求項2】

請求項1に記載の雑音除去装置において、

前記雑音除去装置は、前記一の画素の前記信号と、前記他の画素各々の前記信号と、差分値を、前記記憶手段を用いてそれぞれ検出する検出手段と、前記検出された各差分値と閾値とをそれぞれ比較する比較手段と、前記比較手段による比較結果に基づいて前記雑音除去処理の対象とすべき前記他の画素を特定する特定手段と、特定された前記他の画素それぞれについて、前記検出された差分値に対して予め設定されたフィルタ係数を乗算する乗算手段と、前記乗算手段による乗算結果を前記一の画素の前記信号に加算して出力する加算手段と、前記検出手段による検出処理、前記比較手段による比較処理、前記特定手段による特定処理、前記乗算手段による乗算処理、及び前記加算手段による加算処理を、前記デジタル画像を構成する各前記画素のそれぞれを前記一の画素として、前記デジタル画像を形成する各前記画素について繰り返す制御手段と、を備え、

前記対象領域における前記一の画素を通る前記走査線上の画素数が、当該対象領域における他の前記走査線上の画素数より大きいことを特徴とする雑音除去装置。

【請求項3】

請求項2に記載の雑音除去装置において、

前記加算手段は、前記加算処理のために前記一の画素の前記信号を記憶する加算用記憶手段を備え、

当該加算用記憶手段が、各前記画素の前記信号を記憶する前記記憶手段としても用いられることを特徴とする雑音除去装置。

【請求項4】

請求項1から請求項3のいずれか一項に記載の雑音除去装置において、

前記デジタル画像はデジタル静止画像であり、

前記他の画素は、当該デジタル静止画像内において前記一の画素について対称の位置にある前記画素であり、

前記フィルタ係数の値は、相互に前記対称の位置にある前記他の画素において同一とされることを特徴とする雑音除去装置。

【請求項5】

請求項1から請求項4のいずれか一項に記載の雑音除去装置において、

前記一の画素が含まれる前記対象領域を構成する前記他の画素の一部が仮想的に前記デジタル画像外となる場合において、

当該デジタル画像外となった前記他の画素の前記信号として、前記デジタル画像の外縁を対称軸として当該他の画素に対して対称の位置にある前記対象領域内の前記画素の前記信号を、前記雑音除去処理に供させる画素処理手段を備えることを特徴とする雑音除去装置。

【請求項6】

請求項1から請求項4のいずれか一項に記載の雑音除去装置において、

前記一の画素が含まれる前記対象領域を構成する前記他の画素の一部が仮想的に前記デジタル画像外となる場合において、

当該デジタル画像外となった前記他の画素の前記信号として、前記対象領域内の前記一の画素の前記信号を前記雑音除去処理に供させる画素処理手段を備えることを特徴とする雑音除去装置。

【請求項1】

一定方向の走査線により順次走査される複数の画素により形成されるデジタル画像における一の画素の信号と、当該一の画素の周囲の複数の他の画素の信号と、を用いて、当該一の画素と当該他の画素から構成される対象領域における雑音除去処理を行う雑音除去装置であって、前記対象領域において前記走査線上に並ぶ前記画素の前記信号を記憶し、且つ前記対象領域における前記走査線の数に対応した数の記憶手段を備える雑音除去装置において、

前記対象領域における前記走査線上の画素数が、当該対象領域において前記走査線に垂直な方向の画素数より大きいことを特徴とする雑音除去装置。

【請求項2】

請求項1に記載の雑音除去装置において、

前記雑音除去装置は、前記一の画素の前記信号と、前記他の画素各々の前記信号と、差分値を、前記記憶手段を用いてそれぞれ検出する検出手段と、前記検出された各差分値と閾値とをそれぞれ比較する比較手段と、前記比較手段による比較結果に基づいて前記雑音除去処理の対象とすべき前記他の画素を特定する特定手段と、特定された前記他の画素それぞれについて、前記検出された差分値に対して予め設定されたフィルタ係数を乗算する乗算手段と、前記乗算手段による乗算結果を前記一の画素の前記信号に加算して出力する加算手段と、前記検出手段による検出処理、前記比較手段による比較処理、前記特定手段による特定処理、前記乗算手段による乗算処理、及び前記加算手段による加算処理を、前記デジタル画像を構成する各前記画素のそれぞれを前記一の画素として、前記デジタル画像を形成する各前記画素について繰り返す制御手段と、を備え、

前記対象領域における前記一の画素を通る前記走査線上の画素数が、当該対象領域における他の前記走査線上の画素数より大きいことを特徴とする雑音除去装置。

【請求項3】

請求項2に記載の雑音除去装置において、

前記加算手段は、前記加算処理のために前記一の画素の前記信号を記憶する加算用記憶手段を備え、

当該加算用記憶手段が、各前記画素の前記信号を記憶する前記記憶手段としても用いられることを特徴とする雑音除去装置。

【請求項4】

請求項1から請求項3のいずれか一項に記載の雑音除去装置において、

前記デジタル画像はデジタル静止画像であり、

前記他の画素は、当該デジタル静止画像内において前記一の画素について対称の位置にある前記画素であり、

前記フィルタ係数の値は、相互に前記対称の位置にある前記他の画素において同一とされることを特徴とする雑音除去装置。

【請求項5】

請求項1から請求項4のいずれか一項に記載の雑音除去装置において、

前記一の画素が含まれる前記対象領域を構成する前記他の画素の一部が仮想的に前記デジタル画像外となる場合において、

当該デジタル画像外となった前記他の画素の前記信号として、前記デジタル画像の外縁を対称軸として当該他の画素に対して対称の位置にある前記対象領域内の前記画素の前記信号を、前記雑音除去処理に供させる画素処理手段を備えることを特徴とする雑音除去装置。

【請求項6】

請求項1から請求項4のいずれか一項に記載の雑音除去装置において、

前記一の画素が含まれる前記対象領域を構成する前記他の画素の一部が仮想的に前記デジタル画像外となる場合において、

当該デジタル画像外となった前記他の画素の前記信号として、前記対象領域内の前記一の画素の前記信号を前記雑音除去処理に供させる画素処理手段を備えることを特徴とする雑音除去装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−78064(P2013−78064A)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願番号】特願2011−217985(P2011−217985)

【出願日】平成23年9月30日(2011.9.30)

【出願人】(000002897)大日本印刷株式会社 (14,506)

【Fターム(参考)】

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願日】平成23年9月30日(2011.9.30)

【出願人】(000002897)大日本印刷株式会社 (14,506)

【Fターム(参考)】

[ Back to top ]