電力供給制御回路

【課題】従来技術の電力供給制御回路は、回路規模が増大するという問題があった。

【解決手段】本発明にかかる電力供給制御回路は、負荷に対する電力の供給を制御する出力トランジスタ32と、外部入力信号に基づいて出力トランジスタ32のオンオフを制御するための制御信号a,bを生成するゲート駆動回路31と、出力トランジスタ32のゲート−ソース間に設けられ、出力トランジスタ32をオフする場合、制御信号a,bに基づいて出力トランジスタ32のゲート電荷を放電するためのトランジスタ37と、トランジスタ37よりも緩やかに放電するためのトランジスタ39と、トランジスタ37に直列に接続され、出力トランジスタ32をオフする場合において、出力トランジスタ32のゲート電圧が所定の電圧レベルに低下したことを検出し、出力トランジスタ32のゲート電荷の放電を遮断するダイオード40aと、を備える。

【解決手段】本発明にかかる電力供給制御回路は、負荷に対する電力の供給を制御する出力トランジスタ32と、外部入力信号に基づいて出力トランジスタ32のオンオフを制御するための制御信号a,bを生成するゲート駆動回路31と、出力トランジスタ32のゲート−ソース間に設けられ、出力トランジスタ32をオフする場合、制御信号a,bに基づいて出力トランジスタ32のゲート電荷を放電するためのトランジスタ37と、トランジスタ37よりも緩やかに放電するためのトランジスタ39と、トランジスタ37に直列に接続され、出力トランジスタ32をオフする場合において、出力トランジスタ32のゲート電圧が所定の電圧レベルに低下したことを検出し、出力トランジスタ32のゲート電荷の放電を遮断するダイオード40aと、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電力供給制御回路に関し、特に負荷への電源供給を制御する出力トランジスタを有する電力供給制御回路に関する。

【背景技術】

【0002】

電源から負荷に対する電力の供給を制御する回路として電力供給制御回路が知られている。電力供給制御回路は、応用分野の一つとして、自動車のアクチュエータやランプを駆動するために用いられている。

【0003】

電力供給制御回路は、電源から負荷に対して電力を供給するか否かを切り替えるスイッチとして、出力トランジスタを備えている。例えば、ハイサイドスイッチ用の出力トランジスタには、NチャネルMOSトランジスタが用いられる。ここで、出力トランジスタをオン状態にする場合、電源電圧以上の電圧をゲートに印加してオン抵抗を十分に小さくする必要がある。一方、出力トランジスタをオフ状態にする場合、ゲートに蓄積された電荷を放電する必要があるが、スイッチング時のノイズを抑制するために、ターンオフ時間及びスルーレートに関して厳しい制約が設けられている。

【0004】

図7に、特許文献1に開示された半導体出力回路(電力供給制御回路)100の回路図を示す。図7に示すように、電力供給制御回路100は、ゲート駆動回路131と、出力トランジスタ132と、放電回路133と、電圧検出部134と、放電回路135と、を備える。電力供給制御回路100の回路構成については、特許文献中に詳細な説明が記載されているため、説明を省略する。図8は、図7の電力供給制御回路100の動作を説明するためのタイミングチャートである。なお、縦軸は電圧及び電流を示し、横軸は時間を示す。

【0005】

図7及び図8を参照して、電力供給制御回路100の動作について説明する。まず、時刻t1において、入力信号inおよび制御信号aがハイレベル(例えば、電源電圧Vcc)からロウレベル(例えば、接地電圧GND)に遷移する。同時に、制御信号bがロウレベルから電源電圧Vcc以上の電圧(例えば、Vcc+10V)に遷移する。時刻t2において、出力トランジスタ132のゲート電圧Gがロウレベルから電源電圧Vcc以上の電圧(例えばVcc+10V)に遷移する。それにより、出力トランジスタ132がオン状態となる。それにより、電力供給制御回路100は、電源から出力端子Toに対して電力を供給する。このとき、出力端子Toの出力電圧Voは、電源電圧Vccとほぼ同じ電圧レベルを示す。この出力電圧Voは、次段の負荷(不図示)に供給される。また、容量136には、NMOSトランジスタ138の寄生ダイオードを介して、出力電圧Voの電荷が充電される。制御信号cの電圧が出力電圧Voと同じ電圧レベルになるため、NMOSトランジスタ137はオフ状態となる。

【0006】

時刻t3において、入力信号inおよび制御信号aがロウレベルからハイレベル(電源電圧Vcc)に遷移する。同時に、ゲート駆動回路131において、制御信号bを出力する端子側がハイインピーダンス状態となる。このとき、デプレッション型のNMOSトランジスタ139はオン状態となる。そのため、出力トランジスタ132のゲート電荷は、電流制限素子140およびNMOSトランジスタ139を介して緩やかに放電される。

【0007】

さらに時刻t3において、制御信号cの電圧が、制御信号aの電圧に出力電圧Voを重畳した電圧レベルとなる。そのため、NMOSトランジスタ137がオン状態となる。それにより、出力トランジスタ132のゲート電荷が、NMOSトランジスタ137を介して高速に放電される。

【0008】

時刻t3から遅れ時間td経過後の時刻t4において、ゲート電圧Gが電源電圧Vccと同じ電圧レベルまで低下すると、出力電圧Voが低下し始める。時刻t5において、出力電圧Voが電源電圧VccよりもNMOSトランジスタ138のしきい値電圧hだけ低くなると、NMOSトランジスタ138がオン状態となる。これにより、NMOSトランジスタ137がオフ状態となる。つまり、出力トランジスタ132のゲート電荷は、NMOSトランジスタ137を介して放電されなくなる。一方、NMOSトランジスタ139を介した緩やかな放電は継続される。時刻t6において、放電が完了してゲート電圧Gがロウレベルになると、出力電圧Voもロウレベルとなる。なお、出力端子Toに接続される負荷(不図示)が抵抗性の場合、図8に示すように、出力電流Ioも、出力電圧Voと同様の変化を示す。

【0009】

このように、出力トランジスタ132をオン状態からオフ状態に切り替える場合において、出力電圧Voが電源電圧Vccと同等程度である場合、NMOSトランジスタ137がオン状態となる。それにより、出力トランジスタ132のゲート電荷は高速に放電される。その後、出力電圧Voが電源電圧VccよりもNMOSトランジスタ138のしきい値電圧だけ低くなった場合、NMOSトランジスタ137がオフ状態となる。それにより、出力トランジスタ132のゲート電荷は高速に放電されなくなる。

【0010】

一方、出力トランジスタ132をオン状態からオフ状態に切り替える場合において、NMOSトランジスタ139は、ロウレベルの制御信号aによってオン状態となる。それにより、出力トランジスタ132のゲート電荷は、電流制限素子140及びトランジスタ139を介して、NMOSトランジスタ137よりも緩やかに放電され続ける。

【0011】

つまり、電力供給制御回路100は、上記2つの放電経路を用いて放電動作を行うことにより、ターンオフ動作を開始してから(時刻t3)、出力電圧Voが変化を開始(時刻t4)するまでの時間(遅れ時間td)を短縮することができる。つまり、ターンオフ時間(時刻t3〜t6)を短縮することができる。同時に、電力供給制御回路100は、ターンオフ時の出力電圧Voのスルーレートを緩やかにすることができる。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2005−130245号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

図6は、出力トランジスタのオン抵抗及びゲート・ソース間電圧の特性を示す図である。縦軸がオン抵抗を示し、横軸がゲート・ソース間電圧を示す。図6に示すように、オン抵抗を十分に小さくするためには、ゲート電圧を十分に昇圧させる必要がある。しかし、出力トランジスタをオン状態からオフ状態に切り替える(ターンオフする)場合において、ゲート電圧が高い場合、ゲート電荷の放電に長い時間を要する。そのため、オフ時間に関する制約を満足することが困難である。一方、高速にゲート電荷を放電した場合、出力電圧(Vo)のスルーレートが大きくなるため、スイッチングノイズが大きくなってしまう。

【0014】

特許文献1は、このような問題を解決するために提案されたものである。しかし、従来技術の場合、ターンオフ時において、NMOSトランジスタ137を高速にオフ状態からオン状態に移行させるためには、容量136に多くの電荷を蓄積する必要があった。つまり、NMOSトランジスタ137を高速にオフ状態からオン状態に移行させるためには、容量136を十分に大きくする必要があった。そのため、従来技術では、回路規模が増大するという問題があった。

【課題を解決するための手段】

【0015】

本発明にかかる電力供給制御回路は、電源ラインと出力端子との間に設けられ、負荷に対する電力の供給を制御するNチャネル型の出力トランジスタと、外部入力信号に基づいて前記出力トランジスタのオンオフを制御するための制御信号を生成するゲート駆動回路と、前記出力トランジスタのゲート−ソース間に設けられ、前記出力トランジスタをオフする場合、前記制御信号に基づいて前記出力トランジスタのゲートに蓄積された電荷を放電するための第1のデプレション型NチャネルMOSトランジスタと、前記出力トランジスタのゲート−ソース間に設けられ、前記出力トランジスタをオフする場合、前記制御信号に基づいて前記出力トランジスタのゲートに蓄積された電荷を前記第1のデプレション型NチャネルMOSトランジスタよりも緩やかに放電するための第2のデプレション型NチャネルMOSトランジスタと、前記第1のデプレション型NチャネルMOSトランジスタに直列に接続され、前記出力トランジスタをオフする場合において、前記出力トランジスタのゲート電圧が所定の電圧レベルに低下したことを検出し、前記出力トランジスタのゲートに蓄積された電荷の放電を遮断する放電遮断回路と、を備える。

【0016】

上述のような回路構成により、回路規模の増大を抑制することができる。

【発明の効果】

【0017】

本発明により、回路規模の増大を抑制することが可能な電力供給制御回路を提供することができる。

【図面の簡単な説明】

【0018】

【図1】本発明の実施の形態1にかかる電力供給制御回路を示す図である。

【図2】本発明の実施の形態1にかかる電力供給制御回路の動作を示すタイミングチャートである。

【図3】本発明の実施の形態2にかかる電力供給制御回路を示す図である。

【図4】本発明の実施の形態3にかかる電力供給制御回路を示す図である。

【図5】本発明の実施の形態3にかかる電力供給制御回路に用いられるトランジスタの構造を示す図である。

【図6】出力トランジスタのオン抵抗及びゲート・ソース間電圧の特性を示す図である。

【図7】従来の電力供給制御回路を示す図ある。

【図8】従来の電力供給制御回路の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0019】

以下では、本発明を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。説明の明確化のため、必要に応じて重複説明は省略される。

【0020】

実施の形態1

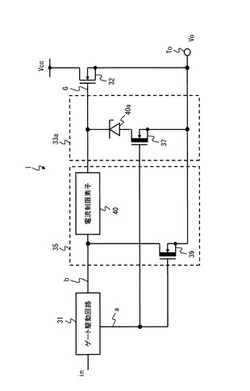

図1に、本発明の実施の形態1にかかる電力供給制御回路1の回路図を示す。図1に示す電力供給制御回路1は、ゲート駆動回路31と、出力トランジスタ32と、放電回路33aと、放電回路35と、を備える。また、放電回路33aは、トランジスタ(第1のデプレション型NチャネルMOSトランジスタ)37と、放電遮断回路40aと、を有する。放電回路35は、電流制限素子40と、トランジスタ(第2のデプレション型NチャネルMOSトランジスタ)39と、を有する。なお、出力トランジスタ32は、NチャネルMOSトランジスタである。トランジスタ37,39は、デプレッション型のNチャネルMOSトランジスタである。また、放電遮断回路40aとして、ツェナーダイオード40aが用いられている。

【0021】

ゲート駆動回路31では、入力端子が外部入力端子inに接続され、一方の出力端子がトランジスタ39のゲートに接続され、他方の出力端子が電流制限素子40の一方の端子に接続される。トランジスタ39では、ドレインが電流制限素子40の一方の端子に接続され、ソースが出力トランジスタ32のソースに接続される。出力トランジスタ32では、ドレインが電源電圧端子(電源ライン)Vccに接続され、ゲートが電流制限素子40の他方の端子に接続され、ドレインが外部出力端子(出力端子)Toに接続される。トランジスタ37では、ドレインがツェナーダイオード40aのアノードに接続され、ゲートがゲート駆動回路31の一方の出力端子に接続され、ソースが出力トランジスタ32のソースに接続される。ツェナーダイオード40aのカソードは、出力トランジスタ32のゲートに接続される。なお、便宜上、記号「Vcc」、「in」は、それぞれ端子名を示すと同時に、電源電圧、入力信号、を示すものとする。

【0022】

ゲート駆動回路31は、入力端子inを介して外部から供給された入力信号(外部入力信号)inに基づいて、制御信号a、bを生成する。

【0023】

より具体的には、ゲート駆動回路31は、ロウレベルの入力信号inに基づいてロウレベルの制御信号aを生成し、トランジスタ39のゲート及びトランジスタ37のゲートに対して出力する。同時に、ゲート駆動回路31は、電源電圧Vccよりも電圧レベルの高いハイレベルの制御信号bを生成し、電流制限素子40を介して出力トランジスタ32のゲートに対して出力する。このとき、ゲート駆動回路31は、内部に設けられたチャージポンプ回路(不図示)によって制御信号bの電圧を昇圧する。

【0024】

一方、ゲート駆動回路31は、ハイレベルの入力信号inに基づいてハイレベルの制御信号aを生成し、トランジスタ39のゲート及びトランジスタ37のゲートに対して出力する。同時に、ゲート駆動回路31は、制御信号bを出力する側の出力端子(他方の出力端子)をハイインピーダンス状態にする。

【0025】

出力トランジスタ32は、ゲートに印加される電圧(以下、ゲート電圧Gと称す)によってオンオフが制御される。例えば、出力トランジスタ32は、ハイレベルの制御信号bによってオン状態に制御される。それにより、電力供給制御回路1は、電源電圧端子Vccから外部出力端子Toに対して電力を供給する。そして、この電力は後段の負荷(不図示)に供給される。このとき、外部出力端子Toの電圧(出力電圧Vo)は、電源電圧Vccとほぼ同じ電圧レベルを示す。

【0026】

また、出力トランジスタ32は、放電回路33a,35を介してゲート電荷が放電されることにより、オフ状態に制御される。それにより、電力供給制御回路1は、電源電圧端子Vccから外部出力端子Toに対して電力の供給を停止する。

【0027】

放電回路33aは、出力トランジスタ32をオン状態からオフ状態に切り替える(ターンオフする)場合に、出力トランジスタ32のゲート−ソース間を電気的に接続する第1の電流経路を形成する。つまり、出力トランジスタ32のゲート−ソース間は、ツェナーダイオード40a及びトランジスタ37を介して、第1の電流経路を形成する。なお、トランジスタ37は、制御信号aに基づいてオンオフが制御される。また、ツェナーダイオード40aは、出力トランジスタ32のゲート−ソース間電圧に基づいてオンオフが制御される。

【0028】

例えば、出力トランジスタ32をオフ状態からオン状態に切り替える(ターンオンする)場合、トランジスタ37はロウレベルの制御信号aに基づいてオフ状態に制御される。つまり、出力トランジスタ32をターンオンする場合、第1の電流経路は遮断される。

【0029】

一方、出力トランジスタ32をターンオフする場合、トランジスタ37はハイレベルの制御信号aに基づいてオン状態に制御される。このとき、出力トランジスタ32のゲート−ソース間電圧がツェナーダイオード40aの降伏電圧以上の場合には、第1の電流経路は導通状態となる。それにより、出力トランジスタ32のゲート電荷は、第1の電流経路を介して放電される。他方、出力トランジスタ32のゲート−ソース間電圧がツェナーダイオード40aの降伏電圧よりも低い場合には、第1の電流経路は遮断される。それにより、出力トランジスタ32のゲート電荷は、第1の電流経路を介して放電されなくなる。なお、第1の電流経路は、後述する第2の電流経路よりも、急速に出力トランジスタ32のゲート電荷を放電する。また、本実施の形態では、ツェナーダイオード40aの耐圧は、製造上の公差が小さく温度依存性の少ない、6V程度に設定されている。

【0030】

放電回路35は、出力トランジスタ32をターンオフする場合に、出力トランジスタ32のゲート−ソース間を電気的に接続する第2の電流経路を形成する。つまり、出力トランジスタ32のゲート−ソース間は、電流制限素子40及びトランジスタ39を介して、第2の電流経路を形成する。なお、トランジスタ39は、制御信号aに基づいてオンオフが制御される。また、電流制限素子40は、例えば抵抗等により構成され、トランジスタ39に流れる電流を制限する。

【0031】

例えば、出力トランジスタ32をターンオンする場合、トランジスタ39はロウレベルの制御信号aに基づいてオフ状態に制御される。一方、出力トランジスタ32をターンオフする場合、トランジスタ39はハイレベルの制御信号aに基づいてオン状態に制御される。なお、本実施の形態では、第2の電流経路は、第1の電流経路よりも、緩やかに出力トランジスタ32のゲート電荷を放電する。

【0032】

次に、図1に示す回路の動作について、図2を用いてさらに具体的に説明する。図2は、本実施の形態にかかる電力供給制御回路1の動作を示すタイミングチャートである。なお、縦軸は電圧及び電流を示し、横軸は時間を示す。

【0033】

まず、時刻t1において、出力トランジスタ32のターンオン動作が開始する。つまり、入力信号inがハイレベル(例えば電源電圧Vcc)からロウレベル(例えば接地電圧)に遷移する。それにより、制御信号aはハイレベルからロウレベルに遷移する。同時に、制御信号bはロウレベルから電源電圧Vcc以上の電圧(例えば、電源電圧Vcc+10V)に遷移する。

【0034】

時刻t2において、出力トランジスタ32のゲート電圧Gは、ロウレベルから電源電圧Vcc以上の電圧(例えば電源電圧Vcc+10V)に遷移する。それにより、出力トランジスタ32はオン状態となる。それにより、電力供給制御回路1は、電源電圧端子Vccから外部出力端子Toに対して電力を供給する。このとき、出力電圧Voは電源電圧Vccとほぼ同じ電圧レベルを示す。なお、トランジスタ37は、ゲートにロウレベルの制御信号aが印加され、ソースに電源電圧Vccが印加されているため、オフ状態となっている。

【0035】

次に、時刻t3において、出力トランジスタ32のターンオフ動作が開始する。つまり、入力信号inがロウレベルからハイレベルに遷移する。それにより、制御信号aはロウレベルからハイレベルに遷移する。同時に、ゲート駆動回路31の制御信号bを出力する側の出力端子(他方の出力端子)が、ハイインピーダンス状態になる。

【0036】

このとき、トランジスタ37は、ゲートにハイレベルの制御信号aが印加され、ソースに出力電圧Voが印加されるため、オン状態となる。それにより、出力トランジスタ32のゲート電荷は、ツェナーダイオード40a及びトランジスタ37を介して、高速に放電される。つまり、出力トランジスタ32のゲート電荷は、第1の電流経路を介して、高速に放電される。

【0037】

また、トランジスタ39は、ゲートにハイレベルの制御信号aが印加され、ソースに出力電圧Voが印加されるため、オン状態となる。それにより、出力トランジスタ32のゲート電荷は、電流制限素子40及びトランジスタ39を介して、放電される。つまり、出力トランジスタ32のゲート電荷は、第1の電流経路に加え、さらに第2の電流経路を介して、放電される。

【0038】

時刻t4において、ゲート電圧Gが電源電圧Vcc+6Vまで低下した場合、第1の電流経路が遮断される。時刻t4以降、出力トランジスタ32のゲート電荷は、第2の電流経路のみを介して、緩やかに放電される。その後、出力トランジスタ32のゲート電圧がさらに低下すると、時刻t3から遅れ時間td経過後の時刻t5において、出力電圧Voが低下し始める。

【0039】

時刻t6において、放電が完了してゲート電圧Gがロウレベルになると、出力トランジスタ32はオフ状態となる。それにより、出力電圧Voはロウレベルになる。なお、出力端子Toに接続される負荷(不図示)が抵抗性の場合、図2に示すように、出力電流Ioも、出力電圧Voと同様の変化を示す。

【0040】

このように、電力供給制御回路1は、ターンオフ時において、出力トランジスタ32のゲート電圧が電源電圧Vccよりも十分に高い(例えば、電源電圧Vcc+10V)場合には、第1及び第2の電流経路を介して、出力トランジスタ32のゲート電荷を高速に放電する。そして、電力供給制御回路1は、ターンオフ時において、出力トランジスタ32のゲート電圧が電源電圧Vccよりも6V程度高い電圧まで低下すると、第1の電流経路を遮断し、第2の電流経路のみを介して、出力トランジスタ32のゲート電荷を緩やかに放電する。

【0041】

このような回路構成により、電力供給制御回路1は、出力トランジスタ32のゲート電圧が電源電圧Vccよりも十分に高い電圧に昇圧された場合でも、ターンオフ動作を開始してから(時刻t3)、出力電圧Voが変化を開始(時刻t5)するまでの時間(遅れ時間td)を短縮することができる。つまり、ターンオフ時間(時刻t3〜t6)を短縮することができる。ここで、電力供給制御回路1は、出力電圧Voが電源電圧Vccよりも低くなる前に、第1の電流経路を遮断する。そのため、電力供給制御回路1では、従来技術と異なり、出力電圧Voの波形に歪みが生じない。それにより、電力供給制御回路1は、出力電圧Voのノイズを抑制することができる。同時に、電力供給制御回路1は、ターンオフ時における出力電圧Voのスルーレートを小さくすることができる。

【0042】

また、従来技術の場合、ターンオフ時において、NMOSトランジスタ137を高速にオン状態に移行させるために、容量136を十分に大きくする必要があった。そのため、従来技術では、回路規模が増大するという問題があった。一方、電力供給制御回路1は、従来技術と異なり容量136を用いないため、回路規模の増大を抑制することができる。なお、電力供給制御回路1は、容量136を用いたブートストラップ回路を用いず、デプレッション型のNチャネルMOSトランジスタ37を用いて第1の電流経路を形成する。

【0043】

実施の形態2

図3に、本発明の実施の形態2にかかる電力供給制御回路2の回路図を示す。図3に示す電力供給制御回路2は、図1に示す電力供給制御回路1と比較して、放電回路33aの代わりに放電回路33bを備える。放電回路33bは、トランジスタ37と放電遮断回路40bとを有する。放電遮断回路40bは、ゲート−ドレイン間が共通接続されたNチャネルMOSトランジスタ40b1〜40bn(nは自然数)を複数有する。トランジスタ40b1〜40bnは、出力トランジスタ32のゲートとトランジスタ37のドレインとの間に直列に接続される。その他の回路構成については、図1に示す回路と同様であるため説明を省略する。

【0044】

図1に示す電力供給制御回路1は、ターンオフ時において、出力トランジスタ32のゲート電圧Gが電源電圧Vcc+6Vまで低下した場合に、第1の電流経路を遮断していた。一方、図3に示す電力供給制御回路2は、ターンオフ時において、出力トランジスタ32のゲート電圧Gが電源電圧Vccのさらに近傍まで低下した場合に、第1の電流経路を遮断することができる。つまり、電力供給制御回路2は、図2のターンオフ時間(時刻t3〜t6)のうち、時刻t3〜t4の期間の占める割合を増加させることができる。それにより、電力供給制御回路2は、実施の形態1の場合と比較して、ターンオフ時間を短くすることができる。また、電力供給制御回路2は、実施の形態1の場合と同様に、容量136からなるブートストラップ回路を用いないため、回路規模の増大を抑制することができる。

【0045】

図3の動作について、図2を用いて説明する。時刻t3において、出力トランジスタ32のターンオフ動作が開始する。つまり、入力信号inがロウレベルからハイレベルに遷移する。それにより、制御信号aはロウレベルからハイレベルに遷移する。同時に、ゲート駆動回路31の制御信号bを出力する側の出力端子(他方の出力端子)が、ハイインピーダンス状態になる。

【0046】

このとき、トランジスタ37は、ゲートにハイレベルの制御信号aが印加され、ソースに電源電圧Vccが印加されるため、オン状態となる。それにより、出力トランジスタ32のゲート電荷は、放電遮断回路40b及びトランジスタ37を介して、高速に放電される。つまり、出力トランジスタ32のゲート電荷は、第1の電流経路を介して、高速に放電される。

【0047】

そして、出力トランジスタ32のゲート電圧Gが、トランジスタ40b1〜40bnのしきい値電圧と電源電圧Vccとの合計程度まで低下すると、トランジスタ40b1〜40bnがオフ状態となり、第1の電流経路が遮断される。ここで、トランジスタ40b1〜40bnのしきい値電圧の合計を、出力トランジスタ32のしきい値電圧よりわずかに高く設定しておく。それにより、電力供給制御回路2は、出力電圧Voが電源電圧Vccより低くなる前に、第1の電流経路を遮断することができる。そのため、電力供給制御回路2では、実施の形態1の場合と同様に、出力電圧Voの波形に歪みが生じない。つまり、電力供給制御回路2は、出力電圧Voのノイズを抑制することができる。同時に、電力供給制御回路2は、ターンオフ時における出力電圧Voのスルーレートを小さくすることができる。また、電力供給制御回路2は、実施の形態1の場合と同様に、容量136からなるブートストラップ回路を用いないため、回路規模の増大を抑制することができる。その他の動作については、実施の形態1の場合と同様であるため、説明を省略する。

【0048】

例えば、放電遮断回路40bが2個のトランジスタ40b1,40b2(n=2)を有する場合について説明する。なお、各トランジスタ40b1,40b2のしきい値電圧は2V程度である。この例では、ターンオフ時において、出力トランジスタ32のゲート電圧Gが電源電圧Vcc+4V程度まで低下すると、第1の電流経路が遮断される。このように、本実施の形態では、実施の形態1と比較して、出力トランジスタ32のゲート電圧Gが電源電圧Vccのさらに近傍まで低下した場合に、第1の電流経路を遮断することができる。

【0049】

実施の形態3

図4に、本発明の実施の形態3にかかる電力供給制御回路3の回路図を示す。図4に示す電力供給制御回路3は、図1に示す電力供給制御回路1と比較して、放電回路33aの代わりに放電回路33cを備える。放電回路33cは、トランジスタ37と放電遮断回路40cとを有する。なお、放電遮断回路40cとして、NチャネルMOSトランジスタ40cが用いられている。トランジスタ40cでは、ゲート及びドレインが出力トランジスタ32のゲートに共通接続され、ソースがトランジスタ37のドレインに接続される。その他の回路構成については、図1に示す回路と同様であるため、説明を省略する。

【0050】

実施の形態2では、トランジスタ40b1〜40bnの個数に応じて、第1の電流経路を遮断するか否かのしきい値電圧を調整していた。一方、本実施の形態では、出力トランジスタと同等程度のしきい値電圧を有するトランジスタ40cを用いることにより、第1の電流経路を遮断するか否かのしきい値電圧を調整する。それにより、電力供給制御回路3は、ターンオフ時において、出力トランジスタ32のゲート電圧Gが電源電圧Vccのさらに近傍まで低下した場合に、第1の電流経路を遮断することができる。つまり、本実施の形態にかかる電力供給制御回路3は、実施の形態2の場合と比較して、ターンオフ時間を短くすることができる。また、電力供給制御回路3は、上記実施の形態の場合と同様に、容量136からなるブートストラップ回路を用いないため、回路規模の増大を抑制することができる。

【0051】

図4の動作について、図2を用いて説明する。時刻t3において、出力トランジスタ32のターンオフ動作が開始する。つまり、入力信号inがロウレベルからハイレベルに遷移する。それにより、制御信号aはロウレベルからハイレベルに遷移する。同時に、ゲート駆動回路31の制御信号bを出力する側の出力端子(他方の出力端子)が、ハイインピーダンス状態になる。

【0052】

このとき、トランジスタ37は、ゲートにハイレベルの制御信号aが印加され、ソースに電源電圧Vccが印加されるため、オン状態となる。それにより、出力トランジスタ32のゲート電荷は、放電遮断回路40b及びトランジスタ37を介して、高速に放電される。つまり、出力トランジスタ32のゲート電荷は、第1の電流経路を介して、高速に放電される。

【0053】

そして、出力トランジスタ32のゲート電圧Gが、トランジスタ40cのしきい値電圧と電源電圧Vccとの合計程度まで低下すると、トランジスタ40cがオフ状態となり、第1の電流経路が遮断される。ここで、トランジスタ40cのしきい値電圧を、出力トランジスタ32のしきい値電圧よりわずかに高く設定しておく。それにより、電力供給制御回路3は、出力電圧Voが電源電圧Vccより低くなる前に、第1の電流経路を遮断することができる。

【0054】

なお、このような設定は、トランジスタ40c及び出力トランジスタ32のしきい値電圧を決定する拡散層を同じにすることにより、容易に実現可能である。図5に、トランジスタ40c及び出力トランジスタ32のトランジスタ構造の断面図を示す。

【0055】

トランジスタ40cは、n−基板50を有する。n−基板50の下側には、背面接触のためのn+拡散層51が設けられている。また、n−基板50上には第1のp−拡散層52が設けられている。第1のp−拡散層52に相対する表面に2つのn+拡散層53,54が位置している。なお、一方のn+拡散層(凹み拡散層)53は、ソース端子Sに接続されている。他方のn+拡散層54は、ドレイン端子Dに接続されている。また、両n+拡散層53,54の間には、より浅い深さのn−拡散層55が位置している。なお、n−拡散層55は、n+拡散層54に隣接している。

【0056】

n+拡散層53及びn−拡散層55間は、長さLのチャネル領域を有する。チャネル上には、ゲート電極56が配置されている。そして、ゲート電極56はゲート端子Gに接続されている。また、n+拡散層53は、第1のp−拡散層52よりも濃度の濃い第2のp−拡散層57に囲われている。第2のp−拡散層57は、p+拡散層58を介して基板端子BGに接続されている。

【0057】

出力トランジスタ32は、n−基板60を有する。n−基板60の下側には、背面接触のためのn+拡散層61が設けられている。なお、このn+拡散層61は、ドレイン端子Dに接続されている。また、n−基板60上には、トランジスタ40cに用いられているものと同一の第2のp−拡散層57が設けられている。この第2のp−拡散層57は、p+拡散層62を介して基板端子BGに接続されている。

【0058】

第2のp−拡散層57に相対する表面に2つのn+拡散層63,64が位置している。なお、n+拡散層63,64は、いずれもソース端子Sに接続されている。また、両n+拡散層63,64の間に、p+拡散層62が位置している。チャネル上には、ゲート電極65が配置されている。そして、ゲート電極65はゲート端子Gに接続されている。

【0059】

図5に示す例のように、トランジスタ40c及び出力トランジスタ32のしきい値電圧は、いずれも同一のp−拡散層57に基づいて決定される。それにより、両トランジスタのしきい値電圧はほぼ等しくなる。また、両トランジスタのしきい値電圧は製造上の公差に対して連動する。

【0060】

このような回路構成により、本実施の形態にかかる電力供給制御回路3では、上記実施の形態の場合と同様に、出力電圧Voの波形に歪みが生じない。つまり、電力供給制御回路3は、出力電圧Voのノイズを抑制することができる。同時に、電力供給制御回路3は、ターンオフ時における出力電圧Voのスルーレートを小さくすることができる。また、本実施の形態にかかる電力供給制御回路3は、上記実施の形態の場合と同様に、容量136からなるブートストラップ回路を用いないため、回路規模の増大を抑制することができる。その他の動作については、上記実施の形態の場合と同様であるため、説明を省略する。

【0061】

例えば、出力トランジスタ32及びトランジスタ40cのしきい値電圧がそれぞれ2Vである場合について説明する。この例では、ターンオフ時において、出力トランジスタ32のゲート電圧Gが電源電圧Vcc+2V程度まで低下すると、第1の電流経路が遮断される。このように、本実施の形態では、実施の形態2と比較して、出力トランジスタ32のゲート電圧Gが電源電圧Vccのさらに近傍まで低下してから、第1の電流経路を遮断することができる。

【0062】

以上のように、上記実施の形態にかかる電力供給制御回路は、ターンオフ時において、出力トランジスタ32のゲート電圧が電源電圧Vccよりも十分に高い場合には、第1及び第2の電流経路を介して、出力トランジスタ32のゲート電荷を高速に放電する。そして、上記実施の形態にかかる電力供給制御回路は、ターンオフ時において、出力トランジスタ32のゲート電圧Gが電源電圧Vccの近傍まで低下すると、第1の電流経路を遮断し、第2の電流経路のみを介して、出力トランジスタ32のゲート電荷を緩やかに放電する。

【0063】

このような回路構成により、上記実施の形態にかかる電力供給制御回路は、出力トランジスタ32のゲート電圧が電源電圧Vccよりも十分に高い電圧に昇圧された場合でも、ターンオフ動作を開始してから(時刻t3)、出力電圧Voが変化を開始(時刻t5)するまでの時間(遅れ時間td)を短縮することができる。つまり、ターンオフ時間(時刻t3〜t6)を短縮することができる。ここで、上記実施の形態にかかる電力供給制御回路は、出力電圧Voが電源電圧Vccよりも低くなる前に、第1の電流経路を遮断する。そのため、上記実施の形態にかかる電力供給制御回路では、従来技術と異なり、出力電圧Voの波形に歪みが生じない。それにより、上記実施の形態にかかる電力供給制御回路は、出力電圧Voのノイズを抑制することができる。同時に、上記実施の形態にかかる電力供給制御回路は、ターンオフ時における出力電圧Voのスルーレートを小さくすることができる。

【0064】

また、上記実施の形態にかかる電力供給制御回路は、従来技術と異なり、容量136からなるブートストラップ回路を用いないため、回路規模の増大を抑制することができる。

【0065】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。上記実施の形態では、電流制限素子40に抵抗を用いた場合を例に説明したが、これに限られない。例えば、デプレッション型のNチャネルMOSトランジスタのゲートとソースとを接続した定電流素子を用いてもよい。

【符号の説明】

【0066】

1〜3 電力供給制御回路

31 ゲート駆動回路

32 出力トランジスタ

33a,33b,33c 放電回路

35 放電回路

37,39 トランジスタ

40 電流制限素子

40a,40b,40c 放電遮断回路

40b1〜40bn トランジスタ

【技術分野】

【0001】

本発明は、電力供給制御回路に関し、特に負荷への電源供給を制御する出力トランジスタを有する電力供給制御回路に関する。

【背景技術】

【0002】

電源から負荷に対する電力の供給を制御する回路として電力供給制御回路が知られている。電力供給制御回路は、応用分野の一つとして、自動車のアクチュエータやランプを駆動するために用いられている。

【0003】

電力供給制御回路は、電源から負荷に対して電力を供給するか否かを切り替えるスイッチとして、出力トランジスタを備えている。例えば、ハイサイドスイッチ用の出力トランジスタには、NチャネルMOSトランジスタが用いられる。ここで、出力トランジスタをオン状態にする場合、電源電圧以上の電圧をゲートに印加してオン抵抗を十分に小さくする必要がある。一方、出力トランジスタをオフ状態にする場合、ゲートに蓄積された電荷を放電する必要があるが、スイッチング時のノイズを抑制するために、ターンオフ時間及びスルーレートに関して厳しい制約が設けられている。

【0004】

図7に、特許文献1に開示された半導体出力回路(電力供給制御回路)100の回路図を示す。図7に示すように、電力供給制御回路100は、ゲート駆動回路131と、出力トランジスタ132と、放電回路133と、電圧検出部134と、放電回路135と、を備える。電力供給制御回路100の回路構成については、特許文献中に詳細な説明が記載されているため、説明を省略する。図8は、図7の電力供給制御回路100の動作を説明するためのタイミングチャートである。なお、縦軸は電圧及び電流を示し、横軸は時間を示す。

【0005】

図7及び図8を参照して、電力供給制御回路100の動作について説明する。まず、時刻t1において、入力信号inおよび制御信号aがハイレベル(例えば、電源電圧Vcc)からロウレベル(例えば、接地電圧GND)に遷移する。同時に、制御信号bがロウレベルから電源電圧Vcc以上の電圧(例えば、Vcc+10V)に遷移する。時刻t2において、出力トランジスタ132のゲート電圧Gがロウレベルから電源電圧Vcc以上の電圧(例えばVcc+10V)に遷移する。それにより、出力トランジスタ132がオン状態となる。それにより、電力供給制御回路100は、電源から出力端子Toに対して電力を供給する。このとき、出力端子Toの出力電圧Voは、電源電圧Vccとほぼ同じ電圧レベルを示す。この出力電圧Voは、次段の負荷(不図示)に供給される。また、容量136には、NMOSトランジスタ138の寄生ダイオードを介して、出力電圧Voの電荷が充電される。制御信号cの電圧が出力電圧Voと同じ電圧レベルになるため、NMOSトランジスタ137はオフ状態となる。

【0006】

時刻t3において、入力信号inおよび制御信号aがロウレベルからハイレベル(電源電圧Vcc)に遷移する。同時に、ゲート駆動回路131において、制御信号bを出力する端子側がハイインピーダンス状態となる。このとき、デプレッション型のNMOSトランジスタ139はオン状態となる。そのため、出力トランジスタ132のゲート電荷は、電流制限素子140およびNMOSトランジスタ139を介して緩やかに放電される。

【0007】

さらに時刻t3において、制御信号cの電圧が、制御信号aの電圧に出力電圧Voを重畳した電圧レベルとなる。そのため、NMOSトランジスタ137がオン状態となる。それにより、出力トランジスタ132のゲート電荷が、NMOSトランジスタ137を介して高速に放電される。

【0008】

時刻t3から遅れ時間td経過後の時刻t4において、ゲート電圧Gが電源電圧Vccと同じ電圧レベルまで低下すると、出力電圧Voが低下し始める。時刻t5において、出力電圧Voが電源電圧VccよりもNMOSトランジスタ138のしきい値電圧hだけ低くなると、NMOSトランジスタ138がオン状態となる。これにより、NMOSトランジスタ137がオフ状態となる。つまり、出力トランジスタ132のゲート電荷は、NMOSトランジスタ137を介して放電されなくなる。一方、NMOSトランジスタ139を介した緩やかな放電は継続される。時刻t6において、放電が完了してゲート電圧Gがロウレベルになると、出力電圧Voもロウレベルとなる。なお、出力端子Toに接続される負荷(不図示)が抵抗性の場合、図8に示すように、出力電流Ioも、出力電圧Voと同様の変化を示す。

【0009】

このように、出力トランジスタ132をオン状態からオフ状態に切り替える場合において、出力電圧Voが電源電圧Vccと同等程度である場合、NMOSトランジスタ137がオン状態となる。それにより、出力トランジスタ132のゲート電荷は高速に放電される。その後、出力電圧Voが電源電圧VccよりもNMOSトランジスタ138のしきい値電圧だけ低くなった場合、NMOSトランジスタ137がオフ状態となる。それにより、出力トランジスタ132のゲート電荷は高速に放電されなくなる。

【0010】

一方、出力トランジスタ132をオン状態からオフ状態に切り替える場合において、NMOSトランジスタ139は、ロウレベルの制御信号aによってオン状態となる。それにより、出力トランジスタ132のゲート電荷は、電流制限素子140及びトランジスタ139を介して、NMOSトランジスタ137よりも緩やかに放電され続ける。

【0011】

つまり、電力供給制御回路100は、上記2つの放電経路を用いて放電動作を行うことにより、ターンオフ動作を開始してから(時刻t3)、出力電圧Voが変化を開始(時刻t4)するまでの時間(遅れ時間td)を短縮することができる。つまり、ターンオフ時間(時刻t3〜t6)を短縮することができる。同時に、電力供給制御回路100は、ターンオフ時の出力電圧Voのスルーレートを緩やかにすることができる。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2005−130245号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

図6は、出力トランジスタのオン抵抗及びゲート・ソース間電圧の特性を示す図である。縦軸がオン抵抗を示し、横軸がゲート・ソース間電圧を示す。図6に示すように、オン抵抗を十分に小さくするためには、ゲート電圧を十分に昇圧させる必要がある。しかし、出力トランジスタをオン状態からオフ状態に切り替える(ターンオフする)場合において、ゲート電圧が高い場合、ゲート電荷の放電に長い時間を要する。そのため、オフ時間に関する制約を満足することが困難である。一方、高速にゲート電荷を放電した場合、出力電圧(Vo)のスルーレートが大きくなるため、スイッチングノイズが大きくなってしまう。

【0014】

特許文献1は、このような問題を解決するために提案されたものである。しかし、従来技術の場合、ターンオフ時において、NMOSトランジスタ137を高速にオフ状態からオン状態に移行させるためには、容量136に多くの電荷を蓄積する必要があった。つまり、NMOSトランジスタ137を高速にオフ状態からオン状態に移行させるためには、容量136を十分に大きくする必要があった。そのため、従来技術では、回路規模が増大するという問題があった。

【課題を解決するための手段】

【0015】

本発明にかかる電力供給制御回路は、電源ラインと出力端子との間に設けられ、負荷に対する電力の供給を制御するNチャネル型の出力トランジスタと、外部入力信号に基づいて前記出力トランジスタのオンオフを制御するための制御信号を生成するゲート駆動回路と、前記出力トランジスタのゲート−ソース間に設けられ、前記出力トランジスタをオフする場合、前記制御信号に基づいて前記出力トランジスタのゲートに蓄積された電荷を放電するための第1のデプレション型NチャネルMOSトランジスタと、前記出力トランジスタのゲート−ソース間に設けられ、前記出力トランジスタをオフする場合、前記制御信号に基づいて前記出力トランジスタのゲートに蓄積された電荷を前記第1のデプレション型NチャネルMOSトランジスタよりも緩やかに放電するための第2のデプレション型NチャネルMOSトランジスタと、前記第1のデプレション型NチャネルMOSトランジスタに直列に接続され、前記出力トランジスタをオフする場合において、前記出力トランジスタのゲート電圧が所定の電圧レベルに低下したことを検出し、前記出力トランジスタのゲートに蓄積された電荷の放電を遮断する放電遮断回路と、を備える。

【0016】

上述のような回路構成により、回路規模の増大を抑制することができる。

【発明の効果】

【0017】

本発明により、回路規模の増大を抑制することが可能な電力供給制御回路を提供することができる。

【図面の簡単な説明】

【0018】

【図1】本発明の実施の形態1にかかる電力供給制御回路を示す図である。

【図2】本発明の実施の形態1にかかる電力供給制御回路の動作を示すタイミングチャートである。

【図3】本発明の実施の形態2にかかる電力供給制御回路を示す図である。

【図4】本発明の実施の形態3にかかる電力供給制御回路を示す図である。

【図5】本発明の実施の形態3にかかる電力供給制御回路に用いられるトランジスタの構造を示す図である。

【図6】出力トランジスタのオン抵抗及びゲート・ソース間電圧の特性を示す図である。

【図7】従来の電力供給制御回路を示す図ある。

【図8】従来の電力供給制御回路の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0019】

以下では、本発明を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。説明の明確化のため、必要に応じて重複説明は省略される。

【0020】

実施の形態1

図1に、本発明の実施の形態1にかかる電力供給制御回路1の回路図を示す。図1に示す電力供給制御回路1は、ゲート駆動回路31と、出力トランジスタ32と、放電回路33aと、放電回路35と、を備える。また、放電回路33aは、トランジスタ(第1のデプレション型NチャネルMOSトランジスタ)37と、放電遮断回路40aと、を有する。放電回路35は、電流制限素子40と、トランジスタ(第2のデプレション型NチャネルMOSトランジスタ)39と、を有する。なお、出力トランジスタ32は、NチャネルMOSトランジスタである。トランジスタ37,39は、デプレッション型のNチャネルMOSトランジスタである。また、放電遮断回路40aとして、ツェナーダイオード40aが用いられている。

【0021】

ゲート駆動回路31では、入力端子が外部入力端子inに接続され、一方の出力端子がトランジスタ39のゲートに接続され、他方の出力端子が電流制限素子40の一方の端子に接続される。トランジスタ39では、ドレインが電流制限素子40の一方の端子に接続され、ソースが出力トランジスタ32のソースに接続される。出力トランジスタ32では、ドレインが電源電圧端子(電源ライン)Vccに接続され、ゲートが電流制限素子40の他方の端子に接続され、ドレインが外部出力端子(出力端子)Toに接続される。トランジスタ37では、ドレインがツェナーダイオード40aのアノードに接続され、ゲートがゲート駆動回路31の一方の出力端子に接続され、ソースが出力トランジスタ32のソースに接続される。ツェナーダイオード40aのカソードは、出力トランジスタ32のゲートに接続される。なお、便宜上、記号「Vcc」、「in」は、それぞれ端子名を示すと同時に、電源電圧、入力信号、を示すものとする。

【0022】

ゲート駆動回路31は、入力端子inを介して外部から供給された入力信号(外部入力信号)inに基づいて、制御信号a、bを生成する。

【0023】

より具体的には、ゲート駆動回路31は、ロウレベルの入力信号inに基づいてロウレベルの制御信号aを生成し、トランジスタ39のゲート及びトランジスタ37のゲートに対して出力する。同時に、ゲート駆動回路31は、電源電圧Vccよりも電圧レベルの高いハイレベルの制御信号bを生成し、電流制限素子40を介して出力トランジスタ32のゲートに対して出力する。このとき、ゲート駆動回路31は、内部に設けられたチャージポンプ回路(不図示)によって制御信号bの電圧を昇圧する。

【0024】

一方、ゲート駆動回路31は、ハイレベルの入力信号inに基づいてハイレベルの制御信号aを生成し、トランジスタ39のゲート及びトランジスタ37のゲートに対して出力する。同時に、ゲート駆動回路31は、制御信号bを出力する側の出力端子(他方の出力端子)をハイインピーダンス状態にする。

【0025】

出力トランジスタ32は、ゲートに印加される電圧(以下、ゲート電圧Gと称す)によってオンオフが制御される。例えば、出力トランジスタ32は、ハイレベルの制御信号bによってオン状態に制御される。それにより、電力供給制御回路1は、電源電圧端子Vccから外部出力端子Toに対して電力を供給する。そして、この電力は後段の負荷(不図示)に供給される。このとき、外部出力端子Toの電圧(出力電圧Vo)は、電源電圧Vccとほぼ同じ電圧レベルを示す。

【0026】

また、出力トランジスタ32は、放電回路33a,35を介してゲート電荷が放電されることにより、オフ状態に制御される。それにより、電力供給制御回路1は、電源電圧端子Vccから外部出力端子Toに対して電力の供給を停止する。

【0027】

放電回路33aは、出力トランジスタ32をオン状態からオフ状態に切り替える(ターンオフする)場合に、出力トランジスタ32のゲート−ソース間を電気的に接続する第1の電流経路を形成する。つまり、出力トランジスタ32のゲート−ソース間は、ツェナーダイオード40a及びトランジスタ37を介して、第1の電流経路を形成する。なお、トランジスタ37は、制御信号aに基づいてオンオフが制御される。また、ツェナーダイオード40aは、出力トランジスタ32のゲート−ソース間電圧に基づいてオンオフが制御される。

【0028】

例えば、出力トランジスタ32をオフ状態からオン状態に切り替える(ターンオンする)場合、トランジスタ37はロウレベルの制御信号aに基づいてオフ状態に制御される。つまり、出力トランジスタ32をターンオンする場合、第1の電流経路は遮断される。

【0029】

一方、出力トランジスタ32をターンオフする場合、トランジスタ37はハイレベルの制御信号aに基づいてオン状態に制御される。このとき、出力トランジスタ32のゲート−ソース間電圧がツェナーダイオード40aの降伏電圧以上の場合には、第1の電流経路は導通状態となる。それにより、出力トランジスタ32のゲート電荷は、第1の電流経路を介して放電される。他方、出力トランジスタ32のゲート−ソース間電圧がツェナーダイオード40aの降伏電圧よりも低い場合には、第1の電流経路は遮断される。それにより、出力トランジスタ32のゲート電荷は、第1の電流経路を介して放電されなくなる。なお、第1の電流経路は、後述する第2の電流経路よりも、急速に出力トランジスタ32のゲート電荷を放電する。また、本実施の形態では、ツェナーダイオード40aの耐圧は、製造上の公差が小さく温度依存性の少ない、6V程度に設定されている。

【0030】

放電回路35は、出力トランジスタ32をターンオフする場合に、出力トランジスタ32のゲート−ソース間を電気的に接続する第2の電流経路を形成する。つまり、出力トランジスタ32のゲート−ソース間は、電流制限素子40及びトランジスタ39を介して、第2の電流経路を形成する。なお、トランジスタ39は、制御信号aに基づいてオンオフが制御される。また、電流制限素子40は、例えば抵抗等により構成され、トランジスタ39に流れる電流を制限する。

【0031】

例えば、出力トランジスタ32をターンオンする場合、トランジスタ39はロウレベルの制御信号aに基づいてオフ状態に制御される。一方、出力トランジスタ32をターンオフする場合、トランジスタ39はハイレベルの制御信号aに基づいてオン状態に制御される。なお、本実施の形態では、第2の電流経路は、第1の電流経路よりも、緩やかに出力トランジスタ32のゲート電荷を放電する。

【0032】

次に、図1に示す回路の動作について、図2を用いてさらに具体的に説明する。図2は、本実施の形態にかかる電力供給制御回路1の動作を示すタイミングチャートである。なお、縦軸は電圧及び電流を示し、横軸は時間を示す。

【0033】

まず、時刻t1において、出力トランジスタ32のターンオン動作が開始する。つまり、入力信号inがハイレベル(例えば電源電圧Vcc)からロウレベル(例えば接地電圧)に遷移する。それにより、制御信号aはハイレベルからロウレベルに遷移する。同時に、制御信号bはロウレベルから電源電圧Vcc以上の電圧(例えば、電源電圧Vcc+10V)に遷移する。

【0034】

時刻t2において、出力トランジスタ32のゲート電圧Gは、ロウレベルから電源電圧Vcc以上の電圧(例えば電源電圧Vcc+10V)に遷移する。それにより、出力トランジスタ32はオン状態となる。それにより、電力供給制御回路1は、電源電圧端子Vccから外部出力端子Toに対して電力を供給する。このとき、出力電圧Voは電源電圧Vccとほぼ同じ電圧レベルを示す。なお、トランジスタ37は、ゲートにロウレベルの制御信号aが印加され、ソースに電源電圧Vccが印加されているため、オフ状態となっている。

【0035】

次に、時刻t3において、出力トランジスタ32のターンオフ動作が開始する。つまり、入力信号inがロウレベルからハイレベルに遷移する。それにより、制御信号aはロウレベルからハイレベルに遷移する。同時に、ゲート駆動回路31の制御信号bを出力する側の出力端子(他方の出力端子)が、ハイインピーダンス状態になる。

【0036】

このとき、トランジスタ37は、ゲートにハイレベルの制御信号aが印加され、ソースに出力電圧Voが印加されるため、オン状態となる。それにより、出力トランジスタ32のゲート電荷は、ツェナーダイオード40a及びトランジスタ37を介して、高速に放電される。つまり、出力トランジスタ32のゲート電荷は、第1の電流経路を介して、高速に放電される。

【0037】

また、トランジスタ39は、ゲートにハイレベルの制御信号aが印加され、ソースに出力電圧Voが印加されるため、オン状態となる。それにより、出力トランジスタ32のゲート電荷は、電流制限素子40及びトランジスタ39を介して、放電される。つまり、出力トランジスタ32のゲート電荷は、第1の電流経路に加え、さらに第2の電流経路を介して、放電される。

【0038】

時刻t4において、ゲート電圧Gが電源電圧Vcc+6Vまで低下した場合、第1の電流経路が遮断される。時刻t4以降、出力トランジスタ32のゲート電荷は、第2の電流経路のみを介して、緩やかに放電される。その後、出力トランジスタ32のゲート電圧がさらに低下すると、時刻t3から遅れ時間td経過後の時刻t5において、出力電圧Voが低下し始める。

【0039】

時刻t6において、放電が完了してゲート電圧Gがロウレベルになると、出力トランジスタ32はオフ状態となる。それにより、出力電圧Voはロウレベルになる。なお、出力端子Toに接続される負荷(不図示)が抵抗性の場合、図2に示すように、出力電流Ioも、出力電圧Voと同様の変化を示す。

【0040】

このように、電力供給制御回路1は、ターンオフ時において、出力トランジスタ32のゲート電圧が電源電圧Vccよりも十分に高い(例えば、電源電圧Vcc+10V)場合には、第1及び第2の電流経路を介して、出力トランジスタ32のゲート電荷を高速に放電する。そして、電力供給制御回路1は、ターンオフ時において、出力トランジスタ32のゲート電圧が電源電圧Vccよりも6V程度高い電圧まで低下すると、第1の電流経路を遮断し、第2の電流経路のみを介して、出力トランジスタ32のゲート電荷を緩やかに放電する。

【0041】

このような回路構成により、電力供給制御回路1は、出力トランジスタ32のゲート電圧が電源電圧Vccよりも十分に高い電圧に昇圧された場合でも、ターンオフ動作を開始してから(時刻t3)、出力電圧Voが変化を開始(時刻t5)するまでの時間(遅れ時間td)を短縮することができる。つまり、ターンオフ時間(時刻t3〜t6)を短縮することができる。ここで、電力供給制御回路1は、出力電圧Voが電源電圧Vccよりも低くなる前に、第1の電流経路を遮断する。そのため、電力供給制御回路1では、従来技術と異なり、出力電圧Voの波形に歪みが生じない。それにより、電力供給制御回路1は、出力電圧Voのノイズを抑制することができる。同時に、電力供給制御回路1は、ターンオフ時における出力電圧Voのスルーレートを小さくすることができる。

【0042】

また、従来技術の場合、ターンオフ時において、NMOSトランジスタ137を高速にオン状態に移行させるために、容量136を十分に大きくする必要があった。そのため、従来技術では、回路規模が増大するという問題があった。一方、電力供給制御回路1は、従来技術と異なり容量136を用いないため、回路規模の増大を抑制することができる。なお、電力供給制御回路1は、容量136を用いたブートストラップ回路を用いず、デプレッション型のNチャネルMOSトランジスタ37を用いて第1の電流経路を形成する。

【0043】

実施の形態2

図3に、本発明の実施の形態2にかかる電力供給制御回路2の回路図を示す。図3に示す電力供給制御回路2は、図1に示す電力供給制御回路1と比較して、放電回路33aの代わりに放電回路33bを備える。放電回路33bは、トランジスタ37と放電遮断回路40bとを有する。放電遮断回路40bは、ゲート−ドレイン間が共通接続されたNチャネルMOSトランジスタ40b1〜40bn(nは自然数)を複数有する。トランジスタ40b1〜40bnは、出力トランジスタ32のゲートとトランジスタ37のドレインとの間に直列に接続される。その他の回路構成については、図1に示す回路と同様であるため説明を省略する。

【0044】

図1に示す電力供給制御回路1は、ターンオフ時において、出力トランジスタ32のゲート電圧Gが電源電圧Vcc+6Vまで低下した場合に、第1の電流経路を遮断していた。一方、図3に示す電力供給制御回路2は、ターンオフ時において、出力トランジスタ32のゲート電圧Gが電源電圧Vccのさらに近傍まで低下した場合に、第1の電流経路を遮断することができる。つまり、電力供給制御回路2は、図2のターンオフ時間(時刻t3〜t6)のうち、時刻t3〜t4の期間の占める割合を増加させることができる。それにより、電力供給制御回路2は、実施の形態1の場合と比較して、ターンオフ時間を短くすることができる。また、電力供給制御回路2は、実施の形態1の場合と同様に、容量136からなるブートストラップ回路を用いないため、回路規模の増大を抑制することができる。

【0045】

図3の動作について、図2を用いて説明する。時刻t3において、出力トランジスタ32のターンオフ動作が開始する。つまり、入力信号inがロウレベルからハイレベルに遷移する。それにより、制御信号aはロウレベルからハイレベルに遷移する。同時に、ゲート駆動回路31の制御信号bを出力する側の出力端子(他方の出力端子)が、ハイインピーダンス状態になる。

【0046】

このとき、トランジスタ37は、ゲートにハイレベルの制御信号aが印加され、ソースに電源電圧Vccが印加されるため、オン状態となる。それにより、出力トランジスタ32のゲート電荷は、放電遮断回路40b及びトランジスタ37を介して、高速に放電される。つまり、出力トランジスタ32のゲート電荷は、第1の電流経路を介して、高速に放電される。

【0047】

そして、出力トランジスタ32のゲート電圧Gが、トランジスタ40b1〜40bnのしきい値電圧と電源電圧Vccとの合計程度まで低下すると、トランジスタ40b1〜40bnがオフ状態となり、第1の電流経路が遮断される。ここで、トランジスタ40b1〜40bnのしきい値電圧の合計を、出力トランジスタ32のしきい値電圧よりわずかに高く設定しておく。それにより、電力供給制御回路2は、出力電圧Voが電源電圧Vccより低くなる前に、第1の電流経路を遮断することができる。そのため、電力供給制御回路2では、実施の形態1の場合と同様に、出力電圧Voの波形に歪みが生じない。つまり、電力供給制御回路2は、出力電圧Voのノイズを抑制することができる。同時に、電力供給制御回路2は、ターンオフ時における出力電圧Voのスルーレートを小さくすることができる。また、電力供給制御回路2は、実施の形態1の場合と同様に、容量136からなるブートストラップ回路を用いないため、回路規模の増大を抑制することができる。その他の動作については、実施の形態1の場合と同様であるため、説明を省略する。

【0048】

例えば、放電遮断回路40bが2個のトランジスタ40b1,40b2(n=2)を有する場合について説明する。なお、各トランジスタ40b1,40b2のしきい値電圧は2V程度である。この例では、ターンオフ時において、出力トランジスタ32のゲート電圧Gが電源電圧Vcc+4V程度まで低下すると、第1の電流経路が遮断される。このように、本実施の形態では、実施の形態1と比較して、出力トランジスタ32のゲート電圧Gが電源電圧Vccのさらに近傍まで低下した場合に、第1の電流経路を遮断することができる。

【0049】

実施の形態3

図4に、本発明の実施の形態3にかかる電力供給制御回路3の回路図を示す。図4に示す電力供給制御回路3は、図1に示す電力供給制御回路1と比較して、放電回路33aの代わりに放電回路33cを備える。放電回路33cは、トランジスタ37と放電遮断回路40cとを有する。なお、放電遮断回路40cとして、NチャネルMOSトランジスタ40cが用いられている。トランジスタ40cでは、ゲート及びドレインが出力トランジスタ32のゲートに共通接続され、ソースがトランジスタ37のドレインに接続される。その他の回路構成については、図1に示す回路と同様であるため、説明を省略する。

【0050】

実施の形態2では、トランジスタ40b1〜40bnの個数に応じて、第1の電流経路を遮断するか否かのしきい値電圧を調整していた。一方、本実施の形態では、出力トランジスタと同等程度のしきい値電圧を有するトランジスタ40cを用いることにより、第1の電流経路を遮断するか否かのしきい値電圧を調整する。それにより、電力供給制御回路3は、ターンオフ時において、出力トランジスタ32のゲート電圧Gが電源電圧Vccのさらに近傍まで低下した場合に、第1の電流経路を遮断することができる。つまり、本実施の形態にかかる電力供給制御回路3は、実施の形態2の場合と比較して、ターンオフ時間を短くすることができる。また、電力供給制御回路3は、上記実施の形態の場合と同様に、容量136からなるブートストラップ回路を用いないため、回路規模の増大を抑制することができる。

【0051】

図4の動作について、図2を用いて説明する。時刻t3において、出力トランジスタ32のターンオフ動作が開始する。つまり、入力信号inがロウレベルからハイレベルに遷移する。それにより、制御信号aはロウレベルからハイレベルに遷移する。同時に、ゲート駆動回路31の制御信号bを出力する側の出力端子(他方の出力端子)が、ハイインピーダンス状態になる。

【0052】

このとき、トランジスタ37は、ゲートにハイレベルの制御信号aが印加され、ソースに電源電圧Vccが印加されるため、オン状態となる。それにより、出力トランジスタ32のゲート電荷は、放電遮断回路40b及びトランジスタ37を介して、高速に放電される。つまり、出力トランジスタ32のゲート電荷は、第1の電流経路を介して、高速に放電される。

【0053】

そして、出力トランジスタ32のゲート電圧Gが、トランジスタ40cのしきい値電圧と電源電圧Vccとの合計程度まで低下すると、トランジスタ40cがオフ状態となり、第1の電流経路が遮断される。ここで、トランジスタ40cのしきい値電圧を、出力トランジスタ32のしきい値電圧よりわずかに高く設定しておく。それにより、電力供給制御回路3は、出力電圧Voが電源電圧Vccより低くなる前に、第1の電流経路を遮断することができる。

【0054】

なお、このような設定は、トランジスタ40c及び出力トランジスタ32のしきい値電圧を決定する拡散層を同じにすることにより、容易に実現可能である。図5に、トランジスタ40c及び出力トランジスタ32のトランジスタ構造の断面図を示す。

【0055】

トランジスタ40cは、n−基板50を有する。n−基板50の下側には、背面接触のためのn+拡散層51が設けられている。また、n−基板50上には第1のp−拡散層52が設けられている。第1のp−拡散層52に相対する表面に2つのn+拡散層53,54が位置している。なお、一方のn+拡散層(凹み拡散層)53は、ソース端子Sに接続されている。他方のn+拡散層54は、ドレイン端子Dに接続されている。また、両n+拡散層53,54の間には、より浅い深さのn−拡散層55が位置している。なお、n−拡散層55は、n+拡散層54に隣接している。

【0056】

n+拡散層53及びn−拡散層55間は、長さLのチャネル領域を有する。チャネル上には、ゲート電極56が配置されている。そして、ゲート電極56はゲート端子Gに接続されている。また、n+拡散層53は、第1のp−拡散層52よりも濃度の濃い第2のp−拡散層57に囲われている。第2のp−拡散層57は、p+拡散層58を介して基板端子BGに接続されている。

【0057】

出力トランジスタ32は、n−基板60を有する。n−基板60の下側には、背面接触のためのn+拡散層61が設けられている。なお、このn+拡散層61は、ドレイン端子Dに接続されている。また、n−基板60上には、トランジスタ40cに用いられているものと同一の第2のp−拡散層57が設けられている。この第2のp−拡散層57は、p+拡散層62を介して基板端子BGに接続されている。

【0058】

第2のp−拡散層57に相対する表面に2つのn+拡散層63,64が位置している。なお、n+拡散層63,64は、いずれもソース端子Sに接続されている。また、両n+拡散層63,64の間に、p+拡散層62が位置している。チャネル上には、ゲート電極65が配置されている。そして、ゲート電極65はゲート端子Gに接続されている。

【0059】

図5に示す例のように、トランジスタ40c及び出力トランジスタ32のしきい値電圧は、いずれも同一のp−拡散層57に基づいて決定される。それにより、両トランジスタのしきい値電圧はほぼ等しくなる。また、両トランジスタのしきい値電圧は製造上の公差に対して連動する。

【0060】

このような回路構成により、本実施の形態にかかる電力供給制御回路3では、上記実施の形態の場合と同様に、出力電圧Voの波形に歪みが生じない。つまり、電力供給制御回路3は、出力電圧Voのノイズを抑制することができる。同時に、電力供給制御回路3は、ターンオフ時における出力電圧Voのスルーレートを小さくすることができる。また、本実施の形態にかかる電力供給制御回路3は、上記実施の形態の場合と同様に、容量136からなるブートストラップ回路を用いないため、回路規模の増大を抑制することができる。その他の動作については、上記実施の形態の場合と同様であるため、説明を省略する。

【0061】

例えば、出力トランジスタ32及びトランジスタ40cのしきい値電圧がそれぞれ2Vである場合について説明する。この例では、ターンオフ時において、出力トランジスタ32のゲート電圧Gが電源電圧Vcc+2V程度まで低下すると、第1の電流経路が遮断される。このように、本実施の形態では、実施の形態2と比較して、出力トランジスタ32のゲート電圧Gが電源電圧Vccのさらに近傍まで低下してから、第1の電流経路を遮断することができる。

【0062】

以上のように、上記実施の形態にかかる電力供給制御回路は、ターンオフ時において、出力トランジスタ32のゲート電圧が電源電圧Vccよりも十分に高い場合には、第1及び第2の電流経路を介して、出力トランジスタ32のゲート電荷を高速に放電する。そして、上記実施の形態にかかる電力供給制御回路は、ターンオフ時において、出力トランジスタ32のゲート電圧Gが電源電圧Vccの近傍まで低下すると、第1の電流経路を遮断し、第2の電流経路のみを介して、出力トランジスタ32のゲート電荷を緩やかに放電する。

【0063】

このような回路構成により、上記実施の形態にかかる電力供給制御回路は、出力トランジスタ32のゲート電圧が電源電圧Vccよりも十分に高い電圧に昇圧された場合でも、ターンオフ動作を開始してから(時刻t3)、出力電圧Voが変化を開始(時刻t5)するまでの時間(遅れ時間td)を短縮することができる。つまり、ターンオフ時間(時刻t3〜t6)を短縮することができる。ここで、上記実施の形態にかかる電力供給制御回路は、出力電圧Voが電源電圧Vccよりも低くなる前に、第1の電流経路を遮断する。そのため、上記実施の形態にかかる電力供給制御回路では、従来技術と異なり、出力電圧Voの波形に歪みが生じない。それにより、上記実施の形態にかかる電力供給制御回路は、出力電圧Voのノイズを抑制することができる。同時に、上記実施の形態にかかる電力供給制御回路は、ターンオフ時における出力電圧Voのスルーレートを小さくすることができる。

【0064】

また、上記実施の形態にかかる電力供給制御回路は、従来技術と異なり、容量136からなるブートストラップ回路を用いないため、回路規模の増大を抑制することができる。

【0065】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。上記実施の形態では、電流制限素子40に抵抗を用いた場合を例に説明したが、これに限られない。例えば、デプレッション型のNチャネルMOSトランジスタのゲートとソースとを接続した定電流素子を用いてもよい。

【符号の説明】

【0066】

1〜3 電力供給制御回路

31 ゲート駆動回路

32 出力トランジスタ

33a,33b,33c 放電回路

35 放電回路

37,39 トランジスタ

40 電流制限素子

40a,40b,40c 放電遮断回路

40b1〜40bn トランジスタ

【特許請求の範囲】

【請求項1】

電源ラインと出力端子との間に設けられ、負荷に対する電力の供給を制御するNチャネル型の出力トランジスタと、

外部入力信号に基づいて前記出力トランジスタのオンオフを制御するための制御信号を生成するゲート駆動回路と、

前記出力トランジスタのゲート−ソース間に設けられ、前記出力トランジスタをオフする場合、前記制御信号に基づいて前記出力トランジスタのゲートに蓄積された電荷を放電するための第1のデプレション型NチャネルMOSトランジスタと、

前記出力トランジスタのゲート−ソース間に設けられ、前記出力トランジスタをオフする場合、前記制御信号に基づいて前記出力トランジスタのゲートに蓄積された電荷を前記第1のデプレション型NチャネルMOSトランジスタよりも緩やかに放電するための第2のデプレション型NチャネルMOSトランジスタと、

前記第1のデプレション型NチャネルMOSトランジスタに直列に接続され、前記出力トランジスタをオフする場合において、前記出力トランジスタのゲート電圧が所定の電圧レベルに低下したことを検出し、前記出力トランジスタのゲートに蓄積された電荷の放電を遮断する放電遮断回路と、を備えた電力供給制御回路。

【請求項2】

前記所定の電圧レベルは、

前記電源ラインの電圧と前記出力トランジスタのしきい値電圧との和よりも大きいことを特徴とする請求項1に記載の電力供給制御回路。

【請求項3】

前記放電遮断回路は、

前記出力トランジスタをオフする場合、前記出力端子の電圧が前記電源ラインの電圧よりも低下する前に、前記出力トランジスタのゲートに蓄積された電荷の放電を停止することを特徴とする請求項1又は2に記載の電力供給制御回路。

【請求項4】

前記放電遮断回路は、

ツェナーダイオードであることを特徴とする請求項1〜3のいずれか一項に記載の電力供給制御回路。

【請求項5】

前記放電遮断回路は、

ダイオード接続されたNチャネルMOSトランジスタであることを特徴とする請求項1〜3のいずれか一項に記載の電力供給制御回路。

【請求項6】

前記放電遮断回路としてのNチャネルMOSトランジスタでは、

ソース領域が前記出力トランジスタのソース領域と同一の拡散層によって形成されていることを特徴とする請求項5に記載の電力供給制御回路。

【請求項7】

前記放電遮断回路は、

ダイオード接続された複数のNチャネルMOSトランジスタが直列に設けられたものであることを特徴とする請求項1〜3のいずれか一項に記載の電力供給制御回路。

【請求項1】

電源ラインと出力端子との間に設けられ、負荷に対する電力の供給を制御するNチャネル型の出力トランジスタと、

外部入力信号に基づいて前記出力トランジスタのオンオフを制御するための制御信号を生成するゲート駆動回路と、

前記出力トランジスタのゲート−ソース間に設けられ、前記出力トランジスタをオフする場合、前記制御信号に基づいて前記出力トランジスタのゲートに蓄積された電荷を放電するための第1のデプレション型NチャネルMOSトランジスタと、

前記出力トランジスタのゲート−ソース間に設けられ、前記出力トランジスタをオフする場合、前記制御信号に基づいて前記出力トランジスタのゲートに蓄積された電荷を前記第1のデプレション型NチャネルMOSトランジスタよりも緩やかに放電するための第2のデプレション型NチャネルMOSトランジスタと、

前記第1のデプレション型NチャネルMOSトランジスタに直列に接続され、前記出力トランジスタをオフする場合において、前記出力トランジスタのゲート電圧が所定の電圧レベルに低下したことを検出し、前記出力トランジスタのゲートに蓄積された電荷の放電を遮断する放電遮断回路と、を備えた電力供給制御回路。

【請求項2】

前記所定の電圧レベルは、

前記電源ラインの電圧と前記出力トランジスタのしきい値電圧との和よりも大きいことを特徴とする請求項1に記載の電力供給制御回路。

【請求項3】

前記放電遮断回路は、

前記出力トランジスタをオフする場合、前記出力端子の電圧が前記電源ラインの電圧よりも低下する前に、前記出力トランジスタのゲートに蓄積された電荷の放電を停止することを特徴とする請求項1又は2に記載の電力供給制御回路。

【請求項4】

前記放電遮断回路は、

ツェナーダイオードであることを特徴とする請求項1〜3のいずれか一項に記載の電力供給制御回路。

【請求項5】

前記放電遮断回路は、

ダイオード接続されたNチャネルMOSトランジスタであることを特徴とする請求項1〜3のいずれか一項に記載の電力供給制御回路。

【請求項6】

前記放電遮断回路としてのNチャネルMOSトランジスタでは、

ソース領域が前記出力トランジスタのソース領域と同一の拡散層によって形成されていることを特徴とする請求項5に記載の電力供給制御回路。

【請求項7】

前記放電遮断回路は、

ダイオード接続された複数のNチャネルMOSトランジスタが直列に設けられたものであることを特徴とする請求項1〜3のいずれか一項に記載の電力供給制御回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2011−139403(P2011−139403A)

【公開日】平成23年7月14日(2011.7.14)

【国際特許分類】

【出願番号】特願2010−132(P2010−132)

【出願日】平成22年1月4日(2010.1.4)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成23年7月14日(2011.7.14)

【国際特許分類】

【出願日】平成22年1月4日(2010.1.4)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]