電力増幅器

【課題】差動信号の増幅および合成を行ない、かつ高調波を抑制することが可能な電力増幅器を提供する。

【解決手段】電力増幅器101は、差動信号である第1の入力信号および第2の入力信号を増幅する第1の増幅器11,12と、第1の増幅器11,12によって増幅された第1の入力信号および第2の入力信号を受ける第1のコイル21と、第1のコイル21と磁気的に結合され、増幅された第1の入力信号および第2の入力信号の合成信号が出力される第2のコイル22と、第2のコイル22と磁気的に結合された第3のコイル23と、第3のコイル23の両端間に接続された第1のキャパシタ41とを備え、第1のキャパシタ41の一端が接地ノードに接続されている。

【解決手段】電力増幅器101は、差動信号である第1の入力信号および第2の入力信号を増幅する第1の増幅器11,12と、第1の増幅器11,12によって増幅された第1の入力信号および第2の入力信号を受ける第1のコイル21と、第1のコイル21と磁気的に結合され、増幅された第1の入力信号および第2の入力信号の合成信号が出力される第2のコイル22と、第2のコイル22と磁気的に結合された第3のコイル23と、第3のコイル23の両端間に接続された第1のキャパシタ41とを備え、第1のキャパシタ41の一端が接地ノードに接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電力増幅器に関し、特に、差動信号の増幅および合成を行なう電力増幅器に関する。

【背景技術】

【0002】

携帯電話端末および無線LAN端末においては、送信機即ち電力増幅器は、最大で10〜30dBmの電力を送信する必要がある。信号周波数が1GHz〜6GHz程度である電力増幅器において、近年、シリコンMOS型トランジスタ(絶縁ゲート型電界効果トランジスタ)を用い、1対のトランジスタで増幅された差動信号をトランスで合成する手法が提案されている。このような電力増幅器は、たとえば非特許文献1のFigure.11.9.2に示されており、以下、1差動対のトランス型電力増幅器と呼ぶ。

【0003】

この非特許文献1に記載の電力増幅器においては、1次コイル(非特許文献1では、コイルのことをスラブと呼ぶ)と、この1次コイルとの磁気的結合を有する2次コイルとが互いに平行に配置されている。1次コイルの中点は電源電圧が供給される端子であり、この中点にキャパシタを接続することで、2次高調波を抑圧することができる。

【0004】

このような1差動対のトランス型電力増幅器よりもさらに高出力化を図る手法として、2対以上のトランジスタからの差動増幅信号をトランスで合成することが提案されている。このような電力増幅器は、たとえば分布型環状電力増幅器として特許文献1に示されており、以下、多差動対のトランス型電力増幅器と呼ぶ。この特許文献1では、4対のトランジスタによりそれぞれ増幅された差動信号を、直列接続されたトランスの2次コイルによって合成する構成が開示されている。

【0005】

非特許文献1に記載の1差動対のトランス型電力増幅器よりもさらに高効率化を図る他の手法として、特許文献2には、2対のトランジスタの差動信号をトランスで合成し、トランスの2次コイルの両側に形状の異なる1次コイルを配置する構成が開示されている。

【非特許文献1】Jongchan Kang, et. al. “A Single-Chip Linear CMOS Power Amplifier for 2.4 GHz WLAN” ISSCC(International Solid-State Circuits Conference)2006, p208-209.

【特許文献1】特表2005−503679号公報

【特許文献2】特開2006−295896号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、非特許文献1では、2次高調波を抑制するための構成は開示されているが、2次高調波とともに出力信号に含まれる3次高調波を抑制することについては何ら考慮されていない。また、特許文献1および特許文献2では、2次高調波の抑制および3次高調波の抑制のいずれも考慮されていない。

【0007】

それゆえに、この発明の目的は、差動信号の増幅および合成を行ない、かつ高調波を抑制することが可能な電力増幅器を提供することである。

【課題を解決するための手段】

【0008】

上記課題を解決するために、この発明のある局面に係わる電力増幅器は、差動信号である第1の入力信号および第2の入力信号を増幅する第1の増幅器と、第1の増幅器によって増幅された第1の入力信号および第2の入力信号を受ける第1のコイルと、第1のコイルと磁気的に結合され、増幅された第1の入力信号および第2の入力信号の合成信号が出力される第2のコイルと、第2のコイルと磁気的に結合された第3のコイルと、第3のコイルの両端間に接続された第1のキャパシタとを備え、第1のキャパシタの一端が接地ノードに接続されている。

【発明の効果】

【0009】

本発明によれば、差動信号の増幅および合成を行ない、かつ高調波を抑制することができる。

【発明を実施するための最良の形態】

【0010】

以下、本発明の実施の形態について図面を用いて説明する。なお、図中同一または相当部分には同一符号を付してその説明は繰り返さない。

【0011】

<第1の実施の形態>

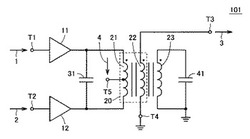

図1は、本発明の第1の実施の形態に係る電力増幅器の構成を示す図である。

【0012】

図1を参照して、電力増幅器101は、1差動対のトランス型電力増幅器であり、増幅器11および12と、トランス20と、キャパシタ31および41と、3次コイル23と、端子T1〜T5を備える。トランス20は、1次コイル21と、2次コイル22とを含む。

【0013】

増幅器11および12は、それぞれ端子T1およびT2を介して受けた入力信号1および入力信号2を増幅する。入力信号1および入力信号2は、たとえば互いの位相が180度異なる差動信号である。

【0014】

トランス20は、増幅器11の出力信号および増幅器12の出力信号を合成する。すなわち、1次コイル21は、増幅器11によって増幅された入力信号1を受ける第1端と、増幅器12によって増幅された入力信号2を受ける第2端とを有する。1次コイル21の中点に端子T5が接続され、この端子T5に電源電圧4が供給される。

【0015】

キャパシタ31は、1次コイル21の第1端と第2端との間に接続されている。1次コイル21およびキャパシタ31は、増幅器11および12の出力整合回路を構成している。

【0016】

2次コイル22は、1次コイル21と磁気的に結合され、増幅後の入力信号1および入力信号2の合成信号3が出力される。より詳細には、2次コイル22は、端子T3に接続された第1端と、端子T4に接続された第2端とを有する。電力増幅器101の出力信号3すなわち増幅後の入力信号1および入力信号2の合成信号3は、端子T3から出力される。端子T4は、接地電圧が供給される接地ノードに接続されている。

【0017】

3次コイル23は、2次コイル22と磁気的に結合され、キャパシタ41の第1端に接続された第1端と、キャパシタ41の第2端および接地電圧が供給される接地ノードに接続された第2端とを有する。

【0018】

図2は、本発明の第1の実施の形態に係る電力増幅器における各コイルの概略レイアウトを示す図である。

【0019】

図2を参照して、電力増幅器101は、図1に示す回路が設けられた主表面を有する半導体基板Bを備える。

【0020】

1次コイル21、2次コイル22および3次コイル23は半導体基板Bの同一主表面上に配線層を用いて形成され、略C字型の形状を有する。たとえば、最外周に1次コイル21が配置され、1次コイル21の内側に2次コイル22が配置され、2次コイル22の内側に3次コイル23が配置されている。3次コイルの両端間にキャパシタ41が接続されている。キャパシタ41は、2次コイル22の内側に配置されている。

【0021】

より詳細には、1次コイル21は、半導体基板Bの主表面に設けられ、周方向に延伸し、その周方向において一部区間が開放された導電線路によって形成されている。

【0022】

2次コイル22は、半導体基板Bの主表面に設けられ、周方向に延伸し、その周方向において一部区間が開放された導電線路によって形成されている。

【0023】

1次コイル21は、2次コイル22を囲むように配置されている。なお、2次コイル22が、1次コイル21を囲むように配置されている構成であってもよい。

【0024】

3次コイル23は、半導体基板Bの主表面に設けられ、周方向に延伸し、その周方向において一部区間が開放され、1次コイル21および2次コイル22に囲まれた導電線路によって形成されている。

【0025】

増幅器11は、たとえばNチャネルMOS型トランジスタ51aおよび51bをカスコード接続した回路で構成される。増幅器12は、たとえばNチャネルMOS型トランジスタ52aおよび52bをカスコード接続した回路で構成される。

【0026】

より詳細には、NチャネルMOS型トランジスタ51aは、ドレインと、接地ノードに接続されたソースと、入力信号1を受けるゲートとを有する。NチャネルMOS型トランジスタ51bは、1次コイル21の第1端に接続されたドレインと、NチャネルMOS型トランジスタ51aのドレインに接続されたソースと、所定電圧を受けるゲートとを有する。NチャネルMOS型トランジスタ52aは、ドレインと、接地ノードに接続されたソースと、入力信号2を受けるゲートとを有する。NチャネルMOS型トランジスタ52bは、1次コイル21の第2端に接続されたドレインと、NチャネルMOS型トランジスタ52aのドレインに接続されたソースと、所定電圧を受けるゲートとを有する。

【0027】

図3は、本発明の第1の実施の形態に係る電力増幅器に適用されるトランス20と3次コイル23とキャパシタ41とを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。

【0028】

図3に示す通過特性の計算においては、1次コイル21を理想インダクタとし、そのL(インダクタンス)値を2.4nHとしている。2次コイル22を理想インダクタとし、そのL値を2.2nHとしている。3次コイル23を理想インダクタとし、そのL値を2.0nHとしている。また、1次コイルと2次コイルとの磁気的な結合係数k値を0.565とし、2次コイルと3次コイルとの磁気的な結合係数k値を0.565としている。また、キャパシタ41を理想キャパシタとし、そのC(キャパシタンス)値を0.24pFとしている。

【0029】

図3を参照して、電力増幅器101の出力信号の周波数が2.4GHzである場合、この出力信号の3倍の周波数である7.2GHzにおいて、40dBの通過損失が得られる。即ち、トランス20と3次コイル23とキャパシタ41とを含む回路ブロックが、出力信号の周波数である2.4GHzの3倍の周波数成分を抑制する機能を有していることがわかる。

【0030】

図4は、本発明の第1の実施の形態に係る電力増幅器の入出力特性を示す図である。図4では、トランス20と3次コイル23とキャパシタ41とを含む回路ブロックの回路定数をそのまま用い、かつ図2に示すMOS型トランジスタ51a、51b、52aおよび52bに対して等価回路モデルを適用した条件で、2.4GHzの入力信号に対する出力信号特性を計算した結果を示している。図4において、グラフG1が基本波である2.4GHzの入力信号に対する出力信号特性を示しており、グラフG2が2.4GHzの入力信号に対する3次高調波信号特性を示している。また、比較のため、電力増幅器101が3次コイル23およびキャパシタ41を備えないと仮定した構成における、2.4GHzの入力信号に対する3次高調波信号特性をグラフG3に示している。

【0031】

グラフG1〜G3より、電力増幅器101では、3次コイル23およびキャパシタ41で構成されるLC共振回路により、3次高調波成分が20dB程度抑制されていることがわかる。

【0032】

したがって、本発明の第1の実施の形態に係る電力増幅器では、高次の周波数歪、すなわち2次コイル22から出力される合成信号3における3次高調波を抑制する効果が得られる。これにより、出力特性が改善される。また、トランス20の内側に3次コイル23およびキャパシタ41を配置することにより、半導体基板Bにおける実質的な面積増加を伴わず、電力増幅器101のサイズの増大を防ぐことができる。

【0033】

なお、本発明の第1の実施の形態に係る電力増幅器では、1次コイル21、2次コイル22および3次コイル23は略C字型の形状を有する構成であるとしたが、これに限定するものではない。半導体基板Bの主表面において、1次コイル21および2次コイル22によって全周を取り囲まれた領域(図2のAR)が形成され、3次コイル23がこの領域AR内に設けられている構成であれば、電力増幅器101のサイズの増大を防ぐことができる。

【0034】

図5は、本発明の第1の実施の形態に係る電力増幅器において、キャパシタ41にMOS型トランジスタを適用した構成を示す図である。

【0035】

図5を参照して、電力増幅器102は、電力増幅器101と比べて、さらに、端子T6を備える。キャパシタ41は、NチャネルMOS型トランジスタ53a,53bと、ゲート抵抗61a,61bとを含む。

【0036】

前述した電力増幅器101は、3次コイル23およびキャパシタ41によって3次高調波成分を抑制する構成である。

【0037】

MOS型トランジスタ53aのドレインとMOS型トランジスタ53bのドレインとが接続されている。MOS型トランジスタ53a,53bのソースと3次コイル23の第1端および第2端とがそれぞれ接続されている。MOS型トランジスタ53bのソースは接地されている。MOS型トランジスタ53a,53bのゲートは、ゲート抵抗61a,61bを介して端子T6に接続されている。この端子T6には、制御信号5が与えられる。

【0038】

制御信号5は、たとえば、+3.3Vおよび−3.3Vの2つのDC電圧に設定される。制御信号5が−3.3VのDC電圧に設定されると、MOS型トランジスタ53a,53bはオフするため、MOS型トランジスタ53a,53bはキャパシタとして機能する。一方、制御信号5が+3.3VのDC電圧に設定されると、MOS型トランジスタ53a,53bはオンするため、抵抗として機能する。

【0039】

図6は、図5に示す電力増幅器102に適用されるトランス20と3次コイル23とキャパシタ41とを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。図6に示す通過特性の計算においては、MOS型トランジスタ53a,53bのゲート幅を2mmとし、ゲート抵抗61a,61bのR(抵抗)値を40kΩとしている。グラフG1は、制御信号5が+3.3VのDC電圧に設定された場合を示し、グラフG2は、制御信号5が−3.3VのDC電圧に設定された場合を示している。その他の回路定数は、図3に示す通過特性の計算と同様である。

【0040】

グラフG2より、制御信号5が−3.3VのDC電圧に設定されている場合には、図3と同程度の通過特性が得られていることがわかる。

【0041】

一方、グラフG1より、制御信号5が+3.3VのDC電圧に設定されている場合には、図3に示す通過特性とは異なり、3次高調波成分が抑制されておらず、3次コイル23が無い場合の特性とほぼ同じである。しかしながら、2.4GHzの出力信号の通過損失は、図3に示す通過特性と比べて約0.6dB小さい。

【0042】

一般に、電力増幅器では、入力電力が小さい場合には、図4からもわかるように3次高調波成分は小さい。

【0043】

したがって、電力増幅器102では、入力電力が小さい場合には、制御信号5を+3.3VのDC電圧に設定することにより出力信号の通過損失を抑えることができる。一方、入力電力が大きい場合には、制御信号5を−3.3VのDC電圧に設定することにより3次高調波成分を抑えることができる。

【0044】

次に、本発明の他の実施の形態について図面を用いて説明する。なお、図中同一または相当部分には同一符号を付してその説明は繰り返さない。

【0045】

<第2の実施の形態>

本実施の形態は、第1の実施の形態に係る電力増幅器と比べてコイルを追加した電力増幅器に関する。以下で説明する内容以外は第1の実施の形態に係る電力増幅器と同様である。

【0046】

図7は、本発明の第2の実施の形態に係る電力増幅器における各コイルの概略レイアウトを示す図である。

【0047】

図7を参照して、電力増幅器103は、本発明の第1の実施の形態に係る電力増幅器と比べて、さらに、4次コイル24と、キャパシタ42とを備える。

【0048】

4次コイル24は、たとえば、1次コイル21の外側に配置されている。4次コイル24は、1次コイル21、2次コイル22および3次コイル23と同じ半導体基板Bの主表面上に配線層を用いて形成され、略C字型の形状を有する。4次コイル24の両端間にキャパシタ42が接続されている。

【0049】

より詳細には、4次コイル24は、1次コイル21と磁気的に結合され、キャパシタ42の第1端に接続された第1端と、キャパシタ42の第2端および接地電圧が供給される接地ノードに接続された第2端とを有する。キャパシタ42は、4次コイル24の第1端と第2端との間に接続されている。

【0050】

4次コイル24は、半導体基板Bの主表面に設けられ、1次コイル21ないし3次コイル23を囲むように周方向に延伸し、その周方向において一部区間が開放された導電線路によって形成されている。

【0051】

図8は、本発明の第2の実施の形態に係る電力増幅器に適用されるトランス20と3次コイル23と4次コイル24とキャパシタ41とキャパシタ42とを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。

【0052】

図8に示す通過特性の計算においては、4次コイル24を理想インダクタとし、そのL値を2.6nHとしている。また、1次コイルと4次コイルとの磁気的な結合係数k値を0.565としている。キャパシタ42を理想キャパシタとし、そのC値を0.42pFとしている。その他の回路定数は、図3に示す通過特性の計算と同様である。

【0053】

図8を参照して、電力増幅器103の出力信号の周波数が2.4GHzである場合、この出力信号の3倍の周波数である7.2GHzにおいて、30dBの通過損失が得られる。また、電力増幅器101と比べて新たに追加された4次コイル24およびキャパシタ42により、電力増幅器103の出力信号の周波数が2.4GHzである場合、この出力信号の2倍の周波数である4.8GHzにおいて、40dBの通過損失が得られる。即ち、電力増幅器103では、トランス20と3次コイル23とキャパシタ41とを含む回路ブロックが、出力信号の周波数である2.4GHzの3倍の周波数成分を抑制する機能を有し、さらに、トランス20と4次コイル24とキャパシタ42とを含む回路ブロックが、2.4GHzの2倍の周波数成分を抑制する機能を有していることがわかる。

【0054】

1差動対のトランス型電力増幅器では、入力信号1および入力信号2が理想的な差動信号であり、増幅器11および増幅器12が全く同じ特性を有している場合であって1次コイル21、2次コイル22、3次コイル23および4次コイル24が対称な形状を有しているときには、2次高調波は出力信号3には現れない。

【0055】

しかしながら、増幅器11および増幅器12はMOS型トランジスタで構成されているため、全く同じ特性とはならず、また、各コイルも完全な対称形状にはならない。

【0056】

したがって、本発明の第2の実施の形態に係る電力増幅器のように、4次コイル24およびキャパシタ42を追加することにより、2次高調波を確実に抑制することは非常に効果的である。

【0057】

その他の構成および動作は第1の実施の形態に係る電力増幅器と同様であるため、ここでは詳細な説明を繰り返さない。

【0058】

次に、本発明の他の実施の形態について図面を用いて説明する。なお、図中同一または相当部分には同一符号を付してその説明は繰り返さない。

【0059】

<第3の実施の形態>

本実施の形態は、第1の実施の形態に係る電力増幅器と比べてさらに高出力化を図った電力増幅器に関する。以下で説明する内容以外は第1の実施の形態に係る電力増幅器と同様である。

【0060】

図9は、本発明の第3の実施の形態に係る電力増幅器における各コイルの概略レイアウトを示す図である。

【0061】

図9を参照して、電力増幅器104は、2差動対のトランス型電力増幅器であり、増幅器11aおよび12aと、トランス20aと、キャパシタ31aおよび41aと、3次コイル23aと、増幅器11bおよび12bと、トランス20bと、キャパシタ31bおよび41bと、3次コイル23bと、端子T1〜T4,T5a,T5bとを備える。トランス20aは、1次コイル21aと、2次コイル22aとを含む。トランス20bは、1次コイル21bと、2次コイル22bとを含む。

【0062】

増幅器11aおよび12aと、トランス20aと、キャパシタ31aおよび41aと、3次コイル23aと、端子T1〜T4,T5aとは、本発明の第1の実施の形態に係る電力増幅器における増幅器11および12と、トランス20と、キャパシタ31および41と、3次コイル23と、端子T1〜T4,T5とにそれぞれ対応している。このため、本発明の第1の実施の形態に係る電力増幅器と重複する内容については詳細な説明を繰り返さない。

【0063】

増幅器11bおよび12bは、それぞれ端子T1およびT2を介して受けた入力信号1および入力信号2を増幅する。

【0064】

トランス20bは、増幅器11bの出力信号および増幅器12bの出力信号を合成する。すなわち、1次コイル21bは、増幅器11bによって増幅された入力信号1を受ける第1端と、増幅器12bによって増幅された入力信号2を受ける第2端とを有する。1次コイル21bの中点に端子T5bが接続され、この端子T5bに電源電圧4が供給されている。

【0065】

キャパシタ31bは、1次コイル21bの第1端と第2端との間に接続されている。1次コイル21bおよびキャパシタ31bは、増幅器11bおよび12bの出力整合回路を構成している。

【0066】

2次コイル22bは、1次コイル21bと磁気的に結合され、コイル22aと接続されている。2次コイル22bの第2端が端子T4を介して接地され、2次コイル22aの第1端から出力信号3が取り出される。

【0067】

より詳細には、2次コイル22aは、端子T3に接続された第1端と、2次コイル22bの第1端に接続された第2端とを有する。2次コイル22bは、2次コイル22aの第2端に接続された第1端と、端子T4に接続された第2端とを有する。電力増幅器104の出力信号3すなわち増幅器11aおよび12aによって増幅された入力信号1および入力信号2ならびに増幅器11bおよび12bによって増幅された入力信号1および入力信号2の合成信号3は、端子T3から出力される。端子T4は、接地電圧が供給される接地ノードに接続されている。

【0068】

3次コイル23aおよびキャパシタ41aは並列に接続され、3次コイル23bおよびキャパシタ41bは並列に接続されている。3次コイル23aおよびキャパシタ41aからなる並列回路と3次コイル23bおよびキャパシタ41bからなる並列回路とが直列に接続されている。

【0069】

より詳細には、3次コイル23aは、2次コイル22aと磁気的に結合され、キャパシタ41aの第1端に接続された第1端と、キャパシタ41aの第2端および3次コイル23bの第1端に接続された第2端とを有する。

【0070】

3次コイル23bは、2次コイル22bと磁気的に結合され、キャパシタ41bの第1端に接続された第1端と、キャパシタ41bの第2端および接地電圧が供給される接地ノードに接続された第2端とを有する。キャパシタ41bは、コイル23bの両端間に接続されている。

【0071】

たとえば、増幅器11a、11b、12aおよび12bは同じ構成であり、3次コイル23aおよび3次コイル23bは同じL値を有し、キャパシタ41aおよびキャパシタ41bは異なるC値を有している。

【0072】

図10は、本発明の第3の実施の形態に係る電力増幅器に適用されるトランス20a,20bと3次コイル23a,23bとキャパシタ41a,41bとを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。

【0073】

図10に示す通過特性の計算においては、1次コイル21a,21bを理想インダクタとし、そのL(インダクタンス)値を2.4nHとしている。2次コイル22a,22bを理想インダクタとし、そのL値を2.2nHとしている。3次コイル23a,23bを理想インダクタとし、そのL値を2.0nHとしている。また、1次コイルと2次コイルとの磁気的な結合係数k値を0.565とし、2次コイルと3次コイルとの磁気的な結合係数k値を0.565としている。また、キャパシタ41a,41bを理想キャパシタとし、そのC(キャパシタンス)値をそれぞれ0.24pF,0.54pFとしている。

【0074】

図10を参照して、電力増幅器104の出力信号の周波数が2.4GHzである場合、この出力信号の3倍の周波数である7.2GHzにおいて、30dBの通過損失が得られ、2倍の周波数である4.8GHzにおいて、25dBの通過損失が得られる。即ち、電力増幅器104は、出力信号の周波数である2.4GHzの2倍の周波数成分および3倍の周波数成分を抑制する機能を有していることがわかる。

【0075】

したがって、本発明の第3の実施の形態に係る電力増幅器では、高次の周波数歪、すなわち3次高調波歪を抑えるだけでなく、2次高調波歪を抑える効果が得られるとともに、2対の差動信号を合成することにより高出力化を図ることができる。

【0076】

なお、本発明の第3の実施の形態に係る電力増幅器では、2次高調波歪および3次高調波歪を抑えるために、3次コイル23a,23bを同じL値に設定し、キャパシタ41a,41bのC値を異なる値に設定することにより、出力信号の2倍の周波数および3倍の周波数に対応する共振周波数をそれぞれ得たが、このような構成に限定するものではない。キャパシタ41a,41bを同じC値に設定し、3次コイル23a,23bのL値を異なる値に設定することにより、これらの共振周波数を得ることも可能である。

【0077】

その他の構成および動作は第1の実施の形態に係る電力増幅器と同様であるため、ここでは詳細な説明を繰り返さない。

【0078】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【図面の簡単な説明】

【0079】

【図1】本発明の第1の実施の形態に係る電力増幅器の構成を示す図である。

【図2】本発明の第1の実施の形態に係る電力増幅器における各コイルの概略レイアウトを示す図である。

【図3】本発明の第1の実施の形態に係る電力増幅器に適用されるトランス20と3次コイル23とキャパシタ41とを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。

【図4】本発明の第1の実施の形態に係る電力増幅器の入出力特性を示す図である。

【図5】本発明の第1の実施の形態に係る電力増幅器において、キャパシタ41にMOS型トランジスタを適用した構成を示す図である。

【図6】図5に示す電力増幅器102に適用されるトランス20と3次コイル23とキャパシタ41とを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。

【図7】本発明の第2の実施の形態に係る電力増幅器における各コイルの概略レイアウトを示す図である。

【図8】本発明の第2の実施の形態に係る電力増幅器に適用されるトランス20と3次コイル23と4次コイル24とキャパシタ41とキャパシタ42とを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。

【図9】本発明の第3の実施の形態に係る電力増幅器における各コイルの概略レイアウトを示す図である。

【図10】本発明の第3の実施の形態に係る電力増幅器に適用されるトランス20a,20bと3次コイル23a,23bとキャパシタ41a,41bとを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。

【符号の説明】

【0080】

11,12,11a,12a,11b,12b 増幅器、20,20a,20b トランス、21,21a,21b 1次コイル、22,22a,22b 2次コイル、23,23a,23b 3次コイル、24 4次コイル、31,41,42,31a,41a,31b,41b キャパシタ、51a,51b,52a,52b,53a,53b NチャネルMOS型トランジスタ、61a,61b ゲート抵抗、101,102,103,104 電力増幅器、T1〜T6,T5a,T5b 端子。

【技術分野】

【0001】

本発明は、電力増幅器に関し、特に、差動信号の増幅および合成を行なう電力増幅器に関する。

【背景技術】

【0002】

携帯電話端末および無線LAN端末においては、送信機即ち電力増幅器は、最大で10〜30dBmの電力を送信する必要がある。信号周波数が1GHz〜6GHz程度である電力増幅器において、近年、シリコンMOS型トランジスタ(絶縁ゲート型電界効果トランジスタ)を用い、1対のトランジスタで増幅された差動信号をトランスで合成する手法が提案されている。このような電力増幅器は、たとえば非特許文献1のFigure.11.9.2に示されており、以下、1差動対のトランス型電力増幅器と呼ぶ。

【0003】

この非特許文献1に記載の電力増幅器においては、1次コイル(非特許文献1では、コイルのことをスラブと呼ぶ)と、この1次コイルとの磁気的結合を有する2次コイルとが互いに平行に配置されている。1次コイルの中点は電源電圧が供給される端子であり、この中点にキャパシタを接続することで、2次高調波を抑圧することができる。

【0004】

このような1差動対のトランス型電力増幅器よりもさらに高出力化を図る手法として、2対以上のトランジスタからの差動増幅信号をトランスで合成することが提案されている。このような電力増幅器は、たとえば分布型環状電力増幅器として特許文献1に示されており、以下、多差動対のトランス型電力増幅器と呼ぶ。この特許文献1では、4対のトランジスタによりそれぞれ増幅された差動信号を、直列接続されたトランスの2次コイルによって合成する構成が開示されている。

【0005】

非特許文献1に記載の1差動対のトランス型電力増幅器よりもさらに高効率化を図る他の手法として、特許文献2には、2対のトランジスタの差動信号をトランスで合成し、トランスの2次コイルの両側に形状の異なる1次コイルを配置する構成が開示されている。

【非特許文献1】Jongchan Kang, et. al. “A Single-Chip Linear CMOS Power Amplifier for 2.4 GHz WLAN” ISSCC(International Solid-State Circuits Conference)2006, p208-209.

【特許文献1】特表2005−503679号公報

【特許文献2】特開2006−295896号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、非特許文献1では、2次高調波を抑制するための構成は開示されているが、2次高調波とともに出力信号に含まれる3次高調波を抑制することについては何ら考慮されていない。また、特許文献1および特許文献2では、2次高調波の抑制および3次高調波の抑制のいずれも考慮されていない。

【0007】

それゆえに、この発明の目的は、差動信号の増幅および合成を行ない、かつ高調波を抑制することが可能な電力増幅器を提供することである。

【課題を解決するための手段】

【0008】

上記課題を解決するために、この発明のある局面に係わる電力増幅器は、差動信号である第1の入力信号および第2の入力信号を増幅する第1の増幅器と、第1の増幅器によって増幅された第1の入力信号および第2の入力信号を受ける第1のコイルと、第1のコイルと磁気的に結合され、増幅された第1の入力信号および第2の入力信号の合成信号が出力される第2のコイルと、第2のコイルと磁気的に結合された第3のコイルと、第3のコイルの両端間に接続された第1のキャパシタとを備え、第1のキャパシタの一端が接地ノードに接続されている。

【発明の効果】

【0009】

本発明によれば、差動信号の増幅および合成を行ない、かつ高調波を抑制することができる。

【発明を実施するための最良の形態】

【0010】

以下、本発明の実施の形態について図面を用いて説明する。なお、図中同一または相当部分には同一符号を付してその説明は繰り返さない。

【0011】

<第1の実施の形態>

図1は、本発明の第1の実施の形態に係る電力増幅器の構成を示す図である。

【0012】

図1を参照して、電力増幅器101は、1差動対のトランス型電力増幅器であり、増幅器11および12と、トランス20と、キャパシタ31および41と、3次コイル23と、端子T1〜T5を備える。トランス20は、1次コイル21と、2次コイル22とを含む。

【0013】

増幅器11および12は、それぞれ端子T1およびT2を介して受けた入力信号1および入力信号2を増幅する。入力信号1および入力信号2は、たとえば互いの位相が180度異なる差動信号である。

【0014】

トランス20は、増幅器11の出力信号および増幅器12の出力信号を合成する。すなわち、1次コイル21は、増幅器11によって増幅された入力信号1を受ける第1端と、増幅器12によって増幅された入力信号2を受ける第2端とを有する。1次コイル21の中点に端子T5が接続され、この端子T5に電源電圧4が供給される。

【0015】

キャパシタ31は、1次コイル21の第1端と第2端との間に接続されている。1次コイル21およびキャパシタ31は、増幅器11および12の出力整合回路を構成している。

【0016】

2次コイル22は、1次コイル21と磁気的に結合され、増幅後の入力信号1および入力信号2の合成信号3が出力される。より詳細には、2次コイル22は、端子T3に接続された第1端と、端子T4に接続された第2端とを有する。電力増幅器101の出力信号3すなわち増幅後の入力信号1および入力信号2の合成信号3は、端子T3から出力される。端子T4は、接地電圧が供給される接地ノードに接続されている。

【0017】

3次コイル23は、2次コイル22と磁気的に結合され、キャパシタ41の第1端に接続された第1端と、キャパシタ41の第2端および接地電圧が供給される接地ノードに接続された第2端とを有する。

【0018】

図2は、本発明の第1の実施の形態に係る電力増幅器における各コイルの概略レイアウトを示す図である。

【0019】

図2を参照して、電力増幅器101は、図1に示す回路が設けられた主表面を有する半導体基板Bを備える。

【0020】

1次コイル21、2次コイル22および3次コイル23は半導体基板Bの同一主表面上に配線層を用いて形成され、略C字型の形状を有する。たとえば、最外周に1次コイル21が配置され、1次コイル21の内側に2次コイル22が配置され、2次コイル22の内側に3次コイル23が配置されている。3次コイルの両端間にキャパシタ41が接続されている。キャパシタ41は、2次コイル22の内側に配置されている。

【0021】

より詳細には、1次コイル21は、半導体基板Bの主表面に設けられ、周方向に延伸し、その周方向において一部区間が開放された導電線路によって形成されている。

【0022】

2次コイル22は、半導体基板Bの主表面に設けられ、周方向に延伸し、その周方向において一部区間が開放された導電線路によって形成されている。

【0023】

1次コイル21は、2次コイル22を囲むように配置されている。なお、2次コイル22が、1次コイル21を囲むように配置されている構成であってもよい。

【0024】

3次コイル23は、半導体基板Bの主表面に設けられ、周方向に延伸し、その周方向において一部区間が開放され、1次コイル21および2次コイル22に囲まれた導電線路によって形成されている。

【0025】

増幅器11は、たとえばNチャネルMOS型トランジスタ51aおよび51bをカスコード接続した回路で構成される。増幅器12は、たとえばNチャネルMOS型トランジスタ52aおよび52bをカスコード接続した回路で構成される。

【0026】

より詳細には、NチャネルMOS型トランジスタ51aは、ドレインと、接地ノードに接続されたソースと、入力信号1を受けるゲートとを有する。NチャネルMOS型トランジスタ51bは、1次コイル21の第1端に接続されたドレインと、NチャネルMOS型トランジスタ51aのドレインに接続されたソースと、所定電圧を受けるゲートとを有する。NチャネルMOS型トランジスタ52aは、ドレインと、接地ノードに接続されたソースと、入力信号2を受けるゲートとを有する。NチャネルMOS型トランジスタ52bは、1次コイル21の第2端に接続されたドレインと、NチャネルMOS型トランジスタ52aのドレインに接続されたソースと、所定電圧を受けるゲートとを有する。

【0027】

図3は、本発明の第1の実施の形態に係る電力増幅器に適用されるトランス20と3次コイル23とキャパシタ41とを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。

【0028】

図3に示す通過特性の計算においては、1次コイル21を理想インダクタとし、そのL(インダクタンス)値を2.4nHとしている。2次コイル22を理想インダクタとし、そのL値を2.2nHとしている。3次コイル23を理想インダクタとし、そのL値を2.0nHとしている。また、1次コイルと2次コイルとの磁気的な結合係数k値を0.565とし、2次コイルと3次コイルとの磁気的な結合係数k値を0.565としている。また、キャパシタ41を理想キャパシタとし、そのC(キャパシタンス)値を0.24pFとしている。

【0029】

図3を参照して、電力増幅器101の出力信号の周波数が2.4GHzである場合、この出力信号の3倍の周波数である7.2GHzにおいて、40dBの通過損失が得られる。即ち、トランス20と3次コイル23とキャパシタ41とを含む回路ブロックが、出力信号の周波数である2.4GHzの3倍の周波数成分を抑制する機能を有していることがわかる。

【0030】

図4は、本発明の第1の実施の形態に係る電力増幅器の入出力特性を示す図である。図4では、トランス20と3次コイル23とキャパシタ41とを含む回路ブロックの回路定数をそのまま用い、かつ図2に示すMOS型トランジスタ51a、51b、52aおよび52bに対して等価回路モデルを適用した条件で、2.4GHzの入力信号に対する出力信号特性を計算した結果を示している。図4において、グラフG1が基本波である2.4GHzの入力信号に対する出力信号特性を示しており、グラフG2が2.4GHzの入力信号に対する3次高調波信号特性を示している。また、比較のため、電力増幅器101が3次コイル23およびキャパシタ41を備えないと仮定した構成における、2.4GHzの入力信号に対する3次高調波信号特性をグラフG3に示している。

【0031】

グラフG1〜G3より、電力増幅器101では、3次コイル23およびキャパシタ41で構成されるLC共振回路により、3次高調波成分が20dB程度抑制されていることがわかる。

【0032】

したがって、本発明の第1の実施の形態に係る電力増幅器では、高次の周波数歪、すなわち2次コイル22から出力される合成信号3における3次高調波を抑制する効果が得られる。これにより、出力特性が改善される。また、トランス20の内側に3次コイル23およびキャパシタ41を配置することにより、半導体基板Bにおける実質的な面積増加を伴わず、電力増幅器101のサイズの増大を防ぐことができる。

【0033】

なお、本発明の第1の実施の形態に係る電力増幅器では、1次コイル21、2次コイル22および3次コイル23は略C字型の形状を有する構成であるとしたが、これに限定するものではない。半導体基板Bの主表面において、1次コイル21および2次コイル22によって全周を取り囲まれた領域(図2のAR)が形成され、3次コイル23がこの領域AR内に設けられている構成であれば、電力増幅器101のサイズの増大を防ぐことができる。

【0034】

図5は、本発明の第1の実施の形態に係る電力増幅器において、キャパシタ41にMOS型トランジスタを適用した構成を示す図である。

【0035】

図5を参照して、電力増幅器102は、電力増幅器101と比べて、さらに、端子T6を備える。キャパシタ41は、NチャネルMOS型トランジスタ53a,53bと、ゲート抵抗61a,61bとを含む。

【0036】

前述した電力増幅器101は、3次コイル23およびキャパシタ41によって3次高調波成分を抑制する構成である。

【0037】

MOS型トランジスタ53aのドレインとMOS型トランジスタ53bのドレインとが接続されている。MOS型トランジスタ53a,53bのソースと3次コイル23の第1端および第2端とがそれぞれ接続されている。MOS型トランジスタ53bのソースは接地されている。MOS型トランジスタ53a,53bのゲートは、ゲート抵抗61a,61bを介して端子T6に接続されている。この端子T6には、制御信号5が与えられる。

【0038】

制御信号5は、たとえば、+3.3Vおよび−3.3Vの2つのDC電圧に設定される。制御信号5が−3.3VのDC電圧に設定されると、MOS型トランジスタ53a,53bはオフするため、MOS型トランジスタ53a,53bはキャパシタとして機能する。一方、制御信号5が+3.3VのDC電圧に設定されると、MOS型トランジスタ53a,53bはオンするため、抵抗として機能する。

【0039】

図6は、図5に示す電力増幅器102に適用されるトランス20と3次コイル23とキャパシタ41とを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。図6に示す通過特性の計算においては、MOS型トランジスタ53a,53bのゲート幅を2mmとし、ゲート抵抗61a,61bのR(抵抗)値を40kΩとしている。グラフG1は、制御信号5が+3.3VのDC電圧に設定された場合を示し、グラフG2は、制御信号5が−3.3VのDC電圧に設定された場合を示している。その他の回路定数は、図3に示す通過特性の計算と同様である。

【0040】

グラフG2より、制御信号5が−3.3VのDC電圧に設定されている場合には、図3と同程度の通過特性が得られていることがわかる。

【0041】

一方、グラフG1より、制御信号5が+3.3VのDC電圧に設定されている場合には、図3に示す通過特性とは異なり、3次高調波成分が抑制されておらず、3次コイル23が無い場合の特性とほぼ同じである。しかしながら、2.4GHzの出力信号の通過損失は、図3に示す通過特性と比べて約0.6dB小さい。

【0042】

一般に、電力増幅器では、入力電力が小さい場合には、図4からもわかるように3次高調波成分は小さい。

【0043】

したがって、電力増幅器102では、入力電力が小さい場合には、制御信号5を+3.3VのDC電圧に設定することにより出力信号の通過損失を抑えることができる。一方、入力電力が大きい場合には、制御信号5を−3.3VのDC電圧に設定することにより3次高調波成分を抑えることができる。

【0044】

次に、本発明の他の実施の形態について図面を用いて説明する。なお、図中同一または相当部分には同一符号を付してその説明は繰り返さない。

【0045】

<第2の実施の形態>

本実施の形態は、第1の実施の形態に係る電力増幅器と比べてコイルを追加した電力増幅器に関する。以下で説明する内容以外は第1の実施の形態に係る電力増幅器と同様である。

【0046】

図7は、本発明の第2の実施の形態に係る電力増幅器における各コイルの概略レイアウトを示す図である。

【0047】

図7を参照して、電力増幅器103は、本発明の第1の実施の形態に係る電力増幅器と比べて、さらに、4次コイル24と、キャパシタ42とを備える。

【0048】

4次コイル24は、たとえば、1次コイル21の外側に配置されている。4次コイル24は、1次コイル21、2次コイル22および3次コイル23と同じ半導体基板Bの主表面上に配線層を用いて形成され、略C字型の形状を有する。4次コイル24の両端間にキャパシタ42が接続されている。

【0049】

より詳細には、4次コイル24は、1次コイル21と磁気的に結合され、キャパシタ42の第1端に接続された第1端と、キャパシタ42の第2端および接地電圧が供給される接地ノードに接続された第2端とを有する。キャパシタ42は、4次コイル24の第1端と第2端との間に接続されている。

【0050】

4次コイル24は、半導体基板Bの主表面に設けられ、1次コイル21ないし3次コイル23を囲むように周方向に延伸し、その周方向において一部区間が開放された導電線路によって形成されている。

【0051】

図8は、本発明の第2の実施の形態に係る電力増幅器に適用されるトランス20と3次コイル23と4次コイル24とキャパシタ41とキャパシタ42とを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。

【0052】

図8に示す通過特性の計算においては、4次コイル24を理想インダクタとし、そのL値を2.6nHとしている。また、1次コイルと4次コイルとの磁気的な結合係数k値を0.565としている。キャパシタ42を理想キャパシタとし、そのC値を0.42pFとしている。その他の回路定数は、図3に示す通過特性の計算と同様である。

【0053】

図8を参照して、電力増幅器103の出力信号の周波数が2.4GHzである場合、この出力信号の3倍の周波数である7.2GHzにおいて、30dBの通過損失が得られる。また、電力増幅器101と比べて新たに追加された4次コイル24およびキャパシタ42により、電力増幅器103の出力信号の周波数が2.4GHzである場合、この出力信号の2倍の周波数である4.8GHzにおいて、40dBの通過損失が得られる。即ち、電力増幅器103では、トランス20と3次コイル23とキャパシタ41とを含む回路ブロックが、出力信号の周波数である2.4GHzの3倍の周波数成分を抑制する機能を有し、さらに、トランス20と4次コイル24とキャパシタ42とを含む回路ブロックが、2.4GHzの2倍の周波数成分を抑制する機能を有していることがわかる。

【0054】

1差動対のトランス型電力増幅器では、入力信号1および入力信号2が理想的な差動信号であり、増幅器11および増幅器12が全く同じ特性を有している場合であって1次コイル21、2次コイル22、3次コイル23および4次コイル24が対称な形状を有しているときには、2次高調波は出力信号3には現れない。

【0055】

しかしながら、増幅器11および増幅器12はMOS型トランジスタで構成されているため、全く同じ特性とはならず、また、各コイルも完全な対称形状にはならない。

【0056】

したがって、本発明の第2の実施の形態に係る電力増幅器のように、4次コイル24およびキャパシタ42を追加することにより、2次高調波を確実に抑制することは非常に効果的である。

【0057】

その他の構成および動作は第1の実施の形態に係る電力増幅器と同様であるため、ここでは詳細な説明を繰り返さない。

【0058】

次に、本発明の他の実施の形態について図面を用いて説明する。なお、図中同一または相当部分には同一符号を付してその説明は繰り返さない。

【0059】

<第3の実施の形態>

本実施の形態は、第1の実施の形態に係る電力増幅器と比べてさらに高出力化を図った電力増幅器に関する。以下で説明する内容以外は第1の実施の形態に係る電力増幅器と同様である。

【0060】

図9は、本発明の第3の実施の形態に係る電力増幅器における各コイルの概略レイアウトを示す図である。

【0061】

図9を参照して、電力増幅器104は、2差動対のトランス型電力増幅器であり、増幅器11aおよび12aと、トランス20aと、キャパシタ31aおよび41aと、3次コイル23aと、増幅器11bおよび12bと、トランス20bと、キャパシタ31bおよび41bと、3次コイル23bと、端子T1〜T4,T5a,T5bとを備える。トランス20aは、1次コイル21aと、2次コイル22aとを含む。トランス20bは、1次コイル21bと、2次コイル22bとを含む。

【0062】

増幅器11aおよび12aと、トランス20aと、キャパシタ31aおよび41aと、3次コイル23aと、端子T1〜T4,T5aとは、本発明の第1の実施の形態に係る電力増幅器における増幅器11および12と、トランス20と、キャパシタ31および41と、3次コイル23と、端子T1〜T4,T5とにそれぞれ対応している。このため、本発明の第1の実施の形態に係る電力増幅器と重複する内容については詳細な説明を繰り返さない。

【0063】

増幅器11bおよび12bは、それぞれ端子T1およびT2を介して受けた入力信号1および入力信号2を増幅する。

【0064】

トランス20bは、増幅器11bの出力信号および増幅器12bの出力信号を合成する。すなわち、1次コイル21bは、増幅器11bによって増幅された入力信号1を受ける第1端と、増幅器12bによって増幅された入力信号2を受ける第2端とを有する。1次コイル21bの中点に端子T5bが接続され、この端子T5bに電源電圧4が供給されている。

【0065】

キャパシタ31bは、1次コイル21bの第1端と第2端との間に接続されている。1次コイル21bおよびキャパシタ31bは、増幅器11bおよび12bの出力整合回路を構成している。

【0066】

2次コイル22bは、1次コイル21bと磁気的に結合され、コイル22aと接続されている。2次コイル22bの第2端が端子T4を介して接地され、2次コイル22aの第1端から出力信号3が取り出される。

【0067】

より詳細には、2次コイル22aは、端子T3に接続された第1端と、2次コイル22bの第1端に接続された第2端とを有する。2次コイル22bは、2次コイル22aの第2端に接続された第1端と、端子T4に接続された第2端とを有する。電力増幅器104の出力信号3すなわち増幅器11aおよび12aによって増幅された入力信号1および入力信号2ならびに増幅器11bおよび12bによって増幅された入力信号1および入力信号2の合成信号3は、端子T3から出力される。端子T4は、接地電圧が供給される接地ノードに接続されている。

【0068】

3次コイル23aおよびキャパシタ41aは並列に接続され、3次コイル23bおよびキャパシタ41bは並列に接続されている。3次コイル23aおよびキャパシタ41aからなる並列回路と3次コイル23bおよびキャパシタ41bからなる並列回路とが直列に接続されている。

【0069】

より詳細には、3次コイル23aは、2次コイル22aと磁気的に結合され、キャパシタ41aの第1端に接続された第1端と、キャパシタ41aの第2端および3次コイル23bの第1端に接続された第2端とを有する。

【0070】

3次コイル23bは、2次コイル22bと磁気的に結合され、キャパシタ41bの第1端に接続された第1端と、キャパシタ41bの第2端および接地電圧が供給される接地ノードに接続された第2端とを有する。キャパシタ41bは、コイル23bの両端間に接続されている。

【0071】

たとえば、増幅器11a、11b、12aおよび12bは同じ構成であり、3次コイル23aおよび3次コイル23bは同じL値を有し、キャパシタ41aおよびキャパシタ41bは異なるC値を有している。

【0072】

図10は、本発明の第3の実施の形態に係る電力増幅器に適用されるトランス20a,20bと3次コイル23a,23bとキャパシタ41a,41bとを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。

【0073】

図10に示す通過特性の計算においては、1次コイル21a,21bを理想インダクタとし、そのL(インダクタンス)値を2.4nHとしている。2次コイル22a,22bを理想インダクタとし、そのL値を2.2nHとしている。3次コイル23a,23bを理想インダクタとし、そのL値を2.0nHとしている。また、1次コイルと2次コイルとの磁気的な結合係数k値を0.565とし、2次コイルと3次コイルとの磁気的な結合係数k値を0.565としている。また、キャパシタ41a,41bを理想キャパシタとし、そのC(キャパシタンス)値をそれぞれ0.24pF,0.54pFとしている。

【0074】

図10を参照して、電力増幅器104の出力信号の周波数が2.4GHzである場合、この出力信号の3倍の周波数である7.2GHzにおいて、30dBの通過損失が得られ、2倍の周波数である4.8GHzにおいて、25dBの通過損失が得られる。即ち、電力増幅器104は、出力信号の周波数である2.4GHzの2倍の周波数成分および3倍の周波数成分を抑制する機能を有していることがわかる。

【0075】

したがって、本発明の第3の実施の形態に係る電力増幅器では、高次の周波数歪、すなわち3次高調波歪を抑えるだけでなく、2次高調波歪を抑える効果が得られるとともに、2対の差動信号を合成することにより高出力化を図ることができる。

【0076】

なお、本発明の第3の実施の形態に係る電力増幅器では、2次高調波歪および3次高調波歪を抑えるために、3次コイル23a,23bを同じL値に設定し、キャパシタ41a,41bのC値を異なる値に設定することにより、出力信号の2倍の周波数および3倍の周波数に対応する共振周波数をそれぞれ得たが、このような構成に限定するものではない。キャパシタ41a,41bを同じC値に設定し、3次コイル23a,23bのL値を異なる値に設定することにより、これらの共振周波数を得ることも可能である。

【0077】

その他の構成および動作は第1の実施の形態に係る電力増幅器と同様であるため、ここでは詳細な説明を繰り返さない。

【0078】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【図面の簡単な説明】

【0079】

【図1】本発明の第1の実施の形態に係る電力増幅器の構成を示す図である。

【図2】本発明の第1の実施の形態に係る電力増幅器における各コイルの概略レイアウトを示す図である。

【図3】本発明の第1の実施の形態に係る電力増幅器に適用されるトランス20と3次コイル23とキャパシタ41とを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。

【図4】本発明の第1の実施の形態に係る電力増幅器の入出力特性を示す図である。

【図5】本発明の第1の実施の形態に係る電力増幅器において、キャパシタ41にMOS型トランジスタを適用した構成を示す図である。

【図6】図5に示す電力増幅器102に適用されるトランス20と3次コイル23とキャパシタ41とを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。

【図7】本発明の第2の実施の形態に係る電力増幅器における各コイルの概略レイアウトを示す図である。

【図8】本発明の第2の実施の形態に係る電力増幅器に適用されるトランス20と3次コイル23と4次コイル24とキャパシタ41とキャパシタ42とを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。

【図9】本発明の第3の実施の形態に係る電力増幅器における各コイルの概略レイアウトを示す図である。

【図10】本発明の第3の実施の形態に係る電力増幅器に適用されるトランス20a,20bと3次コイル23a,23bとキャパシタ41a,41bとを含む回路ブロックの高周波領域における通過特性の計算結果を示す図である。

【符号の説明】

【0080】

11,12,11a,12a,11b,12b 増幅器、20,20a,20b トランス、21,21a,21b 1次コイル、22,22a,22b 2次コイル、23,23a,23b 3次コイル、24 4次コイル、31,41,42,31a,41a,31b,41b キャパシタ、51a,51b,52a,52b,53a,53b NチャネルMOS型トランジスタ、61a,61b ゲート抵抗、101,102,103,104 電力増幅器、T1〜T6,T5a,T5b 端子。

【特許請求の範囲】

【請求項1】

差動信号である第1の入力信号および第2の入力信号を増幅する第1の増幅器と、

前記第1の増幅器によって増幅された前記第1の入力信号および前記第2の入力信号を受ける第1のコイルと、

前記第1のコイルと磁気的に結合され、前記増幅された前記第1の入力信号および前記第2の入力信号の合成信号が出力される第2のコイルと、

前記第2のコイルと磁気的に結合された第3のコイルと、

前記第3のコイルの両端間に接続された第1のキャパシタとを備え、

前記第1のキャパシタの一端が接地ノードに接続されている電力増幅器。

【請求項2】

前記電力増幅器は、さらに、半導体基板を備え、

前記第1のコイルおよび前記第2のコイルは前記半導体基板の主表面に設けられ、

前記半導体基板の主表面において、前記第1のコイルおよび前記第2のコイルによって全周を取り囲まれた領域が形成され、

前記第3のコイルは、前記領域内に設けられている請求項1に記載の電力増幅器。

【請求項3】

前記第1のキャパシタは、

前記第3のコイルの第1端に接続された第1導通電極と、第2導通電極と、制御電極とを有する第1のトランジスタと、

前記第3のコイルの第2端に接続された第1導通電極と、前記第1のトランジスタの第2導通電極に接続された第2導通電極と、前記第1のトランジスタの制御電極に接続された制御電極とを有する第2のトランジスタとを含む請求項1に記載の電力増幅器。

【請求項4】

前記電力増幅器は、さらに、

前記第1のコイルと磁気的に結合された第4のコイルと、

前記第4のコイルの両端間に接続された第2のキャパシタとを備え、

前記第2のキャパシタの一端が接地ノードに接続されている請求項1に記載の電力増幅器。

【請求項5】

前記電力増幅器は、さらに、半導体基板を備え、

前記第1のコイルおよび前記第2のコイルは前記半導体基板の主表面に設けられ、

前記半導体基板の主表面において、前記第1のコイルおよび前記第2のコイルによって全周を取り囲まれた領域が形成され、

前記第3のコイルは、前記領域内に設けられ、

前記第4のコイルは、前記第1のコイルおよび第2のコイルを囲むように前記半導体基板の主表面に設けられている請求項4に記載の電力増幅器。

【請求項6】

前記電力増幅器は、さらに、

前記第1の入力信号および前記第2の入力信号を増幅する第2の増幅器と、

前記第2の増幅器によって増幅された前記第1の入力信号および前記第2の入力信号を受ける第5のコイルと、

前記第5のコイルと磁気的に結合され、かつ前記第2のコイルの一端と接続された第6のコイルと、

前記第6のコイルと磁気的に結合され、かつ前記第3のコイルの一端と接続された第7のコイルと、

前記第7のコイルの両端間に接続された第3のキャパシタとを備え、

前記第2のコイルおよび前記第6のコイルから、前記第1の増幅器によって増幅された前記第1の入力信号および前記第2の入力信号ならびに前記第2の増幅器によって増幅された前記第1の入力信号および前記第2の入力信号の合成信号が出力される請求項1に記載の電力増幅器。

【請求項7】

前記1次コイルは、前記増幅器によって増幅された前記第1の入力信号を受ける第1端と、前記第2の入力信号を受ける第2端とを有し、

前記2次コイルは、接地ノードに接続された第1端を有し、前記第1端を接地することにより、前記増幅された前記第1の入力信号および前記第2の入力信号の合成信号が出力される第2端とを有し、

前記3次コイルは、前記第1のキャパシタの第1端に接続された第1端と、前記第1のキャパシタの第2端および接地ノードに接続された第2端とを有する請求項1に記載の電力増幅器。

【請求項1】

差動信号である第1の入力信号および第2の入力信号を増幅する第1の増幅器と、

前記第1の増幅器によって増幅された前記第1の入力信号および前記第2の入力信号を受ける第1のコイルと、

前記第1のコイルと磁気的に結合され、前記増幅された前記第1の入力信号および前記第2の入力信号の合成信号が出力される第2のコイルと、

前記第2のコイルと磁気的に結合された第3のコイルと、

前記第3のコイルの両端間に接続された第1のキャパシタとを備え、

前記第1のキャパシタの一端が接地ノードに接続されている電力増幅器。

【請求項2】

前記電力増幅器は、さらに、半導体基板を備え、

前記第1のコイルおよび前記第2のコイルは前記半導体基板の主表面に設けられ、

前記半導体基板の主表面において、前記第1のコイルおよび前記第2のコイルによって全周を取り囲まれた領域が形成され、

前記第3のコイルは、前記領域内に設けられている請求項1に記載の電力増幅器。

【請求項3】

前記第1のキャパシタは、

前記第3のコイルの第1端に接続された第1導通電極と、第2導通電極と、制御電極とを有する第1のトランジスタと、

前記第3のコイルの第2端に接続された第1導通電極と、前記第1のトランジスタの第2導通電極に接続された第2導通電極と、前記第1のトランジスタの制御電極に接続された制御電極とを有する第2のトランジスタとを含む請求項1に記載の電力増幅器。

【請求項4】

前記電力増幅器は、さらに、

前記第1のコイルと磁気的に結合された第4のコイルと、

前記第4のコイルの両端間に接続された第2のキャパシタとを備え、

前記第2のキャパシタの一端が接地ノードに接続されている請求項1に記載の電力増幅器。

【請求項5】

前記電力増幅器は、さらに、半導体基板を備え、

前記第1のコイルおよび前記第2のコイルは前記半導体基板の主表面に設けられ、

前記半導体基板の主表面において、前記第1のコイルおよび前記第2のコイルによって全周を取り囲まれた領域が形成され、

前記第3のコイルは、前記領域内に設けられ、

前記第4のコイルは、前記第1のコイルおよび第2のコイルを囲むように前記半導体基板の主表面に設けられている請求項4に記載の電力増幅器。

【請求項6】

前記電力増幅器は、さらに、

前記第1の入力信号および前記第2の入力信号を増幅する第2の増幅器と、

前記第2の増幅器によって増幅された前記第1の入力信号および前記第2の入力信号を受ける第5のコイルと、

前記第5のコイルと磁気的に結合され、かつ前記第2のコイルの一端と接続された第6のコイルと、

前記第6のコイルと磁気的に結合され、かつ前記第3のコイルの一端と接続された第7のコイルと、

前記第7のコイルの両端間に接続された第3のキャパシタとを備え、

前記第2のコイルおよび前記第6のコイルから、前記第1の増幅器によって増幅された前記第1の入力信号および前記第2の入力信号ならびに前記第2の増幅器によって増幅された前記第1の入力信号および前記第2の入力信号の合成信号が出力される請求項1に記載の電力増幅器。

【請求項7】

前記1次コイルは、前記増幅器によって増幅された前記第1の入力信号を受ける第1端と、前記第2の入力信号を受ける第2端とを有し、

前記2次コイルは、接地ノードに接続された第1端を有し、前記第1端を接地することにより、前記増幅された前記第1の入力信号および前記第2の入力信号の合成信号が出力される第2端とを有し、

前記3次コイルは、前記第1のキャパシタの第1端に接続された第1端と、前記第1のキャパシタの第2端および接地ノードに接続された第2端とを有する請求項1に記載の電力増幅器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2010−147574(P2010−147574A)

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願番号】特願2008−319833(P2008−319833)

【出願日】平成20年12月16日(2008.12.16)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願日】平成20年12月16日(2008.12.16)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]