電力変換器制御装置

【課題】 制御回路部から主回路部へ少ない数のケーブルを用いて、波形をずらすことなくゲート信号を正確に伝送し、電力変換器としての制御性能を劣化を防ぐ。

【解決手段】 実施形態に係る電力変換器制御装置は、複数の電力用半導体素子及び前記複数の電力用半導体素子を駆動するゲート駆動回路から構成される主回路部と、前記ゲート駆動回路に入力されるゲート信号を生成する制御回路部とを備えた電力変換器において、前記制御回路部は、ゲート信号の生成周期毎にゲート信号を符号化する手段と、前記制御回路部から前記主回路部へ、前記生成周期毎にクロック信号を伴わせずにゲート信号を符号伝送する手段とを具備し、前記ゲート駆動回路は、前記生成周期毎にゲート信号を復元し、復元されたゲート信号を前記複数の電力用半導体素子に供給する手段を具備する。

【解決手段】 実施形態に係る電力変換器制御装置は、複数の電力用半導体素子及び前記複数の電力用半導体素子を駆動するゲート駆動回路から構成される主回路部と、前記ゲート駆動回路に入力されるゲート信号を生成する制御回路部とを備えた電力変換器において、前記制御回路部は、ゲート信号の生成周期毎にゲート信号を符号化する手段と、前記制御回路部から前記主回路部へ、前記生成周期毎にクロック信号を伴わせずにゲート信号を符号伝送する手段とを具備し、前記ゲート駆動回路は、前記生成周期毎にゲート信号を復元し、復元されたゲート信号を前記複数の電力用半導体素子に供給する手段を具備する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はモータ等を駆動する電力変換器の制御装置に関する。

【背景技術】

【0002】

直流電力から交流電力へ、また逆に交流電力から直流電力への変換を行う電力変換器は、IGBT等の電力用半導体素子と、それを駆動するゲート駆動回路からなる主回路部と、電力変換器を目的に応じて動作させるために、ゲート駆動回路に与えるゲート信号を生成する制御回路部とを備えている。主回路部と制御回路部の間は、ゲート信号を伝送するための信号ケーブルが電力用半導体素子数分だけ必要となる。例えば、一般的な三相フルブリッジ回路の電力変換器の場合に電力用半導体素子数は6個となり、6本の信号ケーブルが必要である。電力変換器の出力電圧を高められる方式として中性点クランプ方式の3レベル主回路構成があるが、この場合には12本の信号ケーブルが必要となる。

【0003】

図11に三相フルブリッジ回路の電力変換器の一例を示す。1は電圧型インバータの三相フルブリッジ回路である。3相フルブリッジ回路1の直流側端子には整流器、電池等の直流電圧源2が接続され、交流側端子にはモータ等の3相負荷3が接続される。3相フルブリッジ回路を構成する6個の電力用半導体素子の各ゲート端子にはゲート駆動回路4が出力する6個のゲート駆動信号のうちの対応する1個が入力される。制御回路部5がPWM制御等の結果として出力する6個のゲート信号はそれぞれ専用の信号ケーブル6A〜6Fを通してゲート駆動回路4に入力され、論理回路レベルから、電力用半導体素子を駆動できる電気回路レベルに増幅され、それぞれ対応するゲート駆動信号として出力される。

【0004】

電力変換器の主回路部と制御回路部は、一般的に距離を置いて配置されるため、ゲート信号を伝送するための信号ケーブルの全長が長くなる場合がある。また、主回路部と制御回路部の電気的な絶縁を保つ目的で、信号ケーブルには高価な光ファイバーケーブルが用いられる場合もある。結果として、全長の長い光ファイバーケーブルが電力用半導体素子数分だけ必要となり、電力変換器の価格を押し上げることにつながる。

【0005】

この課題に対して、ゲート信号を符号化して送信するとともに、電力用半導体素子をそれぞれターンオンさせる全てのタイミングを合成したタイミング信号を送信し、受信側でゲート信号を再生する方式がある。また、ゲート信号を任意のタイミング信号に従って符号化するとともに、クロック信号を重畳して1本の信号ケーブルで送信する方式がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特許第3286161号公報

【特許文献2】特開平11−178349号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上記した従来方式のうち前者の方式では、ゲート信号の伝送に必要な信号ケーブルの本数を電力半導体素子数よりは減少できるが、符号化信号とタイミング信号用の合計2本の信号ケーブルが必要となる。また、後者の方式では、1本の信号ケーブルでゲート信号を伝送することは可能であるが、ゲート信号生成回路により、ゲート信号が、タイミング信号に従ってサンプリングした信号から生成されるため、ゲート信号の原波形に対して、伝送されるゲート信号の波形が一致しない可能性が生じる。インバータに出力されるゲート信号の原波形との不一致は、電力変換器としての制御性能を劣化させる場合がある。

【0008】

本発明は上記を考慮してなされたもので、制御回路部から主回路部へ少ない数のケーブルを用いて、波形(変化タイミング)をずらすことなくゲート信号を正確に伝送することで、電力変換器としての制御性能を劣化を防ぐことが可能な電力変換器の制御装置を実現することを目的とする。

【課題を解決するための手段】

【0009】

実施形態に係る電力変換器制御装置は、複数の電力用半導体素子及び前記複数の電力用半導体素子を駆動するゲート駆動回路から構成される主回路部と、前記ゲート駆動回路に入力されるゲート信号を生成する制御回路部とを備えた電力変換器において、前記制御回路部は、ゲート信号の生成周期毎にゲート信号を符号化する手段と、前記制御回路部から前記主回路部へ、前記生成周期毎にクロック信号を伴わせずにゲート信号を符号伝送する手段とを具備し、前記ゲート駆動回路は、前記生成周期毎にゲート信号を復元し、復元されたゲート信号を前記複数の電力用半導体素子に供給する手段を具備する。

【発明の効果】

【0010】

本発明によれば、制御回路部から主回路部へ少ない数のケーブルを用いて、波形(変化タイミング)をずらすことなくゲート信号を正確に伝送し、電力変換器としての制御性能の劣化を防ぐことが可能となる。

【図面の簡単な説明】

【0011】

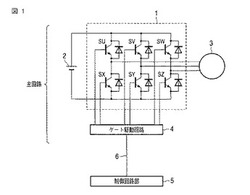

【図1】本発明による電力変換器制御装置の第1実施形態の構成を示す図である。

【図2】図1の制御回路部の構成を示す図である。

【図3】ゲート信号の生成を説明するためのタイミングチャートである。

【図4】符号化データのフォーマットの一例を示す。

【図5】ゲート駆動回路4の機能ブロック図を示す図である。

【図6】ゲート信号伝送のタイミングチャートを示すタイミングチャートである。

【図7】本発明の第2実施形態に係る電力変換器制御装置の構成を示す説明図。

【図8】本発明の第3実施形態に係る電力変換器制御装置の構成を示す図である。

【図9】本発明の第4実施形態に係る電力変換器制御装置の構成を示す図である。

【図10】本発明の第5実施形態に係る電力変換器制御装置の構成を示す図である。

【図11】従来の電力変換器の構成を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明に係る電力変換器制御装置の実施の形態について、図面を参照して説明する。尚、同一の構成要素には同一の符号を付してその説明を省略する。

【実施例1】

【0013】

図1は、本発明による電力変換器制御装置の第1実施形態の構成を示すブロック図である。

【0014】

図1において、インバータ1とゲート駆動回路4は主回路を構成する。制御回路部5がPWM制御等の結果として出力するゲート信号はその出力段で符号化される。符号化されたゲート信号は信号ケーブル6を通して伝送される。この他にケーブル6は、金属の信号線とアースラインのツイストペア、あるいは差動信号のツイストペアでも良い。ここでは、ケーブル6として単一の光ファイバケーブルが使用されるものとする。単一の信号ケーブル6を通して伝送されたゲート信号は、主回路のゲート駆動回路4に入力される。

【0015】

ゲート駆動回路4はその入力段において、符号化されたゲート信号から6個の並列なゲート信号を復元する。復元された6個のゲート信号は論理回路レベル(例えば0V/5V)から、電力用半導体素子を駆動できる電気回路レベル(例えば±15V)に増幅され、それぞれ対応する電力用半導体素子のゲート駆動信号としてインバータ1に出力される。

【0016】

図2は制御回路部5の機能ブロック図を示したものである。

【0017】

ゲート信号生成回路8はある一定の周期毎にゲート信号SU、SX、SV、SY、SW、SZを同時に生成する。ゲート信号の生成は例えば三角波キャリア比較PWM制御方式等によって行われる。

【0018】

図3はゲート信号の生成を説明するためのタイミングチャートである。

【0019】

ゲート信号生成回路8は図3(a)のように、三角波キャリアとUVW相正弦変調波とを比較し、図3(b)のようにゲート信号を生成する。本実施形態では、三角波キャリアとUVW相正弦変調波とを比較を、三角波キャリア1周期で数百回(例えば200回)行う。各比較において三角波キャリアとUVW相正弦変調波の比較を例えば同時に行い、1組のゲート信号(SU、SV、SW、SX、SY、SZ)が生成される。つまり三角波キャリア1周期で数百組のゲート信号が生成される。ここでは、比較の周期つまり1組のゲート信号(SU、SV、SW、SX、SY、SZ)が生成される周期をゲート生成周期という。このゲート生成周期が短い(生成レートが高い)ほど正確なオン/オフタイミングを示すゲート信号が伝送される。

【0020】

尚、ゲート信号の生成は三角波キャリア比較PWM制御方式に限らず、ある一定周期毎に1組のゲート信号SU、SX、SV、SY、SW、SZを生成するものであればその手法は限定しない。

【0021】

生成されたゲート信号は、符号化回路9によってゲート生成周期毎に符号化ゲート信号にP/S(パラレル/シリアル)変換される。ゲート信号は対応する電力用半導体素子のオンかオフの状態を決めるものであり、それぞれオン状態が1、オフ状態が0の2値として表すことが可能である。したがって、ある周期における1組のゲート信号の状態が以下の場合、

SU=1、SX=0、SV=1、SY=0、SW=0、SZ=1

符号化ゲート信号として、以下の2進数に変換することができる。

【0022】

「101001」

上記は、2値ゲート信号をSU、SX、SV、SY、SW、SZの順番に並べて6ビットで符号化した一例であるが、誤り訂正符号等を付加することも可能である。図4は他の符号化データのフォーマット例を示す。この例ではスタートビットSTとストップビットSPの間にゲート信号U、X、V、Y、W、Z及びパリティビットPが配列されている。

【0023】

符号化の方式は、ゲート生成周期毎に符号化ゲート信号を生成するものであればその手法は限定されない。生成された符号化ゲート信号は、符号伝送送信回路10によってあるゲート生成周期毎に符号伝送信号に変換され、信号ケーブル6を通してゲート駆動回路4に送信される。符号伝送の方式は、非同期伝送、同期伝送等があげられるが、ゲート生成周期毎に符号化ゲート信号を符号伝送信号に変換するものであれば、その手法は限定されない。

【0024】

符号伝送送信回路10は例えばレーザ発振器を含み、符号化回路9からシリアル伝送される符号化ゲート信号に対応するレーザ光を発生し、符号伝送信号として光ファイバケーブル6に送出する。以上より、制御回路部5はある一定周期毎にゲート信号を生成し、符号伝送信号としてゲート駆動回路4に送信することが可能となる。

【0025】

図5はゲート駆動回路4の機能ブロック図を示したものである。

【0026】

信号ケーブル6を通してゲート生成周期毎に制御回路部5から送信される符号化伝送信号は、符号伝送受信回路11に受信される。符号伝送受信回路11は例えばフォトダイオードのような受光素子を含み、符号伝送信号を光電変換する。符号伝送受信回路11はまた、送信側に対応する符号伝送方式に従って、ゲート生成周期毎に符号化ゲート信号を生成する。このとき符号伝送受信回路11は、図4のような形式で伝送されたゲート信号の1フレームを例えば数百回サンプリングして、伝送されたデータを読み取る。例えば同一の情報(0か1の情報)が所定回数連続した場合、当該情報を真の情報として決定する。

【0027】

符号化ゲート信号はゲート信号復元回路12によってS/P(シリアル/パラレル)変換され、制御回路部5の符号化方式に対応してゲート生成周期毎にゲート信号SU、SX、SV、SY、SW、SZに復元される。復元されたゲート信号SU、SX、SV、SY、SW、SZは、ゲート駆動信号増幅回路13によってゲート駆動信号に増幅され、対応する電力用半導体素子を駆動する。

【0028】

図6にゲート信号伝送のタイミングチャートを示す。

【0029】

図6(a)は制御回路部5のゲート信号生成回路8により生成されるパラレルゲート信号、図6(b)は符号化回路9により符号化されたシリアル符号化ゲート信号を示す。図6(c)は符号化回路9からゲート駆動回路4にシリアル伝送される信号を示す。図6(d)はゲート信号復元回路12により復元されたパラレルゲート信号、図6(e)はゲート駆動信号増幅回路13から出力されるゲート駆動信号を示し、Tはゲート生成周期に対応する。

【0030】

図6より、ゲート生成周期T毎にゲート駆動信号が更新されることがわかる。ゲート信号の生成から、ゲート駆動信号の更新まで、最短でもゲート生成周期Tだけの遅れ時間が生じるが、ゲート生成周期Tを適切に設計することにより、電力変換器の性能には影響を与えない。

【0031】

以上の実施の形態によれば、制御回路部がある一定周期毎に生成するゲート信号を、クロック信号を伴わせずに、つまり同時にクロック信号を伝送することなく、そのまま主回路部に伝送することが可能となる。結果として、電力変換器としての制御性能を劣化させることなく、制御回路部から主回路部へ単一の信号ケーブルでゲート信号を伝送することが可能となる電力変換器の制御装置を実現できる。

【実施例2】

【0032】

図7は本発明の第2実施形態に係る電力変換器の制御装置の構成を示す図である。

【0033】

図7において、1U、1V、1Wはそれぞれ3相フルブリッジ回路がU相、V相、W相に分割されたものである。同様に4U、4V、4Wはそれぞれゲート駆動回路がU相、V相、W相に分割されたものである。制御回路部5からは、U相、V相、W相毎にそれぞれ単一の信号ケーブル6U、6V、6Wを通してゲート信号が伝送される。この例では、各相のゲート信号(2信号)が図6のように変換及び伝送される。

【0034】

本実施の形態によれば、大型の電力変換器の場合に見られるような、主回路部(インバータ及びゲート駆動回路)が各相毎に分割配置された場合でも、電力変換器としての制御性能を劣化させることなく、各相毎に単一の信号ケーブルでゲート信号を伝送することが可能となる電力変換器の制御装置を実現できる。

【実施例3】

【0035】

図8は本発明の第3実施形態に係る電力変換器の制御装置の構成を示す図である。図8において、7A、7B、7Cはそれぞれ単位主回路部を表す。制御回路部5からは、単位主回路部毎にそれぞれ単一の信号ケーブル6A、6B、6Cを通してゲート信号が伝送される。本実施形態によれば、複数台の電力変換器を単一の制御回路部で制御する場合でも、電力変換器の制御性能を劣化させることなく、各単位主回路部毎に単一の信号ケーブルでゲート信号を伝送することが可能となる電力変換器の制御装置を実現できる。

【実施例4】

【0036】

図9は本発明の第4実施形態に係る電力変換器の制御装置の構成を示す図である。

【0037】

図9において、制御回路部5からは、第1の単位主回路部7Aに単一の信号ケーブル6Aを通してゲート信号が伝送される。第1の単位主回路部7Aには、制御回路部5から伝送されたゲート信号をそのまま符号伝送する機能があり、第2の単位主回路部7Bに単一の信号ケーブル6Bを通してゲート信号が伝送される。同様に第2の単位主回路部7Bには、第1の単位主回路部7Aから伝送されたゲート信号をそのまま符号伝送する機能があり、第3の単位主回路部7Cに単一の信号ケーブル6Cを通してゲート信号が伝送される。本例では、第1〜第3の単位主回路部7A〜7Cは、それぞれ図6(d)、5(f)のようにゲート信号を復元しインバータを制御する。

【0038】

本実施形態によれば、複数台の電力変換器を単一の制御回路部で制御する場合でも、電力変換器としての制御性能を劣化させることなく、各単位主回路部毎に単一の信号ケーブルでゲート信号を伝送することが可能となる電力変換器の制御装置を実現できる。

【実施例5】

【0039】

図10は本発明の第5実施形態に係る電力変換器の制御装置の一例を示す図である。

【0040】

図10において、制御回路部5から符号化されたシリアルゲート信号が出力され、無線送信器14により無線送信される。無線送信されたゲート信号は、無線受信器15により無線受信され、ゲート信号としてゲート駆動回路4に入力される。

【0041】

本実施の形態によれば、信号ケーブルを用いることなく無線通信により、ゲート信号を伝送することが可能な電力変換器の制御装置を実現できる。

【0042】

以上の説明はこの発明の実施の形態であって、この発明の装置及び方法を限定するものではなく、様々な変形例を容易に実施することができるものである。例えば、上記実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を構成できる。

【符号の説明】

【0043】

1U、1V、1W…3相フルブリッジ回路、2…直流電圧源、3…3相負荷、4…ゲート駆動回路、5…制御回路部、6、6A、6B、6C、6D、6E、6F、6U、6V、6W…信号ケーブル、7A、7B、7C…単位主回路部、8…ゲート信号生成回路、9…符号化回路、10…符号伝送送信回路、11…符号伝送受信回路、12…ゲート信号復元回路、13…ゲート駆動信号増幅回路、14…無線送信器、15…無線受信器。

【技術分野】

【0001】

本発明はモータ等を駆動する電力変換器の制御装置に関する。

【背景技術】

【0002】

直流電力から交流電力へ、また逆に交流電力から直流電力への変換を行う電力変換器は、IGBT等の電力用半導体素子と、それを駆動するゲート駆動回路からなる主回路部と、電力変換器を目的に応じて動作させるために、ゲート駆動回路に与えるゲート信号を生成する制御回路部とを備えている。主回路部と制御回路部の間は、ゲート信号を伝送するための信号ケーブルが電力用半導体素子数分だけ必要となる。例えば、一般的な三相フルブリッジ回路の電力変換器の場合に電力用半導体素子数は6個となり、6本の信号ケーブルが必要である。電力変換器の出力電圧を高められる方式として中性点クランプ方式の3レベル主回路構成があるが、この場合には12本の信号ケーブルが必要となる。

【0003】

図11に三相フルブリッジ回路の電力変換器の一例を示す。1は電圧型インバータの三相フルブリッジ回路である。3相フルブリッジ回路1の直流側端子には整流器、電池等の直流電圧源2が接続され、交流側端子にはモータ等の3相負荷3が接続される。3相フルブリッジ回路を構成する6個の電力用半導体素子の各ゲート端子にはゲート駆動回路4が出力する6個のゲート駆動信号のうちの対応する1個が入力される。制御回路部5がPWM制御等の結果として出力する6個のゲート信号はそれぞれ専用の信号ケーブル6A〜6Fを通してゲート駆動回路4に入力され、論理回路レベルから、電力用半導体素子を駆動できる電気回路レベルに増幅され、それぞれ対応するゲート駆動信号として出力される。

【0004】

電力変換器の主回路部と制御回路部は、一般的に距離を置いて配置されるため、ゲート信号を伝送するための信号ケーブルの全長が長くなる場合がある。また、主回路部と制御回路部の電気的な絶縁を保つ目的で、信号ケーブルには高価な光ファイバーケーブルが用いられる場合もある。結果として、全長の長い光ファイバーケーブルが電力用半導体素子数分だけ必要となり、電力変換器の価格を押し上げることにつながる。

【0005】

この課題に対して、ゲート信号を符号化して送信するとともに、電力用半導体素子をそれぞれターンオンさせる全てのタイミングを合成したタイミング信号を送信し、受信側でゲート信号を再生する方式がある。また、ゲート信号を任意のタイミング信号に従って符号化するとともに、クロック信号を重畳して1本の信号ケーブルで送信する方式がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特許第3286161号公報

【特許文献2】特開平11−178349号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上記した従来方式のうち前者の方式では、ゲート信号の伝送に必要な信号ケーブルの本数を電力半導体素子数よりは減少できるが、符号化信号とタイミング信号用の合計2本の信号ケーブルが必要となる。また、後者の方式では、1本の信号ケーブルでゲート信号を伝送することは可能であるが、ゲート信号生成回路により、ゲート信号が、タイミング信号に従ってサンプリングした信号から生成されるため、ゲート信号の原波形に対して、伝送されるゲート信号の波形が一致しない可能性が生じる。インバータに出力されるゲート信号の原波形との不一致は、電力変換器としての制御性能を劣化させる場合がある。

【0008】

本発明は上記を考慮してなされたもので、制御回路部から主回路部へ少ない数のケーブルを用いて、波形(変化タイミング)をずらすことなくゲート信号を正確に伝送することで、電力変換器としての制御性能を劣化を防ぐことが可能な電力変換器の制御装置を実現することを目的とする。

【課題を解決するための手段】

【0009】

実施形態に係る電力変換器制御装置は、複数の電力用半導体素子及び前記複数の電力用半導体素子を駆動するゲート駆動回路から構成される主回路部と、前記ゲート駆動回路に入力されるゲート信号を生成する制御回路部とを備えた電力変換器において、前記制御回路部は、ゲート信号の生成周期毎にゲート信号を符号化する手段と、前記制御回路部から前記主回路部へ、前記生成周期毎にクロック信号を伴わせずにゲート信号を符号伝送する手段とを具備し、前記ゲート駆動回路は、前記生成周期毎にゲート信号を復元し、復元されたゲート信号を前記複数の電力用半導体素子に供給する手段を具備する。

【発明の効果】

【0010】

本発明によれば、制御回路部から主回路部へ少ない数のケーブルを用いて、波形(変化タイミング)をずらすことなくゲート信号を正確に伝送し、電力変換器としての制御性能の劣化を防ぐことが可能となる。

【図面の簡単な説明】

【0011】

【図1】本発明による電力変換器制御装置の第1実施形態の構成を示す図である。

【図2】図1の制御回路部の構成を示す図である。

【図3】ゲート信号の生成を説明するためのタイミングチャートである。

【図4】符号化データのフォーマットの一例を示す。

【図5】ゲート駆動回路4の機能ブロック図を示す図である。

【図6】ゲート信号伝送のタイミングチャートを示すタイミングチャートである。

【図7】本発明の第2実施形態に係る電力変換器制御装置の構成を示す説明図。

【図8】本発明の第3実施形態に係る電力変換器制御装置の構成を示す図である。

【図9】本発明の第4実施形態に係る電力変換器制御装置の構成を示す図である。

【図10】本発明の第5実施形態に係る電力変換器制御装置の構成を示す図である。

【図11】従来の電力変換器の構成を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明に係る電力変換器制御装置の実施の形態について、図面を参照して説明する。尚、同一の構成要素には同一の符号を付してその説明を省略する。

【実施例1】

【0013】

図1は、本発明による電力変換器制御装置の第1実施形態の構成を示すブロック図である。

【0014】

図1において、インバータ1とゲート駆動回路4は主回路を構成する。制御回路部5がPWM制御等の結果として出力するゲート信号はその出力段で符号化される。符号化されたゲート信号は信号ケーブル6を通して伝送される。この他にケーブル6は、金属の信号線とアースラインのツイストペア、あるいは差動信号のツイストペアでも良い。ここでは、ケーブル6として単一の光ファイバケーブルが使用されるものとする。単一の信号ケーブル6を通して伝送されたゲート信号は、主回路のゲート駆動回路4に入力される。

【0015】

ゲート駆動回路4はその入力段において、符号化されたゲート信号から6個の並列なゲート信号を復元する。復元された6個のゲート信号は論理回路レベル(例えば0V/5V)から、電力用半導体素子を駆動できる電気回路レベル(例えば±15V)に増幅され、それぞれ対応する電力用半導体素子のゲート駆動信号としてインバータ1に出力される。

【0016】

図2は制御回路部5の機能ブロック図を示したものである。

【0017】

ゲート信号生成回路8はある一定の周期毎にゲート信号SU、SX、SV、SY、SW、SZを同時に生成する。ゲート信号の生成は例えば三角波キャリア比較PWM制御方式等によって行われる。

【0018】

図3はゲート信号の生成を説明するためのタイミングチャートである。

【0019】

ゲート信号生成回路8は図3(a)のように、三角波キャリアとUVW相正弦変調波とを比較し、図3(b)のようにゲート信号を生成する。本実施形態では、三角波キャリアとUVW相正弦変調波とを比較を、三角波キャリア1周期で数百回(例えば200回)行う。各比較において三角波キャリアとUVW相正弦変調波の比較を例えば同時に行い、1組のゲート信号(SU、SV、SW、SX、SY、SZ)が生成される。つまり三角波キャリア1周期で数百組のゲート信号が生成される。ここでは、比較の周期つまり1組のゲート信号(SU、SV、SW、SX、SY、SZ)が生成される周期をゲート生成周期という。このゲート生成周期が短い(生成レートが高い)ほど正確なオン/オフタイミングを示すゲート信号が伝送される。

【0020】

尚、ゲート信号の生成は三角波キャリア比較PWM制御方式に限らず、ある一定周期毎に1組のゲート信号SU、SX、SV、SY、SW、SZを生成するものであればその手法は限定しない。

【0021】

生成されたゲート信号は、符号化回路9によってゲート生成周期毎に符号化ゲート信号にP/S(パラレル/シリアル)変換される。ゲート信号は対応する電力用半導体素子のオンかオフの状態を決めるものであり、それぞれオン状態が1、オフ状態が0の2値として表すことが可能である。したがって、ある周期における1組のゲート信号の状態が以下の場合、

SU=1、SX=0、SV=1、SY=0、SW=0、SZ=1

符号化ゲート信号として、以下の2進数に変換することができる。

【0022】

「101001」

上記は、2値ゲート信号をSU、SX、SV、SY、SW、SZの順番に並べて6ビットで符号化した一例であるが、誤り訂正符号等を付加することも可能である。図4は他の符号化データのフォーマット例を示す。この例ではスタートビットSTとストップビットSPの間にゲート信号U、X、V、Y、W、Z及びパリティビットPが配列されている。

【0023】

符号化の方式は、ゲート生成周期毎に符号化ゲート信号を生成するものであればその手法は限定されない。生成された符号化ゲート信号は、符号伝送送信回路10によってあるゲート生成周期毎に符号伝送信号に変換され、信号ケーブル6を通してゲート駆動回路4に送信される。符号伝送の方式は、非同期伝送、同期伝送等があげられるが、ゲート生成周期毎に符号化ゲート信号を符号伝送信号に変換するものであれば、その手法は限定されない。

【0024】

符号伝送送信回路10は例えばレーザ発振器を含み、符号化回路9からシリアル伝送される符号化ゲート信号に対応するレーザ光を発生し、符号伝送信号として光ファイバケーブル6に送出する。以上より、制御回路部5はある一定周期毎にゲート信号を生成し、符号伝送信号としてゲート駆動回路4に送信することが可能となる。

【0025】

図5はゲート駆動回路4の機能ブロック図を示したものである。

【0026】

信号ケーブル6を通してゲート生成周期毎に制御回路部5から送信される符号化伝送信号は、符号伝送受信回路11に受信される。符号伝送受信回路11は例えばフォトダイオードのような受光素子を含み、符号伝送信号を光電変換する。符号伝送受信回路11はまた、送信側に対応する符号伝送方式に従って、ゲート生成周期毎に符号化ゲート信号を生成する。このとき符号伝送受信回路11は、図4のような形式で伝送されたゲート信号の1フレームを例えば数百回サンプリングして、伝送されたデータを読み取る。例えば同一の情報(0か1の情報)が所定回数連続した場合、当該情報を真の情報として決定する。

【0027】

符号化ゲート信号はゲート信号復元回路12によってS/P(シリアル/パラレル)変換され、制御回路部5の符号化方式に対応してゲート生成周期毎にゲート信号SU、SX、SV、SY、SW、SZに復元される。復元されたゲート信号SU、SX、SV、SY、SW、SZは、ゲート駆動信号増幅回路13によってゲート駆動信号に増幅され、対応する電力用半導体素子を駆動する。

【0028】

図6にゲート信号伝送のタイミングチャートを示す。

【0029】

図6(a)は制御回路部5のゲート信号生成回路8により生成されるパラレルゲート信号、図6(b)は符号化回路9により符号化されたシリアル符号化ゲート信号を示す。図6(c)は符号化回路9からゲート駆動回路4にシリアル伝送される信号を示す。図6(d)はゲート信号復元回路12により復元されたパラレルゲート信号、図6(e)はゲート駆動信号増幅回路13から出力されるゲート駆動信号を示し、Tはゲート生成周期に対応する。

【0030】

図6より、ゲート生成周期T毎にゲート駆動信号が更新されることがわかる。ゲート信号の生成から、ゲート駆動信号の更新まで、最短でもゲート生成周期Tだけの遅れ時間が生じるが、ゲート生成周期Tを適切に設計することにより、電力変換器の性能には影響を与えない。

【0031】

以上の実施の形態によれば、制御回路部がある一定周期毎に生成するゲート信号を、クロック信号を伴わせずに、つまり同時にクロック信号を伝送することなく、そのまま主回路部に伝送することが可能となる。結果として、電力変換器としての制御性能を劣化させることなく、制御回路部から主回路部へ単一の信号ケーブルでゲート信号を伝送することが可能となる電力変換器の制御装置を実現できる。

【実施例2】

【0032】

図7は本発明の第2実施形態に係る電力変換器の制御装置の構成を示す図である。

【0033】

図7において、1U、1V、1Wはそれぞれ3相フルブリッジ回路がU相、V相、W相に分割されたものである。同様に4U、4V、4Wはそれぞれゲート駆動回路がU相、V相、W相に分割されたものである。制御回路部5からは、U相、V相、W相毎にそれぞれ単一の信号ケーブル6U、6V、6Wを通してゲート信号が伝送される。この例では、各相のゲート信号(2信号)が図6のように変換及び伝送される。

【0034】

本実施の形態によれば、大型の電力変換器の場合に見られるような、主回路部(インバータ及びゲート駆動回路)が各相毎に分割配置された場合でも、電力変換器としての制御性能を劣化させることなく、各相毎に単一の信号ケーブルでゲート信号を伝送することが可能となる電力変換器の制御装置を実現できる。

【実施例3】

【0035】

図8は本発明の第3実施形態に係る電力変換器の制御装置の構成を示す図である。図8において、7A、7B、7Cはそれぞれ単位主回路部を表す。制御回路部5からは、単位主回路部毎にそれぞれ単一の信号ケーブル6A、6B、6Cを通してゲート信号が伝送される。本実施形態によれば、複数台の電力変換器を単一の制御回路部で制御する場合でも、電力変換器の制御性能を劣化させることなく、各単位主回路部毎に単一の信号ケーブルでゲート信号を伝送することが可能となる電力変換器の制御装置を実現できる。

【実施例4】

【0036】

図9は本発明の第4実施形態に係る電力変換器の制御装置の構成を示す図である。

【0037】

図9において、制御回路部5からは、第1の単位主回路部7Aに単一の信号ケーブル6Aを通してゲート信号が伝送される。第1の単位主回路部7Aには、制御回路部5から伝送されたゲート信号をそのまま符号伝送する機能があり、第2の単位主回路部7Bに単一の信号ケーブル6Bを通してゲート信号が伝送される。同様に第2の単位主回路部7Bには、第1の単位主回路部7Aから伝送されたゲート信号をそのまま符号伝送する機能があり、第3の単位主回路部7Cに単一の信号ケーブル6Cを通してゲート信号が伝送される。本例では、第1〜第3の単位主回路部7A〜7Cは、それぞれ図6(d)、5(f)のようにゲート信号を復元しインバータを制御する。

【0038】

本実施形態によれば、複数台の電力変換器を単一の制御回路部で制御する場合でも、電力変換器としての制御性能を劣化させることなく、各単位主回路部毎に単一の信号ケーブルでゲート信号を伝送することが可能となる電力変換器の制御装置を実現できる。

【実施例5】

【0039】

図10は本発明の第5実施形態に係る電力変換器の制御装置の一例を示す図である。

【0040】

図10において、制御回路部5から符号化されたシリアルゲート信号が出力され、無線送信器14により無線送信される。無線送信されたゲート信号は、無線受信器15により無線受信され、ゲート信号としてゲート駆動回路4に入力される。

【0041】

本実施の形態によれば、信号ケーブルを用いることなく無線通信により、ゲート信号を伝送することが可能な電力変換器の制御装置を実現できる。

【0042】

以上の説明はこの発明の実施の形態であって、この発明の装置及び方法を限定するものではなく、様々な変形例を容易に実施することができるものである。例えば、上記実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を構成できる。

【符号の説明】

【0043】

1U、1V、1W…3相フルブリッジ回路、2…直流電圧源、3…3相負荷、4…ゲート駆動回路、5…制御回路部、6、6A、6B、6C、6D、6E、6F、6U、6V、6W…信号ケーブル、7A、7B、7C…単位主回路部、8…ゲート信号生成回路、9…符号化回路、10…符号伝送送信回路、11…符号伝送受信回路、12…ゲート信号復元回路、13…ゲート駆動信号増幅回路、14…無線送信器、15…無線受信器。

【特許請求の範囲】

【請求項1】

複数の電力用半導体素子及び前記複数の電力用半導体素子を駆動するゲート駆動回路から構成される主回路部と、前記ゲート駆動回路に入力されるゲート信号を生成する制御回路部とを備えた電力変換器において、

前記制御回路部は、

ゲート信号の生成周期毎にゲート信号を符号化する手段と、

前記制御回路部から前記主回路部へ、前記生成周期毎にクロック信号を伴わせずにゲート信号を符号伝送する手段とを具備し、

前記ゲート駆動回路は、

前記生成周期毎にゲート信号を復元し、復元されたゲート信号を前記複数の電力用半導体素子に供給する手段を具備することを特徴とする電力変換器制御装置。

【請求項2】

電力変換器の交流側の各相毎に分割されて主回路部が構成され、単一の制御回路部から交流側各相の主回路部に単一の信号ケーブルを用いてゲート信号を伝送することを特徴とする請求項1記載の電力変換器制御装置。

【請求項3】

主回路部が複数の単位主回路部から構成され、単一の制御回路部から各単位主回路部に単一の信号ケーブルを用いてゲート信号を伝送することを特徴とする請求項1記載の電力変換器制御装置。

【請求項4】

単一の制御回路部から第1の単位主回路部に単一の信号ケーブルを用いてゲート信号を伝送し、前記第1の単位主回路部から第2の単位主回路部に単一の信号ケーブルを用いてゲート信号を伝送し、以下順次単位主回路部間を単一の信号ケーブルを用いてゲート信号を伝送することを特徴とする請求項3記載の電力変換器制御装置。

【請求項5】

前記制御回路部から符号化されたゲート信号を無線送信する無線送信器と、無線送信されたゲート信号を主回路部で受信する無線受信器とを備えることを特徴とする請求項1乃至4のうち1項記載の電力変換器制御装置。

【請求項1】

複数の電力用半導体素子及び前記複数の電力用半導体素子を駆動するゲート駆動回路から構成される主回路部と、前記ゲート駆動回路に入力されるゲート信号を生成する制御回路部とを備えた電力変換器において、

前記制御回路部は、

ゲート信号の生成周期毎にゲート信号を符号化する手段と、

前記制御回路部から前記主回路部へ、前記生成周期毎にクロック信号を伴わせずにゲート信号を符号伝送する手段とを具備し、

前記ゲート駆動回路は、

前記生成周期毎にゲート信号を復元し、復元されたゲート信号を前記複数の電力用半導体素子に供給する手段を具備することを特徴とする電力変換器制御装置。

【請求項2】

電力変換器の交流側の各相毎に分割されて主回路部が構成され、単一の制御回路部から交流側各相の主回路部に単一の信号ケーブルを用いてゲート信号を伝送することを特徴とする請求項1記載の電力変換器制御装置。

【請求項3】

主回路部が複数の単位主回路部から構成され、単一の制御回路部から各単位主回路部に単一の信号ケーブルを用いてゲート信号を伝送することを特徴とする請求項1記載の電力変換器制御装置。

【請求項4】

単一の制御回路部から第1の単位主回路部に単一の信号ケーブルを用いてゲート信号を伝送し、前記第1の単位主回路部から第2の単位主回路部に単一の信号ケーブルを用いてゲート信号を伝送し、以下順次単位主回路部間を単一の信号ケーブルを用いてゲート信号を伝送することを特徴とする請求項3記載の電力変換器制御装置。

【請求項5】

前記制御回路部から符号化されたゲート信号を無線送信する無線送信器と、無線送信されたゲート信号を主回路部で受信する無線受信器とを備えることを特徴とする請求項1乃至4のうち1項記載の電力変換器制御装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2012−60793(P2012−60793A)

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願番号】特願2010−202099(P2010−202099)

【出願日】平成22年9月9日(2010.9.9)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願日】平成22年9月9日(2010.9.9)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]