電力変換装置用の駆動回路および電力変換装置

【課題】上側のスイッチング素子の誤動作を抑制できる電力変換装置用の駆動回路を提供する。

【解決手段】第1回路10は、直流電源E1の低電位端と高電位端との間で相互に直列に接続される第1素子11及び第2素子12を有し、第1素子11は高電位端側に設けられ、第2素子12は低電位端側に設けられる。第1素子11及び第2素子12は、その両方がスイッチである。第2回路20は、第2素子12の両端の電圧が所定値よりも大きいときにスイッチング素子Tx1を非導通とし、当該電圧が所定値よりも小さいときにスイッチング素子Tx1を導通させる。スイッチ素子32は、第1素子11と並列に接続され、スイッチング素子Tx1が非導通である状態で導通し、スイッチング素子Tx1が導通する状態で非導通する。

【解決手段】第1回路10は、直流電源E1の低電位端と高電位端との間で相互に直列に接続される第1素子11及び第2素子12を有し、第1素子11は高電位端側に設けられ、第2素子12は低電位端側に設けられる。第1素子11及び第2素子12は、その両方がスイッチである。第2回路20は、第2素子12の両端の電圧が所定値よりも大きいときにスイッチング素子Tx1を非導通とし、当該電圧が所定値よりも小さいときにスイッチング素子Tx1を導通させる。スイッチ素子32は、第1素子11と並列に接続され、スイッチング素子Tx1が非導通である状態で導通し、スイッチング素子Tx1が導通する状態で非導通する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電力変換装置用の駆動回路および電力変換装置に関し、特に電力変換装置に属する上側のスイッチング素子の誤動作を抑制する技術に関する。

【背景技術】

【0002】

特許文献1には三相インバータが記載されている。三相インバータは、正極側および負極側のスイッチング素子を有するアームを三相分備えている。各相のアームは互いに並列に接続される。正極側及び負極側のスイッチング素子にはそれぞれドライブ回路が接続される。正極側のスイッチング素子についてのドライブ回路は、正極側のスイッチング素子のゲート電極とエミッタ電極との間に設けられる。ドライブ回路は、ゲート電極とエミッタ電極との間の電圧を制御して、正極側のスイッチング素子を制御する。またドライブ回路には入力絶縁回路が含まれる。

【0003】

かかるドライブ回路は、当該電圧を印加するための動作電源となる第1及び第2のコンデンサを有している。第1及び第2のコンデンサは互いに直列に接続され、これらの間の点が上記エミッタ電極に接続される。第1及び第2のコンデンサは互いに反対側でそれぞれ第1及び第2のスイッチ素子を介してゲート電極に接続される。かかる構造において、第1のスイッチ素子が導通すれば、第1のコンデンサがゲート電極に接続されて、正極側のスイッチング素子が導通する。一方、第2のスイッチング素子が導通すれば、第2のコンデンサがゲート電極に接続されて、正極側のスイッチング素子が非導通となる。

【0004】

さらに、特許文献1では、第1及び第2のコンデンサの間の点と、上記エミッタ電極との間に抵抗を設けている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特許第3292662号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1では、第1及び第2のコンデンサの間の点と、上記エミッタ電極との間にはノイズ除去用抵抗が設けられている。よって、入力絶縁回路の入出力間容量を介したdv/dtノイズを低減できる。しかし、当該抵抗はゲート電極とエミッタ電極との間に設けられるので、抵抗に生じる電圧がゲート電極とエミッタ電極との間の電圧に影響を与える。したがって、抵抗に生じる電圧が大きければ、正極側のスイッチング素子が誤動作する可能性がある。

【0007】

なお、以下では正極側のスイッチング素子を上側のスイッチング素子と呼び、負極側のスイッチング素子を下側のスイッチング素子と呼ぶ。

【0008】

本発明は、上側のスイッチング素子の誤動作を抑制できる電力変換装置用の駆動回路を提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明にかかる電力変換装置用の駆動回路の第1の態様は、第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、出力端(Pu,Pv,Pw,Px)を介して互いに直列に接続される上側のスイッチング素子(Tu1,Tv1,Tw1,Tx1)及び下側のスイッチング素子(Tu2,Tv2,Tw2,Tx2)を有し、前記上側のスイッチング素子が前記第1の電源線側に配置される電力変換装置の、前記上側のスイッチング素子の駆動回路(DVu1,DVv1,DVw1,DVx1)であって、前記出力端に接続される低電位端と、高電位端とを有する直流電源(E1)と、前記低電位端と前記高電位端との間で相互に直列に接続される第1素子(11,15)及び第2素子(12,16)を有し、前記第1素子は前記高電位端側に設けられ、前記第2素子は前記低電位端側に設けられる第1回路(10)と、前記第2素子の両端の電圧(V1)が所定値よりも大きいときに前記上側のスイッチング素子を非導通とし、前記電圧が前記所定値よりも小さいときに前記上側のスイッチング素子を導通させる第2回路(20)と、前記第1素子と並列に接続され、前記上側のスイッチング素子が非導通である状態で導通し、前記上側のスイッチング素子が導通する状態で非導通するスイッチ素子(32)とを備え、前記第1素子及び第2素子は、その両方がスイッチ(11,12)であるか、又は一方がスイッチであって他方が抵抗素子(15,16)である。

【0010】

本発明にかかる電力変換装置用の駆動回路の第2の態様は、第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、出力端(Pu,Pv,Pw,Px)を介して互いに直列に接続される上側のスイッチング素子(Tu1,Tv1,Tw1,Tx1)及び下側のスイッチング素子(Tu2,Tv2,Tw2,Tx2)を有し、前記上側のスイッチング素子が前記第1の電源線側に配置される電力変換装置の、前記上側のスイッチング素子の駆動回路(DVu1,DVv1,DVw1,DVx1)であって、前記出力端に接続される低電位端と、高電位端とを有する直流電源(E1)と、前記低電位端と前記高電位端との間で相互に直列に接続される第1素子(11,15)及び第2素子(12,16)を有し、前記第1素子は前記高電位端側に設けられ、前記第2素子は前記低電位端側に設けられる第1回路(10)と、前記第2素子の両端の電圧(V1)が所定値よりも小さいときに前記上側のスイッチング素子を非導通とし、前記電圧が前記所定値よりも大きいときに前記上側のスイッチング素子を導通させる第2回路(20)と、前記第1素子と並列に接続され、前記上側のスイッチング素子が導通する状態で導通し、前記上側のスイッチング素子が非導通である状態で非導通するスイッチ素子(32)とを備え、前記第1素子及び第2素子は、その両方がスイッチ(11,12)であるか、又は一方がスイッチであって他方が抵抗素子(15,16)である。

【0011】

本発明にかかる電力変換装置用の駆動回路の第3の態様は、第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、出力端(Pu,Pv,Pw,Px)を介して互いに直列に接続される上側のスイッチング素子(Tu1,Tv1,Tw1,Tx1)及び下側のスイッチング素子(Tu2,Tv2,Tw2,Tx2)を有し、前記上側のスイッチング素子が前記第1の電源線側に配置される電力変換装置の、前記上側のスイッチング素子の駆動回路(DVu1,DVv1,DVw1,DVx1)であって、前記出力端に接続される低電位端と、高電位端とを有する直流電源(E1)と、前記低電位端と前記高電位端との間で相互に直列に接続される第1素子(11,15)及び第2素子(12,16)を有し、前記第1素子は前記高電位端側に設けられ、前記第2素子は前記低電位端側に設けられる第1回路(10)と、前記第2素子の両端の電圧(V1)が所定値よりも小さいときに前記上側のスイッチング素子を非導通とし、前記電圧が前記所定値よりも大きいときに前記上側のスイッチング素子を導通させる第2回路(20)と、前記第2素子と並列に接続され、前記上側のスイッチング素子が非導通する状態で導通し、前記上側のスイッチング素子が導通する状態で非導通するスイッチ素子(35)と、を備える。

【0012】

本発明にかかる電力変換用の駆動回路の第4の態様は、第3の態様にかかる電力変換用の駆動回路であって、前記第1素子(11,15)と並列に接続され、前記上側のスイッチング素子(Tx1)が導通する状態で導通し、前記上側のスイッチング素子が非導通である状態で非導通する第2のスイッチ素子(32)を更に備える。

【0013】

本発明にかかる電力変換用の駆動回路の第5の態様は、第1から第4の何れか一つの態様にかかる電力変換用の駆動回路であって、前記スイッチ素子(32,35)と直列に接続される抵抗(31,34)を備える。

【0014】

本発明にかかる電力変換装置の第6の態様は、第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、互いに直列に接続される上側及び下側のスイッチング素子(Tu1,Tv1,Tw1,Tu2,Tv2,Tw2)と、第1から第5の何れか一つの態様にかかる駆動回路(DVu1,DVv1,DVw1)とを備える。

【発明の効果】

【0015】

本発明にかかる電力変換装置用の駆動回路の第1の態様によれば、上側スイッチング素子は第2素子の両端の電圧が所定値よりも大きいときに非導通となる。当該電圧を所定値よりも大きくするには、第1素子を経由して直流電源の高電位端を第2素子に接続する。例えば第1素子及び第2素子がスイッチである場合、第1素子を導通させ、第2素子を非導通とする。また例えば第1素子がスイッチ、第2素子が抵抗である場合は、第1素子を導通させる。また例えば第1素子が抵抗、第2素子がスイッチである場合は、第2素子を非導通とする。

【0016】

さて、一般的に電力変換装置においては、上側および下側のスイッチング素子が同時に導通しないように、これらを互いに排他的に制御する。したがって、上側のスイッチング素子が非導通である状態で、すなわち、当該電圧が所定値よりも大きい状態で、下側のスイッチング素子が導通から非導通に切り替る。

【0017】

そして、この切り替わりに応じて下側のスイッチング素子の両端電圧(第2の直流線の電位に対する出力端の電位)が増大すれば、かかる変化に起因して、第2素子の両端における静電容量には、寄生容量(第2素子の高電位側の端と第2の直流線との間の寄生容量)を経由して電流が流れ、静電容量が放電される。これに伴って第2素子の両端の電圧が低減する。

【0018】

しかしながら、当該電圧の低減は次の理由から抑制される。まず、上側のスイッチング素子は非導通なので、スイッチ素子は導通する。したがって、直流電源から第1素子及びスイッチ素子を並列に経由して上記静電容量へと電流が供給される。第1素子及びスイッチ素子が並列に接続されるので、これらの合成抵抗値は、第1素子単体の抵抗値よりも小さい。よって、スイッチ素子が設けられない場合に比べて、充電電流を高めることができる。これにより、第2素子の両端の電圧(静電容量の電圧)の低下を抑制することができる。ひいては、当該電圧が所定値を下回る可能性を低減でき、上側のスイッチング素子が意図せず導通することを抑制できる。

【0019】

しかも、第2素子の両端の電圧が所定値よりも小さく上側のスイッチング素子が導通するときには、スイッチ素子は非導通となるので、不要な消費電力を低減できる。

【0020】

本発明にかかる電力変換装置用の駆動回路の第2の態様によれば、上側スイッチング素子は第2素子の両端の電圧が所定値よりも大きいときに導通する。当該電圧を所定値よりも大きくするには、第1素子を経由して直流電源の高電位端を第2素子に接続する。例えば第1素子及び第2素子がスイッチである場合、第1素子を導通させ、第2素子を非導通とする。また例えば第1素子がスイッチ、第2素子が抵抗である場合は、第1素子を導通させる。また例えば第1素子が抵抗、第2素子がスイッチである場合は、第2素子を非導通とする。

【0021】

さて、上側のスイッチング素子の非導通から導通への切り替わりに応じて、下側のスイッチング素子の両端電圧(第2の直流線の電位に対する出力端の電位)が増大すれば、かかる変化に起因して、第2素子の両端における静電容量には、寄生容量(第2素子の高電位側の端と第2の直流線との間の寄生容量)を経由して電流が流れ、静電容量が放電される。これに伴って第2素子の両端の電圧が低減する。

【0022】

しかしながら、当該電圧の低減は次の理由から抑制される。まず、上側のスイッチング素子は導通するので、スイッチ素子は導通する。したがって、直流電源から第1素子及びスイッチ素子を並列に経由して上記静電容量へと電流が供給される。第1素子及びスイッチ素子が並列に接続されるので、これらの合成抵抗値は、第1素子単体の抵抗値よりも小さい。よって、スイッチ素子が設けられない場合に比べて、充電電流を高めることができる。これにより、第2素子の両端の電圧(静電容量の電圧)の低下を抑制することができる。ひいては、当該電圧が所定値を下回る可能性を低減でき、上側のスイッチング素子が意図せず非導通することを抑制できる。

【0023】

しかも、第2素子の両端の電圧が所定値よりも小さく上側のスイッチング素子が非導通するときには、スイッチ素子は非導通となるので、不要な消費電力を低減できる。

【0024】

本発明にかかる電力変換装置用の駆動回路の第3の態様によれば、上側スイッチング素子は第2素子の両端の電圧が所定値よりも小さいときに非導通する。当該電圧を所定値よりも小さくするには、例えば第1素子及び第2素子がスイッチである場合、第1素子を非導通とし、第2素子を導通させる。また例えば第1素子がスイッチ、第2素子が抵抗である場合は、第1素子を非導通させる。また例えば第1素子が抵抗、第2素子がスイッチである場合は、第2素子を導通させる。

【0025】

さて、一般的に電力変換装置においては、上側および下側のスイッチング素子が同時に導通しないように、これらを互いに排他的に制御する。したがって、上側のスイッチング素子が非導通である状態で、すなわち、当該電圧が所定値よりも小さい状態で、下側のスイッチング素子が非導通から導通に切り替る。

【0026】

そして、この切り替わりに応じて下側のスイッチング素子の両端電圧(第2の直流線の電位に対する出力端の電位)が低減すれば、かかる変化に起因して、第2素子の両端における静電容量には、寄生容量(第2素子の高電位側の端と第2の直流線との間の寄生容量)を経由して電流が流れ、静電容量が充電される。これに伴って第2素子の両端の電圧が増大する。

【0027】

しかしながら、当該電圧の増大は次の理由から抑制される。まず、上側のスイッチング素子は非導通なので、スイッチ素子は導通する。しかもスイッチ素子は第2素子と並列に接続される。したがって、第2素子の両端における静電容量へと向かう電流の一部がスイッチ素子へと流れるので、第2素子の両端の電圧の増大を抑制することができる。ひいては、第2素子の両端の電圧が所定値を上回る可能性を低減でき、上側のスイッチング素子が意図せずに導通することを抑制できる。

【0028】

しかも、第2素子の両端の電圧が所定値よりも大きく上側のスイッチング素子が導通するときには、スイッチ素子は導通となるので、不要な消費電力を低減できる。

【0029】

本発明にかかる電力変換用の駆動回路の第1の態様によれば、請求項2に記載の電力変換用の駆動回路と同じ効果を招来する。

【0030】

本発明にかかる電力変換用の駆動回路の第2の態様によれば、スイッチ素子に流れる電流を制限できる。

【0031】

本発明にかかる電力変換装置の第1の態様によれば、上側のスイッチング素子の誤動作を抑制できる電力変換装置を提供できる。

【図面の簡単な説明】

【0032】

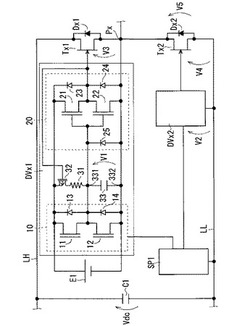

【図1】電力変換装置1の概念的な構成の一例を例示する図である。

【図2】電力変換装置1のうち1相に相当する部分の概念的な構成の一例を例示する図である。

【図3】回路10の概念的な構成の一例を例示する図である。

【図4】回路10の概念的な構成の一例を例示する図である。

【図5】タイミングチャートの一例を示す図である。

【図6】等価回路の概念的な一例を示す図である。

【図7】等価回路の概念的な一例を示す図である。

【図8】タイミングチャートの一例を示す図である。

【図9】電力変換装置1のうち1相に相当する部分の概念的な構成の一例を例示する図である。

【図10】タイミングチャートの一例を示す図である。

【図11】等価回路の概念的な一例を示す図である。

【図12】等価回路の概念的な一例を示す図である。

【図13】タイミングチャートの一例を示す図である。

【発明を実施するための形態】

【0033】

第1の実施の形態.

<電力変換装置の構成>

図1に例示する電力変換装置1は、直流線LH,LLの間に印加される直流電圧を交流電圧に変換して、当該交流電圧を出力端Pu,Pv,Pwへと出力する。ここでは直流線LLに印加される電位は直流線LHに印加される電位よりも低い。

【0034】

電力変換装置1は上側のスイッチング素子Tu1,Tv1,Tw1と下側のスイッチング素子Tu2,Tv2,Tw2とを備えている。スイッチング素子Tu1,Tu2は直流線LH,LLの間で出力端Puを介して互いに直列に接続され、スイッチング素子Tv1,Tv2は直流線LH,LLの間で出力端Pvを介して互いに直列に接続され、スイッチング素子Tw1,Tw2は直流線LH,LLの間で出力端Pwを介して互いに直列に接続される。上側のスイッチング素子Tu1,Tv1,Tw1は直流線LH側に配置され、下側のスイッチング素子Tu2,Tv2,Tw2は直流線LL側に配置される。

【0035】

スイッチング素子Tx1,Tx2(xはu,v,wを代表する、以下同様)は例えばMOS電界効果トランジスタ、絶縁ゲートバイポーラトランジスタ、接合型トランジスタ等である。

【0036】

またスイッチング素子Tx1,Tx2にはそれぞれダイオードDx1,Dx2が並列接続される。ダイオードDx1,Dx2は、その順方向が直流線LLから直流線LHへと向かう方向に沿うように設けられる。なお、スイッチング素子Tx1,Tx2が直流線LLからLHに向けて流れる寄生ダイオード等のような構造を有していれば、別途ダイオードを設けなくてもよい。

【0037】

スイッチング素子Tx1にはそれぞれ駆動回路DVx1が接続されている。駆動回路DVx1は上側のスイッチング素子Tx1の制御電極(例えばゲート電極)と出力端Pxとに接続され、またスイッチング信号生成部SP1からスイッチング信号を受け取る。駆動回路DVx1は入力されたスイッチング信号に基づいて上側のスイッチング素子Tx1の制御電圧(制御電極と出力端Pxとの間の電圧)を変化させる。上側のスイッチング素子Tx1は制御電圧に基づいてその導通/非導通を選択する。

【0038】

スイッチング素子Tx2にはそれぞれ駆動回路DVx2が接続されている。駆動回路DVx2は下側のスイッチング素子Tx2の制御電極と直流線LLとに接続され、またスイッチング信号生成部SP1からスイッチング信号を受け取る。駆動回路DVx2は入力されたスイッチング信号に基づいて下側のスイッチング素子Tx2の制御電圧(制御電極と直流線LLとの間の電圧)を変化させる。下側のスイッチング素子Tx2は制御電圧に基づいてその導通/非導通を選択する。

【0039】

スイッチング信号生成部SP1は直流線LLと接続されており、上述のとおり駆動回路DVx1,DVx2へとスイッチング信号を出力する。スイッチング信号生成部SP1は例えばPWM方式によってスイッチング信号を生成する。スイッチング信号生成部SP1が適切にスイッチング信号を生成して、これらを各駆動回路DVx1,DVx2へと出力することによって、電力変換装置1は直流電圧を所望の交流電圧に変換してこれを出力端Pu,Pv,Pwに出力することができる。かかるスイッチング信号生成部SP1の構成及び機能は公知技術を用いて容易に実現されるので、ここでは詳細な説明を省略する。

【0040】

出力端Pu,Pv,Pwには例えば誘導性負荷2が接続される。誘導性負荷2は例えばモータであって、電力変換装置1から出力される交流電圧に基づいて回転する。

【0041】

なお図1の例示では、直流線LH,LLの間には平滑コンデンサC1が設けられている。平滑コンデンサC1は直流線LH,LLの間の直流電圧を平滑する。但し、平滑コンデンサC1は必須要件ではなく、直流線LH,LLの間に直流電圧が印加されれば電力変換装置1は機能する。

【0042】

また図1の例示では、電力変換装置1は3つの出力端Pu,Pv,Pwに接続される3相の電力変換装置である。ただし、これに限らず、電力変換装置1は単相の電力変換装置であってもよく、3相以上の電力変換装置であってもよい。

【0043】

<駆動回路DVx1の構成の一例>

図2は電力変換装置1のうち1相分の概念的な構成の一例を示している。図2に例示するように、駆動回路DVx1は回路10,20とプルアップスイッチ素子32とを備えている。なお、以下ではプルアップスイッチ素子32を単にスイッチ素子32とも呼ぶ。

【0044】

回路10には直流電源E1が入力される。直流電源E1の低電位端は出力端Pxに接続される。また回路10は一対のスイッチ素子11,12を備えている。スイッチ素子11,12は直流電源E1の高電位端と低電位端との間で相互に直列に接続される。図2の例示では、スイッチ素子11は高電位端側に設けられ、スイッチ素子12は低電位端側に設けられる。スイッチ素子11,12は互いに排他的に導通する。スイッチ素子11,12は例えばフォトカプラであって、スイッチング信号生成部SP1から受け取ったスイッチング信号に基づいて導通する。より詳細には、スイッチ素子11は発光部(不図示)と受光部(制御電極の機能に相当)とを備える。発光部はスイッチング信号に基づいて発光し、例えばスイッチング信号が高電圧値を採るときに発光する。受光部はかかる発光を受光し、受光部が受光したことを以て、スイッチ素子11が導通し、スイッチ素子12が非導通する。またスイッチング信号が低電圧値を採るときに発光部は発光を停止し、これによってスイッチ素子11が非導通し、スイッチ素子12が導通する。

【0045】

なお図2の例示では、スイッチ素子11,12にはそれぞれダイオード13,14が並列に接続される。ダイオード13,14は各々のアノードが直流電源E1の低電位端側を向いて設けられる。これにより、スイッチ素子11,12に逆電圧が印加されることを防止することができる。これらは寄生ダイオードであってもよいし、設けられなくてもよい。

【0046】

また図2の例示では、回路10の出力側に、スイッチ素子12に並列に接続されるコンデンサ33が設けられる。なお、コンデンサ33はいわゆる素子であってもよく、回路の寄生容量であってもよい。

【0047】

以下では、回路10の技術的意義について述べる。ここではスイッチング信号生成部SP1から出力されるスイッチング信号の基準電位は直流線LLの電位である。一方で、上側のスイッチング素子Tx1の制御電極に印加されるべき制御電圧の基準電位は出力端Pxの電位である。本回路10によれば、スイッチング信号に基づいてスイッチ素子11,12が制御される。そして、スイッチ素子11,12の導通/非導通によってスイッチ素子12の両端の電圧V1(コンデンサ33の両端電圧)を変化させることができる。スイッチ素子12の一端(コンデンサ33の一端332)は出力端Pxに接続されているので、電圧V1の基準電位は出力端Pxの電位である。したがって本回路10によれば、直流線LLの電位を基準とするスイッチング信号に基づいて、出力端Pxの電位を基準電位とする電圧V1を生成できる。

【0048】

なお回路10は必ずしも一対のスイッチ素子11,12の両方を備えている必要はない。例えば図3に例示するように、スイッチ素子11の替わりに抵抗素子15を備えていても良く、また図4に例示するように、スイッチ素子12の替わりに抵抗素子16を備えてもよい。図3の回路10であれば、スイッチ素子12の導通/非導通によって電圧V1を変化させることができ、図4の回路10であれば、スイッチ素子11の導通/非導通によって電圧V1を変化させることができるからである。

【0049】

また、スイッチング信号の基準電位とスイッチング素子Tx1の制御電極の基準電位との間の相違を吸収するという観点では、回路10はフォトカプラに限らずレベルシフタであってもよい。

【0050】

回路20はスイッチ素子12の両端の電圧V1が所定値Vref1よりも大きいときに上側のスイッチング素子Tx1を非導通とし、当該電圧V1が所定値Vref1よりも小さいときに上側のスイッチング素子Tx1を導通させる。なお、図2の例示ではスイッチ素子12とコンデンサ33とが並列接続されていることから、電圧V1はコンデンサ33の両端電圧と見なすことができる。よって、以下では電圧V1をコンデンサ33の電圧とも呼ぶ。また、上側のスイッチング素子Tx1はヒステリシス特性を有していても良い。即ち、電圧V1が所定値Vref1とは異なる所定値よりも小さいときにスイッチング素子Tx1が導通しても良い。

【0051】

図2の例示では、回路20は、直流電源E1の高電位端と低電位端との間で、互いに排他的に導通する一対のスイッチ素子21,22を備えている。一対のスイッチ素子21,22は例えばCMOS(相補型金属酸化膜半導体)であって、これらの制御電極(ゲート電極)は共通してコンデンサ33の他端331(高電位側の端)に接続されている。またスイッチ素子21は上側のスイッチング素子Tx1の制御電極と直流電源E1の高電位端との間に設けられ、スイッチ素子22は上側のスイッチング素子Tx1の制御電極と出力端Pxとの間に接続される。スイッチ素子22はコンデンサ33の電圧V1が所定値よりも大きいときに導通する。このとき上側のスイッチング素子Tx1の制御電極には、上側のスイッチング素子Tx1を非導通とする制御電圧(図2の例示では、低電圧値(ほぼ零))が印加される。またスイッチ素子21はコンデンサ33の電圧V1が所定値よりも小さいときに導通する。このとき上側のスイッチング素子Tx1の制御電極には、上側のスイッチング素子Tx1を導通させる制御電圧(図2の例示では、高電圧値(ほぼ直流電源E1の直流電圧))が印加される。またスイッチ素子21、22とスイッチング素子Tx1の制御電極の間にノイズ除去用ではないゲート抵抗を設けてもよい。

【0052】

図2の例示では、スイッチ素子21,22のそれぞれに並列接続されるダイオード23,24が設けられている。ダイオード23,24はそれぞれアノードを出力端Pxに向けて設けられる。ダイオード23,24はそれぞれスイッチ素子21,22に逆電圧が印加されることを抑制する。またスイッチ素子21,22の制御電極と直流線LLとの間にダイオード25が設けられている。ダイオード25はこれらの制御電極と直流線LLとの間に逆電圧が印加されることを抑制する。これらは寄生ダイオードであってもよいし、設けられなくてもよい。

【0053】

なお、スイッチ素子21,22およびダイオード23〜25を設けずに、コンデンサ33の他端331が上側のスイッチング素子Tx1の制御電極に直接に接続されていても良い。この場合、制御電圧として高電圧が印加されたときに非導通し、制御電圧として低電圧が印加されたときに導通するスイッチング素子を上側のスイッチング素子Tx1として採用すればよい。またこの場合、回路20はコンデンサ33の他端331とスイッチング素子Tx1とを接続する配線によって形成される。

【0054】

プルアップスイッチ素子32はスイッチ素子11と並列に接続される。スイッチ素子32は、上側のスイッチング素子Tx1が非導通である状態で導通し、上側のスイッチング素子Tx1が導通する状態で非導通する。図2の例示では、スイッチ素子32の制御電極が上側のスイッチング素子Tx1の制御電極に接続されている。

【0055】

なお図2の例示では、スイッチ素子32に直列に抵抗31が設けられている。より詳細には、スイッチ素子32と抵抗31との直列接続体がスイッチ素子11に並列接続されている。抵抗31はいわゆるプルアップ抵抗として機能する。抵抗31によってスイッチ素子32に流れる電流を制限することができる。したがって、スイッチ素子32の電流容量を低減できる。

【0056】

<スイッチング動作>

かかる電力変換装置1において、スイッチング信号生成部SP1は上述したように駆動回路DVx1,DVx2へとスイッチング信号を出力する。このとき、上側のスイッチング素子Tx1と下側のスイッチング素子Tx2とは互いに排他的に導通するように、スイッチング信号が生成される。これは、スイッチング素子Tx1,Tx2が同時に導通すると直流線LH,LLがスイッチング素子Tx1,Tx2を介して短絡し、スイッチング素子Tx1,Tx2に大電流が流れるからである。かかる同時導通をより確実に回避すべく、スイッチング素子Tx1,Tx2の切り替えに際してデッドタイムを設けることが望ましい。即ち、スイッチング素子Tx1,Tx2のスイッチングに際して、一旦、スイッチング素子Tx1,Tx2の両方を非導通とする。

【0057】

スイッチング信号生成部SP1がかかる条件の下で適宜にスイッチング信号をそれぞれ3相のスイッチング素子Tx1,Tx2へと与えることで、電力変換装置1は交流電圧を出力する。かかる制御は公知な技術であって、本願の本質とは異なるため、詳細な説明は省略する。ここでは、1相のスイッチング素子Tx1,Tx2のスイッチングに着目して電圧V1の変動について説明する。

【0058】

図5は、所定の1相のスイッチング素子Tx1,Tx2がスイッチングするときの、各電圧V1〜V5の一例を示している。図2も参照して、電圧V1はスイッチ素子12(コンデンサ33)の両端電圧であり、電圧V2は駆動回路DVx2に入力される電圧である。換言すれば、電圧V1,V2はそれぞれスイッチング信号生成部SP1からそれぞれ駆動回路DVx1,DVx2に出力されるスイッチング信号と見なすことができる。電圧V3は駆動回路DVx1が出力する電圧(即ち上側のスイッチング素子Tx1の制御電極に印加される制御電圧)であり、電圧V4は駆動回路DVx2が出力する電圧(即ち下側のスイッチング素子Tx2の制御電極に印加される制御電圧)である。電圧V5は下側のスイッチング素子Tx2の両端電圧(即ち直流線LLと出力端Pxとの間の電圧)である。

【0059】

なお、図5の例示では、下側のスイッチング素子Tx2の導通/非導通の切り替わり(電圧V4の変化)に起因して電圧V5が変化する場合のタイミングチャートが示されている。上側のスイッチング素子Tx1の導通/非導通の切り替わり(電圧V3の変化)に起因して電圧V5が変化する場合については後述する。

【0060】

また各電圧V1〜V4は高電圧値及び低電圧値を採るところ、各電圧V1〜V4が採る高電圧値は互いに等しくても良く、或いは異なっていても良い。同様に各電圧V1〜V4が採る低電圧値は互いに等しくても良く、或いは異なっていても良い。

【0061】

図5の例示では、時点t1においてスイッチ素子11が非導通し、スイッチ素子12が導通しており、電圧V1が低電圧値を採る。低電圧値は所定値Vref1よりも小さく、例えば零である。電圧V1が低電圧値を採るのでスイッチ素子21が導通する。よって電圧V3は高電圧値を採り、上側のスイッチング素子Tx1は導通する。これにより出力端Pxの電位はほぼ直流線LHの電位となる。また電圧V3が高電圧値を採るのでプルアップスイッチ素子32は非導通する。一方、時点t1において電圧V2は例えば高電圧値(>所定値Vref2)を採る。ここでは駆動回路DVx2は電圧V2が高電圧値を採るときに電圧V4(<所定値Vref4)として低電圧値を出力する。したがって、時点t1において電圧V4は低電圧値を採り、下側のスイッチング素子Tx2が非導通となる。

【0062】

その後の時点t2においてスイッチ素子11が導通へと遷移し、スイッチ素子12が非導通へと遷移すると、電圧V1が低電圧値から高電圧値へと遷移する。かかる高電圧値は所定値Vref1よりも高く、例えば直流電源E1の直流電圧(例えば数十V)とほぼ等しい。かかる遷移から後述する時間が経過した時点において電圧V3は低下し始め、その後の時点t3において電圧V3が所定値Vref3を下回る。かかる経過時間および電圧V3の低下速度は回路20のデバイス特性及びスイッチング素子Tx1のゲート容量によって決定される。電圧V3が所定値Vref3を下回ると、上側のスイッチング素子Tx1が非導通となる。言い換えれば、デッドタイムが開始する。

【0063】

また電圧V3が所定値Vref3を下回ると、プルアップスイッチ素子32が導通する。

【0064】

そして時点t4において、電圧V2が高電圧値から低電圧値へと遷移する。かかる遷移から後述する時間が経過した後の時点において電圧V4が上昇し始める。かかる経過時間および電圧V4の上昇速度は駆動回路DVx2のデバイス特性及び下側のスイッチング素子Tx2のゲート容量によって決定される。そして電圧V4が所定値Vref4を超える時点t5において下側のスイッチング素子Tx2が導通する。

【0065】

さて図5の例示では、電圧V5は下側のスイッチング素子Tx2が導通する時点t5において直流電圧値Vdcとほぼ等しい値(以下、単に直流電圧値Vdc)から低下し始め、時点t6においてほぼ零(以下、単に零)を採る。なお電圧V5は上側のスイッチング素子Tx1が非導通となる時点t3において低下し始める場合もあるものの、この場合については後に詳述する。

【0066】

このように電圧V5が低下すると、電圧V5の変化に伴って回路の寄生容量を経由して電流がコンデンサ33に流れる。かかる電流についての等価回路が図6に例示される。電圧V5は直流電圧値Vdcから零へと変化する電圧源として把握される。本等価回路において、この電圧源に対してスイッチング信号生成部SP1の容量CSP1とスイッチ素子11,12の寄生容量C12とコンデンサ33とが互いに直列に接続される。なお、スイッチング信号生成部SP1はスイッチング信号を生成するためのスイッチ素子(不図示)を有しており、容量CSP1は例えばスイッチ素子の電源用コンデンサである。なお図6の図示では、容量CSP1を経由して、寄生容量C12と直流線LLとが接続されている場合が示されているが、これに限らない。寄生容量C12は、スイッチ素子11,12を接続する接続点と、スイッチ素子11,12の制御電極との間に存在する寄生容量である。

【0067】

また本等価回路においては、スイッチ素子11,12の寄生容量の他の一つとして寄生容量C11が、寄生容量CSP1,C12の間の点と直流電源E1の高電位端との間に設けられる。かかる寄生容量C11はスイッチ素子11,12の制御電極と、スイッチ素子11の高電位端との間の寄生容量である。図6の例示では、これらの寄生容量がコンデンサとして示されている。

【0068】

また時点t5,t6の間の期間において、スイッチ素子11,32は導通しているので、図6において、これらがそれぞれ抵抗11,32として示されている。よって、直流電源E1の高電位端と低電位端との間で、コンデンサ33と抵抗31,32とが互いに直列に接続され、抵抗11が抵抗31,32の直列接続体に対して並列に接続される。

【0069】

かかる等価回路において、電圧V5が低下することによって例えば容量CSP1,C12に蓄えられた電荷が放電し、これによってコンデンサ33が充電される(電流経路A1参照)。あるいは寄生容量C11から抵抗31,32,11を介してコンデンサ33が充電される。よって、コンデンサ33の電圧V1は増大する。

【0070】

かかるコンデンサ33の電圧V1の増大により、コンデンサ33の電圧V1が直流電源E1の電圧より大きくなると、コンデンサ33は抵抗31,32,11を経由して直流電源E1側に放電する(電流経路A2参照)。さて本駆動回路DVx1によれば、抵抗31,32の直列接続体と抵抗11とが互いに並列接続される。したがって、抵抗31,32が設けられていない場合に比べて、直流電源E1とコンデンサ33との間の抵抗部(抵抗31,32,11)の合成抵抗値を低減することができる。したがって、コンデンサ33から直流電源E1へと放電する電流を増大させることができ、以てコンデンサ33の電圧V1の増大をより抑制することができる。

【0071】

なお、時点t5,t6の間の期間において、仮に抵抗部(抵抗11,31,32)を経由してコンデンサ33が充電されれば、抵抗部の合成抵抗値が小さいことによって抵抗部を介したコンデンサ33の充電が促進される。つまり、電圧V1の増大が促進される。しかしながら、本駆動回路DVx1において、このような抵抗部を経由したコンデンサ33への充電はほとんど生じない。以下に説明する。

【0072】

抵抗部を介したコンデンサ33への充電として、寄生容量C11から抵抗部を経由したコンデンサ33への充電が考慮される。寄生容量C11からの電流は、コンデンサ33側よりも直流電源E1側に流れやすい(電流経路A3参照)。なぜなら、コンデンサ33と抵抗部のインピーダンスは直流電源E1のインピーダンスよりも十分に大きい(例えば直流電源E1の十分の1以下)からである。以上のように、抵抗部(抵抗11,31,32)を通ってコンデンサ33が充電されることはほとんどなく、当該抵抗部の合成抵抗値を低下させることによってコンデンサ33の充電が高まることはほとんどない。したがって、抵抗部の合成抵抗値が小さい本駆動回路DVx1において、適切に電圧V1の増大を抑制することができる。

【0073】

再び図5を参照して、時点t6において電圧V5が零に至ると、コンデンサ33への充電が停止する。コンデンサ33の抵抗部を経由した直流電源E1への放電は維持されるので、電圧V1は直流電源E1の電圧値と略一致するまで低減する。

【0074】

次に、時点t7において電圧V2が低電圧値から高電圧値(>所定値Vref2)へと遷移する。かかる遷移から後述する時間が経過した後の時点において電圧V4が低下し始める。かかる経過時間及び電圧V4の低下速度は駆動回路DVx2のデバイス特性及び下側のスイッチング素子Tx2のゲート容量によって決定される。そして、電圧V4が所定値Vref4を下回る時点t8において、下側のスイッチング素子Tx2が非導通となる。

【0075】

さて、図5の例示では、電圧V5は下側のスイッチング素子Tx2が非導通となる時点t8において増大し始め、時点t9において直流電圧値Vdcに至っている。なお、電圧V5は上側のスイッチング素子Tx1が導通する時点において増大し始める場合もあるものの、この場合については後に詳述する。

【0076】

このように電圧V5が増大すると、かかる変化に伴って回路の寄生容量を経由して電流が流れる。かかる電流についての等価回路が図7に例示される。電圧V5は零から直流電圧値Vdcに変化する電圧源として把握される。その他の構成は図6と同様である。

【0077】

かかる等価回路において、電圧源として機能する電圧V5が増大することによってコンデンサ33が容量C11,CSP1を経由して放電する(電流経路A4参照)。なお、下側のスイッチング素子Tx2が非導通であるにもかかわらず、電流が直流線LLからコンデンサ33へと向かって電圧源を通過するのは、導通状態から完全な非導通状態へと遷移する途中であって電流が流れるスイッチング素子Tx2やスイッチング素子Tx2の寄生容量が電流経路として存在するからである。かかる放電によってコンデンサ33の電圧V1は電圧V5が増大する時点t8から時点t9までの期間において低下する。

【0078】

一方、コンデンサ33の電圧V1が低下すれば、直流電源E1から抵抗31,32,11を経由してコンデンサ33へと充電電流が流れる(電流経路A5参照)。しかも、抵抗31,32が設けられていない場合に比べて抵抗部(抵抗31,32,11)の合成抵抗値を低減できるので、この充電電流を高めることができる。したがって、電圧V1の低下を抑制することができる。

【0079】

なお、仮にコンデンサ33が抵抗31,32,11を経由して寄生容量C11側或いは直流電源E1側へと放電すれば、抵抗31,32によって電圧V1の低下が促進され得る。しかしながら、コンデンサ33は抵抗31,32,11を介してはほとんど放電しない。これは、抵抗31,32,11よりも低い抵抗値で寄生容量C12と接続されているため、電流経路A4を経由して放電しやすいからである。そして、コンデンサ33が電流経路A4を経由して放電すれば、コンデンサ33の高電位端の電位が直流電源E1の高電位端の電位よりも小さくなる。よって、電流は、コンデンサ33から直流電源E1の高電位端に向かって抵抗31,32,11を流れない。したがって、抵抗部の合成抵抗値が小さい本駆動回路DVx1において、適切に電圧V1の低下を抑制することができる。

【0080】

以上のように、コンデンサ33の電圧V1の低下を適切に抑制することができるので、電圧V1が所定値Vref1を下回ることを抑制できる。これによって、上側のスイッチング素子Tx1が意図せずに導通することを抑制できる。

【0081】

再び図5も参照して、時点t9において電圧V5が直流電圧値Vdcを採ると、コンデンサ33の放電が停止する。一方、直流電源E1からのコンデンサ33の充電は維持されるので、コンデンサ33の電圧V1は増大して再び高電圧値を採る。

【0082】

その後、時点t10においてスイッチ素子11が非導通へと遷移し、スイッチ素子12が導通へと遷移すると、電圧V1が高電圧値から低電圧値へと遷移する。かかる遷移から後述する時間が経過した後の時点において電圧V3が増大し始める。かかる経過時間及び電圧V3の上昇速度は回路20のデバイス特性および上側のスイッチング素子Tx1のゲート容量によって決定される。そして、電圧V3が所定値Vref3を上回る時点t11において、上側のスイッチング素子Tx1が導通する。またこのときプルアップスイッチ素子32が非導通となる。

【0083】

そして、時点t12において再び電圧V1が低電圧値から高電圧値へと遷移する。その後は時点t2〜時点t11と同様の動作を行う。

【0084】

以上のように、本駆動回路DVx1によれば、電圧V1が高電圧値を採る状態で電圧V5が増大した(時点t8,t9の間の期間参照)としても、電圧V5の増大に起因する電圧V1の低下を抑制することができる。よって、上側のスイッチング素子Tx1の誤動作を抑制することができる。

【0085】

しかもプルアップスイッチ素子32は、上側のスイッチング素子Tx1を導通させる状態で、非導通となる(図5の「プルアップスイッチ素子OFF」参照)。したがって、プルアップスイッチ素子32を介した消費電力を低減することができる。

【0086】

しかも、特許文献1と異なって、上側のスイッチング素子Tx1の制御電極に流れる電流の経路上にはノイズ除去用抵抗を設ける必要がない。したがって、特許文献1のように当該抵抗に発生する電圧によって上側のスイッチング素子Tx1の誤動作が発生する事態を招かない。さらに特許文献1においてはノイズ除去用抵抗によって上側のスイッチング素子Tx1の高速化が妨げられる。本駆動回路DVx1ではかかる抵抗を設ける必要がないので、かかる高速化を招かない。

【0087】

以下では、電圧V5が上側のスイッチング素子Tx1の導通/非導通に基づいて変化する場合について説明する。図8に例示するように、電圧V5は、上側のスイッチング素子Tx1が導通した時点t3において直流電圧値Vdcから低下し始め、その後の時点t21においてほぼ零に至る。

【0088】

さて、電圧V5が低減するに際して、上述したように、コンデンサ33が充電されて電圧V1が増大する。このときの等価回路は図6と同様である。またコンデンサ33の電圧V1が直流電源E1の直流電圧よりも大きくなると、コンデンサ33は抵抗31,32,11を経由して放電する。よって、電圧V1の増大が抑制される。そして、時点t21において電圧V5がほぼ零に至るとコンデンサ33の充電が停止し、コンデンサ33の電圧V1は低減して再び高電圧値を採る。

【0089】

その後の時点t4において電圧V2が高電圧値から低電圧値へと遷移し、かかる遷移から所定時間が経過した後の時点において電圧V4が増大し始め、時点t5において電圧V4が所定値Vref4を超えたときに下側のスイッチング素子Tx2が導通する。そして、時点t7において電圧V2が低電圧値から高電圧値へと遷移し、かかる遷移から所定時間が経過した時点において電圧V4が低下し始め、時点t8において電圧V4が所定値Vref4を下回ったときに下側のスイッチング素子Tx2が非導通となる。

【0090】

その後の時点t10においてスイッチ素子11が非導通に遷移し、スイッチ素子12が導通へと遷移すると、電圧V1が高電圧値から低電圧値へと遷移する。かかる遷移から所定時間が経過した後の時点において電圧V3が増大し始め、電圧V3が所定値Vref3を超えた時点t11において上側のスイッチング素子Tx1が導通する。これに伴って、電圧V5がほぼ零から増大し始め、時点t22において直流電圧値Vdcに至る。

【0091】

さて、電圧V5が増大したことに起因して、コンデンサ33に電流が流れ、時点t11から時点t22の間において電圧V1は低下する。時点t11において電圧V1は零であるので、かかる低減によって電圧V1は負の値を採る。言い換えれば、コンデンサ33は出力端Px側を高電位として充電される。

【0092】

しかしながら、電圧V1が負の値を採ることによって上側のスイッチング素子Tx1が導通することはないので、電圧V1の低下は上側のスイッチング素子Tx1の誤動作を招かない。よって、この時点での電圧V1の低下は問題とならない。

【0093】

よって、電圧V5が上側のスイッチング素子Tx1の導通/非導通に応答して変化した場合も、上側のスイッチング素子Tx1の誤動作を招かない。

【0094】

さて、本実施の形態では、電圧V5が下側のスイッチング素子Tx2の導通/非導通に基づいて変化する第1の場合(図5)と、電圧V5が上側のスイッチング素子Tx1の導通/非導通に基づいて変化する第2の場合(図8)とについて説明した。これらの第1及び第2の場合のいずれもが、電力変換装置1による誘導性負荷2の制御中に生じる事象である。したがって、本駆動回路DVx1を採用することで、この制御中に生じる上側のスイッチング素子Tx1の誤動作を抑制することができる。

【0095】

また本駆動回路DVx1による効果を次のように表現することもできる。即ち、たとえ電圧V1が高電圧値を採るときに電圧V5が増大したとしても、電圧V5の変化に起因する電圧V1の低下を抑制することができる。よって、電圧V1が所定値Vref1を下回ることを抑制でき、ひいては上側のスイッチング素子Tx1の誤動作を抑制できる。

【0096】

ここで、本駆動回路DVx1とは異なる次の技術を採用して電圧V1の低下を抑制することを考慮する。すなわち、時点t8から時点t9までの期間における電圧V1の低下速度を遅くすることで、電圧V1の低下を抑制することを考慮する。電圧V1の低下速度を遅くするためには、例えば直流電源E1からコンデンサ33へと流れる電流を増やせばよい。したがって、回路10の供給能力を増大させる、あるいは直流電源E1とコンデンサ33との間の配線インピーダンスを低下させることが考えられる。しかしながら、一対のスイッチ素子11,12としてCMOSを採用すればその供給能力を十分に高めることが難しい。また配線の断面積を増大させて配線インピーダンスを低減すれば、回路規模が大きくなる。

【0097】

或いは、電圧V1の低下速度を遅くすべく、コンデンサ33の静電容量を高めることが考えられる。しかしながらコンデンサ33の静電容量を高めれば、応答性や遅延時間が劣化する。

【0098】

本駆動回路DVx1によれば、スイッチ素子32および抵抗31によって、電圧V1が高電圧値を採るときに生じる電圧V1の低下を抑制できるので、上述の対策を採る必要性を低減できる。ただし、本駆動回路DVx1に対して上述の対策を施しても良い。この場合であっても、必要となる回路10の供給能力を比較的小さくでき、或いは必要となる配線インピーダンスを比較的大きくでき、或いは必要となるコンデンサ33の静電容量を小さくできる。

【0099】

なお、上述の例では、プルアップスイッチ素子32は電圧V3が所定値Vref3を下回ったときに導通しているが、電圧V3が所定値Vref3よりも大きい値を下回ったときに導通してもよい。

【0100】

<上側および下側のスイッチング素子>

上側及び下側のスイッチング素子Tx1,Tx2は、SiC半導体またはGaN半導体等、新素材半導体で形成されていてもよい。この場合、上側及び下側のスイッチング素子Tx1,Tx2の高速スイッチングを実現することができる。一方で、高速スイッチングによって、回路10についての電流供給能力の不足、或いは配線インピーダンスの影響により、コンデンサ33の電圧V3の低下を招きやすい。したがって、本駆動回路DVx1を適用することの意義が高まる。

【0101】

第2の実施の形態.

以下、第2の実施の形態における駆動回路DVx1の、第1の実施の形態と異なる点について説明する。

【0102】

<駆動回路DVx1>

図9に例示する駆動回路DVx1は、図2に例示する駆動回路DVx1と比較して、プルダウンスイッチ素子35を更に備えている。なお、以下ではプルダウンスイッチ素子35を単にスイッチ素子35とも呼ぶ。プルダウンスイッチ素子35はスイッチ素子12と並列に接続される。換言すれば、プルダウンスイッチ素子35はコンデンサ33と並列に接続される。また図9の例示では、プルダウンスイッチ素子35に直列接続される抵抗34が設けられている。より詳細には、スイッチ素子35と抵抗34との直列接続体がスイッチ素子12に並列接続される。抵抗34はいわゆるプルダウン抵抗として機能する。抵抗34によってスイッチ素子35に流れる電流を制限することができる。したがって、スイッチ素子35の電流容量を低減できる。

【0103】

また図9の回路20の機能は、図2の回路20の機能と相違する。即ち、図9の回路20は、電圧V1が所定値Vref1よりも小さいときに、上側のスイッチング素子Tx1を非導通とする制御電圧を、上側のスイッチング素子Tx1の制御電圧に印可する。また回路20は、コンデンサ33の電圧V1が所定値Vref1よりも大きいときに、上側のスイッチング素子Tx1を導通させる制御電圧を上側のスイッチング素子Tx1の制御電圧に印可する。

【0104】

図9の例示では、回路20は一対のスイッチ素子21,22を備えている。一対のスイッチ素子21,22の接続関係は、図1のそれと同じである。ただし、スイッチ素子21はコンデンサ33の電圧V1が所定値Vref1よりも大きいときに導通する。このとき上側のスイッチング素子Tx1の制御電極には、上側のスイッチング素子Tx1を導通する制御電圧(ここでは高電圧)が印加される。またスイッチ素子22はコンデンサ33の電圧V1が所定値Vref1よりも小さいときに導通する。このとき上側のスイッチング素子Tx1の制御電極には、上側のスイッチング素子Tx1を非導通とする制御電圧(ここでは低電圧)が印加される。

【0105】

なお、図1と同様に、一対のスイッチ素子21,22及びダイオード23〜25を設けずに、コンデンサ33を直接に上側のスイッチング素子Tx1の制御電極に接続してもよい。

【0106】

また図9のプルアップスイッチ素子32の動作は、図2のプルアップスイッチ素子32の動作と相違する。即ち、図9のプルアップスイッチ素子32は、上側のスイッチング素子Tx1が導通する状態で導通し、上側のスイッチング素子Tx1が非導通する状態で非導通する。

【0107】

プルダウンスイッチ素子35はプルアップスイッチ素子32と排他的に導通する。より詳細には、プルダウンスイッチ素子35は、上側のスイッチング素子Tx1が非導通となる状態で導通し、上側のスイッチング素子Tx1が導通する状態で非導通となる。

【0108】

これを実現すべく図9の例示では、直流電源E1の高電位端と低電位端との間で相互に直列に接続される抵抗36及びスイッチ素子37が設けられている。抵抗36はスイッチ素子37よりも直流電源E1の高電位端側に配置され、抵抗36とスイッチ素子37との間の接続点がスイッチ素子32,35の制御電極に共通して接続される。スイッチ素子37の制御電極は上側のスイッチング素子Tx1の制御電極に接続される。スイッチ素子37は上側のスイッチング素子Tx1の制御電極が高電圧値を採るときに、導通する。これに伴って、スイッチ素子32,35の制御電極には低電圧が印加される。これにより、スイッチ素子32が導通し、スイッチ素子35が非導通する。一方、スイッチ素子37は、上側のスイッチング素子Tx1の制御電極が低電圧値を採るときに非導通する。これに伴って、スイッチ素子32,35の制御電極には高電圧が印加される。これにより、スイッチ素子32が非導通し、スイッチ素子35が導通する。

【0109】

なお、プルアップスイッチ素子32および抵抗31の一組と、プルダウンスイッチ素子35および抵抗34の一組との両方が設けられる必要はなく、何れか一方のみが設けられていても良い。以下では、図10のタイミングチャートを参照して、プルダウンスイッチ素子35と抵抗34による作用・効果について説明し、次いで、図13のタイミングチャートを参照して、プルアップスイッチ素子32および抵抗31による作用・効果も説明する。

【0110】

なお、図10,13におけるタイミングチャートの相違は、図5,8と同様に、電圧V5が下側のスイッチング素子Tx2の導通/非導通に起因して変化するのか、上側のスイッチング素子Tx1の導通/非導通に起因して変化するのか、に依る。

【0111】

<スイッチング動作>

図10に例示では、時点t1においてスイッチ素子11が導通し、スイッチ素子12が非導通しており、電圧V1が高電圧値を採る。よってこのとき電圧V3は高電圧値を採り、上側のスイッチング素子Tx1が導通する。また電圧V3が高電圧値を採るのでスイッチ素子37は導通する。これにより、プルアップスイッチ素子32は導通し、プルダウンスイッチ素子35は非導通する。一方、時点t1において電圧V2は低電圧値を採る。よってこのとき電圧V4は低電圧値を採る。このとき下側のスイッチング素子Tx2は非導通する。

【0112】

その後の時点t2において、スイッチ素子11が非導通に遷移し、スイッチ素子12が導通へと遷移すると、電圧V1が高電圧値から低電圧値へと遷移する。かかる遷移から所定時間が経過した時点において電圧V3は低下し始め、その後の時点t3において電圧V3が所定値Vref3を下回る。電圧V3が所定値Vref3を下回ると上側のスイッチング素子Tx1が非導通する。また時点t3においてスイッチ素子37が非導通する。これにより、プルアップスイッチ素子32が非導通し、プルダウンスイッチ素子35が導通する。

【0113】

そして時点t5において、電圧V2が低電圧値から高電圧値へと遷移する。かかる遷移から所定時間が経過した後の時点において電圧V4が上昇し始め、電圧V4が所定値Vref4を超える時点t5において下側のスイッチング素子Tx2が導通する。

【0114】

さて図10の例示では、電圧V5は下側のスイッチング素子Tx2が導通する時点t5において直流電圧値Vdcとほぼ等しい値(以下、単に直流電圧値Vdc)から低下し始め、時点t6においてほぼ零(以下、単に零)を採っている。なお電圧V5は上側のスイッチング素子Tx1が非導通となる時点t3において低下し始める場合もあるものの、この場合については後に詳述する。

【0115】

このように電圧V5が低下すると、電圧V5の変化に伴って回路の寄生容量を経由して電流がコンデンサ33に流れる。かかる電流についての等価回路が図11に例示される。電圧V5は直流電圧値Vdcから零へと変化する電圧源として把握される。本等価回路において、この電圧源に対してスイッチング信号生成部SP1の容量CSP1とスイッチ素子11,12の寄生容量C12とコンデンサ33とが互いに直列に接続される。この点は図6と同様である。

【0116】

また時点t5,t6の間の期間において、スイッチ素子12,35が導通しているので、図11において、これらがそれぞれ抵抗12,35として示されている。よって、抵抗12と、抵抗34,35の直列接続体とがそれぞれコンデンサ33と並列に接続される。

【0117】

かかる等価回路において、電圧V5が低下することによって例えば容量CSP1,C12に蓄えられた電荷が放電し、これによってコンデンサ33が充電される(電流経路A6参照)。よって、コンデンサ33の電圧V1は増大する。しかしながら、容量CSP1,C12の放電電流は、コンデンサ33のみならず、これと並列に接続される抵抗12及び抵抗34,35の直列接続体も流れる。したがって、抵抗34,35が設けられていない場合に比べて、コンデンサ33に流れる電流を減らすことができ、ひいてはコンデンサ33の電圧V1の増大を抑制することができる。よって、電圧V1が所定値Vref1を超える可能性を低減でき、ひいては上側のスイッチング素子Tx1が意図せず導通することを抑制できる。

【0118】

再び図10を参照して、時点t6において電圧V5が零に至ると、コンデンサ33への充電が停止する。コンデンサ33は抵抗12,34,35へと放電するので、コンデンサ33の電圧V1は低電圧値(ここではほぼ零)と一致するまで低減する。

【0119】

次に、時点t7において電圧V2が高電圧値から低電圧値へ遷移する。かかる遷移から所定時間が経過した後の時点において電圧V4が低下し始め、電圧V4が所定値Vref4を下回る時点t8において、下側のスイッチング素子Tx2が非導通となる。

【0120】

さて、図10の例示では、電圧V5は下側のスイッチング素子Tx2が非導通となる時点t8において増大し始め、時点t9において直流電圧値Vdcに至っている。なお、電圧V5は上側のスイッチング素子Tx1が導通する時点において増大し始める場合もあるものの、この場合については後に詳述する。

【0121】

このように電圧V5が増大すると、かかる変化に伴って回路の寄生容量を経由して電流が流れる。かかる電流についての等価回路が図12に例示される。電圧V5は零から直流電圧値Vdcに変化する電圧源として把握される。その他の構成は図11と同様である。

【0122】

かかる等価回路において、電圧源として機能する電圧V5が増大することによってコンデンサ33に電流が流れる(電流経路A7参照)。なお、下側のスイッチング素子Tx2が非導通であるにもかかわらず、電流が直流線LLからコンデンサ33へと向かって電圧源を通過するのは、導通状態から完全な非導通状態へと遷移する途中であって電流が流れるスイッチング素子Tx2やスイッチング素子Tx2の寄生容量が電流経路として存在するからである。かかる電流によって、コンデンサ33の一端332側を高電位として充電される。言い換えれば、電圧V1は時点t8から時点t9までの期間において負の領域で低下する。しかしながら、かかる電流は、コンデンサ33のみならず、これと並列に接続される抵抗12及び抵抗34,35の直列接続体も流れる。したがって、コンデンサ33に流れる電流を減らすことができ、ひいてはコンデンサ33の電圧V1の低下(絶対値としては増大)を抑制することができる。

【0123】

次に時点t10においてスイッチ素子11が導通へと遷移し、スイッチ素子12が非導通へと遷移すると、電圧V1が低電圧値から高電圧値へと遷移する。かかる遷移から所定時間が経過した後の時点において電圧V3が上昇し始め、電圧V3が所定値Vref3を超える時点t11において上側のスイッチング素子Tx1が導通する。またこのとき、スイッチ素子37が導通する。これにより、プルアップスイッチ素子32が導通し、プルダウンスイッチ素子35が非導通する。

【0124】

その後の時点t12において、再びスイッチ素子11が非導通し、スイッチ素子12が導通すると、電圧V1が高電圧値から低電圧値へと遷移する。その後は時点t2〜時点t11と同様の動作を行う。

【0125】

以上のように、時点t5,t6の間における電圧V1の増大を抑制することができるので、電圧V1が所定値Vref1を超えることを抑制できる。これによって、上側のスイッチング素子Tx1が意図せずに導通することを抑制できる。

【0126】

しかもプルダウンスイッチ素子35は、上側のスイッチング素子Tx1を導通させる状態で、非導通となる(図10の「プルダウンスイッチ素子OFF」参照)。したがって、プルダウンスイッチ素子35を介した消費電力を低減することができる。

【0127】

なお、図10の状況は誘導性負荷2の制御中に生じる事象であるところ、図10の状況ではプルアップスイッチ素子32及び抵抗31は上側のスイッチング素子Tx1の誤動作の抑制という観点で寄与しない。図10の状況において上側のスイッチング素子Tx1の誤動作を抑制するためにはプルダウンスイッチ素子35が設けられていれば足りる。

【0128】

次に、電圧V5が上側のスイッチング素子Tx1の導通/非導通に基づいて変化する場合について説明する。図13に例示するように、電圧V5は、上側のスイッチング素子Tx1が導通した時点t3において直流電圧値Vdcから低下し始め、その後の時点t21においてほぼ零に至る。

【0129】

さて、電圧V5が低減するに際して、上述したように、コンデンサ33が充電されて電圧V1が増大する。このときの等価回路は図11と同様である。したがって、抵抗34,35が設けられていない場合に比べて、電圧V1の増大を抑制することができる。そして、時点t21において電圧V5がほぼ零に至るとコンデンサ33の充電が停止し、電圧V1は低減して再び低電圧値を採る。

【0130】

その後の時点t5において電圧V2が低電圧値から高電圧値へと遷移し、かかる遷移から所定時間が経過した後の時点において電圧V4が増大し始め、時点t6において電圧V4が所定値Vref4を超えたときに下側のスイッチング素子Tx2が導通する。そして、時点t8において電圧V2が高電圧値から低電圧値へと遷移し、かかる遷移から所定時間が経過した時点において電圧V4が低下し始め、時点t9において電圧V4が所定値Vref4を下回ったときに下側のスイッチング素子Tx2が非導通となる。

【0131】

その後の時点t10においてスイッチ素子11が導通に遷移し、スイッチ素子12が非導通へと遷移すると、電圧V1が低電圧値から高電圧値へと遷移する。かかる遷移から所定時間が経過した後の時点において電圧V3が増大し始め、電圧V3が所定値Vref3を超えた時点t11において上側のスイッチング素子Tx1が導通する。またこのとき、スイッチ素子37が導通する。これにより、プルアップスイッチ素子32が導通し、プルダウンスイッチ素子35が非導通する。

【0132】

電圧V5が増大したことに起因して、コンデンサ33は放電するので、時点t11から時点t22の間において電圧V1は低下する。かかる放電時の等価回路は図7と同様である。したがって、抵抗31,32が設けられていない場合に比べて、電圧V1の低下を抑制することができる。

【0133】

そして、時点t22において電圧V5がほぼ直流電圧値Vdcと等しい値に至ると、コンデンサ33の放電が停止し、電圧V1が再び高電圧値を採るまで増大する。

【0134】

その後の時点t12において、スイッチ素子11が非導通へと遷移し、スイッチ素子12が導通へと遷移すると、電圧V1が高電圧値から低電圧値へと遷移する。

【0135】

以上のように、電圧V1が低電圧値を採る状態で電圧V5が低減することに起因してコンデンサ33が充電されたとしても、プルダウンスイッチ素子35が導通しているので電圧V1の増大を抑制でき、また電圧V1が高電圧値を採る状態で電圧V5が増大することに起因してコンデンサ33が放電したとしても、プルアップスイッチ素子32が導通しているので、電圧V1の低下を抑制することができる。したがって、上側のスイッチング素子Tx1が意図せずに切り替わることを抑制することができる。

【0136】

なお、プルダウンスイッチ素子35と抵抗34とが設けられていない場合であっても、プルアップスイッチ素子32、或いは更に抵抗31によって、図13の時点t11,t22の間の期間における電圧V1の低下を抑制することができる。したがって、プルダウンスイッチ素子35および抵抗34は必ずしも必要ではない。逆に、プルアップスイッチ素子32と抵抗31とが設けられていない場合であっても、プルダウンスイッチ素子35、或いは更に抵抗34によって図10の時点t5,t6、或いは図13の時点t3,t21の間の期間における電圧V1の増大を抑制できる。したがって、プルアップスイッチ素子32および抵抗31は必ずしも必要ではない。

【符号の説明】

【0137】

10,20 回路

31,34 抵抗

32 プルアップスイッチ素子

33 コンデンサ

35 プルダウンスイッチ素子

DVx1 駆動回路

E1 直流電源

LH,LL 直流線

Px 出力端

Tx1,Tx2 スイッチング素子

【技術分野】

【0001】

本発明は、電力変換装置用の駆動回路および電力変換装置に関し、特に電力変換装置に属する上側のスイッチング素子の誤動作を抑制する技術に関する。

【背景技術】

【0002】

特許文献1には三相インバータが記載されている。三相インバータは、正極側および負極側のスイッチング素子を有するアームを三相分備えている。各相のアームは互いに並列に接続される。正極側及び負極側のスイッチング素子にはそれぞれドライブ回路が接続される。正極側のスイッチング素子についてのドライブ回路は、正極側のスイッチング素子のゲート電極とエミッタ電極との間に設けられる。ドライブ回路は、ゲート電極とエミッタ電極との間の電圧を制御して、正極側のスイッチング素子を制御する。またドライブ回路には入力絶縁回路が含まれる。

【0003】

かかるドライブ回路は、当該電圧を印加するための動作電源となる第1及び第2のコンデンサを有している。第1及び第2のコンデンサは互いに直列に接続され、これらの間の点が上記エミッタ電極に接続される。第1及び第2のコンデンサは互いに反対側でそれぞれ第1及び第2のスイッチ素子を介してゲート電極に接続される。かかる構造において、第1のスイッチ素子が導通すれば、第1のコンデンサがゲート電極に接続されて、正極側のスイッチング素子が導通する。一方、第2のスイッチング素子が導通すれば、第2のコンデンサがゲート電極に接続されて、正極側のスイッチング素子が非導通となる。

【0004】

さらに、特許文献1では、第1及び第2のコンデンサの間の点と、上記エミッタ電極との間に抵抗を設けている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特許第3292662号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1では、第1及び第2のコンデンサの間の点と、上記エミッタ電極との間にはノイズ除去用抵抗が設けられている。よって、入力絶縁回路の入出力間容量を介したdv/dtノイズを低減できる。しかし、当該抵抗はゲート電極とエミッタ電極との間に設けられるので、抵抗に生じる電圧がゲート電極とエミッタ電極との間の電圧に影響を与える。したがって、抵抗に生じる電圧が大きければ、正極側のスイッチング素子が誤動作する可能性がある。

【0007】

なお、以下では正極側のスイッチング素子を上側のスイッチング素子と呼び、負極側のスイッチング素子を下側のスイッチング素子と呼ぶ。

【0008】

本発明は、上側のスイッチング素子の誤動作を抑制できる電力変換装置用の駆動回路を提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明にかかる電力変換装置用の駆動回路の第1の態様は、第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、出力端(Pu,Pv,Pw,Px)を介して互いに直列に接続される上側のスイッチング素子(Tu1,Tv1,Tw1,Tx1)及び下側のスイッチング素子(Tu2,Tv2,Tw2,Tx2)を有し、前記上側のスイッチング素子が前記第1の電源線側に配置される電力変換装置の、前記上側のスイッチング素子の駆動回路(DVu1,DVv1,DVw1,DVx1)であって、前記出力端に接続される低電位端と、高電位端とを有する直流電源(E1)と、前記低電位端と前記高電位端との間で相互に直列に接続される第1素子(11,15)及び第2素子(12,16)を有し、前記第1素子は前記高電位端側に設けられ、前記第2素子は前記低電位端側に設けられる第1回路(10)と、前記第2素子の両端の電圧(V1)が所定値よりも大きいときに前記上側のスイッチング素子を非導通とし、前記電圧が前記所定値よりも小さいときに前記上側のスイッチング素子を導通させる第2回路(20)と、前記第1素子と並列に接続され、前記上側のスイッチング素子が非導通である状態で導通し、前記上側のスイッチング素子が導通する状態で非導通するスイッチ素子(32)とを備え、前記第1素子及び第2素子は、その両方がスイッチ(11,12)であるか、又は一方がスイッチであって他方が抵抗素子(15,16)である。

【0010】

本発明にかかる電力変換装置用の駆動回路の第2の態様は、第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、出力端(Pu,Pv,Pw,Px)を介して互いに直列に接続される上側のスイッチング素子(Tu1,Tv1,Tw1,Tx1)及び下側のスイッチング素子(Tu2,Tv2,Tw2,Tx2)を有し、前記上側のスイッチング素子が前記第1の電源線側に配置される電力変換装置の、前記上側のスイッチング素子の駆動回路(DVu1,DVv1,DVw1,DVx1)であって、前記出力端に接続される低電位端と、高電位端とを有する直流電源(E1)と、前記低電位端と前記高電位端との間で相互に直列に接続される第1素子(11,15)及び第2素子(12,16)を有し、前記第1素子は前記高電位端側に設けられ、前記第2素子は前記低電位端側に設けられる第1回路(10)と、前記第2素子の両端の電圧(V1)が所定値よりも小さいときに前記上側のスイッチング素子を非導通とし、前記電圧が前記所定値よりも大きいときに前記上側のスイッチング素子を導通させる第2回路(20)と、前記第1素子と並列に接続され、前記上側のスイッチング素子が導通する状態で導通し、前記上側のスイッチング素子が非導通である状態で非導通するスイッチ素子(32)とを備え、前記第1素子及び第2素子は、その両方がスイッチ(11,12)であるか、又は一方がスイッチであって他方が抵抗素子(15,16)である。

【0011】

本発明にかかる電力変換装置用の駆動回路の第3の態様は、第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、出力端(Pu,Pv,Pw,Px)を介して互いに直列に接続される上側のスイッチング素子(Tu1,Tv1,Tw1,Tx1)及び下側のスイッチング素子(Tu2,Tv2,Tw2,Tx2)を有し、前記上側のスイッチング素子が前記第1の電源線側に配置される電力変換装置の、前記上側のスイッチング素子の駆動回路(DVu1,DVv1,DVw1,DVx1)であって、前記出力端に接続される低電位端と、高電位端とを有する直流電源(E1)と、前記低電位端と前記高電位端との間で相互に直列に接続される第1素子(11,15)及び第2素子(12,16)を有し、前記第1素子は前記高電位端側に設けられ、前記第2素子は前記低電位端側に設けられる第1回路(10)と、前記第2素子の両端の電圧(V1)が所定値よりも小さいときに前記上側のスイッチング素子を非導通とし、前記電圧が前記所定値よりも大きいときに前記上側のスイッチング素子を導通させる第2回路(20)と、前記第2素子と並列に接続され、前記上側のスイッチング素子が非導通する状態で導通し、前記上側のスイッチング素子が導通する状態で非導通するスイッチ素子(35)と、を備える。

【0012】

本発明にかかる電力変換用の駆動回路の第4の態様は、第3の態様にかかる電力変換用の駆動回路であって、前記第1素子(11,15)と並列に接続され、前記上側のスイッチング素子(Tx1)が導通する状態で導通し、前記上側のスイッチング素子が非導通である状態で非導通する第2のスイッチ素子(32)を更に備える。

【0013】

本発明にかかる電力変換用の駆動回路の第5の態様は、第1から第4の何れか一つの態様にかかる電力変換用の駆動回路であって、前記スイッチ素子(32,35)と直列に接続される抵抗(31,34)を備える。

【0014】

本発明にかかる電力変換装置の第6の態様は、第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、互いに直列に接続される上側及び下側のスイッチング素子(Tu1,Tv1,Tw1,Tu2,Tv2,Tw2)と、第1から第5の何れか一つの態様にかかる駆動回路(DVu1,DVv1,DVw1)とを備える。

【発明の効果】

【0015】

本発明にかかる電力変換装置用の駆動回路の第1の態様によれば、上側スイッチング素子は第2素子の両端の電圧が所定値よりも大きいときに非導通となる。当該電圧を所定値よりも大きくするには、第1素子を経由して直流電源の高電位端を第2素子に接続する。例えば第1素子及び第2素子がスイッチである場合、第1素子を導通させ、第2素子を非導通とする。また例えば第1素子がスイッチ、第2素子が抵抗である場合は、第1素子を導通させる。また例えば第1素子が抵抗、第2素子がスイッチである場合は、第2素子を非導通とする。

【0016】

さて、一般的に電力変換装置においては、上側および下側のスイッチング素子が同時に導通しないように、これらを互いに排他的に制御する。したがって、上側のスイッチング素子が非導通である状態で、すなわち、当該電圧が所定値よりも大きい状態で、下側のスイッチング素子が導通から非導通に切り替る。

【0017】

そして、この切り替わりに応じて下側のスイッチング素子の両端電圧(第2の直流線の電位に対する出力端の電位)が増大すれば、かかる変化に起因して、第2素子の両端における静電容量には、寄生容量(第2素子の高電位側の端と第2の直流線との間の寄生容量)を経由して電流が流れ、静電容量が放電される。これに伴って第2素子の両端の電圧が低減する。

【0018】

しかしながら、当該電圧の低減は次の理由から抑制される。まず、上側のスイッチング素子は非導通なので、スイッチ素子は導通する。したがって、直流電源から第1素子及びスイッチ素子を並列に経由して上記静電容量へと電流が供給される。第1素子及びスイッチ素子が並列に接続されるので、これらの合成抵抗値は、第1素子単体の抵抗値よりも小さい。よって、スイッチ素子が設けられない場合に比べて、充電電流を高めることができる。これにより、第2素子の両端の電圧(静電容量の電圧)の低下を抑制することができる。ひいては、当該電圧が所定値を下回る可能性を低減でき、上側のスイッチング素子が意図せず導通することを抑制できる。

【0019】

しかも、第2素子の両端の電圧が所定値よりも小さく上側のスイッチング素子が導通するときには、スイッチ素子は非導通となるので、不要な消費電力を低減できる。

【0020】

本発明にかかる電力変換装置用の駆動回路の第2の態様によれば、上側スイッチング素子は第2素子の両端の電圧が所定値よりも大きいときに導通する。当該電圧を所定値よりも大きくするには、第1素子を経由して直流電源の高電位端を第2素子に接続する。例えば第1素子及び第2素子がスイッチである場合、第1素子を導通させ、第2素子を非導通とする。また例えば第1素子がスイッチ、第2素子が抵抗である場合は、第1素子を導通させる。また例えば第1素子が抵抗、第2素子がスイッチである場合は、第2素子を非導通とする。

【0021】

さて、上側のスイッチング素子の非導通から導通への切り替わりに応じて、下側のスイッチング素子の両端電圧(第2の直流線の電位に対する出力端の電位)が増大すれば、かかる変化に起因して、第2素子の両端における静電容量には、寄生容量(第2素子の高電位側の端と第2の直流線との間の寄生容量)を経由して電流が流れ、静電容量が放電される。これに伴って第2素子の両端の電圧が低減する。

【0022】

しかしながら、当該電圧の低減は次の理由から抑制される。まず、上側のスイッチング素子は導通するので、スイッチ素子は導通する。したがって、直流電源から第1素子及びスイッチ素子を並列に経由して上記静電容量へと電流が供給される。第1素子及びスイッチ素子が並列に接続されるので、これらの合成抵抗値は、第1素子単体の抵抗値よりも小さい。よって、スイッチ素子が設けられない場合に比べて、充電電流を高めることができる。これにより、第2素子の両端の電圧(静電容量の電圧)の低下を抑制することができる。ひいては、当該電圧が所定値を下回る可能性を低減でき、上側のスイッチング素子が意図せず非導通することを抑制できる。

【0023】

しかも、第2素子の両端の電圧が所定値よりも小さく上側のスイッチング素子が非導通するときには、スイッチ素子は非導通となるので、不要な消費電力を低減できる。

【0024】

本発明にかかる電力変換装置用の駆動回路の第3の態様によれば、上側スイッチング素子は第2素子の両端の電圧が所定値よりも小さいときに非導通する。当該電圧を所定値よりも小さくするには、例えば第1素子及び第2素子がスイッチである場合、第1素子を非導通とし、第2素子を導通させる。また例えば第1素子がスイッチ、第2素子が抵抗である場合は、第1素子を非導通させる。また例えば第1素子が抵抗、第2素子がスイッチである場合は、第2素子を導通させる。

【0025】

さて、一般的に電力変換装置においては、上側および下側のスイッチング素子が同時に導通しないように、これらを互いに排他的に制御する。したがって、上側のスイッチング素子が非導通である状態で、すなわち、当該電圧が所定値よりも小さい状態で、下側のスイッチング素子が非導通から導通に切り替る。

【0026】

そして、この切り替わりに応じて下側のスイッチング素子の両端電圧(第2の直流線の電位に対する出力端の電位)が低減すれば、かかる変化に起因して、第2素子の両端における静電容量には、寄生容量(第2素子の高電位側の端と第2の直流線との間の寄生容量)を経由して電流が流れ、静電容量が充電される。これに伴って第2素子の両端の電圧が増大する。

【0027】

しかしながら、当該電圧の増大は次の理由から抑制される。まず、上側のスイッチング素子は非導通なので、スイッチ素子は導通する。しかもスイッチ素子は第2素子と並列に接続される。したがって、第2素子の両端における静電容量へと向かう電流の一部がスイッチ素子へと流れるので、第2素子の両端の電圧の増大を抑制することができる。ひいては、第2素子の両端の電圧が所定値を上回る可能性を低減でき、上側のスイッチング素子が意図せずに導通することを抑制できる。

【0028】

しかも、第2素子の両端の電圧が所定値よりも大きく上側のスイッチング素子が導通するときには、スイッチ素子は導通となるので、不要な消費電力を低減できる。

【0029】

本発明にかかる電力変換用の駆動回路の第1の態様によれば、請求項2に記載の電力変換用の駆動回路と同じ効果を招来する。

【0030】

本発明にかかる電力変換用の駆動回路の第2の態様によれば、スイッチ素子に流れる電流を制限できる。

【0031】

本発明にかかる電力変換装置の第1の態様によれば、上側のスイッチング素子の誤動作を抑制できる電力変換装置を提供できる。

【図面の簡単な説明】

【0032】

【図1】電力変換装置1の概念的な構成の一例を例示する図である。

【図2】電力変換装置1のうち1相に相当する部分の概念的な構成の一例を例示する図である。

【図3】回路10の概念的な構成の一例を例示する図である。

【図4】回路10の概念的な構成の一例を例示する図である。

【図5】タイミングチャートの一例を示す図である。

【図6】等価回路の概念的な一例を示す図である。

【図7】等価回路の概念的な一例を示す図である。

【図8】タイミングチャートの一例を示す図である。

【図9】電力変換装置1のうち1相に相当する部分の概念的な構成の一例を例示する図である。

【図10】タイミングチャートの一例を示す図である。

【図11】等価回路の概念的な一例を示す図である。

【図12】等価回路の概念的な一例を示す図である。

【図13】タイミングチャートの一例を示す図である。

【発明を実施するための形態】

【0033】

第1の実施の形態.

<電力変換装置の構成>

図1に例示する電力変換装置1は、直流線LH,LLの間に印加される直流電圧を交流電圧に変換して、当該交流電圧を出力端Pu,Pv,Pwへと出力する。ここでは直流線LLに印加される電位は直流線LHに印加される電位よりも低い。

【0034】

電力変換装置1は上側のスイッチング素子Tu1,Tv1,Tw1と下側のスイッチング素子Tu2,Tv2,Tw2とを備えている。スイッチング素子Tu1,Tu2は直流線LH,LLの間で出力端Puを介して互いに直列に接続され、スイッチング素子Tv1,Tv2は直流線LH,LLの間で出力端Pvを介して互いに直列に接続され、スイッチング素子Tw1,Tw2は直流線LH,LLの間で出力端Pwを介して互いに直列に接続される。上側のスイッチング素子Tu1,Tv1,Tw1は直流線LH側に配置され、下側のスイッチング素子Tu2,Tv2,Tw2は直流線LL側に配置される。

【0035】

スイッチング素子Tx1,Tx2(xはu,v,wを代表する、以下同様)は例えばMOS電界効果トランジスタ、絶縁ゲートバイポーラトランジスタ、接合型トランジスタ等である。

【0036】

またスイッチング素子Tx1,Tx2にはそれぞれダイオードDx1,Dx2が並列接続される。ダイオードDx1,Dx2は、その順方向が直流線LLから直流線LHへと向かう方向に沿うように設けられる。なお、スイッチング素子Tx1,Tx2が直流線LLからLHに向けて流れる寄生ダイオード等のような構造を有していれば、別途ダイオードを設けなくてもよい。

【0037】

スイッチング素子Tx1にはそれぞれ駆動回路DVx1が接続されている。駆動回路DVx1は上側のスイッチング素子Tx1の制御電極(例えばゲート電極)と出力端Pxとに接続され、またスイッチング信号生成部SP1からスイッチング信号を受け取る。駆動回路DVx1は入力されたスイッチング信号に基づいて上側のスイッチング素子Tx1の制御電圧(制御電極と出力端Pxとの間の電圧)を変化させる。上側のスイッチング素子Tx1は制御電圧に基づいてその導通/非導通を選択する。

【0038】

スイッチング素子Tx2にはそれぞれ駆動回路DVx2が接続されている。駆動回路DVx2は下側のスイッチング素子Tx2の制御電極と直流線LLとに接続され、またスイッチング信号生成部SP1からスイッチング信号を受け取る。駆動回路DVx2は入力されたスイッチング信号に基づいて下側のスイッチング素子Tx2の制御電圧(制御電極と直流線LLとの間の電圧)を変化させる。下側のスイッチング素子Tx2は制御電圧に基づいてその導通/非導通を選択する。

【0039】

スイッチング信号生成部SP1は直流線LLと接続されており、上述のとおり駆動回路DVx1,DVx2へとスイッチング信号を出力する。スイッチング信号生成部SP1は例えばPWM方式によってスイッチング信号を生成する。スイッチング信号生成部SP1が適切にスイッチング信号を生成して、これらを各駆動回路DVx1,DVx2へと出力することによって、電力変換装置1は直流電圧を所望の交流電圧に変換してこれを出力端Pu,Pv,Pwに出力することができる。かかるスイッチング信号生成部SP1の構成及び機能は公知技術を用いて容易に実現されるので、ここでは詳細な説明を省略する。

【0040】

出力端Pu,Pv,Pwには例えば誘導性負荷2が接続される。誘導性負荷2は例えばモータであって、電力変換装置1から出力される交流電圧に基づいて回転する。

【0041】

なお図1の例示では、直流線LH,LLの間には平滑コンデンサC1が設けられている。平滑コンデンサC1は直流線LH,LLの間の直流電圧を平滑する。但し、平滑コンデンサC1は必須要件ではなく、直流線LH,LLの間に直流電圧が印加されれば電力変換装置1は機能する。

【0042】

また図1の例示では、電力変換装置1は3つの出力端Pu,Pv,Pwに接続される3相の電力変換装置である。ただし、これに限らず、電力変換装置1は単相の電力変換装置であってもよく、3相以上の電力変換装置であってもよい。

【0043】

<駆動回路DVx1の構成の一例>

図2は電力変換装置1のうち1相分の概念的な構成の一例を示している。図2に例示するように、駆動回路DVx1は回路10,20とプルアップスイッチ素子32とを備えている。なお、以下ではプルアップスイッチ素子32を単にスイッチ素子32とも呼ぶ。

【0044】

回路10には直流電源E1が入力される。直流電源E1の低電位端は出力端Pxに接続される。また回路10は一対のスイッチ素子11,12を備えている。スイッチ素子11,12は直流電源E1の高電位端と低電位端との間で相互に直列に接続される。図2の例示では、スイッチ素子11は高電位端側に設けられ、スイッチ素子12は低電位端側に設けられる。スイッチ素子11,12は互いに排他的に導通する。スイッチ素子11,12は例えばフォトカプラであって、スイッチング信号生成部SP1から受け取ったスイッチング信号に基づいて導通する。より詳細には、スイッチ素子11は発光部(不図示)と受光部(制御電極の機能に相当)とを備える。発光部はスイッチング信号に基づいて発光し、例えばスイッチング信号が高電圧値を採るときに発光する。受光部はかかる発光を受光し、受光部が受光したことを以て、スイッチ素子11が導通し、スイッチ素子12が非導通する。またスイッチング信号が低電圧値を採るときに発光部は発光を停止し、これによってスイッチ素子11が非導通し、スイッチ素子12が導通する。

【0045】

なお図2の例示では、スイッチ素子11,12にはそれぞれダイオード13,14が並列に接続される。ダイオード13,14は各々のアノードが直流電源E1の低電位端側を向いて設けられる。これにより、スイッチ素子11,12に逆電圧が印加されることを防止することができる。これらは寄生ダイオードであってもよいし、設けられなくてもよい。

【0046】

また図2の例示では、回路10の出力側に、スイッチ素子12に並列に接続されるコンデンサ33が設けられる。なお、コンデンサ33はいわゆる素子であってもよく、回路の寄生容量であってもよい。

【0047】

以下では、回路10の技術的意義について述べる。ここではスイッチング信号生成部SP1から出力されるスイッチング信号の基準電位は直流線LLの電位である。一方で、上側のスイッチング素子Tx1の制御電極に印加されるべき制御電圧の基準電位は出力端Pxの電位である。本回路10によれば、スイッチング信号に基づいてスイッチ素子11,12が制御される。そして、スイッチ素子11,12の導通/非導通によってスイッチ素子12の両端の電圧V1(コンデンサ33の両端電圧)を変化させることができる。スイッチ素子12の一端(コンデンサ33の一端332)は出力端Pxに接続されているので、電圧V1の基準電位は出力端Pxの電位である。したがって本回路10によれば、直流線LLの電位を基準とするスイッチング信号に基づいて、出力端Pxの電位を基準電位とする電圧V1を生成できる。

【0048】

なお回路10は必ずしも一対のスイッチ素子11,12の両方を備えている必要はない。例えば図3に例示するように、スイッチ素子11の替わりに抵抗素子15を備えていても良く、また図4に例示するように、スイッチ素子12の替わりに抵抗素子16を備えてもよい。図3の回路10であれば、スイッチ素子12の導通/非導通によって電圧V1を変化させることができ、図4の回路10であれば、スイッチ素子11の導通/非導通によって電圧V1を変化させることができるからである。

【0049】

また、スイッチング信号の基準電位とスイッチング素子Tx1の制御電極の基準電位との間の相違を吸収するという観点では、回路10はフォトカプラに限らずレベルシフタであってもよい。

【0050】

回路20はスイッチ素子12の両端の電圧V1が所定値Vref1よりも大きいときに上側のスイッチング素子Tx1を非導通とし、当該電圧V1が所定値Vref1よりも小さいときに上側のスイッチング素子Tx1を導通させる。なお、図2の例示ではスイッチ素子12とコンデンサ33とが並列接続されていることから、電圧V1はコンデンサ33の両端電圧と見なすことができる。よって、以下では電圧V1をコンデンサ33の電圧とも呼ぶ。また、上側のスイッチング素子Tx1はヒステリシス特性を有していても良い。即ち、電圧V1が所定値Vref1とは異なる所定値よりも小さいときにスイッチング素子Tx1が導通しても良い。

【0051】

図2の例示では、回路20は、直流電源E1の高電位端と低電位端との間で、互いに排他的に導通する一対のスイッチ素子21,22を備えている。一対のスイッチ素子21,22は例えばCMOS(相補型金属酸化膜半導体)であって、これらの制御電極(ゲート電極)は共通してコンデンサ33の他端331(高電位側の端)に接続されている。またスイッチ素子21は上側のスイッチング素子Tx1の制御電極と直流電源E1の高電位端との間に設けられ、スイッチ素子22は上側のスイッチング素子Tx1の制御電極と出力端Pxとの間に接続される。スイッチ素子22はコンデンサ33の電圧V1が所定値よりも大きいときに導通する。このとき上側のスイッチング素子Tx1の制御電極には、上側のスイッチング素子Tx1を非導通とする制御電圧(図2の例示では、低電圧値(ほぼ零))が印加される。またスイッチ素子21はコンデンサ33の電圧V1が所定値よりも小さいときに導通する。このとき上側のスイッチング素子Tx1の制御電極には、上側のスイッチング素子Tx1を導通させる制御電圧(図2の例示では、高電圧値(ほぼ直流電源E1の直流電圧))が印加される。またスイッチ素子21、22とスイッチング素子Tx1の制御電極の間にノイズ除去用ではないゲート抵抗を設けてもよい。

【0052】

図2の例示では、スイッチ素子21,22のそれぞれに並列接続されるダイオード23,24が設けられている。ダイオード23,24はそれぞれアノードを出力端Pxに向けて設けられる。ダイオード23,24はそれぞれスイッチ素子21,22に逆電圧が印加されることを抑制する。またスイッチ素子21,22の制御電極と直流線LLとの間にダイオード25が設けられている。ダイオード25はこれらの制御電極と直流線LLとの間に逆電圧が印加されることを抑制する。これらは寄生ダイオードであってもよいし、設けられなくてもよい。

【0053】

なお、スイッチ素子21,22およびダイオード23〜25を設けずに、コンデンサ33の他端331が上側のスイッチング素子Tx1の制御電極に直接に接続されていても良い。この場合、制御電圧として高電圧が印加されたときに非導通し、制御電圧として低電圧が印加されたときに導通するスイッチング素子を上側のスイッチング素子Tx1として採用すればよい。またこの場合、回路20はコンデンサ33の他端331とスイッチング素子Tx1とを接続する配線によって形成される。

【0054】

プルアップスイッチ素子32はスイッチ素子11と並列に接続される。スイッチ素子32は、上側のスイッチング素子Tx1が非導通である状態で導通し、上側のスイッチング素子Tx1が導通する状態で非導通する。図2の例示では、スイッチ素子32の制御電極が上側のスイッチング素子Tx1の制御電極に接続されている。

【0055】

なお図2の例示では、スイッチ素子32に直列に抵抗31が設けられている。より詳細には、スイッチ素子32と抵抗31との直列接続体がスイッチ素子11に並列接続されている。抵抗31はいわゆるプルアップ抵抗として機能する。抵抗31によってスイッチ素子32に流れる電流を制限することができる。したがって、スイッチ素子32の電流容量を低減できる。

【0056】

<スイッチング動作>

かかる電力変換装置1において、スイッチング信号生成部SP1は上述したように駆動回路DVx1,DVx2へとスイッチング信号を出力する。このとき、上側のスイッチング素子Tx1と下側のスイッチング素子Tx2とは互いに排他的に導通するように、スイッチング信号が生成される。これは、スイッチング素子Tx1,Tx2が同時に導通すると直流線LH,LLがスイッチング素子Tx1,Tx2を介して短絡し、スイッチング素子Tx1,Tx2に大電流が流れるからである。かかる同時導通をより確実に回避すべく、スイッチング素子Tx1,Tx2の切り替えに際してデッドタイムを設けることが望ましい。即ち、スイッチング素子Tx1,Tx2のスイッチングに際して、一旦、スイッチング素子Tx1,Tx2の両方を非導通とする。

【0057】

スイッチング信号生成部SP1がかかる条件の下で適宜にスイッチング信号をそれぞれ3相のスイッチング素子Tx1,Tx2へと与えることで、電力変換装置1は交流電圧を出力する。かかる制御は公知な技術であって、本願の本質とは異なるため、詳細な説明は省略する。ここでは、1相のスイッチング素子Tx1,Tx2のスイッチングに着目して電圧V1の変動について説明する。

【0058】

図5は、所定の1相のスイッチング素子Tx1,Tx2がスイッチングするときの、各電圧V1〜V5の一例を示している。図2も参照して、電圧V1はスイッチ素子12(コンデンサ33)の両端電圧であり、電圧V2は駆動回路DVx2に入力される電圧である。換言すれば、電圧V1,V2はそれぞれスイッチング信号生成部SP1からそれぞれ駆動回路DVx1,DVx2に出力されるスイッチング信号と見なすことができる。電圧V3は駆動回路DVx1が出力する電圧(即ち上側のスイッチング素子Tx1の制御電極に印加される制御電圧)であり、電圧V4は駆動回路DVx2が出力する電圧(即ち下側のスイッチング素子Tx2の制御電極に印加される制御電圧)である。電圧V5は下側のスイッチング素子Tx2の両端電圧(即ち直流線LLと出力端Pxとの間の電圧)である。

【0059】

なお、図5の例示では、下側のスイッチング素子Tx2の導通/非導通の切り替わり(電圧V4の変化)に起因して電圧V5が変化する場合のタイミングチャートが示されている。上側のスイッチング素子Tx1の導通/非導通の切り替わり(電圧V3の変化)に起因して電圧V5が変化する場合については後述する。

【0060】

また各電圧V1〜V4は高電圧値及び低電圧値を採るところ、各電圧V1〜V4が採る高電圧値は互いに等しくても良く、或いは異なっていても良い。同様に各電圧V1〜V4が採る低電圧値は互いに等しくても良く、或いは異なっていても良い。

【0061】

図5の例示では、時点t1においてスイッチ素子11が非導通し、スイッチ素子12が導通しており、電圧V1が低電圧値を採る。低電圧値は所定値Vref1よりも小さく、例えば零である。電圧V1が低電圧値を採るのでスイッチ素子21が導通する。よって電圧V3は高電圧値を採り、上側のスイッチング素子Tx1は導通する。これにより出力端Pxの電位はほぼ直流線LHの電位となる。また電圧V3が高電圧値を採るのでプルアップスイッチ素子32は非導通する。一方、時点t1において電圧V2は例えば高電圧値(>所定値Vref2)を採る。ここでは駆動回路DVx2は電圧V2が高電圧値を採るときに電圧V4(<所定値Vref4)として低電圧値を出力する。したがって、時点t1において電圧V4は低電圧値を採り、下側のスイッチング素子Tx2が非導通となる。

【0062】

その後の時点t2においてスイッチ素子11が導通へと遷移し、スイッチ素子12が非導通へと遷移すると、電圧V1が低電圧値から高電圧値へと遷移する。かかる高電圧値は所定値Vref1よりも高く、例えば直流電源E1の直流電圧(例えば数十V)とほぼ等しい。かかる遷移から後述する時間が経過した時点において電圧V3は低下し始め、その後の時点t3において電圧V3が所定値Vref3を下回る。かかる経過時間および電圧V3の低下速度は回路20のデバイス特性及びスイッチング素子Tx1のゲート容量によって決定される。電圧V3が所定値Vref3を下回ると、上側のスイッチング素子Tx1が非導通となる。言い換えれば、デッドタイムが開始する。

【0063】

また電圧V3が所定値Vref3を下回ると、プルアップスイッチ素子32が導通する。

【0064】

そして時点t4において、電圧V2が高電圧値から低電圧値へと遷移する。かかる遷移から後述する時間が経過した後の時点において電圧V4が上昇し始める。かかる経過時間および電圧V4の上昇速度は駆動回路DVx2のデバイス特性及び下側のスイッチング素子Tx2のゲート容量によって決定される。そして電圧V4が所定値Vref4を超える時点t5において下側のスイッチング素子Tx2が導通する。

【0065】

さて図5の例示では、電圧V5は下側のスイッチング素子Tx2が導通する時点t5において直流電圧値Vdcとほぼ等しい値(以下、単に直流電圧値Vdc)から低下し始め、時点t6においてほぼ零(以下、単に零)を採る。なお電圧V5は上側のスイッチング素子Tx1が非導通となる時点t3において低下し始める場合もあるものの、この場合については後に詳述する。

【0066】

このように電圧V5が低下すると、電圧V5の変化に伴って回路の寄生容量を経由して電流がコンデンサ33に流れる。かかる電流についての等価回路が図6に例示される。電圧V5は直流電圧値Vdcから零へと変化する電圧源として把握される。本等価回路において、この電圧源に対してスイッチング信号生成部SP1の容量CSP1とスイッチ素子11,12の寄生容量C12とコンデンサ33とが互いに直列に接続される。なお、スイッチング信号生成部SP1はスイッチング信号を生成するためのスイッチ素子(不図示)を有しており、容量CSP1は例えばスイッチ素子の電源用コンデンサである。なお図6の図示では、容量CSP1を経由して、寄生容量C12と直流線LLとが接続されている場合が示されているが、これに限らない。寄生容量C12は、スイッチ素子11,12を接続する接続点と、スイッチ素子11,12の制御電極との間に存在する寄生容量である。

【0067】

また本等価回路においては、スイッチ素子11,12の寄生容量の他の一つとして寄生容量C11が、寄生容量CSP1,C12の間の点と直流電源E1の高電位端との間に設けられる。かかる寄生容量C11はスイッチ素子11,12の制御電極と、スイッチ素子11の高電位端との間の寄生容量である。図6の例示では、これらの寄生容量がコンデンサとして示されている。

【0068】

また時点t5,t6の間の期間において、スイッチ素子11,32は導通しているので、図6において、これらがそれぞれ抵抗11,32として示されている。よって、直流電源E1の高電位端と低電位端との間で、コンデンサ33と抵抗31,32とが互いに直列に接続され、抵抗11が抵抗31,32の直列接続体に対して並列に接続される。

【0069】

かかる等価回路において、電圧V5が低下することによって例えば容量CSP1,C12に蓄えられた電荷が放電し、これによってコンデンサ33が充電される(電流経路A1参照)。あるいは寄生容量C11から抵抗31,32,11を介してコンデンサ33が充電される。よって、コンデンサ33の電圧V1は増大する。

【0070】

かかるコンデンサ33の電圧V1の増大により、コンデンサ33の電圧V1が直流電源E1の電圧より大きくなると、コンデンサ33は抵抗31,32,11を経由して直流電源E1側に放電する(電流経路A2参照)。さて本駆動回路DVx1によれば、抵抗31,32の直列接続体と抵抗11とが互いに並列接続される。したがって、抵抗31,32が設けられていない場合に比べて、直流電源E1とコンデンサ33との間の抵抗部(抵抗31,32,11)の合成抵抗値を低減することができる。したがって、コンデンサ33から直流電源E1へと放電する電流を増大させることができ、以てコンデンサ33の電圧V1の増大をより抑制することができる。

【0071】

なお、時点t5,t6の間の期間において、仮に抵抗部(抵抗11,31,32)を経由してコンデンサ33が充電されれば、抵抗部の合成抵抗値が小さいことによって抵抗部を介したコンデンサ33の充電が促進される。つまり、電圧V1の増大が促進される。しかしながら、本駆動回路DVx1において、このような抵抗部を経由したコンデンサ33への充電はほとんど生じない。以下に説明する。

【0072】

抵抗部を介したコンデンサ33への充電として、寄生容量C11から抵抗部を経由したコンデンサ33への充電が考慮される。寄生容量C11からの電流は、コンデンサ33側よりも直流電源E1側に流れやすい(電流経路A3参照)。なぜなら、コンデンサ33と抵抗部のインピーダンスは直流電源E1のインピーダンスよりも十分に大きい(例えば直流電源E1の十分の1以下)からである。以上のように、抵抗部(抵抗11,31,32)を通ってコンデンサ33が充電されることはほとんどなく、当該抵抗部の合成抵抗値を低下させることによってコンデンサ33の充電が高まることはほとんどない。したがって、抵抗部の合成抵抗値が小さい本駆動回路DVx1において、適切に電圧V1の増大を抑制することができる。

【0073】

再び図5を参照して、時点t6において電圧V5が零に至ると、コンデンサ33への充電が停止する。コンデンサ33の抵抗部を経由した直流電源E1への放電は維持されるので、電圧V1は直流電源E1の電圧値と略一致するまで低減する。

【0074】

次に、時点t7において電圧V2が低電圧値から高電圧値(>所定値Vref2)へと遷移する。かかる遷移から後述する時間が経過した後の時点において電圧V4が低下し始める。かかる経過時間及び電圧V4の低下速度は駆動回路DVx2のデバイス特性及び下側のスイッチング素子Tx2のゲート容量によって決定される。そして、電圧V4が所定値Vref4を下回る時点t8において、下側のスイッチング素子Tx2が非導通となる。

【0075】

さて、図5の例示では、電圧V5は下側のスイッチング素子Tx2が非導通となる時点t8において増大し始め、時点t9において直流電圧値Vdcに至っている。なお、電圧V5は上側のスイッチング素子Tx1が導通する時点において増大し始める場合もあるものの、この場合については後に詳述する。

【0076】

このように電圧V5が増大すると、かかる変化に伴って回路の寄生容量を経由して電流が流れる。かかる電流についての等価回路が図7に例示される。電圧V5は零から直流電圧値Vdcに変化する電圧源として把握される。その他の構成は図6と同様である。

【0077】

かかる等価回路において、電圧源として機能する電圧V5が増大することによってコンデンサ33が容量C11,CSP1を経由して放電する(電流経路A4参照)。なお、下側のスイッチング素子Tx2が非導通であるにもかかわらず、電流が直流線LLからコンデンサ33へと向かって電圧源を通過するのは、導通状態から完全な非導通状態へと遷移する途中であって電流が流れるスイッチング素子Tx2やスイッチング素子Tx2の寄生容量が電流経路として存在するからである。かかる放電によってコンデンサ33の電圧V1は電圧V5が増大する時点t8から時点t9までの期間において低下する。

【0078】

一方、コンデンサ33の電圧V1が低下すれば、直流電源E1から抵抗31,32,11を経由してコンデンサ33へと充電電流が流れる(電流経路A5参照)。しかも、抵抗31,32が設けられていない場合に比べて抵抗部(抵抗31,32,11)の合成抵抗値を低減できるので、この充電電流を高めることができる。したがって、電圧V1の低下を抑制することができる。

【0079】

なお、仮にコンデンサ33が抵抗31,32,11を経由して寄生容量C11側或いは直流電源E1側へと放電すれば、抵抗31,32によって電圧V1の低下が促進され得る。しかしながら、コンデンサ33は抵抗31,32,11を介してはほとんど放電しない。これは、抵抗31,32,11よりも低い抵抗値で寄生容量C12と接続されているため、電流経路A4を経由して放電しやすいからである。そして、コンデンサ33が電流経路A4を経由して放電すれば、コンデンサ33の高電位端の電位が直流電源E1の高電位端の電位よりも小さくなる。よって、電流は、コンデンサ33から直流電源E1の高電位端に向かって抵抗31,32,11を流れない。したがって、抵抗部の合成抵抗値が小さい本駆動回路DVx1において、適切に電圧V1の低下を抑制することができる。

【0080】

以上のように、コンデンサ33の電圧V1の低下を適切に抑制することができるので、電圧V1が所定値Vref1を下回ることを抑制できる。これによって、上側のスイッチング素子Tx1が意図せずに導通することを抑制できる。

【0081】

再び図5も参照して、時点t9において電圧V5が直流電圧値Vdcを採ると、コンデンサ33の放電が停止する。一方、直流電源E1からのコンデンサ33の充電は維持されるので、コンデンサ33の電圧V1は増大して再び高電圧値を採る。

【0082】

その後、時点t10においてスイッチ素子11が非導通へと遷移し、スイッチ素子12が導通へと遷移すると、電圧V1が高電圧値から低電圧値へと遷移する。かかる遷移から後述する時間が経過した後の時点において電圧V3が増大し始める。かかる経過時間及び電圧V3の上昇速度は回路20のデバイス特性および上側のスイッチング素子Tx1のゲート容量によって決定される。そして、電圧V3が所定値Vref3を上回る時点t11において、上側のスイッチング素子Tx1が導通する。またこのときプルアップスイッチ素子32が非導通となる。

【0083】

そして、時点t12において再び電圧V1が低電圧値から高電圧値へと遷移する。その後は時点t2〜時点t11と同様の動作を行う。

【0084】

以上のように、本駆動回路DVx1によれば、電圧V1が高電圧値を採る状態で電圧V5が増大した(時点t8,t9の間の期間参照)としても、電圧V5の増大に起因する電圧V1の低下を抑制することができる。よって、上側のスイッチング素子Tx1の誤動作を抑制することができる。

【0085】

しかもプルアップスイッチ素子32は、上側のスイッチング素子Tx1を導通させる状態で、非導通となる(図5の「プルアップスイッチ素子OFF」参照)。したがって、プルアップスイッチ素子32を介した消費電力を低減することができる。

【0086】

しかも、特許文献1と異なって、上側のスイッチング素子Tx1の制御電極に流れる電流の経路上にはノイズ除去用抵抗を設ける必要がない。したがって、特許文献1のように当該抵抗に発生する電圧によって上側のスイッチング素子Tx1の誤動作が発生する事態を招かない。さらに特許文献1においてはノイズ除去用抵抗によって上側のスイッチング素子Tx1の高速化が妨げられる。本駆動回路DVx1ではかかる抵抗を設ける必要がないので、かかる高速化を招かない。

【0087】

以下では、電圧V5が上側のスイッチング素子Tx1の導通/非導通に基づいて変化する場合について説明する。図8に例示するように、電圧V5は、上側のスイッチング素子Tx1が導通した時点t3において直流電圧値Vdcから低下し始め、その後の時点t21においてほぼ零に至る。

【0088】

さて、電圧V5が低減するに際して、上述したように、コンデンサ33が充電されて電圧V1が増大する。このときの等価回路は図6と同様である。またコンデンサ33の電圧V1が直流電源E1の直流電圧よりも大きくなると、コンデンサ33は抵抗31,32,11を経由して放電する。よって、電圧V1の増大が抑制される。そして、時点t21において電圧V5がほぼ零に至るとコンデンサ33の充電が停止し、コンデンサ33の電圧V1は低減して再び高電圧値を採る。

【0089】

その後の時点t4において電圧V2が高電圧値から低電圧値へと遷移し、かかる遷移から所定時間が経過した後の時点において電圧V4が増大し始め、時点t5において電圧V4が所定値Vref4を超えたときに下側のスイッチング素子Tx2が導通する。そして、時点t7において電圧V2が低電圧値から高電圧値へと遷移し、かかる遷移から所定時間が経過した時点において電圧V4が低下し始め、時点t8において電圧V4が所定値Vref4を下回ったときに下側のスイッチング素子Tx2が非導通となる。

【0090】

その後の時点t10においてスイッチ素子11が非導通に遷移し、スイッチ素子12が導通へと遷移すると、電圧V1が高電圧値から低電圧値へと遷移する。かかる遷移から所定時間が経過した後の時点において電圧V3が増大し始め、電圧V3が所定値Vref3を超えた時点t11において上側のスイッチング素子Tx1が導通する。これに伴って、電圧V5がほぼ零から増大し始め、時点t22において直流電圧値Vdcに至る。

【0091】

さて、電圧V5が増大したことに起因して、コンデンサ33に電流が流れ、時点t11から時点t22の間において電圧V1は低下する。時点t11において電圧V1は零であるので、かかる低減によって電圧V1は負の値を採る。言い換えれば、コンデンサ33は出力端Px側を高電位として充電される。

【0092】

しかしながら、電圧V1が負の値を採ることによって上側のスイッチング素子Tx1が導通することはないので、電圧V1の低下は上側のスイッチング素子Tx1の誤動作を招かない。よって、この時点での電圧V1の低下は問題とならない。

【0093】

よって、電圧V5が上側のスイッチング素子Tx1の導通/非導通に応答して変化した場合も、上側のスイッチング素子Tx1の誤動作を招かない。

【0094】

さて、本実施の形態では、電圧V5が下側のスイッチング素子Tx2の導通/非導通に基づいて変化する第1の場合(図5)と、電圧V5が上側のスイッチング素子Tx1の導通/非導通に基づいて変化する第2の場合(図8)とについて説明した。これらの第1及び第2の場合のいずれもが、電力変換装置1による誘導性負荷2の制御中に生じる事象である。したがって、本駆動回路DVx1を採用することで、この制御中に生じる上側のスイッチング素子Tx1の誤動作を抑制することができる。

【0095】

また本駆動回路DVx1による効果を次のように表現することもできる。即ち、たとえ電圧V1が高電圧値を採るときに電圧V5が増大したとしても、電圧V5の変化に起因する電圧V1の低下を抑制することができる。よって、電圧V1が所定値Vref1を下回ることを抑制でき、ひいては上側のスイッチング素子Tx1の誤動作を抑制できる。

【0096】

ここで、本駆動回路DVx1とは異なる次の技術を採用して電圧V1の低下を抑制することを考慮する。すなわち、時点t8から時点t9までの期間における電圧V1の低下速度を遅くすることで、電圧V1の低下を抑制することを考慮する。電圧V1の低下速度を遅くするためには、例えば直流電源E1からコンデンサ33へと流れる電流を増やせばよい。したがって、回路10の供給能力を増大させる、あるいは直流電源E1とコンデンサ33との間の配線インピーダンスを低下させることが考えられる。しかしながら、一対のスイッチ素子11,12としてCMOSを採用すればその供給能力を十分に高めることが難しい。また配線の断面積を増大させて配線インピーダンスを低減すれば、回路規模が大きくなる。

【0097】

或いは、電圧V1の低下速度を遅くすべく、コンデンサ33の静電容量を高めることが考えられる。しかしながらコンデンサ33の静電容量を高めれば、応答性や遅延時間が劣化する。

【0098】

本駆動回路DVx1によれば、スイッチ素子32および抵抗31によって、電圧V1が高電圧値を採るときに生じる電圧V1の低下を抑制できるので、上述の対策を採る必要性を低減できる。ただし、本駆動回路DVx1に対して上述の対策を施しても良い。この場合であっても、必要となる回路10の供給能力を比較的小さくでき、或いは必要となる配線インピーダンスを比較的大きくでき、或いは必要となるコンデンサ33の静電容量を小さくできる。

【0099】

なお、上述の例では、プルアップスイッチ素子32は電圧V3が所定値Vref3を下回ったときに導通しているが、電圧V3が所定値Vref3よりも大きい値を下回ったときに導通してもよい。

【0100】

<上側および下側のスイッチング素子>

上側及び下側のスイッチング素子Tx1,Tx2は、SiC半導体またはGaN半導体等、新素材半導体で形成されていてもよい。この場合、上側及び下側のスイッチング素子Tx1,Tx2の高速スイッチングを実現することができる。一方で、高速スイッチングによって、回路10についての電流供給能力の不足、或いは配線インピーダンスの影響により、コンデンサ33の電圧V3の低下を招きやすい。したがって、本駆動回路DVx1を適用することの意義が高まる。

【0101】

第2の実施の形態.

以下、第2の実施の形態における駆動回路DVx1の、第1の実施の形態と異なる点について説明する。

【0102】

<駆動回路DVx1>

図9に例示する駆動回路DVx1は、図2に例示する駆動回路DVx1と比較して、プルダウンスイッチ素子35を更に備えている。なお、以下ではプルダウンスイッチ素子35を単にスイッチ素子35とも呼ぶ。プルダウンスイッチ素子35はスイッチ素子12と並列に接続される。換言すれば、プルダウンスイッチ素子35はコンデンサ33と並列に接続される。また図9の例示では、プルダウンスイッチ素子35に直列接続される抵抗34が設けられている。より詳細には、スイッチ素子35と抵抗34との直列接続体がスイッチ素子12に並列接続される。抵抗34はいわゆるプルダウン抵抗として機能する。抵抗34によってスイッチ素子35に流れる電流を制限することができる。したがって、スイッチ素子35の電流容量を低減できる。

【0103】

また図9の回路20の機能は、図2の回路20の機能と相違する。即ち、図9の回路20は、電圧V1が所定値Vref1よりも小さいときに、上側のスイッチング素子Tx1を非導通とする制御電圧を、上側のスイッチング素子Tx1の制御電圧に印可する。また回路20は、コンデンサ33の電圧V1が所定値Vref1よりも大きいときに、上側のスイッチング素子Tx1を導通させる制御電圧を上側のスイッチング素子Tx1の制御電圧に印可する。

【0104】

図9の例示では、回路20は一対のスイッチ素子21,22を備えている。一対のスイッチ素子21,22の接続関係は、図1のそれと同じである。ただし、スイッチ素子21はコンデンサ33の電圧V1が所定値Vref1よりも大きいときに導通する。このとき上側のスイッチング素子Tx1の制御電極には、上側のスイッチング素子Tx1を導通する制御電圧(ここでは高電圧)が印加される。またスイッチ素子22はコンデンサ33の電圧V1が所定値Vref1よりも小さいときに導通する。このとき上側のスイッチング素子Tx1の制御電極には、上側のスイッチング素子Tx1を非導通とする制御電圧(ここでは低電圧)が印加される。

【0105】

なお、図1と同様に、一対のスイッチ素子21,22及びダイオード23〜25を設けずに、コンデンサ33を直接に上側のスイッチング素子Tx1の制御電極に接続してもよい。

【0106】

また図9のプルアップスイッチ素子32の動作は、図2のプルアップスイッチ素子32の動作と相違する。即ち、図9のプルアップスイッチ素子32は、上側のスイッチング素子Tx1が導通する状態で導通し、上側のスイッチング素子Tx1が非導通する状態で非導通する。

【0107】

プルダウンスイッチ素子35はプルアップスイッチ素子32と排他的に導通する。より詳細には、プルダウンスイッチ素子35は、上側のスイッチング素子Tx1が非導通となる状態で導通し、上側のスイッチング素子Tx1が導通する状態で非導通となる。

【0108】

これを実現すべく図9の例示では、直流電源E1の高電位端と低電位端との間で相互に直列に接続される抵抗36及びスイッチ素子37が設けられている。抵抗36はスイッチ素子37よりも直流電源E1の高電位端側に配置され、抵抗36とスイッチ素子37との間の接続点がスイッチ素子32,35の制御電極に共通して接続される。スイッチ素子37の制御電極は上側のスイッチング素子Tx1の制御電極に接続される。スイッチ素子37は上側のスイッチング素子Tx1の制御電極が高電圧値を採るときに、導通する。これに伴って、スイッチ素子32,35の制御電極には低電圧が印加される。これにより、スイッチ素子32が導通し、スイッチ素子35が非導通する。一方、スイッチ素子37は、上側のスイッチング素子Tx1の制御電極が低電圧値を採るときに非導通する。これに伴って、スイッチ素子32,35の制御電極には高電圧が印加される。これにより、スイッチ素子32が非導通し、スイッチ素子35が導通する。

【0109】

なお、プルアップスイッチ素子32および抵抗31の一組と、プルダウンスイッチ素子35および抵抗34の一組との両方が設けられる必要はなく、何れか一方のみが設けられていても良い。以下では、図10のタイミングチャートを参照して、プルダウンスイッチ素子35と抵抗34による作用・効果について説明し、次いで、図13のタイミングチャートを参照して、プルアップスイッチ素子32および抵抗31による作用・効果も説明する。

【0110】

なお、図10,13におけるタイミングチャートの相違は、図5,8と同様に、電圧V5が下側のスイッチング素子Tx2の導通/非導通に起因して変化するのか、上側のスイッチング素子Tx1の導通/非導通に起因して変化するのか、に依る。

【0111】

<スイッチング動作>

図10に例示では、時点t1においてスイッチ素子11が導通し、スイッチ素子12が非導通しており、電圧V1が高電圧値を採る。よってこのとき電圧V3は高電圧値を採り、上側のスイッチング素子Tx1が導通する。また電圧V3が高電圧値を採るのでスイッチ素子37は導通する。これにより、プルアップスイッチ素子32は導通し、プルダウンスイッチ素子35は非導通する。一方、時点t1において電圧V2は低電圧値を採る。よってこのとき電圧V4は低電圧値を採る。このとき下側のスイッチング素子Tx2は非導通する。

【0112】

その後の時点t2において、スイッチ素子11が非導通に遷移し、スイッチ素子12が導通へと遷移すると、電圧V1が高電圧値から低電圧値へと遷移する。かかる遷移から所定時間が経過した時点において電圧V3は低下し始め、その後の時点t3において電圧V3が所定値Vref3を下回る。電圧V3が所定値Vref3を下回ると上側のスイッチング素子Tx1が非導通する。また時点t3においてスイッチ素子37が非導通する。これにより、プルアップスイッチ素子32が非導通し、プルダウンスイッチ素子35が導通する。

【0113】

そして時点t5において、電圧V2が低電圧値から高電圧値へと遷移する。かかる遷移から所定時間が経過した後の時点において電圧V4が上昇し始め、電圧V4が所定値Vref4を超える時点t5において下側のスイッチング素子Tx2が導通する。

【0114】

さて図10の例示では、電圧V5は下側のスイッチング素子Tx2が導通する時点t5において直流電圧値Vdcとほぼ等しい値(以下、単に直流電圧値Vdc)から低下し始め、時点t6においてほぼ零(以下、単に零)を採っている。なお電圧V5は上側のスイッチング素子Tx1が非導通となる時点t3において低下し始める場合もあるものの、この場合については後に詳述する。

【0115】

このように電圧V5が低下すると、電圧V5の変化に伴って回路の寄生容量を経由して電流がコンデンサ33に流れる。かかる電流についての等価回路が図11に例示される。電圧V5は直流電圧値Vdcから零へと変化する電圧源として把握される。本等価回路において、この電圧源に対してスイッチング信号生成部SP1の容量CSP1とスイッチ素子11,12の寄生容量C12とコンデンサ33とが互いに直列に接続される。この点は図6と同様である。

【0116】

また時点t5,t6の間の期間において、スイッチ素子12,35が導通しているので、図11において、これらがそれぞれ抵抗12,35として示されている。よって、抵抗12と、抵抗34,35の直列接続体とがそれぞれコンデンサ33と並列に接続される。

【0117】

かかる等価回路において、電圧V5が低下することによって例えば容量CSP1,C12に蓄えられた電荷が放電し、これによってコンデンサ33が充電される(電流経路A6参照)。よって、コンデンサ33の電圧V1は増大する。しかしながら、容量CSP1,C12の放電電流は、コンデンサ33のみならず、これと並列に接続される抵抗12及び抵抗34,35の直列接続体も流れる。したがって、抵抗34,35が設けられていない場合に比べて、コンデンサ33に流れる電流を減らすことができ、ひいてはコンデンサ33の電圧V1の増大を抑制することができる。よって、電圧V1が所定値Vref1を超える可能性を低減でき、ひいては上側のスイッチング素子Tx1が意図せず導通することを抑制できる。

【0118】

再び図10を参照して、時点t6において電圧V5が零に至ると、コンデンサ33への充電が停止する。コンデンサ33は抵抗12,34,35へと放電するので、コンデンサ33の電圧V1は低電圧値(ここではほぼ零)と一致するまで低減する。

【0119】

次に、時点t7において電圧V2が高電圧値から低電圧値へ遷移する。かかる遷移から所定時間が経過した後の時点において電圧V4が低下し始め、電圧V4が所定値Vref4を下回る時点t8において、下側のスイッチング素子Tx2が非導通となる。

【0120】

さて、図10の例示では、電圧V5は下側のスイッチング素子Tx2が非導通となる時点t8において増大し始め、時点t9において直流電圧値Vdcに至っている。なお、電圧V5は上側のスイッチング素子Tx1が導通する時点において増大し始める場合もあるものの、この場合については後に詳述する。

【0121】

このように電圧V5が増大すると、かかる変化に伴って回路の寄生容量を経由して電流が流れる。かかる電流についての等価回路が図12に例示される。電圧V5は零から直流電圧値Vdcに変化する電圧源として把握される。その他の構成は図11と同様である。

【0122】

かかる等価回路において、電圧源として機能する電圧V5が増大することによってコンデンサ33に電流が流れる(電流経路A7参照)。なお、下側のスイッチング素子Tx2が非導通であるにもかかわらず、電流が直流線LLからコンデンサ33へと向かって電圧源を通過するのは、導通状態から完全な非導通状態へと遷移する途中であって電流が流れるスイッチング素子Tx2やスイッチング素子Tx2の寄生容量が電流経路として存在するからである。かかる電流によって、コンデンサ33の一端332側を高電位として充電される。言い換えれば、電圧V1は時点t8から時点t9までの期間において負の領域で低下する。しかしながら、かかる電流は、コンデンサ33のみならず、これと並列に接続される抵抗12及び抵抗34,35の直列接続体も流れる。したがって、コンデンサ33に流れる電流を減らすことができ、ひいてはコンデンサ33の電圧V1の低下(絶対値としては増大)を抑制することができる。

【0123】

次に時点t10においてスイッチ素子11が導通へと遷移し、スイッチ素子12が非導通へと遷移すると、電圧V1が低電圧値から高電圧値へと遷移する。かかる遷移から所定時間が経過した後の時点において電圧V3が上昇し始め、電圧V3が所定値Vref3を超える時点t11において上側のスイッチング素子Tx1が導通する。またこのとき、スイッチ素子37が導通する。これにより、プルアップスイッチ素子32が導通し、プルダウンスイッチ素子35が非導通する。

【0124】

その後の時点t12において、再びスイッチ素子11が非導通し、スイッチ素子12が導通すると、電圧V1が高電圧値から低電圧値へと遷移する。その後は時点t2〜時点t11と同様の動作を行う。

【0125】

以上のように、時点t5,t6の間における電圧V1の増大を抑制することができるので、電圧V1が所定値Vref1を超えることを抑制できる。これによって、上側のスイッチング素子Tx1が意図せずに導通することを抑制できる。

【0126】

しかもプルダウンスイッチ素子35は、上側のスイッチング素子Tx1を導通させる状態で、非導通となる(図10の「プルダウンスイッチ素子OFF」参照)。したがって、プルダウンスイッチ素子35を介した消費電力を低減することができる。

【0127】

なお、図10の状況は誘導性負荷2の制御中に生じる事象であるところ、図10の状況ではプルアップスイッチ素子32及び抵抗31は上側のスイッチング素子Tx1の誤動作の抑制という観点で寄与しない。図10の状況において上側のスイッチング素子Tx1の誤動作を抑制するためにはプルダウンスイッチ素子35が設けられていれば足りる。

【0128】

次に、電圧V5が上側のスイッチング素子Tx1の導通/非導通に基づいて変化する場合について説明する。図13に例示するように、電圧V5は、上側のスイッチング素子Tx1が導通した時点t3において直流電圧値Vdcから低下し始め、その後の時点t21においてほぼ零に至る。

【0129】

さて、電圧V5が低減するに際して、上述したように、コンデンサ33が充電されて電圧V1が増大する。このときの等価回路は図11と同様である。したがって、抵抗34,35が設けられていない場合に比べて、電圧V1の増大を抑制することができる。そして、時点t21において電圧V5がほぼ零に至るとコンデンサ33の充電が停止し、電圧V1は低減して再び低電圧値を採る。

【0130】

その後の時点t5において電圧V2が低電圧値から高電圧値へと遷移し、かかる遷移から所定時間が経過した後の時点において電圧V4が増大し始め、時点t6において電圧V4が所定値Vref4を超えたときに下側のスイッチング素子Tx2が導通する。そして、時点t8において電圧V2が高電圧値から低電圧値へと遷移し、かかる遷移から所定時間が経過した時点において電圧V4が低下し始め、時点t9において電圧V4が所定値Vref4を下回ったときに下側のスイッチング素子Tx2が非導通となる。

【0131】

その後の時点t10においてスイッチ素子11が導通に遷移し、スイッチ素子12が非導通へと遷移すると、電圧V1が低電圧値から高電圧値へと遷移する。かかる遷移から所定時間が経過した後の時点において電圧V3が増大し始め、電圧V3が所定値Vref3を超えた時点t11において上側のスイッチング素子Tx1が導通する。またこのとき、スイッチ素子37が導通する。これにより、プルアップスイッチ素子32が導通し、プルダウンスイッチ素子35が非導通する。

【0132】

電圧V5が増大したことに起因して、コンデンサ33は放電するので、時点t11から時点t22の間において電圧V1は低下する。かかる放電時の等価回路は図7と同様である。したがって、抵抗31,32が設けられていない場合に比べて、電圧V1の低下を抑制することができる。

【0133】

そして、時点t22において電圧V5がほぼ直流電圧値Vdcと等しい値に至ると、コンデンサ33の放電が停止し、電圧V1が再び高電圧値を採るまで増大する。

【0134】

その後の時点t12において、スイッチ素子11が非導通へと遷移し、スイッチ素子12が導通へと遷移すると、電圧V1が高電圧値から低電圧値へと遷移する。

【0135】

以上のように、電圧V1が低電圧値を採る状態で電圧V5が低減することに起因してコンデンサ33が充電されたとしても、プルダウンスイッチ素子35が導通しているので電圧V1の増大を抑制でき、また電圧V1が高電圧値を採る状態で電圧V5が増大することに起因してコンデンサ33が放電したとしても、プルアップスイッチ素子32が導通しているので、電圧V1の低下を抑制することができる。したがって、上側のスイッチング素子Tx1が意図せずに切り替わることを抑制することができる。

【0136】

なお、プルダウンスイッチ素子35と抵抗34とが設けられていない場合であっても、プルアップスイッチ素子32、或いは更に抵抗31によって、図13の時点t11,t22の間の期間における電圧V1の低下を抑制することができる。したがって、プルダウンスイッチ素子35および抵抗34は必ずしも必要ではない。逆に、プルアップスイッチ素子32と抵抗31とが設けられていない場合であっても、プルダウンスイッチ素子35、或いは更に抵抗34によって図10の時点t5,t6、或いは図13の時点t3,t21の間の期間における電圧V1の増大を抑制できる。したがって、プルアップスイッチ素子32および抵抗31は必ずしも必要ではない。

【符号の説明】

【0137】

10,20 回路

31,34 抵抗

32 プルアップスイッチ素子

33 コンデンサ

35 プルダウンスイッチ素子

DVx1 駆動回路

E1 直流電源

LH,LL 直流線

Px 出力端

Tx1,Tx2 スイッチング素子

【特許請求の範囲】

【請求項1】

第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、出力端(Pu,Pv,Pw,Px)を介して互いに直列に接続される上側のスイッチング素子(Tu1,Tv1,Tw1,Tx1)及び下側のスイッチング素子(Tu2,Tv2,Tw2,Tx2)を有し、前記上側のスイッチング素子が前記第1の電源線側に配置される電力変換装置の、前記上側のスイッチング素子の駆動回路(DVu1,DVv1,DVw1,DVx1)であって、

前記出力端に接続される低電位端と、高電位端とを有する直流電源(E1)と、

前記低電位端と前記高電位端との間で相互に直列に接続される第1素子(11,15)及び第2素子(12,16)を有し、前記第1素子は前記高電位端側に設けられ、前記第2素子は前記低電位端側に設けられる第1回路(10)と、

前記第2素子の両端の電圧(V1)が所定値よりも大きいときに前記上側のスイッチング素子を非導通とし、前記電圧が前記所定値よりも小さいときに前記上側のスイッチング素子を導通させる第2回路(20)と、

前記第1素子と並列に接続され、前記上側のスイッチング素子が非導通である状態で導通し、前記上側のスイッチング素子が導通する状態で非導通するスイッチ素子(32)と

を備え、

前記第1素子及び第2素子は、その両方がスイッチ(11,12)であるか、又は一方がスイッチであって他方が抵抗素子(15,16)である、電力変換装置用の駆動回路。

【請求項2】

第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、出力端(Pu,Pv,Pw,Px)を介して互いに直列に接続される上側のスイッチング素子(Tu1,Tv1,Tw1,Tx1)及び下側のスイッチング素子(Tu2,Tv2,Tw2,Tx2)を有し、前記上側のスイッチング素子が前記第1の電源線側に配置される電力変換装置の、前記上側のスイッチング素子の駆動回路(DVu1,DVv1,DVw1,DVx1)であって、

前記出力端に接続される低電位端と、高電位端とを有する直流電源(E1)と、

前記低電位端と前記高電位端との間で相互に直列に接続される第1素子(11,15)及び第2素子(12,16)を有し、前記第1素子は前記高電位端側に設けられ、前記第2素子は前記低電位端側に設けられる第1回路(10)と、

前記第2素子の両端の電圧(V1)が所定値よりも小さいときに前記上側のスイッチング素子を非導通とし、前記電圧が前記所定値よりも大きいときに前記上側のスイッチング素子を導通させる第2回路(20)と、

前記第1素子と並列に接続され、前記上側のスイッチング素子が導通する状態で導通し、前記上側のスイッチング素子が非導通である状態で非導通するスイッチ素子(32)と

を備え、

前記第1素子及び第2素子は、その両方がスイッチ(11,12)であるか、又は一方がスイッチであって他方が抵抗素子(15,16)である、電力変換装置用の駆動回路。

【請求項3】

第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、出力端(Pu,Pv,Pw,Px)を介して互いに直列に接続される上側のスイッチング素子(Tu1,Tv1,Tw1,Tx1)及び下側のスイッチング素子(Tu2,Tv2,Tw2,Tx2)を有し、前記上側のスイッチング素子が前記第1の電源線側に配置される電力変換装置の、前記上側のスイッチング素子の駆動回路(DVu1,DVv1,DVw1,DVx1)であって、

前記出力端に接続される低電位端と、高電位端とを有する直流電源(E1)と、

前記低電位端と前記高電位端との間で相互に直列に接続される第1素子(11,15)及び第2素子(12,16)を有し、前記第1素子は前記高電位端側に設けられ、前記第2素子は前記低電位端側に設けられる第1回路(10)と、

前記第2素子の両端の電圧(V1)が所定値よりも小さいときに前記上側のスイッチング素子を非導通とし、前記電圧が前記所定値よりも大きいときに前記上側のスイッチング素子を導通させる第2回路(20)と、

前記第2素子と並列に接続され、前記上側のスイッチング素子が非導通する状態で導通し、前記上側のスイッチング素子が導通する状態で非導通するスイッチ素子(35)と、

を備える、電力変換装置用の駆動回路。

【請求項4】

前記第1素子(11,15)と並列に接続され、前記上側のスイッチング素子(Tx1)が導通する状態で導通し、前記上側のスイッチング素子が非導通である状態で非導通する第2のスイッチ素子(32)を更に備える、請求項3に記載の電力変換装置用の駆動回路。

【請求項5】

前記スイッチ素子(32,35)と直列に接続される抵抗(31,34)を備える、請求項1から4の何れか一つに記載の電力変換装置用の駆動回路。

【請求項6】

第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、互いに直列に接続される上側及び下側のスイッチング素子(Tu1,Tv1,Tw1,Tu2,Tv2,Tw2)と、

請求項1から5の何れか一つに記載の駆動回路(DVu1,DVv1,DVw1)と

を備える、電力変換装置。

【請求項1】

第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、出力端(Pu,Pv,Pw,Px)を介して互いに直列に接続される上側のスイッチング素子(Tu1,Tv1,Tw1,Tx1)及び下側のスイッチング素子(Tu2,Tv2,Tw2,Tx2)を有し、前記上側のスイッチング素子が前記第1の電源線側に配置される電力変換装置の、前記上側のスイッチング素子の駆動回路(DVu1,DVv1,DVw1,DVx1)であって、

前記出力端に接続される低電位端と、高電位端とを有する直流電源(E1)と、

前記低電位端と前記高電位端との間で相互に直列に接続される第1素子(11,15)及び第2素子(12,16)を有し、前記第1素子は前記高電位端側に設けられ、前記第2素子は前記低電位端側に設けられる第1回路(10)と、

前記第2素子の両端の電圧(V1)が所定値よりも大きいときに前記上側のスイッチング素子を非導通とし、前記電圧が前記所定値よりも小さいときに前記上側のスイッチング素子を導通させる第2回路(20)と、

前記第1素子と並列に接続され、前記上側のスイッチング素子が非導通である状態で導通し、前記上側のスイッチング素子が導通する状態で非導通するスイッチ素子(32)と

を備え、

前記第1素子及び第2素子は、その両方がスイッチ(11,12)であるか、又は一方がスイッチであって他方が抵抗素子(15,16)である、電力変換装置用の駆動回路。

【請求項2】

第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、出力端(Pu,Pv,Pw,Px)を介して互いに直列に接続される上側のスイッチング素子(Tu1,Tv1,Tw1,Tx1)及び下側のスイッチング素子(Tu2,Tv2,Tw2,Tx2)を有し、前記上側のスイッチング素子が前記第1の電源線側に配置される電力変換装置の、前記上側のスイッチング素子の駆動回路(DVu1,DVv1,DVw1,DVx1)であって、

前記出力端に接続される低電位端と、高電位端とを有する直流電源(E1)と、

前記低電位端と前記高電位端との間で相互に直列に接続される第1素子(11,15)及び第2素子(12,16)を有し、前記第1素子は前記高電位端側に設けられ、前記第2素子は前記低電位端側に設けられる第1回路(10)と、

前記第2素子の両端の電圧(V1)が所定値よりも小さいときに前記上側のスイッチング素子を非導通とし、前記電圧が前記所定値よりも大きいときに前記上側のスイッチング素子を導通させる第2回路(20)と、

前記第1素子と並列に接続され、前記上側のスイッチング素子が導通する状態で導通し、前記上側のスイッチング素子が非導通である状態で非導通するスイッチ素子(32)と

を備え、

前記第1素子及び第2素子は、その両方がスイッチ(11,12)であるか、又は一方がスイッチであって他方が抵抗素子(15,16)である、電力変換装置用の駆動回路。

【請求項3】

第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、出力端(Pu,Pv,Pw,Px)を介して互いに直列に接続される上側のスイッチング素子(Tu1,Tv1,Tw1,Tx1)及び下側のスイッチング素子(Tu2,Tv2,Tw2,Tx2)を有し、前記上側のスイッチング素子が前記第1の電源線側に配置される電力変換装置の、前記上側のスイッチング素子の駆動回路(DVu1,DVv1,DVw1,DVx1)であって、

前記出力端に接続される低電位端と、高電位端とを有する直流電源(E1)と、

前記低電位端と前記高電位端との間で相互に直列に接続される第1素子(11,15)及び第2素子(12,16)を有し、前記第1素子は前記高電位端側に設けられ、前記第2素子は前記低電位端側に設けられる第1回路(10)と、

前記第2素子の両端の電圧(V1)が所定値よりも小さいときに前記上側のスイッチング素子を非導通とし、前記電圧が前記所定値よりも大きいときに前記上側のスイッチング素子を導通させる第2回路(20)と、

前記第2素子と並列に接続され、前記上側のスイッチング素子が非導通する状態で導通し、前記上側のスイッチング素子が導通する状態で非導通するスイッチ素子(35)と、

を備える、電力変換装置用の駆動回路。

【請求項4】

前記第1素子(11,15)と並列に接続され、前記上側のスイッチング素子(Tx1)が導通する状態で導通し、前記上側のスイッチング素子が非導通である状態で非導通する第2のスイッチ素子(32)を更に備える、請求項3に記載の電力変換装置用の駆動回路。

【請求項5】

前記スイッチ素子(32,35)と直列に接続される抵抗(31,34)を備える、請求項1から4の何れか一つに記載の電力変換装置用の駆動回路。

【請求項6】

第1の直流線(LH)と、前記第1の直流線よりも低い電位が印加される第2の直流線(LL)との間で、互いに直列に接続される上側及び下側のスイッチング素子(Tu1,Tv1,Tw1,Tu2,Tv2,Tw2)と、

請求項1から5の何れか一つに記載の駆動回路(DVu1,DVv1,DVw1)と

を備える、電力変換装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2013−34300(P2013−34300A)

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願番号】特願2011−168906(P2011−168906)

【出願日】平成23年8月2日(2011.8.2)

【出願人】(000002853)ダイキン工業株式会社 (7,604)

【Fターム(参考)】

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願日】平成23年8月2日(2011.8.2)

【出願人】(000002853)ダイキン工業株式会社 (7,604)

【Fターム(参考)】

[ Back to top ]