電力変換装置

【課題】ダイオードリカバリによるサージ電圧を抑制すると共に、半導体スイッチング素子のターンオン時の損失増加を抑えることにより、電力変換効率の低下を抑えることが可能な電力変換装置を提供する。

【解決手段】ゲート抵抗で第1半導体スイッチング素子のスイッチング速度を決定し、第1半導体スイッチング素子を駆動する第1のゲート駆動回路7と、前記半導体スイッチング素子に制御パルスを供給する制御パルス発生回路12の出力端に、第2半導体スイッチング素子のゲートの充電開始から所定の時間後にオンするスイッチ素子であるPチャネル型のMOS-FET15とツェナーダイオード16との並列回路を直列に接続し、更に並列回路の出力端をゲート抵抗17を介して第2半導体スイッチング素子のゲート端子に接続し、第2半導体スイッチング素子を駆動する第2のゲート駆動回路8とを備える。

【解決手段】ゲート抵抗で第1半導体スイッチング素子のスイッチング速度を決定し、第1半導体スイッチング素子を駆動する第1のゲート駆動回路7と、前記半導体スイッチング素子に制御パルスを供給する制御パルス発生回路12の出力端に、第2半導体スイッチング素子のゲートの充電開始から所定の時間後にオンするスイッチ素子であるPチャネル型のMOS-FET15とツェナーダイオード16との並列回路を直列に接続し、更に並列回路の出力端をゲート抵抗17を介して第2半導体スイッチング素子のゲート端子に接続し、第2半導体スイッチング素子を駆動する第2のゲート駆動回路8とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体スイッチング素子を用いた電力変換装置、特にその半導体スイッチング素子のゲート駆動回路に関するものである。

【背景技術】

【0002】

半導体スイッチング素子を用いて構成される電力変換装置では、半導体スイッチング素子のスイッチングの際にサージ電圧が発生する。スイッチングする際に電流が変化率di/dtで増減する場合、配線自身が持つ浮遊インダクタンスLに対して誘導電圧(L・di/dt)がスパイク状に発生する。半導体スイッチング素子のスイッチング速度が高速化すると電流変化率が大きくなるため、発生するサージ電圧が高くなり破壊に至るケースもある。このため、サージ電圧抑制のために、各種のスナバ技術、インダクタンス低減技術及び半導体スイッチング素子のゲート駆動方法が考案されている(例えば、特許文献1参照)。

【0003】

【特許文献1】特開平3−63457号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

パルス幅変調方式(以下PWM)インバータ等の電力変換装置は、2個の半導体スイッチング素子を直列に接続したブリッジ回路を持ち、負荷電流が連続モードで流れている場合、半導体スイッチング素子に逆並列に接続したダイオードによる還流モードで動作させることは非常に多い。しかしこの還流モードから復帰する際の逆側半導体スイッチング素子のターンオン時に、半導体スイッチング素子に逆並列に接続したダイオードで発生するダイオードリカバリにより電圧変化率の高い過大なサージ電圧が発生する。このサージ電圧の抑制のために配線インダクタンスを小さくする方法があるが、回路の構成次第で限界がある。よってダイオードリカバリによるサージ電圧を抑制するにはオンする側の半導体素子のターンオン速度を遅くしリカバリ電流を抑えることでサージを抑制できるが、単純にゲート抵抗の値を高くしスイッチングを遅くする方法ではスイッチング時の損失が増加する。

【0005】

本発明は、ダイオードリカバリによるサージ電圧を抑制すると共に、半導体スイッチング素子のターンオン時の損失増加を最小限に抑えることにより、電力変換効率の低下を抑えることが可能な電力変換装置を提供することを目的とするものである。

【課題を解決するための手段】

【0006】

本発明は、逆並列にダイオードが接続された一対の第1半導体スイッチング素子を直列接続し、出力極性が切り替わるときに前記第1半導体スイッチング素子をスイッチングする出力極性固定アームと、逆並列にダイオードが接続された一対の第2半導体スイッチング素子を直列接続し、前記第2半導体スイッチング素子を常時PWMスイッチングし出力値を調整するPWMスイッチングアームとから構成された単相のフルブリッジインバータを備えた電力変換装置において、ゲート抵抗で前記第1半導体スイッチング素子のスイッチング速度を決定し、前記第1半導体スイッチング素子を駆動する第1のゲート駆動回路と、前記第2半導体スイッチング素子にゲート制御パルスを供給する制御パルス発生回路の出力端に、前記第2半導体スイッチング素子のゲートの充電開始から所定の時間後にオンするスイッチ素子とツェナーダイオードまたは抵抗との並列回路を直列に接続し、更に前記並列回路の出力端をゲート抵抗を介して前記第2半導体スイッチング素子のゲート端子に接続し、前記第2半導体スイッチング素子を駆動する第2のゲート駆動回路とを備えたものである。

【発明の効果】

【0007】

本発明の電力変換装置によれば、リカバリ電流を小さくしてリカバリサージを抑えることが可能であり、またリカバリ終了後はオン速度が速くなるためターンオンに伴い発生する半導体スイッチング素子の損失の増加を抑え、またターンオフ速度がゲート抵抗のみで決定されるのでターンオフロスは変化しないため、電力変換効率の低下を抑えることができる。

【発明を実施するための最良の形態】

【0008】

実施の形態1.

以下、本発明の実施の形態1による電力変換装置について説明する。

図1は、本発明による電力変換装置の基本構成を示すブロック回路図である。この電力変換装置は、ゲート駆動回路(第1のゲート駆動回路)7により制御される一対の第1半導体スイッチング素子Qa及びQbで構成され、電力変換装置の出力の正負が切り替わるときのみスイッチングする出力極性固定アーム5と、ゲート駆動回路(第2のゲート駆動回路)8により制御される一対の第2半導体スイッチング素子Qc及びQdで構成され、常にPWMスイッチングしているPWMスイッチングアーム6とを有し、直流電源1から得られる直流電力を交流電力に変換し、出力フィルタ9を通して、電力系統に代表される交流負荷10に供給する単相のフルブリッジインバータ100として構成されている。なお、PWMスイッチングアーム6は、PWMスイッチングを行い電圧又は電流の出力値を調整する。

【0009】

本電力変換装置で用いる各半導体スイッチング素子Qa〜QdはNチャネル型のMOS-FETであり、そのMOS-FETには逆並列にフリーホイールダイオード(以下FWDという)が接続されている。

また本電力変換装置には、図1のように直流母線のコンデンサ2から各アームまでの間に、その配線による浮遊インダクタンス3及び4が存在している。実際には他の配線部にもインダクタンスが存在するが、その浮遊インダクタンスの大きさは上述の浮遊インダクタンス3及び4より十分小さいため説明を省略する。

【0010】

本発明による電力変換装置は、次のように動作する。

インバータ100が交流負荷10に対して正極性の交流を出力する場合、出力極性固定アーム5の半導体スイッチング素子Qbをオンさせ、半導体スイッチング素子Qc及びQdをPWMにてスイッチングし、所定の電圧を出力する。同様に負電圧を出力する場合は半導体スイッチング素子Qaをオンさせ、半導体スイッチング素子Qc及びQdをPWMにてスイッチングし所定の電圧を出力する。この動作にてインバータは直流電力を交流電力に変換している。

【0011】

次にダイオードリカバリによりスイッチング素子に発生するサージ電圧について説明する。

正極性の交流を出力する場合、半導体スイッチング素子Qcがオフしている間は半導体スイッチング素子Qdもしくは逆並列に接続されているフリーホイールダイオード(以下FWD)とオン状態である半導体スイッチング素子Qbを通り還流モードで電流が流れる。ブリッジされている各アームの一対の半導体スイッチング素子間にはスイッチングの際、短絡が生じないようデッドタイムと呼ばれる短絡防止期間が設けられており、その期間では各アームの両素子は共にオフしているため、半導体スイッチング素子Qcがオンする前には必ずFWDを電流が流れている。よって半導体スイッチング素子QdのFWDにはダイオードリカバリが発生し、そのリカバリ電流は直流母線を半導体スイッチング素子QcとFWDで短絡する経路で流れる短絡電流となる。半導体スイッチング素子Qdのドレイン・ソース端子間には図2に示されるようなサージ電圧Vsg1が発生し、このサージ電圧は非常に高い電圧変化率(dV/dt)及びピーク値であることが多い。

同様にインバータ100が負極性の交流を出力する場合、半導体スイッチング素子Qdがオフしている間は半導体スイッチング素子QcもしくはFWDと半導体スイッチング素子Qaを通り還流モードで電流が流れる。よって半導体スイッチング素子Qcには図2のようなダイオードリカバリによるサージ電圧Vsg1が発生する。

【0012】

図2に示されたダイオードリカバリにより発生するサージ電圧Vsg1は次の式(1)で求められる。

Vsg1=L・d(irr)/dt・・・・・(1)

但し、irrはリカバリ電流である。

式(1)中のLはモジュール内部の浮遊インダクタンス3及び4の総和となるインダクタンス値である。

浮遊のインダクタンス3及び4が非常に大きく、発生するサージ電圧がその母線電圧Vddに対して無視できない大きさとなるような場合、そのサージ電圧は素子定格を超え破壊に至る結果となる。特にMOS-FETの場合、そのMOS-FETがアバランシェ耐量保証品であっても、通常スイッチングであるターンオフにより自己に発生するサージに関してはアバランシェ耐量保証されているが、自己のターンオフ以外の原因で発生するドレイン・ソース間の電圧変動に対しては、アバランシェ耐量による保証は難しく、破壊が起こり易いためダイオードリカバリサージの抑制が必要である。

式(1)より、サージ電圧を下げるには、浮遊インダクタンスLを小さくする、もしくは電流変化率d(irr)/dtを下げる必要がある。しかし、浮遊インダクタンスを小さくすることは回路の構成次第で限界がある。よってダイオードリカバリによるサージ電圧を抑制するにはオンする側の半導体素子のターンオン速度を遅くしリカバリ電流を抑えることでサージを抑制できるが、ゲート抵抗の値を高くしスイッチングを遅くする方法では、ゲートの充電の全時間が長くなりスイッチング時の損失が増加する。

【0013】

本実施の形態1による電力変換装置は、このような問題を解決するため、PWMスイッチングアーム6を形成する半導体スイッチング素子Qc及びQdのゲート駆動回路8として、図3のようなゲート駆動回路を備えたものである。

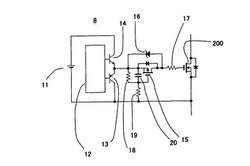

このゲート駆動回路8は、ゲート駆動用直流電源11に逆直列接続された相補のトランジスタ13とトランジスタ14を有し、これらのトランジスタ13,14のゲートに制御パルス発生回路12からのゲート制御パルスを供給して、トランジスタ13のエミッタ・コレクタ間にゲート駆動電圧Vsを出力し、このゲート駆動電圧Vsを、スイッチ素子であるPチャネル型のMOS-FET15とツェナーダイオード16との並列回路及び主回路用半導体素子200(例えば半導体スイッチング素子Qc)のゲートのスイッチング速度を定めるゲート抵抗17を介して主回路用半導体素子200のゲートに供給する。

また、トランジスタ13のエミッタ・コレクタ間には抵抗18,19が接続され、その中点がMOS-FET15のゲートに接続される共に、抵抗19と直列に、かつMOS-FET15のゲート・ソース間にコンデンサ20が接続されている。

【0014】

ゲート駆動回路8は、主回路用半導体素子200がターンオンするとき、まずトランジスタ14がオンして主回路用半導体素子200にゲート駆動電圧Vsを供給しようとするが、Pチャネル型のMOS-FET15がオフしているためツェナーダイオード16を通して電流を流すため、ゲート駆動電圧Vsからツェナーダイオード16のツェナー電圧を引いた電圧で主回路用半導体素子200のゲートを駆動することになる。

またその間には、抵抗19を通じコンデンサ20が充電される。Pチャネル型のMOS-FET15は、そのソースとゲート間の電圧差がその素子のゲート閾値電圧を超えた場合にオンするので、抵抗19とコンデンサ20によりトランジスタ14がオンしてからMOS-FET15がオンするまでの遅延時間を設定することが可能である。この設定する遅延時間については、主回路用半導体素子200のゲートの充電開始からゲート閾値電圧Vthまで達する時間とダイオードのリカバリ期間の合計だけあれば十分である。

MOS-FET15がオンすれば、ゲート駆動電圧Vsとゲート抵抗17で決定される速度で充電されるため、主回路用半導体素子200のターンオンを速くすることが可能であり、スイッチング時に生じる損失の上昇を抑えることが可能となる。実際にはゲート抵抗17とMOS-FET15のオン抵抗の合計値で充電速度が決定されるが、MOS-FET15のオン抵抗は他の抵抗より十分小さいものとし説明では省略する。

【0015】

図4は、本実施の形態1における上述のゲート駆動回路8を用いた場合のゲート電圧の立ち上がり波形32と、上述のゲート駆動回路8のゲート抵抗17と同じ値のゲート抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形30と、ゲート駆動回路8を用いた場合と同程度にリカバリサージを抑制可能なゲート抵抗17よりも大きい値の抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形31を示している。

またターンオフについてはゲート抵抗17、ツェナーダイオード16もしくはMOS-FET15内蔵のダイオード、トランジスタ13を流れる電流ループで主回路用半導体素子200のゲートが放電されるためスイッチング速度は変わらず、ターンオフ時の損失は変化しない。

【0016】

ここで図3中の抵抗18は、MOS-FET15のゲート・ソース間容量放電用の抵抗であり抵抗19より十分大きい値である。また図3の回路ではコンデンサ20を挿入しているが、MOS-FET15はゲート・ソース間容量が存在しているので、その容量と抵抗19のみで遅延時間を設定することも可能であり、MOS-FET15のゲート・ソース間容量の大きさにより、コンデンサ20挿入の有無を決定すればよい。電子回路においては、抵抗が大きくなりすぎるとノイズが重畳しやすくなるため、本実施の形態では抵抗19の値が大きくならないよう、別途コンデンサ20を挿入して遅延時間を決定している。

【0017】

一方、出力極性固定アーム5の半導体スイッチング素子Qa及びQbのゲート駆動回路7には、この図3の回路は用いずにゲート抵抗の値を大きくするのみで対応する。出力極性固定アーム5は、電力変換装置の正負の出力極性が切り替わるときのみスイッチングするので、このアームで発生するスイッチングロスは、高周波でPWMスイッチングしているPWMスイッチングアーム6のスイッチングロスに比べて無視できる大きさであり、電力変換効率にもたらす影響は非常に小さい。よって、ゲート駆動回路7において、半導体スイッチング素子Qa,Qbのスイッチング速度を決定する部品をゲート抵抗のみとし、部品点数を少なくすることで、電力変換装置の小型化、コストの低下が可能である。

【0018】

以上のように、本発明の実施の形態1による電力変換装置は、逆並列にダイオードが接続された一対の第1半導体スイッチング素子Qa,Qbを直列接続し、出力極性が切り替わるときに半導体スイッチング素子をスイッチングする出力極性固定アーム5と、逆並列にダイオードが接続された一対の第2半導体スイッチング素子Qc,Qdを直列接続し、前記半導体スイッチング素子を常時PWMスイッチングし出力値を調整するPWMスイッチングアーム6とから構成された単相のフルブリッジインバータ100を備えた電力変換装置において、ゲート抵抗で第1半導体スイッチング素子のスイッチング速度を決定し、前記第1半導体スイッチング素子を駆動する第1のゲート駆動回路7と、前記半導体スイッチング素子に制御パルスを供給する制御パルス発生回路12の出力端に、第2半導体スイッチング素子のゲートの充電開始から所定の時間後にオンするスイッチ素子であるPチャネル型のMOS-FET15とツェナーダイオード16との並列回路を直列に接続し、更に並列回路の出力端をゲート抵抗17を介して第2半導体スイッチング素子のゲート端子に接続し、前記第2半導体スイッチング素子を駆動する第2のゲート駆動回路8とを備えているので、リカバリ電流が流れる期間ではターンオンする半導体スイッチング素子のゲート電圧は低くなりドレイン電流が制限されるため、短絡経路であるリカバリ電流を小さく抑えることが可能となり、またリカバリ終了後はオン速度が速くなるためターンオンに伴い発生する半導体スイッチング素子の損失の増加を最小限に抑え、またターンオフ速度がゲート抵抗のみで決定されるのでターンオフロスは変化しないため、電力変換効率の低下を抑えることができる。

【0019】

実施の形態2.

以下、本発明の実施の形態2による電力変換装置ついて説明する。

本実施の形態2は、図1の電力変換装置にて、実施の形態1と同じくPWMスイッチングアーム6のゲート駆動回路8を改良したものである。

図5は本実施の形態2によるゲート駆動回路8の回路図であり、ゲート駆動電圧Vsの出力段である相補のトランジスタ13とトランジスタ14のエミッタに、Pチャネル型のMOS-FET15と抵抗21との並列回路を介して主回路用半導体素子200(例えば半導体スイッチング素子Qc)のゲート抵抗17を接続している。

【0020】

ゲート駆動回路8は、主回路用半導体素子200がターンオンするとき、まずトランジスタ14がオンしてゲートにゲート駆動電圧Vsを供給しようとするが、MOS-FET15がオフしているため抵抗21を通して電流を流すため、ゲートの充電電流を決定する抵抗値は、ゲート抵抗17と追加された抵抗21の合計値となる。

またその間には、抵抗19を通じコンデンサ20が充電される。Pチャネル型のMOS-FET15は、そのソースとゲート間の電圧差がその素子のゲート閾値電圧を超えた場合にオンするので、抵抗19とコンデンサ20によりトランジスタ14がオンしてからMOS-FET15がオンするまでの遅延時間を設定することが可能である。この設定する遅延時間については、主回路用半導体素子200のゲートの充電開始からゲート閾値電圧Vthまで達する時間とダイオードのリカバリ期間の合計だけあれば十分である。

MOS-FET15がオンすれば、ゲートの充電電流はMOS-FET15を流れるためゲート抵抗17で決定される速度で充電されるため、主回路用半導体素子200のターンオンを速くすることが可能であり、スイッチング時に生じる損失の増加を抑えることが可能となる。実際にはゲート抵抗17とMOS-FET15のオン抵抗の合計値で充電速度が決定するが、MOS-FET15のオン抵抗はゲート抵抗より十分小さいものとし説明では省略する。

【0021】

図6は、本実施の形態2における上述のゲート駆動回路8を用いた場合の主回路用半導体素子200のゲート電圧の立ち上がり波形33と、上述のゲート駆動回路8のゲート抵抗17と同じ値のゲート抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形30と、ゲート駆動回路8を用いた場合と同程度にリカバリサージを抑制可能なゲート抵抗17よりも大きい値の抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形31を示している。

またターンオフについてはゲート抵抗17、MOS-FET15内蔵のダイオード、トランジスタ13を通る電流ループで主回路用半導体素子200のゲートが放電されるためスイッチング速度は変わらず、ターンオフ時の損失は変化しない。

【0022】

本実施の形態2によるゲート駆動回路8を用いれば、実施の形態1と同様に、リカバリ電流が流れる期間ではターンオンする素子のゲート電圧を低くしドレイン電流を制限できるため、短絡経路であるリカバリ電流を小さく抑えることが可能となるので、電流変化率が低下し、サージ電圧を低下させることができる。

【0023】

実施の形態3.

図7は、本実施の形態3によるゲート駆動回路8を示すもので、実施の形態2における抵抗21に並列にコンデンサ22を挿入したものである。

実施の形態2ではゲート抵抗を大きくしたのみであり、主回路用半導体素子200のゲート閾値電圧Vthまでゲートが充電されるまでの時間が長くなり、トータルでのスイッチングに要する時間が長くなるが、本実施の形態3では、抵抗21に並列にコンデンサ22を挿入したことで、主回路用半導体素子200のゲートがゲート閾値電圧Vth以下の期間では、コンデンサ22に電流を流して抵抗21はスルーさせることができる。

そしてコンデンサ22が所定の電圧まで充電されれば、コンデンサ22には電流が流れなくなり、その後は抵抗21とゲート抵抗17により決定される充電電流でゲートが充電されることになる。よってゲートの総充電時間が短縮される。

【0024】

抵抗21が十分大きいとすれば、初期充電にて、コンデンサ22の静電容量C27と主回路用半導体素子200のゲート・ソース間容量CGSの比から近似の式(2)で示されるような主回路用半導体素子200のゲート・ソース間電圧値VGSaが充電されるので、この電圧値が最低でもその素子のゲート閾値電圧Vthになるようにコンデンサ22の静電容量を決定すればよい。ゲート駆動電圧はVs[V]である。

VGSa≒Vs×{C27÷(C27+CGS)} [V]・・・・・(2)

実施の形態2と同様にMOS-FET15がオンすれば、実施の形態2のようにゲート抵抗17のみでゲートが駆動されるので、本実施の形態3においても、実施の形態2と同様の効果を得ることが可能である。

【0025】

図8は、本実施の形態3における上述のゲート駆動回路8を用いた場合の主回路用半導体素子200のゲート電圧の立ち上がり波形34と、上述のゲート駆動回路8のゲート抵抗17と同じ値のゲート抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形30と、ゲート駆動回路8を用いた場合と同程度にリカバリサージを抑制可能なゲート抵抗17よりも大きい値の抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形31を示している。

抵抗21を十分に大きくすれば、リカバリ期間において図8の波形34のようにオンさせた状態のままゲート電圧の上昇を抑え、ほぼ一定の値に保つことが可能であるので、サージ抑制効果は実施の形態2よりも高いものになる。

またMOS-FET15がオンするとコンデンサ22を短絡する経路となるので、ゲート抵抗の値を図9のように抵抗23、ゲート抵抗17に分割し、抵抗23をMOS-FET15に直列接続して、短絡電流が過大にならないように抑えるようにしても良い。このときMOS-FET15がオンしてからは、抵抗21と抵抗23の並列抵抗値とゲート抵抗17の合計値により主回路用半導体素子200のゲートの充電速度が決定する。

【0026】

実施の形態4.

本実施の形態4は、PWMスイッチングアーム6のゲート駆動回路8において、実施の形態1で用いたPチャネル型のMOS-FET15に代わり、スイッチ素子であるNチャネル型のMOS-FET24を用いたものである。

図10は本実施の形態4によるゲート駆動回路8である。使用するMOS-FET24はNチャネル型であるので、オンさせるためにはゲート・ソース間の電位差がゲート閾値電圧以上になる必要があるため、遅延時間を設定する抵抗25とコンデンサ26を図10の位置に配置し、コンデンサ26を充電しゲートの電位を上げていくことでスイッチングさせる。トランジスタ14がオンした直後は、ゲート駆動電圧Vsからツェナーダイオード16のツェナー電圧を引いた電圧だけMOS-FET24のソース電位の方がゲートよりも高くなっているので、遅延時間を決定する際にはこの電位差分を考慮し、実施の形態1に用いた抵抗23よりも小さい値にする必要がある。なお、抵抗27はMOS-FET24のゲート・ソース間容量放電用の抵抗である。

【0027】

本実施の形態4のゲート駆動回路8ではMOS-FET24がオンした場合ソースの電位がゲート駆動電圧の電位まで上昇するためMOS-FET24はオフする。オフすることによりまたソースの電位が下がるため、MOS-FET24は再びオンするというようにスイッチングを繰り返し行う。そのスイッチングを繰り返す期間に、時間は短いがゲート駆動電圧Vsによる大きい充電電流がスイッチング毎に流れるので、同程度にサージ電圧を抑制可能な大きな抵抗のみで駆動するよりも速く主回路用半導体素子200のゲート・ソース間電圧が上昇する。但し大電流は上述のように断続的であるため、連続的に高電圧で充電できる実施の形態1よりはゲート電圧の立ち上がりは遅くなる。

【0028】

図11は、本実施の形態4における上述のゲート駆動回路8を用いた場合の主回路用半導体素子200のゲート電圧の立ち上がり波形35と、上述のゲート駆動回路8と同じ値のゲート抵抗17のみで駆動させた場合のゲート電圧の立ち上がり波形30と、ゲート駆動回路8を用いた場合と同程度にリカバリサージを抑制可能なゲート抵抗17よりも大きい値の抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形31を示している。

最初にMOS-FETをオンさせるまでの低ゲート電圧化に関しては問題は無く、ダイオードのリカバリによるサージ抑制の効果は、本実施の形態4においても実施の形態1と同様の効果を得ることが可能である。

また同程度にサージ電圧を抑制可能な大きな抵抗のみのゲート抵抗にて駆動するよりもターンオン時のスイッチングに伴う損失を低下することが可能である。

【0029】

実施の形態5.

図12は本実施の形態5によるゲート駆動回路8を示す回路図で、実施の形態4で示したツェナーダイオード16を抵抗21に変更したものである。

トランジスタ14がオンしてからMOS-FET24が初めにオンするまでは、ゲート抵抗17と抵抗21で決まる充電速度で主回路用半導体素子200のゲートを充電可能であり、ダイオードリカバリによるサージ電圧を抑える効果は実施の形態2と同様の効果を得る。 MOS-FET24が初めにオンしてからの回路の挙動は、本実施の形態5についても、実施の形態4と同様にMOS-FET24がスイッチングを繰り返すことになる。

スイッチングを繰り返す期間に、短時間ではあるが低ゲート抵抗による大きい充電電流がスイッチング毎に流れるので、同程度にサージ電圧を抑制可能な大きな抵抗のみで駆動するよりも速く主回路用半導体素子200のゲート・ソース間電圧が上昇する。但し大電流は上述のように断続的であるため、連続的に高電圧で充電できる実施の形態2よりはゲート電圧の立ち上がりは遅くなる。

【0030】

図13は、本実施の形態5における上述のゲート駆動回路8を用いた場合の主回路用半導体素子200のゲート電圧の立ち上がり波形36と、上述のゲート駆動回路8と同じ値のゲート抵抗17のみで駆動させた場合のゲート電圧の立ち上がり波形30と、ゲート駆動回路8を用いた場合と同程度にリカバリサージを抑制可能なゲート抵抗17よりも大きい値の抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形31を示している。

本実施の形態5についても、実施の形態4と同様に、同程度にサージ電圧を抑制可能な大きな抵抗のみのゲート抵抗にて駆動するよりもスイッチング時の損失を低下することが可能である。

【0031】

実施の形態6.

図14は本実施の形態6によるゲート駆動回路8を示す回路図で、実施の形態5で示した抵抗21にコンデンサ22を並列に接続した回路である。

トランジスタ14がオンしてからMOS-FET24が初めにオンするまでの動作は、実施の形態3で示したゲート駆動回路の動作と同じであるので、ダイオードリカバリによるサージ電圧を抑える効果は実施の形態3と同様の効果を得る。

MOS-FET24が初めにオンしてからの回路の挙動は、本実施の形態6についても、実施の形態4と同様にMOS-FET24がスイッチングを繰り返すことになる。

スイッチングを繰り返す期間に、コンデンサ22は、MOS-FET24がオンするたびに放電するため、MOS-FET24がオフしても、コンデンサ22が充電されるまで抵抗21はスルーされ、ゲート抵抗17の抵抗値で充電速度が決定されるため、実施の形態5よりも充電は高速になる。

【0032】

図15は、本実施の形態6における上述のゲート駆動回路8を用いた場合のゲート電圧の立ち上がり波形37と、上述のゲート駆動回路8と同じ値のゲート抵抗17のみで駆動させた場合のゲート電圧の立ち上がり波形30と、ゲート駆動回路8を用いた場合と同程度にリカバリサージを抑制可能なゲート抵抗17よりも大きい値の抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形31を示している。

本実施の形態6についても実施の形態4及び実施の形態5と同様に、同程度にサージ電圧を抑制可能な大きな抵抗のみのゲート抵抗にて駆動するよりもスイッチング時の損失を低下することが可能である。

【0033】

実施の形態3と同様にMOS-FET24がオンしたときコンデンサ22から短絡電流が流れるので、ゲート抵抗の値を分割して図16のように抵抗23、ゲート抵抗17を配置して、短絡電流が過大にならないように抑えるようにしても良い。このときコンデンサ22の放電電流を制限していることになるので、短いオン期間でのコンデンサ22の電圧の低下量は減少するので、1回のスイッチング毎の主回路用半導体素子200のゲートの充電量は減少する。しかしMOS-FET24のソース電位も上昇しにくいため、MOS-FET24のスイッチング回数が増加し、総充電時間は、短絡させた場合と同程度となる。

【図面の簡単な説明】

【0034】

【図1】本発明の電力変換装置の基本構成を示すブロック回路図である。

【図2】図1の電力変換装置においてダイオードリカバリ時に発生するサージ電圧とリカバリ電流の例を示す波形図である。

【図3】本発明の実施の形態1におけるゲート駆動回路を示す回路図である。

【図4】実施の形態1におけるゲート駆動回路を用いた場合のゲート電圧の立ち上がり波形を示す図である。

【図5】本発明の実施の形態2におけるゲート駆動回路を示す回路図である。

【図6】実施の形態2におけるゲート駆動回路を用いた場合のゲート電圧の立ち上がり波形を示す図である。

【図7】本発明の実施の形態3におけるゲート駆動回路を示す回路図である。

【図8】実施の形態3におけるゲート駆動回路を用いた場合のゲート電圧の立ち上がり波形を示す図である。

【図9】実施の形態3におけるゲート駆動回路の他の例を示す回路図である。

【図10】本発明の実施の形態4におけるゲート駆動回路を示す回路図である。

【図11】実施の形態4におけるゲート駆動回路を用いた場合のゲート電圧の立ち上がり波形を示す図である。

【図12】本発明の実施の形態5におけるゲート駆動回路を示す回路図である。

【図13】実施の形態5におけるゲート駆動回路を用いた場合のゲート電圧の立ち上がり波形を示す図である。

【図14】本発明の実施の形態6におけるゲート駆動回路を示す回路図である。

【図15】実施の形態6におけるゲート駆動回路を用いた場合のゲート電圧の立ち上がり波形を示す図である。

【図16】実施の形態6におけるゲート駆動回路の他の例を示す回路図である。

【符号の説明】

【0035】

1 直流電源、2 コンデンサ、3,4 浮遊インダクタンス、5 出力極性固定アーム、6 PWMスイッチングアーム、7,8 ゲート駆動回路、9 出力フィルタ、10 交流負荷、11 ゲート駆動用直流電源、12 制御パルス発生回路、13,14 トランジスタ、15 Pチャネル型のMOS-FET、16 ツェナーダイオード、17 ゲート抵抗、18,19 抵抗、20 コンデンサ、21抵抗、22 コンデンサ、23 抵抗、24 Nチャネル型のMOS-FET、25 抵抗、26 コンデンサ、27 抵抗、100 単相のフルブリッジインバータ、200 主回路用半導体素子。

【技術分野】

【0001】

本発明は、半導体スイッチング素子を用いた電力変換装置、特にその半導体スイッチング素子のゲート駆動回路に関するものである。

【背景技術】

【0002】

半導体スイッチング素子を用いて構成される電力変換装置では、半導体スイッチング素子のスイッチングの際にサージ電圧が発生する。スイッチングする際に電流が変化率di/dtで増減する場合、配線自身が持つ浮遊インダクタンスLに対して誘導電圧(L・di/dt)がスパイク状に発生する。半導体スイッチング素子のスイッチング速度が高速化すると電流変化率が大きくなるため、発生するサージ電圧が高くなり破壊に至るケースもある。このため、サージ電圧抑制のために、各種のスナバ技術、インダクタンス低減技術及び半導体スイッチング素子のゲート駆動方法が考案されている(例えば、特許文献1参照)。

【0003】

【特許文献1】特開平3−63457号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

パルス幅変調方式(以下PWM)インバータ等の電力変換装置は、2個の半導体スイッチング素子を直列に接続したブリッジ回路を持ち、負荷電流が連続モードで流れている場合、半導体スイッチング素子に逆並列に接続したダイオードによる還流モードで動作させることは非常に多い。しかしこの還流モードから復帰する際の逆側半導体スイッチング素子のターンオン時に、半導体スイッチング素子に逆並列に接続したダイオードで発生するダイオードリカバリにより電圧変化率の高い過大なサージ電圧が発生する。このサージ電圧の抑制のために配線インダクタンスを小さくする方法があるが、回路の構成次第で限界がある。よってダイオードリカバリによるサージ電圧を抑制するにはオンする側の半導体素子のターンオン速度を遅くしリカバリ電流を抑えることでサージを抑制できるが、単純にゲート抵抗の値を高くしスイッチングを遅くする方法ではスイッチング時の損失が増加する。

【0005】

本発明は、ダイオードリカバリによるサージ電圧を抑制すると共に、半導体スイッチング素子のターンオン時の損失増加を最小限に抑えることにより、電力変換効率の低下を抑えることが可能な電力変換装置を提供することを目的とするものである。

【課題を解決するための手段】

【0006】

本発明は、逆並列にダイオードが接続された一対の第1半導体スイッチング素子を直列接続し、出力極性が切り替わるときに前記第1半導体スイッチング素子をスイッチングする出力極性固定アームと、逆並列にダイオードが接続された一対の第2半導体スイッチング素子を直列接続し、前記第2半導体スイッチング素子を常時PWMスイッチングし出力値を調整するPWMスイッチングアームとから構成された単相のフルブリッジインバータを備えた電力変換装置において、ゲート抵抗で前記第1半導体スイッチング素子のスイッチング速度を決定し、前記第1半導体スイッチング素子を駆動する第1のゲート駆動回路と、前記第2半導体スイッチング素子にゲート制御パルスを供給する制御パルス発生回路の出力端に、前記第2半導体スイッチング素子のゲートの充電開始から所定の時間後にオンするスイッチ素子とツェナーダイオードまたは抵抗との並列回路を直列に接続し、更に前記並列回路の出力端をゲート抵抗を介して前記第2半導体スイッチング素子のゲート端子に接続し、前記第2半導体スイッチング素子を駆動する第2のゲート駆動回路とを備えたものである。

【発明の効果】

【0007】

本発明の電力変換装置によれば、リカバリ電流を小さくしてリカバリサージを抑えることが可能であり、またリカバリ終了後はオン速度が速くなるためターンオンに伴い発生する半導体スイッチング素子の損失の増加を抑え、またターンオフ速度がゲート抵抗のみで決定されるのでターンオフロスは変化しないため、電力変換効率の低下を抑えることができる。

【発明を実施するための最良の形態】

【0008】

実施の形態1.

以下、本発明の実施の形態1による電力変換装置について説明する。

図1は、本発明による電力変換装置の基本構成を示すブロック回路図である。この電力変換装置は、ゲート駆動回路(第1のゲート駆動回路)7により制御される一対の第1半導体スイッチング素子Qa及びQbで構成され、電力変換装置の出力の正負が切り替わるときのみスイッチングする出力極性固定アーム5と、ゲート駆動回路(第2のゲート駆動回路)8により制御される一対の第2半導体スイッチング素子Qc及びQdで構成され、常にPWMスイッチングしているPWMスイッチングアーム6とを有し、直流電源1から得られる直流電力を交流電力に変換し、出力フィルタ9を通して、電力系統に代表される交流負荷10に供給する単相のフルブリッジインバータ100として構成されている。なお、PWMスイッチングアーム6は、PWMスイッチングを行い電圧又は電流の出力値を調整する。

【0009】

本電力変換装置で用いる各半導体スイッチング素子Qa〜QdはNチャネル型のMOS-FETであり、そのMOS-FETには逆並列にフリーホイールダイオード(以下FWDという)が接続されている。

また本電力変換装置には、図1のように直流母線のコンデンサ2から各アームまでの間に、その配線による浮遊インダクタンス3及び4が存在している。実際には他の配線部にもインダクタンスが存在するが、その浮遊インダクタンスの大きさは上述の浮遊インダクタンス3及び4より十分小さいため説明を省略する。

【0010】

本発明による電力変換装置は、次のように動作する。

インバータ100が交流負荷10に対して正極性の交流を出力する場合、出力極性固定アーム5の半導体スイッチング素子Qbをオンさせ、半導体スイッチング素子Qc及びQdをPWMにてスイッチングし、所定の電圧を出力する。同様に負電圧を出力する場合は半導体スイッチング素子Qaをオンさせ、半導体スイッチング素子Qc及びQdをPWMにてスイッチングし所定の電圧を出力する。この動作にてインバータは直流電力を交流電力に変換している。

【0011】

次にダイオードリカバリによりスイッチング素子に発生するサージ電圧について説明する。

正極性の交流を出力する場合、半導体スイッチング素子Qcがオフしている間は半導体スイッチング素子Qdもしくは逆並列に接続されているフリーホイールダイオード(以下FWD)とオン状態である半導体スイッチング素子Qbを通り還流モードで電流が流れる。ブリッジされている各アームの一対の半導体スイッチング素子間にはスイッチングの際、短絡が生じないようデッドタイムと呼ばれる短絡防止期間が設けられており、その期間では各アームの両素子は共にオフしているため、半導体スイッチング素子Qcがオンする前には必ずFWDを電流が流れている。よって半導体スイッチング素子QdのFWDにはダイオードリカバリが発生し、そのリカバリ電流は直流母線を半導体スイッチング素子QcとFWDで短絡する経路で流れる短絡電流となる。半導体スイッチング素子Qdのドレイン・ソース端子間には図2に示されるようなサージ電圧Vsg1が発生し、このサージ電圧は非常に高い電圧変化率(dV/dt)及びピーク値であることが多い。

同様にインバータ100が負極性の交流を出力する場合、半導体スイッチング素子Qdがオフしている間は半導体スイッチング素子QcもしくはFWDと半導体スイッチング素子Qaを通り還流モードで電流が流れる。よって半導体スイッチング素子Qcには図2のようなダイオードリカバリによるサージ電圧Vsg1が発生する。

【0012】

図2に示されたダイオードリカバリにより発生するサージ電圧Vsg1は次の式(1)で求められる。

Vsg1=L・d(irr)/dt・・・・・(1)

但し、irrはリカバリ電流である。

式(1)中のLはモジュール内部の浮遊インダクタンス3及び4の総和となるインダクタンス値である。

浮遊のインダクタンス3及び4が非常に大きく、発生するサージ電圧がその母線電圧Vddに対して無視できない大きさとなるような場合、そのサージ電圧は素子定格を超え破壊に至る結果となる。特にMOS-FETの場合、そのMOS-FETがアバランシェ耐量保証品であっても、通常スイッチングであるターンオフにより自己に発生するサージに関してはアバランシェ耐量保証されているが、自己のターンオフ以外の原因で発生するドレイン・ソース間の電圧変動に対しては、アバランシェ耐量による保証は難しく、破壊が起こり易いためダイオードリカバリサージの抑制が必要である。

式(1)より、サージ電圧を下げるには、浮遊インダクタンスLを小さくする、もしくは電流変化率d(irr)/dtを下げる必要がある。しかし、浮遊インダクタンスを小さくすることは回路の構成次第で限界がある。よってダイオードリカバリによるサージ電圧を抑制するにはオンする側の半導体素子のターンオン速度を遅くしリカバリ電流を抑えることでサージを抑制できるが、ゲート抵抗の値を高くしスイッチングを遅くする方法では、ゲートの充電の全時間が長くなりスイッチング時の損失が増加する。

【0013】

本実施の形態1による電力変換装置は、このような問題を解決するため、PWMスイッチングアーム6を形成する半導体スイッチング素子Qc及びQdのゲート駆動回路8として、図3のようなゲート駆動回路を備えたものである。

このゲート駆動回路8は、ゲート駆動用直流電源11に逆直列接続された相補のトランジスタ13とトランジスタ14を有し、これらのトランジスタ13,14のゲートに制御パルス発生回路12からのゲート制御パルスを供給して、トランジスタ13のエミッタ・コレクタ間にゲート駆動電圧Vsを出力し、このゲート駆動電圧Vsを、スイッチ素子であるPチャネル型のMOS-FET15とツェナーダイオード16との並列回路及び主回路用半導体素子200(例えば半導体スイッチング素子Qc)のゲートのスイッチング速度を定めるゲート抵抗17を介して主回路用半導体素子200のゲートに供給する。

また、トランジスタ13のエミッタ・コレクタ間には抵抗18,19が接続され、その中点がMOS-FET15のゲートに接続される共に、抵抗19と直列に、かつMOS-FET15のゲート・ソース間にコンデンサ20が接続されている。

【0014】

ゲート駆動回路8は、主回路用半導体素子200がターンオンするとき、まずトランジスタ14がオンして主回路用半導体素子200にゲート駆動電圧Vsを供給しようとするが、Pチャネル型のMOS-FET15がオフしているためツェナーダイオード16を通して電流を流すため、ゲート駆動電圧Vsからツェナーダイオード16のツェナー電圧を引いた電圧で主回路用半導体素子200のゲートを駆動することになる。

またその間には、抵抗19を通じコンデンサ20が充電される。Pチャネル型のMOS-FET15は、そのソースとゲート間の電圧差がその素子のゲート閾値電圧を超えた場合にオンするので、抵抗19とコンデンサ20によりトランジスタ14がオンしてからMOS-FET15がオンするまでの遅延時間を設定することが可能である。この設定する遅延時間については、主回路用半導体素子200のゲートの充電開始からゲート閾値電圧Vthまで達する時間とダイオードのリカバリ期間の合計だけあれば十分である。

MOS-FET15がオンすれば、ゲート駆動電圧Vsとゲート抵抗17で決定される速度で充電されるため、主回路用半導体素子200のターンオンを速くすることが可能であり、スイッチング時に生じる損失の上昇を抑えることが可能となる。実際にはゲート抵抗17とMOS-FET15のオン抵抗の合計値で充電速度が決定されるが、MOS-FET15のオン抵抗は他の抵抗より十分小さいものとし説明では省略する。

【0015】

図4は、本実施の形態1における上述のゲート駆動回路8を用いた場合のゲート電圧の立ち上がり波形32と、上述のゲート駆動回路8のゲート抵抗17と同じ値のゲート抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形30と、ゲート駆動回路8を用いた場合と同程度にリカバリサージを抑制可能なゲート抵抗17よりも大きい値の抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形31を示している。

またターンオフについてはゲート抵抗17、ツェナーダイオード16もしくはMOS-FET15内蔵のダイオード、トランジスタ13を流れる電流ループで主回路用半導体素子200のゲートが放電されるためスイッチング速度は変わらず、ターンオフ時の損失は変化しない。

【0016】

ここで図3中の抵抗18は、MOS-FET15のゲート・ソース間容量放電用の抵抗であり抵抗19より十分大きい値である。また図3の回路ではコンデンサ20を挿入しているが、MOS-FET15はゲート・ソース間容量が存在しているので、その容量と抵抗19のみで遅延時間を設定することも可能であり、MOS-FET15のゲート・ソース間容量の大きさにより、コンデンサ20挿入の有無を決定すればよい。電子回路においては、抵抗が大きくなりすぎるとノイズが重畳しやすくなるため、本実施の形態では抵抗19の値が大きくならないよう、別途コンデンサ20を挿入して遅延時間を決定している。

【0017】

一方、出力極性固定アーム5の半導体スイッチング素子Qa及びQbのゲート駆動回路7には、この図3の回路は用いずにゲート抵抗の値を大きくするのみで対応する。出力極性固定アーム5は、電力変換装置の正負の出力極性が切り替わるときのみスイッチングするので、このアームで発生するスイッチングロスは、高周波でPWMスイッチングしているPWMスイッチングアーム6のスイッチングロスに比べて無視できる大きさであり、電力変換効率にもたらす影響は非常に小さい。よって、ゲート駆動回路7において、半導体スイッチング素子Qa,Qbのスイッチング速度を決定する部品をゲート抵抗のみとし、部品点数を少なくすることで、電力変換装置の小型化、コストの低下が可能である。

【0018】

以上のように、本発明の実施の形態1による電力変換装置は、逆並列にダイオードが接続された一対の第1半導体スイッチング素子Qa,Qbを直列接続し、出力極性が切り替わるときに半導体スイッチング素子をスイッチングする出力極性固定アーム5と、逆並列にダイオードが接続された一対の第2半導体スイッチング素子Qc,Qdを直列接続し、前記半導体スイッチング素子を常時PWMスイッチングし出力値を調整するPWMスイッチングアーム6とから構成された単相のフルブリッジインバータ100を備えた電力変換装置において、ゲート抵抗で第1半導体スイッチング素子のスイッチング速度を決定し、前記第1半導体スイッチング素子を駆動する第1のゲート駆動回路7と、前記半導体スイッチング素子に制御パルスを供給する制御パルス発生回路12の出力端に、第2半導体スイッチング素子のゲートの充電開始から所定の時間後にオンするスイッチ素子であるPチャネル型のMOS-FET15とツェナーダイオード16との並列回路を直列に接続し、更に並列回路の出力端をゲート抵抗17を介して第2半導体スイッチング素子のゲート端子に接続し、前記第2半導体スイッチング素子を駆動する第2のゲート駆動回路8とを備えているので、リカバリ電流が流れる期間ではターンオンする半導体スイッチング素子のゲート電圧は低くなりドレイン電流が制限されるため、短絡経路であるリカバリ電流を小さく抑えることが可能となり、またリカバリ終了後はオン速度が速くなるためターンオンに伴い発生する半導体スイッチング素子の損失の増加を最小限に抑え、またターンオフ速度がゲート抵抗のみで決定されるのでターンオフロスは変化しないため、電力変換効率の低下を抑えることができる。

【0019】

実施の形態2.

以下、本発明の実施の形態2による電力変換装置ついて説明する。

本実施の形態2は、図1の電力変換装置にて、実施の形態1と同じくPWMスイッチングアーム6のゲート駆動回路8を改良したものである。

図5は本実施の形態2によるゲート駆動回路8の回路図であり、ゲート駆動電圧Vsの出力段である相補のトランジスタ13とトランジスタ14のエミッタに、Pチャネル型のMOS-FET15と抵抗21との並列回路を介して主回路用半導体素子200(例えば半導体スイッチング素子Qc)のゲート抵抗17を接続している。

【0020】

ゲート駆動回路8は、主回路用半導体素子200がターンオンするとき、まずトランジスタ14がオンしてゲートにゲート駆動電圧Vsを供給しようとするが、MOS-FET15がオフしているため抵抗21を通して電流を流すため、ゲートの充電電流を決定する抵抗値は、ゲート抵抗17と追加された抵抗21の合計値となる。

またその間には、抵抗19を通じコンデンサ20が充電される。Pチャネル型のMOS-FET15は、そのソースとゲート間の電圧差がその素子のゲート閾値電圧を超えた場合にオンするので、抵抗19とコンデンサ20によりトランジスタ14がオンしてからMOS-FET15がオンするまでの遅延時間を設定することが可能である。この設定する遅延時間については、主回路用半導体素子200のゲートの充電開始からゲート閾値電圧Vthまで達する時間とダイオードのリカバリ期間の合計だけあれば十分である。

MOS-FET15がオンすれば、ゲートの充電電流はMOS-FET15を流れるためゲート抵抗17で決定される速度で充電されるため、主回路用半導体素子200のターンオンを速くすることが可能であり、スイッチング時に生じる損失の増加を抑えることが可能となる。実際にはゲート抵抗17とMOS-FET15のオン抵抗の合計値で充電速度が決定するが、MOS-FET15のオン抵抗はゲート抵抗より十分小さいものとし説明では省略する。

【0021】

図6は、本実施の形態2における上述のゲート駆動回路8を用いた場合の主回路用半導体素子200のゲート電圧の立ち上がり波形33と、上述のゲート駆動回路8のゲート抵抗17と同じ値のゲート抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形30と、ゲート駆動回路8を用いた場合と同程度にリカバリサージを抑制可能なゲート抵抗17よりも大きい値の抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形31を示している。

またターンオフについてはゲート抵抗17、MOS-FET15内蔵のダイオード、トランジスタ13を通る電流ループで主回路用半導体素子200のゲートが放電されるためスイッチング速度は変わらず、ターンオフ時の損失は変化しない。

【0022】

本実施の形態2によるゲート駆動回路8を用いれば、実施の形態1と同様に、リカバリ電流が流れる期間ではターンオンする素子のゲート電圧を低くしドレイン電流を制限できるため、短絡経路であるリカバリ電流を小さく抑えることが可能となるので、電流変化率が低下し、サージ電圧を低下させることができる。

【0023】

実施の形態3.

図7は、本実施の形態3によるゲート駆動回路8を示すもので、実施の形態2における抵抗21に並列にコンデンサ22を挿入したものである。

実施の形態2ではゲート抵抗を大きくしたのみであり、主回路用半導体素子200のゲート閾値電圧Vthまでゲートが充電されるまでの時間が長くなり、トータルでのスイッチングに要する時間が長くなるが、本実施の形態3では、抵抗21に並列にコンデンサ22を挿入したことで、主回路用半導体素子200のゲートがゲート閾値電圧Vth以下の期間では、コンデンサ22に電流を流して抵抗21はスルーさせることができる。

そしてコンデンサ22が所定の電圧まで充電されれば、コンデンサ22には電流が流れなくなり、その後は抵抗21とゲート抵抗17により決定される充電電流でゲートが充電されることになる。よってゲートの総充電時間が短縮される。

【0024】

抵抗21が十分大きいとすれば、初期充電にて、コンデンサ22の静電容量C27と主回路用半導体素子200のゲート・ソース間容量CGSの比から近似の式(2)で示されるような主回路用半導体素子200のゲート・ソース間電圧値VGSaが充電されるので、この電圧値が最低でもその素子のゲート閾値電圧Vthになるようにコンデンサ22の静電容量を決定すればよい。ゲート駆動電圧はVs[V]である。

VGSa≒Vs×{C27÷(C27+CGS)} [V]・・・・・(2)

実施の形態2と同様にMOS-FET15がオンすれば、実施の形態2のようにゲート抵抗17のみでゲートが駆動されるので、本実施の形態3においても、実施の形態2と同様の効果を得ることが可能である。

【0025】

図8は、本実施の形態3における上述のゲート駆動回路8を用いた場合の主回路用半導体素子200のゲート電圧の立ち上がり波形34と、上述のゲート駆動回路8のゲート抵抗17と同じ値のゲート抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形30と、ゲート駆動回路8を用いた場合と同程度にリカバリサージを抑制可能なゲート抵抗17よりも大きい値の抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形31を示している。

抵抗21を十分に大きくすれば、リカバリ期間において図8の波形34のようにオンさせた状態のままゲート電圧の上昇を抑え、ほぼ一定の値に保つことが可能であるので、サージ抑制効果は実施の形態2よりも高いものになる。

またMOS-FET15がオンするとコンデンサ22を短絡する経路となるので、ゲート抵抗の値を図9のように抵抗23、ゲート抵抗17に分割し、抵抗23をMOS-FET15に直列接続して、短絡電流が過大にならないように抑えるようにしても良い。このときMOS-FET15がオンしてからは、抵抗21と抵抗23の並列抵抗値とゲート抵抗17の合計値により主回路用半導体素子200のゲートの充電速度が決定する。

【0026】

実施の形態4.

本実施の形態4は、PWMスイッチングアーム6のゲート駆動回路8において、実施の形態1で用いたPチャネル型のMOS-FET15に代わり、スイッチ素子であるNチャネル型のMOS-FET24を用いたものである。

図10は本実施の形態4によるゲート駆動回路8である。使用するMOS-FET24はNチャネル型であるので、オンさせるためにはゲート・ソース間の電位差がゲート閾値電圧以上になる必要があるため、遅延時間を設定する抵抗25とコンデンサ26を図10の位置に配置し、コンデンサ26を充電しゲートの電位を上げていくことでスイッチングさせる。トランジスタ14がオンした直後は、ゲート駆動電圧Vsからツェナーダイオード16のツェナー電圧を引いた電圧だけMOS-FET24のソース電位の方がゲートよりも高くなっているので、遅延時間を決定する際にはこの電位差分を考慮し、実施の形態1に用いた抵抗23よりも小さい値にする必要がある。なお、抵抗27はMOS-FET24のゲート・ソース間容量放電用の抵抗である。

【0027】

本実施の形態4のゲート駆動回路8ではMOS-FET24がオンした場合ソースの電位がゲート駆動電圧の電位まで上昇するためMOS-FET24はオフする。オフすることによりまたソースの電位が下がるため、MOS-FET24は再びオンするというようにスイッチングを繰り返し行う。そのスイッチングを繰り返す期間に、時間は短いがゲート駆動電圧Vsによる大きい充電電流がスイッチング毎に流れるので、同程度にサージ電圧を抑制可能な大きな抵抗のみで駆動するよりも速く主回路用半導体素子200のゲート・ソース間電圧が上昇する。但し大電流は上述のように断続的であるため、連続的に高電圧で充電できる実施の形態1よりはゲート電圧の立ち上がりは遅くなる。

【0028】

図11は、本実施の形態4における上述のゲート駆動回路8を用いた場合の主回路用半導体素子200のゲート電圧の立ち上がり波形35と、上述のゲート駆動回路8と同じ値のゲート抵抗17のみで駆動させた場合のゲート電圧の立ち上がり波形30と、ゲート駆動回路8を用いた場合と同程度にリカバリサージを抑制可能なゲート抵抗17よりも大きい値の抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形31を示している。

最初にMOS-FETをオンさせるまでの低ゲート電圧化に関しては問題は無く、ダイオードのリカバリによるサージ抑制の効果は、本実施の形態4においても実施の形態1と同様の効果を得ることが可能である。

また同程度にサージ電圧を抑制可能な大きな抵抗のみのゲート抵抗にて駆動するよりもターンオン時のスイッチングに伴う損失を低下することが可能である。

【0029】

実施の形態5.

図12は本実施の形態5によるゲート駆動回路8を示す回路図で、実施の形態4で示したツェナーダイオード16を抵抗21に変更したものである。

トランジスタ14がオンしてからMOS-FET24が初めにオンするまでは、ゲート抵抗17と抵抗21で決まる充電速度で主回路用半導体素子200のゲートを充電可能であり、ダイオードリカバリによるサージ電圧を抑える効果は実施の形態2と同様の効果を得る。 MOS-FET24が初めにオンしてからの回路の挙動は、本実施の形態5についても、実施の形態4と同様にMOS-FET24がスイッチングを繰り返すことになる。

スイッチングを繰り返す期間に、短時間ではあるが低ゲート抵抗による大きい充電電流がスイッチング毎に流れるので、同程度にサージ電圧を抑制可能な大きな抵抗のみで駆動するよりも速く主回路用半導体素子200のゲート・ソース間電圧が上昇する。但し大電流は上述のように断続的であるため、連続的に高電圧で充電できる実施の形態2よりはゲート電圧の立ち上がりは遅くなる。

【0030】

図13は、本実施の形態5における上述のゲート駆動回路8を用いた場合の主回路用半導体素子200のゲート電圧の立ち上がり波形36と、上述のゲート駆動回路8と同じ値のゲート抵抗17のみで駆動させた場合のゲート電圧の立ち上がり波形30と、ゲート駆動回路8を用いた場合と同程度にリカバリサージを抑制可能なゲート抵抗17よりも大きい値の抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形31を示している。

本実施の形態5についても、実施の形態4と同様に、同程度にサージ電圧を抑制可能な大きな抵抗のみのゲート抵抗にて駆動するよりもスイッチング時の損失を低下することが可能である。

【0031】

実施の形態6.

図14は本実施の形態6によるゲート駆動回路8を示す回路図で、実施の形態5で示した抵抗21にコンデンサ22を並列に接続した回路である。

トランジスタ14がオンしてからMOS-FET24が初めにオンするまでの動作は、実施の形態3で示したゲート駆動回路の動作と同じであるので、ダイオードリカバリによるサージ電圧を抑える効果は実施の形態3と同様の効果を得る。

MOS-FET24が初めにオンしてからの回路の挙動は、本実施の形態6についても、実施の形態4と同様にMOS-FET24がスイッチングを繰り返すことになる。

スイッチングを繰り返す期間に、コンデンサ22は、MOS-FET24がオンするたびに放電するため、MOS-FET24がオフしても、コンデンサ22が充電されるまで抵抗21はスルーされ、ゲート抵抗17の抵抗値で充電速度が決定されるため、実施の形態5よりも充電は高速になる。

【0032】

図15は、本実施の形態6における上述のゲート駆動回路8を用いた場合のゲート電圧の立ち上がり波形37と、上述のゲート駆動回路8と同じ値のゲート抵抗17のみで駆動させた場合のゲート電圧の立ち上がり波形30と、ゲート駆動回路8を用いた場合と同程度にリカバリサージを抑制可能なゲート抵抗17よりも大きい値の抵抗のみで駆動させた場合のゲート電圧の立ち上がり波形31を示している。

本実施の形態6についても実施の形態4及び実施の形態5と同様に、同程度にサージ電圧を抑制可能な大きな抵抗のみのゲート抵抗にて駆動するよりもスイッチング時の損失を低下することが可能である。

【0033】

実施の形態3と同様にMOS-FET24がオンしたときコンデンサ22から短絡電流が流れるので、ゲート抵抗の値を分割して図16のように抵抗23、ゲート抵抗17を配置して、短絡電流が過大にならないように抑えるようにしても良い。このときコンデンサ22の放電電流を制限していることになるので、短いオン期間でのコンデンサ22の電圧の低下量は減少するので、1回のスイッチング毎の主回路用半導体素子200のゲートの充電量は減少する。しかしMOS-FET24のソース電位も上昇しにくいため、MOS-FET24のスイッチング回数が増加し、総充電時間は、短絡させた場合と同程度となる。

【図面の簡単な説明】

【0034】

【図1】本発明の電力変換装置の基本構成を示すブロック回路図である。

【図2】図1の電力変換装置においてダイオードリカバリ時に発生するサージ電圧とリカバリ電流の例を示す波形図である。

【図3】本発明の実施の形態1におけるゲート駆動回路を示す回路図である。

【図4】実施の形態1におけるゲート駆動回路を用いた場合のゲート電圧の立ち上がり波形を示す図である。

【図5】本発明の実施の形態2におけるゲート駆動回路を示す回路図である。

【図6】実施の形態2におけるゲート駆動回路を用いた場合のゲート電圧の立ち上がり波形を示す図である。

【図7】本発明の実施の形態3におけるゲート駆動回路を示す回路図である。

【図8】実施の形態3におけるゲート駆動回路を用いた場合のゲート電圧の立ち上がり波形を示す図である。

【図9】実施の形態3におけるゲート駆動回路の他の例を示す回路図である。

【図10】本発明の実施の形態4におけるゲート駆動回路を示す回路図である。

【図11】実施の形態4におけるゲート駆動回路を用いた場合のゲート電圧の立ち上がり波形を示す図である。

【図12】本発明の実施の形態5におけるゲート駆動回路を示す回路図である。

【図13】実施の形態5におけるゲート駆動回路を用いた場合のゲート電圧の立ち上がり波形を示す図である。

【図14】本発明の実施の形態6におけるゲート駆動回路を示す回路図である。

【図15】実施の形態6におけるゲート駆動回路を用いた場合のゲート電圧の立ち上がり波形を示す図である。

【図16】実施の形態6におけるゲート駆動回路の他の例を示す回路図である。

【符号の説明】

【0035】

1 直流電源、2 コンデンサ、3,4 浮遊インダクタンス、5 出力極性固定アーム、6 PWMスイッチングアーム、7,8 ゲート駆動回路、9 出力フィルタ、10 交流負荷、11 ゲート駆動用直流電源、12 制御パルス発生回路、13,14 トランジスタ、15 Pチャネル型のMOS-FET、16 ツェナーダイオード、17 ゲート抵抗、18,19 抵抗、20 コンデンサ、21抵抗、22 コンデンサ、23 抵抗、24 Nチャネル型のMOS-FET、25 抵抗、26 コンデンサ、27 抵抗、100 単相のフルブリッジインバータ、200 主回路用半導体素子。

【特許請求の範囲】

【請求項1】

逆並列にダイオードが接続された一対の第1半導体スイッチング素子を直列接続し、出力極性が切り替わるときに前記第1半導体スイッチング素子をスイッチングする出力極性固定アームと、逆並列にダイオードが接続された一対の第2半導体スイッチング素子を直列接続し、前記第2半導体スイッチング素子を常時PWMスイッチングし出力値を調整するPWMスイッチングアームとから構成された単相のフルブリッジインバータを備えた電力変換装置において、

ゲート抵抗で前記第1半導体スイッチング素子のスイッチング速度を決定し、前記第1半導体スイッチング素子を駆動する第1のゲート駆動回路と、

前記第2半導体スイッチング素子にゲート制御パルスを供給する制御パルス発生回路の出力端に、前記第2半導体スイッチング素子のゲートの充電開始から所定の時間後にオンするスイッチ素子とツェナーダイオードまたは抵抗との並列回路を直列に接続し、更に前記並列回路の出力端をゲート抵抗を介して前記第2半導体スイッチング素子のゲート端子に接続し、前記第2半導体スイッチング素子を駆動する第2のゲート駆動回路とを備えたことを特徴とする電力変換装置。

【請求項2】

第2のゲート駆動回路は、スイッチ素子と抵抗との並列回路に、更にコンデンサを並列に接続したことを特徴とする請求項1記載の電力変換装置。

【請求項3】

第2のゲート駆動回路は、並列回路を形成するスイッチ素子に抵抗を直列接続したことを特徴とする請求項2記載の電力変換装置。

【請求項4】

第2のゲート駆動回路を構成するスイッチ素子はPチャネル型のMOS-FETであり、前記第2のゲート駆動回路は、前記スイッチ素子のゲート・ソース間に接続されたコンデンサおよび第2半導体スイッチング素子のソースと前記スイッチ素子のゲートとの間に接続された抵抗で前記スイッチ素子がオンするまでの遅延時間の決定を行い、前記第2半導体スイッチング素子を駆動することを特徴とする請求項1乃至3のいずれか一つに記載の電力変換装置。

【請求項5】

第2のゲート駆動回路を構成するスイッチ素子はNチャネル型のMOS-FETであり、前記第2のゲート駆動回路は、前記スイッチ素子のゲート・ドレイン間に接続された抵抗および第2半導体スイッチング素子のソースと前記スイッチ素子のゲートとの間に接続されたコンデンサで前記スイッチ素子がオンするまでの遅延時間の決定を行い、前記第2半導体スイッチング素子を駆動することを特徴とする請求項1乃至3のいずれか一つに記載の電力変換装置。

【請求項1】

逆並列にダイオードが接続された一対の第1半導体スイッチング素子を直列接続し、出力極性が切り替わるときに前記第1半導体スイッチング素子をスイッチングする出力極性固定アームと、逆並列にダイオードが接続された一対の第2半導体スイッチング素子を直列接続し、前記第2半導体スイッチング素子を常時PWMスイッチングし出力値を調整するPWMスイッチングアームとから構成された単相のフルブリッジインバータを備えた電力変換装置において、

ゲート抵抗で前記第1半導体スイッチング素子のスイッチング速度を決定し、前記第1半導体スイッチング素子を駆動する第1のゲート駆動回路と、

前記第2半導体スイッチング素子にゲート制御パルスを供給する制御パルス発生回路の出力端に、前記第2半導体スイッチング素子のゲートの充電開始から所定の時間後にオンするスイッチ素子とツェナーダイオードまたは抵抗との並列回路を直列に接続し、更に前記並列回路の出力端をゲート抵抗を介して前記第2半導体スイッチング素子のゲート端子に接続し、前記第2半導体スイッチング素子を駆動する第2のゲート駆動回路とを備えたことを特徴とする電力変換装置。

【請求項2】

第2のゲート駆動回路は、スイッチ素子と抵抗との並列回路に、更にコンデンサを並列に接続したことを特徴とする請求項1記載の電力変換装置。

【請求項3】

第2のゲート駆動回路は、並列回路を形成するスイッチ素子に抵抗を直列接続したことを特徴とする請求項2記載の電力変換装置。

【請求項4】

第2のゲート駆動回路を構成するスイッチ素子はPチャネル型のMOS-FETであり、前記第2のゲート駆動回路は、前記スイッチ素子のゲート・ソース間に接続されたコンデンサおよび第2半導体スイッチング素子のソースと前記スイッチ素子のゲートとの間に接続された抵抗で前記スイッチ素子がオンするまでの遅延時間の決定を行い、前記第2半導体スイッチング素子を駆動することを特徴とする請求項1乃至3のいずれか一つに記載の電力変換装置。

【請求項5】

第2のゲート駆動回路を構成するスイッチ素子はNチャネル型のMOS-FETであり、前記第2のゲート駆動回路は、前記スイッチ素子のゲート・ドレイン間に接続された抵抗および第2半導体スイッチング素子のソースと前記スイッチ素子のゲートとの間に接続されたコンデンサで前記スイッチ素子がオンするまでの遅延時間の決定を行い、前記第2半導体スイッチング素子を駆動することを特徴とする請求項1乃至3のいずれか一つに記載の電力変換装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2009−153315(P2009−153315A)

【公開日】平成21年7月9日(2009.7.9)

【国際特許分類】

【出願番号】特願2007−329970(P2007−329970)

【出願日】平成19年12月21日(2007.12.21)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成21年7月9日(2009.7.9)

【国際特許分類】

【出願日】平成19年12月21日(2007.12.21)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]