電力変換装置

【課題】第1のスイッチング素子と第2のスイッチング素子との接続部に負電圧が発生することを防止し、絶縁を不要としパワーモジュールへの適用を可能にしてインバータ回路を構成する部品点数の削減、基板実装面積の低減を図ることのできる電力変換装置を提供する。

【解決手段】上相スイッチング素子2と下相スイッチング素子3とからなる半導体スイッチ1を備える電力変換装置Sであり、下相スイッチング素子3は第1のスイッチング素子4と第2のスイッチング素子5とからなり、両者の負極を接続し、前者の正極を正極端子8、後者の正極を負極端子9とし、正極端子8と負極端子9との間に並列に接続される高速環流ダイオード7と、上相スイッチング素子2がオン中に第2のスイッチング素子5をオンさせ、上相スイッチング素子2のオフ中は第2のスイッチング素子5のオンを継続させる駆動信号を出力するロジック回路10とを備える。

【解決手段】上相スイッチング素子2と下相スイッチング素子3とからなる半導体スイッチ1を備える電力変換装置Sであり、下相スイッチング素子3は第1のスイッチング素子4と第2のスイッチング素子5とからなり、両者の負極を接続し、前者の正極を正極端子8、後者の正極を負極端子9とし、正極端子8と負極端子9との間に並列に接続される高速環流ダイオード7と、上相スイッチング素子2がオン中に第2のスイッチング素子5をオンさせ、上相スイッチング素子2のオフ中は第2のスイッチング素子5のオンを継続させる駆動信号を出力するロジック回路10とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、誘導性負荷に電力を供給する電力変換装置に関する。

【背景技術】

【0002】

従来、モータ等の誘導性負荷を駆動する電力変換装置内のインバータ回路に設けられるスイッチング回路として順接続された主素子(IGBTやMOSFET)と逆接続された補助素子(MOSFET)の直列回路を使用し、さらにこの両素子の両端間に高速環流ダイオードを逆並列接続させた電力変換装置が提案されている(以下の特許文献1参照)。

【0003】

この特許文献1において開示される電力変換装置によると、回路構成を単純化しつつも従来のスイッチング素子のON、或いはOFFに伴って発生する還流ダイオードの逆回復電流を効果的に抑制することで、この逆回復電流による損失を低減させることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−193839号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上述の特許文献1に開示されている回路構成を採用すると、以下のような不具合が生ずる可能性がある。

【0006】

すなわち、上記特許文献1に開示された回路では、補助素子(逆接続されたMOSFET)を主素子(順接続されたIGBT)と同じ駆動信号で動作させることによって主素子の寄生ダイオードに起因する逆回復電流による損失を発生させなくしている。

【0007】

但し、インバータ回路を構成する上相のスイッチング素子がONからOFFとなり主素子と補助素子がONするまでの期間(高速環流ダイオードに負荷電流が流れている期間)は、主素子の出力容量へ充電される(チャージされる)電荷の影響によって主素子と補助素子の接続部に負電位が発生する可能性がある。

【0008】

上記特許文献1においては、補助素子に印加される瞬間的な負電位(特許文献1においては「サージ電圧」と表わされている)の発生に対処するため別途クランプ回路を設けて、チャージされた電荷を逃がす経路を確保している。また、併せて補助素子のゲート駆動用電源として利用する旨記載されている。

【0009】

また、例えば、フォトカプラを使用して制御用電源と駆動用電源とを絶縁することによってこの負電位発生による影響を受けないようにすることも不可能ではないが、フォトカプラ等の使用は新たな部品の追加となるため、回路構成を複雑にする。

【0010】

さらに、スイッチン速度向上による効率向上及びインバータ回路を構成する部品点数の削減、基板実装面積の低減を意図して、例えば、スーパージャンクションMOSFETを搭載するパワーモジュール(Power Module;以下、「PM」と表わす)をインバータ回路に利用しようとする場合に、負電位が発生することによって回路の誤動作を誘発する等、障害となる。なお、パワーモジュールとは、インバータ回路を構成するスイッチング素子とそのスイッチング素子の駆動回路を1つのパッケージに組み込んだ素子をいう。

【0011】

本発明は上記課題を解決するためになされたものであり、本発明の目的は、上相のスイッチング素子がONからOFFに切り替わった後、下相スイッチング素子がオンするまでの期間に下相スイッチング素子の第1のスイッチング素子の両端が電源から切り離された状態になることをなくしたため、第1のスイッチング素子と第2のスイッチング素子との接続部に負電圧が発生することを防止することができる電力変換装置を提供することである。また、絶縁を必要とせずにパワーモジュールへの適用を可能とすることでインバータ回路を構成する部品点数の削減、基板実装面積の低減を図ることのできる電力変換装置を提供することである。

【課題を解決するための手段】

【0012】

本発明の実施の形態に係る特徴は、直流電圧源に直列に接続され、スイッチング信号に基づくONまたはOFF制御により誘導性負荷に電力を供給する上相スイッチング素子と下相スイッチング素子とから構成される半導体スイッチを備える電力変換装置であって、下相スイッチング素子は、逆導通性能を有し、高耐圧な第1のスイッチング素子と、第1のスイッチング素子に比べて低耐圧な第2のスイッチング素子と、第1のスイッチング素子の負極と第2のスイッチング素子の負極とを接続して第1のスイッチング素子の正極を正極端子とし、第2のスイッチング素子の正極を負極端子とし、正極端子と負極端子との間に負極端子から正極端子に向かう方向が順方向となるように並列に接続される高速環流ダイオードと、上相スイッチング素子がオン中に第2のスイッチング素子をオンさせ、その後、上相スイッチング素子のオフ中は第2のスイッチング素子のオンを継続させる駆動信号を出力するロジック回路とを備える。

【発明の効果】

【0013】

本発明によれば、上相のスイッチング素子がONからOFFに切り替わった後、下相スイッチング素子がオンするまでの期間に下相スイッチング素子の第1のスイッチング素子の両端が電源から切り離された状態になることをなくしたため、第1のスイッチング素子と第2のスイッチング素子との接続部に負電圧が発生することを防止することができる電力変換装置を提供することができる。また、絶縁を必要とせずにパワーモジュールへの適用を可能とすることでインバータ回路を構成する部品点数の削減、基板実装面積の低減を図ることのできる電力変換装置を提供することができる。

【図面の簡単な説明】

【0014】

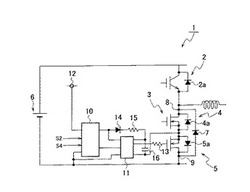

【図1】本発明の実施の形態における電力変換装置に使用される半導体スイッチの構成を示す回路図である。

【図2】本発明の実施の形態における電力変換装置に使用される半導体スイッチに印加される駆動信号を示すタイムチャートである。

【図3】図2に示すタイムチャートに基づく電流の流れを示す回路図である。

【図4】図2に示すタイムチャートに基づく電流の流れを示す回路図である。

【図5】図2に示すタイムチャートに基づく電流の流れを示す回路図である。

【図6】図2に示すタイムチャートに基づく電流の流れを示す回路図である。

【図7】本発明の実施の形態における電力変換装置に使用されるインバータ回路として、半導体スイッチ素子を内蔵するPMを利用した場合の回路構成の一例を示す回路図である。

【発明を実施するための形態】

【0015】

以下、本発明の実施の形態について図面を参照して詳細に説明する。

【0016】

図1は、本発明の実施の形態における電力変換装置に使用される半導体スイッチ1の構成を示す回路図である。半導体スイッチ1は、上相のスイッチング素子2と、下相のスイッチング素子3とから構成される。下相のスイッチング素子3は、さらに第1のスイッチング素子4と第2のスイッチング素子5を備える。

【0017】

なお、電力変換装置では、このような半導体スイッチ1の2組または3組が直流電圧源6に並列接続された構成とするのが一般的である。半導体スイッチ1を2組とした場合、単相出力のインバータ回路となり、3組とした場合は3相出力のインバータ回路が構成される。

【0018】

上相スイッチング素子2及び下相スイッチング素子3(第1のスイッチング素子4及び第2のスイッチング素子5)は、直列に接続される。これら上相スイッチング素子2及び下相スイッチング素子3の両端は、直流電圧源6の電源ラインに接続されている。さらに直列に接続される第1のスイッチング素子4及び第2のスイッチング素子5に対して高速環流ダイオード7が逆並列に接続されている。

【0019】

上相スイッチング素子2には、例えば、電圧駆動型素子でありIGBTが好適に用いられる。また、上相スイッチング素子2の両端には、電流の流れが逆になるように並列接続された逆並列ダイオード2aが設けられる。

【0020】

第1のスイッチング素子4は、例えば、高い耐圧性能を備える高耐圧な電圧駆動型素子であり、例えば、スーパージャンクションMOSFETが好適に使用される。第1のスイッチング素子には、ダイオード4a(寄生ダイオード)が逆並列接続されている。

【0021】

第2のスイッチング素子5は、第1のスイッチング素子4に比べれば低い耐圧性能を備える電圧駆動型素子である。第2のスイッチング素子5には、低耐圧なMOSFETが好適に使用され、ダイオード5a(寄生ダイオード)が逆並列接続されている。

【0022】

第1のスイッチング素子4と第2のスイッチング素子5の接続は、第1のスイッチング素子4の負極と第2のスイッチング素子5の負極とが接続されて行われる。第1のスイッチング素子4の正極が正極端子8となり、第2のスイッチング素子5の正極が負極端子9となる。

【0023】

高速環流ダイオード7は、この正極端子8と負極端子9との間に負極端子9から正極端子8に向かう方向が順方向となるように並列に接続される。この高速環流ダイオード7は、例えば、第1のスイッチング素子4の逆並列ダイオード4aに比べて、チップ面積が小さく、順方向の電圧降下は高く、逆回復特性に優れる素子が用いられる。

【0024】

第2のスイッチング素子5に対しては、ロジック回路10、及び駆動回路11を介して駆動信号が印加される。このロジック回路10、及び駆動回路11には、直流電圧源6よりも電圧値が低い低電圧直流電圧源12によって電圧が印加される。

【0025】

なお、本発明の実施の形態においては、この駆動回路11については、高耐圧な回路が使用されている。ロジック回路10には、外部で生成される上相スイッチング素子2の駆動信号(ON/OFF指令)S2と第1のスイッチング素子4に印加される駆動信号(ON/OFF指令)S4が入力される。ロジック回路10は、この2つの信号を論理演算することで、第2のスイッチング素子5のON/OFFタイミングを生成する。

【0026】

駆動回路11と第2のスイッチング素子5との間には抵抗13が接続されている。また、低電圧直流電圧源12と直列に、ダイオード14、抵抗15、コンデンサ16がそれぞれ接続されている。なお、上相スイッチング素子2及び第1のスイッチング素子4に対する駆動回路等については一般的な構成であるため、図1では図示を省略する。

【0027】

図2は、本発明の実施の形態における電力変換装置Sに使用される半導体スイッチ1に印加される駆動信号を説明するタイムチャートである。最上段から最下段へ向けて順に、上相スイッチング素子2の駆動信号S2、第1のスイッチング素子4の駆動信号S4、駆動信号S2を所定期間遅延させた遅延信号Sd、及び第2のスイッチング素子5の駆動信号(ON/OFF指令)S5である。

【0028】

上相スイッチング素子2の駆動信号S2、第1のスイッチング素子4の駆動信号S4は、図示しない制御回路から出力されてくるもので、一般的には、PWM生成器から出力されるPWM信号を上相スイッチング素子2の駆動信号S2とする。また、この信号を反転させた信号に、さらに上相スイッチング素子2と第1のスイッチング素子4が同時にONして短絡しないように立ち上がりに遅延を設けた信号を第1のスイッチング素子4の駆動信号S4としている。なお、同様の理由で上相スイッチング素子2の駆動信号S2も立ち上がりには遅延が設けられている。

【0029】

駆動信号S2を所定期間遅延させた遅延信号Sdは、上述のロジック回路10内で生成される信号で、さらにロジック回路10は、この遅延信号Sdの立ち上がり(ON)に同期してONとなり、その後の第1のスイッチング素子4の駆動信号S4の立下りに同期してOFFする信号を生成する。この生成信号が第2のスイッチング素子5の駆動信号(ON/OFF指令)S5となる。

【0030】

この結果、上相スイッチング素子2がONしている間に第2のスイッチング素子5がONし、その後、上相スイッチング素子2がOFFした後に第1のスイッチング素子4がONしてOFFするまでの期間、第2のスイッチング素子5はONを継続する。

【0031】

このため、上相スイッチング素子2がOFFした後、第1のスイッチング素子4がONするまでの間も第1のスイッチング素子4の負極は、第2のスイッチング素子5を経由して直流電圧源6のグランド側に接続されるため、第1のスイッチング素子4の負極には負電圧が発生しない。

【0032】

すなわち、第2のスイッチング素子5は、上相スイッチング素子2がONからOFFに変わり、その後、第1のスイッチング素子4がONするまでの期間は少なくともONする。従って、第1のスイッチング素子4と第2のスイッチング素子5とは別の駆動信号にて動作する。

【0033】

以下、図2のタイムチャート及び図3ないし図6の回路図を用いて、半導体スイッチ1の動きについて説明する。なお、説明の便宜上、図2のタイムチャートには破線で区切ってAないしEの5つの期間を設けている。

【0034】

まずA及びBの期間についてである。上相スイッチング素子2に対しては、Aの期間開始時に駆動信号S2が印加(ON)され、Bの期間終了時に駆動信号S2はOFFされる。一方、第1のスイッチング素子4についてはA、Bの期間通して駆動信号S4は印加(ON)されない(OFFのまま)。

【0035】

第2のスイッチング素子5に対しては、上述の駆動信号S5が印加される。駆動信号S5の立ち上がりは遅延信号Sdの立ち上がり(ON)と同期し、図2に示されているように、上相スイッチング素子2に印加される駆動信号S2からAの期間分だけ遅れて出力が追従して立ち上がる(ONとなる)。

【0036】

本発明の実施の形態においては、Aの期間(時間)は1μsecである。但し、この期間(時間)は上相スイッチング素子2がON中にAの期間が終了する範囲内で任意に設定することができる。このように第2のスイッチング素子5の立ち上がりは、遅延信号Sdの立ち上がりと同期する。このため、第2のスイッチング素子5は、上相スイッチング素子2がON中のBの期間開始時に駆動信号(ON)が印加され、ONする。

【0037】

第2のスイッチング素子5はBの期間開始時にONとなるが、第1のスイッチング素子4はOFFの状態にある。従って、図3に示すように、直流電圧源6からの電流は上相のスイッチング素子2を経由して負荷側に流れる。この際、第1のスイッチング素子4には上相スイッチング素子2がONされていることによって、直流電圧源6からの電圧分の電荷がチャージされる。

【0038】

次にCの期間である。この期間は上相スイッチング素子2がOFFしてから第1のスイッチング素子4がONするまでの期間である。従来、このCの期間は、第1のスイッチング素子4へ充電された(チャージされた)電荷の影響によって第2のスイッチング素子5の両端間に負電位が発生する期間となる。このような負電位の発生を抑制することが本発明の目的である。

【0039】

図2に示すように、このCの期間、上相スイッチング素子2はOFFのままである。一方、第1のスイッチング素子4はOFF、第2のスイッチング素子5はONの状態である。第2のスイッチング素子5はONのままであるので、環流電流は、図4に示すように、主に第1のスイッチング素子4の逆並列ダイオード4aを経由して流れる。これは、高速環流ダイオード7に全く電流が流れない訳ではないが、高速環流ダイオード7の電圧の方が、第2のスイッチング素子5のON抵抗と第1のスイッチング素子4の順電圧との和よりも大きいからである。

【0040】

このように、Cの期間中第2のスイッチング素子5をONし続けることによって、A及びBの期間中に第1のスイッチング素子4にチャージされた電荷を放電する経路を確保することが可能となる。従って、チャージされた電荷の存在による第1のスイッチング素子4と第2のスイッチング素子5との接続点と、負極端子9との間において負電圧が発生することがなくなる。

【0041】

Dの期間は、上相スイッチング素子2はOFFの状態が継続する。第1のスイッチング素子4は駆動信号が印加されてONの状態となる。第1のスイッチング素子4がONの状態にあるので、第2のスイッチング素子5もONの状態が維持される。

【0042】

従って、図5に示すように、環流電流は第1のスイッチング素子4及び第2のスイッチング素子5を経由して流れる。また、第1のスイッチング素子4及び第2のスイッチング素子5のいずれもがONの状態にあるため、環流電流は高速環流ダイオード7に流れない。

【0043】

なお、CからDの期間への転流時は、既に第2のスイッチング素子5がONとなっているため、第1のスイッチング素子4の逆並列ダイオード4aへの逆電圧が印加されることはなく、過大な逆回復電流が発生することもない。

【0044】

Eの期間は、第1のスイッチング素子4及び第2のスイッチング素子5のいずれもOFFとなる。従って、図6に示すように、環流電流は全て高速環流ダイオード7に流れる。上述したように、Cの期間に第1のスイッチング素子4にチャージされた電荷は全て放電されているので、第1のスイッチング素子4と第2のスイッチング素子5との接続点と、負極端子9との間において負電圧が発生することはない。

【0045】

なお、直流電圧源6からの電流が逆方向、すなわち、上相スイッチング素子2の逆並列ダイオード2aに環流電流が流れる場合であってもこの逆並列ダイオード2aは十分に高速であるため、過大な逆回復電流が発生することはない。

【0046】

図7は、本発明の実施の形態における電力変換装置Sに使用されるインバータ回路Iとして、半導体スイッチ1を内蔵するパワーモジュールへ適用した場合の回路構成の一例を示す回路図である。電力変換装置Sにおいては、直流電圧源6の電源ラインにインバータ回路Iが接続され、このインバータ回路Iの出力側に、例えばモータ等の誘導性負荷Mが接続されている。

【0047】

インバータ回路Iは、上相スイッチング素子2Uないし2Wと下相スイッチング素子とが三相ブリッジ接続される。ここで、上相スイッチング素子2Uと下相スイッチング素子である第1のスイッチング素子4X及び第2のスイッチング素子5X、上相スイッチング素子2Vと下相スイッチング素子である第1のスイッチング素子4Y及び第2のスイッチング素子5Y、上相スイッチング素子2Wと下相スイッチング素子である第1のスイッチング素子4Z及び第2のスイッチング素子5Zが、それぞれ一対の主回路スイッチング素子を構成している。

【0048】

上相スイッチング素子2U、2V、2Wに対してそれぞれ駆動回路Ua,Va,Waが設けられている。3つの第1のスイッチング素子4X、4Y、4Zの駆動回路Daは、グランド側が共通であるため、電源が共通にできるため1つの駆動回路でまかなわれている。第2のスイッチング素子5X,5Y,5Zにはそれぞれ駆動回路11X、11Y、11Zが設けられるが、ロジック回路10は、この3つの第2のスイッチング素子5X,5Y,5Zに対して1つとし、第2のスイッチング素子5X,5Y,5Zの各々に対応した3種類の駆動信号を出力する。

【0049】

図7に示されているインバータ回路Iは、パワーモジュールの使用に関して2種類の態様を示している。

【0050】

1つ目は、破線で示される従来から使用されているパワーモジュールPM1を用いた場合で、パワーモジュールPM1内には、上相スイッチング素子2及び下相スイッチング素子3のうち第1のスイッチング素子4、各スイッチング素子の駆動回路Wa,Va,Ua及び駆動回路Daが内蔵されている態様である。

【0051】

すなわち、第2のスイッチング素子5X,5Y,5Z、高速環流ダイオード7U,7V,7W、ロジック回路10及び駆動回路11X、11Y、11Zは、パワーモジュールPM1の外部で接続されている。このように、図7の破線に示されるような既存のパワーモジュールPM1を用いても本発明のインバータ回路Iを構成することができる。

【0052】

2つ目は、インバータ回路I全体をパワーモジュールPM2内に組み込んだものである。この場合、上相スイッチング素子2、第1のスイッチング素子4及び駆動回路Wa,Va,Uaとともに、第2のスイッチング素子5X,5Y,5Z、高速環流ダイオード7U,7V,7W、ロジック回路10、及び駆動回路11X、11Y、11Z及び駆動回路Daをも、図7に太実線で表わされているようにパワーモジュールPM2内に内蔵させる。

【0053】

このように主回路スイッチング素子及び周辺回路すべてをパワーモジュールPM2に内蔵させる構成とすることによって、インバータ回路Iをモジュール化することができ、電力変換装置Sを構成する部品点数を大幅に減らすことができる。

【0054】

なお、パワーモジュールPM2の端子S21〜S23は、3つの上相スイッチング素子2W〜2Uの駆動信号の入力端子で、端子S41〜S43は、3つの第1のスイッチング素子4Z〜4Xの駆動信号の入力端子である。さらに、パワーモジュールPM2の端子Hと端子Lは、3つの上相スイッチング素子2W〜2Uの駆動電源端子となっている。

【0055】

また、パワーモジュールPM2の外部において各第2のスイッチング素子5X,5Y,5Zと負側の電源ラインとの間には、ベクトル制御及び過電流保護用の電流検出用抵抗R1〜R3が設けられている。 そして、上述したように、本発明の実施の形態によれば、上相のスイッチング素子がONからOFFに切り替わった後、下相スイッチング素子がオンするまでの期間に第1のスイッチング素子4の端子に負電位を発生させなくすることができ、絶縁処理が不要となることから、すべてのスイッチング素子とその駆動回路をパワーモジュールPM2内に内蔵しても誤動作や素子の破壊などの問題が生じず、好適である。なお、部品点数が若干増加するが、ロジック回路10をパワーモジュールPM2の外部に設けることも可能である。

【0056】

以上説明した構成を採用することによって、上相のスイッチング素子がONからOFFに切り替わった後、下相スイッチング素子がオンするまでの期間に下相スイッチング素子の第1のスイッチング素子の両端が電源から切り離された状態になることをなくしたため、第1のスイッチング素子と第2のスイッチング素子との接続部に負電圧が発生することを防止することができる。また、絶縁を必要とせずにパワーモジュールへの適用を可能とすることでインバータ回路を構成する部品点数の削減、基板実装面積の低減を図ることのできる電力変換装置を提供することができる。

【0057】

なお、この発明は、上記実施の形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施の形態に開示されている複数の構成要素を適宜組み合わせることにより種々の発明を形成できる。例えば、実施の形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施の形態に亘る構成要素を適宜組み合わせてもよい。

【符号の説明】

【0058】

1…半導体スイッチ、2…上相スイッチング素子、2a…ダイオード、3…下相スイッチング素子、4…第1のスイッチング素子、4a…ダイオード、5…第2のスイッチング素子、5a…ダイオード、6…直流電圧源、7…高速環流ダイオード、8…正極端子、9…負極端子、10…ロジック回路、11…駆動回路、12…低電圧直流電圧源、13…抵抗、14…ダイオード、15…抵抗、16…コンデンサ、I…インバータ回路、M…誘導性負荷、S…電力変換装置、S2…上相スイッチング素子の駆動信号、S4…第1のスイッチング素子の駆動信号、S5…第2のスイッチング素子の駆動信号、Sd…遅延信号

【技術分野】

【0001】

本発明は、誘導性負荷に電力を供給する電力変換装置に関する。

【背景技術】

【0002】

従来、モータ等の誘導性負荷を駆動する電力変換装置内のインバータ回路に設けられるスイッチング回路として順接続された主素子(IGBTやMOSFET)と逆接続された補助素子(MOSFET)の直列回路を使用し、さらにこの両素子の両端間に高速環流ダイオードを逆並列接続させた電力変換装置が提案されている(以下の特許文献1参照)。

【0003】

この特許文献1において開示される電力変換装置によると、回路構成を単純化しつつも従来のスイッチング素子のON、或いはOFFに伴って発生する還流ダイオードの逆回復電流を効果的に抑制することで、この逆回復電流による損失を低減させることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−193839号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上述の特許文献1に開示されている回路構成を採用すると、以下のような不具合が生ずる可能性がある。

【0006】

すなわち、上記特許文献1に開示された回路では、補助素子(逆接続されたMOSFET)を主素子(順接続されたIGBT)と同じ駆動信号で動作させることによって主素子の寄生ダイオードに起因する逆回復電流による損失を発生させなくしている。

【0007】

但し、インバータ回路を構成する上相のスイッチング素子がONからOFFとなり主素子と補助素子がONするまでの期間(高速環流ダイオードに負荷電流が流れている期間)は、主素子の出力容量へ充電される(チャージされる)電荷の影響によって主素子と補助素子の接続部に負電位が発生する可能性がある。

【0008】

上記特許文献1においては、補助素子に印加される瞬間的な負電位(特許文献1においては「サージ電圧」と表わされている)の発生に対処するため別途クランプ回路を設けて、チャージされた電荷を逃がす経路を確保している。また、併せて補助素子のゲート駆動用電源として利用する旨記載されている。

【0009】

また、例えば、フォトカプラを使用して制御用電源と駆動用電源とを絶縁することによってこの負電位発生による影響を受けないようにすることも不可能ではないが、フォトカプラ等の使用は新たな部品の追加となるため、回路構成を複雑にする。

【0010】

さらに、スイッチン速度向上による効率向上及びインバータ回路を構成する部品点数の削減、基板実装面積の低減を意図して、例えば、スーパージャンクションMOSFETを搭載するパワーモジュール(Power Module;以下、「PM」と表わす)をインバータ回路に利用しようとする場合に、負電位が発生することによって回路の誤動作を誘発する等、障害となる。なお、パワーモジュールとは、インバータ回路を構成するスイッチング素子とそのスイッチング素子の駆動回路を1つのパッケージに組み込んだ素子をいう。

【0011】

本発明は上記課題を解決するためになされたものであり、本発明の目的は、上相のスイッチング素子がONからOFFに切り替わった後、下相スイッチング素子がオンするまでの期間に下相スイッチング素子の第1のスイッチング素子の両端が電源から切り離された状態になることをなくしたため、第1のスイッチング素子と第2のスイッチング素子との接続部に負電圧が発生することを防止することができる電力変換装置を提供することである。また、絶縁を必要とせずにパワーモジュールへの適用を可能とすることでインバータ回路を構成する部品点数の削減、基板実装面積の低減を図ることのできる電力変換装置を提供することである。

【課題を解決するための手段】

【0012】

本発明の実施の形態に係る特徴は、直流電圧源に直列に接続され、スイッチング信号に基づくONまたはOFF制御により誘導性負荷に電力を供給する上相スイッチング素子と下相スイッチング素子とから構成される半導体スイッチを備える電力変換装置であって、下相スイッチング素子は、逆導通性能を有し、高耐圧な第1のスイッチング素子と、第1のスイッチング素子に比べて低耐圧な第2のスイッチング素子と、第1のスイッチング素子の負極と第2のスイッチング素子の負極とを接続して第1のスイッチング素子の正極を正極端子とし、第2のスイッチング素子の正極を負極端子とし、正極端子と負極端子との間に負極端子から正極端子に向かう方向が順方向となるように並列に接続される高速環流ダイオードと、上相スイッチング素子がオン中に第2のスイッチング素子をオンさせ、その後、上相スイッチング素子のオフ中は第2のスイッチング素子のオンを継続させる駆動信号を出力するロジック回路とを備える。

【発明の効果】

【0013】

本発明によれば、上相のスイッチング素子がONからOFFに切り替わった後、下相スイッチング素子がオンするまでの期間に下相スイッチング素子の第1のスイッチング素子の両端が電源から切り離された状態になることをなくしたため、第1のスイッチング素子と第2のスイッチング素子との接続部に負電圧が発生することを防止することができる電力変換装置を提供することができる。また、絶縁を必要とせずにパワーモジュールへの適用を可能とすることでインバータ回路を構成する部品点数の削減、基板実装面積の低減を図ることのできる電力変換装置を提供することができる。

【図面の簡単な説明】

【0014】

【図1】本発明の実施の形態における電力変換装置に使用される半導体スイッチの構成を示す回路図である。

【図2】本発明の実施の形態における電力変換装置に使用される半導体スイッチに印加される駆動信号を示すタイムチャートである。

【図3】図2に示すタイムチャートに基づく電流の流れを示す回路図である。

【図4】図2に示すタイムチャートに基づく電流の流れを示す回路図である。

【図5】図2に示すタイムチャートに基づく電流の流れを示す回路図である。

【図6】図2に示すタイムチャートに基づく電流の流れを示す回路図である。

【図7】本発明の実施の形態における電力変換装置に使用されるインバータ回路として、半導体スイッチ素子を内蔵するPMを利用した場合の回路構成の一例を示す回路図である。

【発明を実施するための形態】

【0015】

以下、本発明の実施の形態について図面を参照して詳細に説明する。

【0016】

図1は、本発明の実施の形態における電力変換装置に使用される半導体スイッチ1の構成を示す回路図である。半導体スイッチ1は、上相のスイッチング素子2と、下相のスイッチング素子3とから構成される。下相のスイッチング素子3は、さらに第1のスイッチング素子4と第2のスイッチング素子5を備える。

【0017】

なお、電力変換装置では、このような半導体スイッチ1の2組または3組が直流電圧源6に並列接続された構成とするのが一般的である。半導体スイッチ1を2組とした場合、単相出力のインバータ回路となり、3組とした場合は3相出力のインバータ回路が構成される。

【0018】

上相スイッチング素子2及び下相スイッチング素子3(第1のスイッチング素子4及び第2のスイッチング素子5)は、直列に接続される。これら上相スイッチング素子2及び下相スイッチング素子3の両端は、直流電圧源6の電源ラインに接続されている。さらに直列に接続される第1のスイッチング素子4及び第2のスイッチング素子5に対して高速環流ダイオード7が逆並列に接続されている。

【0019】

上相スイッチング素子2には、例えば、電圧駆動型素子でありIGBTが好適に用いられる。また、上相スイッチング素子2の両端には、電流の流れが逆になるように並列接続された逆並列ダイオード2aが設けられる。

【0020】

第1のスイッチング素子4は、例えば、高い耐圧性能を備える高耐圧な電圧駆動型素子であり、例えば、スーパージャンクションMOSFETが好適に使用される。第1のスイッチング素子には、ダイオード4a(寄生ダイオード)が逆並列接続されている。

【0021】

第2のスイッチング素子5は、第1のスイッチング素子4に比べれば低い耐圧性能を備える電圧駆動型素子である。第2のスイッチング素子5には、低耐圧なMOSFETが好適に使用され、ダイオード5a(寄生ダイオード)が逆並列接続されている。

【0022】

第1のスイッチング素子4と第2のスイッチング素子5の接続は、第1のスイッチング素子4の負極と第2のスイッチング素子5の負極とが接続されて行われる。第1のスイッチング素子4の正極が正極端子8となり、第2のスイッチング素子5の正極が負極端子9となる。

【0023】

高速環流ダイオード7は、この正極端子8と負極端子9との間に負極端子9から正極端子8に向かう方向が順方向となるように並列に接続される。この高速環流ダイオード7は、例えば、第1のスイッチング素子4の逆並列ダイオード4aに比べて、チップ面積が小さく、順方向の電圧降下は高く、逆回復特性に優れる素子が用いられる。

【0024】

第2のスイッチング素子5に対しては、ロジック回路10、及び駆動回路11を介して駆動信号が印加される。このロジック回路10、及び駆動回路11には、直流電圧源6よりも電圧値が低い低電圧直流電圧源12によって電圧が印加される。

【0025】

なお、本発明の実施の形態においては、この駆動回路11については、高耐圧な回路が使用されている。ロジック回路10には、外部で生成される上相スイッチング素子2の駆動信号(ON/OFF指令)S2と第1のスイッチング素子4に印加される駆動信号(ON/OFF指令)S4が入力される。ロジック回路10は、この2つの信号を論理演算することで、第2のスイッチング素子5のON/OFFタイミングを生成する。

【0026】

駆動回路11と第2のスイッチング素子5との間には抵抗13が接続されている。また、低電圧直流電圧源12と直列に、ダイオード14、抵抗15、コンデンサ16がそれぞれ接続されている。なお、上相スイッチング素子2及び第1のスイッチング素子4に対する駆動回路等については一般的な構成であるため、図1では図示を省略する。

【0027】

図2は、本発明の実施の形態における電力変換装置Sに使用される半導体スイッチ1に印加される駆動信号を説明するタイムチャートである。最上段から最下段へ向けて順に、上相スイッチング素子2の駆動信号S2、第1のスイッチング素子4の駆動信号S4、駆動信号S2を所定期間遅延させた遅延信号Sd、及び第2のスイッチング素子5の駆動信号(ON/OFF指令)S5である。

【0028】

上相スイッチング素子2の駆動信号S2、第1のスイッチング素子4の駆動信号S4は、図示しない制御回路から出力されてくるもので、一般的には、PWM生成器から出力されるPWM信号を上相スイッチング素子2の駆動信号S2とする。また、この信号を反転させた信号に、さらに上相スイッチング素子2と第1のスイッチング素子4が同時にONして短絡しないように立ち上がりに遅延を設けた信号を第1のスイッチング素子4の駆動信号S4としている。なお、同様の理由で上相スイッチング素子2の駆動信号S2も立ち上がりには遅延が設けられている。

【0029】

駆動信号S2を所定期間遅延させた遅延信号Sdは、上述のロジック回路10内で生成される信号で、さらにロジック回路10は、この遅延信号Sdの立ち上がり(ON)に同期してONとなり、その後の第1のスイッチング素子4の駆動信号S4の立下りに同期してOFFする信号を生成する。この生成信号が第2のスイッチング素子5の駆動信号(ON/OFF指令)S5となる。

【0030】

この結果、上相スイッチング素子2がONしている間に第2のスイッチング素子5がONし、その後、上相スイッチング素子2がOFFした後に第1のスイッチング素子4がONしてOFFするまでの期間、第2のスイッチング素子5はONを継続する。

【0031】

このため、上相スイッチング素子2がOFFした後、第1のスイッチング素子4がONするまでの間も第1のスイッチング素子4の負極は、第2のスイッチング素子5を経由して直流電圧源6のグランド側に接続されるため、第1のスイッチング素子4の負極には負電圧が発生しない。

【0032】

すなわち、第2のスイッチング素子5は、上相スイッチング素子2がONからOFFに変わり、その後、第1のスイッチング素子4がONするまでの期間は少なくともONする。従って、第1のスイッチング素子4と第2のスイッチング素子5とは別の駆動信号にて動作する。

【0033】

以下、図2のタイムチャート及び図3ないし図6の回路図を用いて、半導体スイッチ1の動きについて説明する。なお、説明の便宜上、図2のタイムチャートには破線で区切ってAないしEの5つの期間を設けている。

【0034】

まずA及びBの期間についてである。上相スイッチング素子2に対しては、Aの期間開始時に駆動信号S2が印加(ON)され、Bの期間終了時に駆動信号S2はOFFされる。一方、第1のスイッチング素子4についてはA、Bの期間通して駆動信号S4は印加(ON)されない(OFFのまま)。

【0035】

第2のスイッチング素子5に対しては、上述の駆動信号S5が印加される。駆動信号S5の立ち上がりは遅延信号Sdの立ち上がり(ON)と同期し、図2に示されているように、上相スイッチング素子2に印加される駆動信号S2からAの期間分だけ遅れて出力が追従して立ち上がる(ONとなる)。

【0036】

本発明の実施の形態においては、Aの期間(時間)は1μsecである。但し、この期間(時間)は上相スイッチング素子2がON中にAの期間が終了する範囲内で任意に設定することができる。このように第2のスイッチング素子5の立ち上がりは、遅延信号Sdの立ち上がりと同期する。このため、第2のスイッチング素子5は、上相スイッチング素子2がON中のBの期間開始時に駆動信号(ON)が印加され、ONする。

【0037】

第2のスイッチング素子5はBの期間開始時にONとなるが、第1のスイッチング素子4はOFFの状態にある。従って、図3に示すように、直流電圧源6からの電流は上相のスイッチング素子2を経由して負荷側に流れる。この際、第1のスイッチング素子4には上相スイッチング素子2がONされていることによって、直流電圧源6からの電圧分の電荷がチャージされる。

【0038】

次にCの期間である。この期間は上相スイッチング素子2がOFFしてから第1のスイッチング素子4がONするまでの期間である。従来、このCの期間は、第1のスイッチング素子4へ充電された(チャージされた)電荷の影響によって第2のスイッチング素子5の両端間に負電位が発生する期間となる。このような負電位の発生を抑制することが本発明の目的である。

【0039】

図2に示すように、このCの期間、上相スイッチング素子2はOFFのままである。一方、第1のスイッチング素子4はOFF、第2のスイッチング素子5はONの状態である。第2のスイッチング素子5はONのままであるので、環流電流は、図4に示すように、主に第1のスイッチング素子4の逆並列ダイオード4aを経由して流れる。これは、高速環流ダイオード7に全く電流が流れない訳ではないが、高速環流ダイオード7の電圧の方が、第2のスイッチング素子5のON抵抗と第1のスイッチング素子4の順電圧との和よりも大きいからである。

【0040】

このように、Cの期間中第2のスイッチング素子5をONし続けることによって、A及びBの期間中に第1のスイッチング素子4にチャージされた電荷を放電する経路を確保することが可能となる。従って、チャージされた電荷の存在による第1のスイッチング素子4と第2のスイッチング素子5との接続点と、負極端子9との間において負電圧が発生することがなくなる。

【0041】

Dの期間は、上相スイッチング素子2はOFFの状態が継続する。第1のスイッチング素子4は駆動信号が印加されてONの状態となる。第1のスイッチング素子4がONの状態にあるので、第2のスイッチング素子5もONの状態が維持される。

【0042】

従って、図5に示すように、環流電流は第1のスイッチング素子4及び第2のスイッチング素子5を経由して流れる。また、第1のスイッチング素子4及び第2のスイッチング素子5のいずれもがONの状態にあるため、環流電流は高速環流ダイオード7に流れない。

【0043】

なお、CからDの期間への転流時は、既に第2のスイッチング素子5がONとなっているため、第1のスイッチング素子4の逆並列ダイオード4aへの逆電圧が印加されることはなく、過大な逆回復電流が発生することもない。

【0044】

Eの期間は、第1のスイッチング素子4及び第2のスイッチング素子5のいずれもOFFとなる。従って、図6に示すように、環流電流は全て高速環流ダイオード7に流れる。上述したように、Cの期間に第1のスイッチング素子4にチャージされた電荷は全て放電されているので、第1のスイッチング素子4と第2のスイッチング素子5との接続点と、負極端子9との間において負電圧が発生することはない。

【0045】

なお、直流電圧源6からの電流が逆方向、すなわち、上相スイッチング素子2の逆並列ダイオード2aに環流電流が流れる場合であってもこの逆並列ダイオード2aは十分に高速であるため、過大な逆回復電流が発生することはない。

【0046】

図7は、本発明の実施の形態における電力変換装置Sに使用されるインバータ回路Iとして、半導体スイッチ1を内蔵するパワーモジュールへ適用した場合の回路構成の一例を示す回路図である。電力変換装置Sにおいては、直流電圧源6の電源ラインにインバータ回路Iが接続され、このインバータ回路Iの出力側に、例えばモータ等の誘導性負荷Mが接続されている。

【0047】

インバータ回路Iは、上相スイッチング素子2Uないし2Wと下相スイッチング素子とが三相ブリッジ接続される。ここで、上相スイッチング素子2Uと下相スイッチング素子である第1のスイッチング素子4X及び第2のスイッチング素子5X、上相スイッチング素子2Vと下相スイッチング素子である第1のスイッチング素子4Y及び第2のスイッチング素子5Y、上相スイッチング素子2Wと下相スイッチング素子である第1のスイッチング素子4Z及び第2のスイッチング素子5Zが、それぞれ一対の主回路スイッチング素子を構成している。

【0048】

上相スイッチング素子2U、2V、2Wに対してそれぞれ駆動回路Ua,Va,Waが設けられている。3つの第1のスイッチング素子4X、4Y、4Zの駆動回路Daは、グランド側が共通であるため、電源が共通にできるため1つの駆動回路でまかなわれている。第2のスイッチング素子5X,5Y,5Zにはそれぞれ駆動回路11X、11Y、11Zが設けられるが、ロジック回路10は、この3つの第2のスイッチング素子5X,5Y,5Zに対して1つとし、第2のスイッチング素子5X,5Y,5Zの各々に対応した3種類の駆動信号を出力する。

【0049】

図7に示されているインバータ回路Iは、パワーモジュールの使用に関して2種類の態様を示している。

【0050】

1つ目は、破線で示される従来から使用されているパワーモジュールPM1を用いた場合で、パワーモジュールPM1内には、上相スイッチング素子2及び下相スイッチング素子3のうち第1のスイッチング素子4、各スイッチング素子の駆動回路Wa,Va,Ua及び駆動回路Daが内蔵されている態様である。

【0051】

すなわち、第2のスイッチング素子5X,5Y,5Z、高速環流ダイオード7U,7V,7W、ロジック回路10及び駆動回路11X、11Y、11Zは、パワーモジュールPM1の外部で接続されている。このように、図7の破線に示されるような既存のパワーモジュールPM1を用いても本発明のインバータ回路Iを構成することができる。

【0052】

2つ目は、インバータ回路I全体をパワーモジュールPM2内に組み込んだものである。この場合、上相スイッチング素子2、第1のスイッチング素子4及び駆動回路Wa,Va,Uaとともに、第2のスイッチング素子5X,5Y,5Z、高速環流ダイオード7U,7V,7W、ロジック回路10、及び駆動回路11X、11Y、11Z及び駆動回路Daをも、図7に太実線で表わされているようにパワーモジュールPM2内に内蔵させる。

【0053】

このように主回路スイッチング素子及び周辺回路すべてをパワーモジュールPM2に内蔵させる構成とすることによって、インバータ回路Iをモジュール化することができ、電力変換装置Sを構成する部品点数を大幅に減らすことができる。

【0054】

なお、パワーモジュールPM2の端子S21〜S23は、3つの上相スイッチング素子2W〜2Uの駆動信号の入力端子で、端子S41〜S43は、3つの第1のスイッチング素子4Z〜4Xの駆動信号の入力端子である。さらに、パワーモジュールPM2の端子Hと端子Lは、3つの上相スイッチング素子2W〜2Uの駆動電源端子となっている。

【0055】

また、パワーモジュールPM2の外部において各第2のスイッチング素子5X,5Y,5Zと負側の電源ラインとの間には、ベクトル制御及び過電流保護用の電流検出用抵抗R1〜R3が設けられている。 そして、上述したように、本発明の実施の形態によれば、上相のスイッチング素子がONからOFFに切り替わった後、下相スイッチング素子がオンするまでの期間に第1のスイッチング素子4の端子に負電位を発生させなくすることができ、絶縁処理が不要となることから、すべてのスイッチング素子とその駆動回路をパワーモジュールPM2内に内蔵しても誤動作や素子の破壊などの問題が生じず、好適である。なお、部品点数が若干増加するが、ロジック回路10をパワーモジュールPM2の外部に設けることも可能である。

【0056】

以上説明した構成を採用することによって、上相のスイッチング素子がONからOFFに切り替わった後、下相スイッチング素子がオンするまでの期間に下相スイッチング素子の第1のスイッチング素子の両端が電源から切り離された状態になることをなくしたため、第1のスイッチング素子と第2のスイッチング素子との接続部に負電圧が発生することを防止することができる。また、絶縁を必要とせずにパワーモジュールへの適用を可能とすることでインバータ回路を構成する部品点数の削減、基板実装面積の低減を図ることのできる電力変換装置を提供することができる。

【0057】

なお、この発明は、上記実施の形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施の形態に開示されている複数の構成要素を適宜組み合わせることにより種々の発明を形成できる。例えば、実施の形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施の形態に亘る構成要素を適宜組み合わせてもよい。

【符号の説明】

【0058】

1…半導体スイッチ、2…上相スイッチング素子、2a…ダイオード、3…下相スイッチング素子、4…第1のスイッチング素子、4a…ダイオード、5…第2のスイッチング素子、5a…ダイオード、6…直流電圧源、7…高速環流ダイオード、8…正極端子、9…負極端子、10…ロジック回路、11…駆動回路、12…低電圧直流電圧源、13…抵抗、14…ダイオード、15…抵抗、16…コンデンサ、I…インバータ回路、M…誘導性負荷、S…電力変換装置、S2…上相スイッチング素子の駆動信号、S4…第1のスイッチング素子の駆動信号、S5…第2のスイッチング素子の駆動信号、Sd…遅延信号

【特許請求の範囲】

【請求項1】

直流電圧源に直列に接続され、スイッチング信号に基づくONまたはOFF制御により誘導性負荷に電力を供給する上相スイッチング素子と下相スイッチング素子とから構成される半導体スイッチを備える電力変換装置であって、

前記下相スイッチング素子は、

逆導通性能を有し、高耐圧な第1のスイッチング素子と、

前記第1のスイッチング素子に比べて低耐圧な第2のスイッチング素子と、

前記第1のスイッチング素子の負極と前記第2のスイッチング素子の負極とを接続して前記第1のスイッチング素子の正極を正極端子とし、前記第2のスイッチング素子の正極を負極端子とし、前記正極端子と前記負極端子との間に前記負極端子から前記正極端子に向かう方向が順方向となるように並列に接続される高速環流ダイオードと、

前記上相スイッチング素子がオン中に第2のスイッチング素子をオンさせ、その後、前記上相スイッチング素子のオフ中は前記第2のスイッチング素子のオンを継続させる駆動信号を出力するロジック回路とを備えたことを特徴とする電力変換装置。

【請求項2】

前記電力変換装置は、前記上相スイッチング素子と前記第1のスイッチング素子と、前記上相スイッチング素子と前記第1のスイッチング素子の各駆動回路とを内蔵したパワーモジュールを備えることを特徴とする請求項1に記載の電力変換装置。

【請求項3】

前記電力変換装置は、前記半導体スイッチを構成する前記スイッチング素子の全て及び各スイッチング素子の駆動回路、前記高速環流ダイオードが内蔵されるパワーモジュールを備えることを特徴とする請求項1に記載の電力変換装置。

【請求項1】

直流電圧源に直列に接続され、スイッチング信号に基づくONまたはOFF制御により誘導性負荷に電力を供給する上相スイッチング素子と下相スイッチング素子とから構成される半導体スイッチを備える電力変換装置であって、

前記下相スイッチング素子は、

逆導通性能を有し、高耐圧な第1のスイッチング素子と、

前記第1のスイッチング素子に比べて低耐圧な第2のスイッチング素子と、

前記第1のスイッチング素子の負極と前記第2のスイッチング素子の負極とを接続して前記第1のスイッチング素子の正極を正極端子とし、前記第2のスイッチング素子の正極を負極端子とし、前記正極端子と前記負極端子との間に前記負極端子から前記正極端子に向かう方向が順方向となるように並列に接続される高速環流ダイオードと、

前記上相スイッチング素子がオン中に第2のスイッチング素子をオンさせ、その後、前記上相スイッチング素子のオフ中は前記第2のスイッチング素子のオンを継続させる駆動信号を出力するロジック回路とを備えたことを特徴とする電力変換装置。

【請求項2】

前記電力変換装置は、前記上相スイッチング素子と前記第1のスイッチング素子と、前記上相スイッチング素子と前記第1のスイッチング素子の各駆動回路とを内蔵したパワーモジュールを備えることを特徴とする請求項1に記載の電力変換装置。

【請求項3】

前記電力変換装置は、前記半導体スイッチを構成する前記スイッチング素子の全て及び各スイッチング素子の駆動回路、前記高速環流ダイオードが内蔵されるパワーモジュールを備えることを特徴とする請求項1に記載の電力変換装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2011−41348(P2011−41348A)

【公開日】平成23年2月24日(2011.2.24)

【国際特許分類】

【出願番号】特願2009−183773(P2009−183773)

【出願日】平成21年8月6日(2009.8.6)

【出願人】(505461072)東芝キヤリア株式会社 (477)

【Fターム(参考)】

【公開日】平成23年2月24日(2011.2.24)

【国際特許分類】

【出願日】平成21年8月6日(2009.8.6)

【出願人】(505461072)東芝キヤリア株式会社 (477)

【Fターム(参考)】

[ Back to top ]