電力用半導体モジュールの駆動回路

【課題】低損失で高効率のゲート駆動回路を提供する。

【解決手段】昇圧を目的とする第1の半導体スイッチ5を駆動するゲート駆動回路11の内部回路定数を、前記第1の半導体スイッチに対して直列に接続され電源回生を目的とする第2の半導体スイッチ4を駆動するゲート駆動回路10の内部回路定数に比べて、スイッチング時間が短くなるように設定(選択)することにより、サージ電圧は高くなるが、その代わりにスイッチング損失を低減できるようにし、高効率,低コスト化を実現する。

【解決手段】昇圧を目的とする第1の半導体スイッチ5を駆動するゲート駆動回路11の内部回路定数を、前記第1の半導体スイッチに対して直列に接続され電源回生を目的とする第2の半導体スイッチ4を駆動するゲート駆動回路10の内部回路定数に比べて、スイッチング時間が短くなるように設定(選択)することにより、サージ電圧は高くなるが、その代わりにスイッチング損失を低減できるようにし、高効率,低コスト化を実現する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、直流電圧を異なる直流電圧へと双方向に変換することが可能な、DC/DC(直流/直流)変換装置などの電力変換装置に適用して好適な電力用半導体モジュールの駆動回路に関する。

【背景技術】

【0002】

図2に、バッテリなどの直流電圧源から昇圧して負荷側に電力を供給するDC/DC変換システムの例を示す。

1は直流電圧源(電圧値:Vb)、2は昇圧用のリアクタ、3は電力用半導体モジュールで、4,5はスイッチ素子であるIGBT(絶縁ゲートバイポーラトランジスタ)、6,7はIGBTに逆並列に接続されているダイオード(FWD)、8は昇圧側の電位安定化のためのコンデンサ(電圧値:Ed)、9はモータなどの負荷である。また、10,11はIGBT4,5駆動用のゲート駆動回路、12はシステムの制御回路で、主に直流電圧Edの値に基づきIGBT4,5のオン・オフ信号を作成し、その信号をゲート駆動回路10,11に伝送する。また、13は、電力用半導体モジュール3とコンデンサ8間の配線インダクタンスを示している。

【0003】

通常電力供給モード(パワーフローA)の場合は、IGBT5をオン・オフさせることで、次の(1)式に基づく昇圧動作が行なわれる。γは通電率を示す。

Ed=Vb/(1−γ) …(1)

図3(a),(b)にIGBT5がオンしている場合と、オフしている場合の電流経路を示す。

【0004】

一方、電力回生モード(パワーフローB)の場合は、IGBT4をオン・オフさせることで、降圧動作が行なわれる。

図4(a),(b)にIGBT4がオンしている場合と、オフしている場合の電流経路を示す。

【0005】

そして、直流電圧Edの実際(検出)値が或る設定電圧値16より低いとコンパレータ17で判断したときは、電力供給モードとしてIGBT5をオン・オフさせる。このとき、IGBT5がオフ時にはダイオード6が導通する。また、直流電圧Edの検出値が設定電圧値16より高い場合(負荷側に接続しているモータが、発電機モードになった場合に発生する)は、IGBT4をオン・オフさせる。このとき、IGBT4がオフ時にはダイオード7が動作する。

【0006】

図5に例えば特許文献1に開示されたゲート駆動回路の例を示す。

18がゲート駆動電源(Vg)、19がターンオン用のスイッチ、20がターンオフ用のスイッチ、21がターンオン用ゲート抵抗(Rgon)、22がターンオフ用ゲート抵抗(Rgoff)、23がターンオン速度調整用のコンデンサ(Cg)である。

外部制御回路12からのオン・オフ指令信号によって、フォトカプラなどの絶縁器25を介してスイッチ19,20が動作し、IGBTのオン・オフが行なわれる。

【0007】

通常、IGBTのターンオフスイッチング時間は、ゲート抵抗22が低抵抗であるほど短くなる。また、IGBTのターンオンスイッチング時間は、ゲート抵抗21が低抵抗であるほど、ゲート駆動電源18(Vg)が高いほど、ターンオン調整用コンデンサ23の容量が小容量なほど短くなる。すなわち、ゲート駆動回路定数が異なると、IGBTの入力容量を充電(ターンオンする場合)または放電(ターンオフする場合)する時間が変化するため、IGBTのスイッチング時間が短くなる(長くなる)。

【0008】

上記特許文献1の外に、特許文献2〜4に示すものがある。

特許文献2は、下アーム側IGBTのターンオン動作遅れを補償するために、下アーム側のゲート駆動回路のターンオン側のスイッチング時間を短くする、つまり上下アームのターンオンスイッチング時間を等しくすることを目的とし、かつ下アーム側のエミッタと補助エミッタ間の配線インダクタンスが上アーム側と比べて大きいことが前提(上アーム側が大きい場合は成立しない)であり、またゲート駆動回路の操作はターンオン時のみに限られている。

【0009】

特許文献3は、IGBTが微小時間オフ後のターンオン時に、対向アームのダイオード(FWD)に急峻なサージ電圧が発生するのを防止する目的で、ターンオン時のスイッチング時間を長くするものである。これもゲート駆動回路の操作はターンオン時のみに限られており、この機能は上下のゲート駆動回路に共通に設けられるものである。

また、特許文献4は、インバータの直流中間の電圧に応じて、高い場合はサージ電圧を抑制し、低い場合は低スイッチング損失化を実現する観点からゲート抵抗値を大きく(または小さく)するものであるが、この機能は上下のゲート駆動回路ともに必要で、さらには切替回路や複数のゲート抵抗を必要として複雑になる。

【0010】

【特許文献1】特開2003−116263号公報

【特許文献2】特開平05−328735号公報

【特許文献3】特開2003−143831号公報

【特許文献4】特開2002−125363号公報

【発明の開示】

【発明が解決しようとする課題】

【0011】

図6に、図5のIGBT4(5)がターンオフする際のコレクタ電流とコレクタ・エミッタ間電圧波形例を示す。同図中に示すサージ電圧(Vsurge)は、直流電圧をEd、配線インダクタンスをL、コレクタ電流の変化率をdi/dtとして、次の(2)式で表わされる。

Vsurge=Ed+L・di/dt …(2)

システムの設計上、Vsurgeの最大値はIGBTやダイオードの電圧定格以下にすることが要求される。例えば、直流電圧Edが高いほど、スイッチング時のdi/dtを低減させることが必要となる。

【0012】

すなわち、図5のシステムでは電源回生モードの場合を考慮して、システムの最高直流電圧値(Edmax)を想定して、ゲート駆動回路の設計をするなど(スイッチング時のdi/dtを低減させるため、ゲート抵抗を高抵抗化するなど)の必要がある。そのトレードオフとして、スイッチング損失が大きくなるため(スイッチング時間が長くなるため)、変換効率の低下やモジュールの大型化によるコストアップなどの新たな問題が発生する。

また、図示しないが、IGBT4(5)がターンオンする際、対向アームのダイオード7(6)に同様のサージ電圧が印加されるため、ターンオン側のゲート駆動回路の設計にも最高直流電圧値(Edmax)を考慮する必要がある。

【0013】

したがって、この発明の課題は、スイッチング損失を低減し、高効率,低コスト化を図ることにある。

【課題を解決するための手段】

【0014】

このような課題を解決するため、請求項1の発明では、直流電源から高電圧に変換して負荷に電力を供給し、負荷の電圧が或る値以上になったときは直流電源側に電源回生が可能なDC/DC変換回路に用いられ、直列接続された第1,第2の半導体スイッチからなる電力用半導体モジュールの駆動回路において、

前記直流電源と並列に接続され昇圧を目的とする前記第1の半導体スイッチを駆動するゲート駆動回路の内部回路定数に対して、前記第1の半導体スイッチと直列に接続され電源回生を目的とする第2の半導体スイッチを駆動するゲート駆動回路の内部回路定数を、互いに異なる値に設定することを特徴とする。

【0015】

上記請求項1の発明においては、前記第1の半導体スイッチのゲート駆動回路の方が、前記第2の半導体スイッチを駆動するゲート駆動回路と比較して、半導体スイッチのスイッチング時間が短くなるように回路定数を選択することができる(請求項2の発明)。

この請求項2の発明においては、前記半導体スイッチのスイッチング時間が短くする手段として、前記第1の半導体スイッチのゲート駆動回路のゲート抵抗値を、前記第2の半導体スイッチを駆動するゲート駆動回路のゲート抵抗値と比較して小さくすることができる(請求項3の発明)。

【0016】

また、請求項2の発明においては、前記半導体スイッチのスイッチング時間が短くする手段として、前記第1の半導体スイッチのゲート駆動回路のゲート・エミッタ間コンデンサ容量を、前記第2の半導体スイッチを駆動するゲート駆動回路のゲート・エミッタ間コンデンサ容量と比較して小さくすることができ(請求項4の発明)、または、前記半導体スイッチのスイッチング時間が短くする手段として、前記第1の半導体スイッチのゲート駆動回路のゲート電圧を、前記第2の半導体スイッチを駆動するゲート駆動回路のゲート電圧と比較して高くすることができる(請求項5の発明)。

【発明の効果】

【0017】

この発明によれば、昇圧を目的とする第1の半導体スイッチを駆動するゲート駆動回路の内部回路定数を、前記第1の半導体スイッチと直列に接続され電源回生を目的とする第2の半導体スイッチを駆動するゲート駆動回路の内部回路定数と比較して、スイッチング時間が短くなるように設定することで、サージ電圧は高くなるが、その代わりにスイッチング損失を減少させることができ、高効率で低コスト化が可能となる。

【発明を実施するための最良の形態】

【0018】

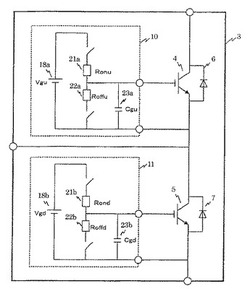

図1はこの発明の実施の形態を示す回路図である。これは、図2の電力用半導体モジュールの、特に図5で説明したゲート駆動回路の詳細を示すもので、その他は省略されている。

図1からも明らかなように、基本的な構成は従来例と同じである。したがって、その動作も従来と同じなので説明は省略するが、ここではそのゲート駆動回路に用いる回路定数を、上アーム(第1の半導体スイッチ)と下アーム(第2の半導体スイッチ)とで互いに異ならせるようにしている。

【0019】

駆動回路の主な回路定数として、上アームのゲート駆動電源電圧Vguと下アームのゲート駆動電源電圧Vgd、同じくターンオン用ゲート抵抗RonuとRond、同じくターンオフ用ゲート抵抗RoffuとRoffdおよび同じくターンオン速度調整用のコンデンサCguとCgdなどがある。このほかにも回路定数の要素としてはスイッチ素子特性(IGBTのゲート容量やゲート抵抗)、駆動回路の配線インダクタンスなどがあるが、設計上、変更・調整が容易なのは、ゲート駆動電源電圧,ターンオン用ゲート抵抗,ターンオフ用ゲート抵抗,ターンオン速度調整用のコンデンサの4種の定数である。

そして、上アーム側IGBTの方のスイッチング時間が長くなるように上記4種の回路定数のうち少なくとも1つをについて、異なった値に設定するものである。

【0020】

例えば、上アームと下アームの回路定数が少なくとも次いずれかの関係を満たすようにする。

上アーム側 下アーム側

Vgu < Vgd

Ronu > Rond

Roffu > Roffd

Cgu > Cgd

【0021】

このように、上アームのゲート駆動回路に用いる回路要素を、上記のような関係を有する定数とすることで、上アーム側IGBTのターンオンおよび/またはターンオフのスイッチング時間が長くなり、その結果、負荷側の直流電圧が高電圧の状況で駆動される上アーム側IGBT(下アーム側FWD)に印加されるサージ電圧は低減される。

一方、上アーム側IGBTのスイッチングと比較して負荷側の直流電圧が低電圧の状況で駆動される下アーム側IGBTは、低損失駆動が可能となる。

【図面の簡単な説明】

【0022】

【図1】この発明の実施の形態を示す回路図

【図2】DC/DC変換システムの一般的な例を示す構成図

【図3】図2の電力供給モードにおける電流経路の説明図

【図4】図2の電源回生モードにおける電流経路の説明図

【図5】ゲート駆動回路の従来例を示す回路図

【図6】図5のIGBTのターンオフ時の波形図

【符号の説明】

【0023】

1…直流電圧源、2…昇圧用リアクタ、3…電力用半導体モジュール、4,5…スイッチ素子(IGBT)、6,7…ダイオード、10,11…ゲート駆動回路、18,19…ゲート駆動電源、21a,21b…ターンオン用ゲート抵抗、22a,22b…ターンオフ用ゲート抵抗、23a,23b…ターンオン速度調整用コンデンサ。

【技術分野】

【0001】

この発明は、直流電圧を異なる直流電圧へと双方向に変換することが可能な、DC/DC(直流/直流)変換装置などの電力変換装置に適用して好適な電力用半導体モジュールの駆動回路に関する。

【背景技術】

【0002】

図2に、バッテリなどの直流電圧源から昇圧して負荷側に電力を供給するDC/DC変換システムの例を示す。

1は直流電圧源(電圧値:Vb)、2は昇圧用のリアクタ、3は電力用半導体モジュールで、4,5はスイッチ素子であるIGBT(絶縁ゲートバイポーラトランジスタ)、6,7はIGBTに逆並列に接続されているダイオード(FWD)、8は昇圧側の電位安定化のためのコンデンサ(電圧値:Ed)、9はモータなどの負荷である。また、10,11はIGBT4,5駆動用のゲート駆動回路、12はシステムの制御回路で、主に直流電圧Edの値に基づきIGBT4,5のオン・オフ信号を作成し、その信号をゲート駆動回路10,11に伝送する。また、13は、電力用半導体モジュール3とコンデンサ8間の配線インダクタンスを示している。

【0003】

通常電力供給モード(パワーフローA)の場合は、IGBT5をオン・オフさせることで、次の(1)式に基づく昇圧動作が行なわれる。γは通電率を示す。

Ed=Vb/(1−γ) …(1)

図3(a),(b)にIGBT5がオンしている場合と、オフしている場合の電流経路を示す。

【0004】

一方、電力回生モード(パワーフローB)の場合は、IGBT4をオン・オフさせることで、降圧動作が行なわれる。

図4(a),(b)にIGBT4がオンしている場合と、オフしている場合の電流経路を示す。

【0005】

そして、直流電圧Edの実際(検出)値が或る設定電圧値16より低いとコンパレータ17で判断したときは、電力供給モードとしてIGBT5をオン・オフさせる。このとき、IGBT5がオフ時にはダイオード6が導通する。また、直流電圧Edの検出値が設定電圧値16より高い場合(負荷側に接続しているモータが、発電機モードになった場合に発生する)は、IGBT4をオン・オフさせる。このとき、IGBT4がオフ時にはダイオード7が動作する。

【0006】

図5に例えば特許文献1に開示されたゲート駆動回路の例を示す。

18がゲート駆動電源(Vg)、19がターンオン用のスイッチ、20がターンオフ用のスイッチ、21がターンオン用ゲート抵抗(Rgon)、22がターンオフ用ゲート抵抗(Rgoff)、23がターンオン速度調整用のコンデンサ(Cg)である。

外部制御回路12からのオン・オフ指令信号によって、フォトカプラなどの絶縁器25を介してスイッチ19,20が動作し、IGBTのオン・オフが行なわれる。

【0007】

通常、IGBTのターンオフスイッチング時間は、ゲート抵抗22が低抵抗であるほど短くなる。また、IGBTのターンオンスイッチング時間は、ゲート抵抗21が低抵抗であるほど、ゲート駆動電源18(Vg)が高いほど、ターンオン調整用コンデンサ23の容量が小容量なほど短くなる。すなわち、ゲート駆動回路定数が異なると、IGBTの入力容量を充電(ターンオンする場合)または放電(ターンオフする場合)する時間が変化するため、IGBTのスイッチング時間が短くなる(長くなる)。

【0008】

上記特許文献1の外に、特許文献2〜4に示すものがある。

特許文献2は、下アーム側IGBTのターンオン動作遅れを補償するために、下アーム側のゲート駆動回路のターンオン側のスイッチング時間を短くする、つまり上下アームのターンオンスイッチング時間を等しくすることを目的とし、かつ下アーム側のエミッタと補助エミッタ間の配線インダクタンスが上アーム側と比べて大きいことが前提(上アーム側が大きい場合は成立しない)であり、またゲート駆動回路の操作はターンオン時のみに限られている。

【0009】

特許文献3は、IGBTが微小時間オフ後のターンオン時に、対向アームのダイオード(FWD)に急峻なサージ電圧が発生するのを防止する目的で、ターンオン時のスイッチング時間を長くするものである。これもゲート駆動回路の操作はターンオン時のみに限られており、この機能は上下のゲート駆動回路に共通に設けられるものである。

また、特許文献4は、インバータの直流中間の電圧に応じて、高い場合はサージ電圧を抑制し、低い場合は低スイッチング損失化を実現する観点からゲート抵抗値を大きく(または小さく)するものであるが、この機能は上下のゲート駆動回路ともに必要で、さらには切替回路や複数のゲート抵抗を必要として複雑になる。

【0010】

【特許文献1】特開2003−116263号公報

【特許文献2】特開平05−328735号公報

【特許文献3】特開2003−143831号公報

【特許文献4】特開2002−125363号公報

【発明の開示】

【発明が解決しようとする課題】

【0011】

図6に、図5のIGBT4(5)がターンオフする際のコレクタ電流とコレクタ・エミッタ間電圧波形例を示す。同図中に示すサージ電圧(Vsurge)は、直流電圧をEd、配線インダクタンスをL、コレクタ電流の変化率をdi/dtとして、次の(2)式で表わされる。

Vsurge=Ed+L・di/dt …(2)

システムの設計上、Vsurgeの最大値はIGBTやダイオードの電圧定格以下にすることが要求される。例えば、直流電圧Edが高いほど、スイッチング時のdi/dtを低減させることが必要となる。

【0012】

すなわち、図5のシステムでは電源回生モードの場合を考慮して、システムの最高直流電圧値(Edmax)を想定して、ゲート駆動回路の設計をするなど(スイッチング時のdi/dtを低減させるため、ゲート抵抗を高抵抗化するなど)の必要がある。そのトレードオフとして、スイッチング損失が大きくなるため(スイッチング時間が長くなるため)、変換効率の低下やモジュールの大型化によるコストアップなどの新たな問題が発生する。

また、図示しないが、IGBT4(5)がターンオンする際、対向アームのダイオード7(6)に同様のサージ電圧が印加されるため、ターンオン側のゲート駆動回路の設計にも最高直流電圧値(Edmax)を考慮する必要がある。

【0013】

したがって、この発明の課題は、スイッチング損失を低減し、高効率,低コスト化を図ることにある。

【課題を解決するための手段】

【0014】

このような課題を解決するため、請求項1の発明では、直流電源から高電圧に変換して負荷に電力を供給し、負荷の電圧が或る値以上になったときは直流電源側に電源回生が可能なDC/DC変換回路に用いられ、直列接続された第1,第2の半導体スイッチからなる電力用半導体モジュールの駆動回路において、

前記直流電源と並列に接続され昇圧を目的とする前記第1の半導体スイッチを駆動するゲート駆動回路の内部回路定数に対して、前記第1の半導体スイッチと直列に接続され電源回生を目的とする第2の半導体スイッチを駆動するゲート駆動回路の内部回路定数を、互いに異なる値に設定することを特徴とする。

【0015】

上記請求項1の発明においては、前記第1の半導体スイッチのゲート駆動回路の方が、前記第2の半導体スイッチを駆動するゲート駆動回路と比較して、半導体スイッチのスイッチング時間が短くなるように回路定数を選択することができる(請求項2の発明)。

この請求項2の発明においては、前記半導体スイッチのスイッチング時間が短くする手段として、前記第1の半導体スイッチのゲート駆動回路のゲート抵抗値を、前記第2の半導体スイッチを駆動するゲート駆動回路のゲート抵抗値と比較して小さくすることができる(請求項3の発明)。

【0016】

また、請求項2の発明においては、前記半導体スイッチのスイッチング時間が短くする手段として、前記第1の半導体スイッチのゲート駆動回路のゲート・エミッタ間コンデンサ容量を、前記第2の半導体スイッチを駆動するゲート駆動回路のゲート・エミッタ間コンデンサ容量と比較して小さくすることができ(請求項4の発明)、または、前記半導体スイッチのスイッチング時間が短くする手段として、前記第1の半導体スイッチのゲート駆動回路のゲート電圧を、前記第2の半導体スイッチを駆動するゲート駆動回路のゲート電圧と比較して高くすることができる(請求項5の発明)。

【発明の効果】

【0017】

この発明によれば、昇圧を目的とする第1の半導体スイッチを駆動するゲート駆動回路の内部回路定数を、前記第1の半導体スイッチと直列に接続され電源回生を目的とする第2の半導体スイッチを駆動するゲート駆動回路の内部回路定数と比較して、スイッチング時間が短くなるように設定することで、サージ電圧は高くなるが、その代わりにスイッチング損失を減少させることができ、高効率で低コスト化が可能となる。

【発明を実施するための最良の形態】

【0018】

図1はこの発明の実施の形態を示す回路図である。これは、図2の電力用半導体モジュールの、特に図5で説明したゲート駆動回路の詳細を示すもので、その他は省略されている。

図1からも明らかなように、基本的な構成は従来例と同じである。したがって、その動作も従来と同じなので説明は省略するが、ここではそのゲート駆動回路に用いる回路定数を、上アーム(第1の半導体スイッチ)と下アーム(第2の半導体スイッチ)とで互いに異ならせるようにしている。

【0019】

駆動回路の主な回路定数として、上アームのゲート駆動電源電圧Vguと下アームのゲート駆動電源電圧Vgd、同じくターンオン用ゲート抵抗RonuとRond、同じくターンオフ用ゲート抵抗RoffuとRoffdおよび同じくターンオン速度調整用のコンデンサCguとCgdなどがある。このほかにも回路定数の要素としてはスイッチ素子特性(IGBTのゲート容量やゲート抵抗)、駆動回路の配線インダクタンスなどがあるが、設計上、変更・調整が容易なのは、ゲート駆動電源電圧,ターンオン用ゲート抵抗,ターンオフ用ゲート抵抗,ターンオン速度調整用のコンデンサの4種の定数である。

そして、上アーム側IGBTの方のスイッチング時間が長くなるように上記4種の回路定数のうち少なくとも1つをについて、異なった値に設定するものである。

【0020】

例えば、上アームと下アームの回路定数が少なくとも次いずれかの関係を満たすようにする。

上アーム側 下アーム側

Vgu < Vgd

Ronu > Rond

Roffu > Roffd

Cgu > Cgd

【0021】

このように、上アームのゲート駆動回路に用いる回路要素を、上記のような関係を有する定数とすることで、上アーム側IGBTのターンオンおよび/またはターンオフのスイッチング時間が長くなり、その結果、負荷側の直流電圧が高電圧の状況で駆動される上アーム側IGBT(下アーム側FWD)に印加されるサージ電圧は低減される。

一方、上アーム側IGBTのスイッチングと比較して負荷側の直流電圧が低電圧の状況で駆動される下アーム側IGBTは、低損失駆動が可能となる。

【図面の簡単な説明】

【0022】

【図1】この発明の実施の形態を示す回路図

【図2】DC/DC変換システムの一般的な例を示す構成図

【図3】図2の電力供給モードにおける電流経路の説明図

【図4】図2の電源回生モードにおける電流経路の説明図

【図5】ゲート駆動回路の従来例を示す回路図

【図6】図5のIGBTのターンオフ時の波形図

【符号の説明】

【0023】

1…直流電圧源、2…昇圧用リアクタ、3…電力用半導体モジュール、4,5…スイッチ素子(IGBT)、6,7…ダイオード、10,11…ゲート駆動回路、18,19…ゲート駆動電源、21a,21b…ターンオン用ゲート抵抗、22a,22b…ターンオフ用ゲート抵抗、23a,23b…ターンオン速度調整用コンデンサ。

【特許請求の範囲】

【請求項1】

直流電源から高電圧に変換して負荷に電力を供給し、負荷の電圧が或る値以上になったときは直流電源側に電源回生が可能なDC/DC変換回路に用いられ、直列接続された第1,第2の半導体スイッチからなる電力用半導体モジュールの駆動回路において、

前記直流電源と並列に接続され昇圧を目的とする前記第1の半導体スイッチを駆動するゲート駆動回路の内部回路定数に対して、前記第1の半導体スイッチと直列に接続され電源回生を目的とする第2の半導体スイッチを駆動するゲート駆動回路の内部回路定数を、互いに異なる値に設定することを特徴とする電力用半導体モジュールの駆動回路。

【請求項2】

前記第1の半導体スイッチのゲート駆動回路の方が、前記第2の半導体スイッチを駆動するゲート駆動回路と比較して、半導体スイッチのスイッチング時間が短くなるように回路定数を選択することを特徴とする請求項1に記載の電力変換装置に用いられる電力用半導体モジュールの駆動回路。

【請求項3】

前記半導体スイッチのスイッチング時間が短くする手段として、前記第1の半導体スイッチのゲート駆動回路のゲート抵抗値を、前記第2の半導体スイッチを駆動するゲート駆動回路のゲート抵抗値と比較して小さくすることを特徴とする請求項2に記載の電力用半導体モジュールの駆動回路。

【請求項4】

前記半導体スイッチのスイッチング時間が短くする手段として、前記第1の半導体スイッチのゲート駆動回路のゲート・エミッタ間コンデンサ容量を、前記第2の半導体スイッチを駆動するゲート駆動回路のゲート・エミッタ間コンデンサ容量と比較して小さくすることを特徴とする請求項2に記載の電力用半導体モジュールの駆動回路。

【請求項5】

前記半導体スイッチのスイッチング時間が短くする手段として、前記第1の半導体スイッチのゲート駆動回路のゲート電圧を、前記第2の半導体スイッチを駆動するゲート駆動回路のゲート電圧と比較して高くすることを特徴とする請求項2に記載の電力用半導体モジュールの駆動回路。

【請求項1】

直流電源から高電圧に変換して負荷に電力を供給し、負荷の電圧が或る値以上になったときは直流電源側に電源回生が可能なDC/DC変換回路に用いられ、直列接続された第1,第2の半導体スイッチからなる電力用半導体モジュールの駆動回路において、

前記直流電源と並列に接続され昇圧を目的とする前記第1の半導体スイッチを駆動するゲート駆動回路の内部回路定数に対して、前記第1の半導体スイッチと直列に接続され電源回生を目的とする第2の半導体スイッチを駆動するゲート駆動回路の内部回路定数を、互いに異なる値に設定することを特徴とする電力用半導体モジュールの駆動回路。

【請求項2】

前記第1の半導体スイッチのゲート駆動回路の方が、前記第2の半導体スイッチを駆動するゲート駆動回路と比較して、半導体スイッチのスイッチング時間が短くなるように回路定数を選択することを特徴とする請求項1に記載の電力変換装置に用いられる電力用半導体モジュールの駆動回路。

【請求項3】

前記半導体スイッチのスイッチング時間が短くする手段として、前記第1の半導体スイッチのゲート駆動回路のゲート抵抗値を、前記第2の半導体スイッチを駆動するゲート駆動回路のゲート抵抗値と比較して小さくすることを特徴とする請求項2に記載の電力用半導体モジュールの駆動回路。

【請求項4】

前記半導体スイッチのスイッチング時間が短くする手段として、前記第1の半導体スイッチのゲート駆動回路のゲート・エミッタ間コンデンサ容量を、前記第2の半導体スイッチを駆動するゲート駆動回路のゲート・エミッタ間コンデンサ容量と比較して小さくすることを特徴とする請求項2に記載の電力用半導体モジュールの駆動回路。

【請求項5】

前記半導体スイッチのスイッチング時間が短くする手段として、前記第1の半導体スイッチのゲート駆動回路のゲート電圧を、前記第2の半導体スイッチを駆動するゲート駆動回路のゲート電圧と比較して高くすることを特徴とする請求項2に記載の電力用半導体モジュールの駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2007−104739(P2007−104739A)

【公開日】平成19年4月19日(2007.4.19)

【国際特許分類】

【出願番号】特願2005−287334(P2005−287334)

【出願日】平成17年9月30日(2005.9.30)

【出願人】(503361248)富士電機デバイステクノロジー株式会社 (1,023)

【Fターム(参考)】

【公開日】平成19年4月19日(2007.4.19)

【国際特許分類】

【出願日】平成17年9月30日(2005.9.30)

【出願人】(503361248)富士電機デバイステクノロジー株式会社 (1,023)

【Fターム(参考)】

[ Back to top ]