電力用半導体装置及びその動作方法

【課題】電力用半導体装置がOFF状態の時に電源電圧の急峻な増加が発生した場合であっても、出力トランジスタがONすることを防止する。

【解決手段】本発明の電力用半導体装置は、電源端子と出力端子との間に接続された出力トランジスタと、出力トランジスタのゲートに接続された第1ノードを充放電し、出力トランジスタをON/OFF制御するゲート充放電回路と、第1ノードと出力端子との間に接続されたショートスイッチ回路と、ショートスイッチ回路を制御するショート制御回路と、を備える。ターンオン期間、ON期間及びターンオフ期間において、ショート制御回路は、ショートスイッチ回路を介した第1ノードと出力端子との間の電気的接続を切断する。OFF期間において、ショート制御回路は、ショートスイッチ回路を介して第1ノードと出力端子との間を電気的に接続する。

【解決手段】本発明の電力用半導体装置は、電源端子と出力端子との間に接続された出力トランジスタと、出力トランジスタのゲートに接続された第1ノードを充放電し、出力トランジスタをON/OFF制御するゲート充放電回路と、第1ノードと出力端子との間に接続されたショートスイッチ回路と、ショートスイッチ回路を制御するショート制御回路と、を備える。ターンオン期間、ON期間及びターンオフ期間において、ショート制御回路は、ショートスイッチ回路を介した第1ノードと出力端子との間の電気的接続を切断する。OFF期間において、ショート制御回路は、ショートスイッチ回路を介して第1ノードと出力端子との間を電気的に接続する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電力用半導体装置(power semiconductor device)及びその動作方法に関する。

【背景技術】

【0002】

負荷に対して電力を供給するための電力用半導体装置が知られている。例えば、インテリジェントパワーデバイス(IPD:Intelligent Power Device)と呼ばれる電力用半導体装置は、自動車の電子制御システムにおいて用いられ、マイコンからの命令に従ってヘッドライト等への電力供給を制御する。このような電力用半導体装置では、典型的には、ハイサイドスイッチが使用される(例えば、特許文献1、特許文献2参照)。

【0003】

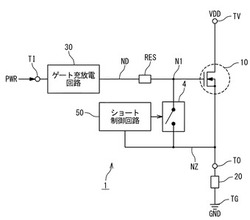

図1は、特許文献1に記載されている電力用半導体装置の構成を示している。この電力用半導体装置は、電源端子TV、入力端子TI、出力端子TO、出力トランジスタ10、及びゲート充放電回路30を備えている。電源端子TVには、電源電圧VDDが供給される。入力端子TIには、パワーON信号PWRが入力される。そのパワーON信号PWRの活性化に応答して、電力用半導体装置は出力端子TOから電力を出力する。

【0004】

出力トランジスタ10は、電源端子TVと出力端子TOとの間に接続されている。より詳細には、出力トランジスタ10は、NチャネルMOSFETであり、そのゲート、ドレイン及びソースは、それぞれノードND、電源端子TV及び出力端子TOに接続されている。出力端子TOは負荷20の一端に接続され、負荷20の他端はグランド端子TGに接続される。このように、出力トランジスタ10は、ハイサイドスイッチとして機能するように接続される。

【0005】

ゲート充放電回路30は、ノードNDを充放電し、それにより出力トランジスタ10をON/OFF制御する。より詳細には、ゲート充放電回路30は、制御入力回路31、昇圧回路32、放電トランジスタ(放電スイッチ)33、及びダイオード34、35を備えている。制御入力回路31は、パワーON信号PWRに応じて、昇圧回路32及び放電トランジスタ33を制御する。昇圧回路32は、ノードNDを、電源電圧VDDよりも高い高電圧まで充電する。放電トランジスタ33は、NチャネルMOSFETであり、そのゲート、バックゲート、ソース及びドレインは、それぞれノードNA、ノードNB、ノードNC及びノードNDに接続されている。ダイオード34のアノード及びカソードは、それぞれノードNC及びグランド端子に接続されている。ダイオード35のアノード及びカソードは、それぞれノードNC及び出力端子TOに接続されている。

【0006】

パワーON信号PWRが活性化されると、制御入力回路31は、昇圧回路32を活性化し、且つ、ノードNAにLowレベル信号を供給して放電トランジスタ33をOFFする。昇圧回路32は、ノードNDを、電源電圧VDDよりも高い高電圧まで充電する。その結果、出力トランジスタ10がONし、負荷20に電力が供給される。

【0007】

パワーON信号PWRが非活性化されると、制御入力回路31は、昇圧回路32を非活性化し、且つ、ノードNAにHighレベル信号を供給する。これにより、昇圧回路32が動作を停止する一方で、放電トランジスタ33がONする。その結果、ノードNDが放電され、出力トランジスタ10がOFFする。尚、ノードNDの電圧が、グランド電圧GNDからダイオード34またはダイオード35の順方向降下電圧(VF)分だけ高いレベルになると、放電トランジスタ33を介した放電は行われなくなる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平6−97375号公報

【特許文献2】特開2002−290221号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

ここで、本願発明者は、次のような課題を発見した。それは、上述のような電力用半導体装置を単一の半導体基板上に形成したときに、外部から印加されるサージ電圧により、出力トランジスタ10が熱破壊する可能性があるということである。この課題について、以下に説明する。

【0010】

上述のような電力用半導体装置において、出力トランジスタ10(パワーMOSFET)のオン抵抗は十分に低いことが望ましい。そのためには、出力トランジスタ10のゲートにつながるノードNDに、十分高い駆動電圧を印加する必要がある。このようにノードNDには高電圧が印加されるため、一般的には、高圧MOSFETが放電トランジスタ33として使用される。図2は、出力トランジスタ10及び放電トランジスタ33の一例の断面構造を示している。放電トランジスタ33は、高圧MOSFET構造を有している。

【0011】

この放電トランジスタ33は、図2に示されるような縦型の寄生バイポーラトランジスタを有する。図3は、その寄生バイポーラトランジスタを含めた回路構成を示している。図3に示されるように、放電トランジスタ33のドレイン及びバックゲートは、それぞれノードND及びノードNBに接続されており、寄生バイポーラトランジスタQ1のコレクタ、エミッタ及びベースは、それぞれ電源端子TV、ノードND及びノードNBに接続されている。また、寄生容量(コレクタ−ベース間容量)C1が、電源端子TVとノードNBとの間に生成される。

【0012】

ここで、電力用半導体装置(出力トランジスタ10)がOFF状態の時に、電源電圧VDDの急峻な増加が発生した場合を考える。OFF状態において、ノードNB(放電トランジスタ33のバックゲート)はハイインピーダンスとなっている。従って、電源電圧VDDの急峻な増加が発生すると、寄生容量C1を通して、ノードNBの電圧(寄生バイポーラトランジスタQ1のベース電圧)が持ち上がる。その結果、寄生バイポーラトランジスタQ1がONする。この時、コレクタ−エミッタ間電圧VCEが耐圧BVCEOを超えていると、大きな降伏電流が流れる。ここで、図4は、寄生バイポーラトランジスタQ1の電流−電圧特性を示している。コレクタ−エミッタ間電圧VCEが耐圧BVCEOを超えると、大きな降伏電流が流れることが分かる。

【0013】

この降伏電流により、出力トランジスタ10のゲートにつながるノードNDの電圧が持ち上がるため、出力トランジスタ10がONしてしまう。但し、この時、出力トランジスタ10は、高オン抵抗でオンする(ハーフオン)。この場合、出力トランジスタ10に過大な電力が印加されるため、熱破壊が発生する可能性がある。

【0014】

例えば、自動車に搭載される電力用半導体装置の電源端子TVは、バッテリーに接続される。この場合の電源電圧VDDの急峻な増加の一例として、図5に示されるような「ダンプサージ」が考えられる。ダンプサージとは、オルタネータの発電中にバッテリーが外れたときに、電源端子TVに発生するサージのことである。ダンプサージが電源端子TVに印加されると、上述の理由により、寄生バイポーラトランジスタQ1が動作し、出力トランジスタ10の熱破壊が発生する可能性がある。

【0015】

以上に説明されたように、電力用半導体装置がOFF状態の時に、電源電圧の急峻な増加が発生した場合、出力トランジスタがハーフオンして熱破壊される可能性があった。電力用半導体装置がOFF状態の時に、電源電圧の急峻な増加が発生した場合であっても、出力トランジスタがONすることを防止することができる技術が望まれる。

【課題を解決するための手段】

【0016】

本発明の1つの観点において、電力用半導体装置が提供される。その電力用半導体装置は、電源端子と出力端子との間に接続された出力トランジスタと、出力トランジスタのゲートに接続された第1ノードを充放電し、出力トランジスタをON/OFF制御するゲート充放電回路と、第1ノードと出力端子との間に接続されたショートスイッチ回路と、ショートスイッチ回路を制御するショート制御回路と、を備える。第1ノードが充電された後、出力トランジスタが安定的にONしている期間がON期間である。第1ノードが放電された後、出力トランジスタが安定的にOFFしている期間がOFF期間である。OFF期間からON期間への遷移期間がターンオン期間である。ON期間からOFF期間への遷移期間がターンオフ期間である。ターンオン期間、ON期間及びターンオフ期間において、ショート制御回路は、ショートスイッチ回路を介した第1ノードと出力端子との間の電気的接続を切断する。OFF期間において、ショート制御回路は、ショートスイッチ回路を介して第1ノードと出力端子との間を電気的に接続する。

【発明の効果】

【0017】

本発明によれば、電力用半導体装置がOFF状態の時に、電源電圧の急峻な増加が発生した場合であっても、出力トランジスタがONすることを防止することが可能となる。更に、本発明に係る機構は、出力トランジスタのターンオン/ターンオフに関連する特性に影響を与えない。

【図面の簡単な説明】

【0018】

【図1】図1は、関連技術に係る電力用半導体装置の構成を示す回路図である。

【図2】図2は、出力トランジスタ及び放電トランジスタの典型的な断面構造を示す概略図である。

【図3】図3は、寄生バイポーラトランジスタを含む電力用半導体装置の構成を示す回路図である。

【図4】図4は、寄生バイポーラトランジスタの電流−電圧特性を示すグラフ図である。

【図5】図5は、自動車に搭載される電力用半導体装置の電源端子に印加されるダンプサージを示す概念図である。

【図6】図6は、本発明の実施の形態に係る電力用半導体装置の構成を概略的に示すブロック図である。

【図7】図7は、本発明の実施の形態に係る電力用半導体装置の動作を示すタイミングチャートである。

【図8】図8は、ダンプサージ印加時の電力用半導体装置の動作を説明するための回路図である。

【図9】図9は、本発明の第1の実施の形態に係る電力用半導体装置の構成を概略的に示すブロック図である。

【図10】図10は、本発明の第1の実施の形態に係るショート制御回路の構成を概略的に示す回路図である。

【図11】図11は、本発明の第1の実施の形態に係るショート制御回路の動作を示すタイミングチャートである。

【図12】図12は、本発明の第1の実施の形態に係るショート制御回路の構成の第1の例を示す回路図である。

【図13】図13は、本発明の第1の実施の形態に係るショート制御回路の構成の第2の例を示す回路図である。

【図14】図14は、本発明の第1の実施の形態に係るショート制御回路の構成の第3の例を示す回路図である。

【図15】図15は、図14に示されたショート制御回路の動作を示すタイミングチャートである。

【図16A】図16Aは、図14に示されたショート制御回路中の遅延回路の構成例を示す回路図である。

【図16B】図16Bは、図14に示されたショート制御回路中の遅延回路の他の構成例を示す回路図である。

【図17】図17は、ターンオフ期間が放電期間と負電圧期間を含む場合を説明するための概念図である。

【図18】図18は、本発明の第1の実施の形態に係るショート制御回路の構成の第4の例を示す回路図である。

【図19】図19は、図18に示されたショート制御回路の動作を示すタイミングチャートである。

【図20】図20は、本発明の第1の実施の形態に係るショート制御回路の構成の第5の例を示す回路図である。

【図21】図21は、本発明の第2の実施の形態に係るショート制御回路の構成を概略的に示す回路図である。

【図22】図22は、本発明の第2の実施の形態に係るショート制御回路の動作を示すタイミングチャートである。

【図23】図23は、本発明の第2の実施の形態に係るショート制御回路の構成の第1の例を示す回路図である。

【図24】図24は、ターンオフ期間が放電期間と負電圧期間を含む場合を説明するための概念図である。

【図25】図25は、本発明の第2の実施の形態に係るショート制御回路の構成の第2の例を示す回路図である。

【図26】図26は、図25に示されたショート制御回路の動作を示すタイミングチャートである。

【図27】図27は、本発明の第2の実施の形態に係るショート制御回路の構成の第3の例を示す回路図である。

【図28】図28は、図27に示されたショート制御回路の動作を示すタイミングチャートである。

【図29A】図29Aは、図27に示されたショート制御回路中の遅延回路の構成例を示す回路図である。

【図29B】図29Bは、図27に示されたショート制御回路中の遅延回路の他の構成例を示す回路図である。

【図30】図30は、本発明の第2の実施の形態に係るショート制御回路の構成の第4の例を示す回路図である。

【図31】図31は、本発明の第2の実施の形態に係るショート制御回路の構成の第5の例を示す回路図である。

【図32】図32は、本発明の実施の形態におけるタイマー回路の構成例を示す回路図である。

【図33】図33は、図32に示されたタイマー回路の動作を示すタイミングチャートである。

【図34】図34は、本発明の第3の実施の形態に係る電力用半導体装置の構成を概略的に示すブロック図である。

【図35】図35は、本発明の第3の実施の形態に係る電力用半導体装置の動作を示すタイミングチャートである。

【図36】図36は、ダンプサージ印加時の電力用半導体装置の動作を説明するための回路図である。

【図37】図37は、本発明の第3の実施の形態に係るショート制御回路の構成を概略的に示す回路図である。

【図38】図38は、本発明の第3の実施の形態に係るショート制御回路の動作を示すタイミングチャートである。

【図39】図39は、本発明の第3の実施の形態に係るショート制御回路の構成の第1の例を示す回路図である。

【図40】図40は、ターンオフ期間が放電期間と負電圧期間を含む場合を説明するための概念図である。

【図41】図41は、本発明の第3の実施の形態に係るショート制御回路の構成の第2の例を示す回路図である。

【図42】図42は、図41に示されたショート制御回路の動作を示すタイミングチャートである。

【図43】図43は、本発明の第3の実施の形態に係るショート制御回路の構成の第3の例を示す回路図である。

【図44】図44は、図43に示されたショート制御回路の動作を示すタイミングチャートである。

【図45A】図45Aは、図43に示されたショート制御回路中の遅延回路の構成例を示す回路図である。

【図45B】図45Bは、図43に示されたショート制御回路中の遅延回路の他の構成例を示す回路図である。

【図46】図46は、本発明の第3の実施の形態に係るショート制御回路の構成の第4の例を示す回路図である。

【図47】図47は、本発明の第3の実施の形態に係るショート制御回路の構成の第5の例を示す回路図である。

【図48】図48は、本発明の実施の形態に係る電力用半導体装置が自動車の電子制御システムに適用される例を示すブロック図である。

【発明を実施するための形態】

【0019】

添付図面を参照して、本発明の実施の形態に係る電力用半導体装置を説明する。

【0020】

<基本構成>

図6は、本発明の実施の形態に係る電力用半導体装置1の構成を概略的に示すブロック図である。電力用半導体装置1は、電源端子TV、入力端子TI、及び出力端子TOを備えている。出力端子TOは負荷20の一端に接続され、負荷20の他端はグランド端子TGに接続される。電源端子TVには、電源電圧VDDが供給される。入力端子TIには、パワーON信号PWRが入力される。そのパワーON信号PWRの活性化に応答して、電力用半導体装置1はONし、出力端子TOを通して負荷20に電力を供給する。

【0021】

より詳細には、電力用半導体装置1は、出力トランジスタ10及びゲート充放電回路30を備えている。出力トランジスタ10は、電源端子TVと出力端子TOとの間に接続されている。具体的には、出力トランジスタ10は、NチャネルMOSFETであり、そのゲート、ドレイン及びソースは、それぞれ第1ノードN1、電源端子TV及び出力端子TO(出力ノードNZ)に接続されている。尚、出力ノードNZは、出力端子TOと同電位であり、出力端子TOと等価なものとして扱われる。

【0022】

出力トランジスタ10のゲートにつながる第1ノードN1は、抵抗素子RESを介して、ノードNDに接続されている。ノードNDは、ゲート充放電回路30の出力端子に接続されている。つまり、ゲート充放電回路30の出力は、抵抗素子RESを介して、第1ノードN1に接続されている。

【0023】

ゲート充放電回路30は、ノードNDすなわち第1ノードN1を充放電し、それにより出力トランジスタ10をON/OFF制御する。例えば、ゲート充放電回路30は、既出の図1で示されたものと同じ構成を有する。パワーON信号PWRが活性化されると、ゲート充放電回路30は、ノードND(第1ノードN1)を、電源電圧VDDよりも高い高電圧まで充電する。その結果、出力トランジスタ10がONし、負荷20に電力が供給される。一方、パワーON信号PWRが非活性化されると、ゲート充放電回路30は、ノードND(第1ノードN1)を放電する。その結果、出力トランジスタ10がOFFする。

【0024】

本実施の形態に係る電力用半導体装置1は、更に、ショートスイッチ回路4及びショート制御回路50を備えている。ショートスイッチ回路4は、出力トランジスタ10のゲート−ソース間を必要に応じてショートさせるために設けられている。すなわち、ショートスイッチ回路4は、第1ノードN1と出力ノードNZとの間に接続されている。ショートスイッチ回路4を制御することにより、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をON/OFFすることができる。そのショートスイッチ回路4を制御するのが、ショート制御回路50である。

【0025】

<基本動作>

図7は、本実施の形態に係る電力用半導体装置1の動作を示すタイミングチャートである。以下、図6及び図7を参照して、電力用半導体装置1の基本的な動作を説明する。その動作を説明するにあたり、4つの期間(フェーズ):ターンオン期間PA、ON期間PB、ターンオフ期間PC、及びOFF期間PD、を考える。

【0026】

ターンオン期間PA及びON期間PBは、パワーON信号PWRが活性化(PWR=Highレベル)されている期間である。パワーON信号PWRが活性化されると、第1ノードN1は充電され、出力トランジスタ10はONし、出力ノードNZも充電される。ON期間PBは、第1ノードN1及び出力ノードNZの電圧が安定し、出力トランジスタ10が安定的にONしている期間である。一方、ターンオン期間PAは、パワーON信号PWRの活性化タイミングからON期間PBまでの期間である。言い換えれば、ターンオン期間PAは、OFF期間PDからON期間PBへの遷移期間である。

【0027】

ターンオフ期間PC及びOFF期間PDは、パワーON信号PWRが非活性化(PWR=Lowレベル)されている期間である。パワーON信号PWRが非活性化されると、第1ノードN1は放電され、出力トランジスタ10はOFFし、出力ノードNZも放電される。OFF期間PDは、第1ノードN1及び出力ノードNZの電圧が安定し、出力トランジスタ10が安定的にOFFしている期間である。一方、ターンオフ期間PCは、パワーON信号PWRの非活性化タイミングからOFF期間PDまでの期間である。言い換えれば、ターンオフ期間PCは、ON期間PBからOFF期間PDへの遷移期間である。

【0028】

(ターンオン期間PA:時刻t1〜t2)

時刻t1において、パワーON信号PWRが活性化され、LowレベルからHighレベルに変わる。それに応答して、ゲート充放電回路30は、ノードND及び第1ノードN1を充電し始める。このターンオン期間PAにおいて、ショート制御回路50は、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をOFF(切断)する。出力トランジスタ10はONし、出力ノードNZの電圧も徐々に上昇する。尚、ターンオン期間PAにおいて、第1ノードN1は、電源電圧VDDよりも高い高電圧まで充電される。

【0029】

(ON期間PB:時刻t2〜t3)

ON期間PBにおいて、ショート制御回路50は、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をOFFのまま維持する。第1ノードN1の電圧は、電源電圧VDDよりも高い高電圧で安定する。出力ノードNZの電圧は、電源電圧VDD近傍で安定する。出力トランジスタ10は、安定的にONしている。

【0030】

(ターンオフ期間PC:時刻t3〜t4)

時刻t3において、パワーON信号PWRが非活性化され、HighレベルからLowレベルに変わる。それに応答して、ゲート充放電回路30は、ノードND及び第1ノードN1を放電し始める。このターンオフ期間PCにおいても、ショート制御回路50は、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をOFFのまま維持する。従って、ショートスイッチ回路4を通した放電は発生しない。すなわち、第1ノードN1の放電は、従来通りゲート充放電回路30によってのみ行われる。第1ノードN1の電圧が低下すると、出力ノードNZの電圧も徐々に低下し、最終的に0Vになる。出力トランジスタ10はOFFする。

【0031】

(OFF期間PD:時刻t4〜)

OFF期間PDの少なくとも一部において、ショート制御回路50は、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をON(有効化)する。従って、第1ノードN1と出力ノードNZとの間、すなわち、出力トランジスタ10のゲート−ソース間がショートする。出力トランジスタ10は、安定的にOFFしている。

【0032】

このように、ショート制御回路50は、OFF期間PDにおいてのみ、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をON(有効化)する。その他の期間PA〜PCにおいて、ショート制御回路50は、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をOFF(切断)する。このショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続がOFFである期間は、パワーON信号PWRが活性化されている期間と一致しない。すなわち、ショート制御回路50は、単純にパワーON信号PWRに同期してショートスイッチ回路4をON/OFF制御しているわけではない。ショート制御回路50は、ターンオン期間PA及びON期間PBだけでなく、ターンオフ期間PCにおいても、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をOFFのまま維持する。その結果、ターンオフ期間PCにおいて、ショートスイッチ回路4を通した第1ノードN1の放電が防止される。すなわち、本実施の形態に係るショートスイッチ回路4及びショート制御回路50は、出力トランジスタ10のターンオフに関連する特性(ターンオフに要する時間等)に影響を与えない。

【0033】

<ダンプサージ印加時の動作>

次に、OFF期間PDにおいて、ダンプサージ等の印加によって、電源電圧VDDの急峻な増加が発生した場合を考える。図7に示される例では、OFF期間PDの最中の時刻t5〜t6において、ダンプサージが電源端子TVに印加される。

【0034】

図8は、ゲート充放電回路30が既出の図1、図3で示されたものと同じ構成を有している場合を示している。上述の通り、ゲート充放電回路30の放電トランジスタ33は、寄生バイポーラトランジスタQ1を有している。寄生バイポーラトランジスタQ1のコレクタ、エミッタ及びベースは、それぞれ電源端子TV、ノードND及びノードNBに接続されている。また、寄生容量(コレクタ−ベース間容量)C1が、電源端子TVとノードNBとの間に接続されている。

【0035】

OFF期間PDの最中に、電源電圧VDDの急峻な増加が発生した場合、上述の通り、寄生バイポーラトランジスタQ1がONする可能性がある。寄生バイポーラトランジスタQ1がONすると、ノードNDの電圧が持ち上がる。しかしながら、OFF期間PDにおいて、ショートスイッチ回路4を介した電気的接続はONしており、第1ノードN1と出力ノードNZとの間、すなわち、出力トランジスタ10のゲート−ソース間はショートしている。ゲート−ソース間電圧が閾値電圧を超えないため、出力トランジスタ10はONすることなく、OFF状態を維持する。

【0036】

尚、ノードNDと第1ノードN1との間には抵抗素子RESが介在している。ノードNDの電圧が持ち上がった場合、ノードNDから、抵抗素子RES、第1ノードN1及びショートスイッチ回路4を通して、出力ノードNZへ電流が流れる。この時、抵抗素子RESにおいてIRドロップが発生するため、第1ノードN1の電圧がLowレベルに維持される。つまり、抵抗素子RESを利用することによって、第1ノードN1の電圧をLowレベルに維持しやすくなる。

【0037】

<効果>

本実施の形態によれば、OFF期間PDにおいて、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続がONする。これにより、第1ノードN1と出力ノードNZとの間、すなわち、出力トランジスタ10のゲート−ソース間がショートする。従って、電源電圧VDDの急峻な増加が発生した場合であっても、出力トランジスタ10がONすることが防止される。すなわち、出力トランジスタ10の熱破壊が防止される。

【0038】

また、本実施の形態によれば、OFF期間PD以外において、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続はOFFのまま維持される。従って、OFF期間PD以外において、ショートスイッチ回路4及びショート制御回路50は、第1ノードN1に影響を及ぼさない。つまり、ショートスイッチ回路4及びショート制御回路50は、出力トランジスタ10のターンオン/ターンオフに関連する特性(ターンオン/ターンオフに要する時間等)に影響を与えない。すなわち、本実施の形態によれば、ターンオン/ターンオフに関連する特性に影響を及ぼすことなく、出力トランジスタ10の熱破壊を防止することが可能である。

【0039】

以下、本発明の様々な実施の形態を説明する。

【0040】

1.第1の実施の形態

図9は、第1の実施の形態に係る電力用半導体装置1の構成を概略的に示すブロック図である。第1の実施の形態において、ショートスイッチ回路4は、第1ノードN1と出力ノードNZとの間に接続されたショートスイッチ40Aを含んでいる。また、第1の実施の形態におけるショート制御回路50は、ショート制御回路50Aと参照される。ショート制御回路50Aは、ショートスイッチ40AをON/OFF制御することによって、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をON/OFFすることができる。

【0041】

図10は、第1の実施の形態に係るショートスイッチ40A及びショート制御回路50Aの構成を概略的に示している。ショートスイッチ40Aとして、例えば、NチャネルMOSFET(以下、「ショートトランジスタ40A」と参照される)が用いられる。ショートトランジスタ40Aのソース、ドレイン及びゲートは、それぞれ出力ノードNZ、第1ノードN1及び第2ノードN2に接続されている。この第2ノードN2の電圧を制御することによって、ショートトランジスタ40AをON/OFF制御することが可能である。

【0042】

ショート制御回路50Aは、第2ノードN2に接続されており、第2ノードN2の電圧を制御する。詳細には、ショート制御回路50Aは、第2ノードN2と出力ノードNZとの間に接続された第1スイッチ51Aと、第2ノードN2と電源端子TVとの間に接続された電源接続回路60Aとを備えている。第1スイッチ51Aは、第2ノードN2と出力ノードNZとの間の電気的接続を制御する。電源接続回路60Aは、制御信号CONに応じて、第2ノードN2と電源端子TVとの間の電気的接続を制御する。

【0043】

ターンオン期間PA、ON期間PB及びターンオフ期間PCにおいて、ショート制御回路50Aは、第1スイッチ51AをONする。これにより、第2ノードN2と出力ノードNZとの間、すなわち、ショートトランジスタ40Aのゲート−ソース間がショートする。その結果、ショートトランジスタ40AがOFFに維持される。一方、OFF期間PDにおいて、ショート制御回路50Aは、第1スイッチ51AをOFFし、第2ノードN2と出力ノードNZとの間の電気的接続を切断する。また、電源接続回路60Aは、第2ノードN2と電源端子TVとを電気的に接続する。その結果、第2ノードN2に電源電圧VDDが印加され、ショートトランジスタ40AがONする。このようにして、上述のショートトランジスタ40AのON/OFF制御が実現される。

【0044】

第1スイッチ51Aとして、例えば、図10に示されるようなNチャネルMOSFETが用いられる。そのNチャネルMOSFET51Aのゲート、ソース及びドレインは、それぞれ第1ノードN1、出力ノードNZ及び第2ノードN2に接続されている。このような構成の場合のショート制御回路50Aの動作を、図11を参照して説明する。尚、既出の図7と重複する説明は、適宜省略される。

【0045】

(ターンオン期間PA:時刻t1〜t2)

時刻t1において、パワーON信号PWRが活性化され、LowレベルからHighレベルに変わる。それに応答して、制御信号CONがHighレベルからLowレベルに変わる。制御信号CONがLowレベルの場合、電源接続回路60Aは、第2ノードN2と電源端子TVとの間の電気的接続を切断する。その一方で、上述の通り、第1ノードN1及び出力ノードNZの電圧は徐々に上昇する。昇圧回路32によって昇圧される第1ノードN1の電圧は、出力ノードNZの電圧より高く、それらノード間には電圧差(N1−NZ)が発生する。すなわち、NチャネルMOSFET51Aのゲート−ソース間にある程度の電圧が印加され、NチャネルMOSFET51AがONする。その結果、第2ノードN2と出力ノードNZとは電気的に接続され、ショートトランジスタ40AがOFFする。

【0046】

(ON期間PB:時刻t2〜t3)

NチャネルMOSFET51AはONのままであり、ショートトランジスタ40AはOFFのままである。

【0047】

(ターンオフ期間PC:時刻t3〜t4)

時刻t3において、パワーON信号PWRが非活性化され、HighレベルからLowレベルに変わる。それに応答して、制御信号CONがLowレベルからHighレベルに変わる。制御信号CONがHighレベルの場合、電源接続回路60Aは、第2ノードN2と電源端子TVとを電気的に接続する。但し、ターンオフ期間PCにおいても、第1ノードN1と出力ノードNZとの間にはある程度の電圧差(N1−NZ)が存在し、NチャネルMOSFET51AはON状態に維持される。つまり、第2ノードN2と出力ノードNZとは電気的に接続されたままである。NチャネルMOSFET51Aの電流能力は十分に大きく設計されるため、ショートトランジスタ40Aのゲート−ソース間電圧(N2−NZ)は十分に低く維持される。従って、ショートトランジスタ40AはOFF状態に維持される。

【0048】

(OFF期間PD:時刻t4〜)

第1ノードN1及び出力ノードNZの放電が進み、第1ノードN1と出力ノードNZとの間の電圧差(N1−NZ)がNチャネルMOSFET51Aの閾値電圧を下回ると、NチャネルMOSFET51AはOFFする。すなわち、第2ノードN2と出力ノードNZとの間の電気的接続が切断される。その結果、ノードN2に電源電圧VDDが印加され、ショートトランジスタ40AがONする。

【0049】

このように、ゲートが第1ノードN1に接続されたNチャネルMOSFET51Aを用いることによって、上述のショートトランジスタ40AのON/OFF制御が実現される。

【0050】

以下、第1の実施の形態に係るショート制御回路50Aの構成の様々な例を説明する。尚、上記と重複する説明は適宜省略される。

【0051】

1−1.第1の例

図12は、第1の例を示す回路図である。電源接続回路60Aは、PチャネルMOSFET61A、63A、NチャネルMOSFET62A、64Aを備えている。

【0052】

PチャネルMOSFET61A及びNチャネルMOSFET62Aは、第1のインバータ回路を構成している。具体的には、PチャネルMOSFET61Aのゲート、ソース及びドレインは、それぞれ、ノードNA、電源端子TV及び第3ノードN3に接続されている。NチャネルMOSFET62Aのゲート、ソース及びドレインは、それぞれ出力ノードNZ、出力ノードNZ及び第3ノードN3に接続されている。尚、NチャネルMOSFET62Aは、デプレッション型である。

【0053】

PチャネルMOSFET63A及びNチャネルMOSFET64Aは、第2のインバータ回路を構成している。具体的には、PチャネルMOSFET63Aのゲート、ソース及びドレインは、それぞれ、第3ノードN3、電源端子TV及び第2ノードN2に接続されている。NチャネルMOSFET64Aのゲート、ソース及びドレインは、それぞれ第3ノードN3、出力ノードNZ及び第2ノードN2に接続されている。

【0054】

このような第1及び第2のインバータ回路が、第2ノードN2と電源端子TVとの間の電気的接続を制御する。このとき、第1のインバータ回路に入力されるノードNAの信号(ゲート充放電回路の放電トランジスタ33のゲート制御信号)が、図10及び図11で示された制御信号CONに相当する。

【0055】

ターンオン期間PA及びON期間PBにおいて、ノードNAの信号(制御信号CON)はLowレベルである。この場合、PチャネルMOSFET61AがONし、PチャネルMOSFET63AはOFFする。従って、第2ノードN2と電源端子TVとの間の電気的接続が切断される。第2ノードN2は、少なくともNチャネルMOSFET51A(第1スイッチ)を介して、出力ノードNZと電気的に接続される。

【0056】

ターンオフ期間PC及びOFF期間PDにおいて、ノードNAの信号(制御信号CON)はHighレベルである。この場合、PチャネルMOSFET61A及びNチャネルMOSFET64AがOFFし、PチャネルMOSFET63AがONする。従って、第2ノードN2と電源端子TVとが電気的に接続される。

【0057】

但し、ターンオフ期間PCでは、上述の通り、NチャネルMOSFET51AもONしている。ターンオフ期間PCにおいてもショートトランジスタ40AをOFFに維持しておくために、NチャネルMOSFET51Aの電流能力は、PチャネルMOSFET63Aの電流能力よりも十分に大きく設計される。

【0058】

OFF期間PDでは、NチャネルMOSFET51AもOFFするため、第2ノードN2と出力ノードNZとの間の電気的接続が切断される。従って、ショート制御回路50Aを通って電源端子TVから出力端子TOに向かって電流は流れない。すなわち、オフ時消費電流は発生しない。

【0059】

尚、ショート制御回路50Aに含まれるNチャネルMOSFETのそれぞれのバックゲートは、出力ノードNZに直接接続されている。そのため、OFF期間PDにおいて、それらバックゲートがハイインピーダンスになることはない。従って、OFF期間PDにおいて、ダンプサージの印加によって、それらNチャネルMOSFETの寄生バイポーラトランジスタが動作することはない。

【0060】

1−2.第2の例

図13は、第2の例を示す回路図である。第2の例では、図12で示された回路構成に対して、デプレッション型のNチャネルMOSFET65Aが更に追加されている。このデプレッション型のNチャネルMOSFET65Aは、PチャネルMOSFET63Aと第2ノードN2との間に介在しており、定電流源として機能する。

【0061】

上述の第1の例で示されたように、ターンオフ期間PC中には、NチャネルMOSFET51AとPチャネルMOSFET63Aが同時にオンする期間がある。しかしながら、ターンオフ期間PCにおいてもショートトランジスタ40AをOFFに維持しておくことが望ましい。その目的のため、第1の例では、NチャネルMOSFET51Aの電流能力は、PチャネルMOSFET63Aの電流能力よりも十分に大きく設計される。つまり、電流能力の設計に十分な注意を払う必要がある。第2の例では、定電流源として機能するNチャネルMOSFET65Aの定電流値を小さくする(インピーダンスを高くする)ことにより、当該目的を容易に達成することができる。つまり、第1の例と比較して、設計がより容易になる。

【0062】

1−3.第3の例

図14は、第3の例を示す回路図である。第3の例では、図12で示された回路構成に対して、遅延回路70A及び補助スイッチ66Aが更に追加されている。NチャネルMOSFET51Aのドレインは、第2ノードN2の代わりにノードN2’に接続されている。そのノードN2’が、遅延回路70Aを介して、第2ノードN2に接続されている。

【0063】

図14及び図15を参照して、OFF期間PD中に電源端子TVにダンプサージが印加された場合を考える。出力トランジスタ10は大面積を有するように作成されることが多く、その場合、ゲート−ドレイン間の寄生容量Cgd(図14参照)を無視することができない。時刻t5においてダンプサージが印加されると、その寄生容量Cgdによって、第1ノードN1の電圧が持ち上げられる。その後、第1ノードN1は、寄生容量Cgdと抵抗素子RESと放電トランジスタ33のインピーダンスに依って決まる時定数で放電される。

【0064】

OFF期間PDの最中に第1ノードN1の電圧が上昇すると、NチャネルMOSFET51A(第1スイッチ)がONしてしまう。図15の例では、時刻t5〜tsの短い期間、NチャネルMOSFET51AがONし、ノードN2’が放電されてしまう。もし、遅延回路70Aがなければ、ショートトランジスタ40Aのゲートにつながる第2ノードN2も放電されてしまい、ショートトランジスタ40AがOFFしてしまう。このことは、出力トランジスタ10のゲート−ソース間のショートの解除を意味し、好ましくない。

【0065】

一方、本例によれば、ノードN2’と第2ノードN2との間に遅延回路70Aが設けられている。従って、たとえノードN2’が放電されても、第2ノードN2の電圧レベルは、ある程度の時間Highレベルに維持される。つまり、時刻t5〜tsの期間においても、ショートトランジスタ40AはON状態のまま維持される。このように、OFF期間PDの最中に出力トランジスタ10のゲート−ソース間のショートが解除されることが防止される。

【0066】

図16A及び図16Bは、遅延回路70Aの構成例を示している。図16Aの例では、抵抗素子71Aと容量素子72Aとにより、遅延回路70Aが構成されている。図16Bの例では、定電流源として機能するデプレッション型のNチャネルMOSFET73Aと、ショートトランジスタ40Aのゲート−ソース間の寄生容量C40Aとにより、遅延回路70Aが構成されている。OFF期間PDにおいて、遅延回路70Aの容量素子(72AあるいはC40A)は、電源電圧VDDに充電されている。上記理由によりノードN2’が放電された場合であっても、遅延回路70Aの容量素子が放電されるまでは、第2ノードN2の電圧レベルをHighレベルに保つことができる。尚、遅延回路70Aの放電時定数は、第1ノードN1の放電時定数よりも大きく設計される。

【0067】

尚、ターンオン期間PAの開始時(時刻t1:図11参照)、第2ノードN2を速やかに放電し、ショートトランジスタ40AをOFFする必要がある。しかしながら、本例では、ノードN2’と第2ノードN2との間に遅延回路70Aが介在しており、NチャネルMOSFET51A、64Aを通した放電は遅延する。このような遅延回路70Aの影響を無くすために、補助スイッチ66Aが追加されている。補助スイッチ66Aは、第2ノードN2と出力ノードNZとの間に接続されており、ターンオン期間PAにおいてONする。その結果、ターンオン期間PAの開始時に、補助スイッチ66Aを通して第2ノードN2が速やかに放電される。つまり、ターンオン期間PAへの遅延回路70Aの影響が排除される。

【0068】

例えば、補助スイッチ66AはNチャネルMOSFETであり、そのゲート、ソース及びドレインは、それぞれ第3ノードN3、出力ノードNZ及び第2ノードN2に接続されている。ターンオン期間PAにおいて、第3ノードN3には電源電圧VDDが印加される。第3ノードN3と出力ノードNZとの間の電圧差(N3−NZ)が閾値電圧を下回るまで、NチャネルMOSFET66AはONする。ターンオン期間PA以外において、NチャネルMOSFET66AはOFFする。これにより、上記目的が達成される。

【0069】

1−4.第4の例

出力端子TOに接続される負荷20が誘導性負荷の場合、ターンオフの際に、逆起電圧(負電圧)が出力端子TOに印加される可能性がある。また、負荷20を接続する配線のインダクタンス成分によっても、同様のことが発生し得る。このような場合、図17に示されるように、ターンオフ期間PCは、第1ノードN1及び出力ノードNZが放電される「放電期間PC1」だけでなく、続いて出力端子TO(出力ノードNZ)に負電圧が印加される「負電圧期間PC2」をも含む。

【0070】

既出の例では、ターンオフ期間PCは、放電期間PC1だけを含んでいた。その放電期間PC1において、第1スイッチ51AがONし、第2ノードN2と出力ノードNZとの間が電気的に接続される。その結果、ショートトランジスタ40Aが、放電期間PC1においてもOFF状態に維持される。しかしながら、第1スイッチ51A(NチャネルMOSFET51A)は、負電圧期間PC2においてもONするとは限らない。従って、第4の例では、第2ノードN2と出力ノードNZとの間に接続され、負電圧期間PC2においてONする第2スイッチ52Aが追加される。

【0071】

図18は、第4の例を示す回路図である。第4の例では、図12で示された回路構成に対して、過電圧保護回路80、制御回路90、及び第2スイッチ52Aが更に追加されている。

【0072】

過電圧保護回路80(ダイナミッククランプ回路)は、電源端子TVと第1ノードN1との間に接続されている。具体的には、過電圧保護回路80は、PチャネルMOSFET81、ダイオード82、83を備えている。PチャネルMOSFET81のソースは、電源端子TVに接続されている。PチャネルMOSFET81のゲート及びドレインは、ダイオード82のカソードに接続されている。ダイオード82のアノードは、ダイオード83のアノードに接続されている。ダイオード83のカソードは、第1ノードN1に接続されている。この過電圧保護回路80は、負電圧期間PC2において動作する。

【0073】

制御回路90は、PチャネルMOSFET91及びデプレッション型のNチャネルMOSFET92を備えている。PチャネルMOSFET91のゲート、ソース及びドレインは、それぞれ、PチャネルMOSFET81のゲート、電源端子TV及び第5ノードN5に接続されている。NチャネルMOSFET92のドレインは第5ノードN5に接続され、そのソース及びゲートは出力ノードNZに接続されている。

【0074】

PチャネルMOSFET81、91はカレントミラー回路を構成している。過電圧保護回路80が動作すると、第5ノードN5が充電され、その電圧はHighレベルになる。過電圧保護回路80が非動作の場合、第5ノードN5の電圧は出力ノードNZの電圧と同等になる。この第5ノードN5の電圧が、第2スイッチ52AをON/OFF制御するための制御信号CON2として使用される。すなわち、制御回路90は、過電圧保護回路80の動作時にだけ制御信号CON2を活性化(CON2=Highレベル)する。

【0075】

第2スイッチ52Aは、第2ノードN2と出力ノードNZとの間に接続されている。この第2スイッチ52Aは、制御信号CON2が活性化されている時(CON2=Highレベル)にONし、非活性化されている時にOFFする。第2スイッチ52Aは、例えばNチャネルMOSFETであり、そのゲート、ソース及びドレインは、それぞれ第5ノードN5、出力ノードNZ及び第2ノードN2に接続されている。制御信号CON2が活性化されHighレベルになると、NチャネルMOSFET52AはONする。その結果、第2ノードN2と出力ノードNZが電気的に接続される。

【0076】

図18及び図19を参照して、本例におけるターンオフ期間PCについて説明する。そのターンオフ期間PCは、放電期間PC1と負電圧期間PC2を含んでいる。

【0077】

(放電期間PC1:時刻t3〜tm)

既出の例の場合と同様に、第1スイッチ51AがONする。そのため、第2ノードN2と出力ノードNZとが電気的に接続され、ショートトランジスタ40AはOFF状態に維持される。

【0078】

(負電圧期間PC2:時刻tm〜t4)

負電圧期間PC2において、過電圧保護回路80を正常に動作させるためには、出力トランジスタ10を低いゲート−ソース間電圧でオンさせる必要がある。従って、ショートトランジスタ40AがONして、第1ノードN1と出力ノードNZとがショートすることは望ましくない。すなわち、負電圧期間PC2においてもショートトランジスタ40AをOFFのまま保つ必要がある。しかしながら、負電圧期間PC2において、第1スイッチ51AはOFFする可能性がある。従って、負電圧期間PC2用に第2スイッチ52Aが設けられている。

【0079】

より詳細には、出力端子TOに負電圧が印加されると、過電圧保護回路80のPチャネルMOSFET81からダイオード82、83、抵抗素子RES、ゲート充放電回路30の放電トランジスタ33を通して出力端子TOへの電流経路が形成される。これにより、出力トランジスタ10のドレイン−ソース間電圧が、過電圧保護回路のクランプ電圧にクランプされる。過電圧保護回路80がこのように動作すると、上述の通り、制御回路90は、制御信号CON2を活性化(CON2=Highレベル)する。それに応答して、第2スイッチ52AがONし、第2ノードN2と出力ノードNZが電気的に接続される。その結果、ショートトランジスタ40AがOFF状態に保たれる。

【0080】

負電圧期間PC2が終わると、第2スイッチ52AはOFFする。

【0081】

以上に説明されたように、第1の実施の形態に係るショートトランジスタ40A及びショート制御回路50Aは、負電圧期間PC2に関連する特性(過電圧保護等)にも影響を及ぼさない。

【0082】

1−5.第5の例

上述の例のうちいくつかを組み合わせることも可能である。図20は、第1〜第4の例の全てを組み合わせた場合の回路構成を示している。

【0083】

2.第2の実施の形態

第2の実施の形態において、ショートスイッチ回路4は、第1ノードN1と出力ノードNZとの間に接続されたショートスイッチ40Bを含んでいる。また、第2の実施の形態におけるショート制御回路50は、ショート制御回路50Bと参照される。ショート制御回路50Bは、ショートスイッチ40BをON/OFF制御することによって、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をON/OFFすることができる。

【0084】

図21は、第2の実施の形態に係るショートスイッチ40B及びショート制御回路50Bの構成を概略的に示している。ショートスイッチ40Bとして、例えば、NチャネルMOSFET(以下、「ショートトランジスタ40B」と参照される)が用いられる。ショートトランジスタ40Bのソース、ドレイン及びゲートは、それぞれ出力ノードNZ、第1ノードN1及び第2ノードN2に接続されている。この第2ノードN2の電圧を制御することによって、ショートトランジスタ40BをON/OFF制御することが可能である。

【0085】

ショート制御回路50Bは、第2ノードN2に接続されており、第2ノードN2の電圧を制御する。より詳細には、ショート制御回路50Bは、第2ノードN2に接続された電源接続回路60Bを備えている。この電源接続回路60Bは、制御信号CONに応じて、第2ノードN2と電源端子TVとの間の電気的接続、及び、第2ノードN2と出力ノードNZとの間の電気的接続を制御する。

【0086】

また、ショート制御回路50Bは、第2ノードN2と出力ノードNZとの間に接続された複数のスイッチを備えている。複数のスイッチは、特に、第2ノードN2と出力ノードNZとの間の電気的接続の制御に用いられる。より詳細には、複数のスイッチは、少なくとも第1スイッチ51Bと第2スイッチ52Bを含んでいる。第1スイッチ51B及び第2スイッチ52Bは、第2ノードN2と出力ノードNZとの間に直列に接続されている。

【0087】

第1スイッチ51Bとして、例えば、図21に示されるようなNチャネルMOSFETが用いられる。そのNチャネルMOSFET51Bのゲート、ソース及びドレインは、それぞれ、第1ノードN1、第2スイッチ52B(出力ノードNZ側)及び第2ノードN2に接続されている。

【0088】

第2スイッチ52Bとして、例えば、図21に示されるようなNチャネルMOSFETが用いられる。そのNチャネルMOSFET52Bのゲート、ソース及びドレインは、それぞれ、ノードNE、出力ノードNZ及び第1スイッチ51B(第2ノードN2側)に接続されている。

【0089】

電源接続回路60Bは、ノードNEにも接続されており、ノードNEの電圧を制御することによってNチャネルMOSFET52B(第2スイッチ)をON/OFF制御する。つまり、電源接続回路60Bは、ノードNEと電源端子TVとの間の電気的接続、及び、ノードNEと出力ノードNZとの間の電気的接続を制御する。特に、電源接続回路60Bは、「所定のタイマー期間PT」において、ノードNEと電源端子TVとを電気的に接続し、それによりNチャネルMOSFET52B(第2スイッチ)をONする。

【0090】

ここで、その所定のタイマー期間PTは、パワーON信号PWRが非活性化されるタイミング(時刻t3)、すなわち、ターンオフ期間PCの開始と同時に始まる。また、所定のタイマー期間PTの長さは、典型的には、ターンオフ期間PCの長さ以上に設計される。但し、後述の第2の例において説明されるように、ターンオフ期間PCが放電期間PC1と負電圧期間PC2を含んでいる場合(図24参照)、所定のタイマー期間PTの長さは、放電期間PC1の長さ以上であればよい。

【0091】

所定のタイマー期間PTは、タイマー回路100から出力される第1制御信号CON1に基いて把握することができる。具体的には、タイマー回路100は、所定のタイマー期間PTの間だけ、第1制御信号CON1を活性化(CON1=Lowレベル)する。所定のタイマー期間PT以外においては、タイマー回路100は、第1制御信号CON1を非活性化(CON1=Highレベル)する。

【0092】

図21及び図22を参照して、第2の実施の形態に係るショート制御回路50Bの動作を説明する。尚、既出の図7と重複する説明は、適宜省略される。

【0093】

(ターンオン期間PA:時刻t1〜t2)

時刻t1において、パワーON信号PWRが活性化され、LowレベルからHighレベルに変わる。それに応答して、制御信号CONがHighレベルからLowレベルに変わる。制御信号CONがLowレベルの場合、電源接続回路60Bは、第2ノードN2と出力ノードNZとを電気的に接続する。これにより、ショートトランジスタ40Bのゲート−ソース間がショートし、ショートトランジスタ40BがOFFする。

【0094】

また、上述の通り、第1ノードN1及び出力ノードNZの電圧は徐々に上昇する。昇圧回路32によって昇圧される第1ノードN1の電圧は、出力ノードNZの電圧より高く、それらノード間には電圧差(N1−NZ)が発生する。すなわち、NチャネルMOSFET51Bのゲート−ソース間にある程度の電圧が印加され、NチャネルMOSFET51B(第1スイッチ)がONする。

【0095】

また、電源接続回路60Bは、ノードNEと電源端子TVとを電気的に接続する。これにより、NチャネルMOSFET52B(第2スイッチ52B)がONする。但し、出力ノードNZの電圧が電源電圧VDD近傍まで上昇し、NチャネルMOSFET52Bのゲート−ソース間電圧(NE−NZ)がその閾値電圧より低くなると、NチャネルMOSFET52BはOFFする。

【0096】

(ON期間PB:時刻t2〜t3)

制御信号CONはLowレベルのままであり、電源接続回路60Bは、第2ノードN2と出力ノードNZとを電気的に接続する。従って、ショートトランジスタ40BはOFFのままである。また、NチャネルMOSFET51B(第1スイッチ)はONし、NチャネルMOSFET52B(第2スイッチ)はOFFする。

【0097】

(ターンオフ期間PC:時刻t3〜t4)

時刻t3において、パワーON信号PWRが非活性化され、HighレベルからLowレベルに変わる。それに応答して、制御信号CONがLowレベルからHighレベルに変わる。制御信号CONがHighレベルの場合、電源接続回路60Bは、第2ノードN2と出力ノードNZとの間の電気的接続を切断する。但し、以下に説明されるように、ターンオフ期間PCにおいて第1スイッチ51B及び第2スイッチ52Bの両方がONする。そのため、ターンオフ期間PCにおいても、第1スイッチ51B及び第2スイッチ52Bを介して第2ノードN2と出力ノードNZとの間の電気的接続が維持される。

【0098】

まず、第1スイッチ51Bに関しては次の通りである。ターンオフ期間PCにおいても、第1ノードN1と出力ノードNZとの間にはある程度の電圧差(N1−NZ)が存在する。従って、NチャネルMOSFET51B(第1スイッチ51B)はON状態に維持される。

【0099】

次に、第2スイッチ52Bに関しては次の通りである。パワー信号PWRの非活性化に応答して、上述のタイマー期間PTが始まり、タイマー回路100が、第1制御信号CON1を活性化(CON1=Lowレベル)する。第1制御信号CON1が活性化されているタイマー期間PTの間、電源接続回路60Bは、ノードNEと電源端子TVとを電気的に接続し、それによりNチャネルMOSFET52B(第2スイッチ)をON状態に維持する。

【0100】

このように、ターンオフ期間PCにおいても、第1スイッチ51B及び第2スイッチ52Bによって、第2ノードN2と出力ノードNZとの間の電気的接続が維持される。従って、ショートトランジスタ40BはOFF状態に維持される。

【0101】

(OFF期間PD:時刻t4〜)

第1ノードN1及び出力ノードNZの放電が進み、第1ノードN1と出力ノードNZとの間の電圧差(N1−NZ)がNチャネルMOSFET51Bの閾値電圧を下回ると、NチャネルMOSFET51B(第1スイッチ)はOFFする。すなわち、第2ノードN2と出力ノードNZとの間の電気的接続が切断される。電源接続回路60Bは、第2ノードN2と電源端子TVとを電気的に接続する。その結果、ショートトランジスタ40BがONする。

【0102】

尚、OFF期間PD中に、所定のタイマー期間PTが終了し、タイマー回路100は、第1制御信号CON1を非活性化(CON1=Highレベル)する。第1制御信号CON1が非活性化された後のOFF期間PDにおいて、電源接続回路60Bは、ノードNEと電源端子TVとの間の電気的接続を切断し、ノードNEを出力ノードNZと電気的に接続する。これにより、NチャネルMOSFET52B(第2スイッチ)もOFFする。

【0103】

このようにして、上述のショートトランジスタ40BのON/OFF制御が実現される。尚、第1スイッチ51Bに加えて第2スイッチ52Bも設けている理由は、次の通りである。

【0104】

OFF期間PD中に電源端子TVにダンプサージが印加された場合を考える。出力トランジスタ10は大面積を有するように作成されることが多く、その場合、ゲート−ドレイン間の寄生容量Cgd(図21参照)を無視することができない。ダンプサージが印加されると、その寄生容量Cgdによって、第1ノードN1の電圧が持ち上げられる。その後、第1ノードN1は、寄生容量Cgdと抵抗素子RESと放電トランジスタ33のインピーダンスに依って決まる時定数で放電される。

【0105】

図21に示される例において、第1スイッチ51Bは、ゲートが第1ノードN1に接続されたNチャネルMOSFETである。従って、OFF期間PDの最中に第1ノードN1の電圧が持ち上げられると、NチャネルMOSFET51BがONしてしまう。この時、もし第2スイッチ52Bが無ければ、第2ノードN2と出力ノードNZとが電気的に接続され、OFF期間PDの最中にショートトランジスタ40BがOFFしてしまう。このことは、出力トランジスタ10のゲート−ソース間のショートの解除を意味し、好ましくない。このような現象を防止するために、第1スイッチ51Bとは別に第2スイッチ52Bが設けられている。

【0106】

以下、第2の実施の形態に係るショート制御回路50Bの構成の様々な例を説明する。尚、上記と重複する説明は適宜省略される。

【0107】

2−1.第1の例

図23は、第1の例を示す回路図である。電源接続回路60Bは、PチャネルMOSFET61B、67B、69B、NチャネルMOSFET62B、63B、64B、68Bを備えている。

【0108】

PチャネルMOSFET61B及びデプレッション型のNチャネルMOSFET62Bは、第1のインバータ回路を構成している。具体的には、PチャネルMOSFET61Bのゲート、ソース及びドレインは、それぞれ、ノードNA、電源端子TV及び第3ノードN3に接続されている。NチャネルMOSFET62Bのゲート、ソース及びドレインは、それぞれ出力ノードNZ、出力ノードNZ及び第3ノードN3に接続されている。

【0109】

NチャネルMOSFET63Bは、デプレッション型である。NチャネルMOSFET63B、64Bは、第2のインバータ回路を構成している。具体的には、NチャネルMOSFET63Bのゲート、ソース及びドレインは、それぞれ、第2ノードN2、第2ノードN2及び電源端子TVに接続されている。NチャネルMOSFET64Bのゲート、ソース及びドレインは、それぞれ第3ノードN3、出力ノードNZ及び第2ノードN2に接続されている。

【0110】

PチャネルMOSFET67B及びデプレッション型のNチャネルMOSFET68Bは、第3のインバータ回路を構成している。具体的には、PチャネルMOSFET67Bのゲート、ソース及びドレインは、それぞれ、ノードNA、電源端子TV及びノードNEに接続されている。NチャネルMOSFET68Bのゲート、ソース及びドレインは、それぞれ出力ノードNZ、出力ノードNZ及びノードNEに接続されている。

【0111】

PチャネルMOSFET69Bのゲート、ソース及びドレインは、それぞれ、第4ノードN4、電源端子TV及びノードNEに接続されている。この第4ノードN4には、タイマー回路100から第1制御信号CON1が供給される。

【0112】

このような構成において、第1及び第3のインバータ回路に入力されるノードNAの信号(ゲート充放電回路の放電トランジスタ33のゲート制御信号)が、図21及び図22で示された制御信号CONに相当する。以下、図22及び図23を参照して、本例に係るショート制御回路50Bの動作を説明する。

【0113】

ターンオン期間PA及びON期間PBにおいて、ノードNAの信号(制御信号CON)はLowレベルである。この場合、PチャネルMOSFET61B、67BがONし、第3ノードN3及びノードNEがプルアップされる。これにより、NチャネルMOSFET64B及びNチャネルMOSFET52B(第2スイッチ)がONし、第2ノードN2と出力ノードNZとが電気的に接続される。従って、ショートトランジスタ40BがOFFする。

【0114】

出力ノードNZの電圧が上昇し、第3ノードN3と出力ノードNZとの間の電圧差がNチャネルMOSFET64Bの閾値電圧を下回ると、NチャネルMOSFET64BがOFFする。また、ノードNEと出力ノードNZとの間の電圧差がNチャネルMOSFET52Bの閾値電圧を下回ると、NチャネルMOSFET52BがOFFする。この場合、第2ノードN2は、NチャネルMOSFET63Bによってプルアップされる。

【0115】

尚、デプレッション型のNチャネルMOSFET63Bは、NチャネルMOSFET52B、64BがOFFした後に第2ノードN2がフローティング状態になることを防止する役割も果たしている。これにより、第2ノードN2に対するノイズ耐性が強まる。

【0116】

ターンオフ期間PC及びOFF期間PDにおいて、ノードNAの信号(制御信号CON)はHighレベルである。この場合、PチャネルMOSFET61B、67B、及びNチャネルMOSFET64BがOFFする。

【0117】

その一方で、タイマー回路100は、ターンオフ期間PCの開始から所定のタイマー期間PTの間、第1制御信号CON1をLowレベルに設定する。これにより、PチャネルMOSFET69BがONし、ノードNEがプルアップされる。その結果、NチャネルMOSFET52B(第2スイッチ)がONする。すなわち、ターンオフ期間PCにおいても、第1スイッチ51B及び第2スイッチ52Bを介して、第2ノードN2と出力ノードNZとの間の電気的接続が維持される。従って、ショートトランジスタ40BもOFF状態のまま維持される。

【0118】

OFF期間PDでは、上述の通り、NチャネルMOSFET51B(第1スイッチ)がOFFする。これにより、第2ノードN2と出力ノードNZとの間の電気的接続が切断される。第2ノードN2がNチャネルMOSFET63Bによってプルアップされるため、ショートトランジスタ40BがONする。

【0119】

尚、OFF期間PD中に、所定のタイマー期間PTが終了し、タイマー回路100は、第1制御信号CON1をHighレベルに設定する。これにより、PチャネルMOSFET69BがOFFし、ノードNEがプルダウンされる。その結果、NチャネルMOSFET52B(第2スイッチ52B)もOFFする。

【0120】

OFF期間PDでは、PチャネルMOSFET61B、67B、69B、及びNチャネルMOSFET51B、64BはOFFしている。従って、ショート制御回路50Bを通って電源端子TVから出力端子TOに向かって電流は流れない。すなわち、オフ時消費電流は発生しない。

【0121】

尚、ショート制御回路50Bに含まれるNチャネルMOSFETのそれぞれのバックゲートは、出力ノードNZに直接接続されている。そのため、OFF期間PDにおいて、それらバックゲートがハイインピーダンスになることはない。従って、OFF期間PDにおいて、ダンプサージの印加によって、それらNチャネルMOSFETの寄生バイポーラトランジスタが動作することはない。

【0122】

2−2.第2の例

出力端子TOに接続される負荷20が誘導性負荷の場合、ターンオフの際に、逆起電圧(負電圧)が出力端子TOに印加される可能性がある。また、負荷20を接続する配線のインダクタンス成分によっても、同様のことが発生し得る。このような場合、図24に示されるように、ターンオフ期間PCは、第1ノードN1及び出力ノードNZが放電される「放電期間PC1」だけでなく、続いて出力端子TO(出力ノードNZ)に負電圧が印加される「負電圧期間PC2」をも含む。

【0123】

既出の例では、ターンオフ期間PCは、放電期間PC1だけを含んでいた。その放電期間PC1において、第1スイッチ51B及び第2スイッチ52Bの両方がONし、第2ノードN2と出力ノードNZとの間が電気的に接続される。その結果、ショートトランジスタ40Bが、放電期間PC1においてOFF状態に維持される。しかしながら、第1スイッチ51B及び第2スイッチ52Bは、負電圧期間PC2においてもONするとは限らない。従って、第2の例では、第2ノードN2と出力ノードNZとの間に接続され、負電圧期間PC2においてONする第3スイッチ53Bが追加される。

【0124】

図25は、第2の例を示す回路図である。第2の例では、図23で示された回路構成に対して、過電圧保護回路80、制御回路90、及び第3スイッチ53Bが更に追加されている。

【0125】

過電圧保護回路80(ダイナミッククランプ回路)は、電源端子TVと第1ノードN1との間に接続されている。具体的には、過電圧保護回路80は、PチャネルMOSFET81、ダイオード82、83を備えている。PチャネルMOSFET81のソースは、電源端子TVに接続されている。PチャネルMOSFET81のゲート及びドレインは、ダイオード82のカソードに接続されている。ダイオード82のアノードは、ダイオード83のアノードに接続されている。ダイオード83のカソードは、第1ノードN1に接続されている。この過電圧保護回路80は、負電圧期間PC2において動作する。

【0126】

制御回路90は、PチャネルMOSFET91及びデプレッション型のNチャネルMOSFET92を備えている。PチャネルMOSFET91のゲート、ソース及びドレインは、それぞれ、PチャネルMOSFET81のゲート、電源端子TV及び第5ノードN5に接続されている。NチャネルMOSFET92のドレインは第5ノードN5に接続され、そのソース及びゲートは出力ノードNZに接続されている。

【0127】

PチャネルMOSFET81、91はカレントミラー回路を構成している。過電圧保護回路80が動作すると、第5ノードN5が充電され、その電圧はHighレベルになる。過電圧保護回路80が非動作の場合、第5ノードN5の電圧は出力ノードNZの電圧と同等になる。この第5ノードN5の電圧が、第3スイッチ53BをON/OFF制御するための第2制御信号CON2として使用される。すなわち、制御回路90は、過電圧保護回路80の動作時にだけ第2制御信号CON2を活性化(CON2=Highレベル)する。

【0128】

第3スイッチ53Bは、第2ノードN2と出力ノードNZとの間に接続されている。特に、第3スイッチ53Bは、既出の第1スイッチ51B及び第2スイッチ52Bに対して並列となるように接続されている。第3スイッチ53Bは、第2制御信号CON2が活性化されている時(CON2=Highレベル)にONし、非活性化されている時にOFFする。第3スイッチ53Bは、例えばNチャネルMOSFETであり、そのゲート、ソース及びドレインは、それぞれ第5ノードN5、出力ノードNZ及び第2ノードN2に接続されている。制御信号CON2が活性化されHighレベルになると、NチャネルMOSFET53BはONする。その結果、第2ノードN2と出力ノードNZが電気的に接続される。

【0129】

図25及び図26を参照して、本例におけるターンオフ期間PCについて説明する。そのターンオフ期間PCは、放電期間PC1と負電圧期間PC2を含んでいる。

【0130】

(放電期間PC1:時刻t3〜tm)

既出の例の場合と同様に、第1スイッチ51B及び第2スイッチ52Bの両方がONする。そのため、第2ノードN2と出力ノードNZとが電気的に接続され、ショートトランジスタ40BはOFF状態に維持される。

【0131】

(負電圧期間PC2:時刻tm〜t4)

負電圧期間PC2において、過電圧保護回路80を正常に動作させるためには、出力トランジスタ10を低いゲート−ソース間電圧でオンさせる必要がある。従って、ショートトランジスタ40BがONして、第1ノードN1と出力ノードNZとがショートすることは望ましくない。すなわち、負電圧期間PC2においてもショートトランジスタ40BをOFFのまま保つ必要がある。しかしながら、負電圧期間PC2では第1スイッチ51Bあるいは第2スイッチ52BがOFFする可能性がある。従って、負電圧期間PC2用に第3スイッチ53Bが設けられている。

【0132】

より詳細には、出力端子TOに負電圧が印加されると、過電圧保護回路80のPチャネルMOSFET81からダイオード82、83、抵抗素子RES、ゲート充放電回路30の放電トランジスタ33を通して出力端子TOへの電流経路が形成される。これにより、出力トランジスタ10のドレイン−ソース間電圧が、過電圧保護回路のクランプ電圧にクランプされる。過電圧保護回路80がこのように動作すると、上述の通り、制御回路90は、第2制御信号CON2を活性化(CON2=Highレベル)する。それに応答して、第3スイッチ53BがONし、第2ノードN2と出力ノードNZが電気的に接続される。その結果、ショートトランジスタ40BがOFF状態に保たれる。

【0133】

負電圧期間PC2が終わると、第3スイッチ53BはOFFする。

【0134】

以上に説明されたように、第2の実施の形態に係るショートトランジスタ40B及びショート制御回路50Bは、負電圧期間PC2に関連する特性(過電圧保護等)にも影響を及ぼさない。

【0135】

2−3.第3の例

図27は、第3の例を示す回路図である。第3の例では、図25で示された回路構成に対して、遅延回路70B及び補助スイッチ66Bが更に追加されている。第3スイッチ53BとしてのNチャネルMOSFETのドレインは、第2ノードN2の代わりにノードN2’に接続されている。そのノードN2’が、遅延回路70Bを介して、第2ノードN2に接続されている。

【0136】

図27及び図28を参照して、OFF期間PD中に電源端子TVにダンプサージが印加された場合を考える。電源端子TVにダンプサージが印加された際、過電圧保護回路80のPチャネルMOSFET81のゲート電圧が一瞬Lowレベルに下がることがある。この場合、第2制御信号CON2が活性化され、第3スイッチ53BのOFF状態が解除されてしまう。図28の例では、時刻t5〜tsの短い期間、第3スイッチ53BがONし、ノードN2’が放電されてしまう。もし、遅延回路70Bがなければ、ショートトランジスタ40Bのゲートにつながる第2ノードN2も放電されてしまい、ショートトランジスタ40BがOFFしてしまう。このことは、出力トランジスタ10のゲート−ソース間のショートの解除を意味し、好ましくない。

【0137】

一方、本例によれば、ノードN2’と第2ノードN2との間に遅延回路70Bが設けられている。従って、たとえノードN2’が放電されても、第2ノードN2の電圧レベルは、ある程度の時間Highレベルに維持される。つまり、時刻t5〜tsの期間においても、ショートトランジスタ40BはON状態のまま維持される。このように、OFF期間PDの最中に出力トランジスタ10のゲート−ソース間のショートが解除されることが防止される。

【0138】

図29A及び図29Bは、遅延回路70Bの構成例を示している。図29Aの例では、抵抗素子71Bと容量素子72Bとにより、遅延回路70Bが構成されている。図29Bの例では、定電流源として機能するデプレッション型のNチャネルMOSFET73Bと、容量素子72Bとにより、遅延回路70Bが構成されている。OFF期間PDにおいて、遅延回路70Bの容量素子72Bは、電源電圧VDDに充電されている。上記理由によりノードN2’が放電された場合であっても、遅延回路70Bの容量素子72Bが放電されるまでは、第2ノードN2の電圧レベルをHighレベルに保つことができる。尚、遅延回路70Bの放電時定数は、ノードN2’の放電時定数よりも大きく設計される。

【0139】

尚、ターンオン期間PAの開始時(時刻t1:図22参照)、第2ノードN2を速やかに放電し、ショートトランジスタ40BをOFFする必要がある。しかしながら、本例では、ノードN2’と第2ノードN2との間に遅延回路70Bが介在しており、NチャネルMOSFET64Bを通した放電は遅延する。このような遅延回路70Bの影響を無くすために、補助スイッチ66Bが追加されている。補助スイッチ66Bは、第2ノードN2と出力ノードNZとの間に接続されており、ターンオン期間PAにおいてONする。その結果、ターンオン期間PAの開始時に、補助スイッチ66Bを通して第2ノードN2が速やかに放電される。つまり、ターンオン期間PAへの遅延回路70Bの影響が排除される。

【0140】

例えば、補助スイッチ66BはNチャネルMOSFETであり、そのゲート、ソース及びドレインは、それぞれ第3ノードN3、出力ノードNZ及び第2ノードN2に接続されている。ターンオン期間PAにおいて、第3ノードN3には電源電圧VDDが印加される。第3ノードN3と出力ノードNZとの間の電圧差(N3−NZ)が閾値電圧を下回るまで、NチャネルMOSFET66BはONする。ターンオン期間PA以外において、NチャネルMOSFET66BはOFFする。これにより、上記目的が達成される。

【0141】

2−4.第4の例

既出の例において、ターンオフ期間PCでの初期動作には注意を要する。上述の通り、ターンオフ期間PCの開始時に、第1制御信号CON1がLowレベルに変わり、ノードNEが電源電圧VDDにプルアップされる。但し、出力ノードNZの電圧が電源電圧VDDに近い初期段階では、NチャネルMOSFET52Bのゲート−ソース間電圧がその閾値電圧よりも低く、NチャネルMOSFET52B(第2スイッチ)がOFFのままである可能性がある。この場合、第2ノードN2がNチャネルMOSFET63Bによってプルアップされ、それにより、ショートトランジスタ40BがONする可能性がある。すなわち、ターンオフ期間PCの初期段階において、一瞬、ショートトランジスタ40BがONし、第1ノードN1からショートトランジスタ40Bを通して出力ノードNZへ向かう放電経路が形成されてしまう可能性がある。

【0142】

このような現象を防止するためには、NチャネルMOSFET52B(第2スイッチ)が、ショートトランジスタ40Bよりも早くONすればよい。つまり、NチャネルMOSFET52Bの閾値電圧が、ショートトランジスタ40Bの閾値電圧よりも小さく設計されていればよい。

【0143】

あるいは、図30に示される構成も有効である。図30に示される例では、図23で示された回路構成に対して、ショートスイッチ回路4の構成要素として他のショートトランジスタ41B(NチャネルMOSFET)が更に追加されている。ショートトランジスタ40B、41Bは、第1ノードN1と出力ノードNZとの間に直列に接続されている。図30では、ショートトランジスタ41Bのゲート、ソース及びドレインは、それぞれ、第4ノードN4、出力ノードNZ及び第1ノードN1側に接続されている。タイマー期間PTにおいて、第1制御信号CON1はLowレベルになり、ショートトランジスタ41BはOFFする。その他の期間において、第1制御信号CON1はHighレベルになり、ショートトランジスタ41BはONする。

【0144】

ターンオフ期間PCの初期段階において、出力ノードNZの電圧は電源電圧VDDに近い。その一方で、第4ノードN4にはLowレベルの第1制御信号CON1が印加される。従って、ショートトランジスタ41Bは完全にOFFする。よって、ターンオフ期間PCの初期段階においてショートトランジスタ40Bが一瞬ONしたとしても、第1ノードN1からショートトランジスタ40B、41Bを通して出力ノードNZへ向かう放電経路は形成されない。タイマー期間PT以外においては、ショートトランジスタ41BはONするため、既出の例の場合と同じ動作が実現される。

【0145】

2−5.第5の例

上述の例のうちいくつかを組み合わせることも可能である。図31は、第1〜第4の例の全てを組み合わせた場合の回路構成を示している。

【0146】

2−6.タイマー回路

本実施の形態に係るタイマー回路100は、パワーON信号PWRがHighレベルからLowレベルに変わった後、所定のタイマー期間PTだけ、Lowレベルの第1制御信号CON1を第4ノードN4に出力する。その他の期間、タイマー回路100は、Highレベルの第1制御信号CON1を第4ノードN4に出力する。このようなタイマー回路100の一例を説明する。

【0147】

図32は、タイマー回路100の構成例を示す回路図である。タイマー回路100は、インバータ回路131、内部電圧制御回路150、遅延生成回路151、レベルシフト回路152、及びRSフリップフロップ回路146を備えている。

【0148】

インバータ回路131は、電源端子TVとグランド端子TGとの間に接続されている。インバータ回路131は、パワーON信号PWRを受け取り、その反転信号PWRBを出力する。

【0149】

内部電圧制御回路150は、反転信号PWRBとRSフリップフロップ回路146の出力信号によって、第4ノードN4の電圧を制御する。内部電圧制御回路150は、PチャネルMOSFET132、133、ツェナーダイオード134、NチャネルMOSFET135、136、137を備えている。PチャネルMOSFET132、133のソースは電源端子TVに接続されており、それらのドレインは第4ノードN4に接続されている。PチャネルMOSFET132のゲートには、反転信号PWRBが入力される。PチャネルMOSFET133のゲートは、RSフリップフロップ回路146の出力端子QBに接続されている。ツェナーダイオード134のカソード及びアノードは、それぞれ電源端子TV及び第4ノードN4に接続されている。デプレッション型のNチャネルMOSFET135のドレインは、第4ノードN4に接続されており、そのソース及びゲートは、NチャネルMOSFET136のドレインに接続されている。NチャネルMOSFET136ソース及びゲートは、それぞれ、NチャネルMOSFET137のドレイン及びRSフリップフロップ回路146の出力端子QBに接続されている。NチャネルMOSFET137のソースは、グランド端子TGに接続されており、そのゲートには反転信号PWRBが入力される。

【0150】

遅延生成回路151は、PチャネルMOSFET138、140、142、NチャネルMOSFET139、143、及び容量素子141を備えている。PチャネルMOSFET138のソースは電源端子TVに接続され、そのドレイン及びゲートはNチャネルMOSFET139のドレインに接続されている。PチャネルMOSFET140のソース、ドレイン及びゲートは、それぞれ、電源端子TV、容量素子141の一端(timer_a)及びPチャネルMOSFET138のゲートに接続されている。PチャネルMOSFET138、140は、カレントミラー回路を構成している。デプレッション型のNチャネルMOSFET139のソースとゲートは、第4ノードN4に接続されている。このNチャネルMOSFET139は、PチャネルMOSFET138、140から構成されるカレントミラー回路の基準電流源となる。容量素子141の他端は、第4ノードN4に接続されている。この容量素子141は、PチャネルMOSFET140からの定電流を充電して、遅延時間を生成する。PチャネルMOSFET142のソース、ドレイン及びゲートは、それぞれ、電源端子TV、NチャネルMOSFET143のドレイン、及び容量素子141の一端(timer_a)に接続されている。デプレッション型のNチャネルMOSFET143のソースとゲートは、第4ノードN4に接続されている。PチャネルMOSFET142とNチャネルMOSFET143は、インバータ回路を構成しており、容量素子141の充電電圧(timer_aの電圧)がその論理しきい値と越えると、遅延時間信号を出力する。

【0151】

レベルシフト回路152は、遅延生成回路151から出力される遅延時間信号のレベルシフトを行う。レベルシフト回路152は、PチャネルMOSFET144及びデプレッション型のNチャネルMOSFET145を備えている。PチャネルMOSFET144のソース、ドレイン及びゲートは、それぞれ、電源端子TV、出力端子timer_b、及び遅延生成回路151のインバータ回路の出力端子に接続されている。NチャネルMOSFET145のソース及びゲートは、グランド端子TGに接続されており、そのドレインは出力端子timer_bに接続されている。レベルシフト回路152の出力端子timer_bは、RSフリップフロップ回路146のセット端子Sに接続されている。

【0152】

RSフリップフロップ回路146は、パワーON信号PWRとレベルシフト回路152の出力信号(timer_b)に応じて、出力信号Q、QBを出力し、内部電圧制御回路150を制御する。RSフリップフロップ回路146はセット優先で動作する。RSフリップフロップ回路146は、電源端子TVとグランド端子TGとの間に接続されている。RSフリップフロップ回路146のセット端子Sはレベルシフト回路152の出力端子timer_bに接続され、そのリセット端子Rは入力端子TIに接続されている。

【0153】

図33は、図32に示されたタイマー回路100の動作を示すタイミングチャートである。

【0154】

状態(1)は、OFF期間PDに相当する。状態(1)では、RSフリップフロップ回路146がセット優先で動作するため、反転信号QBはLowレベルである。そのため、内部電圧制御回路150のNチャネルMOSFET136がOFFし、第4ノードN4とグランド端子TGとの間の電気的接続が遮断される。一方、PチャネルMOSFET133はONするため、第4ノードN4は電源電圧VDDにプルアップされる。

【0155】

状態(2)は、ターンオン期間PA及びON期間PBに相当する。パワーON信号PWRがHighレベルに変化するため、RSフリップフロップ回路146がリセットされ、反転信号QBはHighレベルとなる。これにより、NチャネルMOSFET136はONし、PチャネルMOSFET133はOFFする。その一方、パワーON信号PWRの反転信号PWRBがLowレベルであるため、NチャネルMOSFET137はOFFし、PチャネルMOSFET132はONする。従って、第4ノードN4とグランド端子TGとの間の電気的接続が遮断され、第4ノードN4は電源電圧VDDにプルアップされる。

【0156】

状態(3)は、タイマー期間PTに相当する。パワーON信号PWRがLowレベルに変化するため、RSフリップフロップ回路146のリセットが解除されるが、RSフリップフロップ146の状態は変化しない。従って、反転信号QBはHighレベルのままである。その一方で、パワーON信号PWRの反転信号PWRBがHighレベルに変わるため、PチャネルMOSFET132はOFFし、NチャネルMOSFET137はONする。その結果、第4ノードN4がグランド端子TGと電気的に接続される。

【0157】

このとき、ツェナーダイオード134により、第4ノードN4の電圧は、電源電圧VDDからツェナー耐圧だけ低い電圧となる。デプレッション型のNチャネルMOSFET135は、ツェナーダイオード134に流れる電流を制限する役割を持つ。

【0158】

第4ノードN4の電圧が電源電圧VDDよりも低くなると、遅延生成回路151がアクティブとなり、遅延時間の生成を開始する。具体的には、遅延生成回路151は、カレントミラー回路により容量素子141に対して定電流を供給して、容量素子141を充電する。つまり、ノードtimer_aの電圧は、時間と共に単調増加する。ノードtimer_aの電圧が、次段のインバータ回路(PチャネルMOSFET142とNチャネルMOSFET143から構成される)の論理しきい値を越すまでは、レベルシフト回路152の出力端子timer_bはLowレベルのままである。

【0159】

ノードtimer_aの電圧が、次段のインバータ回路の論理しきい値を越すと、レベルシフト回路152の出力端子timer_bはHighレベルとなる。つまり、RSフリップフロップ回路146のセット端子SにHighレベル信号(セット信号)が与えられ、RSフリップフロップ回路146の反転信号QBはLowレベルに変化する。この状態(4)は、タイマー期間PT後のOFF期間PDに相当する。

【0160】

3.第3の実施の形態

<基本構成>

図34は、第3の実施の形態に係る電力用半導体装置1の構成を概略的に示すブロック図である。第3の実施の形態において、ショートスイッチ回路4は、第1ノードN1と出力ノードNZとの間に直列に接続された第1ショートスイッチ41C及び第2ショートスイッチ42Cを含んでいる。また、本実施の形態におけるショート制御回路50は、ショート制御回路50Cと参照される。ショート制御回路50Cは、第1ショートスイッチ41Cと第2ショートスイッチ42CのそれぞれをON/OFF制御することによって、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をON/OFFすることができる。

【0161】

<基本動作>

図35は、第3の実施の形態に係る電力用半導体装置1の動作を示すタイミングチャートである。以下、図34及び図35を参照して、電力用半導体装置1の基本的な動作を説明する。その動作を説明するにあたり、4つの期間(フェーズ):ターンオン期間PA、ON期間PB、ターンオフ期間PC、及びOFF期間PD、を考える。

【0162】

ターンオン期間PA及びON期間PBは、パワーON信号PWRが活性化(PWR=Highレベル)されている期間である。パワーON信号PWRが活性化されると、第1ノードN1は充電され、出力トランジスタ10はONし、出力ノードNZも充電される。ON期間PBは、第1ノードN1及び出力ノードNZの電圧が安定し、出力トランジスタ10が安定的にONしている期間である。一方、ターンオン期間PAは、パワーON信号PWRの活性化タイミングからON期間PBまでの期間である。言い換えれば、ターンオン期間PAは、OFF期間PDからON期間PBへの遷移期間である。

【0163】

ターンオフ期間PC及びOFF期間PDは、パワーON信号PWRが非活性化(PWR=Lowレベル)されている期間である。パワーON信号PWRが非活性化されると、第1ノードN1は放電され、出力トランジスタ10はOFFし、出力ノードNZも放電される。OFF期間PDは、第1ノードN1及び出力ノードNZの電圧が安定し、出力トランジスタ10が安定的にOFFしている期間である。一方、ターンオフ期間PCは、パワーON信号PWRの非活性化タイミングからOFF期間PDまでの期間である。言い換えれば、ターンオフ期間PCは、ON期間PBからOFF期間PDへの遷移期間である。

【0164】

更に、第3の実施の形態では、「制御期間PX」が説明に用いられる。制御期間PXは、パワーON信号PWRが非活性化されるタイミング、すなわち、ターンオフ期間PCの開始と同時に始まる。その制御期間PXの長さは、ターンオフ期間PCの長さ以上である。制御期間PXとターンオフ期間PCとが一致する場合もある。後に詳しく説明されるように、この制御期間PXでは、第1ショートスイッチ41C及び第2ショートスイッチ42Cのうち少なくとも一方がOFFする。

【0165】

(ターンオン期間PA:時刻t1〜t2)

時刻t1において、パワーON信号PWRが活性化され、LowレベルからHighレベルに変わる。それに応答して、ゲート充放電回路30は、ノードND及び第1ノードN1を充電し始める。このターンオン期間PAにおいて、ショート制御回路50Cは、第1ショートスイッチ41Cと第2ショートスイッチ42Cのうち少なくとも一方をOFFする。図35で示される例では、ショート制御回路50Cは、第2ショートスイッチ42CをOFFする。従って、第1ノードN1と出力ノードNZとの間、すなわち、出力トランジスタ10のゲート−ソース間はショートしない。出力トランジスタ10はONし、出力ノードNZの電圧も徐々に上昇する。尚、ターンオン期間PAにおいて、第1ノードN1は、電源電圧VDDよりも高い高電圧まで充電される。

【0166】

(ON期間PB:時刻t2〜t3)

ON期間PBにおいて、ショート制御回路50Cは、第2ショートスイッチ42CをOFFのまま維持する。第1ノードN1の電圧は、電源電圧VDDよりも高い高電圧で安定する。出力ノードNZの電圧は、電源電圧VDD近傍で安定する。出力トランジスタ10は、安定的にONしている。

【0167】

(ターンオフ期間PC:時刻t3〜t4)

時刻t3において、パワーON信号PWRが非活性化され、HighレベルからLowレベルに変わる。それに応答して、ゲート充放電回路30は、ノードND及び第1ノードN1を放電し始める。このターンオフ期間PCにおいても、ショート制御回路50Cは、第1ショートスイッチ41Cと第2ショートスイッチ42Cのうち少なくとも一方をOFFする。図35で示される例では、ショート制御回路50Cは、パワーON信号PWRの非活性化に応答して、第2ショートスイッチ42CをONする。その一方で、ショート制御回路50Cは、上述の制御期間PX(時刻t3〜tx)の間、第1ショートスイッチ41CをOFFする。従って、第1ショートスイッチ41C及び第2ショートスイッチ42Cを通した放電は発生しない。すなわち、第1ノードN1の放電は、従来通りゲート充放電回路30によってのみ行われる。第1ノードN1の電圧が低下すると、出力ノードNZの電圧も徐々に低下し、最終的に0Vになる。出力トランジスタ10はOFFする。

【0168】

(OFF期間PD:時刻t4〜)

OFF期間PDにおいて、ショート制御回路50Cは、第2ショートスイッチ42CをONのまま維持する。また、制御期間PXが終了すると、ショート制御回路50Cは、第1ショートスイッチ41CもONする。すなわち、制御期間PX終了後のOFF期間PDにおいて、ショート制御回路50Cは、第1ショートスイッチ41Cと第2ショートスイッチ42Cの両方をONする。これにより、第1ノードN1と出力ノードNZとの間、すなわち、出力トランジスタ10のゲート−ソース間がショートする。出力トランジスタ10は、安定的にOFFしている。

【0169】

このように、ショート制御回路50Cは、パワーON信号PWRに同期して第2ショートスイッチ42CをON/OFF制御し、特にパワーON信号PWRが活性化されている間は第2ショートスイッチ42CをOFFする。その一方で、ショート制御回路50Cは、ターンオフ期間PCを含む制御期間PXにおいて、第1ショートスイッチ41CをOFFする。その結果、ターンオン期間PA及びON期間PBだけでなく、ターンオフ期間PCにおいても、第1ショートスイッチ41C及び第2ショートスイッチ42Cを通した第1ノードN1の放電が防止される。すなわち、第3の実施の形態に係るショートスイッチ41C、42C及びショート制御回路50Cは、出力トランジスタ10のターンオフに関連する特性(ターンオフに要する時間等)に影響を与えない。

【0170】

<ダンプサージ印加時の動作>

次に、制御期間PX終了後のOFF期間PDにおいて、ダンプサージ等の印加によって、電源電圧VDDの急峻な増加が発生した場合を考える。図35に示される例では、制御期間PX終了後のOFF期間PDの最中の時刻t5〜t6において、ダンプサージが電源端子TVに印加される。

【0171】

図36は、ゲート充放電回路30が既出の図1、図3で示されたものと同じ構成を有している場合を示している。上述の通り、ゲート充放電回路30の放電トランジスタ33は、寄生バイポーラトランジスタQ1を有している。寄生バイポーラトランジスタQ1のコレクタ、エミッタ及びベースは、それぞれ電源端子TV、ノードND及びノードNBに接続されている。また、寄生容量(コレクタ−ベース間容量)C1が、電源端子TVとノードNBとの間に接続されている。

【0172】

OFF期間PDの最中に、電源電圧VDDの急峻な増加が発生した場合、上述の通り、寄生バイポーラトランジスタQ1がONする可能性がある。寄生バイポーラトランジスタQ1がONすると、ノードNDの電圧が持ち上がる。しかしながら、制御期間PX終了後のOFF期間PDにおいて、第1ショートスイッチ41C及び第2ショートスイッチ42CはONしており、第1ノードN1と出力ノードNZとの間、すなわち、出力トランジスタ10のゲート−ソース間はショートしている。ゲート−ソース間電圧が閾値電圧を超えないため、出力トランジスタ10はONすることなく、OFF状態を維持する。

【0173】

尚、ノードNDと第1ノードN1との間には抵抗素子RESが介在している。ノードNDの電圧が持ち上がった場合、ノードNDから、抵抗素子RES、第1ノードN1及びショートスイッチ41C、42Cを通して、出力ノードNZへ電流が流れる。この時、抵抗素子RESにおいてIRドロップが発生するため、第1ノードN1の電圧がLowレベルに維持される。つまり、抵抗素子RESを利用することによって、第1ノードN1の電圧をLowレベルに維持しやすくなる。

【0174】

<効果>

第3の実施の形態によれば、制御期間PX終了後のOFF期間PDにおいて、第1ノードN1と出力ノードNZとの間に接続された第1ショートスイッチ41C及び第2ショートスイッチ42CがONする。これにより、第1ノードN1と出力ノードNZとの間、すなわち、出力トランジスタ10のゲート−ソース間がショートする。従って、電源電圧VDDの急峻な増加が発生した場合であっても、出力トランジスタ10がONすることが防止される。すなわち、出力トランジスタ10の熱破壊が防止される。

【0175】

また、第3の実施の形態によれば、ターンオン期間PA、ON期間PB及びターンオフ期間PCにおいて、第1ショートスイッチ41C及び第2ショートスイッチ42Cの少なくとも一方はOFFのまま維持される。従って、ターンオン期間PA、ON期間PB及びターンオフ期間PCにおいて、ショートスイッチ41C、42C及びショート制御回路50Cは、第1ノードN1に影響を及ぼさない。つまり、ショートスイッチ41C、42C及びショート制御回路50Cは、出力トランジスタ10のターンオン/ターンオフに関連する特性(ターンオン/ターンオフに要する時間等)に影響を与えない。すなわち、第3の実施の形態によれば、ターンオン/ターンオフに関連する特性に影響を及ぼすことなく、出力トランジスタ10の熱破壊を防止することが可能である。

【0176】

<ショート制御回路の概要>

図37は、第3の実施の形態に係る第1ショートスイッチ41C、第2ショートスイッチ42C及びショート制御回路50Cの構成を概略的に示している。第1ショートスイッチ41Cとして、例えば、NチャネルMOSFET(以下、「第1ショートトランジスタ41C」と参照される)が用いられる。また、第2ショートスイッチ42Cとして、例えば、NチャネルMOSFET(以下、「第2ショートトランジスタ42C」と参照される)が用いられる。第1ショートトランジスタ41Cのソース、ドレイン及びゲートは、それぞれ、第2ショートトランジスタ42Cのドレイン、第1ノードN1及び第2ノードN2に接続されている。第2ショートトランジスタ42Cのソース及びドレインは、それぞれ、出力ノードNZ及び第1ショートトランジスタ41Cのソースに接続されている。

【0177】

第2ショートトランジスタ42Cのゲートには、制御信号PWR’が供給される。ショート制御回路50Cは、制御信号PWR’を供給することにより、第2ショートトランジスタ42CをON/OFF制御する。例えば、制御信号PWR’は、パワーON信号PWRの反転信号である。この場合、パワーON信号PWRが活性化(PWR=Highレベル)されるターンオン期間PA及びON期間PBにおいて、制御信号PWR’が非活性化され(PWR’=Lowレベル)、第2ショートトランジスタ42CがOFFする。また、パワーON信号PWRが非活性化(PWR=Lowレベル)されるターンオフ期間PC及びOFF期間PDにおいて、制御信号PWR’が活性化され(PWR’=Highレベル)、第2ショートトランジスタ42CがONする。

【0178】

第1ショートトランジスタ41Cのゲートは、第2ノードN2に接続されている。この第2ノードN2の電圧を制御することによって、第1ショートトランジスタ41CをON/OFF制御することが可能である。ショート制御回路50Cは、第2ノードN2に接続されており、第2ノードN2の電圧を制御する。より詳細には、ショート制御回路50Cは、スイッチ部60C及びタイマー回路100を備えている。

【0179】

スイッチ部60Cは、第2ノードN2と電源端子TVとの間の電気的接続、及び、第2ノードN2と出力ノードNZとの間の電気的接続を制御する。より詳細には、少なくとも上記制御期間PXにおいて、スイッチ部60Cは、第2ノードN2と出力ノードNZとを電気的に接続する。これにより、第1ショートトランジスタ41Cのゲート−ソース間がショートするため、第1ショートトランジスタ41CがOFFする。また、制御期間PX終了後のOFF期間PDにおいて、スイッチ部60Cは、第2ノードN2と出力ノードNZとの間の電気的接続を切断し、その一方で、第2ノードN2と電源端子TVとを電気的に接続する。その結果、第1ショートトランジスタ41CがONする。

【0180】

ここで、制御期間PXは、所定のタイマー期間PTを含んでいる。その所定のタイマー期間PTは、パワーON信号PWRが非活性化されるタイミング(時刻t3)、すなわち、ターンオフ期間PCの開始と同時に始まる。また、所定のタイマー期間PTの長さは、典型的には、ターンオフ期間PCの長さ以上に設計される。但し、後述の第2の例において説明されるように、ターンオフ期間PCが放電期間PC1と負電圧期間PC2を含んでいる場合(図40参照)、所定のタイマー期間PTの長さは、放電期間PC1の長さ以上であればよい。

【0181】

所定のタイマー期間PTは、タイマー回路100から出力される第1制御信号CON1に基いて把握することができる。具体的には、タイマー回路100は、所定のタイマー期間PTの間だけ、第1制御信号CON1を活性化(CON1=Lowレベル)する。所定のタイマー期間PT以外においては、タイマー回路100は、第1制御信号CON1を非活性化(CON1=Highレベル)する。尚、タイマー回路100は、既出の図32、図33で示されたものと同様である。

【0182】

図37及び図38を参照して、第3の実施の形態に係るショート制御回路50Cの動作を説明する。最も簡単な例として、ターンオフ期間PCが放電期間PC1だけを含んでおり、タイマー期間PTと制御期間PXが一致する場合を考える。また、スイッチ部60Cは、第2ノードN2と出力ノードNZとの間に接続された第1スイッチ51Cを備えているとする。尚、既出の図35と重複する説明は、適宜省略される。

【0183】

(ターンオン期間PA:時刻t1〜t2)

時刻t1において、パワーON信号PWRが活性化され、LowレベルからHighレベルに変わる。それに応答して、制御信号PWR’が非活性化され(PWR’=Lowレベル)、第2ショートトランジスタ42CがOFFする。

【0184】

(ON期間PB:時刻t2〜t3)

制御信号PWR’はLowレベルのままであり、第2ショートトランジスタ42CはOFFのままである。

【0185】

(ターンオフ期間PC:時刻t3〜t4)

時刻t3において、パワーON信号PWRが非活性化され、HighレベルからLowレベルに変わる。それに応答して、制御信号PWR’が活性化され(PWR’=Highレベル)、第2ショートトランジスタ42CがONする。その一方で、パワー信号PWRの非活性化に応答して、タイマー回路100が、第1制御信号CON1を活性化(CON1=Lowレベル)する。第1制御信号CON1が活性化されている時、スイッチ部60Cは、第1スイッチ51CをONし、第2ノードN2と出力ノードNZとを電気的に接続する。これにより、第1ショートトランジスタ41Cのゲート−ソース間がショートするため、第1ショートトランジスタ41CがOFFする。

【0186】

(OFF期間PD:時刻t4〜)

制御信号PWR’はHighレベルのままであり、第2ショートトランジスタ42CはONのままである。OFF期間PD中の時刻ttにおいて、所定のタイマー期間PTが終了し、タイマー回路100は、第1制御信号CON1を非活性化(CON1=Highレベル)する。第1制御信号CON1が非活性化された後のOFF期間PDにおいて、スイッチ部60Cは、第1スイッチ51CをOFFすることによって第2ノードN2と出力ノードNZとの間の電気的接続を切断し、その一方で、第2ノードN2と電源端子TVとを電気的に接続する。その結果、第1ショートトランジスタ41CがONする。すなわち、第1ショートトランジスタ41Cと第2ショートトランジスタ42Cの両方がONする。

【0187】

このように、制御信号PWR’及び第1制御信号CON1を用いることによって、第1ショートトランジスタ41C及び第2ショートトランジスタ42CのON/OFF制御が実現される。

【0188】

以下、第3の実施の形態に係るショート制御回路50Cの構成の様々な例を説明する。尚、上記と重複する説明は適宜省略される。

【0189】

3−1.第1の例

図39は、第1の例を示す回路図である。スイッチ部60Cは、PチャネルMOSFET61C、65C、NチャネルMOSFET62C、63C、64Cを備えている。

【0190】

PチャネルMOSFET61C及びNチャネルMOSFET62Cは、第1のインバータ回路を構成している。具体的には、PチャネルMOSFET61Cのゲート、ソース及びドレインは、それぞれ、ノードNA、電源端子TV及び第3ノードN3に接続されている。NチャネルMOSFET62Cのゲート、ソース及びドレインは、それぞれ出力ノードNZ、出力ノードNZ及び第3ノードN3に接続されている。尚、NチャネルMOSFET62Cは、デプレッション型である。

【0191】

NチャネルMOSFET63Cは、デプレッション型である。NチャネルMOSFET63C、64Cは、第2のインバータ回路を構成している。具体的には、NチャネルMOSFET63Cのゲート、ソース及びドレインは、それぞれ、第2ノードN2、第2ノードN2及び電源端子TVに接続されている。NチャネルMOSFET64Cのゲート、ソース及びドレインは、それぞれ第3ノードN3、出力ノードNZ及び第2ノードN2に接続されている。

【0192】

PチャネルMOSFET65Cのゲート、ソース及びドレインは、それぞれ、第4ノードN4、電源端子TV及び第3ノードN3に接続されている。この第4ノードN4には、タイマー回路100から第1制御信号CON1が供給される。

【0193】

また、ノードNAの信号(ゲート充放電回路の放電トランジスタ33のゲート制御信号)が、図37及び図38で示された制御信号PWR’として用いられる。以下、図38及び図39を参照して、本例に係るショート制御回路50Cの動作を説明する。

【0194】

ターンオン期間PA及びON期間PBにおいて、ノードNAの信号(制御信号PWR’)はLowレベルである。従って、第2ショートトランジスタ42CがOFFする。また、ゲートがノードNAに接続されたPチャネルMOSFET61CがONし、第3ノードN3がプルアップされる。出力ノードNZの電圧が比較的低い間、NチャネルMOSFET64CがONするため、第2ノードN2と出力ノードNZとが電気的に接続される。従って、第1ショートトランジスタ41CもOFFする。出力ノードNZの電圧が上昇し、第3ノードN3と出力ノードNZとの間の電圧差がNチャネルMOSFET64Cの閾値電圧を下回ると、NチャネルMOSFET64CがOFFする。この場合、第2ノードN2は、NチャネルMOSFET63Cによってプルアップされる。このとき、第1ショートトランジスタ41CはONするかもしれない。しかしながら、第2ショートトランジスタ42CがOFFしているため、第1ノードN1と出力ノードNZとの間がショートすることはない。

【0195】

尚、デプレッション型のNチャネルMOSFET63Cは、NチャネルMOSFET64CがOFFした後に第2ノードN2がフローティング状態になることを防止する役割も果たしている。これにより、第2ノードN2に対するノイズ耐性が強まる。

【0196】

ターンオフ期間PC及びOFF期間PDにおいて、ノードNAの信号(制御信号PWR’)はHighレベルである。従って、第2ショートトランジスタ42CがONし、また、PチャネルMOSFET61CがOFFする。その一方で、タイマー回路100は、ターンオフ期間PCの開始から所定のタイマー期間PTの間、第1制御信号CON1をLowレベルに設定する。これにより、PチャネルMOSFET65CがONし、第3ノードN3がプルアップされる。その結果、NチャネルMOSFET64CがONするため、第2ノードN2と出力ノードNZとが電気的に接続される。このNチャネルトランジスタ64Cが、図37及び図38で示された「第1スイッチ51C」に相当する。第1ショートトランジスタ41Cのゲート−ソース間がショートするため、第1ショートトランジスタ41CがOFFする。すなわち、タイマー期間PTの間、第1ノードN1と出力ノードNZとの間のショートが防止される。

【0197】

OFF期間PD中の時刻ttにおいて、所定のタイマー期間PTが終了し、タイマー回路100は、第1制御信号CON1をHighレベルに設定する。これにより、PチャネルMOSFET65CがOFFし、第3ノードN3がプルダウンされる。その結果、NチャネルMOSFET64C(第1スイッチ51C)がOFFし、第2ノードN2と出力ノードNZとの間の電気的接続が切断される。第2ノードN2がNチャネルMOSFET63Cによってプルアップされるため、第1ショートトランジスタ41CがONする。すなわち、第1ショートトランジスタ41Cと第2ショートトランジスタ42Cの両方がONする。

【0198】

尚、タイマー期間PT後のOFF期間PDでは、PチャネルMOSFET61C、65C、及びNチャネルMOSFET64CはOFFしている。従って、ショート制御回路50Cを通って電源端子TVから出力端子TOに向かって電流は流れない。すなわち、オフ時消費電流は発生しない。

【0199】

また、ショート制御回路50Cに含まれるNチャネルMOSFETのそれぞれのバックゲートは、出力ノードNZに直接接続されている。そのため、OFF期間PDにおいて、それらバックゲートがハイインピーダンスになることはない。従って、OFF期間PDにおいて、ダンプサージの印加によって、それらNチャネルMOSFETの寄生バイポーラトランジスタが動作することはない。

【0200】

3−2.第2の例

出力端子TOに接続される負荷20が誘導性負荷の場合、ターンオフの際に、逆起電圧(負電圧)が出力端子TOに印加される可能性がある。また、負荷20を接続する配線のインダクタンス成分によっても、同様のことが発生し得る。このような場合、図40に示されるように、ターンオフ期間PCは、第1ノードN1及び出力ノードNZが放電される「放電期間PC1」だけでなく、続いて出力端子TO(出力ノードNZ)に負電圧が印加される「負電圧期間PC2」をも含む。

【0201】

既出の例では、ターンオフ期間PCは、放電期間PC1だけを含んでいた。その放電期間PC1よりも長い所定のタイマー期間PTにおいて、第1スイッチ51C(NチャネルMOSFET64C)がONし、第2ノードN2と出力ノードNZとの間が電気的に接続される。その結果、第1ショートトランジスタ41Cが、放電期間PC1においてOFF状態に維持される。しかしながら、第1スイッチ51C(NチャネルMOSFET64C)は、負電圧期間PC2においてもONするとは限らない。従って、第2の例では、第2ノードN2と出力ノードNZとの間に接続され、負電圧期間PC2においてONする第2スイッチ52Cが追加される。

【0202】

図41は、第2の例を示す回路図である。第2の例では、図39で示された回路構成に対して、過電圧保護回路80、制御回路90、及び第2スイッチ52Cが更に追加されている。

【0203】

過電圧保護回路80(ダイナミッククランプ回路)は、電源端子TVと第1ノードN1との間に接続されている。具体的には、過電圧保護回路80は、PチャネルMOSFET81、ダイオード82、83を備えている。PチャネルMOSFET81のソースは、電源端子TVに接続されている。PチャネルMOSFET81のゲート及びドレインは、ダイオード82のカソードに接続されている。ダイオード82のアノードは、ダイオード83のアノードに接続されている。ダイオード83のカソードは、第1ノードN1に接続されている。この過電圧保護回路80は、負電圧期間PC2において動作する。

【0204】

制御回路90は、PチャネルMOSFET91及びデプレッション型のNチャネルMOSFET92を備えている。PチャネルMOSFET91のゲート、ソース及びドレインは、それぞれ、PチャネルMOSFET81のゲート、電源端子TV及び第5ノードN5に接続されている。NチャネルMOSFET92のドレインは第5ノードN5に接続され、そのソース及びゲートは出力ノードNZに接続されている。

【0205】

PチャネルMOSFET81、91はカレントミラー回路を構成している。過電圧保護回路80が動作すると、第5ノードN5が充電され、その電圧はHighレベルになる。過電圧保護回路80が非動作の場合、第5ノードN5の電圧は出力ノードNZの電圧と同等になる。この第5ノードN5の電圧が、第2スイッチ52CをON/OFF制御するための第2制御信号CON2として使用される。すなわち、制御回路90は、過電圧保護回路80の動作時にだけ第2制御信号CON2を活性化(CON2=Highレベル)する。

【0206】

第2スイッチ52Cは、第2ノードN2と出力ノードNZとの間に接続されている。この第2スイッチ52Cは、第2制御信号CON2が活性化されている時(CON2=Highレベル)にONし、非活性化されている時にOFFする。第2スイッチ52Cは、例えばNチャネルMOSFETであり、そのゲート、ソース及びドレインは、それぞれ第5ノードN5、出力ノードNZ及び第2ノードN2に接続されている。制御信号CON2が活性化されHighレベルになると、NチャネルMOSFET52CはONする。その結果、第2ノードN2と出力ノードNZが電気的に接続される。

【0207】

図41及び図42を参照して、本例におけるターンオフ期間PCについて説明する。そのターンオフ期間PCは、放電期間PC1と負電圧期間PC2を含んでいる。

【0208】

(放電期間PC1:時刻t3〜tm)

既出の例の場合と同様に、第1スイッチ51CがONする。そのため、第2ノードN2と出力ノードNZとが電気的に接続され、第1ショートトランジスタ41CはOFF状態に維持される。

【0209】

(負電圧期間PC2:時刻tm〜t4)

負電圧期間PC2において、過電圧保護回路80を正常に動作させるためには、出力トランジスタ10を低いゲート−ソース間電圧でオンさせる必要がある。従って、第1ショートトランジスタ41C及び第2ショートトランジスタ42Cの両方がONして、第1ノードN1と出力ノードNZとがショートすることは望ましくない。すなわち、負電圧期間PC2においても第1ショートトランジスタ41CをOFFのまま保つ必要がある。しかしながら、負電圧期間PC2中にタイマー期間PTが終了すると、第1スイッチ51CはOFFする可能性がある。従って、負電圧期間PC2用に第2スイッチ52Cが設けられている。

【0210】

より詳細には、出力端子TOに負電圧が印加されると、過電圧保護回路80のPチャネルMOSFET81からダイオード82、83、抵抗素子RES、ゲート充放電回路30の放電トランジスタ33を通して出力端子TOへの電流経路が形成される。これにより、出力トランジスタ10のドレイン−ソース間電圧が、過電圧保護回路のクランプ電圧にクランプされる。過電圧保護回路80がこのように動作すると、上述の通り、制御回路90は、第2制御信号CON2を活性化(CON2=Highレベル)する。それに応答して、第2スイッチ52CがONし、第2ノードN2と出力ノードNZが電気的に接続される。その結果、第1ショートトランジスタ41CがOFF状態に保たれる。

【0211】

負電圧期間PC2が終わると、第2スイッチ52CはOFFする。

【0212】

以上に説明されたように、第3の実施の形態に係るショートトランジスタ41C、42C及びショート制御回路50Cは、負電圧期間PC2に関連する特性(過電圧保護等)にも影響を及ぼさない。

【0213】

3−3.第3の例

図43は、第3の例を示す回路図である。第3の例では、図41で示された回路構成に対して、遅延回路70C及び補助スイッチ66Cが更に追加されている。第2スイッチ52CとしてのNチャネルMOSFETのドレインは、第2ノードN2の代わりにノードN2’に接続されている。そのノードN2’が、遅延回路70Cを介して、第2ノードN2に接続されている。

【0214】

図43及び図44を参照して、OFF期間PD中に電源端子TVにダンプサージが印加された場合を考える。電源端子TVにダンプサージが印加された際、過電圧保護回路80のPチャネルMOSFET81のゲート電圧が一瞬Lowレベルに下がることがある。この場合、第2制御信号CON2が活性化され、第2スイッチ52CのOFF状態が解除されてしまう。図44の例では、時刻t5〜tsの短い期間、第2スイッチ52CがONし、ノードN2’が放電されてしまう。もし、遅延回路70Cがなければ、第1ショートトランジスタ41Cのゲートにつながる第2ノードN2も放電されてしまい、第1ショートトランジスタ41CがOFFしてしまう。このことは、出力トランジスタ10のゲート−ソース間のショートの解除を意味し、好ましくない。

【0215】

一方、本例によれば、ノードN2’と第2ノードN2との間に遅延回路70Cが設けられている。従って、たとえノードN2’が放電されても、第2ノードN2の電圧レベルは、ある程度の時間Highレベルに維持される。つまり、時刻t5〜tsの期間においても、第1ショートトランジスタ41CはON状態のまま維持される。このように、OFF期間PDの最中に出力トランジスタ10のゲート−ソース間のショートが解除されることが防止される。

【0216】

図45A及び図45Bは、遅延回路70Cの構成例を示している。図45Aの例では、抵抗素子71Cと容量素子72Cとにより、遅延回路70Cが構成されている。図45Bの例では、定電流源として機能するデプレッション型のNチャネルMOSFET73Cと、容量素子72Cとにより、遅延回路70Cが構成されている。OFF期間PDにおいて、遅延回路70Cの容量素子72Cは、電源電圧VDDに充電されている。上記理由によりノードN2’が放電された場合であっても、遅延回路70Cの容量素子72Cが放電されるまでは、第2ノードN2の電圧レベルをHighレベルに保つことができる。尚、遅延回路70Cの放電時定数は、ノードN2’の放電時定数よりも大きく設計される。

【0217】

尚、ターンオン期間PAの開始時(時刻t1:図38参照)、第2ノードN2を速やかに放電し、第1ショートトランジスタ41CをOFFする必要がある。しかしながら、本例では、ノードN2’と第2ノードN2との間に遅延回路70Cが介在しており、NチャネルMOSFET64C(第1スイッチ51C)を通した放電は遅延する。このような遅延回路70Cの影響を無くすために、補助スイッチ66Cが追加されている。補助スイッチ66Cは、第2ノードN2と出力ノードNZとの間に接続されており、ターンオン期間PAにおいてONする。その結果、ターンオン期間PAの開始時に、補助スイッチ66Cを通して第2ノードN2が速やかに放電される。つまり、ターンオン期間PAへの遅延回路70Cの影響が排除される。

【0218】

例えば、補助スイッチ66CはNチャネルMOSFETであり、そのゲート、ソース及びドレインは、それぞれ第3ノードN3、出力ノードNZ及び第2ノードN2に接続されている。ターンオン期間PAにおいて、第3ノードN3には電源電圧VDDが印加される。第3ノードN3と出力ノードNZとの間の電圧差(N3−NZ)が閾値電圧を下回るまで、NチャネルMOSFET66CはONする。ターンオン期間PA以外において、NチャネルMOSFET66CはOFFする。これにより、上記目的が達成される。

【0219】

3−4.第4の例

既出の例において、ターンオフ期間PCでの初期動作には注意を要する。上述の通り、ターンオフ期間PCの開始時に、ノードNAの信号(制御信号PWR’)がHighレベルに変わり、第2ショートトランジスタ42CがONする。また、第1制御信号CON1がLowレベルに変わり、第3ノードN3が電源電圧VDDにプルアップされる。但し、出力ノードNZの電圧が電源電圧VDDに近い初期段階では、NチャネルMOSFET64Cのゲート−ソース間電圧がその閾値電圧よりも低く、NチャネルMOSFET64CがOFFのままである可能性がある。この場合、第2ノードN2がNチャネルMOSFET63Cによってプルアップされ、それにより、第1ショートトランジスタ41CがONする可能性がある。すなわち、ターンオフ期間PCの初期段階において、一瞬、ショートトランジスタ41C、42Cの両方がONし、第1ノードN1からショートトランジスタ41C、42Cを通して出力ノードNZへ向かう放電経路が形成されてしまう可能性がある。

【0220】

このような現象を防止するためには、NチャネルMOSFET64Cが、第1ショートトランジスタ41Cよりも早くONすればよい。つまり、NチャネルMOSFET64Cの閾値電圧が、第1ショートトランジスタ41Cの閾値電圧よりも小さく設計されていればよい。

【0221】

あるいは、図46に示される構成も有効である。図46に示される例では、図39で示された回路構成に対して、ショートスイッチ回路4の構成要素として第3ショートスイッチ43Cが更に追加されている。第1〜第3ショートスイッチ41C〜43Cは、第1ノードN1と出力ノードNZとの間に直列に接続されている。第3ショートスイッチ43Cは、第1制御信号CON1によってON/OFF制御される。具体的には、第1制御信号CON1が活性化されるタイマー期間PTにおいて、第3ショートスイッチ43CはOFFする。第1制御信号が非活性化されるその他の期間において、第3ショートスイッチ43CはONする。

【0222】

例えば、第3ショートスイッチ43Cとして、NチャネルMOSFET(以下、「第3ショートトランジスタ43C」と参照される)が用いられる。第3ショートトランジスタ43Cのゲート、ソース及びドレインは、それぞれ、第4ノードN4、出力ノードNZ及び第1ノードN1側に接続されている。タイマー期間PTにおいて、第1制御信号CON1はLowレベルになり、第3ショートトランジスタ43CはOFFする。その他の期間において、第1制御信号CON1はHighレベルになり、第3ショートトランジスタ43CはONする。

【0223】

ターンオフ期間PCの初期段階において、出力ノードNZの電圧は電源電圧VDDに近い。その一方で、第4ノードN4にはLowレベルの第1制御信号CON1が印加される。従って、第3ショートトランジスタ43Cは完全にOFFする。よって、ターンオフ期間PCの初期段階において第1ショートトランジスタ41Cが一瞬ONしたとしても、第1ノードN1からショートトランジスタ41C〜43Cを通して出力ノードNZへ向かう放電経路は形成されない。タイマー期間PT以外においては、第3ショートトランジスタ43CはONするため、既出の例の場合と同じ動作が実現される。

【0224】

3−5.第5の例

上述の例のうちいくつかを組み合わせることも可能である。図47は、第1〜第4の例の全てを組み合わせた場合の回路構成を示している。

【0225】

尚、第3の実施の形態の一部又は全部は、以下の付記のように記載されうるが、以下には限られない。

【0226】

(付記1)

電源端子と出力端子との間に接続された出力トランジスタと、

前記出力トランジスタのゲートに接続された第1ノードを充放電し、前記出力トランジスタをON/OFF制御するゲート充放電回路と、

前記第1ノードと前記出力端子との間に直列に接続された第1ショートスイッチ及び第2ショートスイッチと、

前記第1ショートスイッチ及び前記第2ショートスイッチをON/OFF制御するショート制御回路と

を備え、

前記第1ノードが充電された後、前記出力トランジスタが安定的にONしている期間がON期間であり、

前記第1ノードが放電された後、前記出力トランジスタが安定的にOFFしている期間がOFF期間であり、

前記OFF期間から前記ON期間への遷移期間がターンオン期間であり、

前記ON期間から前記OFF期間への遷移期間がターンオフ期間であり、

制御期間は、前記ターンオフ期間と同時に始まり、且つ、前記ターンオフ期間以上の長さを有し、

前記ターンオン期間、前記ON期間及び前記制御期間において、前記ショート制御回路は、前記第1ショートスイッチと前記第2ショートスイッチの少なくとも一方をOFFし、

前記制御期間終了後の前記OFF期間において、前記ショート制御回路は、前記第1ショートスイッチと前記第2ショートスイッチの両方をONする

電力用半導体装置。

【0227】

(付記2)

付記1に記載の電力用半導体装置であって、

前記ショート制御回路は、前記ターンオン期間及び前記ON期間において前記第2ショートスイッチをOFFし、前記ターンオフ期間及び前記OFF期間において前記第2ショートスイッチをONし、

前記ショート制御回路は、少なくとも前記制御期間において前記第1ショートスイッチをOFFし、前記制御期間終了後の前記OFF期間において前記第1ショートスイッチをONする

電力用半導体装置。

【0228】

(付記3)

付記2に記載の電力用半導体装置であって、

前記第1ショートスイッチは、ゲートが第2ノードに接続された第1ショートトランジスタであり、

前記ショート制御回路は、前記第2ノードと前記出力端子との間に接続された少なくとも1つのスイッチを備え、

少なくとも前記制御期間において、前記ショート制御回路は、前記少なくとも1つのスイッチをONすることによって、前記第2ノードと前記出力端子とを電気的に接続し、

前記制御期間終了後の前記OFF期間において、前記ショート制御回路は、前記少なくとも1つのスイッチをOFFし、前記第2ノードと前記電源端子とを電気的に接続する

電力用半導体装置。

【0229】

(付記4)

付記3に記載の電力用半導体装置であって、

前記ターンオフ期間は、前記第1ノード及び前記出力端子が放電される放電期間を含み、

前記制御期間は、所定のタイマー期間を含み、

前記所定のタイマー期間は、前記放電期間と同時に始まり、且つ、前記放電期間以上の長さを有し、

前記ショート制御回路は、更に、前記所定のタイマー期間の間だけ第1制御信号を活性化するタイマー回路を備え、

前記少なくとも1つのスイッチは、前記第2ノードと前記出力端子との間に接続された第1スイッチを含み、

前記第1スイッチは、少なくとも前記第1制御信号が活性化されている時にONし、前記第1制御信号が非活性化された後の前記OFF期間においてOFFする

電力用半導体装置。

【0230】

(付記5)

付記4に記載の電力用半導体装置であって、

前記ターンオフ期間は、更に、前記放電期間に続いて前記出力端子に負電圧が印加される負電圧期間を含み、

前記ショート制御回路は、更に、

前記電源端子と前記第1ノードとの間に接続され、前記負電圧期間に動作する過電圧保護回路と、

前記過電圧保護回路の動作時にだけ第2制御信号を活性化する制御回路と

を備え、

前記少なくとも1つのスイッチは、更に、前記第2ノードと前記出力端子との間に接続された第2スイッチを備え、

前記第2スイッチは、前記第2制御信号が活性化されている時にONし、前記第2制御信号が非活性化されている時にOFFする

電力用半導体装置。

【0231】

(付記6)

付記5に記載の電力用半導体装置であって、

前記第2スイッチは、遅延回路を介して前記第2ノードに接続されており、

前記ショート制御回路は、更に、前記第2ノードと前記出力端子との間に接続された補助スイッチを備え、

前記補助スイッチは、少なくとも前記ターンオン期間においてONする

電力用半導体装置。

【0232】

(付記7)

付記4乃至6のいずれか一項に記載の電力用半導体装置であって、

更に、第3ショートスイッチを備え、

前記第1ショートスイッチ、前記第2ショートスイッチ及び前記第3ショートスイッチは、前記第1ノードと前記出力端子との間に直列に接続され、

前記第3ショートスイッチは、前記第1制御信号が活性化されている時にOFFする

電力用半導体装置。

【0233】

(付記8)

付記1乃至7のいずれか一項に記載の電力用半導体装置であって、

前記ゲート充放電回路の出力は、抵抗素子を介して、前記第1ノードに接続されている

電力用半導体装置。

【0234】

(付記9)

付記1乃至8のいずれか一項に記載の電力用半導体装置であって、

前記ゲート充放電回路は、

前記ターンオン期間及び前記ON期間において前記第1ノードを充電する昇圧回路と、

前記第1ノードとグランド端子との間に介在する放電トランジスタと

を備え、

前記放電トランジスタは、前記ターンオン期間及び前記ON期間においてOFFし、前記ターンオフ期間及び前記OFF期間においてONする

電力用半導体装置。

【0235】

(付記10)

付記9に記載の電力用半導体装置であって、

前記放電トランジスタは、寄生バイポーラトランジスタを有し、

前記寄生バイポーラトランジスタのコレクタ、エミッタ及びベースは、それぞれ、前記電源端子、前記第1ノード、及び前記放電トランジスタのバックゲートに接続されている

電力用半導体装置。

【0236】

4.自動車の電子制御システムへの応用

図48は、本実施の形態に係る電力用半導体装置1が自動車の電子制御システムに適用される例を示している。電子制御システムは、バッテリー電源200、電子制御ユニット208、及び負荷20−A、20−Bを備えている。電子制御ユニット208には、外部のバッテリー電源200から電力が供給される。そして、電子制御ユニット208は、負荷20−A(例えばランプ)や負荷20−B(例えばソレノイド)に対する電力供給を制御する。

【0237】

電子制御ユニット208は、電力用半導体装置1−A、1−B、電源IC201、マイコン202、ツェナーダイオード205、及び容量206、207を備えている。電源端子とグランド端子との間には、安定化用の容量206と、ダンプサージに対して電圧をクランプするツェナーダイオード205が接続されている。電源IC201及び電力用半導体装置1−A、1−Bには、外部のバッテリー電源200から電源電圧VDDが供給される。電源IC201は、電源電圧VDDから安定化電圧を生成し、マイコン202に対してその安定化電圧を供給する。電源IC201の出力端子とグランド端子との間には、安定化用の容量207が接続されている。

【0238】

マイコン202は、電力用半導体装置1−A、1−Bのそれぞれに対してパワーON信号PWRを供給する。電力用半導体装置1−Aは、負荷20−Aに接続されており、マイコン202から入力されるパワーON信号PWRに応じて負荷20−Aへの電力供給をON/OFF制御する。同様に、電力用半導体装置1−Bは、負荷20−Bに接続されており、マイコン202から入力されるパワーON信号PWRに応じて負荷20−Bへの電力供給をON/OFF制御する。

【0239】

自動車の走行時には、オルタネータ(不図示)が発電を行い、バッテリー電源200を充電する。オルタネータとバッテリー電源200との間に接続不良が生じると、オルタネータの負荷に変動が生じるため、逆起電圧が発生する。この逆起電圧がダンプサージ電圧と呼ばれる。本実施の形態によれば、その場合であっても、電力用半導体装置1−A、1−Bの出力トランジスタ10の熱破壊が防止される。

【0240】

以上、本発明の実施の形態が添付の図面を参照することにより説明された。但し、本発明は、上述の実施の形態に限定されず、要旨を逸脱しない範囲で当業者により適宜変更され得る。

【符号の説明】

【0241】

1 電力用半導体装置

4 ショートスイッチ回路

10 出力トランジスタ

20 負荷

30 ゲート充放電回路

31 制御入力回路

32 昇圧回路

33 放電トランジスタ

40A ショートスイッチ、ショートトランジスタ

40B ショートスイッチ、ショートトランジスタ

41B ショートスイッチ、ショートトランジスタ

41C 第1ショートスイッチ、第1ショートトランジスタ

42C 第2ショートスイッチ、第2ショートトランジスタ

43C 第3ショートスイッチ、第3ショートトランジスタ

50、50A、50B、50C ショート制御回路

70、70A、70B、70C 遅延回路

80 過電圧保護回路

90 制御回路

100 タイマー回路

200 バッテリー電源

201 電源IC

202 マイコン

205 ツェナーダイオード

206 容量素子

207 容量素子

208 電子制御ユニット

CON 制御信号

N1 第1ノード

N2 第2ノード

NZ 出力ノード

PA ターンオン期間

PB ON期間

PC ターンオフ期間

PC1 放電期間

PC2 負電圧期間

PD OFF期間

PT タイマー期間

PX 制御期間

PWR パワーON信号

Q1 寄生バイポーラトランジスタ

RES 抵抗素子

TG グランド端子

TI 入力端子

TO 出力端子

TV 電源端子

【技術分野】

【0001】

本発明は、電力用半導体装置(power semiconductor device)及びその動作方法に関する。

【背景技術】

【0002】

負荷に対して電力を供給するための電力用半導体装置が知られている。例えば、インテリジェントパワーデバイス(IPD:Intelligent Power Device)と呼ばれる電力用半導体装置は、自動車の電子制御システムにおいて用いられ、マイコンからの命令に従ってヘッドライト等への電力供給を制御する。このような電力用半導体装置では、典型的には、ハイサイドスイッチが使用される(例えば、特許文献1、特許文献2参照)。

【0003】

図1は、特許文献1に記載されている電力用半導体装置の構成を示している。この電力用半導体装置は、電源端子TV、入力端子TI、出力端子TO、出力トランジスタ10、及びゲート充放電回路30を備えている。電源端子TVには、電源電圧VDDが供給される。入力端子TIには、パワーON信号PWRが入力される。そのパワーON信号PWRの活性化に応答して、電力用半導体装置は出力端子TOから電力を出力する。

【0004】

出力トランジスタ10は、電源端子TVと出力端子TOとの間に接続されている。より詳細には、出力トランジスタ10は、NチャネルMOSFETであり、そのゲート、ドレイン及びソースは、それぞれノードND、電源端子TV及び出力端子TOに接続されている。出力端子TOは負荷20の一端に接続され、負荷20の他端はグランド端子TGに接続される。このように、出力トランジスタ10は、ハイサイドスイッチとして機能するように接続される。

【0005】

ゲート充放電回路30は、ノードNDを充放電し、それにより出力トランジスタ10をON/OFF制御する。より詳細には、ゲート充放電回路30は、制御入力回路31、昇圧回路32、放電トランジスタ(放電スイッチ)33、及びダイオード34、35を備えている。制御入力回路31は、パワーON信号PWRに応じて、昇圧回路32及び放電トランジスタ33を制御する。昇圧回路32は、ノードNDを、電源電圧VDDよりも高い高電圧まで充電する。放電トランジスタ33は、NチャネルMOSFETであり、そのゲート、バックゲート、ソース及びドレインは、それぞれノードNA、ノードNB、ノードNC及びノードNDに接続されている。ダイオード34のアノード及びカソードは、それぞれノードNC及びグランド端子に接続されている。ダイオード35のアノード及びカソードは、それぞれノードNC及び出力端子TOに接続されている。

【0006】

パワーON信号PWRが活性化されると、制御入力回路31は、昇圧回路32を活性化し、且つ、ノードNAにLowレベル信号を供給して放電トランジスタ33をOFFする。昇圧回路32は、ノードNDを、電源電圧VDDよりも高い高電圧まで充電する。その結果、出力トランジスタ10がONし、負荷20に電力が供給される。

【0007】

パワーON信号PWRが非活性化されると、制御入力回路31は、昇圧回路32を非活性化し、且つ、ノードNAにHighレベル信号を供給する。これにより、昇圧回路32が動作を停止する一方で、放電トランジスタ33がONする。その結果、ノードNDが放電され、出力トランジスタ10がOFFする。尚、ノードNDの電圧が、グランド電圧GNDからダイオード34またはダイオード35の順方向降下電圧(VF)分だけ高いレベルになると、放電トランジスタ33を介した放電は行われなくなる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平6−97375号公報

【特許文献2】特開2002−290221号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

ここで、本願発明者は、次のような課題を発見した。それは、上述のような電力用半導体装置を単一の半導体基板上に形成したときに、外部から印加されるサージ電圧により、出力トランジスタ10が熱破壊する可能性があるということである。この課題について、以下に説明する。

【0010】

上述のような電力用半導体装置において、出力トランジスタ10(パワーMOSFET)のオン抵抗は十分に低いことが望ましい。そのためには、出力トランジスタ10のゲートにつながるノードNDに、十分高い駆動電圧を印加する必要がある。このようにノードNDには高電圧が印加されるため、一般的には、高圧MOSFETが放電トランジスタ33として使用される。図2は、出力トランジスタ10及び放電トランジスタ33の一例の断面構造を示している。放電トランジスタ33は、高圧MOSFET構造を有している。

【0011】

この放電トランジスタ33は、図2に示されるような縦型の寄生バイポーラトランジスタを有する。図3は、その寄生バイポーラトランジスタを含めた回路構成を示している。図3に示されるように、放電トランジスタ33のドレイン及びバックゲートは、それぞれノードND及びノードNBに接続されており、寄生バイポーラトランジスタQ1のコレクタ、エミッタ及びベースは、それぞれ電源端子TV、ノードND及びノードNBに接続されている。また、寄生容量(コレクタ−ベース間容量)C1が、電源端子TVとノードNBとの間に生成される。

【0012】

ここで、電力用半導体装置(出力トランジスタ10)がOFF状態の時に、電源電圧VDDの急峻な増加が発生した場合を考える。OFF状態において、ノードNB(放電トランジスタ33のバックゲート)はハイインピーダンスとなっている。従って、電源電圧VDDの急峻な増加が発生すると、寄生容量C1を通して、ノードNBの電圧(寄生バイポーラトランジスタQ1のベース電圧)が持ち上がる。その結果、寄生バイポーラトランジスタQ1がONする。この時、コレクタ−エミッタ間電圧VCEが耐圧BVCEOを超えていると、大きな降伏電流が流れる。ここで、図4は、寄生バイポーラトランジスタQ1の電流−電圧特性を示している。コレクタ−エミッタ間電圧VCEが耐圧BVCEOを超えると、大きな降伏電流が流れることが分かる。

【0013】

この降伏電流により、出力トランジスタ10のゲートにつながるノードNDの電圧が持ち上がるため、出力トランジスタ10がONしてしまう。但し、この時、出力トランジスタ10は、高オン抵抗でオンする(ハーフオン)。この場合、出力トランジスタ10に過大な電力が印加されるため、熱破壊が発生する可能性がある。

【0014】

例えば、自動車に搭載される電力用半導体装置の電源端子TVは、バッテリーに接続される。この場合の電源電圧VDDの急峻な増加の一例として、図5に示されるような「ダンプサージ」が考えられる。ダンプサージとは、オルタネータの発電中にバッテリーが外れたときに、電源端子TVに発生するサージのことである。ダンプサージが電源端子TVに印加されると、上述の理由により、寄生バイポーラトランジスタQ1が動作し、出力トランジスタ10の熱破壊が発生する可能性がある。

【0015】

以上に説明されたように、電力用半導体装置がOFF状態の時に、電源電圧の急峻な増加が発生した場合、出力トランジスタがハーフオンして熱破壊される可能性があった。電力用半導体装置がOFF状態の時に、電源電圧の急峻な増加が発生した場合であっても、出力トランジスタがONすることを防止することができる技術が望まれる。

【課題を解決するための手段】

【0016】

本発明の1つの観点において、電力用半導体装置が提供される。その電力用半導体装置は、電源端子と出力端子との間に接続された出力トランジスタと、出力トランジスタのゲートに接続された第1ノードを充放電し、出力トランジスタをON/OFF制御するゲート充放電回路と、第1ノードと出力端子との間に接続されたショートスイッチ回路と、ショートスイッチ回路を制御するショート制御回路と、を備える。第1ノードが充電された後、出力トランジスタが安定的にONしている期間がON期間である。第1ノードが放電された後、出力トランジスタが安定的にOFFしている期間がOFF期間である。OFF期間からON期間への遷移期間がターンオン期間である。ON期間からOFF期間への遷移期間がターンオフ期間である。ターンオン期間、ON期間及びターンオフ期間において、ショート制御回路は、ショートスイッチ回路を介した第1ノードと出力端子との間の電気的接続を切断する。OFF期間において、ショート制御回路は、ショートスイッチ回路を介して第1ノードと出力端子との間を電気的に接続する。

【発明の効果】

【0017】

本発明によれば、電力用半導体装置がOFF状態の時に、電源電圧の急峻な増加が発生した場合であっても、出力トランジスタがONすることを防止することが可能となる。更に、本発明に係る機構は、出力トランジスタのターンオン/ターンオフに関連する特性に影響を与えない。

【図面の簡単な説明】

【0018】

【図1】図1は、関連技術に係る電力用半導体装置の構成を示す回路図である。

【図2】図2は、出力トランジスタ及び放電トランジスタの典型的な断面構造を示す概略図である。

【図3】図3は、寄生バイポーラトランジスタを含む電力用半導体装置の構成を示す回路図である。

【図4】図4は、寄生バイポーラトランジスタの電流−電圧特性を示すグラフ図である。

【図5】図5は、自動車に搭載される電力用半導体装置の電源端子に印加されるダンプサージを示す概念図である。

【図6】図6は、本発明の実施の形態に係る電力用半導体装置の構成を概略的に示すブロック図である。

【図7】図7は、本発明の実施の形態に係る電力用半導体装置の動作を示すタイミングチャートである。

【図8】図8は、ダンプサージ印加時の電力用半導体装置の動作を説明するための回路図である。

【図9】図9は、本発明の第1の実施の形態に係る電力用半導体装置の構成を概略的に示すブロック図である。

【図10】図10は、本発明の第1の実施の形態に係るショート制御回路の構成を概略的に示す回路図である。

【図11】図11は、本発明の第1の実施の形態に係るショート制御回路の動作を示すタイミングチャートである。

【図12】図12は、本発明の第1の実施の形態に係るショート制御回路の構成の第1の例を示す回路図である。

【図13】図13は、本発明の第1の実施の形態に係るショート制御回路の構成の第2の例を示す回路図である。

【図14】図14は、本発明の第1の実施の形態に係るショート制御回路の構成の第3の例を示す回路図である。

【図15】図15は、図14に示されたショート制御回路の動作を示すタイミングチャートである。

【図16A】図16Aは、図14に示されたショート制御回路中の遅延回路の構成例を示す回路図である。

【図16B】図16Bは、図14に示されたショート制御回路中の遅延回路の他の構成例を示す回路図である。

【図17】図17は、ターンオフ期間が放電期間と負電圧期間を含む場合を説明するための概念図である。

【図18】図18は、本発明の第1の実施の形態に係るショート制御回路の構成の第4の例を示す回路図である。

【図19】図19は、図18に示されたショート制御回路の動作を示すタイミングチャートである。

【図20】図20は、本発明の第1の実施の形態に係るショート制御回路の構成の第5の例を示す回路図である。

【図21】図21は、本発明の第2の実施の形態に係るショート制御回路の構成を概略的に示す回路図である。

【図22】図22は、本発明の第2の実施の形態に係るショート制御回路の動作を示すタイミングチャートである。

【図23】図23は、本発明の第2の実施の形態に係るショート制御回路の構成の第1の例を示す回路図である。

【図24】図24は、ターンオフ期間が放電期間と負電圧期間を含む場合を説明するための概念図である。

【図25】図25は、本発明の第2の実施の形態に係るショート制御回路の構成の第2の例を示す回路図である。

【図26】図26は、図25に示されたショート制御回路の動作を示すタイミングチャートである。

【図27】図27は、本発明の第2の実施の形態に係るショート制御回路の構成の第3の例を示す回路図である。

【図28】図28は、図27に示されたショート制御回路の動作を示すタイミングチャートである。

【図29A】図29Aは、図27に示されたショート制御回路中の遅延回路の構成例を示す回路図である。

【図29B】図29Bは、図27に示されたショート制御回路中の遅延回路の他の構成例を示す回路図である。

【図30】図30は、本発明の第2の実施の形態に係るショート制御回路の構成の第4の例を示す回路図である。

【図31】図31は、本発明の第2の実施の形態に係るショート制御回路の構成の第5の例を示す回路図である。

【図32】図32は、本発明の実施の形態におけるタイマー回路の構成例を示す回路図である。

【図33】図33は、図32に示されたタイマー回路の動作を示すタイミングチャートである。

【図34】図34は、本発明の第3の実施の形態に係る電力用半導体装置の構成を概略的に示すブロック図である。

【図35】図35は、本発明の第3の実施の形態に係る電力用半導体装置の動作を示すタイミングチャートである。

【図36】図36は、ダンプサージ印加時の電力用半導体装置の動作を説明するための回路図である。

【図37】図37は、本発明の第3の実施の形態に係るショート制御回路の構成を概略的に示す回路図である。

【図38】図38は、本発明の第3の実施の形態に係るショート制御回路の動作を示すタイミングチャートである。

【図39】図39は、本発明の第3の実施の形態に係るショート制御回路の構成の第1の例を示す回路図である。

【図40】図40は、ターンオフ期間が放電期間と負電圧期間を含む場合を説明するための概念図である。

【図41】図41は、本発明の第3の実施の形態に係るショート制御回路の構成の第2の例を示す回路図である。

【図42】図42は、図41に示されたショート制御回路の動作を示すタイミングチャートである。

【図43】図43は、本発明の第3の実施の形態に係るショート制御回路の構成の第3の例を示す回路図である。

【図44】図44は、図43に示されたショート制御回路の動作を示すタイミングチャートである。

【図45A】図45Aは、図43に示されたショート制御回路中の遅延回路の構成例を示す回路図である。

【図45B】図45Bは、図43に示されたショート制御回路中の遅延回路の他の構成例を示す回路図である。

【図46】図46は、本発明の第3の実施の形態に係るショート制御回路の構成の第4の例を示す回路図である。

【図47】図47は、本発明の第3の実施の形態に係るショート制御回路の構成の第5の例を示す回路図である。

【図48】図48は、本発明の実施の形態に係る電力用半導体装置が自動車の電子制御システムに適用される例を示すブロック図である。

【発明を実施するための形態】

【0019】

添付図面を参照して、本発明の実施の形態に係る電力用半導体装置を説明する。

【0020】

<基本構成>

図6は、本発明の実施の形態に係る電力用半導体装置1の構成を概略的に示すブロック図である。電力用半導体装置1は、電源端子TV、入力端子TI、及び出力端子TOを備えている。出力端子TOは負荷20の一端に接続され、負荷20の他端はグランド端子TGに接続される。電源端子TVには、電源電圧VDDが供給される。入力端子TIには、パワーON信号PWRが入力される。そのパワーON信号PWRの活性化に応答して、電力用半導体装置1はONし、出力端子TOを通して負荷20に電力を供給する。

【0021】

より詳細には、電力用半導体装置1は、出力トランジスタ10及びゲート充放電回路30を備えている。出力トランジスタ10は、電源端子TVと出力端子TOとの間に接続されている。具体的には、出力トランジスタ10は、NチャネルMOSFETであり、そのゲート、ドレイン及びソースは、それぞれ第1ノードN1、電源端子TV及び出力端子TO(出力ノードNZ)に接続されている。尚、出力ノードNZは、出力端子TOと同電位であり、出力端子TOと等価なものとして扱われる。

【0022】

出力トランジスタ10のゲートにつながる第1ノードN1は、抵抗素子RESを介して、ノードNDに接続されている。ノードNDは、ゲート充放電回路30の出力端子に接続されている。つまり、ゲート充放電回路30の出力は、抵抗素子RESを介して、第1ノードN1に接続されている。

【0023】

ゲート充放電回路30は、ノードNDすなわち第1ノードN1を充放電し、それにより出力トランジスタ10をON/OFF制御する。例えば、ゲート充放電回路30は、既出の図1で示されたものと同じ構成を有する。パワーON信号PWRが活性化されると、ゲート充放電回路30は、ノードND(第1ノードN1)を、電源電圧VDDよりも高い高電圧まで充電する。その結果、出力トランジスタ10がONし、負荷20に電力が供給される。一方、パワーON信号PWRが非活性化されると、ゲート充放電回路30は、ノードND(第1ノードN1)を放電する。その結果、出力トランジスタ10がOFFする。

【0024】

本実施の形態に係る電力用半導体装置1は、更に、ショートスイッチ回路4及びショート制御回路50を備えている。ショートスイッチ回路4は、出力トランジスタ10のゲート−ソース間を必要に応じてショートさせるために設けられている。すなわち、ショートスイッチ回路4は、第1ノードN1と出力ノードNZとの間に接続されている。ショートスイッチ回路4を制御することにより、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をON/OFFすることができる。そのショートスイッチ回路4を制御するのが、ショート制御回路50である。

【0025】

<基本動作>

図7は、本実施の形態に係る電力用半導体装置1の動作を示すタイミングチャートである。以下、図6及び図7を参照して、電力用半導体装置1の基本的な動作を説明する。その動作を説明するにあたり、4つの期間(フェーズ):ターンオン期間PA、ON期間PB、ターンオフ期間PC、及びOFF期間PD、を考える。

【0026】

ターンオン期間PA及びON期間PBは、パワーON信号PWRが活性化(PWR=Highレベル)されている期間である。パワーON信号PWRが活性化されると、第1ノードN1は充電され、出力トランジスタ10はONし、出力ノードNZも充電される。ON期間PBは、第1ノードN1及び出力ノードNZの電圧が安定し、出力トランジスタ10が安定的にONしている期間である。一方、ターンオン期間PAは、パワーON信号PWRの活性化タイミングからON期間PBまでの期間である。言い換えれば、ターンオン期間PAは、OFF期間PDからON期間PBへの遷移期間である。

【0027】

ターンオフ期間PC及びOFF期間PDは、パワーON信号PWRが非活性化(PWR=Lowレベル)されている期間である。パワーON信号PWRが非活性化されると、第1ノードN1は放電され、出力トランジスタ10はOFFし、出力ノードNZも放電される。OFF期間PDは、第1ノードN1及び出力ノードNZの電圧が安定し、出力トランジスタ10が安定的にOFFしている期間である。一方、ターンオフ期間PCは、パワーON信号PWRの非活性化タイミングからOFF期間PDまでの期間である。言い換えれば、ターンオフ期間PCは、ON期間PBからOFF期間PDへの遷移期間である。

【0028】

(ターンオン期間PA:時刻t1〜t2)

時刻t1において、パワーON信号PWRが活性化され、LowレベルからHighレベルに変わる。それに応答して、ゲート充放電回路30は、ノードND及び第1ノードN1を充電し始める。このターンオン期間PAにおいて、ショート制御回路50は、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をOFF(切断)する。出力トランジスタ10はONし、出力ノードNZの電圧も徐々に上昇する。尚、ターンオン期間PAにおいて、第1ノードN1は、電源電圧VDDよりも高い高電圧まで充電される。

【0029】

(ON期間PB:時刻t2〜t3)

ON期間PBにおいて、ショート制御回路50は、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をOFFのまま維持する。第1ノードN1の電圧は、電源電圧VDDよりも高い高電圧で安定する。出力ノードNZの電圧は、電源電圧VDD近傍で安定する。出力トランジスタ10は、安定的にONしている。

【0030】

(ターンオフ期間PC:時刻t3〜t4)

時刻t3において、パワーON信号PWRが非活性化され、HighレベルからLowレベルに変わる。それに応答して、ゲート充放電回路30は、ノードND及び第1ノードN1を放電し始める。このターンオフ期間PCにおいても、ショート制御回路50は、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をOFFのまま維持する。従って、ショートスイッチ回路4を通した放電は発生しない。すなわち、第1ノードN1の放電は、従来通りゲート充放電回路30によってのみ行われる。第1ノードN1の電圧が低下すると、出力ノードNZの電圧も徐々に低下し、最終的に0Vになる。出力トランジスタ10はOFFする。

【0031】

(OFF期間PD:時刻t4〜)

OFF期間PDの少なくとも一部において、ショート制御回路50は、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をON(有効化)する。従って、第1ノードN1と出力ノードNZとの間、すなわち、出力トランジスタ10のゲート−ソース間がショートする。出力トランジスタ10は、安定的にOFFしている。

【0032】

このように、ショート制御回路50は、OFF期間PDにおいてのみ、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をON(有効化)する。その他の期間PA〜PCにおいて、ショート制御回路50は、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をOFF(切断)する。このショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続がOFFである期間は、パワーON信号PWRが活性化されている期間と一致しない。すなわち、ショート制御回路50は、単純にパワーON信号PWRに同期してショートスイッチ回路4をON/OFF制御しているわけではない。ショート制御回路50は、ターンオン期間PA及びON期間PBだけでなく、ターンオフ期間PCにおいても、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をOFFのまま維持する。その結果、ターンオフ期間PCにおいて、ショートスイッチ回路4を通した第1ノードN1の放電が防止される。すなわち、本実施の形態に係るショートスイッチ回路4及びショート制御回路50は、出力トランジスタ10のターンオフに関連する特性(ターンオフに要する時間等)に影響を与えない。

【0033】

<ダンプサージ印加時の動作>

次に、OFF期間PDにおいて、ダンプサージ等の印加によって、電源電圧VDDの急峻な増加が発生した場合を考える。図7に示される例では、OFF期間PDの最中の時刻t5〜t6において、ダンプサージが電源端子TVに印加される。

【0034】

図8は、ゲート充放電回路30が既出の図1、図3で示されたものと同じ構成を有している場合を示している。上述の通り、ゲート充放電回路30の放電トランジスタ33は、寄生バイポーラトランジスタQ1を有している。寄生バイポーラトランジスタQ1のコレクタ、エミッタ及びベースは、それぞれ電源端子TV、ノードND及びノードNBに接続されている。また、寄生容量(コレクタ−ベース間容量)C1が、電源端子TVとノードNBとの間に接続されている。

【0035】

OFF期間PDの最中に、電源電圧VDDの急峻な増加が発生した場合、上述の通り、寄生バイポーラトランジスタQ1がONする可能性がある。寄生バイポーラトランジスタQ1がONすると、ノードNDの電圧が持ち上がる。しかしながら、OFF期間PDにおいて、ショートスイッチ回路4を介した電気的接続はONしており、第1ノードN1と出力ノードNZとの間、すなわち、出力トランジスタ10のゲート−ソース間はショートしている。ゲート−ソース間電圧が閾値電圧を超えないため、出力トランジスタ10はONすることなく、OFF状態を維持する。

【0036】

尚、ノードNDと第1ノードN1との間には抵抗素子RESが介在している。ノードNDの電圧が持ち上がった場合、ノードNDから、抵抗素子RES、第1ノードN1及びショートスイッチ回路4を通して、出力ノードNZへ電流が流れる。この時、抵抗素子RESにおいてIRドロップが発生するため、第1ノードN1の電圧がLowレベルに維持される。つまり、抵抗素子RESを利用することによって、第1ノードN1の電圧をLowレベルに維持しやすくなる。

【0037】

<効果>

本実施の形態によれば、OFF期間PDにおいて、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続がONする。これにより、第1ノードN1と出力ノードNZとの間、すなわち、出力トランジスタ10のゲート−ソース間がショートする。従って、電源電圧VDDの急峻な増加が発生した場合であっても、出力トランジスタ10がONすることが防止される。すなわち、出力トランジスタ10の熱破壊が防止される。

【0038】

また、本実施の形態によれば、OFF期間PD以外において、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続はOFFのまま維持される。従って、OFF期間PD以外において、ショートスイッチ回路4及びショート制御回路50は、第1ノードN1に影響を及ぼさない。つまり、ショートスイッチ回路4及びショート制御回路50は、出力トランジスタ10のターンオン/ターンオフに関連する特性(ターンオン/ターンオフに要する時間等)に影響を与えない。すなわち、本実施の形態によれば、ターンオン/ターンオフに関連する特性に影響を及ぼすことなく、出力トランジスタ10の熱破壊を防止することが可能である。

【0039】

以下、本発明の様々な実施の形態を説明する。

【0040】

1.第1の実施の形態

図9は、第1の実施の形態に係る電力用半導体装置1の構成を概略的に示すブロック図である。第1の実施の形態において、ショートスイッチ回路4は、第1ノードN1と出力ノードNZとの間に接続されたショートスイッチ40Aを含んでいる。また、第1の実施の形態におけるショート制御回路50は、ショート制御回路50Aと参照される。ショート制御回路50Aは、ショートスイッチ40AをON/OFF制御することによって、ショートスイッチ回路4を介した第1ノードN1と出力ノードNZとの間の電気的接続をON/OFFすることができる。

【0041】

図10は、第1の実施の形態に係るショートスイッチ40A及びショート制御回路50Aの構成を概略的に示している。ショートスイッチ40Aとして、例えば、NチャネルMOSFET(以下、「ショートトランジスタ40A」と参照される)が用いられる。ショートトランジスタ40Aのソース、ドレイン及びゲートは、それぞれ出力ノードNZ、第1ノードN1及び第2ノードN2に接続されている。この第2ノードN2の電圧を制御することによって、ショートトランジスタ40AをON/OFF制御することが可能である。

【0042】

ショート制御回路50Aは、第2ノードN2に接続されており、第2ノードN2の電圧を制御する。詳細には、ショート制御回路50Aは、第2ノードN2と出力ノードNZとの間に接続された第1スイッチ51Aと、第2ノードN2と電源端子TVとの間に接続された電源接続回路60Aとを備えている。第1スイッチ51Aは、第2ノードN2と出力ノードNZとの間の電気的接続を制御する。電源接続回路60Aは、制御信号CONに応じて、第2ノードN2と電源端子TVとの間の電気的接続を制御する。

【0043】

ターンオン期間PA、ON期間PB及びターンオフ期間PCにおいて、ショート制御回路50Aは、第1スイッチ51AをONする。これにより、第2ノードN2と出力ノードNZとの間、すなわち、ショートトランジスタ40Aのゲート−ソース間がショートする。その結果、ショートトランジスタ40AがOFFに維持される。一方、OFF期間PDにおいて、ショート制御回路50Aは、第1スイッチ51AをOFFし、第2ノードN2と出力ノードNZとの間の電気的接続を切断する。また、電源接続回路60Aは、第2ノードN2と電源端子TVとを電気的に接続する。その結果、第2ノードN2に電源電圧VDDが印加され、ショートトランジスタ40AがONする。このようにして、上述のショートトランジスタ40AのON/OFF制御が実現される。

【0044】

第1スイッチ51Aとして、例えば、図10に示されるようなNチャネルMOSFETが用いられる。そのNチャネルMOSFET51Aのゲート、ソース及びドレインは、それぞれ第1ノードN1、出力ノードNZ及び第2ノードN2に接続されている。このような構成の場合のショート制御回路50Aの動作を、図11を参照して説明する。尚、既出の図7と重複する説明は、適宜省略される。

【0045】

(ターンオン期間PA:時刻t1〜t2)

時刻t1において、パワーON信号PWRが活性化され、LowレベルからHighレベルに変わる。それに応答して、制御信号CONがHighレベルからLowレベルに変わる。制御信号CONがLowレベルの場合、電源接続回路60Aは、第2ノードN2と電源端子TVとの間の電気的接続を切断する。その一方で、上述の通り、第1ノードN1及び出力ノードNZの電圧は徐々に上昇する。昇圧回路32によって昇圧される第1ノードN1の電圧は、出力ノードNZの電圧より高く、それらノード間には電圧差(N1−NZ)が発生する。すなわち、NチャネルMOSFET51Aのゲート−ソース間にある程度の電圧が印加され、NチャネルMOSFET51AがONする。その結果、第2ノードN2と出力ノードNZとは電気的に接続され、ショートトランジスタ40AがOFFする。

【0046】

(ON期間PB:時刻t2〜t3)

NチャネルMOSFET51AはONのままであり、ショートトランジスタ40AはOFFのままである。

【0047】

(ターンオフ期間PC:時刻t3〜t4)

時刻t3において、パワーON信号PWRが非活性化され、HighレベルからLowレベルに変わる。それに応答して、制御信号CONがLowレベルからHighレベルに変わる。制御信号CONがHighレベルの場合、電源接続回路60Aは、第2ノードN2と電源端子TVとを電気的に接続する。但し、ターンオフ期間PCにおいても、第1ノードN1と出力ノードNZとの間にはある程度の電圧差(N1−NZ)が存在し、NチャネルMOSFET51AはON状態に維持される。つまり、第2ノードN2と出力ノードNZとは電気的に接続されたままである。NチャネルMOSFET51Aの電流能力は十分に大きく設計されるため、ショートトランジスタ40Aのゲート−ソース間電圧(N2−NZ)は十分に低く維持される。従って、ショートトランジスタ40AはOFF状態に維持される。

【0048】

(OFF期間PD:時刻t4〜)

第1ノードN1及び出力ノードNZの放電が進み、第1ノードN1と出力ノードNZとの間の電圧差(N1−NZ)がNチャネルMOSFET51Aの閾値電圧を下回ると、NチャネルMOSFET51AはOFFする。すなわち、第2ノードN2と出力ノードNZとの間の電気的接続が切断される。その結果、ノードN2に電源電圧VDDが印加され、ショートトランジスタ40AがONする。

【0049】

このように、ゲートが第1ノードN1に接続されたNチャネルMOSFET51Aを用いることによって、上述のショートトランジスタ40AのON/OFF制御が実現される。

【0050】

以下、第1の実施の形態に係るショート制御回路50Aの構成の様々な例を説明する。尚、上記と重複する説明は適宜省略される。

【0051】

1−1.第1の例

図12は、第1の例を示す回路図である。電源接続回路60Aは、PチャネルMOSFET61A、63A、NチャネルMOSFET62A、64Aを備えている。

【0052】

PチャネルMOSFET61A及びNチャネルMOSFET62Aは、第1のインバータ回路を構成している。具体的には、PチャネルMOSFET61Aのゲート、ソース及びドレインは、それぞれ、ノードNA、電源端子TV及び第3ノードN3に接続されている。NチャネルMOSFET62Aのゲート、ソース及びドレインは、それぞれ出力ノードNZ、出力ノードNZ及び第3ノードN3に接続されている。尚、NチャネルMOSFET62Aは、デプレッション型である。

【0053】

PチャネルMOSFET63A及びNチャネルMOSFET64Aは、第2のインバータ回路を構成している。具体的には、PチャネルMOSFET63Aのゲート、ソース及びドレインは、それぞれ、第3ノードN3、電源端子TV及び第2ノードN2に接続されている。NチャネルMOSFET64Aのゲート、ソース及びドレインは、それぞれ第3ノードN3、出力ノードNZ及び第2ノードN2に接続されている。

【0054】

このような第1及び第2のインバータ回路が、第2ノードN2と電源端子TVとの間の電気的接続を制御する。このとき、第1のインバータ回路に入力されるノードNAの信号(ゲート充放電回路の放電トランジスタ33のゲート制御信号)が、図10及び図11で示された制御信号CONに相当する。

【0055】

ターンオン期間PA及びON期間PBにおいて、ノードNAの信号(制御信号CON)はLowレベルである。この場合、PチャネルMOSFET61AがONし、PチャネルMOSFET63AはOFFする。従って、第2ノードN2と電源端子TVとの間の電気的接続が切断される。第2ノードN2は、少なくともNチャネルMOSFET51A(第1スイッチ)を介して、出力ノードNZと電気的に接続される。

【0056】

ターンオフ期間PC及びOFF期間PDにおいて、ノードNAの信号(制御信号CON)はHighレベルである。この場合、PチャネルMOSFET61A及びNチャネルMOSFET64AがOFFし、PチャネルMOSFET63AがONする。従って、第2ノードN2と電源端子TVとが電気的に接続される。

【0057】

但し、ターンオフ期間PCでは、上述の通り、NチャネルMOSFET51AもONしている。ターンオフ期間PCにおいてもショートトランジスタ40AをOFFに維持しておくために、NチャネルMOSFET51Aの電流能力は、PチャネルMOSFET63Aの電流能力よりも十分に大きく設計される。

【0058】

OFF期間PDでは、NチャネルMOSFET51AもOFFするため、第2ノードN2と出力ノードNZとの間の電気的接続が切断される。従って、ショート制御回路50Aを通って電源端子TVから出力端子TOに向かって電流は流れない。すなわち、オフ時消費電流は発生しない。

【0059】

尚、ショート制御回路50Aに含まれるNチャネルMOSFETのそれぞれのバックゲートは、出力ノードNZに直接接続されている。そのため、OFF期間PDにおいて、それらバックゲートがハイインピーダンスになることはない。従って、OFF期間PDにおいて、ダンプサージの印加によって、それらNチャネルMOSFETの寄生バイポーラトランジスタが動作することはない。

【0060】

1−2.第2の例

図13は、第2の例を示す回路図である。第2の例では、図12で示された回路構成に対して、デプレッション型のNチャネルMOSFET65Aが更に追加されている。このデプレッション型のNチャネルMOSFET65Aは、PチャネルMOSFET63Aと第2ノードN2との間に介在しており、定電流源として機能する。

【0061】

上述の第1の例で示されたように、ターンオフ期間PC中には、NチャネルMOSFET51AとPチャネルMOSFET63Aが同時にオンする期間がある。しかしながら、ターンオフ期間PCにおいてもショートトランジスタ40AをOFFに維持しておくことが望ましい。その目的のため、第1の例では、NチャネルMOSFET51Aの電流能力は、PチャネルMOSFET63Aの電流能力よりも十分に大きく設計される。つまり、電流能力の設計に十分な注意を払う必要がある。第2の例では、定電流源として機能するNチャネルMOSFET65Aの定電流値を小さくする(インピーダンスを高くする)ことにより、当該目的を容易に達成することができる。つまり、第1の例と比較して、設計がより容易になる。

【0062】

1−3.第3の例

図14は、第3の例を示す回路図である。第3の例では、図12で示された回路構成に対して、遅延回路70A及び補助スイッチ66Aが更に追加されている。NチャネルMOSFET51Aのドレインは、第2ノードN2の代わりにノードN2’に接続されている。そのノードN2’が、遅延回路70Aを介して、第2ノードN2に接続されている。

【0063】

図14及び図15を参照して、OFF期間PD中に電源端子TVにダンプサージが印加された場合を考える。出力トランジスタ10は大面積を有するように作成されることが多く、その場合、ゲート−ドレイン間の寄生容量Cgd(図14参照)を無視することができない。時刻t5においてダンプサージが印加されると、その寄生容量Cgdによって、第1ノードN1の電圧が持ち上げられる。その後、第1ノードN1は、寄生容量Cgdと抵抗素子RESと放電トランジスタ33のインピーダンスに依って決まる時定数で放電される。

【0064】

OFF期間PDの最中に第1ノードN1の電圧が上昇すると、NチャネルMOSFET51A(第1スイッチ)がONしてしまう。図15の例では、時刻t5〜tsの短い期間、NチャネルMOSFET51AがONし、ノードN2’が放電されてしまう。もし、遅延回路70Aがなければ、ショートトランジスタ40Aのゲートにつながる第2ノードN2も放電されてしまい、ショートトランジスタ40AがOFFしてしまう。このことは、出力トランジスタ10のゲート−ソース間のショートの解除を意味し、好ましくない。

【0065】

一方、本例によれば、ノードN2’と第2ノードN2との間に遅延回路70Aが設けられている。従って、たとえノードN2’が放電されても、第2ノードN2の電圧レベルは、ある程度の時間Highレベルに維持される。つまり、時刻t5〜tsの期間においても、ショートトランジスタ40AはON状態のまま維持される。このように、OFF期間PDの最中に出力トランジスタ10のゲート−ソース間のショートが解除されることが防止される。

【0066】

図16A及び図16Bは、遅延回路70Aの構成例を示している。図16Aの例では、抵抗素子71Aと容量素子72Aとにより、遅延回路70Aが構成されている。図16Bの例では、定電流源として機能するデプレッション型のNチャネルMOSFET73Aと、ショートトランジスタ40Aのゲート−ソース間の寄生容量C40Aとにより、遅延回路70Aが構成されている。OFF期間PDにおいて、遅延回路70Aの容量素子(72AあるいはC40A)は、電源電圧VDDに充電されている。上記理由によりノードN2’が放電された場合であっても、遅延回路70Aの容量素子が放電されるまでは、第2ノードN2の電圧レベルをHighレベルに保つことができる。尚、遅延回路70Aの放電時定数は、第1ノードN1の放電時定数よりも大きく設計される。

【0067】

尚、ターンオン期間PAの開始時(時刻t1:図11参照)、第2ノードN2を速やかに放電し、ショートトランジスタ40AをOFFする必要がある。しかしながら、本例では、ノードN2’と第2ノードN2との間に遅延回路70Aが介在しており、NチャネルMOSFET51A、64Aを通した放電は遅延する。このような遅延回路70Aの影響を無くすために、補助スイッチ66Aが追加されている。補助スイッチ66Aは、第2ノードN2と出力ノードNZとの間に接続されており、ターンオン期間PAにおいてONする。その結果、ターンオン期間PAの開始時に、補助スイッチ66Aを通して第2ノードN2が速やかに放電される。つまり、ターンオン期間PAへの遅延回路70Aの影響が排除される。

【0068】

例えば、補助スイッチ66AはNチャネルMOSFETであり、そのゲート、ソース及びドレインは、それぞれ第3ノードN3、出力ノードNZ及び第2ノードN2に接続されている。ターンオン期間PAにおいて、第3ノードN3には電源電圧VDDが印加される。第3ノードN3と出力ノードNZとの間の電圧差(N3−NZ)が閾値電圧を下回るまで、NチャネルMOSFET66AはONする。ターンオン期間PA以外において、NチャネルMOSFET66AはOFFする。これにより、上記目的が達成される。

【0069】

1−4.第4の例

出力端子TOに接続される負荷20が誘導性負荷の場合、ターンオフの際に、逆起電圧(負電圧)が出力端子TOに印加される可能性がある。また、負荷20を接続する配線のインダクタンス成分によっても、同様のことが発生し得る。このような場合、図17に示されるように、ターンオフ期間PCは、第1ノードN1及び出力ノードNZが放電される「放電期間PC1」だけでなく、続いて出力端子TO(出力ノードNZ)に負電圧が印加される「負電圧期間PC2」をも含む。

【0070】

既出の例では、ターンオフ期間PCは、放電期間PC1だけを含んでいた。その放電期間PC1において、第1スイッチ51AがONし、第2ノードN2と出力ノードNZとの間が電気的に接続される。その結果、ショートトランジスタ40Aが、放電期間PC1においてもOFF状態に維持される。しかしながら、第1スイッチ51A(NチャネルMOSFET51A)は、負電圧期間PC2においてもONするとは限らない。従って、第4の例では、第2ノードN2と出力ノードNZとの間に接続され、負電圧期間PC2においてONする第2スイッチ52Aが追加される。

【0071】