電圧制御形スイッチングデバイスのゲート駆動装置

【課題】電圧制御形スイッチングデバイスに過電流異常時に、迅速に定電流パルス出力、定電圧パルス出力を停止できる電圧制御形スイッチングデバイスのゲート駆動装置を提案する。

【解決手段】定電流パルス出力または定電圧パルス出力を発生する電流出力トランジスタまたは電圧出力トランジスタを含む定電流駆動回路または定電圧駆動回路を用い、定電流パルス出力または定電圧パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置である。閾値電圧を持った半導体スイッチ素子を有し、スイッチングデバイスの出力電流に応じて大きさが変化する検出電圧が、半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路を備え、このスイッチ出力に基づいて、電流出力トランジスタまたは電圧出力トランジスタの制御端子に、オフ制御電圧を供給する。

【解決手段】定電流パルス出力または定電圧パルス出力を発生する電流出力トランジスタまたは電圧出力トランジスタを含む定電流駆動回路または定電圧駆動回路を用い、定電流パルス出力または定電圧パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置である。閾値電圧を持った半導体スイッチ素子を有し、スイッチングデバイスの出力電流に応じて大きさが変化する検出電圧が、半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路を備え、このスイッチ出力に基づいて、電流出力トランジスタまたは電圧出力トランジスタの制御端子に、オフ制御電圧を供給する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、パワー用IGBTまたはMOSFETなどの電圧制御形スイッチングデバイスのゲート駆動装置に関するものである。

【背景技術】

【0002】

この種の電圧制御形スイッチングデバイスのゲート駆動装置して、定電圧駆動回路を用い、この定電圧駆動回路から電圧制御形スイッチングデバイスのゲートへ定電圧パルス出力を供給し、ゲートを駆動するものが知られていたが、最近では、特許文献1の図8に示すように、定電流駆動回路を用い、この定電流駆動回路から電圧制御形スイッチングデバイスのゲートへ定電流パルス出力を供給し、ゲートを駆動するものも使用されている。特許文献1の段落0025には、抵抗R12、R13、スイッチ素子Q12、Q13、オペアンプQ1、Q2により、定電流回路を構成することが説明されている。

【0003】

【特許文献1】特開2002−95151号公報、とくに図8とその説明

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかし、従来の定電流駆動回路からの定電流パルス出力により電圧制御形スイッチングデバイスのゲートを駆動するものにおいて、定電流パルス出力をオフさせるように制御しても、電圧制御形スイッチングデバイスのストレージ特性や、定電流駆動回路を制御する回路の応答性能などにより、定電流パルス出力が瞬時にオフとならずに、電圧制御形スイッチングデバイスのゲートに電流が流れ続ける可能性がある。また、従来の定電圧駆動回路からの定電圧パルス出力により電圧制御形スイッチングデバイスのゲートを駆動するものにおいて、定電圧パルス出力をオフさせるように制御しても、同様に、定電圧パルス出力が瞬時にオフとならずに、電圧制御形スイッチングデバイスのゲートに電流が流れ続ける可能性がある。

【0005】

このため、電圧制御形スイッチングデバイスの過電流保護、およびそれを用いた応用回路におけるアーム短絡保護の動作時に、電圧制御形スイッチングデバイスのゲートへの電流、電圧の供給が続き、高速に保護回路を動作させるのが困難であった。特に、過電流などの異常事態は、いつ、どのタイミングで発生するか予測できず、また、負荷電流の増大による過電流だけではなく、負荷の短絡や、アーム短絡などで短時間に急激に電圧制御形スイッチングデバイスの出力電流が増大する恐れのある応用回路では、保護回路の応答速度が低いと、電圧制御形スイッチングデバイスの破壊に至る恐れもある。

【0006】

この発明は、定電流パルス出力または定電圧パルス出力をオフさせる速度を改善し、異常事態にあって、迅速に保護動作を行なうことのできる電圧制御形スイッチングデバイスのゲート駆動装置を提案するものである。

【課題を解決するための手段】

【0007】

この発明の第1の観点による電圧制御形スイッチングデバイスのゲート駆動装置は、定電流パルス出力を発生する電流出力トランジスタを含む定電流駆動回路を用い、前記定電流パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路と、前記スイッチ出力に基づいて、前記電流出力トランジスタをオフにするオフ制御電圧を発生するオフ制御回路を備え、前記オフ制御回路が、電流出力トランジスタの制御端子に、前記オフ制御電圧を供給するように構成したことを特徴とする。

【0008】

また、この発明の第2の観点による電圧制御形スイッチングデバイスのゲート駆動装置は、定電流パルス出力を発生する電流出力トランジスタを含む定電流駆動回路を用い、前記定電流パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときに、スイッチ出力を発生するスイッチ回路を備え、前記スイッチ回路は、前記電流出力トランジスタの制御端子に接続され、前記スイッチ出力に基づいて、前記制御端子に、前記電流出力トランジスタをオフにするオフ制御電圧を発生させることを特徴とする。

【0009】

また、この発明の第3の観点による電圧制御形スイッチングデバイスのゲート駆動装置は、定電圧パルス出力を発生する電圧出力トランジスタを含む定電圧駆動回路を用い、前記定電圧パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路と、前記スイッチ出力に基づいて、前記電圧出力トランジスタをオフにするオフ制御電圧を発生するオフ制御回路を備え、前記オフ制御回路が、前記電圧出力トランジスタの制御端子に、前記オフ制御電圧を供給するように構成したことを特徴とする。

【0010】

さらに、この発明の第4の観点による電圧制御形スイッチングデバイスのゲート駆動装置は、定電圧パルス出力を発生する電圧出力トランジスタを含む定電圧駆動回路を用い、前記定電圧パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときに、スイッチ出力を発生するスイッチ回路を備え、前記スイッチ回路は、前記電圧出力トランジスタの制御端子に接続され、前記スイッチ出力に基づいて、前記制御端子に、前記電圧出力トランジスタをオフにするオフ制御電圧を発生させることを特徴とする。

【発明の効果】

【0011】

この発明の第1の観点による電圧制御形スイッチングデバイスのゲート駆動装置では、閾値電圧を持った半導体スイッチ素子を有し、電圧制御形スイッチングデバイスの出力電流に応じて大きさが変化する検出電圧が、前記半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路と、前記スイッチ出力に基づいて、前記電流出力トランジスタをオフにするオフ制御電圧を発生するオフ制御回路を備え、前記オフ制御回路が、定電流パルス出力を出力する電流出力トランジスタの制御端子に、前記オフ制御電圧を供給するように構成しているので、電流出力トランジスタのストレージ特性による遅れは回避できないものの、定電流パルス出力を出力する電流出力トランジスタを迅速にオフすることができ、電圧制御形スイッチングデバイスの他の保護回路との強調が容易になる効果がある。

【0012】

また、この発明の第2の観点による電圧制御形スイッチングデバイスのゲート駆動装置では、閾値電圧を持った半導体スイッチ素子を有し、検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときに、スイッチ出力を発生するスイッチ回路を備え、前記スイッチ回路は、定電流パルス出力を出力する電流出力トランジスタの制御端子に接続され、前記スイッチ出力に基づいて、前記制御端子に、前記電流出力トランジスタをオフにするオフ制御電圧を発生させるので、電流出力トランジスタのストレージ特性による遅れは回避できないものの、定電流パルス出力を出力する電流出力トランジスタを迅速にオフすることができ、電圧制御形スイッチングデバイスの他の保護回路との強調が容易になる効果がある。

【0013】

また、この発明の第3の観点による電圧制御形スイッチングデバイスのゲート駆動装置では、閾値電圧を持った半導体スイッチ素子を有し、検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路と、前記スイッチ出力に基づいて、前記電圧出力トランジスタをオフにするオフ制御電圧を発生するオフ制御回路を備え、前記オフ制御回路が、定電圧パルス出力を出力する電圧出力トランジスタの制御端子に、前記オフ制御電圧を供給するように構成したので、電圧制御形スイッチングデバイスのストレージ特性による遅れは回避できないものの、定電圧パルス出力を出力する電圧出力トランジスタを迅速にオフすることができ、電圧制御形スイッチングデバイスの他の保護回路との強調が容易になる効果がある。

【0014】

さらに、この発明の第4の観点による電圧制御形スイッチングデバイスのゲート駆動装置では、閾値電圧を持った半導体スイッチ素子を有し、検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときに、スイッチ出力を発生するスイッチ回路を備え、前記スイッチ回路は、定電圧パルス出力を出力する電圧出力トランジスタの制御端子に接続され、前記スイッチ出力に基づいて、前記制御端子に、前記電圧出力トランジスタをオフにするオフ制御電圧を発生させるので、出力トランジスタのストレージ特性による遅れは回避できないものの、定電圧パルス出力を出力する電圧出力トランジスタを迅速にオフすることができ、電圧制御形スイッチングデバイスの他の保護回路との強調が容易になる効果がある。

【発明を実施するための最良の形態】

【0015】

以下この発明のいくつかの実施の形態について、図面を参照して説明する。

【0016】

実施の形態1.

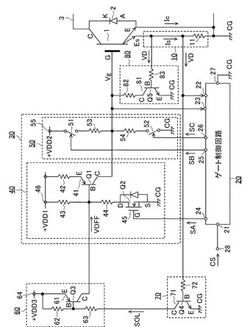

図1は、この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態1を示す電気回路図である。この実施の形態1のゲート駆動装置は、電圧制御形スイッチングデバイス1と、電流検出回路10と、ゲート制御回路20と、ゲート駆動回路30と、オフ制御回路60と、スイッチ回路70と、ゲート遮断回路80を有する。

【0017】

電圧制御形スイッチングデバイス1は、例えばパワー用IGBTであり、ゲートGとコレクタCとエミッタEを有し、さらに、センスエミッタEsも有する。コレクタCとエミッタEとの間には、保護ダイオード2が接続される。この保護ダイオード2のアノードAはエミッタEに、そのカソードKはコレクタCにそれぞれ接続される。コレクタCおよびエミッタEは、応用回路3に接続される。

【0018】

エミッタEは、共通電位CG、例えばグランド電位に直接接続され、センスエミッタEsは、電流検出回路10を通じて、共通電位CGに接続される。電圧制御形スイッチングデバイス1のエミッタEに出力電流Icが流れるときに、センスエミッタEsには、出力電流Icに比例したセンス電流Isが流れる。電流検出回路10は、センスエミッタEsと共通電位CGとの間に接続された検出抵抗11を有し、この検出抵抗11は、その両端に出力電流Icに比例した大きさの検出電圧VDを発生する。このようにセンスエミッタEsを有するIGBTを用い、センスエミッタEsに検出抵抗11を接続することにより、高速度で、出力電流Icに応じて大きさが変化する検出電圧VDを検出することができる。

【0019】

なお、電圧制御形スイッチングデバイス1には、センスエミッタEsを持たないIGBTを用いることもできる。この場合、検出抵抗11は、エミッタEに接続され、検出電圧VDを発生するように構成される。また、電圧制御形スイッチングデバイス1には、パワーMOSFETを使用することもできる。このパワーMOSFETは、ゲート、ドレイン、ソースを有し、ドレインとソースが応用回路3に接続される。ソースには、検出抵抗11が接続され、この検出抵抗11により、出力電流Icに応じて大きさが変化する検出電圧VDが発生される。

【0020】

ゲート制御回路20は、入力端子21、22、23と、出力端子24、25、26と、共通電位端子27を有する。入力端子21は制御信号入力端子28に接続され、この制御信号入力端子28から制御信号CSが供給される。入力端子22は、検出抵抗11のセンスエミッタEs側に接続されており、この入力端子22には、検出電圧VDが入力される。入力端子23は、スイッチングデバイス1のゲートGに接続され、そのゲート電圧Vgが入力される。共通電位端子27は、共通電位CGに直接接続される。ゲート制御回路20は、ゲート電圧Vgを監視しながら、制御信号CSに基づいて、出力端子24、25、26のそれぞれに、制御出力信号SA、SB、SCを発生し、また、検出電圧VDを監視することにより、スイッチングデバイス1に過電流異常が発生したときには、スイッチングデバイス1が故障しないように、ゲート駆動回路30を制御する。

【0021】

ゲート駆動回路30は、定電流駆動回路40と、定電圧駆動回路50を有する。定電流駆動回路40は、スイッチングデバイス1のゲートGに定電流パルス出力を供給する。この定電流駆動回路40は、電流出力トランジスタ41と、抵抗42、43、44と、制御トランジスタ45を含み、直流電源端子46と共通電位CGの間に接続される。直流電源端子46には、直流電圧+VDD1が供給される。電流出力トランジスタ41は、例えばPNP形バイポーラトランジスタQ1で構成される。このトランジスタQ1のコレクタCは、スイッチングデバイス1のゲートGに直接接続され、ゲートGに定電流パルス出力を供給する。トランジスタQ1のエミッタEは、抵抗42を通じて直流電源端子46に接続される。抵抗43、44および制御トランジスタ45は、直流電源端子46と共通電位CGとの間に直列に接続され、抵抗43、44の相互接続点にトランジスタQ1の制御端子、すなわちベースBが直接接続される。

【0022】

なお、電流出力トランジスタ41は、MOSFET、例えばPチャネルMOSFETで構成することもできる。この場合には、PチャネルMOSFETのソースが抵抗42を通じて直流電源端子46に接続され、そのドレインがスイッチングデバイス1のゲートGに接続され、その制御端子、すなわちゲートが抵抗43、44の相互接続点に直接接続される。

【0023】

制御トランジスタ45は、電流出力トランジスタ41を制御する。制御トランジスタ45は、例えばNチャネルMOSトランジスタQ2で構成される。このMOSトランジスタQ2のソースSは、共通電位CGに直接接続され、そのドレインDは、抵抗43、44を通じて直流電源端子46に接続され、またそのゲートGには、ゲート制御回路20の出力端子24から制御出力信号SAが供給される。

【0024】

制御出力信号SAがロウレベルであるときには、制御トランジスタ45はオフとなり、電流出力トランジスタ41もオフとなり、定電流パルス出力は供給されない。制御出力信号SAがハイレベルとなったときには、制御トランジスタ45がオンとなり、電流出力トランジスタ41にベース電流が流れるので、電流出力トランジスタ41もオンとなり、定電流パルス出力がスイッチングデバイス1のゲートGに供給される。

【0025】

定電圧駆動回路50は、スイッチングデバイス1のゲートGに定電圧出力を供給する。定電圧駆動回路50は、一対のスイッチ素子51、52と、一対の抵抗53、54を含み、直流電源端子55と共通電位CGとの間に接続される。一対の抵抗53、54の相互接続点は、スイッチングデバイス1のゲートGに直接接続され、抵抗53、54の相互接続点から、スイッチングデバイス1のゲートGに定電圧出力を供給する。直流電源端子55には、直流電圧+VDD2が供給される。スイッチ素子51と抵抗53は、直流電源端子55とゲートGとの間に直列に接続され、スイッチ素子52と抵抗54は、ゲートGと共通電位CGとの間に直列に接続される。スイッチ素子51、52は、MOSFETまたはバイポーラトランジスタにより構成される。

【0026】

スイッチ素子51には、ゲート制御回路20の出力端子25から制御出力信号SBが供給され、制御出力信号SBがロウレベルであるときに、スイッチ素子51はオンとなる。スイッチ素子52には、ゲート制御回路20の出力端子26から制御出力信号SCが供給され、制御出力信号SCがハイレベルであるときに、スイッチ素子52はオンとなる。制御出力信号SBがハイレベルであるときには、スイッチ素子51はオフとなり、また、制御出力信号SCがロウレベルであるときには、スイッチ素子52はオフとなる。定電圧駆動回路50は、スイッチ素子51がオンとなり、スイッチ素子52がオフとなったときに、直流電圧+VDD2から定電圧出力をスイッチングデバイス1のゲートGに供給する。

【0027】

オフ制御回路60は、定電流駆動回路40の電流出力トランジスタ41を強制的にオフ状態に制御する。電流出力トランジスタ41の動作は、制御トランジスタ45により制御されるが、オフ制御回路60は、制御トランジスタ45による制御とは関係なく、電流出力トランジスタ41の制御端子にオフ制御電圧VOFFを供給する。このオフ制御回路60は、半導体スイッチ素子61と、抵抗62、63を含み、直流電源端子64に接続される。半導体スイッチ素子61は、例えばPNP形バイポーラトランジスタQ3で構成され、そのコレクタCは、電流出力トランジスタ41の制御端子、すなわちトランジスタQ1のベースBに直接接続される。抵抗62、63は、互いに直列に接続され、スイッチ回路70と直列に、直流電源端子64と共通電位CGとの間に接続される。抵抗62、63の相互接続点に、トランジスタQ3のベースBが直接接続される。なお、電流出力トランジスタ41がMOSFETで構成される場合には、トランジスタQ3のコレクタCは、その制御端子、すなわちゲートに接続される。直流電源端子64には、直流電圧+VDD3が供給され、この直流電圧+VDD3は、定電流駆動回路40の直流電圧+VDD1に等しいか、またはそれよりも高い電圧とされる。すなわち、VDD3≧VDD1である。

【0028】

なお、半導体スイッチ素子61は、MOSFET、例えばPチャネルMOSFETで構成することもできる。この場合、MODFETのソースが直流電源端子64に、またそのドレインが、電流出力トランジスタ41の制御端子に接続され、そのゲートが抵抗62、63の相互接続点に直接接続される。

【0029】

オフ制御回路60は、スイッチングデバイス1に過電流異常が発生し、スイッチ回路70がロウレベルのスイッチ出力SOLを発生したときに、半導体スイッチ素子61がオンとなり、オフ制御電圧VOFFを発生し、このオフ制御電圧VOFFを電流出力トランジスタ41の制御端子に供給する。VDD3≧VDD1の関係にあるので、オフ制御電圧VOFFは電流出力トランジスタ41の制御端子に、そのエミッタEの電位以上の電位を与える。このオフ制御電圧VOFFは、電流出力トランジスタ41を強制的にオフにする電圧である。このオフ制御電圧VOFFにより、電流出力トランジスタ41のベース、エミッタ間の電圧は、VDD3=VDD1である場合には0ボルトになり、また、VDD3>VDD1の場合にはベースがエミッタよりも電位の高い逆電圧となる。

【0030】

定電流駆動回路40の制御トランジスタ45がオンし、電流出力トランジスタ41がオンしている状態で、このオフ制御電圧VOFFが、電流出力トランジスタ41の制御端子に与えられると、電流出力トランジスタ41は強制的にオフとされ、定電流パルス出力が停止される。なお、制御トランジスタ45がオフし、電流出力トランジスタ41がオフしている状態で、オフ制御回路60がオフ制御電圧VOFFを発生しても、この状態では、電流出力トランジスタ41がオフ状態にあるので、定電流駆動回路40に特別な影響はない。

【0031】

スイッチ回路70は、スイッチングデバイス1に過電流異常が発生し、検出電圧VDが閾値電圧VT1を越えたときに、オフ制御回路60にロウレベルのスイッチ出力SOLを供給する。このスイッチ回路70は、半導体スイッチ素子71と、抵抗72を含む。半導体スイッチ素子71は、例えばNPN形バイポーラトランジスタQ4により構成され、そのコレクタCは、オフ制御回路60の抵抗62、63を通じて、直流電源端子64に接続される。トランジスタQ4のエミッタEは直接共通電位CGに接続され、そのベースBは抵抗72を通じて、電流検出回路10における検出抵抗11のセンスエミッタEs側に接続される。

【0032】

半導体スイッチ素子71は、トランジスタQ4のベースBとエミッタEとの間に閾値電圧VT1を有し、検出電圧VDが閾値電圧VT1を越えたタイミングでオンとなり、そのコレクタCにロウレベルのスイッチ出力SOLを出力する。検出電圧VDが閾値電圧VT1以下であるときには、半導体スイッチ素子71はオフし、オフ制御回路60の半導体スイッチ素子61もオフとなるので、オフ制御回路60はオフ制御電圧VOFFを発生せず、定電流駆動回路40の動作に影響を与えることはない。

【0033】

なお、半導体スイッチ素子71は、MOSFET、例えばNチャネルMOSFETで構成することもできる。この場合、そのドレインが抵抗62、63を通じて、直流電源端子64に接続され、またそのソースが共通電位CGに接続され、そのゲートが抵抗72を通じて検出抵抗11のセンスエミッタEs側に接続される。このMOSFETでは、そのゲートの閾値電圧が、閾値電圧VT1となる。

【0034】

半導体スイッチ素子61、71には、高速でターンオン動作を行なうトランジスタQ3、Q4が使用される。これらのターンオン速度は、250nsec以下、理想的には、100nsec以下とすることが望ましい。トランジスタQ3、Q4は、具体的には、ディスクリートのトランジスタの中で、前記高いターンオン速度を持ったトランジスタを選択し、このディスクリートのトランジスタで構成される。しかし、ICで構成されたトランジスタの中に、前記高いターンオン速度を持ったものがあれば、このトランジスタを用いて構成することもできる。また、半導体スイッチ素子61については、制御トランジスタ45がオン状態にあるときに、半導体スイッチ素子61がオンに駆動されることが想定されるので、コレクタ電流と発熱を考慮して、構成するトランジスタを選択する。

【0035】

半導体スイッチ素子61、71は前述の高いターンオン速度を持つことにより、スイッチングデバイス1に過電流異常が発生した場合、検出電圧VDが閾値電圧VT1を超えたタイミングで、迅速に電流出力トランジスタ41をオフすることができる。この電流出力トランジスタ41のオフ動作の遅れは、トランジスタ41のストレージ特性による遅れのみとなり、判定の遅れや回路の応答の遅れにより、定電流パルス出力が継続するのを防止することができる。

【0036】

ゲート遮断回路80は、保護用半導体スイッチ素子81と抵抗82、83を含む。保護用半導体スイッチ素子81は、例えばNPN形バイポーラトランジスタQ5で構成され、そのコレクタCは抵抗82を通じてスイッチングデバイス1のゲートGに接続され、そのエミッタEは直接共通電位CGに接続され、そのベースBは抵抗83を通じて、電流検出回路10における検出抵抗11のセンスエミッタEs側に接続される。この保護用半導体スイッチ素子81は、トランジスタQ5のベースBとエミッタEとの間に閾値電圧VT2を有し、スイッチングデバイス1に過電流異常が発生して検出電圧VDが閾値電圧VT2を越えたときにオンとなり、ゲートGを共通電位CGに接続する。この保護用半導体スイッチ素子81のオンにより、スイッチングデバイス1のゲートGの電位は、抵抗82を通じて共通電位CGに放電され、低下するように制御される。

【0037】

なお、閾値電圧VT2は、半導体スイッチ素子71の閾値電圧VT1とほぼ同じか、それよりも少し高い値とされる。閾値電圧VT2が閾値電圧VT1より少し高い場合、またはVT2=VT1であっても、保護用スイッチ素子81が、半導体スイッチ素子71のターンオン速度よりも低い半導体スイッチ素子で構成されると、スイッチングデバイス1に過電圧異常が発生した場合、スイッチ回路70およびオフ制御回路60により、電流出力トランジスタ41にオフ制御電圧VOFFが与えられ、定電流パルス出力が停止された後で、ゲート遮断回路80が動作する。従来のゲート遮断回路は、定電流パルス出力が継続している状態で動作し、このためスイッチングデバイス1に、電流が流れ続ける恐れがあったが、このような問題も解消される。

【0038】

なお、スイッチ素子81は、MOSFET、例えばNチャネルMOSFETで構成することもできる。この場合、そのドレインが抵抗82を通じて、スイッチングデバイス1のゲートGに接続され、またそのソースが共通電位CGに接続され、そのゲートが抵抗82を通じて検出抵抗11のセンスエミッタEs側に接続される。このMOSFETでは、そのゲートの閾値電圧に基づいて、閾値電圧VT2が与えられる。

【0039】

さて、図1に示す実施の形態1の動作について説明する。先ず、ゲート駆動回路30における定電流駆動回路40と定電圧駆動回路50の動作について、図2を参照して説明する。図2は、制御信号CSがハイレベルとなった後に、ロウレベルに変化する場合の動作を示す。図2(a)は、電圧制御形スイッチングデバイス1のコレクタCとエミッタEとの間の電圧Vceと、出力電流Icの変化を示す。図2(b)は、スイッチングデバイス1のゲート電圧Vgの変化を示す。図2(c)は制御信号CSのレベル変化を示し、図2(d)(e)(f)は、それぞれ制御出力信号SA、SB、SCのレベル変化を示す。

【0040】

図2には、制御信号CSがハイレベルとなる制御期間T1と、制御信号CSがロウレベルとなる制御期間T2が示される。制御期間T1の直前には、制御信号CSがロウレベル、制御出力信号SAがロウレベル、制御出力信号SB、SCがともにハイレベルであり、制御出力信号SBがハイレベルであるため、定電圧駆動回路50におけるスイッチ素子51がオフしており、また、制御出力信号SCがハイレベルであるため、スイッチ素子52がオンしている状態にある。

【0041】

制御期間T1は、第1制御区間TAと第2制御区間TBを含み、第1制御区間TAから第2制御区間TBに切換えられる。第1制御区間TAでは、定電流駆動回路40が動作し、この定電流駆動回路40から、定電流パルス出力がスイッチングデバイス1のゲートGに供給される。第2制御区間TBでは、定電圧駆動回路50から定電圧出力が、スイッチングデバイス1のゲートGに供給される。定電流駆動回路40と定電圧駆動回路50を切換え動作させることにより、安定したゲート駆動が行なわれる。

【0042】

第1制御区間TAでは、制御出力信号SA、SBがハイレベル、制御出力信号SCがロウレベルとなる。この状態では、制御出力信号SAがハイレベルであるため、定電流駆動回路40の制御トランジスタ45がオンとなり、電流出力トランジスタ41もオンとなって、定電流駆動回路40が動作し、この定電流駆動回路40から定電流パルス出力がゲートGに供給される。この定電流パルス出力により、ゲートGのゲート電圧Vgは直線的に上昇し、このゲート電圧Vgが所定値Vth1に達したときに、スイッチングデバイス1はターンオン動作Tonを開始する。このターンオン動作Tonでは、出力電流Icが増加し、電圧Vceが低下する。ターンオン動作Tonが完了した後、スイッチングデバイス1はオン状態ONとなる。

【0043】

ゲート制御回路20は、入力端子23に入力されるゲート電圧Vgを監視し、このゲート電圧Vgが所定値Vg1に達したときに、第1制御区間TAから第2制御区間TBへの切換動作を行なう。第2制御区間TBでは、制御出力信号SA、SB、SCのすべてがロウレベルになる。この第2制御区間TBでは、制御出力信号SAがロウレベルとなるため、定電流駆動回路40の制御トランジスタ45がオフとなり、電流出力トランジスタ41もオフとなって、定電流パルス出力は停止する。第2制御区間TBでは、制御出力信号SB、SCがともにロウレベルとなるため、定電圧駆動回路50におけるスイッチ素子51がオンとなり、スイッチ素子52がオフとなる。このため、定電圧駆動回路50は、直流電圧+VDD2に基づいて定電圧をゲートGに供給する。

【0044】

制御期間T2では、制御信号CSがロウレベルとなり、制御出力信号SAはロウレベル、制御出力信号SB、SCはともにハイレベルとなる。制御出力信号SAがロウレベルであるため、定電流駆動回路40は動作しない。また、定電圧駆動回路50では、制御出力信号SB、SCがともにハイレベルであるため、スイッチ素子51はオフ、スイッチ素子52はオンとなる。このため、定電圧駆動回路50からの定電圧も停止し、ゲート電圧Vgはスイッチ素子52と抵抗54を通じて放電するため、低下する。このゲート電圧Vgの低下に伴ない、スイッチングデバイス1は、オン状態ONからターンオフ動作Toffの状態を経て、オフ状態OFFとなる。

【0045】

さて、ゲート駆動回路30の動作状態に拘わらず、スイッチングデバイス1に過電流異常が発生し、その出力電流Icが増大して、検出電圧VDが半導体スイッチ素子71の閾値VT1を越えたタイミングで、半導体スイッチ素子71は、ロウレベルのスイッチ出力SOLを発生し、オフ制御回路60の半導体スイッチ素子61がオフ制御電圧VOFFを、定電流駆動回路40における電流出力トランジスタ41の制御端子に供給する。第1制御区間TAにあって、定電流駆動回路40の電流出力トランジスタ41が定電流パルス出力を発生している状態で、検出電圧VDが閾値VT1を越えれば、半導体スイッチ素子71、61は共に高速のターンオン動作を行ない、電流出力トランジスタ41は強制的にオフ状態とされる。

【0046】

第1制御区間TA以外では、制御トランジスタ45がオフとなり、電流出力トランジスタ41もオフ状態にある。この状態でも検出電圧VDが閾値VT1を越えると、実施の形態1では、半導体スイッチ71、61は、同様に高速でターンオン動作を行ない、電流出力トランジスタ41の制御端子にオフ制御電圧VOFFを与えるが、この状態では電流出力トランジスタ41がオフ状態にあるので、オフ制御電圧VOFFは電流出力トランジスタ41に影響を与えない。第1制御区間TA以外でスイッチングデバイス1に過電流異常が発生したときには、検出電圧VDが閾値電圧VT2を越えたタイミングで、ゲート遮断回路80の保護用半導体スイッチ素子81がオンとなり、このゲート遮断回路80により、スイッチングデバイス1の保護が図られる。

【0047】

スイッチ回路70およびオフ制御回路60に加えてゲート遮断回路80を併用する実施の形態1では、第1制御区間TAにおいて、定電流駆動回路40が定電流パルス出力を出力している状態では、先ずスイッチ回路70およびオフ制御回路60により、電流出力トランジスタ41を強制的にオフ状態にし、定電流パルス出力を停止した後で、ゲート遮断回路80を動作させることにより、スイッチングデバイス1を、より高速度で過電流状態から復帰させることができる。

【0048】

実施の形態2.

図3は、この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態2を示す電気回路図である。

【0049】

この実施の形態2は、実施の形態1に対して、スイッチ出力延長回路90を追加したものである。その他は、実施の形態1と同じに構成される。スイッチ出力延長回路90は、スイッチ回路70の半導体スイッチ素子71と並列に接続される。このスイッチ出力延長回路90は、コンデンサ91と抵抗92を含み、これらを直列接続したもので、コンデンサ91の一端は半導体スイッチ素子71を構成するトランジスタQ4のエミッタEに、また抵抗92の一端は、そのコレクタCにそれぞれ接続される。

【0050】

コンデンサ91は、スイッチ回路70の半導体スイッチ素子71がオフしている状態において、直流電源端子64の直流電圧+VSS3により、抵抗62、63、92を通じて充電され、半導体スイッチ素子71がオンしたときに、抵抗92および半導体スイッチ素子71を通じて放電する。半導体スイッチ素子71がオフ状態に復帰すると、コンデンサ91は、抵抗62、63、92を通じて、直流電源端子64から再び充電されるようになり、半導体スイッチ素子71がオフした後に、所定時間に亘り、ロウレベルのスイッチ出力SOLを延長する。

【0051】

このように、コンデンサ91は、半導体スイッチ素子71がオフした後まで、ロウレベルのスイッチ出力SOLを所定時間延長する機能を持ち、電流出力トランジスタ41を強制的にオフする時間を延長する。このスイッチ出力延長回路90を設けることにより、定電流駆動回路40の電流出力トランジスタ41は、より長い時間に亘り強制的にオフとされるので、一度、スイッチ回路70によるスイッチングデバイス1の過電流保護が行なわれると、その過電流異常が解消した後でも、所定時間は保護動作を続けることが可能となり、他の保護回路との強調が容易となる。

【0052】

なお、スイッチ出力延長回路90には、コンデンサ91と抵抗92に代えて、コンデンサと抵抗により動作時間を設定する単安定マルチバイブレータ回路を用いることもでき、この単安定マルチバイブレータ回路をIC化することもできる。

【0053】

実施の形態3.

図4は、この発明による電圧制御形スイッチングデバイスの実施の形態3を示す電気回路図である。この実施の形態3は、実施の形態1における定電流駆動回路40を、定電流駆動回路140に置き換えたものである。その他は、実施の形態1と同じに構成される。

【0054】

実施の形態3で使用される定電流駆動回路140は、カレントミラー回路141と、定電流回路142と、定電流制御回路143を含む。定電流制御回路143に、ゲート制御回路20の出力端子24から制御出力信号SAが供給される。カレントミラー回路141は、定電流駆動トランジスタ141aと、この定電流駆動トランジスタ141aとほぼ同じ特性を持ち、互いに並列に接続された電流出力トランジスタ群141bで構成される。定電流駆動トランジスタ141aは、例えばPNP形バイポーラトランジスタQ11で構成され、電流出力トランジスタ群141bの各トランジスタも、例えば同じPNP形バイポーラトランジスタQ12で構成される。

【0055】

トランジスタQ11のエミッタEは、直流電圧+VDD1が印加される直流電源端子46に直接接続され、そのコレクタCは定電流回路142を通じて共通電位CGに接続され、また、そのベースBに接続される。トランジスタQ11の制御端子、すなわちベースBは、各トランジスタQ12の制御端子、すなわちベースBに共通接続される。各トランジスタQ12のエミッタEは、互いに共通接続され、直流電源端子46に直接接続される。各トランジスタQ12のコレクタCも互いに共通接続され、スイッチングデバイス1のゲートGに直接接続される。

【0056】

定電流回路142は、トランジスタQ11に流れる定電流値を設定するもので、この定電流値は、定電流制御回路143で決定される。この定電流制御回路143は、ゲート制御回路20の制御出力信号SAによって駆動され、制御出力信号SAがハイレベルになったときには、定電流制御回路143が駆動され、各トランジスタQ12にも、それぞれトランジスタQ11と同じ電流が流れるので、トランジスタQ11に流れる定電流を、トランジスタQ12の数だけ加え合わせた電流値の定電流パルス出力が,スイッチングデバイス1のゲートGに供給される。

【0057】

オフ制御回路60の半導体スイッチ素子61を構成するトランジスタQ3のコレクタCは、トランジスタQ11および各トランジスタQ12の制御端子、すなわちベースBに直接接続される。このトランジスタQ3は、スイッチ回路70からロウレベルのスイッチ出力SOLを受けたときに、実施の形態1と同様に、トランジスタQ11、Q12の各ベースBにオフ制御電圧VOFFを与える。このオフ制御電圧VOFFは、定電流駆動回路140の電流出力トランジスタ群141bがスイッチングデバイス1のゲートGに定電流パルス出力を供給している状態で、各トランジスタQ11、Q12を強制的にオフ状態とし、定電流パルス出力を停止する。この実施の形態3でも、実施の形態1と同じ効果が得られる。

【0058】

実施の形態4.

図5は、この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態4を示す電気回路図である。この実施の形態4は、実施の形態3に対して、図3に示すスイッチ出力延長回路90を追加したもである。その他は、実施の形態3と同じに構成される。

【0059】

実施の形態4のスイッチ出力延長回路90は、実施の形態2と同じに構成され、それと同じ作用を行なうので、実施の形態2と同じ効果を得ることができる。

【0060】

実施の形態5.

図6は、この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態5を示す電気回路図である。この実施の形態5では、実施の形態1における定電流駆動回路40が定電流駆動回路240に置き換えられ、また実施の形態1におけるオフ制御回路60が削除される。その他は、実施の形態1と同じに構成される。

【0061】

実施の形態5で使用される定電流駆動回路240は、電流出力トランジスタ241と、抵抗242、243、244と、定電流制御回路245を有し、定電流制御回路245には、ゲート制御回路20の出力端子24から制御出力信号SAが供給される。電流出力トランジスタ241は、例えばNPN形バイポーラトランジスタQ13で構成される。このトランジスタQ13のコレクタCは、直流電源端子46に直接接続され、そのエミッタEは、抵抗242を通じて、スイッチングデバイス1のゲートGに接続され、このエミッタEから定電流パルス出力がゲートGに供給される。電流出力トランジスタ241の制御端子、すなわちトランジスタQ13のベースBは、抵抗243、244の相互接続点に接続される。

【0062】

定電流制御回路245は、抵抗243を通じて電流出力トランジスタ241の制御端子、すなわちトランジスタQ13のベースBに接続される。この定電流制御回路245は、フィードバック制御を行なう2つの比較回路COM1、COM2を含む。比較回路COM2は、スイッチングデバイス1のゲートGの電圧Vgと、トランジスタQ13のエミッタEの電圧との差電圧を出力し、また、比較回路COM1は、比較回路COM2から出力される差電圧と、定電流設定値入力との偏差を出力する。定電流制御回路245は、制御出力信号SAがハイレベルであるときに動作し、抵抗243を通じて、比較回路COM1から出力される偏差を電流出力トランジスタ241の制御端子、すなわちトランジスタQ13のベースBに供給し、フィードバック制御を行ないながら、電流出力トランジスタ241のエミッタEから、定電流パルス出力をゲートGへ供給する。トランジスタQ13は、エミッタフォロアとして動作し、定電流パルス出力をゲートGに供給する。制御出力信号SAがロウレベルであるときには、定電流制御回路245は動作せず、定電流パルス出力は停止する。

【0063】

スイッチ回路70の半導体スイッチ素子71を構成するトランジスタQ4のコレクタCは、抵抗244を通じて、電流出力トランジスタ241の制御端子、すなわちトランジスタQ13のベースBに直接接続される。実施の形態5では、制御出力信号SAがハイレベルにあるときに、スイッチ回路70は、定電流制御回路245から抵抗243、244を通じて給電を受けるが、制御出力信号SAがロウレベルであるときには、スイッチ回路70には給電されない。

【0064】

実施の形態5では、制御出力信号SAがハイレベルにあり、電流出力トランジスタ241がスイッチングデバイス1のゲートGに定電流パルス出力を供給している状態において、スイッチングデバイス1に過電流異常が発生し、検出電圧VDが閾値電圧VT1を越えたタイミングで、スイッチ回路70はロウレベルのスイッチ出力SOLを発生する。このロウレベルのスイッチ出力SOLにより、抵抗243から抵抗244および半導体スイッチ素子71を通じて共通電位CGに至る回路に電流が流れ、抵抗243、244の相互接続点にオフ制御電圧VOFFが発生する。

【0065】

実施の形態5では、抵抗244は、抵抗243に比べて充分小さな抵抗値とされ、オフ制御電圧VOFFは、スイッチングデバイス1の閾値電圧Vth1以下とされる。この閾値電圧Vth1は、スイッチングデバイス1に定格電流の0.01%の電流が流れるときのゲート電圧Vgの値とされる。電流出力トランジスタ241を構成するトランジスタQ13のエミッタEには、ゲート電圧Vgが印加されており、このゲート電圧Vgは、第1制御区間TAの殆どの期間を通じて、閾値電圧Vth1よりも大きい。したがって、第1制御区間TAの殆どの期間において、オフ制御電圧VOFFが発生したタイミングでは、トランジスタQ13のベースBとエミッタEの間には、ベースB側の電圧がエミッタE側の電圧よりも小さい逆電圧が印加され、電流出力トランジスタ241は強制的にオフ状態とされる。

【0066】

このように、実施の形態5では、第1制御区間TAにおいて、電流出力トランジスタ241が定電流パルス出力を発生している状態で、オフ制御電圧VOFFが発生した場合には、電流出力トランジスタ241が強制的にオフとされ、定電流パルス出力が停止される。半導体スイッチ素子71は、検出電圧VDが閾値電圧VT1を越えたタイミングで、高いターンオン速度でロウレベルのスイッチ出力SOLを発生するので、電流出力トランジスタ241は迅速に定電流パルス出力を停止し、定電流パルス出力が継続するのを防止する。第2制御区間TBおよび制御期間T2では、制御出力信号SAがロウレベルとなり、定電流制御回路245が動作しないので、スイッチ回路70への給電も行なわれず、スイッチ回路70は動作しない。

【0067】

なお、電流出力トランジスタ241は、MOSFET,例えばNチャネルMOSFETで構成することもできる。この場合、MOSFETのドレインは直流電源端子46に直接接続され、そのソースは抵抗242を通じて、スイッチングデバイス1のゲートGに接続され、また、その制御端子、すなわちゲートは、抵抗243、244の相互接続点に直接接続される。

【0068】

実施の形態6.

図7は、この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態6を示す電気回路図である。この実施の形態6では、実施の形態1におけるゲート駆動回路30が、ゲート駆動回路300に置き換えられ、また、ゲート制御回路20では、入力端子23と出力端子25が削除される。このゲート制御回路20は、出力端子24から制御出力信号SAを、また、出力端子26から制御出力信号SCをそれぞれゲート駆動回路300に供給するように構成される。その他は、実施の形態1と同じに構成される。

【0069】

実施の形態6で使用されるゲート駆動回路300は、定電圧駆動回路340と、ゲートオフ回路350を有する。定電圧駆動回路340は、電圧制御形スイッチングデバイス1のゲートGに定電圧パルス出力を供給する。ゲートオフ回路350は、スイッチングデバイス1のゲートGを共通電位CGに接続し、スイッチングデバイス1をオフさせる。

【0070】

定電圧駆動回路340は、電圧出力トランジスタ341と、抵抗342、343、344と、インバータ回路345を含む。電圧出力トランジスタ341は、例えばPチャネルMOSFETQ14で構成される。このMOSFETQ14は、ソースSとドレインDとゲートGを有し、ソースSは、直流電源端子64に直接接続され、ドレインDは、抵抗342を通じて、スイッチングデバイス1のゲートGに接続される。電圧出力トランジスタ341の制御端子は、MOSFETQ13のゲートGであり、これは抵抗343、344の相互接続点に直接接続される。

【0071】

なお、電圧出力トランジスタ341は、バイポーラトランジスタ、例えばPNP形バイポーラトランジスタで構成することもできる。この場合、PNP形バイポーラトランジスタのエミッタが直流電源端子64に直接接続され、そのコレクタが抵抗342を通じてスイッチングデバイス1のゲートGに接続され、そのベースが抵抗343、344の相互接続点に直接接続される。

【0072】

抵抗343、344は直列に接続され、インバータ回路345の出力に接続される。インバータ回路345は、ロジックICで構成され、その入力には、ゲート制御回路20の出力端子24から制御出力信号SAが供給される。インバータ回路345は、制御出力信号SAを反転した制御出力信号ISAを出力する。

【0073】

ゲートオフ回路350は、スイッチ素子351と抵抗352を含み、スイッチングデバイス1のゲートGと共通電位CGとの間に接続される。スイッチ素子351と抵抗352は互いに直列に接続される。スイッチ素子351は、MOSFETまたはバイポーラトランジスタにより構成され、このスイッチ素子351には、ゲート制御回路回路20の出力端子26から制御出力信号SCが供給され、この制御出力信号SCがハイレベルであるときにスイッチ素子351はオンとなり、また、制御出力信号SCがロウレベルであるときにはスイッチ素子351はオフとなる。

【0074】

オフ制御回路60は、実施の形態1と同じに構成され、半導体スイッチ素子61を構成するトランジスタQ3のコレクタCは、電圧出力トランジスタ341の制御端子、すなわちMOSFETQ14のゲートGに直接接続され、オフ制御電圧VOFFを電圧出力トランジスタ341の制御端子に供給する。スイッチ回路70は、実施の形態1と同じに構成され、スイッチングデバイス1に過電流異常が発生し、検出電圧VDが閾値電圧VT1を越えたタイミングで、半導体スイッチ素子71がオンとなり、ロウレベルのスイッチ出力SOLを発生し、このスイッチ出力SOLにより、オフ制御回路60の半導体スイッチ素子61がオフ制御電圧VOFFを発生する。半導体スイッチ素子61、71は、高速のターンオン速度を持ち、検出電圧VDが閾値電圧VT1を越えたタイミングで、迅速にオフ制御電圧VOFFを発生する。定電圧駆動回路340の電圧出力トランジスタ341が、スイッチングデバイス1のゲートGに定電圧パルス出力を供給している状態において、オフ制御電圧VOFFは電圧出力トランジスタ341を強制的にオフ状態とする。

【0075】

ゲート遮断回路80も実施の形態1と同じに構成され、検出電圧VDが閾値電圧VT2を越えたときに、スイッチングデバイス1のゲートGを共通電位CGに接続し、ゲートGのゲート電圧Vgを低下させる。

【0076】

さて、図7に示す実施の形態6の動作について説明する。先ず、ゲート駆動回路300における定電圧駆動回路340とゲートオフ回路350の動作について、図8を参照して説明する。図8は、図2と同様に、制御信号CSがハイレベルとなった後に、ロウレベルに変化する場合の動作を示す。図8(a)は、電圧制御形スイッチングデバイス1のコレクタCとエミッタEとの間の電圧Vceと、出力電流Icの変化を示す。図8(b)は、スイッチングデバイス1のゲート電圧Vgの変化を示す。図8(c)は制御信号CSのレベル変化を示し、図8(d)(e)は、それぞれ制御出力信号SA、SCのレベル変化を示す。

【0077】

図8にも、制御信号CSがハイレベルとなる制御期間T1と、制御信号CSがロウレベルとなる制御期間T2が示される。制御期間T1の直前には、制御信号CSがロウレベル、制御出力信号SAがロウレベル、制御出力信号SCがハイレベルであり、制御出力信号SCがハイレベルであるため、スイッチ素子351がオンしている状態にある。

【0078】

制御期間T1では、定電圧駆動回路340が動作し、この定電圧駆動回路340から、定電圧パルス出力がスイッチングデバイス1のゲートGに供給される。制御期間T1では、制御出力信号SAがハイレベル、制御出力信号SCがロウレベルとなる。この状態では、制御出力信号SAがハイレベルであるため、定電圧駆動回路340のインバータ回路345から出力される反転された制御出力信号ISAがロウレベルとなり、電圧出力トランジスタ341がオンとなって、定電圧駆動回路340が動作し、この定電圧駆動回路340から定電圧パルス出力が、スイッチングデバイス1のゲートGに供給される。この定電圧パルス出力により、スイッチングデバイス1のゲート電圧VgはCR充電波形状に上昇し、このゲート電圧Vgが閾値電圧Vth1に達したときに、スイッチングデバイス1はターンオン動作Tonを開始する。このターンオン動作Tonでは、出力電流Icが増加し、電圧Vceが低下する。ターンオン動作Tonが完了した後、スイッチングデバイス1はオン状態ONとなる。

【0079】

制御期間T2では、制御信号CSがロウレベルとなり、制御出力信号SAがロウレベル、制御出力信号SCがハイレベルとなる。制御出力信号SAがロウレベルであるため、定電圧駆動回路340は動作しない。また、ゲートオフ回路350では、制御出力信号SCがハイレベルであるため、スイッチ素子351はオンとなる。このため、ゲート電圧Vgはスイッチ素子351と抵抗352を通じて放電するため、低下する。このゲート電圧Vgの低下に伴ない、スイッチングデバイス1は、オン状態ONからターンオフ動作Toffの状態を経て、オフ状態OFFとなる。

【0080】

さて、ゲート駆動回路300の動作状態に拘わらず、スイッチングデバイス1に過電流異常が発生し、その出力電流Icが増大して、検出電圧VDが半導体スイッチ素子71の閾値VT1を越えたタイミングで、半導体スイッチ素子71は、ロウレベルのスイッチ出力SOLを発生し、オフ制御回路60の半導体スイッチ素子61がオフ制御電圧VOFFを、定電圧駆動回路340における電圧出力トランジスタ41の制御端子に供給する。制御期間T1にあって、定電圧駆動回路340の電圧出力トランジスタ341が定電圧パルス出力を発生している状態で、検出電圧VDが閾値VT1を越えれば、半導体スイッチ素子71、61は共に高速のターンオン動作を行ない、電圧出力トランジスタ341を強制的にオフ状態とする。

【0081】

制御期間T2では、電圧出力トランジスタ341はオフ状態にある。この状態でも検出電圧VDが閾値VT1を越えると、実施の形態6では、半導体スイッチ71、61は、同様に高速でターンオン動作を行ない、電圧出力トランジスタ341の制御端子にオフ制御電圧VOFFを与えるが、この状態では電圧出力トランジスタ341がオフ状態にあるので、オフ制御電圧VOFFは電圧出力トランジスタ341に影響を与えない。制御期間T2でスイッチングデバイス1の過電流異常が発生したときには、検出電圧VDが閾値電圧VT2を越えたタイミングで、ゲート遮断回路80の保護用半導体スイッチ素子81がオンとなり、このゲート遮断回路80により、スイッチングデバイス1の保護が図られる。

【0082】

スイッチ回路70およびオフ制御回路60に加えてゲート遮断回路80を併用する実施の形態6では、制御期間T1において、定電圧駆動回路340が定電圧パルス出力を出力している状態では、先ずスイッチ回路70およびオフ制御回路60により、電圧出力トランジスタ341を強制的にオフ状態にし、定電圧パルス出力を停止した後で、ゲート遮断回路80を動作させることにより、スイッチングデバイス1を、より高速度で過電流状態から復帰させることができる。

【0083】

実施の形態7.

図9は、この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態7を示す電気回路図である。この実施の形態7は、実施の形態6に対して、図3に示すスイッチ出力延長回路90を追加したもである。その他は、実施の形態6と同じに構成される。実施の形態7のスイッチ出力延長回路90は、実施の形態2と同じに構成され、それと同じ作用を行なうので、実施の形態2と同じ効果を得ることができる。

【0084】

実施の形態8.

図10は、この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態8を示す電気回路図である。この実施の形態8では、実施の形態6における定電圧駆動回路340が定電圧駆動回路440に置き換えられ、また実施の形態6におけるオフ制御回路60が削除される。その他は、実施の形態6と同じに構成される。

【0085】

実施の形態8で使用される定電圧駆動回路440は、電圧出力トランジスタ441と、抵抗442、443、444を有し、抵抗443には、ゲート制御回路20の出力端子24から制御出力信号SAが供給される。電圧出力トランジスタ441は、例えばNPN形バイポーラトランジスタQ15で構成される。このトランジスタQ15のコレクタCは、直流電源端子46に直接接続され、そのエミッタEは、抵抗442を通じて、スイッチングデバイス1のゲートGに接続され、このエミッタEから定電圧パルス出力がゲートGに供給される。

【0086】

電圧出力トランジスタ441の制御端子、すなわちトランジスタQ15のベースBは、抵抗443、444の相互接続点に接続される。トランジスタQ15のベースBには、抵抗443を通じて、制御出力信号SAが供給される。定電圧駆動回路440は、制御出力信号SAがハイレベルであるときに動作する。制御出力信号SAがハイレベルにあるときには、抵抗443を通じて、電圧出力トランジスタ441にベース電流が流れ、電圧出力トランジスタ441のエミッタEから、定電圧パルス出力をスイッチングデバイス1のゲートGに供給する。制御出力信号SAがロウレベルであるときには、定電圧駆動回路440は動作せず、定電圧パルス出力は停止する。

【0087】

スイッチ回路70の半導体スイッチ素子71を構成するトランジスタQ4のコレクタCは、抵抗444を通じて、電圧出力トランジスタ441の制御端子、すなわちトランジスタQ15のベースBに接続される。実施の形態8では、制御出力信号SAがハイレベルにあるときに、スイッチ回路70は、制御出力信号SAから抵抗443、444を通じて給電を受けるが、制御出力信号SAがロウレベルであるときには、スイッチ回路70には給電されない。

【0088】

実施の形態8では、制御出力信号SAがハイレベルにあり、電圧出力トランジスタ441がスイッチングデバイス1のゲートGに定電圧パルス出力を供給している状態において、スイッチングデバイス1に過電流異常が発生し、検出電圧VDが閾値電圧VT1を越えたタイミングで、スイッチ回路70はロウレベルのスイッチ出力SOLを発生する。このロウレベルのスイッチ出力SOLにより、抵抗443から抵抗444および半導体スイッチ素子71を通じて共通電位CGに至る回路に電流が流れ、抵抗443、444の相互接続点にオフ制御電圧VOFFが発生する。

【0089】

実施の形態8では、抵抗444は、抵抗443に比べて充分小さな抵抗値とされ、オフ制御電圧VOFFは、スイッチングデバイス1の閾値電圧Vth1以下とされる。この閾値電圧Vth1は、スイッチングデバイス1に定格電流の0.01%の電流が流れるときのゲート電圧Vgの値とされる。電圧出力トランジスタ441を構成するトランジスタQ15のエミッタEには、ゲート電圧Vgが印加されており、このゲート電圧Vgは、期間T1の殆どの期間を通じて、閾値電圧Vth1よりも大きい。したがって、期間T1の殆どの期間において、オフ制御電圧VOFFが発生したタイミングでは、トランジスタQ15のベースBとエミッタEの間には、ベースB側の電圧がエミッタE側の電圧よりも小さい逆電圧が印加され、電圧出力トランジスタ441は強制的にオフ状態とされる。

【0090】

このように、実施の形態8では、制御期間T1において、電圧出力トランジスタ441が定電圧パルス出力を発生している状態で、オフ制御電圧VOFFが発生した場合には、電圧出力トランジスタ441が強制的にオフとされ、定電圧パルス出力が停止される。半導体スイッチ素子71は、検出電圧VDが閾値電圧VT1を越えたタイミングで、高いターンオン速度でロウレベルのスイッチ出力SOLを発生するので、電圧出力トランジスタ441は迅速に定電圧パルス出力を停止し、定電圧パルス出力が継続するのを防止する。制御期間T2では、制御出力信号SAがロウレベルとなり、スイッチ回路70への給電も行なわれず、スイッチ回路70は動作しない。

【0091】

なお、電圧出力トランジスタ441は、MOSFET,例えばNチャネルMOSFETで構成することもできる。この場合、MOSFETのドレインは直流電源端子46に直接接続され、そのソースは抵抗442を通じて、スイッチングデバイス1にゲートGに接続され、また、その制御端子、すなわちゲートは、抵抗443、444の相互接続点に直接接続される。

【産業上の利用可能性】

【0092】

この発明による電圧制御形スイッチングデバイスのゲート駆動装置は、各種の電圧制御形スイッチングデバイス、例えばIGBT、MOSFETなどに利用される。

【図面の簡単な説明】

【0093】

【図1】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態1を示す電気回路図である。

【図2】実施の形態1の動作説明用タイミング図である。

【図3】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態2を示す電気回路図である。

【図4】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態3を示す電気回路図である。

【図5】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態4を示す電気回路図である。

【図6】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態5を示す電気回路図である。

【図7】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態6を示す電気回路図である。

【図8】実施の形態6の動作説明用タイミング図である。

【図9】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態7を示す電気回路図である。

【図10】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態8を示す電気回路図である。

【符号の説明】

【0094】

1:電圧制御形スイッチングデバイス、10:電流検出回路、20:ゲート制御回路、

30.300:ゲート駆動回路、40、140、240:定電流駆動回路、

41、141b、241:電流出力トランジスタ、60:オフ制御回路、

70:スイッチ回路、71:半導体スイッチ素子、80:ゲート遮断回路、

81:保護用半導体スイッチ素子、90:スイッチ出力延長回路、91:コンデンサ、

340、440:定電圧駆動回路、341、441:電圧出力トランジスタ。

【技術分野】

【0001】

この発明は、パワー用IGBTまたはMOSFETなどの電圧制御形スイッチングデバイスのゲート駆動装置に関するものである。

【背景技術】

【0002】

この種の電圧制御形スイッチングデバイスのゲート駆動装置して、定電圧駆動回路を用い、この定電圧駆動回路から電圧制御形スイッチングデバイスのゲートへ定電圧パルス出力を供給し、ゲートを駆動するものが知られていたが、最近では、特許文献1の図8に示すように、定電流駆動回路を用い、この定電流駆動回路から電圧制御形スイッチングデバイスのゲートへ定電流パルス出力を供給し、ゲートを駆動するものも使用されている。特許文献1の段落0025には、抵抗R12、R13、スイッチ素子Q12、Q13、オペアンプQ1、Q2により、定電流回路を構成することが説明されている。

【0003】

【特許文献1】特開2002−95151号公報、とくに図8とその説明

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかし、従来の定電流駆動回路からの定電流パルス出力により電圧制御形スイッチングデバイスのゲートを駆動するものにおいて、定電流パルス出力をオフさせるように制御しても、電圧制御形スイッチングデバイスのストレージ特性や、定電流駆動回路を制御する回路の応答性能などにより、定電流パルス出力が瞬時にオフとならずに、電圧制御形スイッチングデバイスのゲートに電流が流れ続ける可能性がある。また、従来の定電圧駆動回路からの定電圧パルス出力により電圧制御形スイッチングデバイスのゲートを駆動するものにおいて、定電圧パルス出力をオフさせるように制御しても、同様に、定電圧パルス出力が瞬時にオフとならずに、電圧制御形スイッチングデバイスのゲートに電流が流れ続ける可能性がある。

【0005】

このため、電圧制御形スイッチングデバイスの過電流保護、およびそれを用いた応用回路におけるアーム短絡保護の動作時に、電圧制御形スイッチングデバイスのゲートへの電流、電圧の供給が続き、高速に保護回路を動作させるのが困難であった。特に、過電流などの異常事態は、いつ、どのタイミングで発生するか予測できず、また、負荷電流の増大による過電流だけではなく、負荷の短絡や、アーム短絡などで短時間に急激に電圧制御形スイッチングデバイスの出力電流が増大する恐れのある応用回路では、保護回路の応答速度が低いと、電圧制御形スイッチングデバイスの破壊に至る恐れもある。

【0006】

この発明は、定電流パルス出力または定電圧パルス出力をオフさせる速度を改善し、異常事態にあって、迅速に保護動作を行なうことのできる電圧制御形スイッチングデバイスのゲート駆動装置を提案するものである。

【課題を解決するための手段】

【0007】

この発明の第1の観点による電圧制御形スイッチングデバイスのゲート駆動装置は、定電流パルス出力を発生する電流出力トランジスタを含む定電流駆動回路を用い、前記定電流パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路と、前記スイッチ出力に基づいて、前記電流出力トランジスタをオフにするオフ制御電圧を発生するオフ制御回路を備え、前記オフ制御回路が、電流出力トランジスタの制御端子に、前記オフ制御電圧を供給するように構成したことを特徴とする。

【0008】

また、この発明の第2の観点による電圧制御形スイッチングデバイスのゲート駆動装置は、定電流パルス出力を発生する電流出力トランジスタを含む定電流駆動回路を用い、前記定電流パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときに、スイッチ出力を発生するスイッチ回路を備え、前記スイッチ回路は、前記電流出力トランジスタの制御端子に接続され、前記スイッチ出力に基づいて、前記制御端子に、前記電流出力トランジスタをオフにするオフ制御電圧を発生させることを特徴とする。

【0009】

また、この発明の第3の観点による電圧制御形スイッチングデバイスのゲート駆動装置は、定電圧パルス出力を発生する電圧出力トランジスタを含む定電圧駆動回路を用い、前記定電圧パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路と、前記スイッチ出力に基づいて、前記電圧出力トランジスタをオフにするオフ制御電圧を発生するオフ制御回路を備え、前記オフ制御回路が、前記電圧出力トランジスタの制御端子に、前記オフ制御電圧を供給するように構成したことを特徴とする。

【0010】

さらに、この発明の第4の観点による電圧制御形スイッチングデバイスのゲート駆動装置は、定電圧パルス出力を発生する電圧出力トランジスタを含む定電圧駆動回路を用い、前記定電圧パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときに、スイッチ出力を発生するスイッチ回路を備え、前記スイッチ回路は、前記電圧出力トランジスタの制御端子に接続され、前記スイッチ出力に基づいて、前記制御端子に、前記電圧出力トランジスタをオフにするオフ制御電圧を発生させることを特徴とする。

【発明の効果】

【0011】

この発明の第1の観点による電圧制御形スイッチングデバイスのゲート駆動装置では、閾値電圧を持った半導体スイッチ素子を有し、電圧制御形スイッチングデバイスの出力電流に応じて大きさが変化する検出電圧が、前記半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路と、前記スイッチ出力に基づいて、前記電流出力トランジスタをオフにするオフ制御電圧を発生するオフ制御回路を備え、前記オフ制御回路が、定電流パルス出力を出力する電流出力トランジスタの制御端子に、前記オフ制御電圧を供給するように構成しているので、電流出力トランジスタのストレージ特性による遅れは回避できないものの、定電流パルス出力を出力する電流出力トランジスタを迅速にオフすることができ、電圧制御形スイッチングデバイスの他の保護回路との強調が容易になる効果がある。

【0012】

また、この発明の第2の観点による電圧制御形スイッチングデバイスのゲート駆動装置では、閾値電圧を持った半導体スイッチ素子を有し、検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときに、スイッチ出力を発生するスイッチ回路を備え、前記スイッチ回路は、定電流パルス出力を出力する電流出力トランジスタの制御端子に接続され、前記スイッチ出力に基づいて、前記制御端子に、前記電流出力トランジスタをオフにするオフ制御電圧を発生させるので、電流出力トランジスタのストレージ特性による遅れは回避できないものの、定電流パルス出力を出力する電流出力トランジスタを迅速にオフすることができ、電圧制御形スイッチングデバイスの他の保護回路との強調が容易になる効果がある。

【0013】

また、この発明の第3の観点による電圧制御形スイッチングデバイスのゲート駆動装置では、閾値電圧を持った半導体スイッチ素子を有し、検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路と、前記スイッチ出力に基づいて、前記電圧出力トランジスタをオフにするオフ制御電圧を発生するオフ制御回路を備え、前記オフ制御回路が、定電圧パルス出力を出力する電圧出力トランジスタの制御端子に、前記オフ制御電圧を供給するように構成したので、電圧制御形スイッチングデバイスのストレージ特性による遅れは回避できないものの、定電圧パルス出力を出力する電圧出力トランジスタを迅速にオフすることができ、電圧制御形スイッチングデバイスの他の保護回路との強調が容易になる効果がある。

【0014】

さらに、この発明の第4の観点による電圧制御形スイッチングデバイスのゲート駆動装置では、閾値電圧を持った半導体スイッチ素子を有し、検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときに、スイッチ出力を発生するスイッチ回路を備え、前記スイッチ回路は、定電圧パルス出力を出力する電圧出力トランジスタの制御端子に接続され、前記スイッチ出力に基づいて、前記制御端子に、前記電圧出力トランジスタをオフにするオフ制御電圧を発生させるので、出力トランジスタのストレージ特性による遅れは回避できないものの、定電圧パルス出力を出力する電圧出力トランジスタを迅速にオフすることができ、電圧制御形スイッチングデバイスの他の保護回路との強調が容易になる効果がある。

【発明を実施するための最良の形態】

【0015】

以下この発明のいくつかの実施の形態について、図面を参照して説明する。

【0016】

実施の形態1.

図1は、この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態1を示す電気回路図である。この実施の形態1のゲート駆動装置は、電圧制御形スイッチングデバイス1と、電流検出回路10と、ゲート制御回路20と、ゲート駆動回路30と、オフ制御回路60と、スイッチ回路70と、ゲート遮断回路80を有する。

【0017】

電圧制御形スイッチングデバイス1は、例えばパワー用IGBTであり、ゲートGとコレクタCとエミッタEを有し、さらに、センスエミッタEsも有する。コレクタCとエミッタEとの間には、保護ダイオード2が接続される。この保護ダイオード2のアノードAはエミッタEに、そのカソードKはコレクタCにそれぞれ接続される。コレクタCおよびエミッタEは、応用回路3に接続される。

【0018】

エミッタEは、共通電位CG、例えばグランド電位に直接接続され、センスエミッタEsは、電流検出回路10を通じて、共通電位CGに接続される。電圧制御形スイッチングデバイス1のエミッタEに出力電流Icが流れるときに、センスエミッタEsには、出力電流Icに比例したセンス電流Isが流れる。電流検出回路10は、センスエミッタEsと共通電位CGとの間に接続された検出抵抗11を有し、この検出抵抗11は、その両端に出力電流Icに比例した大きさの検出電圧VDを発生する。このようにセンスエミッタEsを有するIGBTを用い、センスエミッタEsに検出抵抗11を接続することにより、高速度で、出力電流Icに応じて大きさが変化する検出電圧VDを検出することができる。

【0019】

なお、電圧制御形スイッチングデバイス1には、センスエミッタEsを持たないIGBTを用いることもできる。この場合、検出抵抗11は、エミッタEに接続され、検出電圧VDを発生するように構成される。また、電圧制御形スイッチングデバイス1には、パワーMOSFETを使用することもできる。このパワーMOSFETは、ゲート、ドレイン、ソースを有し、ドレインとソースが応用回路3に接続される。ソースには、検出抵抗11が接続され、この検出抵抗11により、出力電流Icに応じて大きさが変化する検出電圧VDが発生される。

【0020】

ゲート制御回路20は、入力端子21、22、23と、出力端子24、25、26と、共通電位端子27を有する。入力端子21は制御信号入力端子28に接続され、この制御信号入力端子28から制御信号CSが供給される。入力端子22は、検出抵抗11のセンスエミッタEs側に接続されており、この入力端子22には、検出電圧VDが入力される。入力端子23は、スイッチングデバイス1のゲートGに接続され、そのゲート電圧Vgが入力される。共通電位端子27は、共通電位CGに直接接続される。ゲート制御回路20は、ゲート電圧Vgを監視しながら、制御信号CSに基づいて、出力端子24、25、26のそれぞれに、制御出力信号SA、SB、SCを発生し、また、検出電圧VDを監視することにより、スイッチングデバイス1に過電流異常が発生したときには、スイッチングデバイス1が故障しないように、ゲート駆動回路30を制御する。

【0021】

ゲート駆動回路30は、定電流駆動回路40と、定電圧駆動回路50を有する。定電流駆動回路40は、スイッチングデバイス1のゲートGに定電流パルス出力を供給する。この定電流駆動回路40は、電流出力トランジスタ41と、抵抗42、43、44と、制御トランジスタ45を含み、直流電源端子46と共通電位CGの間に接続される。直流電源端子46には、直流電圧+VDD1が供給される。電流出力トランジスタ41は、例えばPNP形バイポーラトランジスタQ1で構成される。このトランジスタQ1のコレクタCは、スイッチングデバイス1のゲートGに直接接続され、ゲートGに定電流パルス出力を供給する。トランジスタQ1のエミッタEは、抵抗42を通じて直流電源端子46に接続される。抵抗43、44および制御トランジスタ45は、直流電源端子46と共通電位CGとの間に直列に接続され、抵抗43、44の相互接続点にトランジスタQ1の制御端子、すなわちベースBが直接接続される。

【0022】

なお、電流出力トランジスタ41は、MOSFET、例えばPチャネルMOSFETで構成することもできる。この場合には、PチャネルMOSFETのソースが抵抗42を通じて直流電源端子46に接続され、そのドレインがスイッチングデバイス1のゲートGに接続され、その制御端子、すなわちゲートが抵抗43、44の相互接続点に直接接続される。

【0023】

制御トランジスタ45は、電流出力トランジスタ41を制御する。制御トランジスタ45は、例えばNチャネルMOSトランジスタQ2で構成される。このMOSトランジスタQ2のソースSは、共通電位CGに直接接続され、そのドレインDは、抵抗43、44を通じて直流電源端子46に接続され、またそのゲートGには、ゲート制御回路20の出力端子24から制御出力信号SAが供給される。

【0024】

制御出力信号SAがロウレベルであるときには、制御トランジスタ45はオフとなり、電流出力トランジスタ41もオフとなり、定電流パルス出力は供給されない。制御出力信号SAがハイレベルとなったときには、制御トランジスタ45がオンとなり、電流出力トランジスタ41にベース電流が流れるので、電流出力トランジスタ41もオンとなり、定電流パルス出力がスイッチングデバイス1のゲートGに供給される。

【0025】

定電圧駆動回路50は、スイッチングデバイス1のゲートGに定電圧出力を供給する。定電圧駆動回路50は、一対のスイッチ素子51、52と、一対の抵抗53、54を含み、直流電源端子55と共通電位CGとの間に接続される。一対の抵抗53、54の相互接続点は、スイッチングデバイス1のゲートGに直接接続され、抵抗53、54の相互接続点から、スイッチングデバイス1のゲートGに定電圧出力を供給する。直流電源端子55には、直流電圧+VDD2が供給される。スイッチ素子51と抵抗53は、直流電源端子55とゲートGとの間に直列に接続され、スイッチ素子52と抵抗54は、ゲートGと共通電位CGとの間に直列に接続される。スイッチ素子51、52は、MOSFETまたはバイポーラトランジスタにより構成される。

【0026】

スイッチ素子51には、ゲート制御回路20の出力端子25から制御出力信号SBが供給され、制御出力信号SBがロウレベルであるときに、スイッチ素子51はオンとなる。スイッチ素子52には、ゲート制御回路20の出力端子26から制御出力信号SCが供給され、制御出力信号SCがハイレベルであるときに、スイッチ素子52はオンとなる。制御出力信号SBがハイレベルであるときには、スイッチ素子51はオフとなり、また、制御出力信号SCがロウレベルであるときには、スイッチ素子52はオフとなる。定電圧駆動回路50は、スイッチ素子51がオンとなり、スイッチ素子52がオフとなったときに、直流電圧+VDD2から定電圧出力をスイッチングデバイス1のゲートGに供給する。

【0027】

オフ制御回路60は、定電流駆動回路40の電流出力トランジスタ41を強制的にオフ状態に制御する。電流出力トランジスタ41の動作は、制御トランジスタ45により制御されるが、オフ制御回路60は、制御トランジスタ45による制御とは関係なく、電流出力トランジスタ41の制御端子にオフ制御電圧VOFFを供給する。このオフ制御回路60は、半導体スイッチ素子61と、抵抗62、63を含み、直流電源端子64に接続される。半導体スイッチ素子61は、例えばPNP形バイポーラトランジスタQ3で構成され、そのコレクタCは、電流出力トランジスタ41の制御端子、すなわちトランジスタQ1のベースBに直接接続される。抵抗62、63は、互いに直列に接続され、スイッチ回路70と直列に、直流電源端子64と共通電位CGとの間に接続される。抵抗62、63の相互接続点に、トランジスタQ3のベースBが直接接続される。なお、電流出力トランジスタ41がMOSFETで構成される場合には、トランジスタQ3のコレクタCは、その制御端子、すなわちゲートに接続される。直流電源端子64には、直流電圧+VDD3が供給され、この直流電圧+VDD3は、定電流駆動回路40の直流電圧+VDD1に等しいか、またはそれよりも高い電圧とされる。すなわち、VDD3≧VDD1である。

【0028】

なお、半導体スイッチ素子61は、MOSFET、例えばPチャネルMOSFETで構成することもできる。この場合、MODFETのソースが直流電源端子64に、またそのドレインが、電流出力トランジスタ41の制御端子に接続され、そのゲートが抵抗62、63の相互接続点に直接接続される。

【0029】

オフ制御回路60は、スイッチングデバイス1に過電流異常が発生し、スイッチ回路70がロウレベルのスイッチ出力SOLを発生したときに、半導体スイッチ素子61がオンとなり、オフ制御電圧VOFFを発生し、このオフ制御電圧VOFFを電流出力トランジスタ41の制御端子に供給する。VDD3≧VDD1の関係にあるので、オフ制御電圧VOFFは電流出力トランジスタ41の制御端子に、そのエミッタEの電位以上の電位を与える。このオフ制御電圧VOFFは、電流出力トランジスタ41を強制的にオフにする電圧である。このオフ制御電圧VOFFにより、電流出力トランジスタ41のベース、エミッタ間の電圧は、VDD3=VDD1である場合には0ボルトになり、また、VDD3>VDD1の場合にはベースがエミッタよりも電位の高い逆電圧となる。

【0030】

定電流駆動回路40の制御トランジスタ45がオンし、電流出力トランジスタ41がオンしている状態で、このオフ制御電圧VOFFが、電流出力トランジスタ41の制御端子に与えられると、電流出力トランジスタ41は強制的にオフとされ、定電流パルス出力が停止される。なお、制御トランジスタ45がオフし、電流出力トランジスタ41がオフしている状態で、オフ制御回路60がオフ制御電圧VOFFを発生しても、この状態では、電流出力トランジスタ41がオフ状態にあるので、定電流駆動回路40に特別な影響はない。

【0031】

スイッチ回路70は、スイッチングデバイス1に過電流異常が発生し、検出電圧VDが閾値電圧VT1を越えたときに、オフ制御回路60にロウレベルのスイッチ出力SOLを供給する。このスイッチ回路70は、半導体スイッチ素子71と、抵抗72を含む。半導体スイッチ素子71は、例えばNPN形バイポーラトランジスタQ4により構成され、そのコレクタCは、オフ制御回路60の抵抗62、63を通じて、直流電源端子64に接続される。トランジスタQ4のエミッタEは直接共通電位CGに接続され、そのベースBは抵抗72を通じて、電流検出回路10における検出抵抗11のセンスエミッタEs側に接続される。

【0032】

半導体スイッチ素子71は、トランジスタQ4のベースBとエミッタEとの間に閾値電圧VT1を有し、検出電圧VDが閾値電圧VT1を越えたタイミングでオンとなり、そのコレクタCにロウレベルのスイッチ出力SOLを出力する。検出電圧VDが閾値電圧VT1以下であるときには、半導体スイッチ素子71はオフし、オフ制御回路60の半導体スイッチ素子61もオフとなるので、オフ制御回路60はオフ制御電圧VOFFを発生せず、定電流駆動回路40の動作に影響を与えることはない。

【0033】

なお、半導体スイッチ素子71は、MOSFET、例えばNチャネルMOSFETで構成することもできる。この場合、そのドレインが抵抗62、63を通じて、直流電源端子64に接続され、またそのソースが共通電位CGに接続され、そのゲートが抵抗72を通じて検出抵抗11のセンスエミッタEs側に接続される。このMOSFETでは、そのゲートの閾値電圧が、閾値電圧VT1となる。

【0034】

半導体スイッチ素子61、71には、高速でターンオン動作を行なうトランジスタQ3、Q4が使用される。これらのターンオン速度は、250nsec以下、理想的には、100nsec以下とすることが望ましい。トランジスタQ3、Q4は、具体的には、ディスクリートのトランジスタの中で、前記高いターンオン速度を持ったトランジスタを選択し、このディスクリートのトランジスタで構成される。しかし、ICで構成されたトランジスタの中に、前記高いターンオン速度を持ったものがあれば、このトランジスタを用いて構成することもできる。また、半導体スイッチ素子61については、制御トランジスタ45がオン状態にあるときに、半導体スイッチ素子61がオンに駆動されることが想定されるので、コレクタ電流と発熱を考慮して、構成するトランジスタを選択する。

【0035】

半導体スイッチ素子61、71は前述の高いターンオン速度を持つことにより、スイッチングデバイス1に過電流異常が発生した場合、検出電圧VDが閾値電圧VT1を超えたタイミングで、迅速に電流出力トランジスタ41をオフすることができる。この電流出力トランジスタ41のオフ動作の遅れは、トランジスタ41のストレージ特性による遅れのみとなり、判定の遅れや回路の応答の遅れにより、定電流パルス出力が継続するのを防止することができる。

【0036】

ゲート遮断回路80は、保護用半導体スイッチ素子81と抵抗82、83を含む。保護用半導体スイッチ素子81は、例えばNPN形バイポーラトランジスタQ5で構成され、そのコレクタCは抵抗82を通じてスイッチングデバイス1のゲートGに接続され、そのエミッタEは直接共通電位CGに接続され、そのベースBは抵抗83を通じて、電流検出回路10における検出抵抗11のセンスエミッタEs側に接続される。この保護用半導体スイッチ素子81は、トランジスタQ5のベースBとエミッタEとの間に閾値電圧VT2を有し、スイッチングデバイス1に過電流異常が発生して検出電圧VDが閾値電圧VT2を越えたときにオンとなり、ゲートGを共通電位CGに接続する。この保護用半導体スイッチ素子81のオンにより、スイッチングデバイス1のゲートGの電位は、抵抗82を通じて共通電位CGに放電され、低下するように制御される。

【0037】

なお、閾値電圧VT2は、半導体スイッチ素子71の閾値電圧VT1とほぼ同じか、それよりも少し高い値とされる。閾値電圧VT2が閾値電圧VT1より少し高い場合、またはVT2=VT1であっても、保護用スイッチ素子81が、半導体スイッチ素子71のターンオン速度よりも低い半導体スイッチ素子で構成されると、スイッチングデバイス1に過電圧異常が発生した場合、スイッチ回路70およびオフ制御回路60により、電流出力トランジスタ41にオフ制御電圧VOFFが与えられ、定電流パルス出力が停止された後で、ゲート遮断回路80が動作する。従来のゲート遮断回路は、定電流パルス出力が継続している状態で動作し、このためスイッチングデバイス1に、電流が流れ続ける恐れがあったが、このような問題も解消される。

【0038】

なお、スイッチ素子81は、MOSFET、例えばNチャネルMOSFETで構成することもできる。この場合、そのドレインが抵抗82を通じて、スイッチングデバイス1のゲートGに接続され、またそのソースが共通電位CGに接続され、そのゲートが抵抗82を通じて検出抵抗11のセンスエミッタEs側に接続される。このMOSFETでは、そのゲートの閾値電圧に基づいて、閾値電圧VT2が与えられる。

【0039】

さて、図1に示す実施の形態1の動作について説明する。先ず、ゲート駆動回路30における定電流駆動回路40と定電圧駆動回路50の動作について、図2を参照して説明する。図2は、制御信号CSがハイレベルとなった後に、ロウレベルに変化する場合の動作を示す。図2(a)は、電圧制御形スイッチングデバイス1のコレクタCとエミッタEとの間の電圧Vceと、出力電流Icの変化を示す。図2(b)は、スイッチングデバイス1のゲート電圧Vgの変化を示す。図2(c)は制御信号CSのレベル変化を示し、図2(d)(e)(f)は、それぞれ制御出力信号SA、SB、SCのレベル変化を示す。

【0040】

図2には、制御信号CSがハイレベルとなる制御期間T1と、制御信号CSがロウレベルとなる制御期間T2が示される。制御期間T1の直前には、制御信号CSがロウレベル、制御出力信号SAがロウレベル、制御出力信号SB、SCがともにハイレベルであり、制御出力信号SBがハイレベルであるため、定電圧駆動回路50におけるスイッチ素子51がオフしており、また、制御出力信号SCがハイレベルであるため、スイッチ素子52がオンしている状態にある。

【0041】

制御期間T1は、第1制御区間TAと第2制御区間TBを含み、第1制御区間TAから第2制御区間TBに切換えられる。第1制御区間TAでは、定電流駆動回路40が動作し、この定電流駆動回路40から、定電流パルス出力がスイッチングデバイス1のゲートGに供給される。第2制御区間TBでは、定電圧駆動回路50から定電圧出力が、スイッチングデバイス1のゲートGに供給される。定電流駆動回路40と定電圧駆動回路50を切換え動作させることにより、安定したゲート駆動が行なわれる。

【0042】

第1制御区間TAでは、制御出力信号SA、SBがハイレベル、制御出力信号SCがロウレベルとなる。この状態では、制御出力信号SAがハイレベルであるため、定電流駆動回路40の制御トランジスタ45がオンとなり、電流出力トランジスタ41もオンとなって、定電流駆動回路40が動作し、この定電流駆動回路40から定電流パルス出力がゲートGに供給される。この定電流パルス出力により、ゲートGのゲート電圧Vgは直線的に上昇し、このゲート電圧Vgが所定値Vth1に達したときに、スイッチングデバイス1はターンオン動作Tonを開始する。このターンオン動作Tonでは、出力電流Icが増加し、電圧Vceが低下する。ターンオン動作Tonが完了した後、スイッチングデバイス1はオン状態ONとなる。

【0043】

ゲート制御回路20は、入力端子23に入力されるゲート電圧Vgを監視し、このゲート電圧Vgが所定値Vg1に達したときに、第1制御区間TAから第2制御区間TBへの切換動作を行なう。第2制御区間TBでは、制御出力信号SA、SB、SCのすべてがロウレベルになる。この第2制御区間TBでは、制御出力信号SAがロウレベルとなるため、定電流駆動回路40の制御トランジスタ45がオフとなり、電流出力トランジスタ41もオフとなって、定電流パルス出力は停止する。第2制御区間TBでは、制御出力信号SB、SCがともにロウレベルとなるため、定電圧駆動回路50におけるスイッチ素子51がオンとなり、スイッチ素子52がオフとなる。このため、定電圧駆動回路50は、直流電圧+VDD2に基づいて定電圧をゲートGに供給する。

【0044】

制御期間T2では、制御信号CSがロウレベルとなり、制御出力信号SAはロウレベル、制御出力信号SB、SCはともにハイレベルとなる。制御出力信号SAがロウレベルであるため、定電流駆動回路40は動作しない。また、定電圧駆動回路50では、制御出力信号SB、SCがともにハイレベルであるため、スイッチ素子51はオフ、スイッチ素子52はオンとなる。このため、定電圧駆動回路50からの定電圧も停止し、ゲート電圧Vgはスイッチ素子52と抵抗54を通じて放電するため、低下する。このゲート電圧Vgの低下に伴ない、スイッチングデバイス1は、オン状態ONからターンオフ動作Toffの状態を経て、オフ状態OFFとなる。

【0045】

さて、ゲート駆動回路30の動作状態に拘わらず、スイッチングデバイス1に過電流異常が発生し、その出力電流Icが増大して、検出電圧VDが半導体スイッチ素子71の閾値VT1を越えたタイミングで、半導体スイッチ素子71は、ロウレベルのスイッチ出力SOLを発生し、オフ制御回路60の半導体スイッチ素子61がオフ制御電圧VOFFを、定電流駆動回路40における電流出力トランジスタ41の制御端子に供給する。第1制御区間TAにあって、定電流駆動回路40の電流出力トランジスタ41が定電流パルス出力を発生している状態で、検出電圧VDが閾値VT1を越えれば、半導体スイッチ素子71、61は共に高速のターンオン動作を行ない、電流出力トランジスタ41は強制的にオフ状態とされる。

【0046】

第1制御区間TA以外では、制御トランジスタ45がオフとなり、電流出力トランジスタ41もオフ状態にある。この状態でも検出電圧VDが閾値VT1を越えると、実施の形態1では、半導体スイッチ71、61は、同様に高速でターンオン動作を行ない、電流出力トランジスタ41の制御端子にオフ制御電圧VOFFを与えるが、この状態では電流出力トランジスタ41がオフ状態にあるので、オフ制御電圧VOFFは電流出力トランジスタ41に影響を与えない。第1制御区間TA以外でスイッチングデバイス1に過電流異常が発生したときには、検出電圧VDが閾値電圧VT2を越えたタイミングで、ゲート遮断回路80の保護用半導体スイッチ素子81がオンとなり、このゲート遮断回路80により、スイッチングデバイス1の保護が図られる。

【0047】

スイッチ回路70およびオフ制御回路60に加えてゲート遮断回路80を併用する実施の形態1では、第1制御区間TAにおいて、定電流駆動回路40が定電流パルス出力を出力している状態では、先ずスイッチ回路70およびオフ制御回路60により、電流出力トランジスタ41を強制的にオフ状態にし、定電流パルス出力を停止した後で、ゲート遮断回路80を動作させることにより、スイッチングデバイス1を、より高速度で過電流状態から復帰させることができる。

【0048】

実施の形態2.

図3は、この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態2を示す電気回路図である。

【0049】

この実施の形態2は、実施の形態1に対して、スイッチ出力延長回路90を追加したものである。その他は、実施の形態1と同じに構成される。スイッチ出力延長回路90は、スイッチ回路70の半導体スイッチ素子71と並列に接続される。このスイッチ出力延長回路90は、コンデンサ91と抵抗92を含み、これらを直列接続したもので、コンデンサ91の一端は半導体スイッチ素子71を構成するトランジスタQ4のエミッタEに、また抵抗92の一端は、そのコレクタCにそれぞれ接続される。

【0050】

コンデンサ91は、スイッチ回路70の半導体スイッチ素子71がオフしている状態において、直流電源端子64の直流電圧+VSS3により、抵抗62、63、92を通じて充電され、半導体スイッチ素子71がオンしたときに、抵抗92および半導体スイッチ素子71を通じて放電する。半導体スイッチ素子71がオフ状態に復帰すると、コンデンサ91は、抵抗62、63、92を通じて、直流電源端子64から再び充電されるようになり、半導体スイッチ素子71がオフした後に、所定時間に亘り、ロウレベルのスイッチ出力SOLを延長する。

【0051】

このように、コンデンサ91は、半導体スイッチ素子71がオフした後まで、ロウレベルのスイッチ出力SOLを所定時間延長する機能を持ち、電流出力トランジスタ41を強制的にオフする時間を延長する。このスイッチ出力延長回路90を設けることにより、定電流駆動回路40の電流出力トランジスタ41は、より長い時間に亘り強制的にオフとされるので、一度、スイッチ回路70によるスイッチングデバイス1の過電流保護が行なわれると、その過電流異常が解消した後でも、所定時間は保護動作を続けることが可能となり、他の保護回路との強調が容易となる。

【0052】

なお、スイッチ出力延長回路90には、コンデンサ91と抵抗92に代えて、コンデンサと抵抗により動作時間を設定する単安定マルチバイブレータ回路を用いることもでき、この単安定マルチバイブレータ回路をIC化することもできる。

【0053】

実施の形態3.

図4は、この発明による電圧制御形スイッチングデバイスの実施の形態3を示す電気回路図である。この実施の形態3は、実施の形態1における定電流駆動回路40を、定電流駆動回路140に置き換えたものである。その他は、実施の形態1と同じに構成される。

【0054】

実施の形態3で使用される定電流駆動回路140は、カレントミラー回路141と、定電流回路142と、定電流制御回路143を含む。定電流制御回路143に、ゲート制御回路20の出力端子24から制御出力信号SAが供給される。カレントミラー回路141は、定電流駆動トランジスタ141aと、この定電流駆動トランジスタ141aとほぼ同じ特性を持ち、互いに並列に接続された電流出力トランジスタ群141bで構成される。定電流駆動トランジスタ141aは、例えばPNP形バイポーラトランジスタQ11で構成され、電流出力トランジスタ群141bの各トランジスタも、例えば同じPNP形バイポーラトランジスタQ12で構成される。

【0055】

トランジスタQ11のエミッタEは、直流電圧+VDD1が印加される直流電源端子46に直接接続され、そのコレクタCは定電流回路142を通じて共通電位CGに接続され、また、そのベースBに接続される。トランジスタQ11の制御端子、すなわちベースBは、各トランジスタQ12の制御端子、すなわちベースBに共通接続される。各トランジスタQ12のエミッタEは、互いに共通接続され、直流電源端子46に直接接続される。各トランジスタQ12のコレクタCも互いに共通接続され、スイッチングデバイス1のゲートGに直接接続される。

【0056】

定電流回路142は、トランジスタQ11に流れる定電流値を設定するもので、この定電流値は、定電流制御回路143で決定される。この定電流制御回路143は、ゲート制御回路20の制御出力信号SAによって駆動され、制御出力信号SAがハイレベルになったときには、定電流制御回路143が駆動され、各トランジスタQ12にも、それぞれトランジスタQ11と同じ電流が流れるので、トランジスタQ11に流れる定電流を、トランジスタQ12の数だけ加え合わせた電流値の定電流パルス出力が,スイッチングデバイス1のゲートGに供給される。

【0057】

オフ制御回路60の半導体スイッチ素子61を構成するトランジスタQ3のコレクタCは、トランジスタQ11および各トランジスタQ12の制御端子、すなわちベースBに直接接続される。このトランジスタQ3は、スイッチ回路70からロウレベルのスイッチ出力SOLを受けたときに、実施の形態1と同様に、トランジスタQ11、Q12の各ベースBにオフ制御電圧VOFFを与える。このオフ制御電圧VOFFは、定電流駆動回路140の電流出力トランジスタ群141bがスイッチングデバイス1のゲートGに定電流パルス出力を供給している状態で、各トランジスタQ11、Q12を強制的にオフ状態とし、定電流パルス出力を停止する。この実施の形態3でも、実施の形態1と同じ効果が得られる。

【0058】

実施の形態4.

図5は、この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態4を示す電気回路図である。この実施の形態4は、実施の形態3に対して、図3に示すスイッチ出力延長回路90を追加したもである。その他は、実施の形態3と同じに構成される。

【0059】

実施の形態4のスイッチ出力延長回路90は、実施の形態2と同じに構成され、それと同じ作用を行なうので、実施の形態2と同じ効果を得ることができる。

【0060】

実施の形態5.

図6は、この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態5を示す電気回路図である。この実施の形態5では、実施の形態1における定電流駆動回路40が定電流駆動回路240に置き換えられ、また実施の形態1におけるオフ制御回路60が削除される。その他は、実施の形態1と同じに構成される。

【0061】

実施の形態5で使用される定電流駆動回路240は、電流出力トランジスタ241と、抵抗242、243、244と、定電流制御回路245を有し、定電流制御回路245には、ゲート制御回路20の出力端子24から制御出力信号SAが供給される。電流出力トランジスタ241は、例えばNPN形バイポーラトランジスタQ13で構成される。このトランジスタQ13のコレクタCは、直流電源端子46に直接接続され、そのエミッタEは、抵抗242を通じて、スイッチングデバイス1のゲートGに接続され、このエミッタEから定電流パルス出力がゲートGに供給される。電流出力トランジスタ241の制御端子、すなわちトランジスタQ13のベースBは、抵抗243、244の相互接続点に接続される。

【0062】

定電流制御回路245は、抵抗243を通じて電流出力トランジスタ241の制御端子、すなわちトランジスタQ13のベースBに接続される。この定電流制御回路245は、フィードバック制御を行なう2つの比較回路COM1、COM2を含む。比較回路COM2は、スイッチングデバイス1のゲートGの電圧Vgと、トランジスタQ13のエミッタEの電圧との差電圧を出力し、また、比較回路COM1は、比較回路COM2から出力される差電圧と、定電流設定値入力との偏差を出力する。定電流制御回路245は、制御出力信号SAがハイレベルであるときに動作し、抵抗243を通じて、比較回路COM1から出力される偏差を電流出力トランジスタ241の制御端子、すなわちトランジスタQ13のベースBに供給し、フィードバック制御を行ないながら、電流出力トランジスタ241のエミッタEから、定電流パルス出力をゲートGへ供給する。トランジスタQ13は、エミッタフォロアとして動作し、定電流パルス出力をゲートGに供給する。制御出力信号SAがロウレベルであるときには、定電流制御回路245は動作せず、定電流パルス出力は停止する。

【0063】

スイッチ回路70の半導体スイッチ素子71を構成するトランジスタQ4のコレクタCは、抵抗244を通じて、電流出力トランジスタ241の制御端子、すなわちトランジスタQ13のベースBに直接接続される。実施の形態5では、制御出力信号SAがハイレベルにあるときに、スイッチ回路70は、定電流制御回路245から抵抗243、244を通じて給電を受けるが、制御出力信号SAがロウレベルであるときには、スイッチ回路70には給電されない。

【0064】

実施の形態5では、制御出力信号SAがハイレベルにあり、電流出力トランジスタ241がスイッチングデバイス1のゲートGに定電流パルス出力を供給している状態において、スイッチングデバイス1に過電流異常が発生し、検出電圧VDが閾値電圧VT1を越えたタイミングで、スイッチ回路70はロウレベルのスイッチ出力SOLを発生する。このロウレベルのスイッチ出力SOLにより、抵抗243から抵抗244および半導体スイッチ素子71を通じて共通電位CGに至る回路に電流が流れ、抵抗243、244の相互接続点にオフ制御電圧VOFFが発生する。

【0065】

実施の形態5では、抵抗244は、抵抗243に比べて充分小さな抵抗値とされ、オフ制御電圧VOFFは、スイッチングデバイス1の閾値電圧Vth1以下とされる。この閾値電圧Vth1は、スイッチングデバイス1に定格電流の0.01%の電流が流れるときのゲート電圧Vgの値とされる。電流出力トランジスタ241を構成するトランジスタQ13のエミッタEには、ゲート電圧Vgが印加されており、このゲート電圧Vgは、第1制御区間TAの殆どの期間を通じて、閾値電圧Vth1よりも大きい。したがって、第1制御区間TAの殆どの期間において、オフ制御電圧VOFFが発生したタイミングでは、トランジスタQ13のベースBとエミッタEの間には、ベースB側の電圧がエミッタE側の電圧よりも小さい逆電圧が印加され、電流出力トランジスタ241は強制的にオフ状態とされる。

【0066】

このように、実施の形態5では、第1制御区間TAにおいて、電流出力トランジスタ241が定電流パルス出力を発生している状態で、オフ制御電圧VOFFが発生した場合には、電流出力トランジスタ241が強制的にオフとされ、定電流パルス出力が停止される。半導体スイッチ素子71は、検出電圧VDが閾値電圧VT1を越えたタイミングで、高いターンオン速度でロウレベルのスイッチ出力SOLを発生するので、電流出力トランジスタ241は迅速に定電流パルス出力を停止し、定電流パルス出力が継続するのを防止する。第2制御区間TBおよび制御期間T2では、制御出力信号SAがロウレベルとなり、定電流制御回路245が動作しないので、スイッチ回路70への給電も行なわれず、スイッチ回路70は動作しない。

【0067】

なお、電流出力トランジスタ241は、MOSFET,例えばNチャネルMOSFETで構成することもできる。この場合、MOSFETのドレインは直流電源端子46に直接接続され、そのソースは抵抗242を通じて、スイッチングデバイス1のゲートGに接続され、また、その制御端子、すなわちゲートは、抵抗243、244の相互接続点に直接接続される。

【0068】

実施の形態6.

図7は、この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態6を示す電気回路図である。この実施の形態6では、実施の形態1におけるゲート駆動回路30が、ゲート駆動回路300に置き換えられ、また、ゲート制御回路20では、入力端子23と出力端子25が削除される。このゲート制御回路20は、出力端子24から制御出力信号SAを、また、出力端子26から制御出力信号SCをそれぞれゲート駆動回路300に供給するように構成される。その他は、実施の形態1と同じに構成される。

【0069】

実施の形態6で使用されるゲート駆動回路300は、定電圧駆動回路340と、ゲートオフ回路350を有する。定電圧駆動回路340は、電圧制御形スイッチングデバイス1のゲートGに定電圧パルス出力を供給する。ゲートオフ回路350は、スイッチングデバイス1のゲートGを共通電位CGに接続し、スイッチングデバイス1をオフさせる。

【0070】

定電圧駆動回路340は、電圧出力トランジスタ341と、抵抗342、343、344と、インバータ回路345を含む。電圧出力トランジスタ341は、例えばPチャネルMOSFETQ14で構成される。このMOSFETQ14は、ソースSとドレインDとゲートGを有し、ソースSは、直流電源端子64に直接接続され、ドレインDは、抵抗342を通じて、スイッチングデバイス1のゲートGに接続される。電圧出力トランジスタ341の制御端子は、MOSFETQ13のゲートGであり、これは抵抗343、344の相互接続点に直接接続される。

【0071】

なお、電圧出力トランジスタ341は、バイポーラトランジスタ、例えばPNP形バイポーラトランジスタで構成することもできる。この場合、PNP形バイポーラトランジスタのエミッタが直流電源端子64に直接接続され、そのコレクタが抵抗342を通じてスイッチングデバイス1のゲートGに接続され、そのベースが抵抗343、344の相互接続点に直接接続される。

【0072】

抵抗343、344は直列に接続され、インバータ回路345の出力に接続される。インバータ回路345は、ロジックICで構成され、その入力には、ゲート制御回路20の出力端子24から制御出力信号SAが供給される。インバータ回路345は、制御出力信号SAを反転した制御出力信号ISAを出力する。

【0073】

ゲートオフ回路350は、スイッチ素子351と抵抗352を含み、スイッチングデバイス1のゲートGと共通電位CGとの間に接続される。スイッチ素子351と抵抗352は互いに直列に接続される。スイッチ素子351は、MOSFETまたはバイポーラトランジスタにより構成され、このスイッチ素子351には、ゲート制御回路回路20の出力端子26から制御出力信号SCが供給され、この制御出力信号SCがハイレベルであるときにスイッチ素子351はオンとなり、また、制御出力信号SCがロウレベルであるときにはスイッチ素子351はオフとなる。

【0074】

オフ制御回路60は、実施の形態1と同じに構成され、半導体スイッチ素子61を構成するトランジスタQ3のコレクタCは、電圧出力トランジスタ341の制御端子、すなわちMOSFETQ14のゲートGに直接接続され、オフ制御電圧VOFFを電圧出力トランジスタ341の制御端子に供給する。スイッチ回路70は、実施の形態1と同じに構成され、スイッチングデバイス1に過電流異常が発生し、検出電圧VDが閾値電圧VT1を越えたタイミングで、半導体スイッチ素子71がオンとなり、ロウレベルのスイッチ出力SOLを発生し、このスイッチ出力SOLにより、オフ制御回路60の半導体スイッチ素子61がオフ制御電圧VOFFを発生する。半導体スイッチ素子61、71は、高速のターンオン速度を持ち、検出電圧VDが閾値電圧VT1を越えたタイミングで、迅速にオフ制御電圧VOFFを発生する。定電圧駆動回路340の電圧出力トランジスタ341が、スイッチングデバイス1のゲートGに定電圧パルス出力を供給している状態において、オフ制御電圧VOFFは電圧出力トランジスタ341を強制的にオフ状態とする。

【0075】

ゲート遮断回路80も実施の形態1と同じに構成され、検出電圧VDが閾値電圧VT2を越えたときに、スイッチングデバイス1のゲートGを共通電位CGに接続し、ゲートGのゲート電圧Vgを低下させる。

【0076】

さて、図7に示す実施の形態6の動作について説明する。先ず、ゲート駆動回路300における定電圧駆動回路340とゲートオフ回路350の動作について、図8を参照して説明する。図8は、図2と同様に、制御信号CSがハイレベルとなった後に、ロウレベルに変化する場合の動作を示す。図8(a)は、電圧制御形スイッチングデバイス1のコレクタCとエミッタEとの間の電圧Vceと、出力電流Icの変化を示す。図8(b)は、スイッチングデバイス1のゲート電圧Vgの変化を示す。図8(c)は制御信号CSのレベル変化を示し、図8(d)(e)は、それぞれ制御出力信号SA、SCのレベル変化を示す。

【0077】

図8にも、制御信号CSがハイレベルとなる制御期間T1と、制御信号CSがロウレベルとなる制御期間T2が示される。制御期間T1の直前には、制御信号CSがロウレベル、制御出力信号SAがロウレベル、制御出力信号SCがハイレベルであり、制御出力信号SCがハイレベルであるため、スイッチ素子351がオンしている状態にある。

【0078】

制御期間T1では、定電圧駆動回路340が動作し、この定電圧駆動回路340から、定電圧パルス出力がスイッチングデバイス1のゲートGに供給される。制御期間T1では、制御出力信号SAがハイレベル、制御出力信号SCがロウレベルとなる。この状態では、制御出力信号SAがハイレベルであるため、定電圧駆動回路340のインバータ回路345から出力される反転された制御出力信号ISAがロウレベルとなり、電圧出力トランジスタ341がオンとなって、定電圧駆動回路340が動作し、この定電圧駆動回路340から定電圧パルス出力が、スイッチングデバイス1のゲートGに供給される。この定電圧パルス出力により、スイッチングデバイス1のゲート電圧VgはCR充電波形状に上昇し、このゲート電圧Vgが閾値電圧Vth1に達したときに、スイッチングデバイス1はターンオン動作Tonを開始する。このターンオン動作Tonでは、出力電流Icが増加し、電圧Vceが低下する。ターンオン動作Tonが完了した後、スイッチングデバイス1はオン状態ONとなる。

【0079】

制御期間T2では、制御信号CSがロウレベルとなり、制御出力信号SAがロウレベル、制御出力信号SCがハイレベルとなる。制御出力信号SAがロウレベルであるため、定電圧駆動回路340は動作しない。また、ゲートオフ回路350では、制御出力信号SCがハイレベルであるため、スイッチ素子351はオンとなる。このため、ゲート電圧Vgはスイッチ素子351と抵抗352を通じて放電するため、低下する。このゲート電圧Vgの低下に伴ない、スイッチングデバイス1は、オン状態ONからターンオフ動作Toffの状態を経て、オフ状態OFFとなる。

【0080】

さて、ゲート駆動回路300の動作状態に拘わらず、スイッチングデバイス1に過電流異常が発生し、その出力電流Icが増大して、検出電圧VDが半導体スイッチ素子71の閾値VT1を越えたタイミングで、半導体スイッチ素子71は、ロウレベルのスイッチ出力SOLを発生し、オフ制御回路60の半導体スイッチ素子61がオフ制御電圧VOFFを、定電圧駆動回路340における電圧出力トランジスタ41の制御端子に供給する。制御期間T1にあって、定電圧駆動回路340の電圧出力トランジスタ341が定電圧パルス出力を発生している状態で、検出電圧VDが閾値VT1を越えれば、半導体スイッチ素子71、61は共に高速のターンオン動作を行ない、電圧出力トランジスタ341を強制的にオフ状態とする。

【0081】

制御期間T2では、電圧出力トランジスタ341はオフ状態にある。この状態でも検出電圧VDが閾値VT1を越えると、実施の形態6では、半導体スイッチ71、61は、同様に高速でターンオン動作を行ない、電圧出力トランジスタ341の制御端子にオフ制御電圧VOFFを与えるが、この状態では電圧出力トランジスタ341がオフ状態にあるので、オフ制御電圧VOFFは電圧出力トランジスタ341に影響を与えない。制御期間T2でスイッチングデバイス1の過電流異常が発生したときには、検出電圧VDが閾値電圧VT2を越えたタイミングで、ゲート遮断回路80の保護用半導体スイッチ素子81がオンとなり、このゲート遮断回路80により、スイッチングデバイス1の保護が図られる。

【0082】

スイッチ回路70およびオフ制御回路60に加えてゲート遮断回路80を併用する実施の形態6では、制御期間T1において、定電圧駆動回路340が定電圧パルス出力を出力している状態では、先ずスイッチ回路70およびオフ制御回路60により、電圧出力トランジスタ341を強制的にオフ状態にし、定電圧パルス出力を停止した後で、ゲート遮断回路80を動作させることにより、スイッチングデバイス1を、より高速度で過電流状態から復帰させることができる。

【0083】

実施の形態7.

図9は、この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態7を示す電気回路図である。この実施の形態7は、実施の形態6に対して、図3に示すスイッチ出力延長回路90を追加したもである。その他は、実施の形態6と同じに構成される。実施の形態7のスイッチ出力延長回路90は、実施の形態2と同じに構成され、それと同じ作用を行なうので、実施の形態2と同じ効果を得ることができる。

【0084】

実施の形態8.

図10は、この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態8を示す電気回路図である。この実施の形態8では、実施の形態6における定電圧駆動回路340が定電圧駆動回路440に置き換えられ、また実施の形態6におけるオフ制御回路60が削除される。その他は、実施の形態6と同じに構成される。

【0085】

実施の形態8で使用される定電圧駆動回路440は、電圧出力トランジスタ441と、抵抗442、443、444を有し、抵抗443には、ゲート制御回路20の出力端子24から制御出力信号SAが供給される。電圧出力トランジスタ441は、例えばNPN形バイポーラトランジスタQ15で構成される。このトランジスタQ15のコレクタCは、直流電源端子46に直接接続され、そのエミッタEは、抵抗442を通じて、スイッチングデバイス1のゲートGに接続され、このエミッタEから定電圧パルス出力がゲートGに供給される。

【0086】

電圧出力トランジスタ441の制御端子、すなわちトランジスタQ15のベースBは、抵抗443、444の相互接続点に接続される。トランジスタQ15のベースBには、抵抗443を通じて、制御出力信号SAが供給される。定電圧駆動回路440は、制御出力信号SAがハイレベルであるときに動作する。制御出力信号SAがハイレベルにあるときには、抵抗443を通じて、電圧出力トランジスタ441にベース電流が流れ、電圧出力トランジスタ441のエミッタEから、定電圧パルス出力をスイッチングデバイス1のゲートGに供給する。制御出力信号SAがロウレベルであるときには、定電圧駆動回路440は動作せず、定電圧パルス出力は停止する。

【0087】

スイッチ回路70の半導体スイッチ素子71を構成するトランジスタQ4のコレクタCは、抵抗444を通じて、電圧出力トランジスタ441の制御端子、すなわちトランジスタQ15のベースBに接続される。実施の形態8では、制御出力信号SAがハイレベルにあるときに、スイッチ回路70は、制御出力信号SAから抵抗443、444を通じて給電を受けるが、制御出力信号SAがロウレベルであるときには、スイッチ回路70には給電されない。

【0088】

実施の形態8では、制御出力信号SAがハイレベルにあり、電圧出力トランジスタ441がスイッチングデバイス1のゲートGに定電圧パルス出力を供給している状態において、スイッチングデバイス1に過電流異常が発生し、検出電圧VDが閾値電圧VT1を越えたタイミングで、スイッチ回路70はロウレベルのスイッチ出力SOLを発生する。このロウレベルのスイッチ出力SOLにより、抵抗443から抵抗444および半導体スイッチ素子71を通じて共通電位CGに至る回路に電流が流れ、抵抗443、444の相互接続点にオフ制御電圧VOFFが発生する。

【0089】

実施の形態8では、抵抗444は、抵抗443に比べて充分小さな抵抗値とされ、オフ制御電圧VOFFは、スイッチングデバイス1の閾値電圧Vth1以下とされる。この閾値電圧Vth1は、スイッチングデバイス1に定格電流の0.01%の電流が流れるときのゲート電圧Vgの値とされる。電圧出力トランジスタ441を構成するトランジスタQ15のエミッタEには、ゲート電圧Vgが印加されており、このゲート電圧Vgは、期間T1の殆どの期間を通じて、閾値電圧Vth1よりも大きい。したがって、期間T1の殆どの期間において、オフ制御電圧VOFFが発生したタイミングでは、トランジスタQ15のベースBとエミッタEの間には、ベースB側の電圧がエミッタE側の電圧よりも小さい逆電圧が印加され、電圧出力トランジスタ441は強制的にオフ状態とされる。

【0090】

このように、実施の形態8では、制御期間T1において、電圧出力トランジスタ441が定電圧パルス出力を発生している状態で、オフ制御電圧VOFFが発生した場合には、電圧出力トランジスタ441が強制的にオフとされ、定電圧パルス出力が停止される。半導体スイッチ素子71は、検出電圧VDが閾値電圧VT1を越えたタイミングで、高いターンオン速度でロウレベルのスイッチ出力SOLを発生するので、電圧出力トランジスタ441は迅速に定電圧パルス出力を停止し、定電圧パルス出力が継続するのを防止する。制御期間T2では、制御出力信号SAがロウレベルとなり、スイッチ回路70への給電も行なわれず、スイッチ回路70は動作しない。

【0091】

なお、電圧出力トランジスタ441は、MOSFET,例えばNチャネルMOSFETで構成することもできる。この場合、MOSFETのドレインは直流電源端子46に直接接続され、そのソースは抵抗442を通じて、スイッチングデバイス1にゲートGに接続され、また、その制御端子、すなわちゲートは、抵抗443、444の相互接続点に直接接続される。

【産業上の利用可能性】

【0092】

この発明による電圧制御形スイッチングデバイスのゲート駆動装置は、各種の電圧制御形スイッチングデバイス、例えばIGBT、MOSFETなどに利用される。

【図面の簡単な説明】

【0093】

【図1】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態1を示す電気回路図である。

【図2】実施の形態1の動作説明用タイミング図である。

【図3】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態2を示す電気回路図である。

【図4】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態3を示す電気回路図である。

【図5】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態4を示す電気回路図である。

【図6】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態5を示す電気回路図である。

【図7】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態6を示す電気回路図である。

【図8】実施の形態6の動作説明用タイミング図である。

【図9】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態7を示す電気回路図である。

【図10】この発明による電圧制御形スイッチングデバイスのゲート駆動装置の実施の形態8を示す電気回路図である。

【符号の説明】

【0094】

1:電圧制御形スイッチングデバイス、10:電流検出回路、20:ゲート制御回路、

30.300:ゲート駆動回路、40、140、240:定電流駆動回路、

41、141b、241:電流出力トランジスタ、60:オフ制御回路、

70:スイッチ回路、71:半導体スイッチ素子、80:ゲート遮断回路、

81:保護用半導体スイッチ素子、90:スイッチ出力延長回路、91:コンデンサ、

340、440:定電圧駆動回路、341、441:電圧出力トランジスタ。

【特許請求の範囲】

【請求項1】

定電流パルス出力を発生する電流出力トランジスタを含む定電流駆動回路を用い、前記定電流パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、

前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、

閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路と、

前記スイッチ出力に基づいて、前記電流出力トランジスタをオフにするオフ制御電圧を発生するオフ制御回路を備え、

前記オフ制御回路が、電流出力トランジスタの制御端子に、前記オフ制御電圧を供給するように構成したことを特徴とする電圧駆動形スイッチングデバイスのゲート駆動装置。

【請求項2】

請求項1記載の電圧制御形スイッチングデバイスのゲート駆動装置であって、さらに、コンデンサを含むスイッチ出力延長回路を備え、前記スイッチ出力延長回路は、前記スイッチ回路に接続され、前記スイッチ出力を延長することを特徴とする電圧制御形スイッチングデバイスのゲート駆動装置。

【請求項3】

請求項1記載の電圧制御形スイッチングデバイスのゲート駆動装置であって、さらに、前記電圧制御形スイッチングデバイスのゲートに接続されたゲート遮断回路を備え、前記ゲート遮断回路は、閾値電圧を持った保護用半導体スイッチ素子を含み、前記保護用半導体スイッチ素子にも前記検出電圧を供給し、前記検出電圧が前記保護用半導体スイッチ素子の閾値電圧を越えたときに、前記保護用半導体スイッチ素子により、前記電圧制御形スイッチングデバイスのゲートを共通電位に接続することを特徴とする電圧制御形スイッチングデバイスのゲート駆動装置。

【請求項4】

定電流パルス出力を発生する電流出力トランジスタを含む定電流駆動回路を用い、前記定電流パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、

前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、

閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときに、スイッチ出力を発生するスイッチ回路を備え、

前記スイッチ回路は、前記電流出力トランジスタの制御端子に接続され、前記スイッチ出力に基づいて、前記制御端子に、前記電流出力トランジスタをオフにするオフ制御電圧を発生させることを特徴とする電圧制御形スイッチングデバイスのゲート駆動装置。

【請求項5】

定電圧パルス出力を発生する電圧出力トランジスタを含む定電圧駆動回路を用い、前記定電圧パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、

前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、

閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路と、

前記スイッチ出力に基づいて、前記電圧出力トランジスタをオフにするオフ制御電圧を発生するオフ制御回路を備え、

前記オフ制御回路が、前記電圧出力トランジスタの制御端子に、前記オフ制御電圧を供給するように構成したことを特徴とする電圧制御形スイッチングデバイスのゲート駆動装置。

【請求項6】

請求項5記載の電圧制御形スイッチングデバイスのゲート駆動装置であって、さらに、コンデンサを含むスイッチ出力延長回路を備え、前記スイッチ出力延長回路は、前記スイッチ回路に接続され、前記スイッチ出力を延長することを特徴とする電圧制御形スイッチングデバイスのゲート駆動装置。

【請求項7】

請求項5記載の電圧制御形スイッチングデバイスのゲート駆動装置であって、さらに、前記電圧制御形スイッチングデバイスのゲートに接続されたゲート遮断回路を備え、前記ゲート遮断回路は、閾値電圧を持った保護用半導体スイッチ素子を含み、前記保護用半導体スイッチ素子にも前記検出電圧を供給し、前記検出電圧が前記保護用半導体スイッチ素子の閾値電圧を越えたときに、前記保護用半導体スイッチ素子により、前記電圧制御形スイッチングデバイスのゲートを共通電位に接続することを特徴とする電圧制御形スイッチングデバイスのゲート駆動装置。

【請求項8】

定電圧パルス出力を発生する電圧出力トランジスタを含む定電圧駆動回路を用い、前記定電圧パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、

前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、

閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときに、スイッチ出力を発生するスイッチ回路を備え、

前記スイッチ回路は、前記電圧出力トランジスタの制御端子に接続され、前記スイッチ出力に基づいて、前記制御端子に、前記電圧出力トランジスタをオフにするオフ制御電圧を発生させることを特徴とする電圧制御形スイッチングデバイスのゲート駆動装置。

【請求項1】

定電流パルス出力を発生する電流出力トランジスタを含む定電流駆動回路を用い、前記定電流パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、

前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、

閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路と、

前記スイッチ出力に基づいて、前記電流出力トランジスタをオフにするオフ制御電圧を発生するオフ制御回路を備え、

前記オフ制御回路が、電流出力トランジスタの制御端子に、前記オフ制御電圧を供給するように構成したことを特徴とする電圧駆動形スイッチングデバイスのゲート駆動装置。

【請求項2】

請求項1記載の電圧制御形スイッチングデバイスのゲート駆動装置であって、さらに、コンデンサを含むスイッチ出力延長回路を備え、前記スイッチ出力延長回路は、前記スイッチ回路に接続され、前記スイッチ出力を延長することを特徴とする電圧制御形スイッチングデバイスのゲート駆動装置。

【請求項3】

請求項1記載の電圧制御形スイッチングデバイスのゲート駆動装置であって、さらに、前記電圧制御形スイッチングデバイスのゲートに接続されたゲート遮断回路を備え、前記ゲート遮断回路は、閾値電圧を持った保護用半導体スイッチ素子を含み、前記保護用半導体スイッチ素子にも前記検出電圧を供給し、前記検出電圧が前記保護用半導体スイッチ素子の閾値電圧を越えたときに、前記保護用半導体スイッチ素子により、前記電圧制御形スイッチングデバイスのゲートを共通電位に接続することを特徴とする電圧制御形スイッチングデバイスのゲート駆動装置。

【請求項4】

定電流パルス出力を発生する電流出力トランジスタを含む定電流駆動回路を用い、前記定電流パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、

前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、

閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときに、スイッチ出力を発生するスイッチ回路を備え、

前記スイッチ回路は、前記電流出力トランジスタの制御端子に接続され、前記スイッチ出力に基づいて、前記制御端子に、前記電流出力トランジスタをオフにするオフ制御電圧を発生させることを特徴とする電圧制御形スイッチングデバイスのゲート駆動装置。

【請求項5】

定電圧パルス出力を発生する電圧出力トランジスタを含む定電圧駆動回路を用い、前記定電圧パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、

前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、

閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときにスイッチ出力を発生するスイッチ回路と、

前記スイッチ出力に基づいて、前記電圧出力トランジスタをオフにするオフ制御電圧を発生するオフ制御回路を備え、

前記オフ制御回路が、前記電圧出力トランジスタの制御端子に、前記オフ制御電圧を供給するように構成したことを特徴とする電圧制御形スイッチングデバイスのゲート駆動装置。

【請求項6】

請求項5記載の電圧制御形スイッチングデバイスのゲート駆動装置であって、さらに、コンデンサを含むスイッチ出力延長回路を備え、前記スイッチ出力延長回路は、前記スイッチ回路に接続され、前記スイッチ出力を延長することを特徴とする電圧制御形スイッチングデバイスのゲート駆動装置。

【請求項7】

請求項5記載の電圧制御形スイッチングデバイスのゲート駆動装置であって、さらに、前記電圧制御形スイッチングデバイスのゲートに接続されたゲート遮断回路を備え、前記ゲート遮断回路は、閾値電圧を持った保護用半導体スイッチ素子を含み、前記保護用半導体スイッチ素子にも前記検出電圧を供給し、前記検出電圧が前記保護用半導体スイッチ素子の閾値電圧を越えたときに、前記保護用半導体スイッチ素子により、前記電圧制御形スイッチングデバイスのゲートを共通電位に接続することを特徴とする電圧制御形スイッチングデバイスのゲート駆動装置。

【請求項8】

定電圧パルス出力を発生する電圧出力トランジスタを含む定電圧駆動回路を用い、前記定電圧パルス出力を電圧制御形スイッチングデバイスのゲートに供給して、それを駆動する電圧制御形スイッチングデバイスのゲート駆動装置であって、

前記電圧制御形スイッチングデバイスの出力電流を検出し、この出力電流に応じて大きさが変化する検出電圧を発生する電流検出回路と、

閾値電圧を持った半導体スイッチ素子を有し、前記検出電圧が前記半導体スイッチ素子の閾値電圧を越えたときに、スイッチ出力を発生するスイッチ回路を備え、

前記スイッチ回路は、前記電圧出力トランジスタの制御端子に接続され、前記スイッチ出力に基づいて、前記制御端子に、前記電圧出力トランジスタをオフにするオフ制御電圧を発生させることを特徴とする電圧制御形スイッチングデバイスのゲート駆動装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2009−95166(P2009−95166A)

【公開日】平成21年4月30日(2009.4.30)

【国際特許分類】

【出願番号】特願2007−264609(P2007−264609)

【出願日】平成19年10月10日(2007.10.10)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成21年4月30日(2009.4.30)

【国際特許分類】

【出願日】平成19年10月10日(2007.10.10)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]