電圧検出回路、それを用いた温度検出回路、電子機器

【課題】回路面積、消費電力を低減するとともに、正しい電圧比較が可能な電圧比較回路を提供する。

【解決手段】抵抗ストリング10は、直列に接続された複数の抵抗の接続点に設けられた各タップに電圧を発生する。セレクタ12は、複数のスイッチを含み、ひとつのスイッチがオンした状態において、当該スイッチが接続されるタップの電圧を出力する。コンパレータ14は、入力電圧VINをセレクタ12の出力電圧と比較する。メモリ16_iは、それぞれがしきい値電圧VTHiごとに設けられ、書き込み信号WRITEiに応答してコンパレータ14の出力SCMPを格納して検出信号Siを生成する。シーケンサ20は、N個のメモリ16_1〜16_Nからの検出信号S1〜SNを受け、セレクタ12の複数のスイッチを制御するとともに、書き込み信号を生成する。

【解決手段】抵抗ストリング10は、直列に接続された複数の抵抗の接続点に設けられた各タップに電圧を発生する。セレクタ12は、複数のスイッチを含み、ひとつのスイッチがオンした状態において、当該スイッチが接続されるタップの電圧を出力する。コンパレータ14は、入力電圧VINをセレクタ12の出力電圧と比較する。メモリ16_iは、それぞれがしきい値電圧VTHiごとに設けられ、書き込み信号WRITEiに応答してコンパレータ14の出力SCMPを格納して検出信号Siを生成する。シーケンサ20は、N個のメモリ16_1〜16_Nからの検出信号S1〜SNを受け、セレクタ12の複数のスイッチを制御するとともに、書き込み信号を生成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電圧検出回路に関する。

【背景技術】

【0002】

電子回路において、ある電圧と所定のしきい値の大小関係を判定するために、コンパレータが用いられる。ここで、あるひとつの電圧を、複数の異なるレベルのしきい値電圧と比較する場合、複数のしきい値電圧ごとにコンパレータを設けるのが一般的である。図1は、本発明者らが検討した、ひとつの電圧を複数の異なるしきい値電圧と比較する電圧検出回路の構成を示す回路図である。

【0003】

電圧検出回路100rは、入力電圧VINを、複数のしきい値電圧VTH1、VTH2、VTH3と比較する。たとえば入力電圧VINは、基準電圧VREFを、抵抗R11とサーミスタR12で分圧した電圧であり、温度Taに応じたレベルを有する。すなわち、電圧検出回路100は、温度Taを、複数のしきい値温度TTH1、TTH2、TTH3と比較する温度検出回路として機能する。

【0004】

電圧検出回路100rは、しきい値VTH1〜VTH3ごとに設けられた複数のコンパレータCMP1〜CMP3を備える。しきい値電圧VTHi(1≦i≦3)は、基準電圧VREFを、抵抗RaiとRbiにより分圧することにより生成される。

【0005】

入力電圧VINがしきい値電圧VTHi付近のときに、それと対応するコンパレータCMPiの出力Siがチャタリングするのを防止するために、しきい値電圧VTHiにはヒステリシスが設定される。ヒステリシスは、抵抗Rbiの抵抗値を、コンパレータCMPiの出力に応じて2値で切りかえることで実現される。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−051775号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

図1の電圧検出回路100rでは、しきい値ごとにコンパレータが必要となるため、しきい値の数が多いシステムでは、回路面積および消費電力が増大する。

【0008】

また、一般にコンパレータは入力オフセット電圧を有するが、その大きさはコンパレータごとにばらつく。したがって、複数のしきい値が近接する場合、各コンパレータの判定結果に矛盾が生ずる可能性がある。具体的にはコンパレータCMP1が、温度Taに応じた入力電圧VINを、0℃に応じたしきい値電圧VTH1と比較し、コンパレータCMP2が、温度Taに応じた入力電圧VINを、10℃に応じたしきい値電圧VTH2と比較するとする。この場合に、コンパレータCMP1、CMP2に異なるオフセットが生じていると、コンパレータCMP1の出力S1はTa<0℃を示し、コンパレータCMP2の出力S2はTa>10℃を示すことが起こりうる。

【0009】

本発明はかかる課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、回路面積、消費電力を低減するとともに、正しい電圧比較が可能な電圧比較回路の提供にある。

【課題を解決するための手段】

【0010】

本発明のある態様は、ひとつの入力電圧を、それぞれがヒステリシスを有するN個(Nは2以上の整数)のしきい値電圧と比較し、しきい値電圧ごとの比較結果を示すN個の検出信号を生成する電圧検出回路に関する。電圧検出回路は、抵抗ストリング、セレクタ、コンパレータ、N個のメモリ、シーケンサを備える。

抵抗ストリングは、直列に接続された複数の抵抗と、隣接する抵抗の接続ノードごとに設けられた複数のタップを有し、各タップにN個のしきい値電圧の上側レベルまたは下側レベルを発生させる。セレクタは、それぞれの一端が対応するタップと接続され、それぞれの他端が共通に接続された複数のスイッチを含み、ひとつのスイッチがオンした状態において、当該スイッチが接続されるタップの電圧を出力する。コンパレータは、入力電圧をセレクタの出力電圧と比較する。N個のメモリは、それぞれがしきい値電圧ごとに設けられ、書き込み信号に応答してコンパレータの出力を格納して検出信号を生成する。シーケンサは、N個のメモリからのN個の検出信号を受け、複数のスイッチを制御するとともに、N個のメモリそれぞれに対する書き込み信号を生成する。シーケンサは、変数i(1≦i≦N)を所定の順序で変化させながら、(1)対応するi番目のメモリからの検出信号を参照し、当該検出信号が入力電圧がi番目のしきい値電圧より高いことを示すとき、i番目のしきい値電圧の下側レベルに対応するスイッチをオンし、入力電圧がi番目のしきい値電圧より低いことを示すとき、i番目のしきい値電圧の上側レベルに対応するスイッチをオンするとともに、(2)i番目のメモリに対して、書き込み信号を出力する。

【0011】

この態様によると、単一のコンパレータを用いて、入力電圧を複数のしきい値電圧と比較でき、各しきい値電圧にヒステリシスを設定することができる。単一のコンパレータを複数のしきい値電圧で共有するため、しきい値電圧ごとにコンパレータを設ける場合に比べて回路面積、消費電力を低減できる。さらには、複数のコンパレータを用いる際の、コンパレータ間のオフセット電圧のばらつきの問題が生じないため、正確な電圧比較が可能となる。

【0012】

シーケンサは、変数iに対応して順にアサートされるN個のタイミング信号を生成するタイミング生成部と、それぞれがしきい値電圧ごとに設けられたN個の第1フリップフロップと、それぞれがしきい値電圧ごとに設けられたN個の第2フリップフロップと、を備えてもよい。

N個の第1フリップフロップはそれぞれ、対応するしきい値電圧の上側レベルに対応するスイッチに対する制御信号を生成してもよい。N個の第2フリップフロップはそれぞれ、対応するしきい値電圧の下側レベルに対応するスイッチに対する制御信号を生成してもよい。i番目のタイミング信号がアサートされると、i番目の第1フリップフロップおよび第2フリップフロップの一方は、対応するi番目のメモリの出力を格納し、それらの他方は、対応するi番目のメモリの出力の反転レベルを格納してもよい。

【0013】

シーケンサは、それぞれがしきい値電圧ごとに設けられたN個のインバータと、それぞれがしきい値電圧ごとに設けられたN個の第1ANDゲートと、それぞれがしきい値電圧ごとに設けられたN個の第2ANDゲートと、をさらに備えてもよい。

インバータはそれぞれ、対応するメモリの出力を反転してもよい。第1ANDゲートはそれぞれ、対応するインバータの出力と対応するタイミング信号の論理積を生成してもよい。第2ANDゲートはそれぞれ、対応するメモリの出力と対応するタイミング信号の論理積を生成してもよい。第1フリップフロップには、第1ANDゲートおよび第2ANDゲートの一方の出力が入力され、第2フリップフロップには、第1ANDゲートおよび第2ANDゲートの他方の出力が入力されてもよい。

【0014】

ある態様の電圧比較回路は、それぞれがしきい値電圧ごとに設けられたN個のORゲートをさらに備えてもよい。i番目のORゲートは、i番目の第1フリップフロップの出力とi番目の第2フリップフロップの出力の論理和にもとづいて、i番目のメモリに対する書き込み信号を生成してもよい。

【0015】

N個のメモリはそれぞれ、第3フリップフロップと、コンパレータの出力と第3フリップフロップの出力を受け、対応する書き込み信号が書き込みを指示するとき、コンパレータの出力を選択し、対応する書き込み信号が書き込みを指示しないとき、第3フリップフロップの出力を選択し、選択した信号を第3フリップフロップの入力端子へと出力するセレクタと、を含んでもよい。

【0016】

N個のメモリはそれぞれ、コンパレータの出力と対応する書き込み信号の論理積を生成する第3ANDゲートを含み、第3ANDゲートの出力を格納してもよい。

【0017】

本発明の別の態様は、温度検出回路に関する。温度検出回路は、基準電圧端子と接地端子の間に直列に設けられた抵抗およびサーミスタと、抵抗とサーミスタの接続点の電圧を、入力電圧として受ける上述のいずれかに記載の電圧検出回路と、を備えてもよい。

【0018】

本発明の別の態様は、電子機器に関する。電子機器は、電池と、電池の電圧を入力電圧として受ける電圧検出回路と、を備えてもよい。

この態様によれば、電池電圧を正確に検出できる。

【0019】

本発明の別の態様も、電子機器に関する。電子機器は、電池と、電池の近傍に、基準電圧端子と接地端子の間に直列に設けられた抵抗およびサーミスタと、抵抗とサーミスタの接続点の電圧を、入力電圧として受ける電圧検出回路と、を備えてもよい。

この態様によれば、電池の温度を正確に検出できる。

【0020】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0021】

本発明によれば、回路面積、消費電力を低減するとともに、正しい電圧比較が可能となる。

【図面の簡単な説明】

【0022】

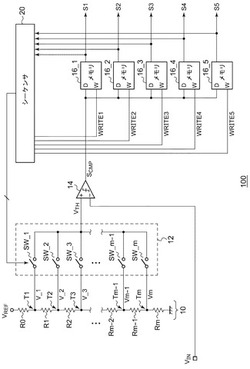

【図1】本発明者らが検討した、ひとつの電圧を複数の異なるしきい値電圧と比較する電圧検出回路の構成を示す回路図である。

【図2】実施の形態に係る電圧検出回路の構成を示す回路図である。

【図3】メモリおよびシーケンサの構成例を示す回路図である。

【図4】図2の電圧検出回路の動作を示すタイムチャートである。

【図5】図5(a)、(b)は、電圧検出回路を備える電子機器の構成を示すブロック図である。

【発明を実施するための形態】

【0023】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0024】

本明細書において、「部材Aが、部材Bと接続された状態」とは、部材Aと部材Bが物理的に直接的に接続される場合のほか、部材Aと部材Bが、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

【0025】

図2は、実施の形態に係る電圧検出回路100の構成を示す回路図である。

電圧検出回路100は、ひとつの入力電圧VINを、複数N個(Nは2以上の整数)のしきい値電圧VTH1〜VTHNと比較し、しきい値電圧VTH1〜VTHNごとの比較結果を示すN個の検出信号S1〜SNを生成する。しきい値電圧VTH1〜VTHNはそれぞれ、ヒステリシスを有しており、i番目(1≦i≦N)のしきい値電圧VTHiは、VIN>VTHiのとき下側レベルVTHi_Lをとり、VIN<VTHiのとき上側レベルVTHi_Uをとる。本実施の形態では、N=5の場合を説明するが、Nは任意の数でよい。

【0026】

電圧検出回路100は、抵抗ストリング10、セレクタ12、コンパレータ14、N個のメモリ16_1〜16_N、シーケンサ20を備える。

【0027】

抵抗ストリング10は、基準電圧端子と接地端子の間に順に直列に設けられた複数m+1個(mは2以上の整数)の抵抗R0〜Rmと、隣接する抵抗の接続ノードごとに設けられた複数のタップT1〜Tmを有する。各タップには、N個のしきい値電圧の上側レベルVTH1_U〜VTHN_Uまたは下側レベルVTH1_L〜VTHN_Lに対応する電圧V1〜Vmが発生する。

【0028】

タップの電圧V1〜Vmと、しきい値電圧VTHの上側レベル、下側レベルの対応関係は特に限定されない。実施の形態では、理解の容易化のため、以下の関係が成り立つものとする。

VTH1_U=V1

VTH1_L=V2

VTH2_U=V3

VTH2_L=V4

VTH3_U=V5

VTH3_L=V6

VTH4_U=V7

VTH4_L=V8

VTH5_U=V9

VTH5_L=V10

一般化すると、以下の関係が成り立つ。

VTHi_U=V(2×i−1)

VTHi_L=V(2×i)

【0029】

セレクタ12は、タップT1〜Tmごとに設けられたスイッチSW_1〜SW_mを含む。j番目(1≦j≦m)のスイッチSW_jの一端は、対応するタップTjと接続され、複数のスイッチSW_1〜SW_mの他端は共通に接続される。セレクタ12は、ひとつのスイッチSW_jがオンした状態において、当該スイッチSW_jが接続されるタップTjの電圧Vjを出力する。

【0030】

コンパレータ14は、入力電圧VINをセレクタ12の出力電圧と比較する。

N個のメモリ16_1〜16_5は、それぞれがしきい値電圧VTH1〜VTH5ごとに設けられる。i番目のメモリ16_iは、それに対する書き込み信号WRITE_iに応答してコンパレータ14の出力SCMPを格納し、検出信号Siを生成する。

【0031】

シーケンサ20は、N個のメモリ16_1〜16_5からのN個の検出信号S1〜S5を受け、セレクタ12の複数のスイッチSW_1〜SW_mを制御するとともに、N個のメモリ16_1〜16_5それぞれに対する書き込み信号WRITE_1〜WRITE_5を生成する。

【0032】

シーケンサ20は、変数i(1≦i≦N)を所定の順序で変化させながら、以下の処理を行う。

(1)シーケンサ20は、対応するi番目のメモリ16_iからの検出信号Siを参照し、当該検出信号Siが、入力電圧VINがi番目のしきい値電圧VTHiより高いことを示すとき(たとえばSi=“1”、ハイレベル)、i番目のしきい値電圧VTHiの下側レベルVTHi_Lに対応するスイッチSW_(2×i)をオンする。反対に、入力電圧VINがi番目のしきい値電圧VTHiより低いことを示すとき(たとえばSi=“0”、ローレベル)、i番目のしきい値電圧VTHiの上側レベルVTHi_Uに対応するスイッチSW_(2×i−1)をオンする。

【0033】

(2)そしてシーケンサ20は、i番目のメモリ16_iに対して書き込み信号WRITE_iを出力する。

【0034】

これによりi番目のメモリ16_iに格納される検出信号Siが、i番目のしきい値電圧VTHiと入力電圧VINの比較結果に応じて更新される。変数iを時間とともに変化させることにより、入力電圧VINと複数のしきい値電圧VTH1〜VTHNの比較結果を示す検出信号S1〜SNが生成される。なお、変数iは1,2,3,…Nの順で変化してもよいし、N,N−1,N−2,…1の順で変化してもよいし、別の順序であってもよい。

【0035】

続いて、メモリ16_1〜16_Nおよびシーケンサ20の具体的な構成を説明する。図3は、メモリ16およびシーケンサ20の構成例を示す回路図である。シーケンサ20は、システムクロック信号CLKと同期して動作する。たとえばクロック信号CLKの周波数は、32kHzである。

【0036】

シーケンサ20は、タイミング生成部22と、しきい値電圧VTH1〜VTH5ごとに設けられた、第1フリップフロップFF11〜5、第2フリップフロップFF21〜5、インバータINV1〜5、バッファBUF1〜5、第1ANDゲートAND11〜5、第2ANDゲートAND21〜5、ORゲートOR1〜5を含む。

【0037】

タイミング生成部22は、変数iに対応して順にアサートされるN個のタイミング信号Ts1〜Ts5を生成する。たとえばタイミング信号Ts1〜Ts5は、64ms周期で順にアサートされる。

【0038】

N個の第1フリップフロップFF11〜5は、それぞれしきい値電圧VTH1〜VTH5ごとに設けられる。i番目の第1フリップフロップFF1iは、対応するしきい値電圧VTHiの上側レベルVTHi_Uに対応するスイッチSW_(2×i−1)に対する制御信号CONT2×i−1を生成する。制御信号CONT2×i−1がハイレベルのとき、スイッチSW_(2×i−1)はオンする。

【0039】

N個の第2フリップフロップFF21〜5も、それぞれしきい値電圧VTH1〜VTH5ごとに設けられる。i番目の第2フリップフロップFF2iは、対応するしきい値電圧VTHiの下側レベルVTHi_Lに対応するスイッチSW_(2×i)に対する制御信号CONT2×iを生成する。制御信号CONT2×iがハイレベルのとき、スイッチSW_(2×i)はオンする。

【0040】

i番目のタイミング信号Tsiがアサートされると、i番目の第1フリップフロップFF1iおよび第2フリップフロップFF2iの一方(FF2i)は、対応するi番目のメモリ16_iの出力を格納し、それらの他方(FF1i)は、対応するi番目のメモリ16_iの出力の反転レベルを格納する。

【0041】

インバータINViは、対応するメモリ16_iの出力レベルを反転する。バッファBUFiは、対応するメモリ16_iの出力レベルをそのまま出力する。バッファBUFiは省略してもよい。

【0042】

第1ANDゲートAND1iは、対応するインバータINViと、対応するタイミング信号Tsiの論理積を生成する。第2ANDゲートAND2iは、対応するバッファBUFiを経由した対応するメモリ16_iの出力と、対応するタイミング信号Tsiの論理積を生成する。第1フリップフロップFF1iには、第1ANDゲートAND1iおよび第2ANDゲートAND2iの一方(AND1i)の出力が入力される。第2フリップフロップFF2iには、第1ANDゲートAND1iおよび第2ANDゲートAND2iの他方(AND2i)の出力が入力される。

【0043】

i番目のORゲートORiは、i番目の第1フリップフロップFF1iの出力CONT(2×i−1)とi番目の第2フリップフロップFF2iの出力CONT2×iの論理和にもとづいて、i番目のメモリ16_iに対する書き込み信号WRITE_iを生成する。

変形例において、タイミング信号Ts1〜Ts5それぞれにもとづいて、書き込み信号WRITE1〜WRITE5を生成してもよい。

【0044】

N個のメモリ16_1〜16_Nはそれぞれ、第3ANDゲートAND31〜N、セレクタSEL1〜N、第3フリップフロップFF31〜Nを含む。i番目のメモリ16_iに着目すると、第3ANDゲートAND3iは、コンパレータ14の出力SCMPと、対応する書き込み信号WRITEiの論理積を生成する。セレクタSELiは、対応する第3ANDゲートAND3iの出力と、対応する第3フリップフロップFF3iの出力を受け、書き込み信号WRITEiが1のとき、第3ANDゲートAND3iの出力を選択し、書き込み信号WRITEiが0のとき、第3フリップフロップFF3iの出力を選択する。第3フリップフロップFF3iには、セレクタSELiの出力が、クロック信号CLKと同期して書き込まれる。この構成によって、メモリ16_iは、書き込み信号WRITEiが0の期間は、第3フリップフロップFF3iの値を保持し続け、書き込み信号WRITEiが1となると、その値がコンパレータ14の出力SCMPによって更新される。なお、第3AND3iの機能は冗長であるため、省略してもよい。

【0045】

以上がメモリ16およびシーケンサ20の構成例である。

【0046】

続いて電圧検出回路100の動作を説明する。図4は、図2の電圧検出回路100の動作を示すタイムチャートである。

初期状態として、検出信号S1〜S5はローレベル(0)であるとする。

【0047】

はじめにタイミング信号Ts1がアサート(ハイレベル)されると、メモリ16_1に格納された検出信号S1が、第2フリップフロップFF21に、その反転信号#S1が第1フリップフロップFF11に格納される。その他のタイミング信号Ts2〜Ts5はネゲート(ローレベル)されているため、フリップフロップFF22〜5、FF12〜5には0が格納される。その結果、制御信号CONT1がハイレベル、残りがローレベルとなり、スイッチSW_1がオンとなり、VTH=VTH1_Uとなる。

【0048】

VIN<VTH1_Uであるため、コンパレータ14の出力SCMPはローレベルとなる。制御信号CONT1がハイレベルであるため、書き込み信号WRITE1がハイレベルとなり、メモリ16_1に、コンパレータ14の出力SCMPであるローレベル(0)が書き込まれる。

【0049】

同様にタイミング信号Ts2、Ts3、Ts4、Ts5が順にアサートされると、しきい値電圧VTHは、順にVTH2_U、VTH3_U、VTH4_U、VTH5_Uに設定される。そして、メモリ16_i(i=2、3、4、5)には、入力電圧VINとしきい値電圧VTHi_Uの比較結果SCMPが格納される。具体的には、S2=0、S3=0、S4=1、S5=1となる。

【0050】

次のサイクルでも、タイミング信号Ts1〜Ts5が順にアサートされる。Ts1〜Ts3については、前のサイクルと同様に動作する。

【0051】

2回目にタイミング信号Ts4がアサートされるとき、メモリ16_4から出力される検出信号S4はハイレベルである。したがって、制御信号CONT8がハイレベルとなり、スイッチSW_8がオンし、しきい値電圧VTH4が下側レベルVTH4_Lとなる。すなわち、入力電圧VINとしきい値電圧VTH4の比較結果に応じて、適切なヒステリシスが設定される。

【0052】

タイミング信号Ts5についても同様であり、しきい値電圧VTH5は、下側レベルVTH5_Lに設定される。

【0053】

以上が電圧検出回路100の動作である。

電圧検出回路100によれば、単一のコンパレータ14を用いて、入力電圧VINを複数のしきい値電圧VTH1〜VTH5と比較でき、さらに各しきい値電圧VTH1〜VTH5にヒステリシスを設定することができる。

【0054】

また、単一のコンパレータ14を複数のしきい値電圧VTH1〜VTH5で共有するため、しきい値電圧ごとにコンパレータを設ける図1の構成に比べて回路面積、消費電力を低減できる。さらには、複数のコンパレータを用いる際のオフセット電圧のばらつきの問題が生じないため、比較結果に矛盾が生じず、正確な電圧比較が可能となる。

【0055】

最後に、電圧検出回路100のアプリケーションを説明する。図5(a)、(b)は、電圧検出回路100を備える電子機器の構成を示すブロック図である。

【0056】

図5(a)の電子機器1aは、電池2、抵抗R11、サーミスタR12、電圧検出回路100を備える。抵抗R11およびサーミスタR12は、基準電圧端子VREFと接地端子の間に直列に設けられる。サーミスタR12は、電池2と近接して配置され、その抵抗は、電池2の温度Taに応じて変化する。電圧検出回路100は、抵抗R11とサーミスタR12の接続点の電圧を入力電圧VINとして受ける。

【0057】

この構成によれば、電池2の温度Taを複数のしきい値温度と正確に比較することができる。

【0058】

図5(b)の電子機器1bは、電池2および電圧検出回路100を備える。電圧検出回路100は、電池電圧VBATに応じた電圧を、入力電圧VINとして受ける。

【0059】

この構成によれば、電池2の電圧レベルを正確にモニターできる。

【0060】

実施の形態にもとづき、具体的な用語を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【符号の説明】

【0061】

1…電子機器、2…電池、100…電圧検出回路、10…抵抗ストリング、12…セレクタ、14…コンパレータ、16…メモリ、20…シーケンサ、22…タイミング生成部。

【技術分野】

【0001】

本発明は、電圧検出回路に関する。

【背景技術】

【0002】

電子回路において、ある電圧と所定のしきい値の大小関係を判定するために、コンパレータが用いられる。ここで、あるひとつの電圧を、複数の異なるレベルのしきい値電圧と比較する場合、複数のしきい値電圧ごとにコンパレータを設けるのが一般的である。図1は、本発明者らが検討した、ひとつの電圧を複数の異なるしきい値電圧と比較する電圧検出回路の構成を示す回路図である。

【0003】

電圧検出回路100rは、入力電圧VINを、複数のしきい値電圧VTH1、VTH2、VTH3と比較する。たとえば入力電圧VINは、基準電圧VREFを、抵抗R11とサーミスタR12で分圧した電圧であり、温度Taに応じたレベルを有する。すなわち、電圧検出回路100は、温度Taを、複数のしきい値温度TTH1、TTH2、TTH3と比較する温度検出回路として機能する。

【0004】

電圧検出回路100rは、しきい値VTH1〜VTH3ごとに設けられた複数のコンパレータCMP1〜CMP3を備える。しきい値電圧VTHi(1≦i≦3)は、基準電圧VREFを、抵抗RaiとRbiにより分圧することにより生成される。

【0005】

入力電圧VINがしきい値電圧VTHi付近のときに、それと対応するコンパレータCMPiの出力Siがチャタリングするのを防止するために、しきい値電圧VTHiにはヒステリシスが設定される。ヒステリシスは、抵抗Rbiの抵抗値を、コンパレータCMPiの出力に応じて2値で切りかえることで実現される。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−051775号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

図1の電圧検出回路100rでは、しきい値ごとにコンパレータが必要となるため、しきい値の数が多いシステムでは、回路面積および消費電力が増大する。

【0008】

また、一般にコンパレータは入力オフセット電圧を有するが、その大きさはコンパレータごとにばらつく。したがって、複数のしきい値が近接する場合、各コンパレータの判定結果に矛盾が生ずる可能性がある。具体的にはコンパレータCMP1が、温度Taに応じた入力電圧VINを、0℃に応じたしきい値電圧VTH1と比較し、コンパレータCMP2が、温度Taに応じた入力電圧VINを、10℃に応じたしきい値電圧VTH2と比較するとする。この場合に、コンパレータCMP1、CMP2に異なるオフセットが生じていると、コンパレータCMP1の出力S1はTa<0℃を示し、コンパレータCMP2の出力S2はTa>10℃を示すことが起こりうる。

【0009】

本発明はかかる課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、回路面積、消費電力を低減するとともに、正しい電圧比較が可能な電圧比較回路の提供にある。

【課題を解決するための手段】

【0010】

本発明のある態様は、ひとつの入力電圧を、それぞれがヒステリシスを有するN個(Nは2以上の整数)のしきい値電圧と比較し、しきい値電圧ごとの比較結果を示すN個の検出信号を生成する電圧検出回路に関する。電圧検出回路は、抵抗ストリング、セレクタ、コンパレータ、N個のメモリ、シーケンサを備える。

抵抗ストリングは、直列に接続された複数の抵抗と、隣接する抵抗の接続ノードごとに設けられた複数のタップを有し、各タップにN個のしきい値電圧の上側レベルまたは下側レベルを発生させる。セレクタは、それぞれの一端が対応するタップと接続され、それぞれの他端が共通に接続された複数のスイッチを含み、ひとつのスイッチがオンした状態において、当該スイッチが接続されるタップの電圧を出力する。コンパレータは、入力電圧をセレクタの出力電圧と比較する。N個のメモリは、それぞれがしきい値電圧ごとに設けられ、書き込み信号に応答してコンパレータの出力を格納して検出信号を生成する。シーケンサは、N個のメモリからのN個の検出信号を受け、複数のスイッチを制御するとともに、N個のメモリそれぞれに対する書き込み信号を生成する。シーケンサは、変数i(1≦i≦N)を所定の順序で変化させながら、(1)対応するi番目のメモリからの検出信号を参照し、当該検出信号が入力電圧がi番目のしきい値電圧より高いことを示すとき、i番目のしきい値電圧の下側レベルに対応するスイッチをオンし、入力電圧がi番目のしきい値電圧より低いことを示すとき、i番目のしきい値電圧の上側レベルに対応するスイッチをオンするとともに、(2)i番目のメモリに対して、書き込み信号を出力する。

【0011】

この態様によると、単一のコンパレータを用いて、入力電圧を複数のしきい値電圧と比較でき、各しきい値電圧にヒステリシスを設定することができる。単一のコンパレータを複数のしきい値電圧で共有するため、しきい値電圧ごとにコンパレータを設ける場合に比べて回路面積、消費電力を低減できる。さらには、複数のコンパレータを用いる際の、コンパレータ間のオフセット電圧のばらつきの問題が生じないため、正確な電圧比較が可能となる。

【0012】

シーケンサは、変数iに対応して順にアサートされるN個のタイミング信号を生成するタイミング生成部と、それぞれがしきい値電圧ごとに設けられたN個の第1フリップフロップと、それぞれがしきい値電圧ごとに設けられたN個の第2フリップフロップと、を備えてもよい。

N個の第1フリップフロップはそれぞれ、対応するしきい値電圧の上側レベルに対応するスイッチに対する制御信号を生成してもよい。N個の第2フリップフロップはそれぞれ、対応するしきい値電圧の下側レベルに対応するスイッチに対する制御信号を生成してもよい。i番目のタイミング信号がアサートされると、i番目の第1フリップフロップおよび第2フリップフロップの一方は、対応するi番目のメモリの出力を格納し、それらの他方は、対応するi番目のメモリの出力の反転レベルを格納してもよい。

【0013】

シーケンサは、それぞれがしきい値電圧ごとに設けられたN個のインバータと、それぞれがしきい値電圧ごとに設けられたN個の第1ANDゲートと、それぞれがしきい値電圧ごとに設けられたN個の第2ANDゲートと、をさらに備えてもよい。

インバータはそれぞれ、対応するメモリの出力を反転してもよい。第1ANDゲートはそれぞれ、対応するインバータの出力と対応するタイミング信号の論理積を生成してもよい。第2ANDゲートはそれぞれ、対応するメモリの出力と対応するタイミング信号の論理積を生成してもよい。第1フリップフロップには、第1ANDゲートおよび第2ANDゲートの一方の出力が入力され、第2フリップフロップには、第1ANDゲートおよび第2ANDゲートの他方の出力が入力されてもよい。

【0014】

ある態様の電圧比較回路は、それぞれがしきい値電圧ごとに設けられたN個のORゲートをさらに備えてもよい。i番目のORゲートは、i番目の第1フリップフロップの出力とi番目の第2フリップフロップの出力の論理和にもとづいて、i番目のメモリに対する書き込み信号を生成してもよい。

【0015】

N個のメモリはそれぞれ、第3フリップフロップと、コンパレータの出力と第3フリップフロップの出力を受け、対応する書き込み信号が書き込みを指示するとき、コンパレータの出力を選択し、対応する書き込み信号が書き込みを指示しないとき、第3フリップフロップの出力を選択し、選択した信号を第3フリップフロップの入力端子へと出力するセレクタと、を含んでもよい。

【0016】

N個のメモリはそれぞれ、コンパレータの出力と対応する書き込み信号の論理積を生成する第3ANDゲートを含み、第3ANDゲートの出力を格納してもよい。

【0017】

本発明の別の態様は、温度検出回路に関する。温度検出回路は、基準電圧端子と接地端子の間に直列に設けられた抵抗およびサーミスタと、抵抗とサーミスタの接続点の電圧を、入力電圧として受ける上述のいずれかに記載の電圧検出回路と、を備えてもよい。

【0018】

本発明の別の態様は、電子機器に関する。電子機器は、電池と、電池の電圧を入力電圧として受ける電圧検出回路と、を備えてもよい。

この態様によれば、電池電圧を正確に検出できる。

【0019】

本発明の別の態様も、電子機器に関する。電子機器は、電池と、電池の近傍に、基準電圧端子と接地端子の間に直列に設けられた抵抗およびサーミスタと、抵抗とサーミスタの接続点の電圧を、入力電圧として受ける電圧検出回路と、を備えてもよい。

この態様によれば、電池の温度を正確に検出できる。

【0020】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0021】

本発明によれば、回路面積、消費電力を低減するとともに、正しい電圧比較が可能となる。

【図面の簡単な説明】

【0022】

【図1】本発明者らが検討した、ひとつの電圧を複数の異なるしきい値電圧と比較する電圧検出回路の構成を示す回路図である。

【図2】実施の形態に係る電圧検出回路の構成を示す回路図である。

【図3】メモリおよびシーケンサの構成例を示す回路図である。

【図4】図2の電圧検出回路の動作を示すタイムチャートである。

【図5】図5(a)、(b)は、電圧検出回路を備える電子機器の構成を示すブロック図である。

【発明を実施するための形態】

【0023】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0024】

本明細書において、「部材Aが、部材Bと接続された状態」とは、部材Aと部材Bが物理的に直接的に接続される場合のほか、部材Aと部材Bが、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

【0025】

図2は、実施の形態に係る電圧検出回路100の構成を示す回路図である。

電圧検出回路100は、ひとつの入力電圧VINを、複数N個(Nは2以上の整数)のしきい値電圧VTH1〜VTHNと比較し、しきい値電圧VTH1〜VTHNごとの比較結果を示すN個の検出信号S1〜SNを生成する。しきい値電圧VTH1〜VTHNはそれぞれ、ヒステリシスを有しており、i番目(1≦i≦N)のしきい値電圧VTHiは、VIN>VTHiのとき下側レベルVTHi_Lをとり、VIN<VTHiのとき上側レベルVTHi_Uをとる。本実施の形態では、N=5の場合を説明するが、Nは任意の数でよい。

【0026】

電圧検出回路100は、抵抗ストリング10、セレクタ12、コンパレータ14、N個のメモリ16_1〜16_N、シーケンサ20を備える。

【0027】

抵抗ストリング10は、基準電圧端子と接地端子の間に順に直列に設けられた複数m+1個(mは2以上の整数)の抵抗R0〜Rmと、隣接する抵抗の接続ノードごとに設けられた複数のタップT1〜Tmを有する。各タップには、N個のしきい値電圧の上側レベルVTH1_U〜VTHN_Uまたは下側レベルVTH1_L〜VTHN_Lに対応する電圧V1〜Vmが発生する。

【0028】

タップの電圧V1〜Vmと、しきい値電圧VTHの上側レベル、下側レベルの対応関係は特に限定されない。実施の形態では、理解の容易化のため、以下の関係が成り立つものとする。

VTH1_U=V1

VTH1_L=V2

VTH2_U=V3

VTH2_L=V4

VTH3_U=V5

VTH3_L=V6

VTH4_U=V7

VTH4_L=V8

VTH5_U=V9

VTH5_L=V10

一般化すると、以下の関係が成り立つ。

VTHi_U=V(2×i−1)

VTHi_L=V(2×i)

【0029】

セレクタ12は、タップT1〜Tmごとに設けられたスイッチSW_1〜SW_mを含む。j番目(1≦j≦m)のスイッチSW_jの一端は、対応するタップTjと接続され、複数のスイッチSW_1〜SW_mの他端は共通に接続される。セレクタ12は、ひとつのスイッチSW_jがオンした状態において、当該スイッチSW_jが接続されるタップTjの電圧Vjを出力する。

【0030】

コンパレータ14は、入力電圧VINをセレクタ12の出力電圧と比較する。

N個のメモリ16_1〜16_5は、それぞれがしきい値電圧VTH1〜VTH5ごとに設けられる。i番目のメモリ16_iは、それに対する書き込み信号WRITE_iに応答してコンパレータ14の出力SCMPを格納し、検出信号Siを生成する。

【0031】

シーケンサ20は、N個のメモリ16_1〜16_5からのN個の検出信号S1〜S5を受け、セレクタ12の複数のスイッチSW_1〜SW_mを制御するとともに、N個のメモリ16_1〜16_5それぞれに対する書き込み信号WRITE_1〜WRITE_5を生成する。

【0032】

シーケンサ20は、変数i(1≦i≦N)を所定の順序で変化させながら、以下の処理を行う。

(1)シーケンサ20は、対応するi番目のメモリ16_iからの検出信号Siを参照し、当該検出信号Siが、入力電圧VINがi番目のしきい値電圧VTHiより高いことを示すとき(たとえばSi=“1”、ハイレベル)、i番目のしきい値電圧VTHiの下側レベルVTHi_Lに対応するスイッチSW_(2×i)をオンする。反対に、入力電圧VINがi番目のしきい値電圧VTHiより低いことを示すとき(たとえばSi=“0”、ローレベル)、i番目のしきい値電圧VTHiの上側レベルVTHi_Uに対応するスイッチSW_(2×i−1)をオンする。

【0033】

(2)そしてシーケンサ20は、i番目のメモリ16_iに対して書き込み信号WRITE_iを出力する。

【0034】

これによりi番目のメモリ16_iに格納される検出信号Siが、i番目のしきい値電圧VTHiと入力電圧VINの比較結果に応じて更新される。変数iを時間とともに変化させることにより、入力電圧VINと複数のしきい値電圧VTH1〜VTHNの比較結果を示す検出信号S1〜SNが生成される。なお、変数iは1,2,3,…Nの順で変化してもよいし、N,N−1,N−2,…1の順で変化してもよいし、別の順序であってもよい。

【0035】

続いて、メモリ16_1〜16_Nおよびシーケンサ20の具体的な構成を説明する。図3は、メモリ16およびシーケンサ20の構成例を示す回路図である。シーケンサ20は、システムクロック信号CLKと同期して動作する。たとえばクロック信号CLKの周波数は、32kHzである。

【0036】

シーケンサ20は、タイミング生成部22と、しきい値電圧VTH1〜VTH5ごとに設けられた、第1フリップフロップFF11〜5、第2フリップフロップFF21〜5、インバータINV1〜5、バッファBUF1〜5、第1ANDゲートAND11〜5、第2ANDゲートAND21〜5、ORゲートOR1〜5を含む。

【0037】

タイミング生成部22は、変数iに対応して順にアサートされるN個のタイミング信号Ts1〜Ts5を生成する。たとえばタイミング信号Ts1〜Ts5は、64ms周期で順にアサートされる。

【0038】

N個の第1フリップフロップFF11〜5は、それぞれしきい値電圧VTH1〜VTH5ごとに設けられる。i番目の第1フリップフロップFF1iは、対応するしきい値電圧VTHiの上側レベルVTHi_Uに対応するスイッチSW_(2×i−1)に対する制御信号CONT2×i−1を生成する。制御信号CONT2×i−1がハイレベルのとき、スイッチSW_(2×i−1)はオンする。

【0039】

N個の第2フリップフロップFF21〜5も、それぞれしきい値電圧VTH1〜VTH5ごとに設けられる。i番目の第2フリップフロップFF2iは、対応するしきい値電圧VTHiの下側レベルVTHi_Lに対応するスイッチSW_(2×i)に対する制御信号CONT2×iを生成する。制御信号CONT2×iがハイレベルのとき、スイッチSW_(2×i)はオンする。

【0040】

i番目のタイミング信号Tsiがアサートされると、i番目の第1フリップフロップFF1iおよび第2フリップフロップFF2iの一方(FF2i)は、対応するi番目のメモリ16_iの出力を格納し、それらの他方(FF1i)は、対応するi番目のメモリ16_iの出力の反転レベルを格納する。

【0041】

インバータINViは、対応するメモリ16_iの出力レベルを反転する。バッファBUFiは、対応するメモリ16_iの出力レベルをそのまま出力する。バッファBUFiは省略してもよい。

【0042】

第1ANDゲートAND1iは、対応するインバータINViと、対応するタイミング信号Tsiの論理積を生成する。第2ANDゲートAND2iは、対応するバッファBUFiを経由した対応するメモリ16_iの出力と、対応するタイミング信号Tsiの論理積を生成する。第1フリップフロップFF1iには、第1ANDゲートAND1iおよび第2ANDゲートAND2iの一方(AND1i)の出力が入力される。第2フリップフロップFF2iには、第1ANDゲートAND1iおよび第2ANDゲートAND2iの他方(AND2i)の出力が入力される。

【0043】

i番目のORゲートORiは、i番目の第1フリップフロップFF1iの出力CONT(2×i−1)とi番目の第2フリップフロップFF2iの出力CONT2×iの論理和にもとづいて、i番目のメモリ16_iに対する書き込み信号WRITE_iを生成する。

変形例において、タイミング信号Ts1〜Ts5それぞれにもとづいて、書き込み信号WRITE1〜WRITE5を生成してもよい。

【0044】

N個のメモリ16_1〜16_Nはそれぞれ、第3ANDゲートAND31〜N、セレクタSEL1〜N、第3フリップフロップFF31〜Nを含む。i番目のメモリ16_iに着目すると、第3ANDゲートAND3iは、コンパレータ14の出力SCMPと、対応する書き込み信号WRITEiの論理積を生成する。セレクタSELiは、対応する第3ANDゲートAND3iの出力と、対応する第3フリップフロップFF3iの出力を受け、書き込み信号WRITEiが1のとき、第3ANDゲートAND3iの出力を選択し、書き込み信号WRITEiが0のとき、第3フリップフロップFF3iの出力を選択する。第3フリップフロップFF3iには、セレクタSELiの出力が、クロック信号CLKと同期して書き込まれる。この構成によって、メモリ16_iは、書き込み信号WRITEiが0の期間は、第3フリップフロップFF3iの値を保持し続け、書き込み信号WRITEiが1となると、その値がコンパレータ14の出力SCMPによって更新される。なお、第3AND3iの機能は冗長であるため、省略してもよい。

【0045】

以上がメモリ16およびシーケンサ20の構成例である。

【0046】

続いて電圧検出回路100の動作を説明する。図4は、図2の電圧検出回路100の動作を示すタイムチャートである。

初期状態として、検出信号S1〜S5はローレベル(0)であるとする。

【0047】

はじめにタイミング信号Ts1がアサート(ハイレベル)されると、メモリ16_1に格納された検出信号S1が、第2フリップフロップFF21に、その反転信号#S1が第1フリップフロップFF11に格納される。その他のタイミング信号Ts2〜Ts5はネゲート(ローレベル)されているため、フリップフロップFF22〜5、FF12〜5には0が格納される。その結果、制御信号CONT1がハイレベル、残りがローレベルとなり、スイッチSW_1がオンとなり、VTH=VTH1_Uとなる。

【0048】

VIN<VTH1_Uであるため、コンパレータ14の出力SCMPはローレベルとなる。制御信号CONT1がハイレベルであるため、書き込み信号WRITE1がハイレベルとなり、メモリ16_1に、コンパレータ14の出力SCMPであるローレベル(0)が書き込まれる。

【0049】

同様にタイミング信号Ts2、Ts3、Ts4、Ts5が順にアサートされると、しきい値電圧VTHは、順にVTH2_U、VTH3_U、VTH4_U、VTH5_Uに設定される。そして、メモリ16_i(i=2、3、4、5)には、入力電圧VINとしきい値電圧VTHi_Uの比較結果SCMPが格納される。具体的には、S2=0、S3=0、S4=1、S5=1となる。

【0050】

次のサイクルでも、タイミング信号Ts1〜Ts5が順にアサートされる。Ts1〜Ts3については、前のサイクルと同様に動作する。

【0051】

2回目にタイミング信号Ts4がアサートされるとき、メモリ16_4から出力される検出信号S4はハイレベルである。したがって、制御信号CONT8がハイレベルとなり、スイッチSW_8がオンし、しきい値電圧VTH4が下側レベルVTH4_Lとなる。すなわち、入力電圧VINとしきい値電圧VTH4の比較結果に応じて、適切なヒステリシスが設定される。

【0052】

タイミング信号Ts5についても同様であり、しきい値電圧VTH5は、下側レベルVTH5_Lに設定される。

【0053】

以上が電圧検出回路100の動作である。

電圧検出回路100によれば、単一のコンパレータ14を用いて、入力電圧VINを複数のしきい値電圧VTH1〜VTH5と比較でき、さらに各しきい値電圧VTH1〜VTH5にヒステリシスを設定することができる。

【0054】

また、単一のコンパレータ14を複数のしきい値電圧VTH1〜VTH5で共有するため、しきい値電圧ごとにコンパレータを設ける図1の構成に比べて回路面積、消費電力を低減できる。さらには、複数のコンパレータを用いる際のオフセット電圧のばらつきの問題が生じないため、比較結果に矛盾が生じず、正確な電圧比較が可能となる。

【0055】

最後に、電圧検出回路100のアプリケーションを説明する。図5(a)、(b)は、電圧検出回路100を備える電子機器の構成を示すブロック図である。

【0056】

図5(a)の電子機器1aは、電池2、抵抗R11、サーミスタR12、電圧検出回路100を備える。抵抗R11およびサーミスタR12は、基準電圧端子VREFと接地端子の間に直列に設けられる。サーミスタR12は、電池2と近接して配置され、その抵抗は、電池2の温度Taに応じて変化する。電圧検出回路100は、抵抗R11とサーミスタR12の接続点の電圧を入力電圧VINとして受ける。

【0057】

この構成によれば、電池2の温度Taを複数のしきい値温度と正確に比較することができる。

【0058】

図5(b)の電子機器1bは、電池2および電圧検出回路100を備える。電圧検出回路100は、電池電圧VBATに応じた電圧を、入力電圧VINとして受ける。

【0059】

この構成によれば、電池2の電圧レベルを正確にモニターできる。

【0060】

実施の形態にもとづき、具体的な用語を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【符号の説明】

【0061】

1…電子機器、2…電池、100…電圧検出回路、10…抵抗ストリング、12…セレクタ、14…コンパレータ、16…メモリ、20…シーケンサ、22…タイミング生成部。

【特許請求の範囲】

【請求項1】

ひとつの入力電圧を、それぞれがヒステリシスを有するN個(Nは2以上の整数)のしきい値電圧と比較し、しきい値電圧ごとの比較結果を示すN個の検出信号を生成する電圧検出回路であって、

直列に接続された複数の抵抗と、隣接する抵抗の接続ノードごとに設けられた複数のタップを有し、各タップに前記N個のしきい値電圧の上側レベルまたは下側レベルを発生させる抵抗ストリングと、

それぞれの一端が対応するタップと接続され、それぞれの他端が共通に接続された複数のスイッチを含み、ひとつのスイッチがオンした状態において、当該スイッチが接続されるタップの電圧を出力するセレクタと、

前記入力電圧を前記セレクタの出力電圧と比較するコンパレータと、

それぞれが前記しきい値電圧ごとに設けられ、書き込み信号に応答して前記コンパレータの出力を格納して前記検出信号を生成する、N個のメモリと、

前記N個のメモリからのN個の前記検出信号を受け、前記複数のスイッチを制御するとともに、前記N個のメモリそれぞれに対する前記書き込み信号を生成するシーケンサであって、

変数i(1≦i≦N)をサイクリックに順に変化させながら、

(1)対応するi番目のメモリからの検出信号を参照し、当該検出信号が前記入力電圧がi番目のしきい値電圧より高いことを示すとき、i番目のしきい値電圧の下側レベルに対応する前記スイッチをオンし、前記入力電圧がi番目のしきい値電圧より低いことを示すとき、i番目のしきい値電圧の上側レベルに対応する前記スイッチをオンするとともに、(2)i番目の前記メモリに対して、前記書き込み信号を出力するシーケンサと、

を備えることを特徴とする電圧検出回路。

【請求項2】

前記シーケンサは、

変数iに対応して順にアサートされるN個のタイミング信号を生成するタイミング生成部と、

それぞれが前記しきい値電圧ごとに設けられ、対応するしきい値電圧の上側レベルに対応するスイッチに対する制御信号を生成する、N個の第1フリップフロップと、

それぞれが前記しきい値電圧ごとに設けられ、対応するしきい値電圧の下側レベルに対応するスイッチに対する制御信号を生成する、N個の第2フリップフロップと、

を備え、

i番目のタイミング信号がアサートされると、i番目の前記第1フリップフロップおよび前記第2フリップフロップの一方は、対応するi番目のメモリの出力を格納し、それらの他方は、対応するi番目のメモリの出力の反転レベルを格納することを特徴とする請求項1に記載の電圧検出回路。

【請求項3】

前記シーケンサは、

それぞれが前記しきい値電圧ごとに設けられ、対応するメモリの出力を反転するN個のインバータと、

それぞれが前記しきい値電圧ごとに設けられ、対応する前記インバータの出力と対応するタイミング信号の論理積を生成する第1ANDゲートと、

それぞれが前記しきい値電圧ごとに設けられ、対応するメモリの出力と対応するタイミング信号の論理積を生成する第2ANDゲートと、

をさらに備え、

前記第1フリップフロップには、前記第1ANDゲートおよび前記第2ANDゲートの一方の出力が入力され、

前記第2フリップフロップには、前記第1ANDゲートおよび前記第2ANDゲートの他方の出力が入力されることを特徴とする請求項2に記載の電圧検出回路。

【請求項4】

それぞれが前記しきい値電圧ごとに設けられたN個のORゲートであって、i番目のORゲートは、i番目の第1フリップフロップの出力とi番目の第2フリップフロップの出力の論理和にもとづいて、i番目のメモリに対する前記書き込み信号を生成する、N個のORゲートをさらに備えることを特徴とする請求項2に記載の電圧検出回路。

【請求項5】

前記N個のメモリはそれぞれ、

第3フリップフロップと、

前記コンパレータの出力と前記第3フリップフロップの出力を受け、対応する書き込み信号が書き込みを指示するとき、前記コンパレータの出力を選択し、対応する書き込み信号が書き込みを指示しないとき、前記第3フリップフロップの出力を選択し、選択した信号を前記第3フリップフロップの入力端子へと出力するセレクタと、

を含むことを特徴とする請求項1から4のいずれかに記載の電圧検出回路。

【請求項6】

前記N個のメモリはそれぞれ、

前記コンパレータの出力と対応する書き込み信号の論理積を生成する第3ANDゲートを含み、前記第3ANDゲートの出力を格納することを特徴とする請求項1から4のいずれかに記載の電圧検出回路。

【請求項7】

基準電圧端子と接地端子の間に直列に設けられた抵抗およびサーミスタと、

前記抵抗とサーミスタの接続点の電圧を、入力電圧として受ける請求項1から6のいずれかに記載の電圧検出回路と、

を備えることを特徴とする温度検出回路。

【請求項8】

電池と、

前記電池の電圧を入力電圧として受ける請求項1から6のいずれかに記載の電圧検出回路と、

を備えることを特徴とする電子機器。

【請求項9】

電池と、

前記電池の近傍に、基準電圧端子と接地端子の間に直列に設けられた抵抗およびサーミスタと、

前記抵抗とサーミスタの接続点の電圧を、入力電圧として受ける請求項1から6のいずれかに記載の電圧検出回路と、

を備えることを特徴とする電子機器。

【請求項1】

ひとつの入力電圧を、それぞれがヒステリシスを有するN個(Nは2以上の整数)のしきい値電圧と比較し、しきい値電圧ごとの比較結果を示すN個の検出信号を生成する電圧検出回路であって、

直列に接続された複数の抵抗と、隣接する抵抗の接続ノードごとに設けられた複数のタップを有し、各タップに前記N個のしきい値電圧の上側レベルまたは下側レベルを発生させる抵抗ストリングと、

それぞれの一端が対応するタップと接続され、それぞれの他端が共通に接続された複数のスイッチを含み、ひとつのスイッチがオンした状態において、当該スイッチが接続されるタップの電圧を出力するセレクタと、

前記入力電圧を前記セレクタの出力電圧と比較するコンパレータと、

それぞれが前記しきい値電圧ごとに設けられ、書き込み信号に応答して前記コンパレータの出力を格納して前記検出信号を生成する、N個のメモリと、

前記N個のメモリからのN個の前記検出信号を受け、前記複数のスイッチを制御するとともに、前記N個のメモリそれぞれに対する前記書き込み信号を生成するシーケンサであって、

変数i(1≦i≦N)をサイクリックに順に変化させながら、

(1)対応するi番目のメモリからの検出信号を参照し、当該検出信号が前記入力電圧がi番目のしきい値電圧より高いことを示すとき、i番目のしきい値電圧の下側レベルに対応する前記スイッチをオンし、前記入力電圧がi番目のしきい値電圧より低いことを示すとき、i番目のしきい値電圧の上側レベルに対応する前記スイッチをオンするとともに、(2)i番目の前記メモリに対して、前記書き込み信号を出力するシーケンサと、

を備えることを特徴とする電圧検出回路。

【請求項2】

前記シーケンサは、

変数iに対応して順にアサートされるN個のタイミング信号を生成するタイミング生成部と、

それぞれが前記しきい値電圧ごとに設けられ、対応するしきい値電圧の上側レベルに対応するスイッチに対する制御信号を生成する、N個の第1フリップフロップと、

それぞれが前記しきい値電圧ごとに設けられ、対応するしきい値電圧の下側レベルに対応するスイッチに対する制御信号を生成する、N個の第2フリップフロップと、

を備え、

i番目のタイミング信号がアサートされると、i番目の前記第1フリップフロップおよび前記第2フリップフロップの一方は、対応するi番目のメモリの出力を格納し、それらの他方は、対応するi番目のメモリの出力の反転レベルを格納することを特徴とする請求項1に記載の電圧検出回路。

【請求項3】

前記シーケンサは、

それぞれが前記しきい値電圧ごとに設けられ、対応するメモリの出力を反転するN個のインバータと、

それぞれが前記しきい値電圧ごとに設けられ、対応する前記インバータの出力と対応するタイミング信号の論理積を生成する第1ANDゲートと、

それぞれが前記しきい値電圧ごとに設けられ、対応するメモリの出力と対応するタイミング信号の論理積を生成する第2ANDゲートと、

をさらに備え、

前記第1フリップフロップには、前記第1ANDゲートおよび前記第2ANDゲートの一方の出力が入力され、

前記第2フリップフロップには、前記第1ANDゲートおよび前記第2ANDゲートの他方の出力が入力されることを特徴とする請求項2に記載の電圧検出回路。

【請求項4】

それぞれが前記しきい値電圧ごとに設けられたN個のORゲートであって、i番目のORゲートは、i番目の第1フリップフロップの出力とi番目の第2フリップフロップの出力の論理和にもとづいて、i番目のメモリに対する前記書き込み信号を生成する、N個のORゲートをさらに備えることを特徴とする請求項2に記載の電圧検出回路。

【請求項5】

前記N個のメモリはそれぞれ、

第3フリップフロップと、

前記コンパレータの出力と前記第3フリップフロップの出力を受け、対応する書き込み信号が書き込みを指示するとき、前記コンパレータの出力を選択し、対応する書き込み信号が書き込みを指示しないとき、前記第3フリップフロップの出力を選択し、選択した信号を前記第3フリップフロップの入力端子へと出力するセレクタと、

を含むことを特徴とする請求項1から4のいずれかに記載の電圧検出回路。

【請求項6】

前記N個のメモリはそれぞれ、

前記コンパレータの出力と対応する書き込み信号の論理積を生成する第3ANDゲートを含み、前記第3ANDゲートの出力を格納することを特徴とする請求項1から4のいずれかに記載の電圧検出回路。

【請求項7】

基準電圧端子と接地端子の間に直列に設けられた抵抗およびサーミスタと、

前記抵抗とサーミスタの接続点の電圧を、入力電圧として受ける請求項1から6のいずれかに記載の電圧検出回路と、

を備えることを特徴とする温度検出回路。

【請求項8】

電池と、

前記電池の電圧を入力電圧として受ける請求項1から6のいずれかに記載の電圧検出回路と、

を備えることを特徴とする電子機器。

【請求項9】

電池と、

前記電池の近傍に、基準電圧端子と接地端子の間に直列に設けられた抵抗およびサーミスタと、

前記抵抗とサーミスタの接続点の電圧を、入力電圧として受ける請求項1から6のいずれかに記載の電圧検出回路と、

を備えることを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−66133(P2013−66133A)

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願番号】特願2011−204928(P2011−204928)

【出願日】平成23年9月20日(2011.9.20)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願日】平成23年9月20日(2011.9.20)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]