電圧比較回路,A/D変換器および半導体装置

【課題】比較器に対して最適な同相電圧を与えることによって、動作速度の向上を図る。

【解決手段】比較器1と、前記比較器の応答速度を判定する判定器2と、前記判定器の判定結果に従って、前記比較器の応答速度の遅延を低減するように、前記比較器の複数の入力における同相電圧を制御する電圧制御器3と、を有し、電圧比較回路100は、電圧比較器(比較器)1,判定器2および電圧制御器3を有する。比較器1は、差動の入力信号Vip,Vimの高低を比較し、判定器2は、比較器1の動作の遅速を判定して電圧制御器3を制御し、電圧制御器3は、判定器2の出力に従って、入力信号Vip,Vimの同相電圧(コモン電圧)を制御する。なお、クロック発生器200は、電圧比較回路100における比較器1および判定器2に対するクロックを発生する。

【解決手段】比較器1と、前記比較器の応答速度を判定する判定器2と、前記判定器の判定結果に従って、前記比較器の応答速度の遅延を低減するように、前記比較器の複数の入力における同相電圧を制御する電圧制御器3と、を有し、電圧比較回路100は、電圧比較器(比較器)1,判定器2および電圧制御器3を有する。比較器1は、差動の入力信号Vip,Vimの高低を比較し、判定器2は、比較器1の動作の遅速を判定して電圧制御器3を制御し、電圧制御器3は、判定器2の出力に従って、入力信号Vip,Vimの同相電圧(コモン電圧)を制御する。なお、クロック発生器200は、電圧比較回路100における比較器1および判定器2に対するクロックを発生する。

【発明の詳細な説明】

【技術分野】

【0001】

この出願で言及する実施例は、電圧比較回路,A/D変換器および半導体装置に関する。

【背景技術】

【0002】

電圧比較回路は、入力端子に印加されたアナログ信号の高低を判定する機能を持った回路で、A/D(Analog to Digital)変換器を始めとするアナログ回路の重要な構成要素の1つである。

【0003】

電圧比較回路の基本的な動作は、印加された信号の直流電位の高低を判定するもので、例えば、全並列型のDC結合によって、各電圧比較回路で比較基準電圧とアナログ入力信号の電圧の高低を直接比較する。

【0004】

しかしながら、この場合、電圧比較回路の動作範囲の関係で変換可能なアナログ入力信号の電圧範囲が制約を受ける。さらに、各電圧比較回路が異なる判定電圧で動作するため、それぞれの電圧比較回路内部の動作点が異なり、その結果、各電圧比較回路の応答時間に差が生じて、速度的な制約となる。

【0005】

そのため、AC結合を介して動作させる手法が提案されている。すなわち、アナログ信号を入力する時に、容量と電圧比較器(比較器)の入出力端子間を短絡する(一般的に、オートゼロと呼ばれる)手法が知られている。

【0006】

ところで、従来、電圧比較回路,A/D変換器および半導体装置としては、様々なものが提案されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2010−124405号公報

【特許文献2】特開2010−252287号公報

【非特許文献】

【0008】

【非特許文献1】S. Park et al., "A 3.5 GS/s 5-b Flash ADC in 90 nm CMOS," 2006 IEEE Custom Integrated Circuits Conference, pp. 489 - 492, September 2006

【非特許文献2】K. Nagaraj et al., "A 700M Sample/s 6b Read Channel A/D Converter with 7b Servo Mode," IEEE International Solid-State Circuits Conference, vol. XLIII, pp. 426 - 427, February 2000

【非特許文献3】D. Draxelmayr, "A 6b 600MHz 10mW ADC Array in Digital 90nm CMOS," IEEE International Solid-State Circuits Conference, vol. XLVII, pp. 264 - 265, February 2004

【非特許文献4】Y. Chen et al., "A 9b 100MS/s 1.46mW SAR ADC in 65nm CMOS," 2009 IEEE Asian Solid-State Circuits Conference, pp. 145 - 148, Nov. 2009

【非特許文献5】M. Kijima et al., "A 6b 3GS/s Flash ADC with Background Calibration," 2009 IEEE Custom Integrated Circuits Conference (CICC), pp. 283 - 286, 2009

【発明の概要】

【発明が解決しようとする課題】

【0009】

前述したように、アナログ信号を入力する時に、容量と比較器の入出力端子間を短絡するオートゼロ手法が知られている。

【0010】

しかしながら、オートゼロ手法は、比較器の出力インピーダンスとスイッチのオン抵抗が加算されて容量を充電するため、時定数が大きくなって時間がかかる。また、比較器には、オートゼロを行っている間も電流が流れるため、消費電力の面から好ましくない。

【0011】

また、近年、ラッチ型電圧比較器を使用して電源電圧の約半分(Vdd/2)のレベルをコモン電圧(同相電圧)にバイアスする手法が主流となっている。この場合、比較器のオフセットはキャンセルされないため、例えば、オフセットキャンセル機能が比較器に組み込まれる。

【0012】

ところで、比較器を並列に配置して動作させる並列型(フラッシュ型)A/D変換器では、比較器のオフセットは線形性に直接影響し、最悪の場合は隣接する比較器の判定点が逆転して単調性を保つことができない虞がある。

【0013】

一般的な逐次比較型A/D変換器、例えば、多チャンネルをタイムインターリーブせずに単一チャネルで使用する場合、比較器自体のオフセットは全ての判定を同一の比較器で行うため、単純にA/D変換結果のオフセットとして現れ、線形性に影響を与えない。

【0014】

しかしながら、同相電圧(コモン電圧Vcm)の設定が適切でないと、例えば、製造ばらつき等によってpMOSとnMOSトランジスタの特性に大きなアンバランスが発生した場合には、電源電圧の半分(Vdd/2)に設定されたVcmは必ずしも最適点ではない。

【0015】

すなわち、比較器の差動入力信号の電位差が1mVであっても同相電圧が異なると、例えば、差動入力信号(Vip,Vim)が(0,1),(100,101),(200,201),(300,301),(400,401)mVでは、比較器の動作速度は異なる。

【0016】

さらに、同相電圧の設定によっては、比較器の応答速度の低下だけでなく、場合によっては比較器の誤判定を招く虞もある。

【課題を解決するための手段】

【0017】

一実施形態によれば、比較器と、前記比較器の応答速度を判定する判定器と、電圧制御器と、を有することを特徴とする電圧比較回路が提供される。

【0018】

前記電圧制御器は、前記判定器の判定結果に従って、前記比較器の応答速度の遅延を低減するように、前記比較器の複数の入力における同相電圧を制御する。

【発明の効果】

【0019】

開示の電圧比較回路,A/D変換器および半導体装置は、比較器に対して最適な同相電圧を与えることによって、動作速度を向上することができるという効果を奏する。

【図面の簡単な説明】

【0020】

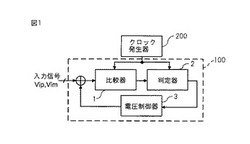

【図1】図1は、本実施例に係る電圧比較回路の全体構成を概略的に示すブロック図である。

【図2】図2は、図1に示す電圧比較回路における比較器の一例を示す回路図である。

【図3】図3は、電圧比較回路の第1実施例を示すブロック図である。

【図4】図4は、図3に示す判定器の動作を説明するためのタイミング図である。

【図5】図5は、図3に示す判定器における判定処理の一例を説明するためのフローチャートである。

【図6】図6は、図5に示す判定処理を説明するための図である。

【図7】図7は、図3に示す判定器における判定処理の他の例を説明するためのフローチャートである。

【図8】図8は、図7に示す判定処理を説明するための図である。

【図9】図9は、本実施例に係る電圧比較回路を適用した逐次比較型A/D変換器の一例を示すブロック図である。

【図10】図10は、図9に示す逐次比較型A/D変換器の動作の一例を説明するためのタイミング図である。

【図11】図11は、図9に示す逐次比較型A/D変換器の動作の他の例を説明するためのタイミング図である。

【図12】図12は、本実施例に係る電圧比較回路を適用したフラッシュ型A/D変換器の一例を示すブロック図である。

【図13】図13は、図12に示すフラッシュ型A/D変換器における1つの電圧比較回路を示すブロック図である。

【図14】図14は、電圧比較回路の第2実施例を示すブロック図である。

【図15】図15は、本実施例に係る電圧比較回路を用いたA/D変換器を適用した半導体装置の一例を示すブロック図である。

【発明を実施するための形態】

【0021】

以下、電圧比較回路,A/D変換器および半導体装置の実施例を、添付図面を参照して詳述する。図1は、本実施例に係る電圧比較回路の全体構成を概略的に示すブロック図である。図1において、参照符号100は電圧比較回路を示し、200はクロック発生器を示す。

【0022】

図1に示されるように、電圧比較回路100は、電圧比較器(比較器)1,判定器2および電圧制御器3を有する。比較器1は、差動の入力信号Vip,Vimの高低を比較し、判定器2は、比較器1の動作の遅速を判定して電圧制御器3を制御する。

【0023】

電圧制御器3は、判定器2の出力に従って、入力信号Vip,Vimの同相電圧(コモン電圧)を制御する。なお、クロック発生器200は、電圧比較回路100における比較器1および判定器2に対するクロック(φC)を発生する。

【0024】

このように、本実施例の電圧比較回路100は、同相電圧制御対象の比較器1、比較器1の出力の遅延時間を判定する判定器2、判定器2の判定結果に基づいてその判定結果を比較器1の入力信号Vip,Vimの同相電圧に帰還して反映させる電圧制御器3を有する。

【0025】

ここで、比較器1は、例えば、ストロングアーム型比較器等の比較器を適用することができ、この比較器1に対して判定器2および電圧制御器3を追加して最速の応答時間が得られる同相電圧を自動的に与えるループを形成する。

【0026】

これにより、差動の入力信号Vip,Vimには、電圧制御器3からの同相電圧が加えられて、比較器1へ入力される。

【0027】

比較器1は、この同相電圧が加えられた入力信号Vip,Vimに対して、クロック発生器200からのクロックに同期した比較(判定)を行う。なお、電圧制御器3の初期値としては、例えば、最低の同相電圧を与える。また、差動電圧(VipとVimの差電圧)は、一定電圧とする。

【0028】

判定器2は、比較器1の遅延時間をtd0として保持(記憶)し、さらに、同相電圧を少しだけ上昇させた後、比較器1に判定させる。そして、同相電圧を上昇させる前に記憶した遅延時間td0と、同相電圧を上昇させた後の遅延時間tdxの遅速を判定する。

【0029】

ここで、td0>tdxのとき、td0=tdxとし、電圧制御器3の出力を変更せずに、比較器1が次の判定を行う。また、判定器2は、更新されたtd0と遅延時間tdxを比較する。

【0030】

一方、Td0<tdxのとき(前よりも遅くなった場合)、td0は更新せず、電圧制御器3によって同相電圧を上昇させる。そして、Td0<tdxを複数回観測したときは、ループを終了させる。このループによって、最終的には、最速遅延時間となる(遅延時間が最も短くなる)同相電圧を得ることができる。

【0031】

図2は、図1に示す電圧比較回路における比較器の一例を示す回路図であり、ストロングアーム型の比較器を示すものである。図2に示されるように、比較器1は、複数のpMOS(pチャネル型MOS)トランジスタTp11〜Tp16および複数のnMOS(nチャネル型MOS)トランジスタTn11〜Tn15を有する。

【0032】

ここで、トランジスタTp11,Tp12,Tp15,Tp16は、プルアップ用トランジスタを示し、リセット時にクロックφCが低レベル『L』となってオン(on)し、各トランジスタのドレインのノードを高電位電源線Vddの電圧にプルアップする。

【0033】

また、比較動作を実行する場合、トランジスタTp11,Tp12,Tp15,Tp16は、クロックφCが高レベル『H』となってオフ(off)し、差動の入力信号Vip,Vimを比較および判定して、差動の出力信号Vop,Vomを出力する。

【0034】

ここで、入力信号VipおよびVimは、差動対トランジスタTn13およびTn14のゲートに入力される。また、出力信号Vop並びにVomは、Tp13のドレインおよびTn11のドレインの共通接続ノード、並びに、Tp14のドレインおよびTn12のドレインの共通接続ノードから出力される。

【0035】

なお、トランジスタTn15は、そのゲートに入力されるクロックφCに従って、φCが『H』のときにオンして接地(GND)へ電流を流し、φCが『L』のときにオフしてリセットする。

【0036】

なお、図2に示す比較器1は、単なる例であり、例えば、pチャネル型およびnチャネル型トランジスタを逆にした相補の回路を始めとする様々な回路でもよいのはもちろんである。

【0037】

図3は、電圧比較回路の第1実施例を示すブロック図であり、図4は、図3に示す判定器の動作を説明するためのタイミング図である。

【0038】

図3において、参照符号21はエクスクルーシブノア(EXNOR)ゲート、22はフリップフロップ(FF)、23は制御回路(CNTL:アップダウンカウンタ)、24はデマルチプレクサ(D−MPX)、そして、25は遅延器を示す。

【0039】

ここで、EXNORゲート21は、比較器1の応答を検出する応答検出器として機能する。また、FF22、制御回路23,D−MPX24,および,D−MPX24から遅延器25への制御経路(並びに、D/A変換器3への制御経路)は、ループ処理回路を構成する。

【0040】

図4に示されるように、比較器1の出力信号Vop,Vomは、φC=『L』のリセット状態時は、トランジスタTp12,Tp15によりプルアップされて『H』となっている。そして、クロックφCが『L』から『H』に立ち上がると、比較器1は比較(判定)動作を開始する。

【0041】

比較器1の出力信号Vop,Vomは、最初は『H』であるが、Vop,Vomの差分に正帰還が作用して、一方が『H』で他方が『L』に振り分けられる。このVop,Vomが後段のEXNORゲート21によって、VO=『L』として出力される。

【0042】

すなわち、EXNORゲート21は、異なるレベルのVop,Vomにより比較器1の判定が完了したことを検出し、低レベル『L』の出力信号VOを出力する。この低レベル『L』の信号VOは、FF22のD端子に入力される。

【0043】

一方、クロックφCは、判定器2の遅延器25にも入力される。遅延器25は、VddとGND間に直列接続された可変抵抗Rd,pMOSトランジスタTp25およびnMOSトランジスタTn25を有する。ここで、可変抵抗Rdの抵抗値は、D−MPX24を介した制御回路23の出力により制御される。

【0044】

すなわち、図4に示されるように、遅延器25の出力信号V1は、クロックφCの『H』への立ち上がりを受けて『L』に変化し、これがFF22の入力クロック(CK)として使われる。ここで、FF22は、クロック端子CKに入力された信号V1の『H』から『L』への立ち下がりで、データ入力Dに入力された信号VOを取り込む。

【0045】

遅延器25の出力信号V1の立ち下がりに対して、比較器1の信号VOの遅延が遅い(遅延時間が長い)場合には、VO=『H』を取り込むことになり、FF22は、『H』の信号Odを出力する。

【0046】

すなわち、遅延器25の遅延時間Td(V1)よりも比較器1側の遅延時間td(V0)の方が大きい(Td(V1)>td(V0))場合、信号Odは『H』になる。

【0047】

一方、遅延器25の出力信号V1の立ち下がりに対して、比較器1の信号VOの遅延が速い(遅延時間が短い)場合には、VO=『L』を取り込むことになり、FF22は、『L』の信号Odを出力する。

【0048】

すなわち、遅延器25の遅延時間Td(V1)よりも比較器1側の遅延時間td(V0)の方が小さい(Td(V1)<td(V0))場合、信号Odは『L』になる。

【0049】

このFF22の出力信号Odは、後段の制御回路23に取り込まれる。ここで、制御回路23は、例えば、アップダウンカウンタで構成され、信号OdのH/Lをカウントする。

【0050】

従って、例えば、Od=『H』(すなわち、比較器1の方が遅延器25よりも速い、或いは、遅延器25の方が比較器1よりも遅い)によってカウントアップされると、可変抵抗Rdの抵抗値を小さくなるように制御する。これによって、遅延器25の遅延時間が短くなる。

【0051】

これを繰り返すことによって、遅延器25の遅延時間は徐々に短縮され、比較器1の遅延時間より短くなって、Od=『L』を出力する。制御回路23は、Od=『L』を受けて電圧制御器(同相電圧制御用のD/A(Digital to Analog)変換器)3を制御する。

【0052】

ここで、D/A変換器3は、最初は最低電圧を出力した状態からスタートする。なお、制御回路23は、カウントダウンすることによってD/A変換器(負論理)3の入力コード(Din)を下げる。その結果、D/A変換器3の出力電圧Voutは、上昇する。

【0053】

そして、D/A変換器3の出力電圧Voutが同相電圧として比較器1に与えられ、再度、クロックφCによって判定を行うループが実行される。このループを繰り返し、2回連続でOd=『L』(すなわち、比較器1の方が遅延器25よりも速い)が得られたところで、D/A変換器3の入力コードを『1』だけ戻してループを終了させる。これによって、比較器1の同相電圧は、比較器1の遅延時間が最小となる電圧へ収束する。

【0054】

図5は、図3に示す判定器における判定処理の一例を説明するためのフローチャートであり、図6は、図5に示す判定処理を説明するための図である。すなわち、図5に示すフローチャートは、上述した判定器の処理をまとめたものである。

【0055】

図5に示されるように、判定器2の判定処理が開始すると、ステップST11において、D−MPX24の出力信号Din=0,Rd=Maxとする。すなわち、ステップST11では、信号Din=0として、D/A変換器3からの同相電圧を最低電圧とし、さらに、遅延器25の可変抵抗Rdの抵抗値を最大にして遅延器25による遅延を最大にする。

【0056】

次に、ステップST12へ進んで、遅延時間の比較、すなわち、FF22による比較器1による遅延時間(信号VO)と遅延器25による遅延時間(信号V1)の比較を行う。さらに、ステップST13へ進んで、FF22の出力信号Od=『L』かどうかを判定する。

【0057】

ステップST13において、Od=『L』であると判定すると、すなわち、比較器1の方が遅延器25よりも速いと判定すると、ステップST15へ進んで、遅延器25の可変抵抗Rdの抵抗値を1段階下げる。

【0058】

すなわち、ステップST15では、遅延器25による遅延時間を小さく(速度アップ)してステップST12へ戻り、同様の処理を繰り返す。これを繰り返すことによって、遅延器25の遅延時間は徐々に短縮され、比較器1の遅延時間より短くなって、Od=『H』を出力する。

【0059】

そして、ステップST13において、Od=『L』ではない(Od=『H』である)と判定すると、ステップST14へ進んで、Od(n−1)=『L』かどうかを判定する。ここで、Od(n−1)は前回の判定結果を示す。

【0060】

ステップST14において、Od(n−1)=『L』であると判定すると、ステップST16へ進んで、信号Dinを1段階下げる。すなわち、D/A変換器3の入力コード(Din)を1段階下げて、D/A変換器3の出力電圧Voutを上昇(比較器1の入力Vip,Vimにおける同相電圧を上昇)させ、ステップST12へ戻り、同様の処理を繰り返す。

【0061】

そして、ステップST14において、Od(n−1)=『L』ではない(Od(n−1)=『H』である)と判定すると、すなわち、2回連続してOd=『L』(比較器1の方が遅延器25よりも速い)と判定すると、ステップST17へ進む。

【0062】

ステップST17では、D−MPX24の出力信号Dinを1段階上げて、すなわち、D/A変換器3の出力電圧Voutを1段階分戻し、比較器1の入力Vip,Vimにおける同相電圧を制御して処理を終了する。

【0063】

以上により、図6に示されるように、同相電圧(Vcm)を、遅延Tdが最小となる最適な電圧へ収束させることが可能になる。なお、図5のフローチャートにおいて、ステップST13およびST14でOd=『L』を2回検出し、その後、ステップST17でD/A変換器3による同相電圧を1段階分戻しているが、これは適宜変更することができる。

【0064】

すなわち、同相電圧を、最下点からスタートして遅延時間tdが最小となる電圧まで上昇した時点で終了させてもよく、また、例えば、Od=『L』を3回検出した後に、D/A変換器3による同相電圧を2段階分戻す等の変更も可能である。

【0065】

このように、図5および図6を参照して説明した処理は、前述したループ処理回路により、同相電圧が最適値になったときに、そのループ処理(判定処理)を終了させるようになっている。次に、図7および図8を参照して説明する処理は、ループ処理回路により、同相電圧が最適値になった後も、ループ処理を継続させるものである。

【0066】

図7は、図3に示す判定器における判定処理の他の例を説明するためのフローチャートであり、図8は、図7に示す判定処理を説明するための図である。ここで、図7と前述した図5との比較から明らかなように、ステップST11〜ST17は共通である。

【0067】

図7に示されるように、ステップST14において、Od(n−1)=『L』であると判定すると、前述したように、ステップST17へ進んで、D−MPX24の出力信号Dinを1段階上げて、ステップST18へ進む。

【0068】

すなわち、ステップST14において、2回連続してOd=『L』(比較器1の方が遅延器25よりも速い)と判定すると、ステップST17へ進んで、D/A変換器3の入力コードDinを1段階下げて、D/A変換器3により同相電圧を1段階分下げる(戻す)。

【0069】

さらに、ステップST18へ進んで、遅延時間の比較、すなわち、FF22による比較器1による遅延時間(信号VO)と遅延器25による遅延時間(信号V1)の比較を行う。そして、ステップST19へ進んで、FF22の出力信号Od=『L』かどうかを判定する。

【0070】

ステップST19において、Od=『L』ではない(Od=『H』である)と判定すると、すなわち、比較器1の方が遅延器25よりも遅いと判定すると、ステップST20へ進んで、遅延器25の可変抵抗Rdの抵抗値を1段階上昇させる。

【0071】

すなわち、ステップST20では、遅延器25による遅延時間を大きく(速度ダウン)してステップST18へ戻り、同様の処理を繰り返す。これを繰り返すことによって、遅延器25の遅延時間は徐々に延長され、比較器1の遅延時間より長くなって、Od=『L』を出力する。

【0072】

そして、ステップST19において、Od=『L』であると判定すると、ステップST21へ進んで、遅延時間を比較する。さらに、ステップST22へ進んで、Od=『L』かどうかを判定する。

【0073】

ステップST22において、Od=『L』ではない(Od=『H』である)と判定すると、すなわち、比較器1の方が遅延器25よりも遅いと判定すると、ステップST23へ進む。ステップST23では、D/A変換器3の入力コードDinを1段階上げて、D/A変換器3による同相電圧を1段階低下させて、ステップST23へ戻り、同様の処理を繰り返す。

【0074】

そして、ステップST22において、Od=『L』であると判定すると、すなわち、比較器1の方が遅延器25よりも速いと判定すると、前述したステップST16を介してステップST12へ戻り、同様の処理を繰り返す。

【0075】

以上により、図8に示されるように、遅延器25の可変抵抗Rdの抵抗値を最大側から順に小さくした後、小さくなり過ぎた可変抵抗Rdの抵抗値を戻すことで、比較器1の同相電圧を、比較器1の遅延時間tdが最小となる電圧へ収束させることができる。

【0076】

このように、図7および図8を参照して説明した処理は、前述したループ処理回路により、同相電圧が最適値になった後も、ループ処理を継続させるようになっている。これにより、例えば、本実施例の電圧比較回路が適用される装置の電源電圧の変動、或いは、周囲の温度変化等により同相電圧の最適値が変化しても対応することが可能になる。

【0077】

以上のように、比較器に対して最適な同相電圧を与えることができ、製造ばらつき、並びに、実動作中における電圧や温度の変動に対する耐性を改善し、精度および動作速度を向上することが可能になる。なお、上述した図5および図7のフローチャートは、単なる例であり、様々な変更が可能なのはいうまでもない。

【0078】

図9は、本実施例に係る電圧比較回路を適用した逐次比較型A/D変換器の一例を示すブロック図であり、図10は、図9に示す逐次比較型A/D変換器の動作を説明するためのタイミング図である。

【0079】

図9において、参照符号30pは正論理側の容量回路、30mは負論理側の容量回路、および、300はSAR(Successive Approximation Register)論理回路を示す。

【0080】

図9に示されるように、逐次比較型A/D変換器において、前述した第1実施例の電圧比較回路を構成する比較器1,判定器2およびD/A変換器(電圧制御器)3が適用されている。なお、D/A変換器3は、正および負論理側の容量回路30pおよび30mに対して、それぞれ設けられている。

【0081】

図9および図10に示されるように、逐次比較型A/D変換器において、例えば、制御信号φAが『H』となる期間(サンプリング期間)、アナログ信号Vin(Vip,Vim)は、容量1C,2C,3C,8C,16C,32Cの一端に与えられる。

【0082】

この時、差動型の比較器1の両入力端子は、D/A変換器3によって所定の同一の電圧が同相電圧として与えられる。これによって、各容量1C,2C,3C,8C,16C,32Cには、アナログ信号Vinの電圧とD/A変換器3からの同相電圧に対応した電荷が充電される。

【0083】

ここで、信号φAが『H』の期間はサンプリング期間であるため、比較器1は、本来、動作する必要はない。そこで、このサンプリング期間において、タイミングTaでクロックφCを『H』に立ち上げて比較器1に判定動作を行わせる。

【0084】

なお、信号φAが『L』の期間(判定期間)におけるタイミングT5〜T0は、それぞれ制御信号φ0〜φ5によりスイッチSW0〜SW5の接続を制御した状態で行う比較器1の判定動作を行わせるものである。

【0085】

すなわち、逐次比較型A/D変換器の判定期間(信号φAが『L』の期間)における制御信号φ0〜φ5によるスイッチSW0〜SW5の制御は、通常の逐次比較型A/D変換器と同様であり、その説明は省略する。

【0086】

また、図9は、1C,2C,3C,8C,16C,32Cの容量を6つのスイッチSW0〜SW5で接続制御する例を示しているが、最小の容量値のものを2つ設け、1C,1C,2C,3C,8C,16C,32Cの容量を7つのスイッチで制御してもよい。

【0087】

図11は、図9に示す逐次比較型A/D変換器の動作の他の例を説明するためのタイミング図である。図11と上述した図10との比較から明らかなように、図11では、同相電圧を制御するために行う比較器1による判定動作を、信号φAが『H』のサンプリング期間ではなく、その直後に行うようになっている。

【0088】

すなわち、同相電圧を制御するための比較器1の判定動作を、信号φAが『L』になるサンプリング終了後から比較器1によるA/D変換を行うための比較動作を開始するタイミングT0までの間、すなわち、タイミングTbで行うようになっている。

【0089】

このように、同相電圧を制御するための比較器1の判定動作をタイミングTbで行うと、容量1C,2C,3C,8C,16C,32Cに蓄えられた後の入力信号Vip,Vimの同相電圧を制御することが可能になる。

【0090】

以上において、比較器1の入力信号Vip,Vimに与える同相電圧は、上述した図5〜図8を参照して説明した判定処理(ループ処理)によって、比較器1により最速の応答時間が得られる電圧へ収束する。

【0091】

なお、時間ごとに異なるアナログ信号が印加された場合でも、各タイミングTa,Tbで比較器1に入力される電圧は、常に、D/A変換器3によって決まるため、上述のループを動作させることができる。

【0092】

また、上述の設定では、通常の逐次比較型A/D変換器のサンプリング期間中に同相電圧の制御を行うため、実際に行うA/D変換動作に余分な期間を必要としないため、性能を犠牲にすることなく、常時、バックグラウンドでこのループを回すことが可能である。

【0093】

なお、図9において、例えば、アナログ信号Vinを固定し、信号φ0〜φ5で制御されるスイッチをVinの導通状態で固定すれば、通常動作時では6回比較動作を行う比較器1の判定処理を、全て同相電圧を制御するためのループに使用することが可能となる。

【0094】

この場合、同相電圧の制御を行うための期間は、逐次比較型A/D変換器による本来のA/D変換動作は行えないため、フォアグラウンド処理に限定されることになる。

【0095】

図12は、本実施例に係る電圧比較回路を適用したフラッシュ型A/D変換器の一例を示すブロック図であり、図13は、図12に示すフラッシュ型A/D変換器における1つの電圧比較回路を示すブロック図である。

【0096】

図12において、参照符号400は抵抗ラダーを示し、500はエンコーダを示す。ここで、本実施例の電圧比較回路100は、抵抗ラダー400とエンコーダ500との間に複数個設けられている。なお、同相電圧の制御は、フォアグラウンドで行うようになっている。

【0097】

各電圧比較回路100は、高電位の基準電圧Vrefpと低電位の基準電圧Vrefmとの間に直列接続された複数の抵抗における隣接する抵抗の接続ノード(タップ)からの基準電圧と、入力アナログ信号Vinを受け取り、その出力信号をエンコーダ500へ出力する。

【0098】

すなわち、図12に示されるように、フラッシュ型A/D変換器は、抵抗ラダー400により基準電圧Vrefp〜Vrefmを分圧して各電圧比較回路100の比較基準電圧として印加する。

【0099】

各電圧比較回路100は、抵抗ラダー400からの比較基準電圧とアナログ信号Vinを比較し、その比較結果(出力信号)は、エンコーダ500に入力される。そして、エンコーダ500は、アナログ信号Vinをデジタル変換した出力Doutを出力する。

【0100】

図13に示されるように、各電圧比較回路100は、比較器1、判定器2、D/A変換器(電圧制御器)3、容量Cp,Cm、および、スイッチSW11,SW12,SW21,SW22,SW31,SW32を有する。

【0101】

なお、図13において、比較器1は、前述した図2におけるトランジスタTp12,Tp15に相当するスイッチを有していないが、図2の比較器をそのまま適用することができるのはいうまでもない。

【0102】

ここで、同相電圧の制御処理(判定処理)は、例えば、図7を参照して説明した処理をそのまま適用することができる。すなわち、図13において、まず、D/A変換器3にDin=0、xCLK’=『H』を与えて処理を開始する。なお、D/A変換器3は、正論理を想定する。

【0103】

xCLK’=『H』とすることにより、スイッチSW31,SW32がオンし、アナログ信号Vinに依存することなく、比較器1の双方の入力Vip,Vimには、D/A変換器3の出力が与えられる。

【0104】

次に、クロックCLK(クロックφCに対応)を通常モードと同様に与えて、比較器1が判定を実行する。ここで、図7を参照して説明したのと同様に、判定器2によって遅延時間を比較する。なお、判定器2の構成は、前述した図3と同様である。

【0105】

そして、判定器2の結果をD/A変換器3または判定器2における遅延器25に与え、図7の処理を実施することによって、最終的に最適な同相電圧に収束する。なお、各電圧比較回路100に対して判定器2を個別に待たせれば、全ての電圧比較回路100が同時並行して処理することができるが、回路規模が大きくなる。

【0106】

そこで、例えば、1つの判定器2の接続を切り替えて、1つの電圧比較回路100(比較器1)ごとに処理すれば、処理時間は長くなるが回路規模を抑えることができる。いずれの構成にしても各比較器の同相電圧は最適点が与えられ、これによって高速動作が可能となる。なお、キャリブレーションが完了した後、xCLK’はCLKの反転レベルの信号(xCLK)として与えることができる。

【0107】

図14は、電圧比較回路の第2実施例を示すブロック図である。図14と前述した図3との比較から明らかなように、本第2実施例の電圧比較回路100では、D−MPX24の出力信号により抵抗値が制御される可変抵抗Rdの代わりに、可変容量Cdが設けられている。

【0108】

すなわち、クロックφCを受け取るインバータTp25,Tn25は、VddとGNDとの間に直接設けられ、FF22のクロック端子CKに入力されるインバータの出力信号V1のノードとGNDとの間に、負荷として可変容量Cdが設けられている。この可変容量Cdは、D−MPX24の出力信号により、その容量値が制御されるようになっている。

【0109】

ここで、図3に示す電圧比較回路の第1実施例では、遅延時間を低下させるために可変抵抗Rdの抵抗値を小さくしていたが、本第2実施例の電圧比較回路では、遅延時間を低下させるために可変容量Cdの容量値を小さくすることになる。

【0110】

なお、本第2実施例の電圧比較回路では、前述した図5および図7に示す処理における可変抵抗Rdの抵抗値の段階的な上昇および低下を、可変容量Cdの容量値の段階的な上昇および低下に置き換えれば、そのまま適用することができる。また、図3および図4に示す電圧比較回路は、単なる例であり、様々な変形が可能なのはいうまでもない。

【0111】

このように、本実施例の電圧比較回路、或いは、A/D変換器を使用することにより、比較器の同相電圧を自動的に最適点に設定できるため、製造時の素子ばらつきや、電源電圧および温度等の動作時の環境変化を補償することができる。その結果、安定した動作を実現することが可能になる。また、同相電圧に起因する要求性能を満たさない半導体装置を低減することになるため、歩留まりの向上にも貢献することができる。

【0112】

図15は、本実施例に係る電圧比較回路を用いたA/D変換器を適用した半導体装置の一例を示すブロック図であり、デジタルTVチューナ(通信システム)50を示すものである。

【0113】

図15において、参照符号51はアンテナ、52は高周波増幅器、53a,53bはミキサ、54は周波数シンセサイザ、55a,55bは低域通過フィルタ、および、56a,56bは低周波増幅器を示す。さらに、参照符号57a,57bはA/D変換器を示し、58はデジタルブロックを示す。

【0114】

図15に示されるように、デジタルTVチューナ50は、アンテナ51により電波を受信し、高周波増幅器52により信号処理に適するレベルまで信号振幅を増幅する。高周波増幅器52の出力信号は、ミキサ53a,53bにおいて、周波数シンセサイザ54からの90度位相をずらした信号と合成され、Ich,Qch信号が生成される。

【0115】

さらに、ミキサ53a,53bで生成されたIch,Qch信号は、低域通過フィルタ55a,55bおよび低周波増幅器56a,56bにより変換域(信号振幅)と信号帯域が調整され、A/D変換器57a,57bに与えられる。

【0116】

そして、A/D変換器57a,57bにおいて、入力されたアナログ信号がデジタル信号へ変換され、そのデジタル信号がデジタルブロック58へ出力される。このデジタルブロック58において、所定の処理が行われ、例えば、映像および音声が表示装置およびスピーカ等から出力される。

【0117】

ここで、図15で使用するA/D変換器57a,57bとしては、前述した図9に示す逐次比較型A/D変換器、或いは、図12に示すフラッシュ型A/D変換器等の本実施例の電圧比較回路を適用した様々なA/D変換器である。

【0118】

なお、A/D変換器57a,57bの前段がアナログ信号を処理するアナログ信号処理部となり、A/D変換器57a,57bの後段が、デジタル信号処理部(デジタルブロック58)となる。

【0119】

また、図15に示すデジタルTVチューナは、本実施例の電圧比較回路、或いは、A/D変換器を適用した半導体装置(システム)の単なる一例であり、本実施例は、様々な半導体装置に対して幅広く適用することができる。

【0120】

以上の実施例を含む実施形態に関し、さらに、以下の付記を開示する。

(付記1)

比較器と、

前記比較器の応答速度を判定する判定器と、

前記判定器の判定結果に従って、前記比較器の応答速度の遅延を低減するように、前記比較器の複数の入力における同相電圧を制御する電圧制御器と、

を有することを特徴とする電圧比較回路。

【0121】

(付記2)

前記判定器は、前記比較器の応答速度の判定を複数回行う、

ことを特徴とする付記1に記載の電圧比較回路。

【0122】

(付記3)

前記判定器は、

前記比較器の応答を検出する応答検出器と、

第1制御信号の遅延を制御する遅延器と、

前記遅延された第1制御信号と前記検出された前記比較器の応答の時間差を低減するように前記遅延器を制御して、前記同相電圧を最適値に収束させるループ処理を行うループ処理回路と、

を有することを特徴とする付記1または付記2に記載の電圧比較回路。

【0123】

(付記4)

前記ループ処理回路は、前記同相電圧が前記最適値になったとき、前記ループ処理を終了させる、

ことを特徴とする付記3に記載の電圧比較回路。

【0124】

(付記5)

前記ループ処理回路は、前記同相電圧が前記最適値になった後も、前記ループ処理を継続させる、

ことを特徴とする付記3に記載の電圧比較回路。

【0125】

(付記6)

前記遅延器は、増幅器と、前記ループ処理回路の出力に応じて、前記増幅器に流れる電流を制御する可変抵抗と、を有し、

前記ループ処理回路は、前記可変抵抗の抵抗値を制御して前記同相電圧を最適値に収束させる、

ことを特徴とする付記3乃至付記5のいずれか1項に記載の電圧比較回路。

【0126】

(付記7)

前記遅延器は、増幅器と、前記ループ処理回路の出力に応じて、前記増幅器の負荷を制御する可変容量と、を有し、

前記ループ処理回路は、前記可変容量の容量値を制御して前記同相電圧を最適値に収束させる、

ことを特徴とする付記3乃至付記5のいずれか1項に記載の電圧比較回路。

【0127】

(付記8)

前記電圧制御器は、前記判定器の判定結果に従って前記比較器の入力に与える前記同相電圧を制御するD/A変換器である、

ことを特徴とする付記1乃至付記7のいずれか1項に記載の電圧比較回路。

【0128】

(付記9)

前記電圧制御器は、前記比較器の差動入力における同相電圧を制御する、

ことを特徴とする付記1乃至付記8のいずれか1項に記載の電圧比較回路。

【0129】

(付記10)

付記1乃至付記9のいずれか1項に記載の電圧比較回路を有するA/D変換器であって、

前記A/D変換器により、アナログ信号をサンプリングしている間に、前記比較器を動作させて前記同相電圧の制御を行う、

ことを特徴とするA/D変換器。

【0130】

(付記11)

付記1乃至付記9のいずれか1項に記載の電圧比較回路を有するA/D変換器であって、

前記A/D変換器により、サンプリングが終了した後から前記比較器によりA/D変換を行うための比較動作を開始するまでの間に、前記比較器を動作させて前記同相電圧の制御を行う、

ことを特徴とするA/D変換器。

【0131】

(付記12)

前記A/D変換器は、逐次比較型A/D変換器であり、

前記比較器は、ストロングアーム型比較器である、

ことを特徴とする付記10または付記11に記載のA/D変換器。

【0132】

(付記13)

アナログ信号を処理するアナログ信号処理部と、

前記アナログ信号処理部からのアナログ信号をデジタル信号へ変換する、付記10乃至付記12のいずれか1項に記載のA/D変換器と、

前記A/D変換器からのデジタル信号を処理するデジタル信号処理部と、

を有することを特徴とする半導体装置。

【符号の説明】

【0133】

1 比較器(電圧比較器)

2 判定器

3 電圧制御器(D/A変換器)

21 エクスクルーシブノア(EXNOR)ゲート

22 フリップフロップ(FF)

23 制御回路(CNTL:アップダウンカウンタ)

24 デマルチプレクサ(D−MPX)

25 遅延器

30p,30m 容量回路

50 デジタルTVチューナ(通信システム)

51 アンテナ

52 高周波増幅器

53a,53b ミキサ

54 周波数シンセサイザ

55a,55b 低域通過フィルタ

56a,56b 低周波増幅器

57a,57b A/D変換器

58 デジタルブロック

100 電圧比較回路

200 クロック発生器

300 SAR論理回路

400 抵抗ラダー

500 エンコーダ

【技術分野】

【0001】

この出願で言及する実施例は、電圧比較回路,A/D変換器および半導体装置に関する。

【背景技術】

【0002】

電圧比較回路は、入力端子に印加されたアナログ信号の高低を判定する機能を持った回路で、A/D(Analog to Digital)変換器を始めとするアナログ回路の重要な構成要素の1つである。

【0003】

電圧比較回路の基本的な動作は、印加された信号の直流電位の高低を判定するもので、例えば、全並列型のDC結合によって、各電圧比較回路で比較基準電圧とアナログ入力信号の電圧の高低を直接比較する。

【0004】

しかしながら、この場合、電圧比較回路の動作範囲の関係で変換可能なアナログ入力信号の電圧範囲が制約を受ける。さらに、各電圧比較回路が異なる判定電圧で動作するため、それぞれの電圧比較回路内部の動作点が異なり、その結果、各電圧比較回路の応答時間に差が生じて、速度的な制約となる。

【0005】

そのため、AC結合を介して動作させる手法が提案されている。すなわち、アナログ信号を入力する時に、容量と電圧比較器(比較器)の入出力端子間を短絡する(一般的に、オートゼロと呼ばれる)手法が知られている。

【0006】

ところで、従来、電圧比較回路,A/D変換器および半導体装置としては、様々なものが提案されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2010−124405号公報

【特許文献2】特開2010−252287号公報

【非特許文献】

【0008】

【非特許文献1】S. Park et al., "A 3.5 GS/s 5-b Flash ADC in 90 nm CMOS," 2006 IEEE Custom Integrated Circuits Conference, pp. 489 - 492, September 2006

【非特許文献2】K. Nagaraj et al., "A 700M Sample/s 6b Read Channel A/D Converter with 7b Servo Mode," IEEE International Solid-State Circuits Conference, vol. XLIII, pp. 426 - 427, February 2000

【非特許文献3】D. Draxelmayr, "A 6b 600MHz 10mW ADC Array in Digital 90nm CMOS," IEEE International Solid-State Circuits Conference, vol. XLVII, pp. 264 - 265, February 2004

【非特許文献4】Y. Chen et al., "A 9b 100MS/s 1.46mW SAR ADC in 65nm CMOS," 2009 IEEE Asian Solid-State Circuits Conference, pp. 145 - 148, Nov. 2009

【非特許文献5】M. Kijima et al., "A 6b 3GS/s Flash ADC with Background Calibration," 2009 IEEE Custom Integrated Circuits Conference (CICC), pp. 283 - 286, 2009

【発明の概要】

【発明が解決しようとする課題】

【0009】

前述したように、アナログ信号を入力する時に、容量と比較器の入出力端子間を短絡するオートゼロ手法が知られている。

【0010】

しかしながら、オートゼロ手法は、比較器の出力インピーダンスとスイッチのオン抵抗が加算されて容量を充電するため、時定数が大きくなって時間がかかる。また、比較器には、オートゼロを行っている間も電流が流れるため、消費電力の面から好ましくない。

【0011】

また、近年、ラッチ型電圧比較器を使用して電源電圧の約半分(Vdd/2)のレベルをコモン電圧(同相電圧)にバイアスする手法が主流となっている。この場合、比較器のオフセットはキャンセルされないため、例えば、オフセットキャンセル機能が比較器に組み込まれる。

【0012】

ところで、比較器を並列に配置して動作させる並列型(フラッシュ型)A/D変換器では、比較器のオフセットは線形性に直接影響し、最悪の場合は隣接する比較器の判定点が逆転して単調性を保つことができない虞がある。

【0013】

一般的な逐次比較型A/D変換器、例えば、多チャンネルをタイムインターリーブせずに単一チャネルで使用する場合、比較器自体のオフセットは全ての判定を同一の比較器で行うため、単純にA/D変換結果のオフセットとして現れ、線形性に影響を与えない。

【0014】

しかしながら、同相電圧(コモン電圧Vcm)の設定が適切でないと、例えば、製造ばらつき等によってpMOSとnMOSトランジスタの特性に大きなアンバランスが発生した場合には、電源電圧の半分(Vdd/2)に設定されたVcmは必ずしも最適点ではない。

【0015】

すなわち、比較器の差動入力信号の電位差が1mVであっても同相電圧が異なると、例えば、差動入力信号(Vip,Vim)が(0,1),(100,101),(200,201),(300,301),(400,401)mVでは、比較器の動作速度は異なる。

【0016】

さらに、同相電圧の設定によっては、比較器の応答速度の低下だけでなく、場合によっては比較器の誤判定を招く虞もある。

【課題を解決するための手段】

【0017】

一実施形態によれば、比較器と、前記比較器の応答速度を判定する判定器と、電圧制御器と、を有することを特徴とする電圧比較回路が提供される。

【0018】

前記電圧制御器は、前記判定器の判定結果に従って、前記比較器の応答速度の遅延を低減するように、前記比較器の複数の入力における同相電圧を制御する。

【発明の効果】

【0019】

開示の電圧比較回路,A/D変換器および半導体装置は、比較器に対して最適な同相電圧を与えることによって、動作速度を向上することができるという効果を奏する。

【図面の簡単な説明】

【0020】

【図1】図1は、本実施例に係る電圧比較回路の全体構成を概略的に示すブロック図である。

【図2】図2は、図1に示す電圧比較回路における比較器の一例を示す回路図である。

【図3】図3は、電圧比較回路の第1実施例を示すブロック図である。

【図4】図4は、図3に示す判定器の動作を説明するためのタイミング図である。

【図5】図5は、図3に示す判定器における判定処理の一例を説明するためのフローチャートである。

【図6】図6は、図5に示す判定処理を説明するための図である。

【図7】図7は、図3に示す判定器における判定処理の他の例を説明するためのフローチャートである。

【図8】図8は、図7に示す判定処理を説明するための図である。

【図9】図9は、本実施例に係る電圧比較回路を適用した逐次比較型A/D変換器の一例を示すブロック図である。

【図10】図10は、図9に示す逐次比較型A/D変換器の動作の一例を説明するためのタイミング図である。

【図11】図11は、図9に示す逐次比較型A/D変換器の動作の他の例を説明するためのタイミング図である。

【図12】図12は、本実施例に係る電圧比較回路を適用したフラッシュ型A/D変換器の一例を示すブロック図である。

【図13】図13は、図12に示すフラッシュ型A/D変換器における1つの電圧比較回路を示すブロック図である。

【図14】図14は、電圧比較回路の第2実施例を示すブロック図である。

【図15】図15は、本実施例に係る電圧比較回路を用いたA/D変換器を適用した半導体装置の一例を示すブロック図である。

【発明を実施するための形態】

【0021】

以下、電圧比較回路,A/D変換器および半導体装置の実施例を、添付図面を参照して詳述する。図1は、本実施例に係る電圧比較回路の全体構成を概略的に示すブロック図である。図1において、参照符号100は電圧比較回路を示し、200はクロック発生器を示す。

【0022】

図1に示されるように、電圧比較回路100は、電圧比較器(比較器)1,判定器2および電圧制御器3を有する。比較器1は、差動の入力信号Vip,Vimの高低を比較し、判定器2は、比較器1の動作の遅速を判定して電圧制御器3を制御する。

【0023】

電圧制御器3は、判定器2の出力に従って、入力信号Vip,Vimの同相電圧(コモン電圧)を制御する。なお、クロック発生器200は、電圧比較回路100における比較器1および判定器2に対するクロック(φC)を発生する。

【0024】

このように、本実施例の電圧比較回路100は、同相電圧制御対象の比較器1、比較器1の出力の遅延時間を判定する判定器2、判定器2の判定結果に基づいてその判定結果を比較器1の入力信号Vip,Vimの同相電圧に帰還して反映させる電圧制御器3を有する。

【0025】

ここで、比較器1は、例えば、ストロングアーム型比較器等の比較器を適用することができ、この比較器1に対して判定器2および電圧制御器3を追加して最速の応答時間が得られる同相電圧を自動的に与えるループを形成する。

【0026】

これにより、差動の入力信号Vip,Vimには、電圧制御器3からの同相電圧が加えられて、比較器1へ入力される。

【0027】

比較器1は、この同相電圧が加えられた入力信号Vip,Vimに対して、クロック発生器200からのクロックに同期した比較(判定)を行う。なお、電圧制御器3の初期値としては、例えば、最低の同相電圧を与える。また、差動電圧(VipとVimの差電圧)は、一定電圧とする。

【0028】

判定器2は、比較器1の遅延時間をtd0として保持(記憶)し、さらに、同相電圧を少しだけ上昇させた後、比較器1に判定させる。そして、同相電圧を上昇させる前に記憶した遅延時間td0と、同相電圧を上昇させた後の遅延時間tdxの遅速を判定する。

【0029】

ここで、td0>tdxのとき、td0=tdxとし、電圧制御器3の出力を変更せずに、比較器1が次の判定を行う。また、判定器2は、更新されたtd0と遅延時間tdxを比較する。

【0030】

一方、Td0<tdxのとき(前よりも遅くなった場合)、td0は更新せず、電圧制御器3によって同相電圧を上昇させる。そして、Td0<tdxを複数回観測したときは、ループを終了させる。このループによって、最終的には、最速遅延時間となる(遅延時間が最も短くなる)同相電圧を得ることができる。

【0031】

図2は、図1に示す電圧比較回路における比較器の一例を示す回路図であり、ストロングアーム型の比較器を示すものである。図2に示されるように、比較器1は、複数のpMOS(pチャネル型MOS)トランジスタTp11〜Tp16および複数のnMOS(nチャネル型MOS)トランジスタTn11〜Tn15を有する。

【0032】

ここで、トランジスタTp11,Tp12,Tp15,Tp16は、プルアップ用トランジスタを示し、リセット時にクロックφCが低レベル『L』となってオン(on)し、各トランジスタのドレインのノードを高電位電源線Vddの電圧にプルアップする。

【0033】

また、比較動作を実行する場合、トランジスタTp11,Tp12,Tp15,Tp16は、クロックφCが高レベル『H』となってオフ(off)し、差動の入力信号Vip,Vimを比較および判定して、差動の出力信号Vop,Vomを出力する。

【0034】

ここで、入力信号VipおよびVimは、差動対トランジスタTn13およびTn14のゲートに入力される。また、出力信号Vop並びにVomは、Tp13のドレインおよびTn11のドレインの共通接続ノード、並びに、Tp14のドレインおよびTn12のドレインの共通接続ノードから出力される。

【0035】

なお、トランジスタTn15は、そのゲートに入力されるクロックφCに従って、φCが『H』のときにオンして接地(GND)へ電流を流し、φCが『L』のときにオフしてリセットする。

【0036】

なお、図2に示す比較器1は、単なる例であり、例えば、pチャネル型およびnチャネル型トランジスタを逆にした相補の回路を始めとする様々な回路でもよいのはもちろんである。

【0037】

図3は、電圧比較回路の第1実施例を示すブロック図であり、図4は、図3に示す判定器の動作を説明するためのタイミング図である。

【0038】

図3において、参照符号21はエクスクルーシブノア(EXNOR)ゲート、22はフリップフロップ(FF)、23は制御回路(CNTL:アップダウンカウンタ)、24はデマルチプレクサ(D−MPX)、そして、25は遅延器を示す。

【0039】

ここで、EXNORゲート21は、比較器1の応答を検出する応答検出器として機能する。また、FF22、制御回路23,D−MPX24,および,D−MPX24から遅延器25への制御経路(並びに、D/A変換器3への制御経路)は、ループ処理回路を構成する。

【0040】

図4に示されるように、比較器1の出力信号Vop,Vomは、φC=『L』のリセット状態時は、トランジスタTp12,Tp15によりプルアップされて『H』となっている。そして、クロックφCが『L』から『H』に立ち上がると、比較器1は比較(判定)動作を開始する。

【0041】

比較器1の出力信号Vop,Vomは、最初は『H』であるが、Vop,Vomの差分に正帰還が作用して、一方が『H』で他方が『L』に振り分けられる。このVop,Vomが後段のEXNORゲート21によって、VO=『L』として出力される。

【0042】

すなわち、EXNORゲート21は、異なるレベルのVop,Vomにより比較器1の判定が完了したことを検出し、低レベル『L』の出力信号VOを出力する。この低レベル『L』の信号VOは、FF22のD端子に入力される。

【0043】

一方、クロックφCは、判定器2の遅延器25にも入力される。遅延器25は、VddとGND間に直列接続された可変抵抗Rd,pMOSトランジスタTp25およびnMOSトランジスタTn25を有する。ここで、可変抵抗Rdの抵抗値は、D−MPX24を介した制御回路23の出力により制御される。

【0044】

すなわち、図4に示されるように、遅延器25の出力信号V1は、クロックφCの『H』への立ち上がりを受けて『L』に変化し、これがFF22の入力クロック(CK)として使われる。ここで、FF22は、クロック端子CKに入力された信号V1の『H』から『L』への立ち下がりで、データ入力Dに入力された信号VOを取り込む。

【0045】

遅延器25の出力信号V1の立ち下がりに対して、比較器1の信号VOの遅延が遅い(遅延時間が長い)場合には、VO=『H』を取り込むことになり、FF22は、『H』の信号Odを出力する。

【0046】

すなわち、遅延器25の遅延時間Td(V1)よりも比較器1側の遅延時間td(V0)の方が大きい(Td(V1)>td(V0))場合、信号Odは『H』になる。

【0047】

一方、遅延器25の出力信号V1の立ち下がりに対して、比較器1の信号VOの遅延が速い(遅延時間が短い)場合には、VO=『L』を取り込むことになり、FF22は、『L』の信号Odを出力する。

【0048】

すなわち、遅延器25の遅延時間Td(V1)よりも比較器1側の遅延時間td(V0)の方が小さい(Td(V1)<td(V0))場合、信号Odは『L』になる。

【0049】

このFF22の出力信号Odは、後段の制御回路23に取り込まれる。ここで、制御回路23は、例えば、アップダウンカウンタで構成され、信号OdのH/Lをカウントする。

【0050】

従って、例えば、Od=『H』(すなわち、比較器1の方が遅延器25よりも速い、或いは、遅延器25の方が比較器1よりも遅い)によってカウントアップされると、可変抵抗Rdの抵抗値を小さくなるように制御する。これによって、遅延器25の遅延時間が短くなる。

【0051】

これを繰り返すことによって、遅延器25の遅延時間は徐々に短縮され、比較器1の遅延時間より短くなって、Od=『L』を出力する。制御回路23は、Od=『L』を受けて電圧制御器(同相電圧制御用のD/A(Digital to Analog)変換器)3を制御する。

【0052】

ここで、D/A変換器3は、最初は最低電圧を出力した状態からスタートする。なお、制御回路23は、カウントダウンすることによってD/A変換器(負論理)3の入力コード(Din)を下げる。その結果、D/A変換器3の出力電圧Voutは、上昇する。

【0053】

そして、D/A変換器3の出力電圧Voutが同相電圧として比較器1に与えられ、再度、クロックφCによって判定を行うループが実行される。このループを繰り返し、2回連続でOd=『L』(すなわち、比較器1の方が遅延器25よりも速い)が得られたところで、D/A変換器3の入力コードを『1』だけ戻してループを終了させる。これによって、比較器1の同相電圧は、比較器1の遅延時間が最小となる電圧へ収束する。

【0054】

図5は、図3に示す判定器における判定処理の一例を説明するためのフローチャートであり、図6は、図5に示す判定処理を説明するための図である。すなわち、図5に示すフローチャートは、上述した判定器の処理をまとめたものである。

【0055】

図5に示されるように、判定器2の判定処理が開始すると、ステップST11において、D−MPX24の出力信号Din=0,Rd=Maxとする。すなわち、ステップST11では、信号Din=0として、D/A変換器3からの同相電圧を最低電圧とし、さらに、遅延器25の可変抵抗Rdの抵抗値を最大にして遅延器25による遅延を最大にする。

【0056】

次に、ステップST12へ進んで、遅延時間の比較、すなわち、FF22による比較器1による遅延時間(信号VO)と遅延器25による遅延時間(信号V1)の比較を行う。さらに、ステップST13へ進んで、FF22の出力信号Od=『L』かどうかを判定する。

【0057】

ステップST13において、Od=『L』であると判定すると、すなわち、比較器1の方が遅延器25よりも速いと判定すると、ステップST15へ進んで、遅延器25の可変抵抗Rdの抵抗値を1段階下げる。

【0058】

すなわち、ステップST15では、遅延器25による遅延時間を小さく(速度アップ)してステップST12へ戻り、同様の処理を繰り返す。これを繰り返すことによって、遅延器25の遅延時間は徐々に短縮され、比較器1の遅延時間より短くなって、Od=『H』を出力する。

【0059】

そして、ステップST13において、Od=『L』ではない(Od=『H』である)と判定すると、ステップST14へ進んで、Od(n−1)=『L』かどうかを判定する。ここで、Od(n−1)は前回の判定結果を示す。

【0060】

ステップST14において、Od(n−1)=『L』であると判定すると、ステップST16へ進んで、信号Dinを1段階下げる。すなわち、D/A変換器3の入力コード(Din)を1段階下げて、D/A変換器3の出力電圧Voutを上昇(比較器1の入力Vip,Vimにおける同相電圧を上昇)させ、ステップST12へ戻り、同様の処理を繰り返す。

【0061】

そして、ステップST14において、Od(n−1)=『L』ではない(Od(n−1)=『H』である)と判定すると、すなわち、2回連続してOd=『L』(比較器1の方が遅延器25よりも速い)と判定すると、ステップST17へ進む。

【0062】

ステップST17では、D−MPX24の出力信号Dinを1段階上げて、すなわち、D/A変換器3の出力電圧Voutを1段階分戻し、比較器1の入力Vip,Vimにおける同相電圧を制御して処理を終了する。

【0063】

以上により、図6に示されるように、同相電圧(Vcm)を、遅延Tdが最小となる最適な電圧へ収束させることが可能になる。なお、図5のフローチャートにおいて、ステップST13およびST14でOd=『L』を2回検出し、その後、ステップST17でD/A変換器3による同相電圧を1段階分戻しているが、これは適宜変更することができる。

【0064】

すなわち、同相電圧を、最下点からスタートして遅延時間tdが最小となる電圧まで上昇した時点で終了させてもよく、また、例えば、Od=『L』を3回検出した後に、D/A変換器3による同相電圧を2段階分戻す等の変更も可能である。

【0065】

このように、図5および図6を参照して説明した処理は、前述したループ処理回路により、同相電圧が最適値になったときに、そのループ処理(判定処理)を終了させるようになっている。次に、図7および図8を参照して説明する処理は、ループ処理回路により、同相電圧が最適値になった後も、ループ処理を継続させるものである。

【0066】

図7は、図3に示す判定器における判定処理の他の例を説明するためのフローチャートであり、図8は、図7に示す判定処理を説明するための図である。ここで、図7と前述した図5との比較から明らかなように、ステップST11〜ST17は共通である。

【0067】

図7に示されるように、ステップST14において、Od(n−1)=『L』であると判定すると、前述したように、ステップST17へ進んで、D−MPX24の出力信号Dinを1段階上げて、ステップST18へ進む。

【0068】

すなわち、ステップST14において、2回連続してOd=『L』(比較器1の方が遅延器25よりも速い)と判定すると、ステップST17へ進んで、D/A変換器3の入力コードDinを1段階下げて、D/A変換器3により同相電圧を1段階分下げる(戻す)。

【0069】

さらに、ステップST18へ進んで、遅延時間の比較、すなわち、FF22による比較器1による遅延時間(信号VO)と遅延器25による遅延時間(信号V1)の比較を行う。そして、ステップST19へ進んで、FF22の出力信号Od=『L』かどうかを判定する。

【0070】

ステップST19において、Od=『L』ではない(Od=『H』である)と判定すると、すなわち、比較器1の方が遅延器25よりも遅いと判定すると、ステップST20へ進んで、遅延器25の可変抵抗Rdの抵抗値を1段階上昇させる。

【0071】

すなわち、ステップST20では、遅延器25による遅延時間を大きく(速度ダウン)してステップST18へ戻り、同様の処理を繰り返す。これを繰り返すことによって、遅延器25の遅延時間は徐々に延長され、比較器1の遅延時間より長くなって、Od=『L』を出力する。

【0072】

そして、ステップST19において、Od=『L』であると判定すると、ステップST21へ進んで、遅延時間を比較する。さらに、ステップST22へ進んで、Od=『L』かどうかを判定する。

【0073】

ステップST22において、Od=『L』ではない(Od=『H』である)と判定すると、すなわち、比較器1の方が遅延器25よりも遅いと判定すると、ステップST23へ進む。ステップST23では、D/A変換器3の入力コードDinを1段階上げて、D/A変換器3による同相電圧を1段階低下させて、ステップST23へ戻り、同様の処理を繰り返す。

【0074】

そして、ステップST22において、Od=『L』であると判定すると、すなわち、比較器1の方が遅延器25よりも速いと判定すると、前述したステップST16を介してステップST12へ戻り、同様の処理を繰り返す。

【0075】

以上により、図8に示されるように、遅延器25の可変抵抗Rdの抵抗値を最大側から順に小さくした後、小さくなり過ぎた可変抵抗Rdの抵抗値を戻すことで、比較器1の同相電圧を、比較器1の遅延時間tdが最小となる電圧へ収束させることができる。

【0076】

このように、図7および図8を参照して説明した処理は、前述したループ処理回路により、同相電圧が最適値になった後も、ループ処理を継続させるようになっている。これにより、例えば、本実施例の電圧比較回路が適用される装置の電源電圧の変動、或いは、周囲の温度変化等により同相電圧の最適値が変化しても対応することが可能になる。

【0077】

以上のように、比較器に対して最適な同相電圧を与えることができ、製造ばらつき、並びに、実動作中における電圧や温度の変動に対する耐性を改善し、精度および動作速度を向上することが可能になる。なお、上述した図5および図7のフローチャートは、単なる例であり、様々な変更が可能なのはいうまでもない。

【0078】

図9は、本実施例に係る電圧比較回路を適用した逐次比較型A/D変換器の一例を示すブロック図であり、図10は、図9に示す逐次比較型A/D変換器の動作を説明するためのタイミング図である。

【0079】

図9において、参照符号30pは正論理側の容量回路、30mは負論理側の容量回路、および、300はSAR(Successive Approximation Register)論理回路を示す。

【0080】

図9に示されるように、逐次比較型A/D変換器において、前述した第1実施例の電圧比較回路を構成する比較器1,判定器2およびD/A変換器(電圧制御器)3が適用されている。なお、D/A変換器3は、正および負論理側の容量回路30pおよび30mに対して、それぞれ設けられている。

【0081】

図9および図10に示されるように、逐次比較型A/D変換器において、例えば、制御信号φAが『H』となる期間(サンプリング期間)、アナログ信号Vin(Vip,Vim)は、容量1C,2C,3C,8C,16C,32Cの一端に与えられる。

【0082】

この時、差動型の比較器1の両入力端子は、D/A変換器3によって所定の同一の電圧が同相電圧として与えられる。これによって、各容量1C,2C,3C,8C,16C,32Cには、アナログ信号Vinの電圧とD/A変換器3からの同相電圧に対応した電荷が充電される。

【0083】

ここで、信号φAが『H』の期間はサンプリング期間であるため、比較器1は、本来、動作する必要はない。そこで、このサンプリング期間において、タイミングTaでクロックφCを『H』に立ち上げて比較器1に判定動作を行わせる。

【0084】

なお、信号φAが『L』の期間(判定期間)におけるタイミングT5〜T0は、それぞれ制御信号φ0〜φ5によりスイッチSW0〜SW5の接続を制御した状態で行う比較器1の判定動作を行わせるものである。

【0085】

すなわち、逐次比較型A/D変換器の判定期間(信号φAが『L』の期間)における制御信号φ0〜φ5によるスイッチSW0〜SW5の制御は、通常の逐次比較型A/D変換器と同様であり、その説明は省略する。

【0086】

また、図9は、1C,2C,3C,8C,16C,32Cの容量を6つのスイッチSW0〜SW5で接続制御する例を示しているが、最小の容量値のものを2つ設け、1C,1C,2C,3C,8C,16C,32Cの容量を7つのスイッチで制御してもよい。

【0087】

図11は、図9に示す逐次比較型A/D変換器の動作の他の例を説明するためのタイミング図である。図11と上述した図10との比較から明らかなように、図11では、同相電圧を制御するために行う比較器1による判定動作を、信号φAが『H』のサンプリング期間ではなく、その直後に行うようになっている。

【0088】

すなわち、同相電圧を制御するための比較器1の判定動作を、信号φAが『L』になるサンプリング終了後から比較器1によるA/D変換を行うための比較動作を開始するタイミングT0までの間、すなわち、タイミングTbで行うようになっている。

【0089】

このように、同相電圧を制御するための比較器1の判定動作をタイミングTbで行うと、容量1C,2C,3C,8C,16C,32Cに蓄えられた後の入力信号Vip,Vimの同相電圧を制御することが可能になる。

【0090】

以上において、比較器1の入力信号Vip,Vimに与える同相電圧は、上述した図5〜図8を参照して説明した判定処理(ループ処理)によって、比較器1により最速の応答時間が得られる電圧へ収束する。

【0091】

なお、時間ごとに異なるアナログ信号が印加された場合でも、各タイミングTa,Tbで比較器1に入力される電圧は、常に、D/A変換器3によって決まるため、上述のループを動作させることができる。

【0092】

また、上述の設定では、通常の逐次比較型A/D変換器のサンプリング期間中に同相電圧の制御を行うため、実際に行うA/D変換動作に余分な期間を必要としないため、性能を犠牲にすることなく、常時、バックグラウンドでこのループを回すことが可能である。

【0093】

なお、図9において、例えば、アナログ信号Vinを固定し、信号φ0〜φ5で制御されるスイッチをVinの導通状態で固定すれば、通常動作時では6回比較動作を行う比較器1の判定処理を、全て同相電圧を制御するためのループに使用することが可能となる。

【0094】

この場合、同相電圧の制御を行うための期間は、逐次比較型A/D変換器による本来のA/D変換動作は行えないため、フォアグラウンド処理に限定されることになる。

【0095】

図12は、本実施例に係る電圧比較回路を適用したフラッシュ型A/D変換器の一例を示すブロック図であり、図13は、図12に示すフラッシュ型A/D変換器における1つの電圧比較回路を示すブロック図である。

【0096】

図12において、参照符号400は抵抗ラダーを示し、500はエンコーダを示す。ここで、本実施例の電圧比較回路100は、抵抗ラダー400とエンコーダ500との間に複数個設けられている。なお、同相電圧の制御は、フォアグラウンドで行うようになっている。

【0097】

各電圧比較回路100は、高電位の基準電圧Vrefpと低電位の基準電圧Vrefmとの間に直列接続された複数の抵抗における隣接する抵抗の接続ノード(タップ)からの基準電圧と、入力アナログ信号Vinを受け取り、その出力信号をエンコーダ500へ出力する。

【0098】

すなわち、図12に示されるように、フラッシュ型A/D変換器は、抵抗ラダー400により基準電圧Vrefp〜Vrefmを分圧して各電圧比較回路100の比較基準電圧として印加する。

【0099】

各電圧比較回路100は、抵抗ラダー400からの比較基準電圧とアナログ信号Vinを比較し、その比較結果(出力信号)は、エンコーダ500に入力される。そして、エンコーダ500は、アナログ信号Vinをデジタル変換した出力Doutを出力する。

【0100】

図13に示されるように、各電圧比較回路100は、比較器1、判定器2、D/A変換器(電圧制御器)3、容量Cp,Cm、および、スイッチSW11,SW12,SW21,SW22,SW31,SW32を有する。

【0101】

なお、図13において、比較器1は、前述した図2におけるトランジスタTp12,Tp15に相当するスイッチを有していないが、図2の比較器をそのまま適用することができるのはいうまでもない。

【0102】

ここで、同相電圧の制御処理(判定処理)は、例えば、図7を参照して説明した処理をそのまま適用することができる。すなわち、図13において、まず、D/A変換器3にDin=0、xCLK’=『H』を与えて処理を開始する。なお、D/A変換器3は、正論理を想定する。

【0103】

xCLK’=『H』とすることにより、スイッチSW31,SW32がオンし、アナログ信号Vinに依存することなく、比較器1の双方の入力Vip,Vimには、D/A変換器3の出力が与えられる。

【0104】

次に、クロックCLK(クロックφCに対応)を通常モードと同様に与えて、比較器1が判定を実行する。ここで、図7を参照して説明したのと同様に、判定器2によって遅延時間を比較する。なお、判定器2の構成は、前述した図3と同様である。

【0105】

そして、判定器2の結果をD/A変換器3または判定器2における遅延器25に与え、図7の処理を実施することによって、最終的に最適な同相電圧に収束する。なお、各電圧比較回路100に対して判定器2を個別に待たせれば、全ての電圧比較回路100が同時並行して処理することができるが、回路規模が大きくなる。

【0106】

そこで、例えば、1つの判定器2の接続を切り替えて、1つの電圧比較回路100(比較器1)ごとに処理すれば、処理時間は長くなるが回路規模を抑えることができる。いずれの構成にしても各比較器の同相電圧は最適点が与えられ、これによって高速動作が可能となる。なお、キャリブレーションが完了した後、xCLK’はCLKの反転レベルの信号(xCLK)として与えることができる。

【0107】

図14は、電圧比較回路の第2実施例を示すブロック図である。図14と前述した図3との比較から明らかなように、本第2実施例の電圧比較回路100では、D−MPX24の出力信号により抵抗値が制御される可変抵抗Rdの代わりに、可変容量Cdが設けられている。

【0108】

すなわち、クロックφCを受け取るインバータTp25,Tn25は、VddとGNDとの間に直接設けられ、FF22のクロック端子CKに入力されるインバータの出力信号V1のノードとGNDとの間に、負荷として可変容量Cdが設けられている。この可変容量Cdは、D−MPX24の出力信号により、その容量値が制御されるようになっている。

【0109】

ここで、図3に示す電圧比較回路の第1実施例では、遅延時間を低下させるために可変抵抗Rdの抵抗値を小さくしていたが、本第2実施例の電圧比較回路では、遅延時間を低下させるために可変容量Cdの容量値を小さくすることになる。

【0110】

なお、本第2実施例の電圧比較回路では、前述した図5および図7に示す処理における可変抵抗Rdの抵抗値の段階的な上昇および低下を、可変容量Cdの容量値の段階的な上昇および低下に置き換えれば、そのまま適用することができる。また、図3および図4に示す電圧比較回路は、単なる例であり、様々な変形が可能なのはいうまでもない。

【0111】

このように、本実施例の電圧比較回路、或いは、A/D変換器を使用することにより、比較器の同相電圧を自動的に最適点に設定できるため、製造時の素子ばらつきや、電源電圧および温度等の動作時の環境変化を補償することができる。その結果、安定した動作を実現することが可能になる。また、同相電圧に起因する要求性能を満たさない半導体装置を低減することになるため、歩留まりの向上にも貢献することができる。

【0112】

図15は、本実施例に係る電圧比較回路を用いたA/D変換器を適用した半導体装置の一例を示すブロック図であり、デジタルTVチューナ(通信システム)50を示すものである。

【0113】

図15において、参照符号51はアンテナ、52は高周波増幅器、53a,53bはミキサ、54は周波数シンセサイザ、55a,55bは低域通過フィルタ、および、56a,56bは低周波増幅器を示す。さらに、参照符号57a,57bはA/D変換器を示し、58はデジタルブロックを示す。

【0114】

図15に示されるように、デジタルTVチューナ50は、アンテナ51により電波を受信し、高周波増幅器52により信号処理に適するレベルまで信号振幅を増幅する。高周波増幅器52の出力信号は、ミキサ53a,53bにおいて、周波数シンセサイザ54からの90度位相をずらした信号と合成され、Ich,Qch信号が生成される。

【0115】

さらに、ミキサ53a,53bで生成されたIch,Qch信号は、低域通過フィルタ55a,55bおよび低周波増幅器56a,56bにより変換域(信号振幅)と信号帯域が調整され、A/D変換器57a,57bに与えられる。

【0116】

そして、A/D変換器57a,57bにおいて、入力されたアナログ信号がデジタル信号へ変換され、そのデジタル信号がデジタルブロック58へ出力される。このデジタルブロック58において、所定の処理が行われ、例えば、映像および音声が表示装置およびスピーカ等から出力される。

【0117】

ここで、図15で使用するA/D変換器57a,57bとしては、前述した図9に示す逐次比較型A/D変換器、或いは、図12に示すフラッシュ型A/D変換器等の本実施例の電圧比較回路を適用した様々なA/D変換器である。

【0118】

なお、A/D変換器57a,57bの前段がアナログ信号を処理するアナログ信号処理部となり、A/D変換器57a,57bの後段が、デジタル信号処理部(デジタルブロック58)となる。

【0119】

また、図15に示すデジタルTVチューナは、本実施例の電圧比較回路、或いは、A/D変換器を適用した半導体装置(システム)の単なる一例であり、本実施例は、様々な半導体装置に対して幅広く適用することができる。

【0120】

以上の実施例を含む実施形態に関し、さらに、以下の付記を開示する。

(付記1)

比較器と、

前記比較器の応答速度を判定する判定器と、

前記判定器の判定結果に従って、前記比較器の応答速度の遅延を低減するように、前記比較器の複数の入力における同相電圧を制御する電圧制御器と、

を有することを特徴とする電圧比較回路。

【0121】

(付記2)

前記判定器は、前記比較器の応答速度の判定を複数回行う、

ことを特徴とする付記1に記載の電圧比較回路。

【0122】

(付記3)

前記判定器は、

前記比較器の応答を検出する応答検出器と、

第1制御信号の遅延を制御する遅延器と、

前記遅延された第1制御信号と前記検出された前記比較器の応答の時間差を低減するように前記遅延器を制御して、前記同相電圧を最適値に収束させるループ処理を行うループ処理回路と、

を有することを特徴とする付記1または付記2に記載の電圧比較回路。

【0123】

(付記4)

前記ループ処理回路は、前記同相電圧が前記最適値になったとき、前記ループ処理を終了させる、

ことを特徴とする付記3に記載の電圧比較回路。

【0124】

(付記5)

前記ループ処理回路は、前記同相電圧が前記最適値になった後も、前記ループ処理を継続させる、

ことを特徴とする付記3に記載の電圧比較回路。

【0125】

(付記6)

前記遅延器は、増幅器と、前記ループ処理回路の出力に応じて、前記増幅器に流れる電流を制御する可変抵抗と、を有し、

前記ループ処理回路は、前記可変抵抗の抵抗値を制御して前記同相電圧を最適値に収束させる、

ことを特徴とする付記3乃至付記5のいずれか1項に記載の電圧比較回路。

【0126】

(付記7)

前記遅延器は、増幅器と、前記ループ処理回路の出力に応じて、前記増幅器の負荷を制御する可変容量と、を有し、

前記ループ処理回路は、前記可変容量の容量値を制御して前記同相電圧を最適値に収束させる、

ことを特徴とする付記3乃至付記5のいずれか1項に記載の電圧比較回路。

【0127】

(付記8)

前記電圧制御器は、前記判定器の判定結果に従って前記比較器の入力に与える前記同相電圧を制御するD/A変換器である、

ことを特徴とする付記1乃至付記7のいずれか1項に記載の電圧比較回路。

【0128】

(付記9)

前記電圧制御器は、前記比較器の差動入力における同相電圧を制御する、

ことを特徴とする付記1乃至付記8のいずれか1項に記載の電圧比較回路。

【0129】

(付記10)

付記1乃至付記9のいずれか1項に記載の電圧比較回路を有するA/D変換器であって、

前記A/D変換器により、アナログ信号をサンプリングしている間に、前記比較器を動作させて前記同相電圧の制御を行う、

ことを特徴とするA/D変換器。

【0130】

(付記11)

付記1乃至付記9のいずれか1項に記載の電圧比較回路を有するA/D変換器であって、

前記A/D変換器により、サンプリングが終了した後から前記比較器によりA/D変換を行うための比較動作を開始するまでの間に、前記比較器を動作させて前記同相電圧の制御を行う、

ことを特徴とするA/D変換器。

【0131】

(付記12)

前記A/D変換器は、逐次比較型A/D変換器であり、

前記比較器は、ストロングアーム型比較器である、

ことを特徴とする付記10または付記11に記載のA/D変換器。

【0132】

(付記13)

アナログ信号を処理するアナログ信号処理部と、

前記アナログ信号処理部からのアナログ信号をデジタル信号へ変換する、付記10乃至付記12のいずれか1項に記載のA/D変換器と、

前記A/D変換器からのデジタル信号を処理するデジタル信号処理部と、

を有することを特徴とする半導体装置。

【符号の説明】

【0133】

1 比較器(電圧比較器)

2 判定器

3 電圧制御器(D/A変換器)

21 エクスクルーシブノア(EXNOR)ゲート

22 フリップフロップ(FF)

23 制御回路(CNTL:アップダウンカウンタ)

24 デマルチプレクサ(D−MPX)

25 遅延器

30p,30m 容量回路

50 デジタルTVチューナ(通信システム)

51 アンテナ

52 高周波増幅器

53a,53b ミキサ

54 周波数シンセサイザ

55a,55b 低域通過フィルタ

56a,56b 低周波増幅器

57a,57b A/D変換器

58 デジタルブロック

100 電圧比較回路

200 クロック発生器

300 SAR論理回路

400 抵抗ラダー

500 エンコーダ

【特許請求の範囲】

【請求項1】

比較器と、

前記比較器の応答速度を判定する判定器と、

前記判定器の判定結果に従って、前記比較器の応答速度の遅延を低減するように、前記比較器の複数の入力における同相電圧を制御する電圧制御器と、

を有することを特徴とする電圧比較回路。

【請求項2】

前記判定器は、

前記比較器の応答を検出する応答検出器と、

第1制御信号の遅延を制御する遅延器と、

前記遅延された第1制御信号と前記検出された前記比較器の応答の時間差を低減するように前記遅延器を制御して、前記同相電圧を最適値に収束させるループ処理を行うループ処理回路と、

を有することを特徴とする請求項1に記載の電圧比較回路。

【請求項3】

請求項1または請求項2に記載の電圧比較回路を有するA/D変換器であって、

前記A/D変換器により、アナログ信号をサンプリングしている間に、前記比較器を動作させて前記同相電圧の制御を行う、

ことを特徴とするA/D変換器。

【請求項4】

請求項1または請求項2に記載の電圧比較回路を有するA/D変換器であって、

前記A/D変換器により、サンプリングが終了した後から前記比較器によりA/D変換を行うための比較動作を開始するまでの間に、前記比較器を動作させて前記同相電圧の制御を行う、

ことを特徴とするA/D変換器。

【請求項5】

アナログ信号を処理するアナログ信号処理部と、

前記アナログ信号処理部からのアナログ信号をデジタル信号へ変換する、請求項3または請求項4に記載のA/D変換器と、

前記A/D変換器からのデジタル信号を処理するデジタル信号処理部と、

を有することを特徴とする半導体装置。

【請求項1】

比較器と、

前記比較器の応答速度を判定する判定器と、

前記判定器の判定結果に従って、前記比較器の応答速度の遅延を低減するように、前記比較器の複数の入力における同相電圧を制御する電圧制御器と、

を有することを特徴とする電圧比較回路。

【請求項2】

前記判定器は、

前記比較器の応答を検出する応答検出器と、

第1制御信号の遅延を制御する遅延器と、

前記遅延された第1制御信号と前記検出された前記比較器の応答の時間差を低減するように前記遅延器を制御して、前記同相電圧を最適値に収束させるループ処理を行うループ処理回路と、

を有することを特徴とする請求項1に記載の電圧比較回路。

【請求項3】

請求項1または請求項2に記載の電圧比較回路を有するA/D変換器であって、

前記A/D変換器により、アナログ信号をサンプリングしている間に、前記比較器を動作させて前記同相電圧の制御を行う、

ことを特徴とするA/D変換器。

【請求項4】

請求項1または請求項2に記載の電圧比較回路を有するA/D変換器であって、

前記A/D変換器により、サンプリングが終了した後から前記比較器によりA/D変換を行うための比較動作を開始するまでの間に、前記比較器を動作させて前記同相電圧の制御を行う、

ことを特徴とするA/D変換器。

【請求項5】

アナログ信号を処理するアナログ信号処理部と、

前記アナログ信号処理部からのアナログ信号をデジタル信号へ変換する、請求項3または請求項4に記載のA/D変換器と、

前記A/D変換器からのデジタル信号を処理するデジタル信号処理部と、

を有することを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2013−62646(P2013−62646A)

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願番号】特願2011−199154(P2011−199154)

【出願日】平成23年9月13日(2011.9.13)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願日】平成23年9月13日(2011.9.13)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]