電圧発生回路、定電圧回路および電圧発生回路の電流検出方法

【課題】低消費電流で低電圧な定電圧を安定して得られる定電圧回路を提供すること。

【解決手段】定電圧回路Aは、閾値電圧が極小でゲート長が特大のMOSトランジスタN1を用いて低電流を作り出し、基準電圧VREFを発生するMOSトランジスタN2、これと対を成してカレントミラー回路を構成する各MOSトランジスタN3、N4、N7、及びその他の各MOSトランジスタN5、N6の何れについても低閾値電圧タイプとし、且つMOSトランジスタN2、N3、N4、N7のゲート長LをMOSトランジスタP1、P2のゲート長Lよりも増大させている。これにより、各MOSトランジスタN2〜N7のドレイン電極−ソース電極間の電圧Vdsが0.1V以上の飽和領域で動作する電圧値を保ち、所望の低い基準電圧VREFを発生でき、カレントミラー回路を構成する際に正常動作が可能となり、定電圧出力端子4から低消費電流で低電圧な定電圧が得られる。

【解決手段】定電圧回路Aは、閾値電圧が極小でゲート長が特大のMOSトランジスタN1を用いて低電流を作り出し、基準電圧VREFを発生するMOSトランジスタN2、これと対を成してカレントミラー回路を構成する各MOSトランジスタN3、N4、N7、及びその他の各MOSトランジスタN5、N6の何れについても低閾値電圧タイプとし、且つMOSトランジスタN2、N3、N4、N7のゲート長LをMOSトランジスタP1、P2のゲート長Lよりも増大させている。これにより、各MOSトランジスタN2〜N7のドレイン電極−ソース電極間の電圧Vdsが0.1V以上の飽和領域で動作する電圧値を保ち、所望の低い基準電圧VREFを発生でき、カレントミラー回路を構成する際に正常動作が可能となり、定電圧出力端子4から低消費電流で低電圧な定電圧が得られる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、レギュレータ用の定電圧回路に関する。

【背景技術】

【0002】

従来、この種の定電圧回路に適用される定電流回路としては、例えばソース電極に第1の電源電圧(正極電源)VDDが接続され、且つゲート電極とドレイン電極とを同電位に接続した一方のP型MOSトランジスタを定電流源と直列に接続することにより、第1の電源電圧VDDと接続点との間に閾値電圧に依存したバイアス電圧を得て他方のP型MOSトランジスタ(同様にソース電極は第1の電源電圧VDDに接続される)のゲート電極に印加し、カレントミラー回路を成す一対のN型MOSトランジスタが他方のP型MOSトランジスタで得られた定電流を被駆動回路へ供給する構成のもの(特許文献1参照)が挙げられる。

【0003】

この定電流回路を定電圧回路に適用する場合、定電流源に代えてゲート電極とソース電極とを同電位に接続した別のN型MOSトランジスタのドレイン電極を一方のP型MOSトランジスタのドレイン電極に接続すると共に、ソース電極を第2の電源電圧VSSに接続した構成にすることが可能である。この場合、他方のP型MOSトランジスタとドレイン電極同士が接続されたN型MOSトランジスタとの結線から、引き出し線を引き出して基準電圧VREFを得ることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平9−128067号公報(第4頁、図1)

【発明の概要】

【発明が解決しようとする課題】

【0005】

上述した特許文献1に係る定電圧回路用の定電流回路の場合、例えばカレントミラー回路を成す一対のN型MOSトランジスタが使用条件によって意図した通りに動作しなくなる場合がある。

一般にMOSトランジスタでは、ゲート電極−ソース電極間の電圧Vgsを閾値電圧Vth未満で動作させる場合を弱反転領域にあり、ゲート電極−ソース電極間の電圧Vgsを閾値電圧Vth以上で動作させる場合を強反転領域にあるとみなすことができる。又、ドレイン電極−ソース電極間の電圧Vdsを凡そ0.1V未満で動作させた場合はダイオード接続の有無に拘らず線形領域にあり、ドレイン電極−ソース電極間の電圧Vdsを凡そ0.1V以上で動作させた場合は飽和領域にあるとみなすことができる。

【0006】

上述した定電流回路におけるカレントミラー回路を成す一対のN型MOSトランジスタの場合、飽和領域で使用した場合に正常動作するものであるため、低閾値電圧タイプのものを用いた場合に弱反転領域の非飽和領域で動作すると、特にダイオード接続された一方のものについては、使用条件によってはドレイン電極−ソース電極間の電圧Vdsが0.1V未満になること(閾値電圧Vthは高温条件下で低下することが知られている)があり、こうした場合には他方のものが正常に動作せず、カレントミラー回路が意図した通りに動作しなくなってしまうという問題がある。

【0007】

即ち、カレントミラー回路におけるダイオード接続された一方のN型MOSトランジスタについては、飽和領域の0.1Vを超えたドレイン電極−ソース電極間の電圧Vdsを保持して使用しないと、カレントミラー回路が正常動作しないことになる。それ故、現状の定電流回路では、低閾値電圧タイプのMOSトランジスタを用いるとドレイン電極−ソース電極間の電圧Vdsが0.1V未満になることを完全には阻止できず、係る定電流回路を定電圧回路として構成した場合には、低消費電流で低電圧な定電圧を安定して得ることができない。

そこで、本発明の技術的課題は、低消費電流で低電圧な定電圧を安定して得られる定電圧回路を提供することにある。

【課題を解決するための手段】

【0008】

上記技術的課題を解決するための第1の発明は、

ソース電極に第1の電源電圧が接続され、且つゲート電極とドレイン電極とを同電位に接続した第1のP型MOSトランジスタ(例えば、図1のMOSトランジスタP1)と、

ソース電極に第1の電源電圧が接続され、且つゲート電極が前記第1のP型MOSトランジスタのゲート電極及びドレイン電極に接続された第2のP型MOSトランジスタ(例えば、図1のMOSトランジスタP2)と、

ソース電極に第2の電源電圧が接続され、且つゲート電極とソース電極とを同電位に接続し、ドレイン電極が第1のP型MOSトランジスタのドレイン電極に接続された第1のN型MOSトランジスタ(例えば、図1のMOSトランジスタN1)と、

ソース電極に第2の電源電圧が接続され、且つゲート電極とドレイン電極とを同電位に接続し、ドレイン電極が前記第2のP型MOSトランジスタのドレイン電極に接続された第2のN型MOSトランジスタ(例えば、図1のMOSトランジスタN2)と、

ソース電極に第2の電源電圧が接続され、且つゲート電極が前記第2のN型MOSトランジスタのドレイン電極に接続され、ドレイン電極がトリム端子(例えば、図1のトリム端子3)に接続された第3のN型MOSトランジスタ(例えば、図1のMOSトランジスタN3)と、を備えて構成され、

前記第2のP型MOSトランジスタと前記第2のN型MOSトランジスタとにおけるドレイン電極同士の結線に対する接続引き出し線から基準電圧を生成出力する基準電圧生成回路(例えば、図1の基準電圧生成回路1)を含み、

前記第1のN型MOSトランジスタは、閾値電圧が極小のデプリーション型であると共に、ゲート長が前記第2のN型MOSトランジスタのゲート長よりも大きく、

前記第2のN型MOSトランジスタは、前記第1のN型MOSトランジスタよりも閾値電圧が高い低閾値電圧タイプであると共に、ゲート長が前記第1のP型MOSトランジスタ及び前記第2のP型MOSトランジスタのゲート長の15倍以上大きく、

前記第3のN型MOSトランジスタの閾値電圧は、前記第2のN型MOSトランジスタの閾値電圧と同じであり、

前記トリム端子は、前記第3のN型MOSトランジスタのドレイン電極へ所定の電圧値を印加することにより、前記第2のP型MOSトランジスタのソース電極−ドレイン電極間、並びに前記第2のN型MOSトランジスタのドレイン電極−ソース電極間を流れる電流をモニタするものであることを特徴とする定電圧回路である。

【0009】

このような構成により、閾値電圧Vthが極小でゲート長が特大のデプリーション型の第1のMOSトランジスタに対し、それよりも閾値電圧Vthが大きい低閾値電圧タイプの基準電圧VREFを発生する第2のN型MOSトランジスタのゲート長を第1のP型MOSトランジスタ及び第2のP型MOSトランジスタP2のゲート長Lの15倍以上大きくし、且つMOSトランジスタN2と対を成してカレントミラー回路を構成する第3のN型MOSトランジスタについても同等な低閾値電圧タイプを用いているため、第1のN型MOSトランジスタで低電流を作り出し、第2のN型MOSトランジスタで低電圧な基準電圧VREFを発生する際、第3のN型MOSトランジスタを介して第2のN型MOSトランジスタに流れる電流を適切に検出でき、第2のN型MOSトランジスタのドレイン電極−ソース電極間の電圧Vdsを0.1V以上に維持できると共に、第3のN型MOSトランジスタのドレイン電極−ソース電極間の電圧Vdsについてはトリム端子への電圧印加により0.1V超過にでき、各N型MOSトランジスタのドレイン電極−ソース電極間の電圧Vdsが飽和領域で動作する電圧値を保つことができる。

この結果、各N型MOSトランジスタに低閾値電圧タイプのものを用いているにも拘らず、ドレイン電極−ソース電極間の電圧Vdsが飽和領域で安定して動作するため、弱反転領域における非飽和領域で動作される状態が回避され、所望の低い基準電圧を発生させることができ、カレントミラー回路を構成する際に正常動作させることが可能となる。

【0010】

又、第2の発明は、

前記第3のN型MOSトランジスタのゲート幅は、前記第2のN型MOSトランジスタのゲート幅よりも大きいことを特徴とする定電圧回路である。

このような構成により、基準電圧生成回路において、基準電圧を発生する第2のN型MOSトランジスタに流れる電流が小さくて外部端子から直接モニタできないため、これを倍増した第3のN型MOSトランジスタを流れる電流により正確にモニタすることができる。

【0011】

更に、第3の発明は、

ゲート電極が前記基準電圧に接続され、且つソース電極が第2の電源電圧に接続された第4のN型MOSトランジスタ(例えば、図1のMOSトランジスタN4)と、

ゲート電極が前記基準電圧に接続され、且つソース電極が前記第4のN型MOSトランジスタのドレイン電極に接続された第5のN型MOSトランジスタ(例えば、図1のMOSトランジスタN5)と、

ソース電極に第1の電源電圧が接続され、且つドレイン電極が前記第5のN型MOSトランジスタのドレイン電極に接続された第3のP型MOSトランジスタ(例えば、図1のMOSトランジスタP3)と、

ソース電極に第1の電源電圧が接続され、且つゲート電極が前記第3のP型MOSトランジスタのゲート電極に接続されると共に、ドレイン電極と同電位に接続した第4のP型MOSトランジスタ(例えば、図1のMOSトランジスタP4)と、

ソース電極に第1の電源電圧が接続され、且つゲート電極が前記第3のP型MOSトランジスタのドレイン電極と前記第5のN型MOSトランジスタのドレイン電極との結線に接続された第5のP型MOSトランジスタ(例えば、図1のMOSトランジスタP5)と、

ソース電極が前記第5のN型MOSトランジスタのソース電極及び前記第4のN型MOSトランジスタのドレイン電極に接続され、且つドレイン電極が前記第4のP型MOSトランジスタのドレイン電極に接続された第6のN型MOSトランジスタ(例えば、図1のMOSトランジスタN6)と、

ソース電極が前記第5のP型MOSトランジスタのドレイン電極に接続され、且つゲート電極とドレイン電極とを同電位に接続した第6のP型MOSトランジスタ(例えば、図1のMOSトランジスタP6)と、

ゲート電極が前記基準電圧に接続され、ソース電極が第2の電源電圧に接続され、且つドレインが前記第6のP型MOSトランジスタのドレイン電極及び前記第6のN型MOSトランジスタのゲート電極に接続された第7のN型MOSトランジスタ(例えば、図1のMOSトランジスタN7)と、を備えて構成され、

前記第4のN型MOSトランジスタ、前記第5のN型MOSトランジスタ、前記第6のN型MOSトランジスタ、及び前記第7のN型MOSトランジスタの閾値電圧は、それぞれ前記第2のN型MOSトランジスタの閾値電圧と同じであり、

前記第5のP型MOSトランジスタのドレイン電極と前記第6のP型MOSトランジスタのソース電極との結線に対する接続引き出し線から定電圧を出力する定電圧出力回路を(例えば、図1の定電圧出力回路2)含むことを特徴とする定電圧回路である。

【0012】

このような構成により、基準電圧生成回路によって低消費電流で生成された低電圧な基準電圧を用いて差動増幅により定電圧を出力するとき、定電圧出力回路におけるMOSトランジスタを低閾値電圧で駆動できるため、低電圧な定電圧を安定して得ることが可能となる。

即ち、本発明によれば、低消費電流で低電圧な基準電圧を生成する定電圧回路を実現することができる。

【0013】

加えて、第4の発明は、

前記第2のN型MOSトランジスタは、ゲート幅に対するゲート長の比を示すゲート長/ゲート幅が15以上であることを特徴とする定電圧回路である。

このような構成により、基準電圧生成回路における低電圧な基準電圧の生成に際して的確に低消費電流化が図られる。

【0014】

又、第5の発明は、

前記第2のN型MOSトランジスタのゲート長は、前記第6のN型MOSトランジスタ及び前記第7のN型MOSトランジスタのゲート長の15倍以上であることを特徴とする定電圧回路である。

このような構成により、基準電圧生成回路における低電圧な基準電圧の生成に際して一層低消費電流化が図られるため、定電圧回路において、低消費電流で低電圧な定電圧出力を得る上で有効となる。

【図面の簡単な説明】

【0015】

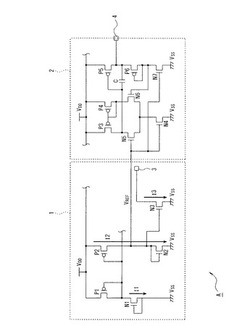

【図1】本発明の実施形態に係る定電圧回路Aの基本構成を示した回路図である。

【図2】ゲート長Lを増大させたMOSトランジスタの構造例を示した模式図であり、(a)はその一例に関するもの、(b)はその他例に関するものである。

【発明を実施するための形態】

【0016】

以下、図を参照して本発明に係る定電圧回路の実施形態を説明する。

図1は、本発明の実施形態に係る定電圧回路Aの基本構成を示した回路図である。ここでの定電圧回路Aは、低電圧な基準電圧VREFを生成出力する基準電圧生成回路1と、この基準電圧VREFを用いて差動増幅により定電圧を出力する定電圧出力回路2とから構成される。このうち、基準電圧生成回路1は、ソース電極に第1の電源電圧VDDが接続され、且つゲート電極とドレイン電極とを同電位に接続したP型のMOSトランジスタP1と、ソース電極に第1の電源電圧VDDが接続され、且つゲート電極がMOSトランジスタP1のゲート電極及びドレイン電極に接続されたP型のMOSトランジスタP2と、ソース電極に第2の電源電圧VSSが接続され、且つゲート電極とソース電極とを同電位に接続し、ドレイン電極がMOSトランジスタP1のドレイン電極に接続されたN型のMOSトランジスタN1と、ソース電極に第2の電源電圧VSSが接続され、且つゲート電極とドレイン電極とを同電位に接続し、ドレイン電極がMOSトランジスタP2のドレイン電極に接続されたN型のMOSトランジスタN2と、ソース電極に第2の電源電圧VSSが接続され、且つゲート電極がN型MOSトランジスタN2のドレイン電極に接続され、ドレイン電極がトリム端子3に接続されたN型のMOSトランジスタN3と、を備えている。

【0017】

この基準電圧生成回路1において、MOSトランジスタP2とMOSトランジスタN2とにおけるドレイン電極同士の結線には、引き出し線が接続されており、この引き出し線から基準電圧VREFが出力される。

細部について説明すれば、MOSトランジスタN1は、閾値電圧Vthが0V以下の極小のデプリーション型であると共に、ゲート電極におけるソース電極−ドレイン電極間の距離を示すゲート長LがMOSトランジスタN2のゲート長Lよりも大きく、定電流源としてドレイン電極−ソース電極間に微弱な電流I1が流れる。基準電圧VREFを発生するMOSトランジスタN2は、MOSトランジスタN1よりも閾値電圧Vthが高く、例えば0.35Vの低閾値電圧タイプである。又、MOSトランジスタN2は、ゲート長LがMOSトランジスタP1、P2のゲート長Lの15倍以上大きくなっている。更に、MOSトランジスタN2と対を成してカレントミラー回路を構成するMOSトランジスタN3の閾値電圧Vthは、MOSトランジスタN2の閾値電圧Vthと同じである。トリム端子3は、MOSトランジスタN3のドレイン電極へ所定の電圧値を印加することにより、MOSトランジスタP2のソース電極−ドレイン電極間、並びにMOSトランジスタN2のドレイン電極−ソース電極間を流れる電流I2をモニタするものである。即ち、トリム端子3は、MOSトランジスタN3を流れる電流I3によって、MOSトランジスタN2に流れる電流I2をモニタするためのものであり、電流モニタ用の電圧(例えば1V程度)が印加されている。

【0018】

この基準電圧生成回路1では、閾値電圧Vthが極小でゲート長Lが特大のデプリーション型のMOSトランジスタN1に対し、それよりも閾値電圧Vthが大きい低閾値電圧タイプの基準電圧VREFを発生するMOSトランジスタN2のゲート長LをMOSトランジスタP1、P2のゲート長Lの15倍以上大きくし、且つMOSトランジスタN2と対を成してカレントミラー回路を構成するMOSトランジスタN3についても同等な低閾値電圧タイプを用いている。このため、MOSトランジスタN1で低電流を作り出し、MOSトランジスタN2で低電圧な基準電圧VREFを発生する際、MOSトランジスタN3を介してMOSトランジスタN2に流れる電流を適切に検出でき、MOSトランジスタN2のドレイン電極−ソース電極間の電圧Vdsを0.1V以上に維持できると共に、MOSトランジスタN3のドレイン電極−ソース電極間の電圧Vdsはトリム端子3に1Vの電圧が印加されているために0.1V超過となり、各N型MOSトランジスタN2、N3のドレイン電極−ソース電極間の電圧Vdsが飽和領域で動作する電圧値を保つことができる。

【0019】

この結果、MOSトランジスタN2、N3に低閾値電圧タイプのものを用いているにも拘らず、各N型MOSトランジスタN2、N3のドレイン電極−ソース電極間の電圧Vdsが飽和領域で安定して動作するため、弱反転領域における非飽和領域で動作される状態が回避され、所望の低い基準電圧VREFを発生させることができ、しかもカレントミラー回路を構成する際に正常動作させることが可能となる。従って、この基準電圧生成回路1の場合、低消費電流で低電圧な基準電圧VREFを生成することができる。

尚、MOSトランジスタN3のゲート電極におけるゲート幅WをMOSトランジスタN2のゲート電極におけるゲート幅Wよりも大きくしておけば、MOSトランジスタN2に流れる電流I2が小さくて外部端子から直接モニタできないため、これを倍増したMOSトランジスタN3を流れる電流I3により正確にモニタすることができる。

【0020】

又、定電圧出力回路2は、ゲート電極が基準電圧生成回路1の引き出し線(基準電圧VREF)に接続され、且つソース電極が第2の電源電圧VSSに接続されたN型のMOSトランジスタN4と、ゲート電極が基準電圧生成回路1の引き出し線(基準電圧VREF)に接続され、且つソース電極がMOSトランジスタN4のドレイン電極に接続されたN型のMOSトランジスタN5と、ソース電極に第1の電源電圧VDDが接続され、且つドレイン電極がMOSトランジスタN5のドレイン電極に接続されたP型のMOSトランジスタP3と、ソース電極に第1の電源電圧VDDが接続され、且つゲート電極がMOSトランジスタP3のゲート電極に接続されると共に、ドレイン電極と同電位に接続したP型のMOSトランジスタP4と、ソース電極に第1の電源電圧VDDが接続され、且つゲート電極がMOSトランジスタP3のドレイン電極とMOSトランジスタN5のドレイン電極との結線に接続されたP型のMOSトランジスタP5と、ソース電極がMOSトランジスタN5のソース電極及びMOSトランジスタN4のドレイン電極に接続され、且つドレイン電極がMOSトランジスタP4のドレイン電極に接続されたN型のMOSトランジスタN6と、ソース電極がMOSトランジスタP5のドレイン電極に接続され、且つゲート電極とドレイン電極とを同電位に接続したP型のMOSトランジスタP6と、ゲート電極が基準電圧生成回路1の引き出し線(基準電圧VREF)に接続され、ソース電極が第2の電源電圧VSSに接続され、且つドレインがMOSトランジスタP6のドレイン電極及びMOSトランジスタN6のゲート電極に接続されたN型のMOSトランジスタN7と、MOSトランジスタP5のドレイン電極及びMOSトランジスタP6のソース電極の結線とMOSトランジスタP5のゲート電極との間に介在させた容量端子Cと、を備えている。

【0021】

この定電圧出力回路2において、MOSトランジスタP5のドレイン電極とMOSトランジスタP6のソース電極との結線には、引き出し線が接続されており、この引き出し線の終端に位置する定電圧出力端子4から定電圧回路Aの出力である定電圧が出力される。MOSトランジスタN4〜N7については、閾値電圧VthがMOSトランジスタN2、N3と同じ0.35Vの低閾値電圧タイプのものとしている。

本実施形態に係る定電圧回路Aの場合、基準電圧生成回路1では消費電力を低減する目的で基準電圧VREFをより低電圧なものとし、MOSトランジスタN1の発生電流I1を低電流化している。例えば、電流I1は10nA程度で発生させる。

このとき、MOSトランジスタP1、P2から成るカレントミラー回路によって、MOSトランジスタN2に電流I2が流れるが、MOSトランジスタN2は弱反転領域で使用するため、ダイオード接続されたMOSトランジスタN2は、ゲート電圧が低電圧の状態で駆動される。

【0022】

ここで、MOSトランジスタN2において、ドレイン電極−ソース電極間の電圧Vdsが閾値電圧Vthを下回り、0.1V程度となった場合、MOSトランジスタN2が弱反転領域の非飽和領域で動作する状態となる可能性がある。

このような事態を回避するため、低閾値電圧タイプのMOSトランジスタN2については、ゲート電極におけるゲート長LをP型MOSトランジスタP1、P2のゲート電極におけるゲート長Lよりも15倍以上大きくしている。上述したデプリーション型のMOSトランジスタN1のゲート電極におけるゲート長Lは数mm程度の特大なものであり、MOSトランジスタN2のゲート電極におけるゲート長Lは数μm程度のものである。

【0023】

図2は、ゲート長Lを増大させたMOSトランジスタの構造例を示した模式図であり、同図(a)はその一例に関するもの、同図(b)はその他例に関するものである。

図2(a)においては、MOSトランジスタのゲート電極におけるゲート長Lを大きくするために、ドレイン電極−ソース電極間に設置されるゲート電極として、ドレイン電極−ソース電極間の距離が短距離構造のMOSトランジスタのゲート電極の場合と比べて2倍となっている。

【0024】

図2(b)においては、MOSトランジスタのゲート電極におけるゲート長Lをより大きくするために、2つのMOSトランジスタを直列に接続した構造としている。具体的には、1段目のMOSトランジスタのソース電極−ゲート電極−ドレイン電極の構造と、次段のMOSトランジスタのソース電極−ゲート電極−ドレイン電極の構造とにおいて、1段目のMOSトランジスタのドレイン電極と、次段のMOSトランジスタのソース電極とを接続し、且つ互いのゲート電極を結線している。このような構造では、1段目のMOSトランジスタのソース電極から次段のMOSトランジスタのドレイン電極に至る経路において、ゲート電極の下部領域が2倍の距離となり、実質的にゲート長Lを大きくすることができる。

こうしたゲート長Lを大きくした構造のMOSトランジスタを用いれば、ドレイン電極−ソース電極間の電位差がより大きくなり、ゲート電圧が閾値電圧Vthを下回り、弱反転領域の非飽和領域で動作する事態を回避することができる。

【0025】

尚、MOSトランジスタN2については、上述したようにゲート長LをP型MOSトランジスタP1、P2のゲート電極におけるゲート長Lよりも15倍以上大きくし、且つゲート長Lとゲート幅Wとの関係をL/W≧15とすることが望ましい。このようにMOSトランジスタN2のゲート長Lやそれとゲート幅Wとの関係を注目し、基準電圧生成回路1における低電圧な基準電圧VREFの生成に際して低消費電流化が図られるようにすれば、定電圧回路Aで低電圧な定電圧出力を得る上で有効となる。又、MOSトランジスタN2と対を成してカレントミラー回路を構成する各N型MOSトランジスタN3、N4、N7のゲート長Lについても、MOSトランジスタP1、P2のゲート長Lよりも増大させれば、定電圧回路Aで低消費電流で低電圧な定電圧出力を得る上で一層有効となる。

【0026】

次に、定電圧回路Aの動作を説明する。

図1の基準電圧生成回路1において、MOSトランジスタN1は定電流源として動作し、電流I1が流れると、第1の電源電圧VDDからMOSトランジスタP1に電流I1が流れると共に、カレントミラー回路を構成するMOSトランジスタP2には、MOSトランジスタP1、P2のサイズ比によって決まる電流I2が流れる。

この電流I2によってMOSトランジスタN2がオンの状態となり、MOSトランジスタN2のドレイン電極−ソース電極間に電流I2が流れるが、このとき、MOSトランジスタN2は、低いゲート電圧でオンの状態となり、ダイオード接続されているMOSトランジスタN2においては、ドレイン電極−ソース電極間の電圧Vdsが低電圧値で発生する。

【0027】

これにより、MOSトランジスタN2と対を成してカレントミラー回路を構成するMOSトランジスタN3、N4、N7において、正常に電流が発生すると共に、ドレイン電極−ソース電極間の電圧Vdsを0.1V以上に維持することができる。

MOSトランジスタN3においては、トリム端子3から、MOSトランジスタN2とのサイズ比で決まる電流I3が流れ、MOSトランジスタN2の電流をモニタリングすることができる。

一方、MOSトランジスタN2のドレイン電極に接続されている引き出し線からは、基準電圧VREFが出力され、定電圧出力回路2のMOSトランジスタN4、N5、N7のゲート電極にそれぞれ印加される。

【0028】

MOSトランジスタN4は、MOSトランジスタN2と対を成してカレントミラー回路を構成し、差動増幅器を構成するMOSトランジスタP3、P4、N5、N6から成る回路に流れる総電流量を決定する。

MOSトランジスタN5は、基準電圧VREFによってドレイン電極−ソース電極間に流れる電流Idsを変化させるが、このとき流れる電流Idsは、MOSトランジスタN6のゲート電圧との関係で異なるものとなる。即ち、MOSトランジスタN5、N6を流れる総電流量は、MOSトランジスタN4によって決定され、MOSトランジスタN5、N6のそれぞれのゲート電圧に印加される電圧によって、各MOSトランジスタN5、N6に流れる電流の比が決定される。

【0029】

このように決定された電流IdsがMOSトランジスタN5に流れ、MOSトランジスタN5のドレイン電極には、この電流Idsによる電圧値が現れる。

そして、この電圧値は、次段の増幅用トランジスタであるMOSトランジスタP5のゲート電圧に印加され、MOSトランジスタP5によって増幅された電圧値(MOSトランジスタP5のドレイン電圧)が定電圧出力端子4から出力される。

ここで、MOSトランジスタP5、P6、N7からなる部分は電流経路を構成するが、MOSトランジスタN7のドレイン電極−ソース電極間の電圧Vds、MOSトランジスタP6のドレイン電極−ソース電極間の電圧Vdsはほぼ一定であり、MOSトランジスタP5のドレイン電極−ソース電極間の電圧Vdsがゲート電圧によって変化されることにより、この電流経路における各部の電圧値が変化する。

【0030】

そして、MOSトランジスタN7のドレイン電極からMOSトランジスタN6のゲート電極には、電圧値がフィードバックされており、この電圧値によってMOSトランジスタN5、N6に流れる電流が変化し、定常の状態においては、これらMOSトランジスタN5、N6に流れる電流が安定して、定電圧出力端子4から出力される低い電圧が定電圧となる。

【0031】

以上のように、本実施形態に係る定電圧回路Aは、閾値電圧Vthが極小でゲート長Lが特大のデプリーション型のN型MOSトランジスタN1を用いて低電流を作り出し、基準電圧VREFを発生するN型MOSトランジスタN2、これと対を成してカレントミラー回路を構成する各N型MOSトランジスタN3、N4、N7、及びその他の各N型MOSトランジスタN5、N6の何れについても低閾値電圧タイプとし、且つMOSトランジスタN2、N3、N4、N7のゲート電極におけるゲート長LをMOSトランジスタP1、P2のゲート電極におけるゲート長Lよりも増大させている。これにより、各N型MOSトランジスタN2〜N7のドレイン電極−ソース電極間の電圧Vdsが0.1V以上の飽和領域で動作する電圧値を保ち、所望の低い基準電圧VREFを発生させることができ、カレントミラー回路を構成する際に正常動作させることが可能となる。

【0032】

即ち、本発明によれば、低消費電流で低電圧な定電圧を安定して得られる定電圧回路Aを実現することができる。

尚、本実施形態では、MOSトランジスタN2、及びこれと対を成してカレントミラー回路を構成する各N型MOSトランジスタN3、N4、N7のゲート長LをMOSトランジスタP1、P2のゲート長Lよりも増大させるものとして説明したが、これらについて、MOSトランジスタN2におけるドレイン電極−ソース電極間の電圧Vdsが一定の値となれば、カレントミラー回路を正常に動作させることができ、適切な基準電圧VREFを発生させることが可能となるため、低コストで課題を解決するためには、MOSトランジスタN2についてのみ、ゲート長Lを増大させることも可能である。

【符号の説明】

【0033】

A 定電圧回路、1 基準電圧生成回路、2 定電圧出力回路、3 トリム端子、4 定電圧出力端子

【技術分野】

【0001】

本発明は、レギュレータ用の定電圧回路に関する。

【背景技術】

【0002】

従来、この種の定電圧回路に適用される定電流回路としては、例えばソース電極に第1の電源電圧(正極電源)VDDが接続され、且つゲート電極とドレイン電極とを同電位に接続した一方のP型MOSトランジスタを定電流源と直列に接続することにより、第1の電源電圧VDDと接続点との間に閾値電圧に依存したバイアス電圧を得て他方のP型MOSトランジスタ(同様にソース電極は第1の電源電圧VDDに接続される)のゲート電極に印加し、カレントミラー回路を成す一対のN型MOSトランジスタが他方のP型MOSトランジスタで得られた定電流を被駆動回路へ供給する構成のもの(特許文献1参照)が挙げられる。

【0003】

この定電流回路を定電圧回路に適用する場合、定電流源に代えてゲート電極とソース電極とを同電位に接続した別のN型MOSトランジスタのドレイン電極を一方のP型MOSトランジスタのドレイン電極に接続すると共に、ソース電極を第2の電源電圧VSSに接続した構成にすることが可能である。この場合、他方のP型MOSトランジスタとドレイン電極同士が接続されたN型MOSトランジスタとの結線から、引き出し線を引き出して基準電圧VREFを得ることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平9−128067号公報(第4頁、図1)

【発明の概要】

【発明が解決しようとする課題】

【0005】

上述した特許文献1に係る定電圧回路用の定電流回路の場合、例えばカレントミラー回路を成す一対のN型MOSトランジスタが使用条件によって意図した通りに動作しなくなる場合がある。

一般にMOSトランジスタでは、ゲート電極−ソース電極間の電圧Vgsを閾値電圧Vth未満で動作させる場合を弱反転領域にあり、ゲート電極−ソース電極間の電圧Vgsを閾値電圧Vth以上で動作させる場合を強反転領域にあるとみなすことができる。又、ドレイン電極−ソース電極間の電圧Vdsを凡そ0.1V未満で動作させた場合はダイオード接続の有無に拘らず線形領域にあり、ドレイン電極−ソース電極間の電圧Vdsを凡そ0.1V以上で動作させた場合は飽和領域にあるとみなすことができる。

【0006】

上述した定電流回路におけるカレントミラー回路を成す一対のN型MOSトランジスタの場合、飽和領域で使用した場合に正常動作するものであるため、低閾値電圧タイプのものを用いた場合に弱反転領域の非飽和領域で動作すると、特にダイオード接続された一方のものについては、使用条件によってはドレイン電極−ソース電極間の電圧Vdsが0.1V未満になること(閾値電圧Vthは高温条件下で低下することが知られている)があり、こうした場合には他方のものが正常に動作せず、カレントミラー回路が意図した通りに動作しなくなってしまうという問題がある。

【0007】

即ち、カレントミラー回路におけるダイオード接続された一方のN型MOSトランジスタについては、飽和領域の0.1Vを超えたドレイン電極−ソース電極間の電圧Vdsを保持して使用しないと、カレントミラー回路が正常動作しないことになる。それ故、現状の定電流回路では、低閾値電圧タイプのMOSトランジスタを用いるとドレイン電極−ソース電極間の電圧Vdsが0.1V未満になることを完全には阻止できず、係る定電流回路を定電圧回路として構成した場合には、低消費電流で低電圧な定電圧を安定して得ることができない。

そこで、本発明の技術的課題は、低消費電流で低電圧な定電圧を安定して得られる定電圧回路を提供することにある。

【課題を解決するための手段】

【0008】

上記技術的課題を解決するための第1の発明は、

ソース電極に第1の電源電圧が接続され、且つゲート電極とドレイン電極とを同電位に接続した第1のP型MOSトランジスタ(例えば、図1のMOSトランジスタP1)と、

ソース電極に第1の電源電圧が接続され、且つゲート電極が前記第1のP型MOSトランジスタのゲート電極及びドレイン電極に接続された第2のP型MOSトランジスタ(例えば、図1のMOSトランジスタP2)と、

ソース電極に第2の電源電圧が接続され、且つゲート電極とソース電極とを同電位に接続し、ドレイン電極が第1のP型MOSトランジスタのドレイン電極に接続された第1のN型MOSトランジスタ(例えば、図1のMOSトランジスタN1)と、

ソース電極に第2の電源電圧が接続され、且つゲート電極とドレイン電極とを同電位に接続し、ドレイン電極が前記第2のP型MOSトランジスタのドレイン電極に接続された第2のN型MOSトランジスタ(例えば、図1のMOSトランジスタN2)と、

ソース電極に第2の電源電圧が接続され、且つゲート電極が前記第2のN型MOSトランジスタのドレイン電極に接続され、ドレイン電極がトリム端子(例えば、図1のトリム端子3)に接続された第3のN型MOSトランジスタ(例えば、図1のMOSトランジスタN3)と、を備えて構成され、

前記第2のP型MOSトランジスタと前記第2のN型MOSトランジスタとにおけるドレイン電極同士の結線に対する接続引き出し線から基準電圧を生成出力する基準電圧生成回路(例えば、図1の基準電圧生成回路1)を含み、

前記第1のN型MOSトランジスタは、閾値電圧が極小のデプリーション型であると共に、ゲート長が前記第2のN型MOSトランジスタのゲート長よりも大きく、

前記第2のN型MOSトランジスタは、前記第1のN型MOSトランジスタよりも閾値電圧が高い低閾値電圧タイプであると共に、ゲート長が前記第1のP型MOSトランジスタ及び前記第2のP型MOSトランジスタのゲート長の15倍以上大きく、

前記第3のN型MOSトランジスタの閾値電圧は、前記第2のN型MOSトランジスタの閾値電圧と同じであり、

前記トリム端子は、前記第3のN型MOSトランジスタのドレイン電極へ所定の電圧値を印加することにより、前記第2のP型MOSトランジスタのソース電極−ドレイン電極間、並びに前記第2のN型MOSトランジスタのドレイン電極−ソース電極間を流れる電流をモニタするものであることを特徴とする定電圧回路である。

【0009】

このような構成により、閾値電圧Vthが極小でゲート長が特大のデプリーション型の第1のMOSトランジスタに対し、それよりも閾値電圧Vthが大きい低閾値電圧タイプの基準電圧VREFを発生する第2のN型MOSトランジスタのゲート長を第1のP型MOSトランジスタ及び第2のP型MOSトランジスタP2のゲート長Lの15倍以上大きくし、且つMOSトランジスタN2と対を成してカレントミラー回路を構成する第3のN型MOSトランジスタについても同等な低閾値電圧タイプを用いているため、第1のN型MOSトランジスタで低電流を作り出し、第2のN型MOSトランジスタで低電圧な基準電圧VREFを発生する際、第3のN型MOSトランジスタを介して第2のN型MOSトランジスタに流れる電流を適切に検出でき、第2のN型MOSトランジスタのドレイン電極−ソース電極間の電圧Vdsを0.1V以上に維持できると共に、第3のN型MOSトランジスタのドレイン電極−ソース電極間の電圧Vdsについてはトリム端子への電圧印加により0.1V超過にでき、各N型MOSトランジスタのドレイン電極−ソース電極間の電圧Vdsが飽和領域で動作する電圧値を保つことができる。

この結果、各N型MOSトランジスタに低閾値電圧タイプのものを用いているにも拘らず、ドレイン電極−ソース電極間の電圧Vdsが飽和領域で安定して動作するため、弱反転領域における非飽和領域で動作される状態が回避され、所望の低い基準電圧を発生させることができ、カレントミラー回路を構成する際に正常動作させることが可能となる。

【0010】

又、第2の発明は、

前記第3のN型MOSトランジスタのゲート幅は、前記第2のN型MOSトランジスタのゲート幅よりも大きいことを特徴とする定電圧回路である。

このような構成により、基準電圧生成回路において、基準電圧を発生する第2のN型MOSトランジスタに流れる電流が小さくて外部端子から直接モニタできないため、これを倍増した第3のN型MOSトランジスタを流れる電流により正確にモニタすることができる。

【0011】

更に、第3の発明は、

ゲート電極が前記基準電圧に接続され、且つソース電極が第2の電源電圧に接続された第4のN型MOSトランジスタ(例えば、図1のMOSトランジスタN4)と、

ゲート電極が前記基準電圧に接続され、且つソース電極が前記第4のN型MOSトランジスタのドレイン電極に接続された第5のN型MOSトランジスタ(例えば、図1のMOSトランジスタN5)と、

ソース電極に第1の電源電圧が接続され、且つドレイン電極が前記第5のN型MOSトランジスタのドレイン電極に接続された第3のP型MOSトランジスタ(例えば、図1のMOSトランジスタP3)と、

ソース電極に第1の電源電圧が接続され、且つゲート電極が前記第3のP型MOSトランジスタのゲート電極に接続されると共に、ドレイン電極と同電位に接続した第4のP型MOSトランジスタ(例えば、図1のMOSトランジスタP4)と、

ソース電極に第1の電源電圧が接続され、且つゲート電極が前記第3のP型MOSトランジスタのドレイン電極と前記第5のN型MOSトランジスタのドレイン電極との結線に接続された第5のP型MOSトランジスタ(例えば、図1のMOSトランジスタP5)と、

ソース電極が前記第5のN型MOSトランジスタのソース電極及び前記第4のN型MOSトランジスタのドレイン電極に接続され、且つドレイン電極が前記第4のP型MOSトランジスタのドレイン電極に接続された第6のN型MOSトランジスタ(例えば、図1のMOSトランジスタN6)と、

ソース電極が前記第5のP型MOSトランジスタのドレイン電極に接続され、且つゲート電極とドレイン電極とを同電位に接続した第6のP型MOSトランジスタ(例えば、図1のMOSトランジスタP6)と、

ゲート電極が前記基準電圧に接続され、ソース電極が第2の電源電圧に接続され、且つドレインが前記第6のP型MOSトランジスタのドレイン電極及び前記第6のN型MOSトランジスタのゲート電極に接続された第7のN型MOSトランジスタ(例えば、図1のMOSトランジスタN7)と、を備えて構成され、

前記第4のN型MOSトランジスタ、前記第5のN型MOSトランジスタ、前記第6のN型MOSトランジスタ、及び前記第7のN型MOSトランジスタの閾値電圧は、それぞれ前記第2のN型MOSトランジスタの閾値電圧と同じであり、

前記第5のP型MOSトランジスタのドレイン電極と前記第6のP型MOSトランジスタのソース電極との結線に対する接続引き出し線から定電圧を出力する定電圧出力回路を(例えば、図1の定電圧出力回路2)含むことを特徴とする定電圧回路である。

【0012】

このような構成により、基準電圧生成回路によって低消費電流で生成された低電圧な基準電圧を用いて差動増幅により定電圧を出力するとき、定電圧出力回路におけるMOSトランジスタを低閾値電圧で駆動できるため、低電圧な定電圧を安定して得ることが可能となる。

即ち、本発明によれば、低消費電流で低電圧な基準電圧を生成する定電圧回路を実現することができる。

【0013】

加えて、第4の発明は、

前記第2のN型MOSトランジスタは、ゲート幅に対するゲート長の比を示すゲート長/ゲート幅が15以上であることを特徴とする定電圧回路である。

このような構成により、基準電圧生成回路における低電圧な基準電圧の生成に際して的確に低消費電流化が図られる。

【0014】

又、第5の発明は、

前記第2のN型MOSトランジスタのゲート長は、前記第6のN型MOSトランジスタ及び前記第7のN型MOSトランジスタのゲート長の15倍以上であることを特徴とする定電圧回路である。

このような構成により、基準電圧生成回路における低電圧な基準電圧の生成に際して一層低消費電流化が図られるため、定電圧回路において、低消費電流で低電圧な定電圧出力を得る上で有効となる。

【図面の簡単な説明】

【0015】

【図1】本発明の実施形態に係る定電圧回路Aの基本構成を示した回路図である。

【図2】ゲート長Lを増大させたMOSトランジスタの構造例を示した模式図であり、(a)はその一例に関するもの、(b)はその他例に関するものである。

【発明を実施するための形態】

【0016】

以下、図を参照して本発明に係る定電圧回路の実施形態を説明する。

図1は、本発明の実施形態に係る定電圧回路Aの基本構成を示した回路図である。ここでの定電圧回路Aは、低電圧な基準電圧VREFを生成出力する基準電圧生成回路1と、この基準電圧VREFを用いて差動増幅により定電圧を出力する定電圧出力回路2とから構成される。このうち、基準電圧生成回路1は、ソース電極に第1の電源電圧VDDが接続され、且つゲート電極とドレイン電極とを同電位に接続したP型のMOSトランジスタP1と、ソース電極に第1の電源電圧VDDが接続され、且つゲート電極がMOSトランジスタP1のゲート電極及びドレイン電極に接続されたP型のMOSトランジスタP2と、ソース電極に第2の電源電圧VSSが接続され、且つゲート電極とソース電極とを同電位に接続し、ドレイン電極がMOSトランジスタP1のドレイン電極に接続されたN型のMOSトランジスタN1と、ソース電極に第2の電源電圧VSSが接続され、且つゲート電極とドレイン電極とを同電位に接続し、ドレイン電極がMOSトランジスタP2のドレイン電極に接続されたN型のMOSトランジスタN2と、ソース電極に第2の電源電圧VSSが接続され、且つゲート電極がN型MOSトランジスタN2のドレイン電極に接続され、ドレイン電極がトリム端子3に接続されたN型のMOSトランジスタN3と、を備えている。

【0017】

この基準電圧生成回路1において、MOSトランジスタP2とMOSトランジスタN2とにおけるドレイン電極同士の結線には、引き出し線が接続されており、この引き出し線から基準電圧VREFが出力される。

細部について説明すれば、MOSトランジスタN1は、閾値電圧Vthが0V以下の極小のデプリーション型であると共に、ゲート電極におけるソース電極−ドレイン電極間の距離を示すゲート長LがMOSトランジスタN2のゲート長Lよりも大きく、定電流源としてドレイン電極−ソース電極間に微弱な電流I1が流れる。基準電圧VREFを発生するMOSトランジスタN2は、MOSトランジスタN1よりも閾値電圧Vthが高く、例えば0.35Vの低閾値電圧タイプである。又、MOSトランジスタN2は、ゲート長LがMOSトランジスタP1、P2のゲート長Lの15倍以上大きくなっている。更に、MOSトランジスタN2と対を成してカレントミラー回路を構成するMOSトランジスタN3の閾値電圧Vthは、MOSトランジスタN2の閾値電圧Vthと同じである。トリム端子3は、MOSトランジスタN3のドレイン電極へ所定の電圧値を印加することにより、MOSトランジスタP2のソース電極−ドレイン電極間、並びにMOSトランジスタN2のドレイン電極−ソース電極間を流れる電流I2をモニタするものである。即ち、トリム端子3は、MOSトランジスタN3を流れる電流I3によって、MOSトランジスタN2に流れる電流I2をモニタするためのものであり、電流モニタ用の電圧(例えば1V程度)が印加されている。

【0018】

この基準電圧生成回路1では、閾値電圧Vthが極小でゲート長Lが特大のデプリーション型のMOSトランジスタN1に対し、それよりも閾値電圧Vthが大きい低閾値電圧タイプの基準電圧VREFを発生するMOSトランジスタN2のゲート長LをMOSトランジスタP1、P2のゲート長Lの15倍以上大きくし、且つMOSトランジスタN2と対を成してカレントミラー回路を構成するMOSトランジスタN3についても同等な低閾値電圧タイプを用いている。このため、MOSトランジスタN1で低電流を作り出し、MOSトランジスタN2で低電圧な基準電圧VREFを発生する際、MOSトランジスタN3を介してMOSトランジスタN2に流れる電流を適切に検出でき、MOSトランジスタN2のドレイン電極−ソース電極間の電圧Vdsを0.1V以上に維持できると共に、MOSトランジスタN3のドレイン電極−ソース電極間の電圧Vdsはトリム端子3に1Vの電圧が印加されているために0.1V超過となり、各N型MOSトランジスタN2、N3のドレイン電極−ソース電極間の電圧Vdsが飽和領域で動作する電圧値を保つことができる。

【0019】

この結果、MOSトランジスタN2、N3に低閾値電圧タイプのものを用いているにも拘らず、各N型MOSトランジスタN2、N3のドレイン電極−ソース電極間の電圧Vdsが飽和領域で安定して動作するため、弱反転領域における非飽和領域で動作される状態が回避され、所望の低い基準電圧VREFを発生させることができ、しかもカレントミラー回路を構成する際に正常動作させることが可能となる。従って、この基準電圧生成回路1の場合、低消費電流で低電圧な基準電圧VREFを生成することができる。

尚、MOSトランジスタN3のゲート電極におけるゲート幅WをMOSトランジスタN2のゲート電極におけるゲート幅Wよりも大きくしておけば、MOSトランジスタN2に流れる電流I2が小さくて外部端子から直接モニタできないため、これを倍増したMOSトランジスタN3を流れる電流I3により正確にモニタすることができる。

【0020】

又、定電圧出力回路2は、ゲート電極が基準電圧生成回路1の引き出し線(基準電圧VREF)に接続され、且つソース電極が第2の電源電圧VSSに接続されたN型のMOSトランジスタN4と、ゲート電極が基準電圧生成回路1の引き出し線(基準電圧VREF)に接続され、且つソース電極がMOSトランジスタN4のドレイン電極に接続されたN型のMOSトランジスタN5と、ソース電極に第1の電源電圧VDDが接続され、且つドレイン電極がMOSトランジスタN5のドレイン電極に接続されたP型のMOSトランジスタP3と、ソース電極に第1の電源電圧VDDが接続され、且つゲート電極がMOSトランジスタP3のゲート電極に接続されると共に、ドレイン電極と同電位に接続したP型のMOSトランジスタP4と、ソース電極に第1の電源電圧VDDが接続され、且つゲート電極がMOSトランジスタP3のドレイン電極とMOSトランジスタN5のドレイン電極との結線に接続されたP型のMOSトランジスタP5と、ソース電極がMOSトランジスタN5のソース電極及びMOSトランジスタN4のドレイン電極に接続され、且つドレイン電極がMOSトランジスタP4のドレイン電極に接続されたN型のMOSトランジスタN6と、ソース電極がMOSトランジスタP5のドレイン電極に接続され、且つゲート電極とドレイン電極とを同電位に接続したP型のMOSトランジスタP6と、ゲート電極が基準電圧生成回路1の引き出し線(基準電圧VREF)に接続され、ソース電極が第2の電源電圧VSSに接続され、且つドレインがMOSトランジスタP6のドレイン電極及びMOSトランジスタN6のゲート電極に接続されたN型のMOSトランジスタN7と、MOSトランジスタP5のドレイン電極及びMOSトランジスタP6のソース電極の結線とMOSトランジスタP5のゲート電極との間に介在させた容量端子Cと、を備えている。

【0021】

この定電圧出力回路2において、MOSトランジスタP5のドレイン電極とMOSトランジスタP6のソース電極との結線には、引き出し線が接続されており、この引き出し線の終端に位置する定電圧出力端子4から定電圧回路Aの出力である定電圧が出力される。MOSトランジスタN4〜N7については、閾値電圧VthがMOSトランジスタN2、N3と同じ0.35Vの低閾値電圧タイプのものとしている。

本実施形態に係る定電圧回路Aの場合、基準電圧生成回路1では消費電力を低減する目的で基準電圧VREFをより低電圧なものとし、MOSトランジスタN1の発生電流I1を低電流化している。例えば、電流I1は10nA程度で発生させる。

このとき、MOSトランジスタP1、P2から成るカレントミラー回路によって、MOSトランジスタN2に電流I2が流れるが、MOSトランジスタN2は弱反転領域で使用するため、ダイオード接続されたMOSトランジスタN2は、ゲート電圧が低電圧の状態で駆動される。

【0022】

ここで、MOSトランジスタN2において、ドレイン電極−ソース電極間の電圧Vdsが閾値電圧Vthを下回り、0.1V程度となった場合、MOSトランジスタN2が弱反転領域の非飽和領域で動作する状態となる可能性がある。

このような事態を回避するため、低閾値電圧タイプのMOSトランジスタN2については、ゲート電極におけるゲート長LをP型MOSトランジスタP1、P2のゲート電極におけるゲート長Lよりも15倍以上大きくしている。上述したデプリーション型のMOSトランジスタN1のゲート電極におけるゲート長Lは数mm程度の特大なものであり、MOSトランジスタN2のゲート電極におけるゲート長Lは数μm程度のものである。

【0023】

図2は、ゲート長Lを増大させたMOSトランジスタの構造例を示した模式図であり、同図(a)はその一例に関するもの、同図(b)はその他例に関するものである。

図2(a)においては、MOSトランジスタのゲート電極におけるゲート長Lを大きくするために、ドレイン電極−ソース電極間に設置されるゲート電極として、ドレイン電極−ソース電極間の距離が短距離構造のMOSトランジスタのゲート電極の場合と比べて2倍となっている。

【0024】

図2(b)においては、MOSトランジスタのゲート電極におけるゲート長Lをより大きくするために、2つのMOSトランジスタを直列に接続した構造としている。具体的には、1段目のMOSトランジスタのソース電極−ゲート電極−ドレイン電極の構造と、次段のMOSトランジスタのソース電極−ゲート電極−ドレイン電極の構造とにおいて、1段目のMOSトランジスタのドレイン電極と、次段のMOSトランジスタのソース電極とを接続し、且つ互いのゲート電極を結線している。このような構造では、1段目のMOSトランジスタのソース電極から次段のMOSトランジスタのドレイン電極に至る経路において、ゲート電極の下部領域が2倍の距離となり、実質的にゲート長Lを大きくすることができる。

こうしたゲート長Lを大きくした構造のMOSトランジスタを用いれば、ドレイン電極−ソース電極間の電位差がより大きくなり、ゲート電圧が閾値電圧Vthを下回り、弱反転領域の非飽和領域で動作する事態を回避することができる。

【0025】

尚、MOSトランジスタN2については、上述したようにゲート長LをP型MOSトランジスタP1、P2のゲート電極におけるゲート長Lよりも15倍以上大きくし、且つゲート長Lとゲート幅Wとの関係をL/W≧15とすることが望ましい。このようにMOSトランジスタN2のゲート長Lやそれとゲート幅Wとの関係を注目し、基準電圧生成回路1における低電圧な基準電圧VREFの生成に際して低消費電流化が図られるようにすれば、定電圧回路Aで低電圧な定電圧出力を得る上で有効となる。又、MOSトランジスタN2と対を成してカレントミラー回路を構成する各N型MOSトランジスタN3、N4、N7のゲート長Lについても、MOSトランジスタP1、P2のゲート長Lよりも増大させれば、定電圧回路Aで低消費電流で低電圧な定電圧出力を得る上で一層有効となる。

【0026】

次に、定電圧回路Aの動作を説明する。

図1の基準電圧生成回路1において、MOSトランジスタN1は定電流源として動作し、電流I1が流れると、第1の電源電圧VDDからMOSトランジスタP1に電流I1が流れると共に、カレントミラー回路を構成するMOSトランジスタP2には、MOSトランジスタP1、P2のサイズ比によって決まる電流I2が流れる。

この電流I2によってMOSトランジスタN2がオンの状態となり、MOSトランジスタN2のドレイン電極−ソース電極間に電流I2が流れるが、このとき、MOSトランジスタN2は、低いゲート電圧でオンの状態となり、ダイオード接続されているMOSトランジスタN2においては、ドレイン電極−ソース電極間の電圧Vdsが低電圧値で発生する。

【0027】

これにより、MOSトランジスタN2と対を成してカレントミラー回路を構成するMOSトランジスタN3、N4、N7において、正常に電流が発生すると共に、ドレイン電極−ソース電極間の電圧Vdsを0.1V以上に維持することができる。

MOSトランジスタN3においては、トリム端子3から、MOSトランジスタN2とのサイズ比で決まる電流I3が流れ、MOSトランジスタN2の電流をモニタリングすることができる。

一方、MOSトランジスタN2のドレイン電極に接続されている引き出し線からは、基準電圧VREFが出力され、定電圧出力回路2のMOSトランジスタN4、N5、N7のゲート電極にそれぞれ印加される。

【0028】

MOSトランジスタN4は、MOSトランジスタN2と対を成してカレントミラー回路を構成し、差動増幅器を構成するMOSトランジスタP3、P4、N5、N6から成る回路に流れる総電流量を決定する。

MOSトランジスタN5は、基準電圧VREFによってドレイン電極−ソース電極間に流れる電流Idsを変化させるが、このとき流れる電流Idsは、MOSトランジスタN6のゲート電圧との関係で異なるものとなる。即ち、MOSトランジスタN5、N6を流れる総電流量は、MOSトランジスタN4によって決定され、MOSトランジスタN5、N6のそれぞれのゲート電圧に印加される電圧によって、各MOSトランジスタN5、N6に流れる電流の比が決定される。

【0029】

このように決定された電流IdsがMOSトランジスタN5に流れ、MOSトランジスタN5のドレイン電極には、この電流Idsによる電圧値が現れる。

そして、この電圧値は、次段の増幅用トランジスタであるMOSトランジスタP5のゲート電圧に印加され、MOSトランジスタP5によって増幅された電圧値(MOSトランジスタP5のドレイン電圧)が定電圧出力端子4から出力される。

ここで、MOSトランジスタP5、P6、N7からなる部分は電流経路を構成するが、MOSトランジスタN7のドレイン電極−ソース電極間の電圧Vds、MOSトランジスタP6のドレイン電極−ソース電極間の電圧Vdsはほぼ一定であり、MOSトランジスタP5のドレイン電極−ソース電極間の電圧Vdsがゲート電圧によって変化されることにより、この電流経路における各部の電圧値が変化する。

【0030】

そして、MOSトランジスタN7のドレイン電極からMOSトランジスタN6のゲート電極には、電圧値がフィードバックされており、この電圧値によってMOSトランジスタN5、N6に流れる電流が変化し、定常の状態においては、これらMOSトランジスタN5、N6に流れる電流が安定して、定電圧出力端子4から出力される低い電圧が定電圧となる。

【0031】

以上のように、本実施形態に係る定電圧回路Aは、閾値電圧Vthが極小でゲート長Lが特大のデプリーション型のN型MOSトランジスタN1を用いて低電流を作り出し、基準電圧VREFを発生するN型MOSトランジスタN2、これと対を成してカレントミラー回路を構成する各N型MOSトランジスタN3、N4、N7、及びその他の各N型MOSトランジスタN5、N6の何れについても低閾値電圧タイプとし、且つMOSトランジスタN2、N3、N4、N7のゲート電極におけるゲート長LをMOSトランジスタP1、P2のゲート電極におけるゲート長Lよりも増大させている。これにより、各N型MOSトランジスタN2〜N7のドレイン電極−ソース電極間の電圧Vdsが0.1V以上の飽和領域で動作する電圧値を保ち、所望の低い基準電圧VREFを発生させることができ、カレントミラー回路を構成する際に正常動作させることが可能となる。

【0032】

即ち、本発明によれば、低消費電流で低電圧な定電圧を安定して得られる定電圧回路Aを実現することができる。

尚、本実施形態では、MOSトランジスタN2、及びこれと対を成してカレントミラー回路を構成する各N型MOSトランジスタN3、N4、N7のゲート長LをMOSトランジスタP1、P2のゲート長Lよりも増大させるものとして説明したが、これらについて、MOSトランジスタN2におけるドレイン電極−ソース電極間の電圧Vdsが一定の値となれば、カレントミラー回路を正常に動作させることができ、適切な基準電圧VREFを発生させることが可能となるため、低コストで課題を解決するためには、MOSトランジスタN2についてのみ、ゲート長Lを増大させることも可能である。

【符号の説明】

【0033】

A 定電圧回路、1 基準電圧生成回路、2 定電圧出力回路、3 トリム端子、4 定電圧出力端子

【特許請求の範囲】

【請求項1】

ソース電極に第1の電源電圧が接続され、且つゲート電極とドレイン電極とを同電位に接続した第1のP型MOSトランジスタと、

ソース電極に第1の電源電圧が接続され、且つゲート電極が前記第1のP型MOSトランジスタのゲート電極及びドレイン電極に接続された第2のP型MOSトランジスタと、

ソース電極に第2の電源電圧が接続され、且つゲート電極とソース電極とを同電位に接続し、ドレイン電極が第1のP型MOSトランジスタのドレイン電極に接続された第1のN型MOSトランジスタと、

ソース電極に第2の電源電圧が接続され、且つゲート電極とドレイン電極とを同電位に接続し、ドレイン電極が前記第2のP型MOSトランジスタのドレイン電極に接続された第2のN型MOSトランジスタと、

ソース電極に第2の電源電圧が接続され、且つゲート電極が前記第2のN型MOSトランジスタのドレイン電極に接続され、ドレイン電極がトリム端子に接続された第3のN型MOSトランジスタと、を備えて構成され、

前記第2のP型MOSトランジスタと前記第2のN型MOSトランジスタとにおけるドレイン電極同士の結線に対する接続引き出し線から基準電圧を生成出力する基準電圧生成回路を含み、

前記第1のN型MOSトランジスタは、閾値電圧が極小のデプリーション型であると共に、ゲート長が前記第2のN型MOSトランジスタのゲート長よりも大きく、

前記第2のN型MOSトランジスタは、前記第1のN型MOSトランジスタよりも閾値電圧が高い低閾値電圧タイプであると共に、ゲート長が前記第1のP型MOSトランジスタ及び前記第2のP型MOSトランジスタのゲート長の15倍以上大きく、

前記第3のN型MOSトランジスタの閾値電圧は、前記第2のN型MOSトランジスタの閾値電圧と同じであり、

前記トリム端子は、前記第3のN型MOSトランジスタのドレイン電極へ所定の電圧値を印加することにより、前記第2のP型MOSトランジスタのソース電極−ドレイン電極間、並びに前記第2のN型MOSトランジスタのドレイン電極−ソース電極間を流れる電流をモニタするものであることを特徴とする定電圧回路。

【請求項2】

前記第3のN型MOSトランジスタのゲート幅は、前記第2のN型MOSトランジスタのゲート幅よりも大きいことを特徴とする請求項1記載の定電圧回路。

【請求項3】

ゲート電極が前記基準電圧に接続され、且つソース電極が第2の電源電圧に接続された第4のN型MOSトランジスタと、

ゲート電極が前記基準電圧に接続され、且つソース電極が前記第4のN型MOSトランジスタのドレイン電極に接続された第5のN型MOSトランジスタと、

ソース電極に第1の電源電圧が接続され、且つドレイン電極が前記第5のN型MOSトランジスタのドレイン電極に接続された第3のP型MOSトランジスタと、

ソース電極に第1の電源電圧が接続され、且つゲート電極が前記第3のP型MOSトランジスタのゲート電極に接続されると共に、ドレイン電極と同電位に接続した第4のP型MOSトランジスタと、

ソース電極に第1の電源電圧が接続され、且つゲート電極が前記第3のP型MOSトランジスタのドレイン電極と前記第5のN型MOSトランジスタのドレイン電極との結線に接続された第5のP型MOSトランジスタと、

ソース電極が前記第5のN型MOSトランジスタのソース電極及び前記第4のN型MOSトランジスタのドレイン電極に接続され、且つドレイン電極が前記第4のP型MOSトランジスタのドレイン電極に接続された第6のN型MOSトランジスタと、

ソース電極が前記第5のP型MOSトランジスタのドレイン電極に接続され、且つゲート電極とドレイン電極とを同電位に接続した第6のP型MOSトランジスタと、

ゲート電極が前記基準電圧に接続され、ソース電極が第2の電源電圧に接続され、且つドレインが前記第6のP型MOSトランジスタのドレイン電極及び前記第6のN型MOSトランジスタのゲート電極に接続された第7のN型MOSトランジスタと、を備えて構成され、

前記第4のN型MOSトランジスタ、前記第5のN型MOSトランジスタ、前記第6のN型MOSトランジスタ、及び前記第7のN型MOSトランジスタの閾値電圧は、それぞれ前記第2のN型MOSトランジスタの閾値電圧と同じであり、

前記第5のP型MOSトランジスタのドレイン電極と前記第6のP型MOSトランジスタのソース電極との結線に対する接続引き出し線から定電圧を出力する定電圧出力回路を含むことを特徴とする請求項1又は2記載の定電圧回路。

【請求項4】

前記第2のN型MOSトランジスタは、ゲート幅に対するゲート長の比を示すゲート長/ゲート幅が15以上であることを特徴とする請求項1〜3の何れか一つに記載の定電圧回路。

【請求項5】

前記第2のN型MOSトランジスタのゲート長は、前記第6のN型MOSトランジスタ及び前記第7のN型MOSトランジスタのゲート長の15倍以上であることを特徴とする請求項3又は4記載の定電圧回路。

【請求項1】

ソース電極に第1の電源電圧が接続され、且つゲート電極とドレイン電極とを同電位に接続した第1のP型MOSトランジスタと、

ソース電極に第1の電源電圧が接続され、且つゲート電極が前記第1のP型MOSトランジスタのゲート電極及びドレイン電極に接続された第2のP型MOSトランジスタと、

ソース電極に第2の電源電圧が接続され、且つゲート電極とソース電極とを同電位に接続し、ドレイン電極が第1のP型MOSトランジスタのドレイン電極に接続された第1のN型MOSトランジスタと、

ソース電極に第2の電源電圧が接続され、且つゲート電極とドレイン電極とを同電位に接続し、ドレイン電極が前記第2のP型MOSトランジスタのドレイン電極に接続された第2のN型MOSトランジスタと、

ソース電極に第2の電源電圧が接続され、且つゲート電極が前記第2のN型MOSトランジスタのドレイン電極に接続され、ドレイン電極がトリム端子に接続された第3のN型MOSトランジスタと、を備えて構成され、

前記第2のP型MOSトランジスタと前記第2のN型MOSトランジスタとにおけるドレイン電極同士の結線に対する接続引き出し線から基準電圧を生成出力する基準電圧生成回路を含み、

前記第1のN型MOSトランジスタは、閾値電圧が極小のデプリーション型であると共に、ゲート長が前記第2のN型MOSトランジスタのゲート長よりも大きく、

前記第2のN型MOSトランジスタは、前記第1のN型MOSトランジスタよりも閾値電圧が高い低閾値電圧タイプであると共に、ゲート長が前記第1のP型MOSトランジスタ及び前記第2のP型MOSトランジスタのゲート長の15倍以上大きく、

前記第3のN型MOSトランジスタの閾値電圧は、前記第2のN型MOSトランジスタの閾値電圧と同じであり、

前記トリム端子は、前記第3のN型MOSトランジスタのドレイン電極へ所定の電圧値を印加することにより、前記第2のP型MOSトランジスタのソース電極−ドレイン電極間、並びに前記第2のN型MOSトランジスタのドレイン電極−ソース電極間を流れる電流をモニタするものであることを特徴とする定電圧回路。

【請求項2】

前記第3のN型MOSトランジスタのゲート幅は、前記第2のN型MOSトランジスタのゲート幅よりも大きいことを特徴とする請求項1記載の定電圧回路。

【請求項3】

ゲート電極が前記基準電圧に接続され、且つソース電極が第2の電源電圧に接続された第4のN型MOSトランジスタと、

ゲート電極が前記基準電圧に接続され、且つソース電極が前記第4のN型MOSトランジスタのドレイン電極に接続された第5のN型MOSトランジスタと、

ソース電極に第1の電源電圧が接続され、且つドレイン電極が前記第5のN型MOSトランジスタのドレイン電極に接続された第3のP型MOSトランジスタと、

ソース電極に第1の電源電圧が接続され、且つゲート電極が前記第3のP型MOSトランジスタのゲート電極に接続されると共に、ドレイン電極と同電位に接続した第4のP型MOSトランジスタと、

ソース電極に第1の電源電圧が接続され、且つゲート電極が前記第3のP型MOSトランジスタのドレイン電極と前記第5のN型MOSトランジスタのドレイン電極との結線に接続された第5のP型MOSトランジスタと、

ソース電極が前記第5のN型MOSトランジスタのソース電極及び前記第4のN型MOSトランジスタのドレイン電極に接続され、且つドレイン電極が前記第4のP型MOSトランジスタのドレイン電極に接続された第6のN型MOSトランジスタと、

ソース電極が前記第5のP型MOSトランジスタのドレイン電極に接続され、且つゲート電極とドレイン電極とを同電位に接続した第6のP型MOSトランジスタと、

ゲート電極が前記基準電圧に接続され、ソース電極が第2の電源電圧に接続され、且つドレインが前記第6のP型MOSトランジスタのドレイン電極及び前記第6のN型MOSトランジスタのゲート電極に接続された第7のN型MOSトランジスタと、を備えて構成され、

前記第4のN型MOSトランジスタ、前記第5のN型MOSトランジスタ、前記第6のN型MOSトランジスタ、及び前記第7のN型MOSトランジスタの閾値電圧は、それぞれ前記第2のN型MOSトランジスタの閾値電圧と同じであり、

前記第5のP型MOSトランジスタのドレイン電極と前記第6のP型MOSトランジスタのソース電極との結線に対する接続引き出し線から定電圧を出力する定電圧出力回路を含むことを特徴とする請求項1又は2記載の定電圧回路。

【請求項4】

前記第2のN型MOSトランジスタは、ゲート幅に対するゲート長の比を示すゲート長/ゲート幅が15以上であることを特徴とする請求項1〜3の何れか一つに記載の定電圧回路。

【請求項5】

前記第2のN型MOSトランジスタのゲート長は、前記第6のN型MOSトランジスタ及び前記第7のN型MOSトランジスタのゲート長の15倍以上であることを特徴とする請求項3又は4記載の定電圧回路。

【図1】

【図2】

【図2】

【公開番号】特開2013−65358(P2013−65358A)

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願番号】特願2013−5196(P2013−5196)

【出願日】平成25年1月16日(2013.1.16)

【分割の表示】特願2008−129296(P2008−129296)の分割

【原出願日】平成20年5月16日(2008.5.16)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願日】平成25年1月16日(2013.1.16)

【分割の表示】特願2008−129296(P2008−129296)の分割

【原出願日】平成20年5月16日(2008.5.16)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]