電圧駆動素子の駆動回路

【課題】電圧駆動素子のスイッチ時のサージ電圧とリンギングを抑制して、ノイズ放射による誤動作を防止する。

【解決手段】電圧駆動素子であるIGBT(Q11)に、誘導性負荷L11とユニポーラ型の還流ダイオードD12が接続されている。Q11のターンオフ時に、Q11のコレクタからコンデンサC11とダイオードD11及び抵抗R19を介して、ベース抵抗R12へ電流が流れ、ベース抵抗R12で電圧が発生し、PNPトランジスタQ12のベース電圧Vbは上昇する。この電圧上昇速度は、コンデンサC11とベース抵抗R12及び抵抗R19によって決まる時定数により決定され、上昇電圧はベース抵抗R12と抵抗R19で分圧される。これによりQ12のベース電圧Vbの変化速度、即ちQ11のゲート電圧Vgの変化速度を制御する。

【解決手段】電圧駆動素子であるIGBT(Q11)に、誘導性負荷L11とユニポーラ型の還流ダイオードD12が接続されている。Q11のターンオフ時に、Q11のコレクタからコンデンサC11とダイオードD11及び抵抗R19を介して、ベース抵抗R12へ電流が流れ、ベース抵抗R12で電圧が発生し、PNPトランジスタQ12のベース電圧Vbは上昇する。この電圧上昇速度は、コンデンサC11とベース抵抗R12及び抵抗R19によって決まる時定数により決定され、上昇電圧はベース抵抗R12と抵抗R19で分圧される。これによりQ12のベース電圧Vbの変化速度、即ちQ11のゲート電圧Vgの変化速度を制御する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電圧駆動素子の駆動回路に係り、特に、電圧駆動素子の電圧変化率を制御するために出力電圧を駆動回路の入力側へフィードバックする駆動回路において、スイッチングノイズを抑制する駆動回路に関する。

【背景技術】

【0002】

制御電極であるゲートに印加する電圧により2つの主電極間に流れる電流を制御する電圧駆動素子として、IGBT(Insulated Gate Bipolar Transistor:絶縁ゲート型バイポーラトランジスタ)やパワーMOSFETがある。これらの電圧駆動素子の場合、ゲートに接続する抵抗値を調整することにより、スイッチング速度をチューニングし、過大なサージ電圧の発生を抑えることが多い。ただし、この手法では、IGBTやパワーMOSFETのバラツキや温度特性により、スイッチング速度も変動してしまう。そのためスイッチング速度信号を電圧駆動素子のゲートにフィードバックすることにより、電圧駆動素子のスイッチング速度を状況に応じて調整する方法が知られている。

【0003】

例えば、負荷を駆動する電圧駆動素子のゲートに、エミッタが接続され、コレクタが接地されたPNPトランジスタを備え、電圧駆動素子のターンオフ時に、電圧駆動素子のゲート電荷をPNPトランジスタを介して放電することにより、電圧駆動素子をターンオフする電圧駆動素子の駆動回路がある。この駆動回路において、コンデンサとダイオードの直列回路におけるコンデンサ側の一端を電圧駆動素子の非接地側の主電極に接続し、ダイオード側の一端をPNPトランジスタのベースに接続し、コンデンサとダイオードの接続点と接地間にプルダウン抵抗を接続し、ダイオードは電流をコンデンサからトランジスタのベース方向へ流す極性に接続した回路がある(特許文献1)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第3997905号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

近年、SiC等の化合物半導体の実用化に伴い、高耐圧電力用のショットキーバリアダイオードやヘテロジャンクションダイオード等のユニポーラ型ダイオードが開発されてきた。ユニポーラ型ダイオードは、動作中に少数キャリアが発生せず、PN接合またはPIN接合を用いたバイポーラ型ダイオードと比較して高速に電流を遮断できるので、スイッチング損失を低減することができる。

【0006】

しかしながら、上記従来の電圧駆動素子の駆動回路においては、誘導性負荷の還流ダイオードに高速のダイオードを用いた場合に、電圧駆動素子のターンオフ時には電圧上昇率(dv/dt)を抑制してサージ電圧を抑制できるものの、ターンオン時には還流ダイオードの急峻なスイッチングにより、リンギングが生じてノイズの放射により誤動作を引き起こす虞があるという問題点があった。この問題点は、特にスイッチング速度の速いユニポーラ型ダイオードを還流ダイオードとして用いた場合に顕著である。

【課題を解決するための手段】

【0007】

上記問題点を解決するために本発明は、電圧駆動素子に誘導性の負荷と還流ダイオードとが接続され、電圧駆動素子のゲートと接地間に第1のPNPトランジスタ又はPチャンネルMOSFETが接続され、電圧駆動素子のゲート電荷を第1のPNPトランジスタ又はPチャンネルMOSFETを介して放電することにより、電圧駆動素子をターンオフする電圧駆動素子の駆動回路において、電圧駆動素子の非接地側の主電極に第1のコンデンサの一端を接続し、第1のコンデンサの他端を第1のダイオードのアノードに接続し、第1のダイオードのカソードを第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートに接続し、第1のコンデンサの他端と接地間にプルダウン抵抗及び第2のダイオードを直列接続したプルダウン回路を接続し、第2のダイオードはアノード端子が接地側を向いている。

【0008】

さらに、第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートと電圧信号入力端子との間には第1の抵抗が接続され、第1の抵抗と第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートとの接続点から、第1のコンデンサの他端とプルダウン回路との接続点までの間に、第1のダイオードに直列接続される第2の抵抗を備えたことを要旨とする。

【発明の効果】

【0009】

本発明によれば、電圧駆動素子のターンオフ時には第1のコンデンサからフィードバックされる電圧のうち、第1の抵抗と第2の抵抗で分圧した電圧をゲート駆動素子に入力することで、適度に電圧駆動素子のゲート電荷放電速度を緩和することができ、電圧駆動素子の電圧上昇率(dv/dt)が抑制されることでサージ電圧を抑制できる。さらに電圧駆動素子のターンオン時においては、ユニポーラ型ダイオード等の高速素子を還流ダイオードに用いた場合でも、還流ダイオードの高速なスイッチングによる急峻な変化電流は第1のコンデンサを通って第1の抵抗と第2の抵抗の両方を流れ、第1の抵抗の抵抗値と第2の抵抗の抵抗値を合計した抵抗値でスナバ回路が形成されるので、スナバ回路としても適当な回路定数となり、リンギングを抑制することができ、電圧駆動素子の誤動作を防止することができるという効果がある。

【図面の簡単な説明】

【0010】

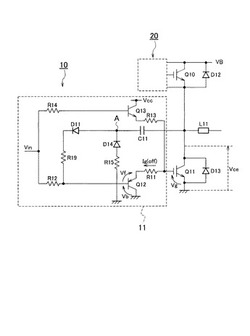

【図1】本発明に係る電圧駆動素子の駆動回路の実施例1を示す回路図である。

【図2】図1の電圧駆動素子の駆動回路を用いた三相インバータ回路の回路図である。

【図3】図1の回路において、入力信号Vinを変化させて、IGBT(Q11)のオン/オフを繰り返したときにおける各部の電圧波形を示す図である。

【図4】本発明に係る電圧駆動素子の駆動回路の実施例2を示す回路図である。

【図5】図4、図6の回路において、入力信号Vinを変化させて、IGBT(Q11)のオン/オフを繰り返したときにおける各部の波形を示す図である。

【図6】本発明に係る電圧駆動素子の駆動回路の実施例3を示す回路図である。

【図7】本発明に係る電圧駆動素子の駆動回路の実施例4を示す回路図である。

【図8】図7、図9の回路において、入力信号Vinを変化させて、IGBT(Q11)のオン/オフを繰り返したときにおける各部の波形を示す図である。

【図9】本発明に係る電圧駆動素子の駆動回路の実施例5を示す回路図である。

【図10】本発明に係る電圧駆動素子の駆動回路の実施例6を示す回路図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施形態を図面に基づいて説明する。尚、以下に説明する各実施例は、電圧駆動素子の一つであるIGBTを用いて負荷を駆動する際の駆動回路を示すが、MOS−FETの駆動回路にも本発明を適用することができるのは明らかである。IGBTの主電極は、エミッタ及びコレクタであり、MOS−FETの主電極は、ドレイン及びソースである。2つの主電極間の電流を制御する制御電極は、IGBT及びMOS−FET共にゲートである。

【実施例1】

【0012】

図1は、本発明に係る電圧駆動素子の駆動回路の実施例1である駆動回路10を用いた、三相インバータの一相分のアーム駆動回路を示す回路図である。図2は、図1の回路を用いた三相インバータ回路の回路図である。

【0013】

図2において、三相インバータは、平滑コンデンサCと、U相のアーム100と、V相のアーム110と、W相のアーム120と、三相同期モータMと、を有している。平滑コンデンサCは電源VBと接地(GND)間に接続されている。アーム100,110,120は、それぞれ同じ構成の図1に示したアームであり、3並列のアームにより三相ブリッジ回路を構成している。そして、各アームの上下のIGBTの接続点が、三相同期モータMのU相、V相、W相にそれぞれ接続されている。

【0014】

次に、図1に示した駆動回路10について説明する。図1において、電源電圧VBと接地(GND)間には、IGBT(Q10)とIGBT(Q11、電圧駆動素子)が直列接続され、それぞれに駆動回路10と駆動回路20が接続され、三相インバータの一つのアームを形成している。IGBT(Q10)のエミッタ−コレクタ間には、還流ダイオードD12が接続され、IGBT(Q11)のエミッタ−コレクタ間には、還流ダイオードD13が接続されている。

【0015】

本実施例における還流ダイオードD12,D13は、ショットキバリアダイオードや本願出願人による特許第4282972号公報に記載のヘテロジャンクションダイオード等のユニポーラ型ダイオードである。

【0016】

負荷L11は三相同期モータMの一部を回路上に書き出したものであり、負荷L11の一端は、IGBT(Q10)のエミッタとIGBT(Q11)のコレクタとの接続点に接続されている。負荷L11の他端は、三相同期モータMの図示しない中性点に接続されている。

【0017】

駆動回路10は、IGBT(Q11)のゲートを駆動するコンプリメンタリ型のエミッタフォロア回路を含むdv/dt抑制・スナバ回路11を備える。

【0018】

dv/dt抑制・スナバ回路11は、コレクタが接地されたPNPトランジスタQ12(第1のPNPトランジスタ)と、コレクタが電源電圧Vccに接続されたNPNトランジスタQ13と、ベース抵抗R12(第1の抵抗)と、ベース抵抗R14と、抵抗R19(第2の抵抗)と、エミッタ抵抗R11,R13と、コンデンサC11(第1のコンデンサ)と、ダイオードD11(第1のダイオード)と、ダイオードD14(第2のダイオード)と、プルダウン抵抗R15とを備える。

【0019】

入力信号Vin(入力信号端子、入力信号電圧)は、ベース抵抗R12,R14を介して、それぞれPNPトランジスタQ12のベースとNPNトランジスタQ13のベースに接続されている。PNPトランジスタQ12のエミッタとNPNトランジスタQ13のエミッタとは、それぞれエミッタ抵抗R11,R13を介して、IGBT(Q11)のゲートに接続されている。また、入力信号Vinとしては、図示しない外部回路により、電源電圧VccをHレベル、GND電位をLレベルとしたPWM信号が入力されている。

【0020】

コンデンサC11の一端は、IGBT(Q10)のエミッタとIGBT(Q11)のコレクタとの接続点に接続され、コンデンサC11の他端は、ダイオードD11のアノードに接続されている。コンデンサC11とダイオードD11のアノードとの接続点を点Aと呼ぶ。ダイオードD11のカソードは、抵抗R19の一端に接続されている。抵抗R19の他端はPNPトランジスタQ12のベースに接続されている。つまり電流はコンデンサC11側からPNPトランジスタQ12のベース側へ流れる方向に規制される。さらに点Aには、ダイオードD14のカソードが接続され、ダイオードD14のアノードはプルダウン抵抗R15を介して接地されている。

【0021】

次に、図1に示した駆動回路10の動作を、図3を用いて説明する。図3は入力信号Vinを変化させてIGBT(Q11)のオン/オフを繰り返したときにおける各部の電圧波形を示す図である。図3(a)は入力信号Vin、(b)はIGBT(Q11)のコレクタ−エミッタ間電圧Vce、(c)はPNPトランジスタQ12のベース電圧Vb、(d)はA点の電圧である。

【0022】

入力信号VinをLからHへ変化させると、若干の遅延の後、IGBT(Q11)はターンオン動作に入る(時刻t11)。この際、IGBT(Q11)のコレクタ−エミッタ間電圧Vceは低下していく。すなわち、負の電圧変化率(dv/dt)が発生する(時刻t11〜t12)。この負のdv/dtにより、コンデンサC11にはA点からIGBT(Q11)のコレクタに向かって電流が流れる。この電流は、プルダウン抵抗R15とダイオードD14を介してGNDから供給されるため、A点の電位はプルダウン抵抗R15の電圧降下分だけ下がり、負の電位となるが、ダイオードD11が存在するため、PNPトランジスタQ12のベースに負電圧が印加されることはない。

【0023】

したがって、ベース抵抗R12やコンデンサC11の値にかかわらず、PNPトランジスタQ12が破壊されるおそれはない。また、ターンオン終了(時刻t12)後、A点の電位はプルダウン抵抗R15とコンデンサC11によって決まる時定数で初期状態である0V近傍へ復帰して行く。プルダウン抵抗R15の値としては、速やかに0V近傍へ復帰させるため、時定数が小さくなるような値が選ばれる。

【0024】

次に、入力信号VinをHからLへ変化させると、若干の遅延の後、IGBT(Q11)はターンオフ動作に入る(時刻t13)。この際、IGBT(Q11)のコレクタ−エミッタ間電圧Vceは上昇していく。すなわち、正の電圧変化率(dv/dt)が発生する。この正のdv/dtにより、コンデンサC11には、IGBT(Q11)のコレクタからA点に向かって電流が流れる。この電流はA点からダイオードD11および抵抗R19を介して、PNPトランジスタQ12のベース抵抗R12へ流れ込むため、ベース抵抗R12で電圧が発生し、PNPトランジスタQ12のベース電圧Vbは上昇する。この電圧上昇速度は、コンデンサC11とベース抵抗R12によって決まる時定数により決定され、上昇電圧はベース抵抗R12と抵抗R19で分圧される。

【0025】

IGBT(Q11)のVceに発生するdv/dtは、IGBT(Q11)のターンオフ速度によって決まる。IGBT(Q11)のターンオフ速度は、ゲート電荷の放電速度すなわちゲート電流Ig(off)の大きさで調整可能であり、ゲート電流Ig(off)は、ゲート電圧をVgとし、PNPトランジスタQ12のベース電圧をVbとし、PNPトランジスタQ12のベースに対するエミッタ電圧をVfとしたときに、式(1)で表すことができる。

Ig(off)=(Vg−Vb−Vf)/R11 …(1)

【0026】

したがってベース電圧Vbの上昇によって、ゲート電流Ig(off)が減少し、IGBT(Q11)のゲート電荷放電速度が緩和されることになる。この負帰還作用により、コンデンサC11、ベース抵抗R12、ゲート抵抗R11によって決まる所定のdv/dt(101)に一致するように、IGBT(Q11)のターンオフ動作が制御され、過大なサージ電圧の発生を抑えることができる。サージ電圧の消滅時(時刻t14〜t15)には、ターンオン時同様、負のdv/dtが発生するが、前述のターンオン時と同じ理由で、PNPトランジスタQ12のベースに負の電圧が印加されることはない。

【0027】

次に回路定数の設定方法を説明する。IGBT(Q11)のターンオフ時の電圧上昇速度dv/dt(101)は、PNPトランジスタQ12のベース−エミッタ間電圧Vfの電圧変化にともなって変化する。PNPトランジスタQ12のVfは入力信号Vinの電圧に対して、ベース抵抗R12における降下電圧の分だけ減少する。すなわち、ベース抵抗R12における降下電圧が大きいとPNPトランジスタQ12のVfは減少することになり、それにともなってIGBT(Q11)のターンオフ時の電圧上昇速度dv/dtが減少することになる。

【0028】

ここで、IGBT(Q11)のターンオフ時には、IGBT(Q11)のコレクタからコンデンサC11を通ってA点に流れる電流が、ダイオードD11、抵抗R19、ベース抵抗R12を介して、Lレベルとなった入力信号Vinの端子へ流れる。この電流により抵抗R19とベース抵抗R12において電圧降下を生じ、その電圧をベース抵抗R12と抵抗R19で分圧した電圧がPNPトランジスタQ12のベース電圧となる。例えば、コンデンサC11の容量として700pFを用いた場合には、分圧比を1/20程度にすればよく、その際にはベース抵抗R12の値として1Ω、抵抗R19の値として19Ωが適した値となる。

【0029】

一方、還流ダイオードD13に還流電流が流れている間にIGBT(Q10)がターンオンする際には、IGBT(Q11)はオフ状態で、IGBT(Q11)のゲート駆動回路10の入力信号VinはGND状態になっており、還流ダイオードD13は遮断するタイミングとなる。還流ダイオードD13はユニポーラ型ダイオードであるため、高速な電流遮断特性となり、通常ではリンギングが発生してしまう。しかし、本回路においては、コンデンサC11とD11と抵抗R19とベース抵抗R12との直列回路が、IGBT(Q11)のコレクタとLレベルの入力信号Vinとの間に接続されているので、この直列回路がスナバ回路として働き、リンギングは抑制される。

【0030】

その際の回路定数として、例えばコンデンサC11の容量として700pFが用いられ、ベース抵抗R12の値として1Ωが用いられ、抵抗R19の値として19Ωが用いられる。この回路定数は次のように求まる。一般的に、CRスナバ回路のコンデンサCはIGBTモジュールの寄生容量と同程度にし、抵抗RはCRスナバ回路の時定数の逆数(1/(2πCR))がIGBTモジュールのリンギング周波数fと同程度になるように設計する(f=1/(2πCR))。例えば、IGBTモジュールの寄生容量が700pFで、リンギング周波数fが11MHzだとすると、CRスナバ回路のコンデンサCは700pFとなり、抵抗Rは、次の式(2)により、約20Ω(正確な計算値は、20.67Ω)と求まる。実際には、計算値の周辺の値を用いて実験的に損失やリンギング抑制効果を検証しながら最適値を求めてもよい。

R=1/(2πCf)≒20 …(2)

【0031】

このように、IGBT(Q11)のターンオフ時のdv/dtを適度に抑制するための抵抗Rの大きさは1Ωであるが、この値では、IGBT(Q10)のターンオン時に発生するリンギングを抑制するためにはスナバ抵抗の値として小さすぎる。そこで、本実施の形態では、回路上でdv/dtを抑制に影響がある部分とdv/dt抑制に影響しない部分があることに着目し、抵抗をベース抵抗R12と抵抗R19に分割して、合計を20Ωにしつつ、dv/dt抑制に影響がある部分のベース抵抗R12は1Ωにして、dv/dt抑制とリンギング抑制を両立している。

【0032】

なお、IGBT(Q11)のターンオフ時に、抵抗R15にはダイオードD14により電流が流れないため、CRスナバ回路に適した20Ω周辺の値にすればよい。

【0033】

本実施例の比較例として、外付けCRスナバ回路を接続する場合、例えばdv/dt抑制回路のコンデンサC11の容量を700pFとすると、外付けスナバ回路に必要なコンデンサ容量は、dv/dt抑制回路の容量700pFとIGBTモジュールの寄生容量700pFを合計した1400pFになる。スナバ回路の損失はコンデンサ容量に比例することから、外付けCRスナバ回路を接続する比較例の場合は、本発明の駆動回路を用いた場合の2倍の損失が発生してしまう。

【0034】

駆動回路の基板上にスナバ回路を設置する場合、スナバの損失は抵抗のサイズ低減の観点で重要な意味を持つ。抵抗のサイズは許容損失で決まり、許容損失が大きい抵抗はサイズも大きく、はんだ接合の信頼性上、好ましくない。本実施例はスナバ回路で発生する損失を減らせるため、抵抗のサイズを小さくすることができるので、はんだ接合の信頼性を向上させることができ、また駆動回路基板のサイズを小さくすることができる。

【0035】

以上説明したように本実施例によれば、電圧駆動素子のターンオフ時にはコンデンサC11からフィードバックされる電圧のうち、ベース抵抗R12と抵抗R19で分圧した一部の電圧をゲート駆動素子に入力することで、適度に電圧駆動素子のゲート電荷放電速度を緩和することができ、電圧駆動素子のdv/dtが抑制されることでサージ電圧を抑制することができるという効果がある。さらに電圧駆動素子のターンオン時においては、ユニポーラ型ダイオードを還流ダイオードを還流ダイオードD13に用いた場合でも、ダイオードのハードなスイッチングによる急峻な変化電流はコンデンサC11を通ってベース抵抗R12と抵抗R19の両方を流れ、合算した抵抗値でスナバ回路が形成されるので、スナバ回路としても適当な回路定数となり、リンギングを抑制することができ、電圧駆動素子の誤動作を防止することができるという効果がある。

【0036】

また本実施例によれば、外付けCRスナバ回路よりもスナバ回路の損失を低減して、駆動回路の信頼性を向上させることができるという効果がある。

【0037】

なお、本実施例において、Q13がNPNトランジスタ、Q12がPNPトランジスタである例を示したが、バイポーラ型トランジスタだけでなく、Q13がNチャンネルMOSFET、Q12がPチャンネルMOSFETであってもよい。その場合には、それぞれ、ベースがゲート、コレクタがドレイン、エミッタがソースに対応する。

【0038】

なお、本実施例では還流ダイオードD12、およびD13にユニポーラ型ダイオードを用いた場合を説明したが、ユニポーラ型ダイオードに限らず、ユニポーラ型ダイオードと同様に従来の駆動回路では電流遮断時にリンギングを生じてしまうような素子であってもよい。例えば、ユニポーラ型ダイオードと同様にハードな(急峻な)リカバリ特性を持つバイポーラ型ダイオードであってもよい。

【実施例2】

【0039】

図4は、本発明に係る電圧駆動素子の駆動回路の実施例2の回路図である。実施例1の駆動回路10に対する実施例2の駆動回路15の変更点は、図1のdv/dt抑制・スナバ回路11において抵抗R19の値を極力小さくして(実際には0Ω)図4のdv/dt抑制・スナバ回路21としたことと、スナバ切り替え回路12を追加した点にある。その他の構成は、実施例1と同様であるので、同じ構成要素には同じ符号を付与している。

【0040】

スナバ切り替え回路12は、PNPトランジスタQ15(第2のPNPトランジスタ)と、NPNトランジスタQ14(スイッチ素子、第1のNPNトランジスタ)と、コンデンサC12(第2のコンデンサ)と、切り替え用抵抗R16(第3の抵抗)と,抵抗R17(第5の抵抗)と、抵抗R18(第4の抵抗)とを備える。PNPトランジスタQ15のエミッタは電源Vccに接続されている。PNPトランジスタQ15のベースは抵抗R17を介して電源Vccに接続されており、また、コンデンサC12を介して入力信号Vinに接続されている。

【0041】

また、PNPトランジスタQ12のベースは抵抗R16を介して、NPNトランジスタQ14のコレクタに接続されている。NPNトランジスタQ14のエミッタは接地されている。NPNトランジスタQ14のベースは抵抗R18を介して接地されており、また、PNPトランジスタQ15のコレクタに接続されている。

【0042】

スナバ切り替え回路12は、入力信号VinがHからLへ切り替わる際、即ちIGBT(Q11)のターンオフ時に、NPNトランジスタQ14をオンさせて、切り替え抵抗R16を抵抗R12に対して並列接続させる回路である。入力信号VinがLからHへ切り替わるIGBT(Q11)のターンオン時には、NPNトランジスタQ14はオフであり、切り替え抵抗R16は抵抗R12に対して切り離されている。

【0043】

次に、図4に示した駆動回路15の動作を、図3を用いて説明する。図3は入力信号Vinを変化させて、IGBT(Q11)およびIGBT(Q10)のオン/オフを繰り返したときにおける各部の電圧波形を示す図である。図3(a)は入力信号Vin、(b)はIGBT(Q11)のコレクタ−エミッタ間電圧Vce、(c)はPNPトランジスタQ12のベース電圧Vb、(d)はA点の電圧である。

【0044】

入力信号VinをLからHへ変化させると、若干の遅延の後、IGBT(Q11)はターンオン動作に入る(時刻t11)。この際、IGBT(Q11)のコレクタ−エミッタ間電圧Vceは低下していく。すなわち、負のdv/dtが発生する(時刻t11〜t12)。この負のdv/dtにより、コンデンサC11にはA点からIGBT(Q11)のコレクタに向かって電流が流れる。この電流は、プルダウン抵抗R15とダイオードD14を介してGNDから供給されるため、A点の電位はプルダウン抵抗R15の電圧降下分だけ下がり、負の電位となるが、ダイオードD11が存在するため、PNPトランジスタQ12のベースに負電圧が印加されることはない。

【0045】

したがって、ベース抵抗R12やコンデンサC11の値にかかわらず、PNPトランジスタQ12が破壊されるおそれはない。また、ターンオン終了(時刻t12)後、A点の電位はプルダウン抵抗R15とコンデンサC11によって決まる時定数で初期状態である0V近傍へ復帰して行く。プルダウン抵抗R15の値としては、速やかに0V近傍へ復帰させるため、時定数が小さくなるような値が選ばれる。

【0046】

次に、入力信号VinをHからLへ変化させると、若干の遅延の後、IGBT(Q11)はターンオフ動作に入る(時刻t13)。この際、IGBT(Q11)のコレクタ−エミッタ間電圧Vceは上昇していく。すなわち、正のdv/dtが発生する。この正のdv/dtにより、コンデンサC11には、IGBT(Q11)のコレクタからA点に向かって電流が流れる。この電流はA点からダイオードD11を介して、PNPトランジスタQ12のベース抵抗R12および切り替え用抵抗R16へ流れ込むため、PNPトランジスタQ12のベース電圧Vbは上昇する。この電圧上昇速度は、コンデンサC11とベース抵抗R12によって決まる時定数により決定される。

【0047】

IGBT(Q11)のVceに発生するdv/dtは、IGBT(Q11)のターンオフ速度によって決まる。IGBT(Q11)のターンオフ速度は、ゲート電荷の放電速度すなわちゲート電流Ig(off)の大きさで調整可能であり、ゲート電流Ig(off)は、ゲート電圧をVgとし、PNPトランジスタQ12のベース電圧をVbとし、PNPトランジスタQ12のベースに対するエミッタ電圧をVfとしたときに、式(3)で表すことができる。

Ig(off)=(Vg−Vb−Vf)/R11 …(3)

【0048】

したがってベース電圧Vbの上昇によって、ゲート電流Ig(off)が減少し、IGBT(Q11)のゲート電荷放電速度が緩和されることになる。この負帰還作用により、コンデンサC11、ベース抵抗R12、ゲート抵抗R11によって決まる所定のdv/dt(101)に一致するように、IGBT(Q11)のターンオフ動作が制御され、過大なサージ電圧の発生を抑えることができる。サージ電圧の消滅時(時刻t14〜t15)には、ターンオン時同様、負のdv/dtが発生するが、前述のターンオン時と同じ理由で、PNPトランジスタQ12のベースに負の電圧が印加されることはない。

【0049】

次に、スナバ切り替え回路12の動作を図5を用いて説明する。図5(a)は入力信号Vin、(b)はIGBT(Q11)のコレクタ−エミッタ間電圧Vce、(c)はダイオードD12の電圧Vdi、(d)はB点の電圧、(e)はPNPトランジスタQ15のコレクタ電流I11、(f)はCR時定数である。

【0050】

IGBT(Q11)のターンオフ時の電圧上昇速度dv/dt(101)は、dv/dt抑制・スナバ回路21の負帰還量を決めるコンデンサと抵抗による時定数に依存している。適した電圧上昇速度dv/dtを得るために、例えば、コンデンサ容量として700pFが用いられ、抵抗値として1Ωが用いられる。

【0051】

一方、IGBT(Q11)がターンオンするタイミングは、ユニポーラ型の還流ダイオードD12は遮断するタイミングとなる。電流が遮断する際に、上記の時定数をそのまま用いると、図5(c)のVdiに示すようなリンギングを生じてしまう。このリンギングは時定数をCRスナバとしての動作に適した値にすることで抑制することができる。その時の値は、おおよそリンギング周波数をfとすると、おおよそf=1/(2πCR)を満たし、例えば、コンデンサ容量として700pFが用いられ、抵抗値として20Ωが用いられる。

【0052】

このように、IGBT(Q11)のターンオフ時のIGBT(Q11)の電圧上昇速度dv/dt(101)を適した値にするCR時定数と、IGBT(Q11)のターンオン時の還流ダイオードD12に発生するリンギング抑制に適するCR時定数は異なる。

【0053】

本実施例のスナバ切り替え回路12によれば、IGBT(Q11)がターンオフする際には、NPNトランジスタQ14がオンすることにより、CR時定数はコンデンサC11と、ベース抵抗R12と切り替え用抵抗R16との合成抵抗によって決まり、IGBT(Q11)がターンオンする際には、NPNトランジスタQ14がオフであることにより、CR時定数はコンデンサC11と、ベース抵抗R12のみによって決まる。

【0054】

以下、スナバ切り替え回路12の動作を図5を参照して説明する。入力信号VinをHからLへ変化させると(時刻t16)、抵抗R17とコンデンサC12の接続点Bの電圧は図5(d)に示すように、Vccから減少する。これは、抵抗R17とコンデンサC12が微分回路を形成しているからであり、その減少している時間は抵抗R17とコンデンサC12による時定数により決まる。このVccから減少した電圧は、PNPトランジスタQ15のベース電圧Vb15になっており、Vb15が約0.6Vよりも大きいときには、PNPトランジスタQ15は導通状態になる。そうすると、PNPトランジスタQ15のコレクタから抵抗R18に電流が流れる。この抵抗R18に流れる電流I11の波形を図5(e)に示した。抵抗R18に電流が流れることで電圧降下が生じる。この電圧は切り替え用NPNトランジスタQ14のベース電圧Vb14になっている。

【0055】

すなわち、入力信号VinをHからLへ変化させる時(IGBT(Q11)のターンオフ時)から一定の時間は、切り替え用NPNトランジスタQ14が導通状態になり、回路の時定数はコンデンサC11と、ベース抵抗R12および切り替え用抵抗R16の合成抵抗によって決まる。

【0056】

例えば、コンデンサC11を700pF、ベース抵抗R12を20Ω、プルダウン抵抗R15を20Ω、切り替え用抵抗R16を1Ωにすると、時定数はおおよそ700pFと1Ωによって決まる値になる。なお、このタイミングにおいては、プルダウン抵抗R15に直列にダイオードD14が直列に接続されているために、プルダウン抵抗R15には電流は流れないため、時定数への影響はない。

【0057】

一方、入力信号VinをLからHへ変化させた時(時刻t17)は、抵抗R17とコンデンサC12の接続点Bの電圧は図5(d)に示すように、電源電圧Vccよりも電圧が上昇する。そのため、PNPトランジスタQ15は導通状態にならないため、切り替え用NPNトランジスタQ14も導通状態にならない。そのため、切り替え用抵抗R16に電流が流れることはない。結果的に、入力信号VinをLからHへ変化させる時(IGBT(Q11)のターンオン時)は、回路の時定数はコンデンサC11とベース抵抗R12のみによって決まる。例えば、上記のようにコンデンサC11を700pF、ベース抵抗R12を20Ω、プルダウン抵抗R15を20Ωとすると、時定数は700pFと20Ωによって決まる値となる。

【0058】

時定数の変化を図5(f)に示す。このように、IGBT(Q11)のターンオフ時とターンオン時で時定数を変化させることができ、dv/dt抑制・スナバ回路21の負帰還量とスナバ時定数をそれぞれに適した値にすることができる。

【0059】

本実施例の駆動回路10を用いた場合、例えば下アームのスイッチング素子(IGBT(Q11)およびダイオードD13)の寄生容量を700pFとすると、リンギング抑制のスナバには同程度の容量を必要とすることから、コンデンサC11の値として、700pF程度にすることができる。この容量は外付けスナバを付ける場合と比較して、少ない値である。スナバ回路の損失はコンデンサ容量に比例することから、スナバ回路で発生する損失を減らすことができる。

【0060】

本実施例の比較例として、外付けCRスナバ回路を接続する場合、例えばdv/dt抑制回路の寄生容量を700pFとすると、外付けスナバ回路に必要なコンデンサ容量はdv/dt抑制回路の寄生容量700pFとスイッチング素子の寄生容量700pFを合計した1400pFになる。スナバ回路の損失はコンデンサ容量に比例することから、外付けCRスナバ回路を接続する比較例の場合は、本発明の駆動回路を用いた場合の2倍の損失が発生する。

【0061】

駆動回路の基板上にスナバ回路を設置する場合、スナバの損失は抵抗のサイズ低減の観点で重要な意味を持つ。抵抗のサイズは許容損失で決まり、許容損失が大きい抵抗はサイズも大きく、はんだ接合の信頼性上、好ましくない。本実施例はスナバ回路で発生する損失を減らせるため、抵抗のサイズを小さくでき、はんだ接合の信頼性を向上させることができる。

【0062】

以上説明したように本実施例によれば、電圧駆動素子のターンオン時とターンオフ時でスナバ時定数を決定する抵抗の値を変化させることで、電圧駆動素子のゲート電荷放電速度を緩和することができ、還流ダイオードにユニポーラ型ダイオードを用いた場合でも、サージ電圧やリンギングを抑制することができ、電圧駆動素子の誤動作を防止することができるという効果がある。

【0063】

また本実施例によれば、外付けCRスナバ回路よりも損失を低減して、駆動回路の信頼性を向上させることができるという効果がある。

【0064】

なお、本実施例において、Q13およびQ14がNPNトランジスタ、Q12およびQ15がPNPトランジスタである例を示したが、バイポーラ型トランジスタだけでなく、Q13およびQ14がNチャンネルMOSFET、Q12およびQ15がPチャンネルMOSFETであってもよい。その場合には、それぞれ、ベースがゲート、コレクタがドレイン、エミッタがソースに対応する。

【実施例3】

【0065】

図6は、本発明に係る電圧駆動素子の駆動回路の実施例3の回路図である。実施例2に対して実施例3の主要な変更点は、時定数を構成する抵抗として、ベース抵抗R32(第1の抵抗)と切り替え抵抗R36(第6の抵抗)の直列回路を用いていることと、IGBT(Q11)がターンオンする際に、切り替え用NPNトランジスタQ14(スイッチ素子、第2のNPNトランジスタ)を導通させて、切り替え抵抗R36をバイパスさせることにより、時定数を変更していることである。

【0066】

本実施例の駆動回路30は、dv/dt抑制・スナバ回路31と、スナバ切り替え回路32とを備える。実施例2のベース抵抗R12に相当するものが、実施例3では、ベース抵抗R32と切り替え用抵抗R36である。

【0067】

スナバ切り替え回路32において、切り替え用抵抗R36をベース抵抗R32に直列に、入力信号Vinとの間に設け、切り替え用NPNトランジスタQ14(第2のNPNトランジスタ)がエミッタを入力信号Vinに、コレクタを切り替え用抵抗R36とベース抵抗R32との接続点に接続している点と、抵抗R38(第7の抵抗)をPNPトランジスタQ15(第3のPNPトランジスタ)のコレクタと入力信号Vinとの間に接続している。抵抗R32,R36,R38と、切り替え用NPNトランジスタQ14以外の構成は、図4に示した実施例2と同様であるので、同じ構成要素には同じ符号を付与して、重複する説明を省略する。

【0068】

動作においては、図5に示すように、入力信号VinをHからLに変化させた時(時刻t16)にPNPトランジスタQ15にベース電圧Vb15が印加される。PNPトランジスタQ15のコレクタ電流I11が流れるタイミングは、実施例2と同じである。異なる点は、コレクタ電流I11は抵抗R38に流れて、切り替え用NPNトランジスタQ14のベース電圧を発生して導通状態にし、切り替え用抵抗R36をバイパスするようになる点である。

【0069】

すなわち、入力信号VinをHからLへ変化させるとき(IGBT(Q11)のターンオフ時)から一定の時間は、切り替え用NPNトランジスタQ14が導通状態になり切り替え用抵抗R36をバイパスするので、回路の時定数はコンデンサC11と、ベース抵抗R32のみによって決まる。例えばコンデンサC11を700pF、ベース抵抗R32を1Ω、プルダウン抵抗R15を20Ω、切り替え用抵抗R36を19Ωとすると、時定数は700pFと1Ωによって決まる値になる。なお、このタイミングにおいては、プルダウン抵抗R15に直列にダイオードD14が直列に接続されているために、プルダウン抵抗R15には電流は流れないため、時定数への影響はない。

【0070】

一方、入力信号VinをLからHへ変化させた時(時刻t17)は、実施例2と同様に、PNPトランジスタQ15は導通状態にならないため、切り替え用NPNトランジスタQ14も導通状態にならない。そのため、切り替え用抵抗R36はバイパスされない。結果的に、入力信号VinをLからHへ変化させる時(IGBT(Q11)のターンオン時)は、回路の時定数はコンデンサC11と、ベース抵抗R32と切り替え用抵抗R36の直列抵抗によって決まる。例えば、上記のようにコンデンサC11を700pF、ベース抵抗R32を1Ω、プルダウン抵抗R15を20Ω、切り替え用抵抗R36を19Ωとすると、時定数は700pFと(1+19)Ωによって決まる値となる。

【0071】

時定数の変化は実施例2と同様に図5に示す。このように、IGBT(Q31)のターンオフ時とターンオン時で時定数を変化させることができ、dv/dt抑制・スナバ回路31の負帰還量とスナバ時定数をそれぞれ適した値にすることができる。

【0072】

以上説明したように本実施例によれば、電圧駆動素子のターンオン時とターンオフ時でスナバ時定数を決定する抵抗の値を変化させることで、電圧駆動素子のゲート電荷放電速度を緩和することができ、還流ダイオードにユニポーラ型ダイオードを用いた場合でも、サージ電圧やリンギングを抑制することができ、電圧駆動素子の誤動作を防止することができるという効果がある。

【0073】

また本実施例によれば、外付けCRスナバ回路よりも損失を低減して、駆動回路の信頼性を向上させることができるという効果がある。

【0074】

なお、本実施例において、Q13およびQ14がNPNトランジスタ、Q12およびQ15がPNPトランジスタである例を示したが、バイポーラ型トランジスタだけでなく、Q13およびQ14がNチャンネルMOSFET、Q12およびQ15がPチャンネルMOSFETであってもよい。その場合には、それぞれ、ベースがゲート、コレクタがドレイン、エミッタがソースに対応する。

【実施例4】

【0075】

図7は、本発明に係る電圧駆動素子の駆動回路の実施例4の回路図である。実施例4は実施例2と異なり、ターンオフ時とターンオン時で抵抗を切り替えるのではなく、コンデンサを切り替える。本実施例の駆動回路50は、dv/dt抑制・スナバ回路51と、スナバ切り替え回路52とを備える。

【0076】

本実施例の特徴は、切り替え用コンデンサC56(第4のコンデンサ)と切り替え用PNPトランジスタQ54(第4のPNPトランジスタ)のエミッタ−コレクタ間を直列に接続し、この直列回路と並列に、コンデンサC51(第1のコンデンサ)を設けている。そして、切り替え用PNPトランジスタQ54のエミッタ−コレクタ間をオン/オフすることにより時定数を変更している点である。

【0077】

下記に構成の違いについて説明する。実施例2と異なる点は以下の6点である。スナバ切り替え回路52において、切り替え用コンデンサC56の一端がコンデンサC51とダイオードD11の接続点に接続されている点。切り替え用コンデンサC56の他端が切り替え用PNPトランジスタQ54のコレクタに接続されている点。切り替え用PNPトランジスタQ54のエミッタがIGBT(Q11)のコレクタに接続されている点。切り替え用PNPトランジスタQ54のベースが抵抗R58(第9の抵抗)を介してIGBT(Q11)のコレクタおよび、NPNトランジスタQ55(第3のNPNトランジスタ)のコレクタに接続されている点。NPNトランジスタQ55のエミッタが接地されている点。NPNトランジスタQ55のベースが抵抗R57(第10の抵抗)を介して接地されており、コンデンサC12(第5のコンデンサ)を介して入力信号Vinに接続されている点である。その他の構成は、図4に示した実施例2と同様であるので、同じ構成要素には同じ符号を付与して、重複する説明を省略する。

【0078】

次に、スナバ切り替え回路52の動作を図8を用いて説明する。IGBT(Q11)のターンオフ時の電圧上昇速度dv/dt(101)と、dv/dt抑制・スナバ回路51の負帰還量は、コンデンサと抵抗により決まる時定数に依存している。適した電圧上昇速度dv/dtを得るために、例えば、コンデンサ容量として35pFが用いられ、抵抗値として20Ωが用いられる。

【0079】

一方、IGBT(Q11)がターンオンするタイミングは、ユニポーラ型の還流ダイオードD12は遮断するタイミングとなる。電流が遮断する際に、上記の時定数をそのまま用いると、図8(c)のVdiに示すようなリンギングを生じてしまう。このリンギングは時定数をCRスナバとしての動作に適した値にすることで抑制することができる。その時の値はおおよそリンギング周波数をfとすると、おおよそf=1/(2πCR)を満たし、例えば、コンデンサ容量として700pFが用いられ、抵抗値として20Ωが用いられる。

【0080】

このように、IGBT(Q11)のターンオフ時のIGBT(Q11)の電圧上昇速度dv/dt(101)を適した値にするCR時定数と、IGBT(Q11)のターンオン時の還流ダイオードD12に発生するリンギング抑制に適するCR時定数は異なる。

【0081】

本実施例のスナバ切り替え回路52は、IGBT(Q11)がターンオフする際には、CR時定数はコンデンサC51とコンデンサC56の並列容量、ベース抵抗R12によって決まり、IGBT(Q11)がターンオンする際にはCR時定数はコンデンサC51と、ベース抵抗R52のみによって決まるようにする回路である。

【0082】

スナバ切り替え回路52の動作を示す図8において、図8(a)は入力信号Vin、(b)はIGBT(Q11)のコレクタ−エミッタ間電圧Vce、(c)はダイオードD12の電圧Vdi、(d)はC点の電圧、(e)はNPNトランジスタQ55のコレクタ電流I51、(f)はCR時定数である。

【0083】

入力信号VinをLからHへ変化させると(時刻t18)、抵抗R57とコンデンサC抵抗R57とコンデンサC52の接続点Cの電圧は、図8(d)に示すように、GNDから上昇する。これは、抵抗R57とコンデンサC52が微分回路を形成しているからであり、その上昇している時間は抵抗R57とコンデンサC52による時定数により決まる。このGNDから上昇した電圧は、NPNトランジスタQ55のベース電圧Vb55になっており、Vb55が約0.6Vよりも大きいときには、NPNトランジスタQ55は導通状態になる。そうすると、NPNトランジスタQ55のコレクタに接続された抵抗R58に電流が流れる。この抵抗R58に流れる電流I51の波形を図8(e)に示した。

【0084】

抵抗R58に電流が流れることで電圧降下が生じる。この電圧は切り替え用PNPトランジスタQ54のベース電圧Vb54になっている。すなわち、入力信号VinをLからHへ変化させる時(IGBT(Q11)のターンオン時)から一定の時間は、切り替え用PNPトランジスタQ54が導通状態になり、回路の時定数はコンデンサC51と切り替え用コンデンサC56との並列容量と、ベース抵抗R12によって決まる。例えば、コンデンサC51を35pF、切り替え用コンデンサC56を665pF、プルダウン抵抗R15を20Ω、ベース抵抗R12を20Ωとすると、時定数は(35+665)pFと20Ωによって決まる値になる。

【0085】

一方、入力信号VinをHからLへ変化させた時(時刻t19)は、抵抗R57とコンデンサC52の接続点Cの電圧は図8(d)に示すように、GNDよりも電圧が減少する。そのため、NPNトランジスタQ55は導通状態にならないため、切り替え用PNPトランジスタQ54も導通状態にならない。そのため、切り替え用コンデンサC56に電流が流れることはない。結果的に、入力信号VinをHからLへ変化させるとき(IGBT(Q11)のターンオフ時)は、回路の時定数はコンデンサC51とベース抵抗R12のみによって決まる。例えば、上記のようにコンデンサC51を35pF、プルダウン抵抗R15を20Ω、ベース抵抗R20Ωとすると、時定数は35pFと20Ωによって決まる値となる。

【0086】

時定数の変化を図8(f)に示す。このように、IGBT(Q11)のターンオフ時とターンオン時で時定数を変化させることができ、dv/dt抑制・スナバ回路51の負帰還量とスナバ時定数をそれぞれに適した値にすることができる。

【0087】

なお本実施例の変形例として、コンデンサを変化させるのと同時に、PNPトランジスタQ12のベース抵抗を実施例2、実施例3のように変化させて、dv/dt抑制・スナバ回路51の負帰還量とスナバ時定数をそれぞれ適した値になるように選んでもよい。

【0088】

以上説明したように本実施例によれば、電圧駆動素子のターンオン時とターンオフ時でスナバ時定数を決定するコンデンサの値を変化させることで、電圧駆動素子のゲート電荷放電速度を緩和することができ、還流ダイオードにユニポーラ型ダイオードを用いた場合でも、サージ電圧やリンギングを抑制することができ、電圧駆動素子の誤動作を防止することができるという効果がある。

【0089】

また本実施例によれば、外付けCRスナバ回路よりも損失を低減して、駆動回路の信頼性を向上させることができるという効果がある。

【0090】

さらに、実施例4においては、電圧駆動素子のターンオフ時の駆動回路50の寄生容量を減らすことができるため、さらに損失を低減することができる。

【0091】

なお、本実施例において、Q13およびQ55がNPNトランジスタ、Q12およびQ54がPNPトランジスタである例を示したが、バイポーラ型トランジスタだけでなく、Q13およびQ55がNチャンネルMOSFET、Q12およびQ54がPチャンネルMOSFETであってもよい。その場合には、それぞれ、ベースがゲート、コレクタがドレイン、エミッタがソースに対応する。

【実施例5】

【0092】

図9は、本発明に係る電圧駆動素子の駆動回路の実施例5の回路図である。本実施例の駆動回路70は、dv/dt抑制・スナバ回路71と、スナバ切り替え回路72とを備える。本実施例の特徴は、コンデンサC71(第1のコンデンサ)と切り替え用コンデンサC76(第6のコンデンサ)とを直列接続し、切り替え用コンデンサC76と並列に接続された切り替え用PNPトランジスタQ54(第5のPNPトランジスタ)のエミッタ−コレクタ間をオン/オフすることにより時定数を変更している点である。

【0093】

実施例4と異なる点は、スナバ切り替え回路72において、切り替え用コンデンサC76がコンデンサC71に直列に、IGBT(Q11)のコレクタとの間に入っている点と、切り替え用PNPトランジスタQ54のコレクタを切り替え用コンデンサC76とコンデンサC71の接続点に接続している点である。その他の構成は、図7に示した実施例4と同様であるので、同じ構成要素には同じ符号を付与して、重複する説明を省略する。

【0094】

動作においては、図8に示すように、入力信号VinをLからHに変化させた時(時刻t18)にNPNトランジスタQ55(第4のNPNトランジスタ)にベース電圧Vb55が印加される。NPNトランジスタQ55のコレクタ電流I51が流れるタイミングは、実施例4と同じである。異なる点は、コレクタ電流I51は抵抗58に流れて、切り替え用PNPトランジスタQ54のベース電圧を発生して切り替え用PNPトランジスタQ54を導通状態にし、切り替え用コンデンサC76をバイパスするようになる点である。すなわち、入力信号VinをLからHへ変化させる時(IGBT(Q11)のターンオン時)から一定の時間は、切り替え用PNPトランジスタQ54が導通状態になり切り替え用コンデンサC76をバイパスするので、回路の時定数はコンデンサC71とベース抵抗R12のみによって決まる。例えばコンデンサC71を700pF、切り替え用コンデンサC76を35pF、プルダウン抵抗R15を20Ω、ベース抵抗R12を20Ωとすると、時定数は700pFと20Ωによって決まる値になる。

【0095】

一方、入力信号をHからLに変化させたとき(時刻t19)は、実施例4と同様に、NPNトランジスタQ55は導通状態にならないため、切り替え用PNPトランジスタQ54も導通状態にならない。そのため、切り替え用コンデンサC76はバイパスされない。結果的に、入力信号VinをHからLへ変化させる時(IGBT(Q11)のターンオフ時)は、回路の時定数はコンデンサC71と切り替えコンデンサC76との直列容量と、ベース抵抗R12によって決まる。例えば、上記のようにコンデンサC71を700pF、切り替え用コンデンサC76を35pF、プルダウン抵抗R15を20Ω、ベース抵抗R12を20Ωとすると、時定数はおおよそ35pFと20Ωによって決まる値となる。

【0096】

時定数の変化は実施例4と同様に図8(f)に示す。このように、IGBT(Q11)のターンオフ時とターンオン時で時定数を変化させることができ、dv/dt抑制・スナバ回路71の負帰還量とスナバ時定数をそれぞれ適した値にすることができる。

【0097】

なお本実施例の変形例として、コンデンサを変化させるのと同時に、PNPトランジスタQ12のベース抵抗を実施例2、実施例3のように変化させて、dv/dt抑制・スナバ回路71の負帰還量とスナバ時定数をそれぞれ適した値になるように選んでもよい。

【0098】

以上説明したように本実施例によれば、電圧駆動素子のターンオン時とターンオフ時でスナバ時定数を決定するコンデンサの値を変化させることで、電圧駆動素子のゲート電荷放電速度を緩和することができ、還流ダイオードにユニポーラ型ダイオードを用いた場合でも、サージ電圧やリンギングを抑制することができ、電圧駆動素子の誤動作を防止することができるという効果がある。

【0099】

また本実施例によれば、外付けCRスナバ回路よりも損失を低減して、駆動回路の信頼性を向上させることができるという効果がある。

【0100】

なお、本実施例において、Q13およびQ55がNPNトランジスタ、Q12およびQ54がPNPトランジスタである例を示したが、バイポーラ型トランジスタだけでなく、Q13およびQ55がNチャンネルMOSFET、Q12およびQ54がPチャンネルMOSFETであってもよい。その場合には、それぞれ、ベースがゲート、コレクタがドレイン、エミッタがソースに対応する。

【実施例6】

【0101】

図10は、本発明に係る電圧駆動素子の駆動回路の実施例6である駆動回路10を用いたソレノイド駆動回路を示す回路図である。本実施例は、ソレノイドや電磁クラッチ等の誘導性負荷を駆動する電圧駆動素子の駆動回路に適用した実施例である。

【0102】

図10において、電源電圧VBには、誘導性負荷であるソレノイドL11の一端及び還流ダイオードD12のカソードが接続されている。ソレノイドL11の他端と還流ダイオードD12のアノードは、電圧駆動素子であるIGBT(Q11)の一方の主電極であるコレクタに接続されている。IGBT(Q11)の他方の主電極であるエミッタは接地されている。IGBT(Q11)のゲートは、駆動回路10に接続されている。ここで、還流ダイオードD12は、ショットキバリアダイオード等のユニポーラ型のダイオードである。

【0103】

駆動回路10は、IGBT(Q11)のゲートを駆動するコンプリメンタリ型のエミッタフォロア回路を含むdv/dt抑制・スナバ回路11を備える。

【0104】

dv/dt抑制・スナバ回路11は、コレクタが接地されたPNPトランジスタQ12(第1のPNPトランジスタ)と、コレクタが電源電圧Vccに接続されたNPNトランジスタQ13と、ベース抵抗R12(第1の抵抗)と、ベースR14と、抵抗R19(第2の抵抗)と、エミッタ抵抗R11,R13と、コンデンサC11(第1のコンデンサ)と、ダイオードD11(第1のダイオード)と、ダイオードD14(第2のダイオード)と、プルダウン抵抗R15とを備える。

【0105】

入力信号Vinは、ベース抵抗R12,R14を介して、それぞれPNPトランジスタQ12のベースとNPNトランジスタQ13のベースに接続されている。PNPトランジスタQ12のエミッタとNPNトランジスタQ13のエミッタとは、それぞれエミッタ抵抗R11,R13を介して、IGBT(Q11)のゲートに接続されている。また、入力信号Vinは図示しない外部回路により、電源電圧VccをHレベル、GND電位をLレベルとしたPWM信号が入力されている。

【0106】

コンデンサC11の一端は、IGBT(Q11)のコレクタに接続され、コンデンサC11の他端は、ダイオードD11のアノードに接続されている。コンデンサC11とダイオードD11のアノードとの接続点を点Aと呼ぶ。ダイオードD11のカソードは、抵抗R19の一端に接続されている。抵抗R19の他端はPNPトランジスタQ12のベースに接続されている。つまり電流はコンデンサC11側からPNPトランジスタQ12のベース側へ流れる方向に規制される。さらに点Aには、ダイオードD14のカソードが接続され、ダイオードD14のアノードはプルダウン抵抗R15を介して接地されている。

【0107】

次に、図10に示した駆動回路10の動作を、図3を用いて説明する。図3は入力信号Vinを変化させてIGBT(Q11)のオン/オフを繰り返したときにおける各部の電圧波形を示す図である。図3(a)は入力信号Vin、(b)はIGBT(Q11)のコレクタ−エミッタ間電圧Vce、(c)はPNPトランジスタQ12のベース電圧Vb、(d)はA点の電圧である。

【0108】

入力信号VinをLからHへ変化させると、若干の遅延の後、IGBT(Q11)はターンオン動作に入る(時刻t11)。この際、IGBT(Q11)のコレクタ−エミッタ間電圧Vceは低下していく。すなわち、負のdv/dtが発生する(時刻t11〜t12)。この負のdv/dtにより、コンデンサC11にはA点からIGBT(Q11)のコレクタに向かって電流が流れる。この電流は、プルダウン抵抗R15とダイオードD14を介してGNDから供給されるため、A点の電位はプルダウン抵抗R15の電圧降下分だけ下がり、負の電位となるが、ダイオードD11が存在するため、PNPトランジスタQ12のベースに負電圧が印加されることはない。

【0109】

したがって、ベース抵抗R12やコンデンサC11の値にかかわらず、PNPトランジスタQ12が破壊されるおそれはない。また、ターンオン終了(時刻t12)後、A点の電位はプルダウン抵抗R15とコンデンサC11によって決まる時定数で初期状態である0V近傍へ復帰して行く。プルダウン抵抗R15の値としては、速やかに0V近傍へ復帰させるため、時定数が小さくなるような値が選ばれる。

【0110】

次に、入力信号VinをHからLへ変化させると、若干の遅延の後、IGBT(Q11)はターンオフ動作に入る(時刻t13)。この際、IGBT(Q11)のコレクタ−エミッタ間電圧Vceは上昇していく。すなわち、正のdv/dtが発生する。この正のdv/dtにより、コンデンサC11には、IGBT(Q11)のコレクタからA点に向かって電流が流れる。この電流はA点からダイオードD11および抵抗R19を介して、PNPトランジスタQ12のベース抵抗R12へ流れ込むため、ベース抵抗R12で電圧が発生し、PNPトランジスタQ12のベース電圧Vbは上昇する。この電圧上昇速度は、コンデンサC11とベース抵抗R12によって決まる時定数により決定され、上昇電圧はベース抵抗R12と抵抗R19で分圧される。

【0111】

IGBT(Q11)のVceに発生するdv/dtは、IGBT(Q11)のターンオフ速度によって決まる。IGBT(Q11)のターンオフ速度は、ゲート電荷の放電速度すなわちゲート電流Ig(off)の大きさで調整可能であり、ゲート電流Ig(off)は、ゲート電圧をVgとし、PNPトランジスタQ12のベース電圧をVbとし、PNPトランジスタQ12のベースに対するエミッタ電圧をVfとしたときに、式(4)で表すことができる。

Ig(off)=(Vg−Vb−Vf)/R11 …(4)

【0112】

したがってベース電圧Vbの上昇によって、ゲート電流Ig(off)が減少し、IGBT(Q11)のゲート電荷放電速度が緩和されることになる。この負帰還作用により、コンデンサC11、ベース抵抗R12、ゲート抵抗R11によって決まる所定のdv/dt(101)に一致するように、IGBT(Q11)のターンオフ動作が制御され、過大なサージ電圧の発生を抑えることができる。サージ電圧の消滅時(時刻t14〜t15)には、ターンオン時同様、負のdv/dtが発生するが、前述のターンオン時と同じ理由で、PNPトランジスタQ12のベースに負の電圧が印加されることはない。

【0113】

尚、本実施例では、必要な回路定数の設定方法を省略したが、実施例1に記載の方法により同様に設定することができる。

【0114】

駆動回路の基板上にスナバ回路を設置する場合、スナバの損失は抵抗のサイズ低減の観点で重要な意味を持つ。抵抗のサイズは許容損失で決まり、許容損失が大きい抵抗はサイズも大きく、はんだ接合の信頼性上、好ましくない。本実施例はスナバ回路で発生する損失を減らせるため、抵抗のサイズを小さくでき、はんだ接合の信頼性を向上させることができる。

【0115】

次に、本実施例の変形例を説明する。図10に示した駆動回路10に代えて、図4に示した実施例2の駆動回路15、図6に示した実施例3の駆動回路30、図7に示した実施例4の駆動回路50、図9に示した実施例5の駆動回路70の何れかを用いることができる。これらの駆動回路により図10のIGBT(Q11)を駆動しても、本実施例と同様の効果を得ることができるのは明らかである。

【0116】

以上説明したように本実施例によれば、電圧駆動素子のターンオフ時にはコンデンサC11からフィードバックされる電圧のうち、ベース抵抗R12と抵抗R19で分圧した一部の電圧をゲート駆動素子に入力することで、適度に電圧駆動素子のゲート電荷放電速度を緩和することができ、電圧駆動素子のdv/dtが抑制されることでサージ電圧を抑制できる。さらに電圧駆動素子のターンオン時においては、ユニポーラ型ダイオードを還流ダイオードを還流ダイオードD12に用いた場合でも、ダイオードのハードなスイッチングによる急峻な変化電流はコンデンサC11を通ってベース抵抗R12と抵抗R19の両方を流れ、合算した抵抗値でスナバ回路が形成される。従って、スナバ回路としても適当な回路定数となり、リンギングを抑制することができ、電圧駆動素子の誤動作を防止することができるという効果がある。

【0117】

また本実施例によれば、外付けCRスナバ回路よりも損失を低減して、駆動回路の信頼性を向上させることができるという効果がある。

【0118】

なお、本実施例において、Q13がNPNトランジスタ、Q12がPNPトランジスタである例を示したが、バイポーラ型トランジスタだけでなく、Q13がNチャンネルMOSFET、Q12がPチャンネルMOSFETであってもよい。その場合には、それぞれ、ベースがゲート、コレクタがドレイン、エミッタがソースに対応する。

【0119】

なお、本実施例では還流ダイオードD12にユニポーラ型ダイオードを例にした場合で説明したが、ユニポーラ型ダイオードと同様に、従来のスイッチング回路において電流遮断時にリンギングを生じる虞があるような素子であってもよい。例えば、ハードな(急峻な)リカバリ特性を持つバイポーラ型ダイオードであってもよい。

【符号の説明】

【0120】

10、15、30、50、70…駆動回路

11、21、31、51、71…dv/dt抑制・スナバ回路

12、32、52、72…スナバ切り替え回路

Q10、Q11…IGBT

D12、D13…還流ダイオード

R11、R12、R13、R14、R17、R18、R19…抵抗

R15…プルダウン抵抗

R16、R36…切り替え用抵抗

R32、R38、R57、R58…抵抗

C11、C12、C51、C71…コンデンサ

C56、C76…切り替え用コンデンサ

D11、D14…ダイオード

Q12、Q15…PNPトランジスタ

Q13、Q55…NPNトランジスタ

Q14…切り替え用NPNトランジスタ

Q54…切り替え用PNPトランジスタ

Vin…入力信号

【技術分野】

【0001】

本発明は、電圧駆動素子の駆動回路に係り、特に、電圧駆動素子の電圧変化率を制御するために出力電圧を駆動回路の入力側へフィードバックする駆動回路において、スイッチングノイズを抑制する駆動回路に関する。

【背景技術】

【0002】

制御電極であるゲートに印加する電圧により2つの主電極間に流れる電流を制御する電圧駆動素子として、IGBT(Insulated Gate Bipolar Transistor:絶縁ゲート型バイポーラトランジスタ)やパワーMOSFETがある。これらの電圧駆動素子の場合、ゲートに接続する抵抗値を調整することにより、スイッチング速度をチューニングし、過大なサージ電圧の発生を抑えることが多い。ただし、この手法では、IGBTやパワーMOSFETのバラツキや温度特性により、スイッチング速度も変動してしまう。そのためスイッチング速度信号を電圧駆動素子のゲートにフィードバックすることにより、電圧駆動素子のスイッチング速度を状況に応じて調整する方法が知られている。

【0003】

例えば、負荷を駆動する電圧駆動素子のゲートに、エミッタが接続され、コレクタが接地されたPNPトランジスタを備え、電圧駆動素子のターンオフ時に、電圧駆動素子のゲート電荷をPNPトランジスタを介して放電することにより、電圧駆動素子をターンオフする電圧駆動素子の駆動回路がある。この駆動回路において、コンデンサとダイオードの直列回路におけるコンデンサ側の一端を電圧駆動素子の非接地側の主電極に接続し、ダイオード側の一端をPNPトランジスタのベースに接続し、コンデンサとダイオードの接続点と接地間にプルダウン抵抗を接続し、ダイオードは電流をコンデンサからトランジスタのベース方向へ流す極性に接続した回路がある(特許文献1)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第3997905号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

近年、SiC等の化合物半導体の実用化に伴い、高耐圧電力用のショットキーバリアダイオードやヘテロジャンクションダイオード等のユニポーラ型ダイオードが開発されてきた。ユニポーラ型ダイオードは、動作中に少数キャリアが発生せず、PN接合またはPIN接合を用いたバイポーラ型ダイオードと比較して高速に電流を遮断できるので、スイッチング損失を低減することができる。

【0006】

しかしながら、上記従来の電圧駆動素子の駆動回路においては、誘導性負荷の還流ダイオードに高速のダイオードを用いた場合に、電圧駆動素子のターンオフ時には電圧上昇率(dv/dt)を抑制してサージ電圧を抑制できるものの、ターンオン時には還流ダイオードの急峻なスイッチングにより、リンギングが生じてノイズの放射により誤動作を引き起こす虞があるという問題点があった。この問題点は、特にスイッチング速度の速いユニポーラ型ダイオードを還流ダイオードとして用いた場合に顕著である。

【課題を解決するための手段】

【0007】

上記問題点を解決するために本発明は、電圧駆動素子に誘導性の負荷と還流ダイオードとが接続され、電圧駆動素子のゲートと接地間に第1のPNPトランジスタ又はPチャンネルMOSFETが接続され、電圧駆動素子のゲート電荷を第1のPNPトランジスタ又はPチャンネルMOSFETを介して放電することにより、電圧駆動素子をターンオフする電圧駆動素子の駆動回路において、電圧駆動素子の非接地側の主電極に第1のコンデンサの一端を接続し、第1のコンデンサの他端を第1のダイオードのアノードに接続し、第1のダイオードのカソードを第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートに接続し、第1のコンデンサの他端と接地間にプルダウン抵抗及び第2のダイオードを直列接続したプルダウン回路を接続し、第2のダイオードはアノード端子が接地側を向いている。

【0008】

さらに、第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートと電圧信号入力端子との間には第1の抵抗が接続され、第1の抵抗と第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートとの接続点から、第1のコンデンサの他端とプルダウン回路との接続点までの間に、第1のダイオードに直列接続される第2の抵抗を備えたことを要旨とする。

【発明の効果】

【0009】

本発明によれば、電圧駆動素子のターンオフ時には第1のコンデンサからフィードバックされる電圧のうち、第1の抵抗と第2の抵抗で分圧した電圧をゲート駆動素子に入力することで、適度に電圧駆動素子のゲート電荷放電速度を緩和することができ、電圧駆動素子の電圧上昇率(dv/dt)が抑制されることでサージ電圧を抑制できる。さらに電圧駆動素子のターンオン時においては、ユニポーラ型ダイオード等の高速素子を還流ダイオードに用いた場合でも、還流ダイオードの高速なスイッチングによる急峻な変化電流は第1のコンデンサを通って第1の抵抗と第2の抵抗の両方を流れ、第1の抵抗の抵抗値と第2の抵抗の抵抗値を合計した抵抗値でスナバ回路が形成されるので、スナバ回路としても適当な回路定数となり、リンギングを抑制することができ、電圧駆動素子の誤動作を防止することができるという効果がある。

【図面の簡単な説明】

【0010】

【図1】本発明に係る電圧駆動素子の駆動回路の実施例1を示す回路図である。

【図2】図1の電圧駆動素子の駆動回路を用いた三相インバータ回路の回路図である。

【図3】図1の回路において、入力信号Vinを変化させて、IGBT(Q11)のオン/オフを繰り返したときにおける各部の電圧波形を示す図である。

【図4】本発明に係る電圧駆動素子の駆動回路の実施例2を示す回路図である。

【図5】図4、図6の回路において、入力信号Vinを変化させて、IGBT(Q11)のオン/オフを繰り返したときにおける各部の波形を示す図である。

【図6】本発明に係る電圧駆動素子の駆動回路の実施例3を示す回路図である。

【図7】本発明に係る電圧駆動素子の駆動回路の実施例4を示す回路図である。

【図8】図7、図9の回路において、入力信号Vinを変化させて、IGBT(Q11)のオン/オフを繰り返したときにおける各部の波形を示す図である。

【図9】本発明に係る電圧駆動素子の駆動回路の実施例5を示す回路図である。

【図10】本発明に係る電圧駆動素子の駆動回路の実施例6を示す回路図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施形態を図面に基づいて説明する。尚、以下に説明する各実施例は、電圧駆動素子の一つであるIGBTを用いて負荷を駆動する際の駆動回路を示すが、MOS−FETの駆動回路にも本発明を適用することができるのは明らかである。IGBTの主電極は、エミッタ及びコレクタであり、MOS−FETの主電極は、ドレイン及びソースである。2つの主電極間の電流を制御する制御電極は、IGBT及びMOS−FET共にゲートである。

【実施例1】

【0012】

図1は、本発明に係る電圧駆動素子の駆動回路の実施例1である駆動回路10を用いた、三相インバータの一相分のアーム駆動回路を示す回路図である。図2は、図1の回路を用いた三相インバータ回路の回路図である。

【0013】

図2において、三相インバータは、平滑コンデンサCと、U相のアーム100と、V相のアーム110と、W相のアーム120と、三相同期モータMと、を有している。平滑コンデンサCは電源VBと接地(GND)間に接続されている。アーム100,110,120は、それぞれ同じ構成の図1に示したアームであり、3並列のアームにより三相ブリッジ回路を構成している。そして、各アームの上下のIGBTの接続点が、三相同期モータMのU相、V相、W相にそれぞれ接続されている。

【0014】

次に、図1に示した駆動回路10について説明する。図1において、電源電圧VBと接地(GND)間には、IGBT(Q10)とIGBT(Q11、電圧駆動素子)が直列接続され、それぞれに駆動回路10と駆動回路20が接続され、三相インバータの一つのアームを形成している。IGBT(Q10)のエミッタ−コレクタ間には、還流ダイオードD12が接続され、IGBT(Q11)のエミッタ−コレクタ間には、還流ダイオードD13が接続されている。

【0015】

本実施例における還流ダイオードD12,D13は、ショットキバリアダイオードや本願出願人による特許第4282972号公報に記載のヘテロジャンクションダイオード等のユニポーラ型ダイオードである。

【0016】

負荷L11は三相同期モータMの一部を回路上に書き出したものであり、負荷L11の一端は、IGBT(Q10)のエミッタとIGBT(Q11)のコレクタとの接続点に接続されている。負荷L11の他端は、三相同期モータMの図示しない中性点に接続されている。

【0017】

駆動回路10は、IGBT(Q11)のゲートを駆動するコンプリメンタリ型のエミッタフォロア回路を含むdv/dt抑制・スナバ回路11を備える。

【0018】

dv/dt抑制・スナバ回路11は、コレクタが接地されたPNPトランジスタQ12(第1のPNPトランジスタ)と、コレクタが電源電圧Vccに接続されたNPNトランジスタQ13と、ベース抵抗R12(第1の抵抗)と、ベース抵抗R14と、抵抗R19(第2の抵抗)と、エミッタ抵抗R11,R13と、コンデンサC11(第1のコンデンサ)と、ダイオードD11(第1のダイオード)と、ダイオードD14(第2のダイオード)と、プルダウン抵抗R15とを備える。

【0019】

入力信号Vin(入力信号端子、入力信号電圧)は、ベース抵抗R12,R14を介して、それぞれPNPトランジスタQ12のベースとNPNトランジスタQ13のベースに接続されている。PNPトランジスタQ12のエミッタとNPNトランジスタQ13のエミッタとは、それぞれエミッタ抵抗R11,R13を介して、IGBT(Q11)のゲートに接続されている。また、入力信号Vinとしては、図示しない外部回路により、電源電圧VccをHレベル、GND電位をLレベルとしたPWM信号が入力されている。

【0020】

コンデンサC11の一端は、IGBT(Q10)のエミッタとIGBT(Q11)のコレクタとの接続点に接続され、コンデンサC11の他端は、ダイオードD11のアノードに接続されている。コンデンサC11とダイオードD11のアノードとの接続点を点Aと呼ぶ。ダイオードD11のカソードは、抵抗R19の一端に接続されている。抵抗R19の他端はPNPトランジスタQ12のベースに接続されている。つまり電流はコンデンサC11側からPNPトランジスタQ12のベース側へ流れる方向に規制される。さらに点Aには、ダイオードD14のカソードが接続され、ダイオードD14のアノードはプルダウン抵抗R15を介して接地されている。

【0021】

次に、図1に示した駆動回路10の動作を、図3を用いて説明する。図3は入力信号Vinを変化させてIGBT(Q11)のオン/オフを繰り返したときにおける各部の電圧波形を示す図である。図3(a)は入力信号Vin、(b)はIGBT(Q11)のコレクタ−エミッタ間電圧Vce、(c)はPNPトランジスタQ12のベース電圧Vb、(d)はA点の電圧である。

【0022】

入力信号VinをLからHへ変化させると、若干の遅延の後、IGBT(Q11)はターンオン動作に入る(時刻t11)。この際、IGBT(Q11)のコレクタ−エミッタ間電圧Vceは低下していく。すなわち、負の電圧変化率(dv/dt)が発生する(時刻t11〜t12)。この負のdv/dtにより、コンデンサC11にはA点からIGBT(Q11)のコレクタに向かって電流が流れる。この電流は、プルダウン抵抗R15とダイオードD14を介してGNDから供給されるため、A点の電位はプルダウン抵抗R15の電圧降下分だけ下がり、負の電位となるが、ダイオードD11が存在するため、PNPトランジスタQ12のベースに負電圧が印加されることはない。

【0023】

したがって、ベース抵抗R12やコンデンサC11の値にかかわらず、PNPトランジスタQ12が破壊されるおそれはない。また、ターンオン終了(時刻t12)後、A点の電位はプルダウン抵抗R15とコンデンサC11によって決まる時定数で初期状態である0V近傍へ復帰して行く。プルダウン抵抗R15の値としては、速やかに0V近傍へ復帰させるため、時定数が小さくなるような値が選ばれる。

【0024】

次に、入力信号VinをHからLへ変化させると、若干の遅延の後、IGBT(Q11)はターンオフ動作に入る(時刻t13)。この際、IGBT(Q11)のコレクタ−エミッタ間電圧Vceは上昇していく。すなわち、正の電圧変化率(dv/dt)が発生する。この正のdv/dtにより、コンデンサC11には、IGBT(Q11)のコレクタからA点に向かって電流が流れる。この電流はA点からダイオードD11および抵抗R19を介して、PNPトランジスタQ12のベース抵抗R12へ流れ込むため、ベース抵抗R12で電圧が発生し、PNPトランジスタQ12のベース電圧Vbは上昇する。この電圧上昇速度は、コンデンサC11とベース抵抗R12によって決まる時定数により決定され、上昇電圧はベース抵抗R12と抵抗R19で分圧される。

【0025】

IGBT(Q11)のVceに発生するdv/dtは、IGBT(Q11)のターンオフ速度によって決まる。IGBT(Q11)のターンオフ速度は、ゲート電荷の放電速度すなわちゲート電流Ig(off)の大きさで調整可能であり、ゲート電流Ig(off)は、ゲート電圧をVgとし、PNPトランジスタQ12のベース電圧をVbとし、PNPトランジスタQ12のベースに対するエミッタ電圧をVfとしたときに、式(1)で表すことができる。

Ig(off)=(Vg−Vb−Vf)/R11 …(1)

【0026】

したがってベース電圧Vbの上昇によって、ゲート電流Ig(off)が減少し、IGBT(Q11)のゲート電荷放電速度が緩和されることになる。この負帰還作用により、コンデンサC11、ベース抵抗R12、ゲート抵抗R11によって決まる所定のdv/dt(101)に一致するように、IGBT(Q11)のターンオフ動作が制御され、過大なサージ電圧の発生を抑えることができる。サージ電圧の消滅時(時刻t14〜t15)には、ターンオン時同様、負のdv/dtが発生するが、前述のターンオン時と同じ理由で、PNPトランジスタQ12のベースに負の電圧が印加されることはない。

【0027】

次に回路定数の設定方法を説明する。IGBT(Q11)のターンオフ時の電圧上昇速度dv/dt(101)は、PNPトランジスタQ12のベース−エミッタ間電圧Vfの電圧変化にともなって変化する。PNPトランジスタQ12のVfは入力信号Vinの電圧に対して、ベース抵抗R12における降下電圧の分だけ減少する。すなわち、ベース抵抗R12における降下電圧が大きいとPNPトランジスタQ12のVfは減少することになり、それにともなってIGBT(Q11)のターンオフ時の電圧上昇速度dv/dtが減少することになる。

【0028】

ここで、IGBT(Q11)のターンオフ時には、IGBT(Q11)のコレクタからコンデンサC11を通ってA点に流れる電流が、ダイオードD11、抵抗R19、ベース抵抗R12を介して、Lレベルとなった入力信号Vinの端子へ流れる。この電流により抵抗R19とベース抵抗R12において電圧降下を生じ、その電圧をベース抵抗R12と抵抗R19で分圧した電圧がPNPトランジスタQ12のベース電圧となる。例えば、コンデンサC11の容量として700pFを用いた場合には、分圧比を1/20程度にすればよく、その際にはベース抵抗R12の値として1Ω、抵抗R19の値として19Ωが適した値となる。

【0029】

一方、還流ダイオードD13に還流電流が流れている間にIGBT(Q10)がターンオンする際には、IGBT(Q11)はオフ状態で、IGBT(Q11)のゲート駆動回路10の入力信号VinはGND状態になっており、還流ダイオードD13は遮断するタイミングとなる。還流ダイオードD13はユニポーラ型ダイオードであるため、高速な電流遮断特性となり、通常ではリンギングが発生してしまう。しかし、本回路においては、コンデンサC11とD11と抵抗R19とベース抵抗R12との直列回路が、IGBT(Q11)のコレクタとLレベルの入力信号Vinとの間に接続されているので、この直列回路がスナバ回路として働き、リンギングは抑制される。

【0030】

その際の回路定数として、例えばコンデンサC11の容量として700pFが用いられ、ベース抵抗R12の値として1Ωが用いられ、抵抗R19の値として19Ωが用いられる。この回路定数は次のように求まる。一般的に、CRスナバ回路のコンデンサCはIGBTモジュールの寄生容量と同程度にし、抵抗RはCRスナバ回路の時定数の逆数(1/(2πCR))がIGBTモジュールのリンギング周波数fと同程度になるように設計する(f=1/(2πCR))。例えば、IGBTモジュールの寄生容量が700pFで、リンギング周波数fが11MHzだとすると、CRスナバ回路のコンデンサCは700pFとなり、抵抗Rは、次の式(2)により、約20Ω(正確な計算値は、20.67Ω)と求まる。実際には、計算値の周辺の値を用いて実験的に損失やリンギング抑制効果を検証しながら最適値を求めてもよい。

R=1/(2πCf)≒20 …(2)

【0031】

このように、IGBT(Q11)のターンオフ時のdv/dtを適度に抑制するための抵抗Rの大きさは1Ωであるが、この値では、IGBT(Q10)のターンオン時に発生するリンギングを抑制するためにはスナバ抵抗の値として小さすぎる。そこで、本実施の形態では、回路上でdv/dtを抑制に影響がある部分とdv/dt抑制に影響しない部分があることに着目し、抵抗をベース抵抗R12と抵抗R19に分割して、合計を20Ωにしつつ、dv/dt抑制に影響がある部分のベース抵抗R12は1Ωにして、dv/dt抑制とリンギング抑制を両立している。

【0032】

なお、IGBT(Q11)のターンオフ時に、抵抗R15にはダイオードD14により電流が流れないため、CRスナバ回路に適した20Ω周辺の値にすればよい。

【0033】

本実施例の比較例として、外付けCRスナバ回路を接続する場合、例えばdv/dt抑制回路のコンデンサC11の容量を700pFとすると、外付けスナバ回路に必要なコンデンサ容量は、dv/dt抑制回路の容量700pFとIGBTモジュールの寄生容量700pFを合計した1400pFになる。スナバ回路の損失はコンデンサ容量に比例することから、外付けCRスナバ回路を接続する比較例の場合は、本発明の駆動回路を用いた場合の2倍の損失が発生してしまう。

【0034】

駆動回路の基板上にスナバ回路を設置する場合、スナバの損失は抵抗のサイズ低減の観点で重要な意味を持つ。抵抗のサイズは許容損失で決まり、許容損失が大きい抵抗はサイズも大きく、はんだ接合の信頼性上、好ましくない。本実施例はスナバ回路で発生する損失を減らせるため、抵抗のサイズを小さくすることができるので、はんだ接合の信頼性を向上させることができ、また駆動回路基板のサイズを小さくすることができる。

【0035】

以上説明したように本実施例によれば、電圧駆動素子のターンオフ時にはコンデンサC11からフィードバックされる電圧のうち、ベース抵抗R12と抵抗R19で分圧した一部の電圧をゲート駆動素子に入力することで、適度に電圧駆動素子のゲート電荷放電速度を緩和することができ、電圧駆動素子のdv/dtが抑制されることでサージ電圧を抑制することができるという効果がある。さらに電圧駆動素子のターンオン時においては、ユニポーラ型ダイオードを還流ダイオードを還流ダイオードD13に用いた場合でも、ダイオードのハードなスイッチングによる急峻な変化電流はコンデンサC11を通ってベース抵抗R12と抵抗R19の両方を流れ、合算した抵抗値でスナバ回路が形成されるので、スナバ回路としても適当な回路定数となり、リンギングを抑制することができ、電圧駆動素子の誤動作を防止することができるという効果がある。

【0036】

また本実施例によれば、外付けCRスナバ回路よりもスナバ回路の損失を低減して、駆動回路の信頼性を向上させることができるという効果がある。

【0037】

なお、本実施例において、Q13がNPNトランジスタ、Q12がPNPトランジスタである例を示したが、バイポーラ型トランジスタだけでなく、Q13がNチャンネルMOSFET、Q12がPチャンネルMOSFETであってもよい。その場合には、それぞれ、ベースがゲート、コレクタがドレイン、エミッタがソースに対応する。

【0038】

なお、本実施例では還流ダイオードD12、およびD13にユニポーラ型ダイオードを用いた場合を説明したが、ユニポーラ型ダイオードに限らず、ユニポーラ型ダイオードと同様に従来の駆動回路では電流遮断時にリンギングを生じてしまうような素子であってもよい。例えば、ユニポーラ型ダイオードと同様にハードな(急峻な)リカバリ特性を持つバイポーラ型ダイオードであってもよい。

【実施例2】

【0039】

図4は、本発明に係る電圧駆動素子の駆動回路の実施例2の回路図である。実施例1の駆動回路10に対する実施例2の駆動回路15の変更点は、図1のdv/dt抑制・スナバ回路11において抵抗R19の値を極力小さくして(実際には0Ω)図4のdv/dt抑制・スナバ回路21としたことと、スナバ切り替え回路12を追加した点にある。その他の構成は、実施例1と同様であるので、同じ構成要素には同じ符号を付与している。

【0040】

スナバ切り替え回路12は、PNPトランジスタQ15(第2のPNPトランジスタ)と、NPNトランジスタQ14(スイッチ素子、第1のNPNトランジスタ)と、コンデンサC12(第2のコンデンサ)と、切り替え用抵抗R16(第3の抵抗)と,抵抗R17(第5の抵抗)と、抵抗R18(第4の抵抗)とを備える。PNPトランジスタQ15のエミッタは電源Vccに接続されている。PNPトランジスタQ15のベースは抵抗R17を介して電源Vccに接続されており、また、コンデンサC12を介して入力信号Vinに接続されている。

【0041】

また、PNPトランジスタQ12のベースは抵抗R16を介して、NPNトランジスタQ14のコレクタに接続されている。NPNトランジスタQ14のエミッタは接地されている。NPNトランジスタQ14のベースは抵抗R18を介して接地されており、また、PNPトランジスタQ15のコレクタに接続されている。

【0042】

スナバ切り替え回路12は、入力信号VinがHからLへ切り替わる際、即ちIGBT(Q11)のターンオフ時に、NPNトランジスタQ14をオンさせて、切り替え抵抗R16を抵抗R12に対して並列接続させる回路である。入力信号VinがLからHへ切り替わるIGBT(Q11)のターンオン時には、NPNトランジスタQ14はオフであり、切り替え抵抗R16は抵抗R12に対して切り離されている。

【0043】

次に、図4に示した駆動回路15の動作を、図3を用いて説明する。図3は入力信号Vinを変化させて、IGBT(Q11)およびIGBT(Q10)のオン/オフを繰り返したときにおける各部の電圧波形を示す図である。図3(a)は入力信号Vin、(b)はIGBT(Q11)のコレクタ−エミッタ間電圧Vce、(c)はPNPトランジスタQ12のベース電圧Vb、(d)はA点の電圧である。

【0044】

入力信号VinをLからHへ変化させると、若干の遅延の後、IGBT(Q11)はターンオン動作に入る(時刻t11)。この際、IGBT(Q11)のコレクタ−エミッタ間電圧Vceは低下していく。すなわち、負のdv/dtが発生する(時刻t11〜t12)。この負のdv/dtにより、コンデンサC11にはA点からIGBT(Q11)のコレクタに向かって電流が流れる。この電流は、プルダウン抵抗R15とダイオードD14を介してGNDから供給されるため、A点の電位はプルダウン抵抗R15の電圧降下分だけ下がり、負の電位となるが、ダイオードD11が存在するため、PNPトランジスタQ12のベースに負電圧が印加されることはない。

【0045】

したがって、ベース抵抗R12やコンデンサC11の値にかかわらず、PNPトランジスタQ12が破壊されるおそれはない。また、ターンオン終了(時刻t12)後、A点の電位はプルダウン抵抗R15とコンデンサC11によって決まる時定数で初期状態である0V近傍へ復帰して行く。プルダウン抵抗R15の値としては、速やかに0V近傍へ復帰させるため、時定数が小さくなるような値が選ばれる。

【0046】

次に、入力信号VinをHからLへ変化させると、若干の遅延の後、IGBT(Q11)はターンオフ動作に入る(時刻t13)。この際、IGBT(Q11)のコレクタ−エミッタ間電圧Vceは上昇していく。すなわち、正のdv/dtが発生する。この正のdv/dtにより、コンデンサC11には、IGBT(Q11)のコレクタからA点に向かって電流が流れる。この電流はA点からダイオードD11を介して、PNPトランジスタQ12のベース抵抗R12および切り替え用抵抗R16へ流れ込むため、PNPトランジスタQ12のベース電圧Vbは上昇する。この電圧上昇速度は、コンデンサC11とベース抵抗R12によって決まる時定数により決定される。

【0047】

IGBT(Q11)のVceに発生するdv/dtは、IGBT(Q11)のターンオフ速度によって決まる。IGBT(Q11)のターンオフ速度は、ゲート電荷の放電速度すなわちゲート電流Ig(off)の大きさで調整可能であり、ゲート電流Ig(off)は、ゲート電圧をVgとし、PNPトランジスタQ12のベース電圧をVbとし、PNPトランジスタQ12のベースに対するエミッタ電圧をVfとしたときに、式(3)で表すことができる。

Ig(off)=(Vg−Vb−Vf)/R11 …(3)

【0048】

したがってベース電圧Vbの上昇によって、ゲート電流Ig(off)が減少し、IGBT(Q11)のゲート電荷放電速度が緩和されることになる。この負帰還作用により、コンデンサC11、ベース抵抗R12、ゲート抵抗R11によって決まる所定のdv/dt(101)に一致するように、IGBT(Q11)のターンオフ動作が制御され、過大なサージ電圧の発生を抑えることができる。サージ電圧の消滅時(時刻t14〜t15)には、ターンオン時同様、負のdv/dtが発生するが、前述のターンオン時と同じ理由で、PNPトランジスタQ12のベースに負の電圧が印加されることはない。

【0049】

次に、スナバ切り替え回路12の動作を図5を用いて説明する。図5(a)は入力信号Vin、(b)はIGBT(Q11)のコレクタ−エミッタ間電圧Vce、(c)はダイオードD12の電圧Vdi、(d)はB点の電圧、(e)はPNPトランジスタQ15のコレクタ電流I11、(f)はCR時定数である。

【0050】

IGBT(Q11)のターンオフ時の電圧上昇速度dv/dt(101)は、dv/dt抑制・スナバ回路21の負帰還量を決めるコンデンサと抵抗による時定数に依存している。適した電圧上昇速度dv/dtを得るために、例えば、コンデンサ容量として700pFが用いられ、抵抗値として1Ωが用いられる。

【0051】

一方、IGBT(Q11)がターンオンするタイミングは、ユニポーラ型の還流ダイオードD12は遮断するタイミングとなる。電流が遮断する際に、上記の時定数をそのまま用いると、図5(c)のVdiに示すようなリンギングを生じてしまう。このリンギングは時定数をCRスナバとしての動作に適した値にすることで抑制することができる。その時の値は、おおよそリンギング周波数をfとすると、おおよそf=1/(2πCR)を満たし、例えば、コンデンサ容量として700pFが用いられ、抵抗値として20Ωが用いられる。

【0052】

このように、IGBT(Q11)のターンオフ時のIGBT(Q11)の電圧上昇速度dv/dt(101)を適した値にするCR時定数と、IGBT(Q11)のターンオン時の還流ダイオードD12に発生するリンギング抑制に適するCR時定数は異なる。

【0053】

本実施例のスナバ切り替え回路12によれば、IGBT(Q11)がターンオフする際には、NPNトランジスタQ14がオンすることにより、CR時定数はコンデンサC11と、ベース抵抗R12と切り替え用抵抗R16との合成抵抗によって決まり、IGBT(Q11)がターンオンする際には、NPNトランジスタQ14がオフであることにより、CR時定数はコンデンサC11と、ベース抵抗R12のみによって決まる。

【0054】

以下、スナバ切り替え回路12の動作を図5を参照して説明する。入力信号VinをHからLへ変化させると(時刻t16)、抵抗R17とコンデンサC12の接続点Bの電圧は図5(d)に示すように、Vccから減少する。これは、抵抗R17とコンデンサC12が微分回路を形成しているからであり、その減少している時間は抵抗R17とコンデンサC12による時定数により決まる。このVccから減少した電圧は、PNPトランジスタQ15のベース電圧Vb15になっており、Vb15が約0.6Vよりも大きいときには、PNPトランジスタQ15は導通状態になる。そうすると、PNPトランジスタQ15のコレクタから抵抗R18に電流が流れる。この抵抗R18に流れる電流I11の波形を図5(e)に示した。抵抗R18に電流が流れることで電圧降下が生じる。この電圧は切り替え用NPNトランジスタQ14のベース電圧Vb14になっている。

【0055】

すなわち、入力信号VinをHからLへ変化させる時(IGBT(Q11)のターンオフ時)から一定の時間は、切り替え用NPNトランジスタQ14が導通状態になり、回路の時定数はコンデンサC11と、ベース抵抗R12および切り替え用抵抗R16の合成抵抗によって決まる。

【0056】

例えば、コンデンサC11を700pF、ベース抵抗R12を20Ω、プルダウン抵抗R15を20Ω、切り替え用抵抗R16を1Ωにすると、時定数はおおよそ700pFと1Ωによって決まる値になる。なお、このタイミングにおいては、プルダウン抵抗R15に直列にダイオードD14が直列に接続されているために、プルダウン抵抗R15には電流は流れないため、時定数への影響はない。

【0057】

一方、入力信号VinをLからHへ変化させた時(時刻t17)は、抵抗R17とコンデンサC12の接続点Bの電圧は図5(d)に示すように、電源電圧Vccよりも電圧が上昇する。そのため、PNPトランジスタQ15は導通状態にならないため、切り替え用NPNトランジスタQ14も導通状態にならない。そのため、切り替え用抵抗R16に電流が流れることはない。結果的に、入力信号VinをLからHへ変化させる時(IGBT(Q11)のターンオン時)は、回路の時定数はコンデンサC11とベース抵抗R12のみによって決まる。例えば、上記のようにコンデンサC11を700pF、ベース抵抗R12を20Ω、プルダウン抵抗R15を20Ωとすると、時定数は700pFと20Ωによって決まる値となる。

【0058】

時定数の変化を図5(f)に示す。このように、IGBT(Q11)のターンオフ時とターンオン時で時定数を変化させることができ、dv/dt抑制・スナバ回路21の負帰還量とスナバ時定数をそれぞれに適した値にすることができる。

【0059】

本実施例の駆動回路10を用いた場合、例えば下アームのスイッチング素子(IGBT(Q11)およびダイオードD13)の寄生容量を700pFとすると、リンギング抑制のスナバには同程度の容量を必要とすることから、コンデンサC11の値として、700pF程度にすることができる。この容量は外付けスナバを付ける場合と比較して、少ない値である。スナバ回路の損失はコンデンサ容量に比例することから、スナバ回路で発生する損失を減らすことができる。

【0060】

本実施例の比較例として、外付けCRスナバ回路を接続する場合、例えばdv/dt抑制回路の寄生容量を700pFとすると、外付けスナバ回路に必要なコンデンサ容量はdv/dt抑制回路の寄生容量700pFとスイッチング素子の寄生容量700pFを合計した1400pFになる。スナバ回路の損失はコンデンサ容量に比例することから、外付けCRスナバ回路を接続する比較例の場合は、本発明の駆動回路を用いた場合の2倍の損失が発生する。

【0061】

駆動回路の基板上にスナバ回路を設置する場合、スナバの損失は抵抗のサイズ低減の観点で重要な意味を持つ。抵抗のサイズは許容損失で決まり、許容損失が大きい抵抗はサイズも大きく、はんだ接合の信頼性上、好ましくない。本実施例はスナバ回路で発生する損失を減らせるため、抵抗のサイズを小さくでき、はんだ接合の信頼性を向上させることができる。

【0062】

以上説明したように本実施例によれば、電圧駆動素子のターンオン時とターンオフ時でスナバ時定数を決定する抵抗の値を変化させることで、電圧駆動素子のゲート電荷放電速度を緩和することができ、還流ダイオードにユニポーラ型ダイオードを用いた場合でも、サージ電圧やリンギングを抑制することができ、電圧駆動素子の誤動作を防止することができるという効果がある。

【0063】

また本実施例によれば、外付けCRスナバ回路よりも損失を低減して、駆動回路の信頼性を向上させることができるという効果がある。

【0064】

なお、本実施例において、Q13およびQ14がNPNトランジスタ、Q12およびQ15がPNPトランジスタである例を示したが、バイポーラ型トランジスタだけでなく、Q13およびQ14がNチャンネルMOSFET、Q12およびQ15がPチャンネルMOSFETであってもよい。その場合には、それぞれ、ベースがゲート、コレクタがドレイン、エミッタがソースに対応する。

【実施例3】

【0065】

図6は、本発明に係る電圧駆動素子の駆動回路の実施例3の回路図である。実施例2に対して実施例3の主要な変更点は、時定数を構成する抵抗として、ベース抵抗R32(第1の抵抗)と切り替え抵抗R36(第6の抵抗)の直列回路を用いていることと、IGBT(Q11)がターンオンする際に、切り替え用NPNトランジスタQ14(スイッチ素子、第2のNPNトランジスタ)を導通させて、切り替え抵抗R36をバイパスさせることにより、時定数を変更していることである。

【0066】

本実施例の駆動回路30は、dv/dt抑制・スナバ回路31と、スナバ切り替え回路32とを備える。実施例2のベース抵抗R12に相当するものが、実施例3では、ベース抵抗R32と切り替え用抵抗R36である。

【0067】

スナバ切り替え回路32において、切り替え用抵抗R36をベース抵抗R32に直列に、入力信号Vinとの間に設け、切り替え用NPNトランジスタQ14(第2のNPNトランジスタ)がエミッタを入力信号Vinに、コレクタを切り替え用抵抗R36とベース抵抗R32との接続点に接続している点と、抵抗R38(第7の抵抗)をPNPトランジスタQ15(第3のPNPトランジスタ)のコレクタと入力信号Vinとの間に接続している。抵抗R32,R36,R38と、切り替え用NPNトランジスタQ14以外の構成は、図4に示した実施例2と同様であるので、同じ構成要素には同じ符号を付与して、重複する説明を省略する。

【0068】

動作においては、図5に示すように、入力信号VinをHからLに変化させた時(時刻t16)にPNPトランジスタQ15にベース電圧Vb15が印加される。PNPトランジスタQ15のコレクタ電流I11が流れるタイミングは、実施例2と同じである。異なる点は、コレクタ電流I11は抵抗R38に流れて、切り替え用NPNトランジスタQ14のベース電圧を発生して導通状態にし、切り替え用抵抗R36をバイパスするようになる点である。

【0069】

すなわち、入力信号VinをHからLへ変化させるとき(IGBT(Q11)のターンオフ時)から一定の時間は、切り替え用NPNトランジスタQ14が導通状態になり切り替え用抵抗R36をバイパスするので、回路の時定数はコンデンサC11と、ベース抵抗R32のみによって決まる。例えばコンデンサC11を700pF、ベース抵抗R32を1Ω、プルダウン抵抗R15を20Ω、切り替え用抵抗R36を19Ωとすると、時定数は700pFと1Ωによって決まる値になる。なお、このタイミングにおいては、プルダウン抵抗R15に直列にダイオードD14が直列に接続されているために、プルダウン抵抗R15には電流は流れないため、時定数への影響はない。

【0070】

一方、入力信号VinをLからHへ変化させた時(時刻t17)は、実施例2と同様に、PNPトランジスタQ15は導通状態にならないため、切り替え用NPNトランジスタQ14も導通状態にならない。そのため、切り替え用抵抗R36はバイパスされない。結果的に、入力信号VinをLからHへ変化させる時(IGBT(Q11)のターンオン時)は、回路の時定数はコンデンサC11と、ベース抵抗R32と切り替え用抵抗R36の直列抵抗によって決まる。例えば、上記のようにコンデンサC11を700pF、ベース抵抗R32を1Ω、プルダウン抵抗R15を20Ω、切り替え用抵抗R36を19Ωとすると、時定数は700pFと(1+19)Ωによって決まる値となる。

【0071】

時定数の変化は実施例2と同様に図5に示す。このように、IGBT(Q31)のターンオフ時とターンオン時で時定数を変化させることができ、dv/dt抑制・スナバ回路31の負帰還量とスナバ時定数をそれぞれ適した値にすることができる。

【0072】

以上説明したように本実施例によれば、電圧駆動素子のターンオン時とターンオフ時でスナバ時定数を決定する抵抗の値を変化させることで、電圧駆動素子のゲート電荷放電速度を緩和することができ、還流ダイオードにユニポーラ型ダイオードを用いた場合でも、サージ電圧やリンギングを抑制することができ、電圧駆動素子の誤動作を防止することができるという効果がある。

【0073】

また本実施例によれば、外付けCRスナバ回路よりも損失を低減して、駆動回路の信頼性を向上させることができるという効果がある。

【0074】

なお、本実施例において、Q13およびQ14がNPNトランジスタ、Q12およびQ15がPNPトランジスタである例を示したが、バイポーラ型トランジスタだけでなく、Q13およびQ14がNチャンネルMOSFET、Q12およびQ15がPチャンネルMOSFETであってもよい。その場合には、それぞれ、ベースがゲート、コレクタがドレイン、エミッタがソースに対応する。

【実施例4】

【0075】

図7は、本発明に係る電圧駆動素子の駆動回路の実施例4の回路図である。実施例4は実施例2と異なり、ターンオフ時とターンオン時で抵抗を切り替えるのではなく、コンデンサを切り替える。本実施例の駆動回路50は、dv/dt抑制・スナバ回路51と、スナバ切り替え回路52とを備える。

【0076】

本実施例の特徴は、切り替え用コンデンサC56(第4のコンデンサ)と切り替え用PNPトランジスタQ54(第4のPNPトランジスタ)のエミッタ−コレクタ間を直列に接続し、この直列回路と並列に、コンデンサC51(第1のコンデンサ)を設けている。そして、切り替え用PNPトランジスタQ54のエミッタ−コレクタ間をオン/オフすることにより時定数を変更している点である。

【0077】

下記に構成の違いについて説明する。実施例2と異なる点は以下の6点である。スナバ切り替え回路52において、切り替え用コンデンサC56の一端がコンデンサC51とダイオードD11の接続点に接続されている点。切り替え用コンデンサC56の他端が切り替え用PNPトランジスタQ54のコレクタに接続されている点。切り替え用PNPトランジスタQ54のエミッタがIGBT(Q11)のコレクタに接続されている点。切り替え用PNPトランジスタQ54のベースが抵抗R58(第9の抵抗)を介してIGBT(Q11)のコレクタおよび、NPNトランジスタQ55(第3のNPNトランジスタ)のコレクタに接続されている点。NPNトランジスタQ55のエミッタが接地されている点。NPNトランジスタQ55のベースが抵抗R57(第10の抵抗)を介して接地されており、コンデンサC12(第5のコンデンサ)を介して入力信号Vinに接続されている点である。その他の構成は、図4に示した実施例2と同様であるので、同じ構成要素には同じ符号を付与して、重複する説明を省略する。

【0078】

次に、スナバ切り替え回路52の動作を図8を用いて説明する。IGBT(Q11)のターンオフ時の電圧上昇速度dv/dt(101)と、dv/dt抑制・スナバ回路51の負帰還量は、コンデンサと抵抗により決まる時定数に依存している。適した電圧上昇速度dv/dtを得るために、例えば、コンデンサ容量として35pFが用いられ、抵抗値として20Ωが用いられる。

【0079】

一方、IGBT(Q11)がターンオンするタイミングは、ユニポーラ型の還流ダイオードD12は遮断するタイミングとなる。電流が遮断する際に、上記の時定数をそのまま用いると、図8(c)のVdiに示すようなリンギングを生じてしまう。このリンギングは時定数をCRスナバとしての動作に適した値にすることで抑制することができる。その時の値はおおよそリンギング周波数をfとすると、おおよそf=1/(2πCR)を満たし、例えば、コンデンサ容量として700pFが用いられ、抵抗値として20Ωが用いられる。

【0080】

このように、IGBT(Q11)のターンオフ時のIGBT(Q11)の電圧上昇速度dv/dt(101)を適した値にするCR時定数と、IGBT(Q11)のターンオン時の還流ダイオードD12に発生するリンギング抑制に適するCR時定数は異なる。

【0081】

本実施例のスナバ切り替え回路52は、IGBT(Q11)がターンオフする際には、CR時定数はコンデンサC51とコンデンサC56の並列容量、ベース抵抗R12によって決まり、IGBT(Q11)がターンオンする際にはCR時定数はコンデンサC51と、ベース抵抗R52のみによって決まるようにする回路である。

【0082】

スナバ切り替え回路52の動作を示す図8において、図8(a)は入力信号Vin、(b)はIGBT(Q11)のコレクタ−エミッタ間電圧Vce、(c)はダイオードD12の電圧Vdi、(d)はC点の電圧、(e)はNPNトランジスタQ55のコレクタ電流I51、(f)はCR時定数である。

【0083】

入力信号VinをLからHへ変化させると(時刻t18)、抵抗R57とコンデンサC抵抗R57とコンデンサC52の接続点Cの電圧は、図8(d)に示すように、GNDから上昇する。これは、抵抗R57とコンデンサC52が微分回路を形成しているからであり、その上昇している時間は抵抗R57とコンデンサC52による時定数により決まる。このGNDから上昇した電圧は、NPNトランジスタQ55のベース電圧Vb55になっており、Vb55が約0.6Vよりも大きいときには、NPNトランジスタQ55は導通状態になる。そうすると、NPNトランジスタQ55のコレクタに接続された抵抗R58に電流が流れる。この抵抗R58に流れる電流I51の波形を図8(e)に示した。

【0084】

抵抗R58に電流が流れることで電圧降下が生じる。この電圧は切り替え用PNPトランジスタQ54のベース電圧Vb54になっている。すなわち、入力信号VinをLからHへ変化させる時(IGBT(Q11)のターンオン時)から一定の時間は、切り替え用PNPトランジスタQ54が導通状態になり、回路の時定数はコンデンサC51と切り替え用コンデンサC56との並列容量と、ベース抵抗R12によって決まる。例えば、コンデンサC51を35pF、切り替え用コンデンサC56を665pF、プルダウン抵抗R15を20Ω、ベース抵抗R12を20Ωとすると、時定数は(35+665)pFと20Ωによって決まる値になる。

【0085】

一方、入力信号VinをHからLへ変化させた時(時刻t19)は、抵抗R57とコンデンサC52の接続点Cの電圧は図8(d)に示すように、GNDよりも電圧が減少する。そのため、NPNトランジスタQ55は導通状態にならないため、切り替え用PNPトランジスタQ54も導通状態にならない。そのため、切り替え用コンデンサC56に電流が流れることはない。結果的に、入力信号VinをHからLへ変化させるとき(IGBT(Q11)のターンオフ時)は、回路の時定数はコンデンサC51とベース抵抗R12のみによって決まる。例えば、上記のようにコンデンサC51を35pF、プルダウン抵抗R15を20Ω、ベース抵抗R20Ωとすると、時定数は35pFと20Ωによって決まる値となる。

【0086】

時定数の変化を図8(f)に示す。このように、IGBT(Q11)のターンオフ時とターンオン時で時定数を変化させることができ、dv/dt抑制・スナバ回路51の負帰還量とスナバ時定数をそれぞれに適した値にすることができる。

【0087】

なお本実施例の変形例として、コンデンサを変化させるのと同時に、PNPトランジスタQ12のベース抵抗を実施例2、実施例3のように変化させて、dv/dt抑制・スナバ回路51の負帰還量とスナバ時定数をそれぞれ適した値になるように選んでもよい。

【0088】

以上説明したように本実施例によれば、電圧駆動素子のターンオン時とターンオフ時でスナバ時定数を決定するコンデンサの値を変化させることで、電圧駆動素子のゲート電荷放電速度を緩和することができ、還流ダイオードにユニポーラ型ダイオードを用いた場合でも、サージ電圧やリンギングを抑制することができ、電圧駆動素子の誤動作を防止することができるという効果がある。

【0089】

また本実施例によれば、外付けCRスナバ回路よりも損失を低減して、駆動回路の信頼性を向上させることができるという効果がある。

【0090】

さらに、実施例4においては、電圧駆動素子のターンオフ時の駆動回路50の寄生容量を減らすことができるため、さらに損失を低減することができる。

【0091】

なお、本実施例において、Q13およびQ55がNPNトランジスタ、Q12およびQ54がPNPトランジスタである例を示したが、バイポーラ型トランジスタだけでなく、Q13およびQ55がNチャンネルMOSFET、Q12およびQ54がPチャンネルMOSFETであってもよい。その場合には、それぞれ、ベースがゲート、コレクタがドレイン、エミッタがソースに対応する。

【実施例5】

【0092】

図9は、本発明に係る電圧駆動素子の駆動回路の実施例5の回路図である。本実施例の駆動回路70は、dv/dt抑制・スナバ回路71と、スナバ切り替え回路72とを備える。本実施例の特徴は、コンデンサC71(第1のコンデンサ)と切り替え用コンデンサC76(第6のコンデンサ)とを直列接続し、切り替え用コンデンサC76と並列に接続された切り替え用PNPトランジスタQ54(第5のPNPトランジスタ)のエミッタ−コレクタ間をオン/オフすることにより時定数を変更している点である。

【0093】

実施例4と異なる点は、スナバ切り替え回路72において、切り替え用コンデンサC76がコンデンサC71に直列に、IGBT(Q11)のコレクタとの間に入っている点と、切り替え用PNPトランジスタQ54のコレクタを切り替え用コンデンサC76とコンデンサC71の接続点に接続している点である。その他の構成は、図7に示した実施例4と同様であるので、同じ構成要素には同じ符号を付与して、重複する説明を省略する。

【0094】

動作においては、図8に示すように、入力信号VinをLからHに変化させた時(時刻t18)にNPNトランジスタQ55(第4のNPNトランジスタ)にベース電圧Vb55が印加される。NPNトランジスタQ55のコレクタ電流I51が流れるタイミングは、実施例4と同じである。異なる点は、コレクタ電流I51は抵抗58に流れて、切り替え用PNPトランジスタQ54のベース電圧を発生して切り替え用PNPトランジスタQ54を導通状態にし、切り替え用コンデンサC76をバイパスするようになる点である。すなわち、入力信号VinをLからHへ変化させる時(IGBT(Q11)のターンオン時)から一定の時間は、切り替え用PNPトランジスタQ54が導通状態になり切り替え用コンデンサC76をバイパスするので、回路の時定数はコンデンサC71とベース抵抗R12のみによって決まる。例えばコンデンサC71を700pF、切り替え用コンデンサC76を35pF、プルダウン抵抗R15を20Ω、ベース抵抗R12を20Ωとすると、時定数は700pFと20Ωによって決まる値になる。

【0095】

一方、入力信号をHからLに変化させたとき(時刻t19)は、実施例4と同様に、NPNトランジスタQ55は導通状態にならないため、切り替え用PNPトランジスタQ54も導通状態にならない。そのため、切り替え用コンデンサC76はバイパスされない。結果的に、入力信号VinをHからLへ変化させる時(IGBT(Q11)のターンオフ時)は、回路の時定数はコンデンサC71と切り替えコンデンサC76との直列容量と、ベース抵抗R12によって決まる。例えば、上記のようにコンデンサC71を700pF、切り替え用コンデンサC76を35pF、プルダウン抵抗R15を20Ω、ベース抵抗R12を20Ωとすると、時定数はおおよそ35pFと20Ωによって決まる値となる。

【0096】

時定数の変化は実施例4と同様に図8(f)に示す。このように、IGBT(Q11)のターンオフ時とターンオン時で時定数を変化させることができ、dv/dt抑制・スナバ回路71の負帰還量とスナバ時定数をそれぞれ適した値にすることができる。

【0097】

なお本実施例の変形例として、コンデンサを変化させるのと同時に、PNPトランジスタQ12のベース抵抗を実施例2、実施例3のように変化させて、dv/dt抑制・スナバ回路71の負帰還量とスナバ時定数をそれぞれ適した値になるように選んでもよい。

【0098】

以上説明したように本実施例によれば、電圧駆動素子のターンオン時とターンオフ時でスナバ時定数を決定するコンデンサの値を変化させることで、電圧駆動素子のゲート電荷放電速度を緩和することができ、還流ダイオードにユニポーラ型ダイオードを用いた場合でも、サージ電圧やリンギングを抑制することができ、電圧駆動素子の誤動作を防止することができるという効果がある。

【0099】

また本実施例によれば、外付けCRスナバ回路よりも損失を低減して、駆動回路の信頼性を向上させることができるという効果がある。

【0100】

なお、本実施例において、Q13およびQ55がNPNトランジスタ、Q12およびQ54がPNPトランジスタである例を示したが、バイポーラ型トランジスタだけでなく、Q13およびQ55がNチャンネルMOSFET、Q12およびQ54がPチャンネルMOSFETであってもよい。その場合には、それぞれ、ベースがゲート、コレクタがドレイン、エミッタがソースに対応する。

【実施例6】

【0101】

図10は、本発明に係る電圧駆動素子の駆動回路の実施例6である駆動回路10を用いたソレノイド駆動回路を示す回路図である。本実施例は、ソレノイドや電磁クラッチ等の誘導性負荷を駆動する電圧駆動素子の駆動回路に適用した実施例である。

【0102】

図10において、電源電圧VBには、誘導性負荷であるソレノイドL11の一端及び還流ダイオードD12のカソードが接続されている。ソレノイドL11の他端と還流ダイオードD12のアノードは、電圧駆動素子であるIGBT(Q11)の一方の主電極であるコレクタに接続されている。IGBT(Q11)の他方の主電極であるエミッタは接地されている。IGBT(Q11)のゲートは、駆動回路10に接続されている。ここで、還流ダイオードD12は、ショットキバリアダイオード等のユニポーラ型のダイオードである。

【0103】

駆動回路10は、IGBT(Q11)のゲートを駆動するコンプリメンタリ型のエミッタフォロア回路を含むdv/dt抑制・スナバ回路11を備える。

【0104】

dv/dt抑制・スナバ回路11は、コレクタが接地されたPNPトランジスタQ12(第1のPNPトランジスタ)と、コレクタが電源電圧Vccに接続されたNPNトランジスタQ13と、ベース抵抗R12(第1の抵抗)と、ベースR14と、抵抗R19(第2の抵抗)と、エミッタ抵抗R11,R13と、コンデンサC11(第1のコンデンサ)と、ダイオードD11(第1のダイオード)と、ダイオードD14(第2のダイオード)と、プルダウン抵抗R15とを備える。

【0105】

入力信号Vinは、ベース抵抗R12,R14を介して、それぞれPNPトランジスタQ12のベースとNPNトランジスタQ13のベースに接続されている。PNPトランジスタQ12のエミッタとNPNトランジスタQ13のエミッタとは、それぞれエミッタ抵抗R11,R13を介して、IGBT(Q11)のゲートに接続されている。また、入力信号Vinは図示しない外部回路により、電源電圧VccをHレベル、GND電位をLレベルとしたPWM信号が入力されている。

【0106】

コンデンサC11の一端は、IGBT(Q11)のコレクタに接続され、コンデンサC11の他端は、ダイオードD11のアノードに接続されている。コンデンサC11とダイオードD11のアノードとの接続点を点Aと呼ぶ。ダイオードD11のカソードは、抵抗R19の一端に接続されている。抵抗R19の他端はPNPトランジスタQ12のベースに接続されている。つまり電流はコンデンサC11側からPNPトランジスタQ12のベース側へ流れる方向に規制される。さらに点Aには、ダイオードD14のカソードが接続され、ダイオードD14のアノードはプルダウン抵抗R15を介して接地されている。

【0107】

次に、図10に示した駆動回路10の動作を、図3を用いて説明する。図3は入力信号Vinを変化させてIGBT(Q11)のオン/オフを繰り返したときにおける各部の電圧波形を示す図である。図3(a)は入力信号Vin、(b)はIGBT(Q11)のコレクタ−エミッタ間電圧Vce、(c)はPNPトランジスタQ12のベース電圧Vb、(d)はA点の電圧である。

【0108】

入力信号VinをLからHへ変化させると、若干の遅延の後、IGBT(Q11)はターンオン動作に入る(時刻t11)。この際、IGBT(Q11)のコレクタ−エミッタ間電圧Vceは低下していく。すなわち、負のdv/dtが発生する(時刻t11〜t12)。この負のdv/dtにより、コンデンサC11にはA点からIGBT(Q11)のコレクタに向かって電流が流れる。この電流は、プルダウン抵抗R15とダイオードD14を介してGNDから供給されるため、A点の電位はプルダウン抵抗R15の電圧降下分だけ下がり、負の電位となるが、ダイオードD11が存在するため、PNPトランジスタQ12のベースに負電圧が印加されることはない。

【0109】

したがって、ベース抵抗R12やコンデンサC11の値にかかわらず、PNPトランジスタQ12が破壊されるおそれはない。また、ターンオン終了(時刻t12)後、A点の電位はプルダウン抵抗R15とコンデンサC11によって決まる時定数で初期状態である0V近傍へ復帰して行く。プルダウン抵抗R15の値としては、速やかに0V近傍へ復帰させるため、時定数が小さくなるような値が選ばれる。

【0110】

次に、入力信号VinをHからLへ変化させると、若干の遅延の後、IGBT(Q11)はターンオフ動作に入る(時刻t13)。この際、IGBT(Q11)のコレクタ−エミッタ間電圧Vceは上昇していく。すなわち、正のdv/dtが発生する。この正のdv/dtにより、コンデンサC11には、IGBT(Q11)のコレクタからA点に向かって電流が流れる。この電流はA点からダイオードD11および抵抗R19を介して、PNPトランジスタQ12のベース抵抗R12へ流れ込むため、ベース抵抗R12で電圧が発生し、PNPトランジスタQ12のベース電圧Vbは上昇する。この電圧上昇速度は、コンデンサC11とベース抵抗R12によって決まる時定数により決定され、上昇電圧はベース抵抗R12と抵抗R19で分圧される。

【0111】

IGBT(Q11)のVceに発生するdv/dtは、IGBT(Q11)のターンオフ速度によって決まる。IGBT(Q11)のターンオフ速度は、ゲート電荷の放電速度すなわちゲート電流Ig(off)の大きさで調整可能であり、ゲート電流Ig(off)は、ゲート電圧をVgとし、PNPトランジスタQ12のベース電圧をVbとし、PNPトランジスタQ12のベースに対するエミッタ電圧をVfとしたときに、式(4)で表すことができる。

Ig(off)=(Vg−Vb−Vf)/R11 …(4)

【0112】

したがってベース電圧Vbの上昇によって、ゲート電流Ig(off)が減少し、IGBT(Q11)のゲート電荷放電速度が緩和されることになる。この負帰還作用により、コンデンサC11、ベース抵抗R12、ゲート抵抗R11によって決まる所定のdv/dt(101)に一致するように、IGBT(Q11)のターンオフ動作が制御され、過大なサージ電圧の発生を抑えることができる。サージ電圧の消滅時(時刻t14〜t15)には、ターンオン時同様、負のdv/dtが発生するが、前述のターンオン時と同じ理由で、PNPトランジスタQ12のベースに負の電圧が印加されることはない。

【0113】

尚、本実施例では、必要な回路定数の設定方法を省略したが、実施例1に記載の方法により同様に設定することができる。

【0114】

駆動回路の基板上にスナバ回路を設置する場合、スナバの損失は抵抗のサイズ低減の観点で重要な意味を持つ。抵抗のサイズは許容損失で決まり、許容損失が大きい抵抗はサイズも大きく、はんだ接合の信頼性上、好ましくない。本実施例はスナバ回路で発生する損失を減らせるため、抵抗のサイズを小さくでき、はんだ接合の信頼性を向上させることができる。

【0115】

次に、本実施例の変形例を説明する。図10に示した駆動回路10に代えて、図4に示した実施例2の駆動回路15、図6に示した実施例3の駆動回路30、図7に示した実施例4の駆動回路50、図9に示した実施例5の駆動回路70の何れかを用いることができる。これらの駆動回路により図10のIGBT(Q11)を駆動しても、本実施例と同様の効果を得ることができるのは明らかである。

【0116】

以上説明したように本実施例によれば、電圧駆動素子のターンオフ時にはコンデンサC11からフィードバックされる電圧のうち、ベース抵抗R12と抵抗R19で分圧した一部の電圧をゲート駆動素子に入力することで、適度に電圧駆動素子のゲート電荷放電速度を緩和することができ、電圧駆動素子のdv/dtが抑制されることでサージ電圧を抑制できる。さらに電圧駆動素子のターンオン時においては、ユニポーラ型ダイオードを還流ダイオードを還流ダイオードD12に用いた場合でも、ダイオードのハードなスイッチングによる急峻な変化電流はコンデンサC11を通ってベース抵抗R12と抵抗R19の両方を流れ、合算した抵抗値でスナバ回路が形成される。従って、スナバ回路としても適当な回路定数となり、リンギングを抑制することができ、電圧駆動素子の誤動作を防止することができるという効果がある。

【0117】

また本実施例によれば、外付けCRスナバ回路よりも損失を低減して、駆動回路の信頼性を向上させることができるという効果がある。

【0118】

なお、本実施例において、Q13がNPNトランジスタ、Q12がPNPトランジスタである例を示したが、バイポーラ型トランジスタだけでなく、Q13がNチャンネルMOSFET、Q12がPチャンネルMOSFETであってもよい。その場合には、それぞれ、ベースがゲート、コレクタがドレイン、エミッタがソースに対応する。

【0119】

なお、本実施例では還流ダイオードD12にユニポーラ型ダイオードを例にした場合で説明したが、ユニポーラ型ダイオードと同様に、従来のスイッチング回路において電流遮断時にリンギングを生じる虞があるような素子であってもよい。例えば、ハードな(急峻な)リカバリ特性を持つバイポーラ型ダイオードであってもよい。

【符号の説明】

【0120】

10、15、30、50、70…駆動回路

11、21、31、51、71…dv/dt抑制・スナバ回路

12、32、52、72…スナバ切り替え回路

Q10、Q11…IGBT

D12、D13…還流ダイオード

R11、R12、R13、R14、R17、R18、R19…抵抗

R15…プルダウン抵抗

R16、R36…切り替え用抵抗

R32、R38、R57、R58…抵抗

C11、C12、C51、C71…コンデンサ

C56、C76…切り替え用コンデンサ

D11、D14…ダイオード

Q12、Q15…PNPトランジスタ

Q13、Q55…NPNトランジスタ

Q14…切り替え用NPNトランジスタ

Q54…切り替え用PNPトランジスタ

Vin…入力信号

【特許請求の範囲】

【請求項1】

2つの主電極間に流れる電流がゲート電圧で制御される電圧駆動素子に誘導性の負荷と還流ダイオードとが接続され、電圧駆動素子のゲートと接地間に第1のPNPトランジスタ又はPチャンネルMOSFETが接続され、電圧駆動素子のゲート電荷を第1のPNPトランジスタ又はPチャンネルMOSFETを介して放電することにより、電圧駆動素子をターンオフする電圧駆動素子の駆動回路において、電圧駆動素子の非接地側の主電極に第1のコンデンサの一端を接続し、第1のコンデンサの他端を第1のダイオードのアノードに接続し、第1のダイオードのカソードを第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートに接続し、第1のコンデンサの他端と接地間にプルダウン抵抗及び第2のダイオードを直列接続したプルダウン回路を接続し、第2のダイオードはアノード端子が接地側を向いており、第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートと入力信号端子との間には第1の抵抗が接続され、第1の抵抗と第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートとの接続点から、第1のコンデンサの他端とプルダウン回路との接続点までの間に、第1のダイオードに直列接続される第2の抵抗を備えたことを特徴とする電圧駆動素子の駆動回路。

【請求項2】

前記還流ダイオードは、ユニポーラ型ダイオードであることを特徴とする請求項1に記載の電圧駆動素子の駆動回路。

【請求項3】

前記電圧駆動素子のターンオフ時もしくはターンオン時に第1の抵抗と第1のコンデンサの少なくともいずれか一方の値を変化させることを特徴とする請求項1または請求項2に記載の電圧駆動素子の駆動回路。

【請求項4】

第1の抵抗と第1のコンデンサの少なくともいずれか一方に、それぞれ同種の部品を並列もしくは直列に接続することにより、合成値を可変とすることを特徴とする請求項3に記載の電圧駆動素子の駆動回路。

【請求項5】

前記電圧駆動素子のゲート電圧の立ち上がりもしくは立下りに同期して、一定の時間、前記合成値を変化させることを特徴とする請求項4に記載の電圧駆動素子の駆動回路。

【請求項6】

第1の抵抗に少なくとも1つのバイパス配線が接続されており、

バイパス配線には任意の数の抵抗が接続されており、

第1の抵抗もしくはバイパス配線に、自身に流れる電流を遮断するスイッチ素子が接続されていることを特徴とする請求項3乃至請求項5の何れか1項に記載の電圧駆動素子の駆動回路。

【請求項7】

第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートに第3の抵抗の一端が接続されており、

第3の抵抗の他端を第1のNPNトランジスタのコレクタ又はNチャンネルMOSFETのドレインに接続し、

第1のNPNトランジスタのエミッタ又はNチャンネルMOSFETのソースを接地し、

第1のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第4の抵抗を介して接地されており、

第1のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第2のPNPトランジスタのコレクタ又はPチャンネルMOSFETのドレインに接続されており、

第2のPNPトランジスタのエミッタ又はPチャンネルMOSFETのソースは電源に接続されており、

第2のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第5の抵抗を介して電源に接続されており、

第2のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第2のコンデンサを介して入力信号端子に接続されていることを特徴とする請求項3乃至請求項6の何れか1項に記載の電圧駆動素子の駆動回路。

【請求項8】

第1の抵抗に少なくとも1つの抵抗が直列に接続されており、

第1の抵抗および前記直列接続した抵抗のうち、少なくとも1つの抵抗にはバイパスする配線が接続されており、

バイパスする配線にはスイッチ素子が接続されていることを特徴とする請求項3乃至請求項5の何れか1項に記載の電圧駆動素子の駆動回路。

【請求項9】

第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートに接続された第1の抵抗に直列に第6の抵抗が接続されており、

第6の抵抗の一端は入力信号端子に接続されており、

第1の抵抗と第6の抵抗の接続点は第2のNPNトランジスタのコレクタ又はNチャンネルMOSFETのドレインに接続されており、

第2のNPNトランジスタのエミッタ又はNチャンネルMOSFETのソースは入力信号端子に接続されており、

第2のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第7の抵抗を介して入力信号端子に接続されており、

第2のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第3のPNPトランジスタのコレクタ又はPチャンネルMOSFETのドレインに接続されており、

第3のPNPトランジスタのエミッタ又はPチャンネルMOSFETのソースは電源に接続されており、

第3のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第8の抵抗を介して電源に接続されており、

第3のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第3のコンデンサを介して入力信号端子に接続されていることを特徴とする請求項3乃至請求項5の何れか1項または請求項7に記載の電圧駆動素子の駆動回路。

【請求項10】

第1のコンデンサに少なくとも1つのバイパス配線が並列に接続されており、

バイパス配線には少なくとも1つのコンデンサが接続されており、

第1のコンデンサもしくはバイパス配線に、自身に流れる電流を遮断するスイッチ素子が接続されていることを特徴とする請求項3乃至請求項9の何れか1項に記載の電圧駆動素子の駆動回路。

【請求項11】

前記第1のコンデンサと前記第1のダイオードとの直列回路における接続点に第4のコンデンサの一端が接続されており、

第4のコンデンサの他端に第4のPNPトランジスタのコレクタ又はPチャンネルMOSFETのドレインが接続されており、

第4のPNPトランジスタのエミッタ又はPチャンネルMOSFETのソースは前記電圧駆動素子の非接地側主電極に接続されており、

第4のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第9の抵抗を介して前記電圧駆動素子の非接地側主電極に接続されており、

第4のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第3のNPNトランジスタのコレクタ又はNチャンネルMOSFETのドレインに接続されており、

第3のNPNトランジスタのエミッタ又はNチャンネルMOSFETのソースは接地されており、

第3のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第10の抵抗を介して接地されており、

第3のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第5のコンデンサを介して入力信号端子に接続されていることを特徴とする請求項3乃至請求項10の何れか1項に記載の電圧駆動素子の駆動回路。

【請求項12】

第1のコンデンサに少なくとも1つのコンデンサが直列に接続されており、

第1のコンデンサおよび前記直列接続したコンデンサのうち、少なくとも1つのコンデンサにはバイパスする配線が接続されており、

バイパスする配線にはスイッチ素子が接続されていることを特徴とする請求項3乃至請求項9の何れか1項に記載の電圧駆動素子の駆動回路。

【請求項13】

前記第1のコンデンサに直列に第6のコンデンサが接続されており、

第1のコンデンサと第6のコンデンサの接続点には第5のPNPトランジスタのコレクタ又はPチャンネルMOSFETのドレインが接続されており、

第5のPNPトランジスタのエミッタ又はPチャンネルMOSFETのソースは前記電圧駆動素子の非接地側の主電極に接続されており、

第5のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第11の抵抗を介して電圧駆動素子の非接地側の主電極に接続されており、

第5のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第4のNPNトランジスタのコレクタ又はNチャンネルMOSFETのドレインに接続されており、

第4のNPNトランジスタのエミッタ又はNチャンネルMOSFETのソースは接地されており、

第4のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第12の抵抗を介して接地されており、

第4のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第7のコンデンサを介して入力信号端子に接続されていることを特徴とする請求項3乃至請求項9の何れか1項または請求項12に記載の電圧駆動素子の駆動回路。

【請求項1】

2つの主電極間に流れる電流がゲート電圧で制御される電圧駆動素子に誘導性の負荷と還流ダイオードとが接続され、電圧駆動素子のゲートと接地間に第1のPNPトランジスタ又はPチャンネルMOSFETが接続され、電圧駆動素子のゲート電荷を第1のPNPトランジスタ又はPチャンネルMOSFETを介して放電することにより、電圧駆動素子をターンオフする電圧駆動素子の駆動回路において、電圧駆動素子の非接地側の主電極に第1のコンデンサの一端を接続し、第1のコンデンサの他端を第1のダイオードのアノードに接続し、第1のダイオードのカソードを第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートに接続し、第1のコンデンサの他端と接地間にプルダウン抵抗及び第2のダイオードを直列接続したプルダウン回路を接続し、第2のダイオードはアノード端子が接地側を向いており、第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートと入力信号端子との間には第1の抵抗が接続され、第1の抵抗と第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートとの接続点から、第1のコンデンサの他端とプルダウン回路との接続点までの間に、第1のダイオードに直列接続される第2の抵抗を備えたことを特徴とする電圧駆動素子の駆動回路。

【請求項2】

前記還流ダイオードは、ユニポーラ型ダイオードであることを特徴とする請求項1に記載の電圧駆動素子の駆動回路。

【請求項3】

前記電圧駆動素子のターンオフ時もしくはターンオン時に第1の抵抗と第1のコンデンサの少なくともいずれか一方の値を変化させることを特徴とする請求項1または請求項2に記載の電圧駆動素子の駆動回路。

【請求項4】

第1の抵抗と第1のコンデンサの少なくともいずれか一方に、それぞれ同種の部品を並列もしくは直列に接続することにより、合成値を可変とすることを特徴とする請求項3に記載の電圧駆動素子の駆動回路。

【請求項5】

前記電圧駆動素子のゲート電圧の立ち上がりもしくは立下りに同期して、一定の時間、前記合成値を変化させることを特徴とする請求項4に記載の電圧駆動素子の駆動回路。

【請求項6】

第1の抵抗に少なくとも1つのバイパス配線が接続されており、

バイパス配線には任意の数の抵抗が接続されており、

第1の抵抗もしくはバイパス配線に、自身に流れる電流を遮断するスイッチ素子が接続されていることを特徴とする請求項3乃至請求項5の何れか1項に記載の電圧駆動素子の駆動回路。

【請求項7】

第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートに第3の抵抗の一端が接続されており、

第3の抵抗の他端を第1のNPNトランジスタのコレクタ又はNチャンネルMOSFETのドレインに接続し、

第1のNPNトランジスタのエミッタ又はNチャンネルMOSFETのソースを接地し、

第1のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第4の抵抗を介して接地されており、

第1のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第2のPNPトランジスタのコレクタ又はPチャンネルMOSFETのドレインに接続されており、

第2のPNPトランジスタのエミッタ又はPチャンネルMOSFETのソースは電源に接続されており、

第2のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第5の抵抗を介して電源に接続されており、

第2のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第2のコンデンサを介して入力信号端子に接続されていることを特徴とする請求項3乃至請求項6の何れか1項に記載の電圧駆動素子の駆動回路。

【請求項8】

第1の抵抗に少なくとも1つの抵抗が直列に接続されており、

第1の抵抗および前記直列接続した抵抗のうち、少なくとも1つの抵抗にはバイパスする配線が接続されており、

バイパスする配線にはスイッチ素子が接続されていることを特徴とする請求項3乃至請求項5の何れか1項に記載の電圧駆動素子の駆動回路。

【請求項9】

第1のPNPトランジスタのベース又はPチャンネルMOSFETのゲートに接続された第1の抵抗に直列に第6の抵抗が接続されており、

第6の抵抗の一端は入力信号端子に接続されており、

第1の抵抗と第6の抵抗の接続点は第2のNPNトランジスタのコレクタ又はNチャンネルMOSFETのドレインに接続されており、

第2のNPNトランジスタのエミッタ又はNチャンネルMOSFETのソースは入力信号端子に接続されており、

第2のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第7の抵抗を介して入力信号端子に接続されており、

第2のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第3のPNPトランジスタのコレクタ又はPチャンネルMOSFETのドレインに接続されており、

第3のPNPトランジスタのエミッタ又はPチャンネルMOSFETのソースは電源に接続されており、

第3のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第8の抵抗を介して電源に接続されており、

第3のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第3のコンデンサを介して入力信号端子に接続されていることを特徴とする請求項3乃至請求項5の何れか1項または請求項7に記載の電圧駆動素子の駆動回路。

【請求項10】

第1のコンデンサに少なくとも1つのバイパス配線が並列に接続されており、

バイパス配線には少なくとも1つのコンデンサが接続されており、

第1のコンデンサもしくはバイパス配線に、自身に流れる電流を遮断するスイッチ素子が接続されていることを特徴とする請求項3乃至請求項9の何れか1項に記載の電圧駆動素子の駆動回路。

【請求項11】

前記第1のコンデンサと前記第1のダイオードとの直列回路における接続点に第4のコンデンサの一端が接続されており、

第4のコンデンサの他端に第4のPNPトランジスタのコレクタ又はPチャンネルMOSFETのドレインが接続されており、

第4のPNPトランジスタのエミッタ又はPチャンネルMOSFETのソースは前記電圧駆動素子の非接地側主電極に接続されており、

第4のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第9の抵抗を介して前記電圧駆動素子の非接地側主電極に接続されており、

第4のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第3のNPNトランジスタのコレクタ又はNチャンネルMOSFETのドレインに接続されており、

第3のNPNトランジスタのエミッタ又はNチャンネルMOSFETのソースは接地されており、

第3のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第10の抵抗を介して接地されており、

第3のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第5のコンデンサを介して入力信号端子に接続されていることを特徴とする請求項3乃至請求項10の何れか1項に記載の電圧駆動素子の駆動回路。

【請求項12】

第1のコンデンサに少なくとも1つのコンデンサが直列に接続されており、

第1のコンデンサおよび前記直列接続したコンデンサのうち、少なくとも1つのコンデンサにはバイパスする配線が接続されており、

バイパスする配線にはスイッチ素子が接続されていることを特徴とする請求項3乃至請求項9の何れか1項に記載の電圧駆動素子の駆動回路。

【請求項13】

前記第1のコンデンサに直列に第6のコンデンサが接続されており、

第1のコンデンサと第6のコンデンサの接続点には第5のPNPトランジスタのコレクタ又はPチャンネルMOSFETのドレインが接続されており、

第5のPNPトランジスタのエミッタ又はPチャンネルMOSFETのソースは前記電圧駆動素子の非接地側の主電極に接続されており、

第5のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第11の抵抗を介して電圧駆動素子の非接地側の主電極に接続されており、

第5のPNPトランジスタのベース又はPチャンネルMOSFETのゲートは第4のNPNトランジスタのコレクタ又はNチャンネルMOSFETのドレインに接続されており、

第4のNPNトランジスタのエミッタ又はNチャンネルMOSFETのソースは接地されており、

第4のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第12の抵抗を介して接地されており、

第4のNPNトランジスタのベース又はNチャンネルMOSFETのゲートは第7のコンデンサを介して入力信号端子に接続されていることを特徴とする請求項3乃至請求項9の何れか1項または請求項12に記載の電圧駆動素子の駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2011−55695(P2011−55695A)

【公開日】平成23年3月17日(2011.3.17)

【国際特許分類】

【出願番号】特願2010−89541(P2010−89541)

【出願日】平成22年4月8日(2010.4.8)

【出願人】(000003997)日産自動車株式会社 (16,386)

【Fターム(参考)】

【公開日】平成23年3月17日(2011.3.17)

【国際特許分類】

【出願日】平成22年4月8日(2010.4.8)

【出願人】(000003997)日産自動車株式会社 (16,386)

【Fターム(参考)】

[ Back to top ]