電子デバイスパッケージとその形成方法

【課題】光電子デバイス、IC又はMEMSデバイスなどの電子デバイスを1つ以上含んでいる密封パッケージの電子産業に応用される電子デバイスパッケージとその形成方法を提供する。

【解決手段】電子デバイスパッケージは、基体4に取り付けられた電子デバイス28と、導電性ビア18と、この基体上の局所的に薄くされた領域を含む。

【解決手段】電子デバイスパッケージは、基体4に取り付けられた電子デバイス28と、導電性ビア18と、この基体上の局所的に薄くされた領域を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般的にはマイクロ加工技術に関し、詳しくは、電子デバイスパッケージとその形成方法に関する。本発明は、例えば、光電子デバイス、ICまたはMEMSデバイスなどの電子デバイスを1つ以上含んでいる密封パッケージの電子産業に応用される。

【背景技術】

【0002】

例えば、集積回路(IC)、光電子デバイス、微小電気機械システム(MEMS)などの電子デバイスを含んでいる密封されたチップスケールパッケージとウエハレベルパッケージが知られている。このようなパッケージは多くの場合、ベース基体と蓋の間に形成されて密封された封入体積を包含しており、この封入体積中に電子デバイスが配置されている。このパッケージは、封入されたデバイスを閉じこめ、パッケージの外部の環境中に存在する汚染物質や水蒸気から、封入されたデバイスの保護を提供する。パッケージ中に汚染物質や水蒸気が存在すると、例えば、金属部分の腐食や、光電子デバイス、光MEMSおよび他の光部品の場合における光学的損失などの問題が発生しかねない。加えて、このようなパッケージは時として、正しく動作させるためにまたはそのデバイスの所望の寿命を達成するために、真空または管理された環境下で密封される。

【0003】

パッケージ中に封入された電子デバイスと、外界との間の電気的接続性を提供するためには、パッケージの内部と外部との間に電気的貫通接続が必要である。密封パッケージのためのさまざまなタイプの電気的貫通接続が開示されている。例えば、シェレル(Sherrer)らによる米国特許出願公開第2005/0111797A1号には、導電性のビア(via)を密封された光電子パッケージで用いることが開示されている。光電子デバイスは、例えばケイ素基板などの基体上に配置されて、蓋を基体に取り付けて密封体積中に同封される。導電性ビアは、該基体を突き抜けて延長し、デバイスに電気的接続性を提供する。上記の公開出願の例示されたビア形成プロセスでは、ビアを一方の側から基体の厚さ全体を突き抜けて窒化ケイ素膜までエッチングし、このビアを金属化し、該窒化物はパターニ化されかつ除去され、及びビアを最上面にまで接続して、密封した電気的ビアを作成する。ビアの達成可能な最小サイズは一般に、ビアのエッチングプロセスのアスペクト比と基体の厚さによって制限される。

【0004】

電子デバイスパッケージ内に高密度で詰め込まれた金属化ビアを形成する能力を有することが望ましい。このようにすれば、縮小された形状を有するパッケージを提供することが可能である。これによって、ウエハレベルプロセス(wafer−level process)においてウエハ上に形成され得るパッケージの数を増やすことが可能となるという付加利益がもたらされ、それにより製造コストが軽減される。その上、ビアのサイズの減少が、このビアの構造に関連する寄生インダクタンスおよび/またはキャパシタンスを減少させることに役立ち得、それによりマイクロ波周波数でのビア性能が向上される。

【0005】

国際公開第2006/097842号には、前記ウエハレベルで行われる、光電子デバイスやMEMSデバイスなどの半導体部品を収納するための比較的薄いパッケージを製造する技術が開示されている。この文献では、一実施形態において、貫通接続金属化が提供されかつ裏側にウエハ薄層化技術を含む、同じウエハ上に取り付けられたまたは同じウエハにより集積されたマイクロ部品が開示されている。ケイ素/酸化物/ケイ素型ウエハがこのプロセスでは用いられる。ウエハのデバイス側のケイ素から酸化物のエッチングがストップされる層までマイクロビアが形成される。マイクロ部品が、マイクロビア間のデバイス側上の領域に取り付けられ、半導体またはガラスの蓋ウエハが最初のウエハに結合され、これで、このマイクロ部品がこの2つのウエハにより画定される領域内に収納されるようにする。ウエハを結合した後、薄層化プロセスが最初の層の裏側のケイ素層に対して実行される。

【特許文献1】米国特許出願公開第2005/0111797号明細書

【特許文献2】国際公開第2006/097842号パンフレット

【発明の開示】

【発明が解決しようとする課題】

【0006】

上記のデバイスと方法はさまざまな欠点を有する。ビア並びに精密マイクロ電子機器、例えば、伝送ライン、薄膜パターン化された半田やキャパシタなどの精密マイクロ電子機器を国際公開第2006/097842号におけるようにウエハのデバイス側上に含んでいるウエハの場合、精密リソグラフィと精密パターン化が必要となる。精密リソグラフィでは、薄いフォトレジストがコーティングされ、適切に露光されかつパターン化され得る平面またはほぼ平面の表面が求められる。ウエハの前面上にマイクロ電子機器を形成するより先に、ビアを同じ前面上からエッチングする場合及び同じ前面上に作成する場合、このビアがこのウエハ上でのフォトレジストの適切なスピンコーティングの妨げとなる。その結果、多くの場合、粗末な被覆性及び不整合なパターン化をもたらすこととなる。例えばフォトレジストを噴霧する方法及びフォトレジストを電気メッキする方法などの方法が用いられてきた。しかしながら、前者の方法ではレジストの厚さに一貫性がなくなり、後者の方法では厚さが比較的大きくなってしまうため、これらの方法では、必要とされる高精度パターン化が不可能である。これは、高い産出高でRF伝送ラインや抵抗体などの精密な機能物のパターン化を特に困難もしくは不可能にする。

【0007】

ウエハの前面上でマイクロ電子機器を作成した後に、同じ面から、またはこの面上にビアを製造する場合、このマイクロ電子機器は、このビアを形成するために用いられる処理に耐えなければならない。異方的にエッチングされるビアの場合、これは、典型的に、20分から数時間にわたって攻撃的なアルカリ性エッチに曝されことになり、多くの場合アルカリ性エッチは、マイクロ電子機器で用いられる物質、例えば、半田に用いられる錫、抵抗体で用いられるNi−CrやTaN、及び接着層の形成でしばしば用いられるチタンなどの物質を攻撃する。加えて、マイクロ電子機器の生産で必要とされる多くの処理工程の後でビアを作成すると、産出高が不充分な場合に大幅なコストが生じ得る。

【0008】

したがって、当該技術分野において、最新技術に伴う1以上のかかる問題を解決する改良された電子デバイスパッケージ及びその形成方法の必要性が存在する。

【課題を解決するための手段】

【0009】

本発明の第1の態様によれば、電子デバイスパッケージが提供される。この電子デバイスパッケージは、第1面と該第1面の反対側の第2面とを有する基体を含む。第2面は、その中に局所的に薄くなった領域を有する。この局所的に薄くなった領域中の導電性ビアは、基体を通って第1面まで延長している。この導電性ビアと局所的に薄くなった領域のそれぞれが、テーパー側壁を含み、ここで、導電性ビアの側壁のテーパーと局所的に薄くなった領域の側壁のテーパーは同じ方向である。電子デバイスは基体の第1面上に取り付けられる。この電子デバイスは、導電性ビアに電気的に接続される。

【0010】

本発明の第2の態様による電子デバイスパッケージは、第1面と該第1面の反対側の第2面とを有する基体を含む。第2面は、その中に局所的に薄くなった領域を有する。この局所的に薄くなった領域中の導電性ビアは、基体を通って第1面まで延長している。電子デバイスは基体の第1面上に取り付けられる。この電子デバイスは、導電性ビアに電気的に接続される。フレックス回路が、局所的に薄くなった領域中に少なくとも部分的に配置され、かつ導電性ビアに電気的に接続される。

【0011】

本発明のさらなる態様によれば、電子デバイスパッケージを形成する方法が提供される。本方法は(a)第1面と該第1面の反対側の第2面とを有する基体を提供する工程と;(b)前記基体の一部分を第2面から薄くして、第2面中に局所的に薄くなった領域を形成する工程と;(c)エッチングして前記局所的に薄くなった領域中に基体を通って延長するビアを形成する工程であって、前記エッチングが、その局所的に薄くなった面から第1面の方向に実施される工程と;(d)前記ビアを金属化する工程であって、導電性のビアと前記局所的に薄くなった領域のそれぞれが、テーパー側壁を含み、ここで前記導電性ビアの側壁のテーパーと前記局所的に薄くなった領域の側壁のテーパーが同じ方向である工程と;(e)電子デバイスを前記基体の前記第1面上に取り付ける工程であって、前記電子デバイスが前記導電性ビアに電気的に接続される工程;を含む。

【0012】

本発明のさらに別の態様によれば、電子デバイスパッケージを形成する方法は(a)第1面と該第1面の反対側の第2面とを有する基体を提供する工程と;(b)基体の一部分を前記第2面から薄くして、第2面中に局所的に薄くなった領域を形成する工程と;(c)基体を通って第1面に延長するビアを局所的に薄くなった領域中に形成する工程と;(d)前記ビアを金属化する工程と;(e)電子デバイスを前記基体の第1面上に取り付ける工程であって、電子デバイスが導電性のビアに電気的に接続される工程と;(f)前記局所的に薄くなった領域に少なくとも部分的に配置され、かつ導電性のビアに電気的に接続されたフレックス回路を提供する工程;を含む。

【0013】

この電子デバイスパッケージとその形成方法において、基体は、例えば半導体(例えば単結晶ケイ素など)を含み、及びシリコンウエハもしくはシリコン−オン−インシュレーター(SOI)ウエハまたはその一部という形をとり得る。この電子デバイスは、電子デバイスパッケージ中に密封され得る。1以上の導電性ビア(典型的には複数の導電性ビア)は、局所的に薄くなった領域中に形成される。この局所的に薄くなった領域は、基体の第1の縁にまで延長させてもよく、こうすると、局所的に薄くなった領域中に少なくとも部分的に配置されかつ導電性ビアに電気的に接続されるフレックス回路の提供を可能となり好都合である。蓋を第1面の上に提供して、電子デバイスを封入する密閉された体積を形成してもよい。本発明の例示の態様では、ウエハを局所的に薄くして、基体の同じ側から、複数のビアがこの局所的に薄くなった領域中に形成される。電子デバイスパッケージは、ウエハレベルで形成すると利点があり得、このウエハは、電子デバイスパッケージを各々が含む複数のダイ(die)を有している。

【0014】

本発明の他の特徴及び利点は、以下の記載、特許請求の範囲および添付の図面を読めば当業者には明らかとなる。

【発明を実施するための最良の形態】

【0015】

本発明は、電子デバイスパッケージを形成する改良された方法並びにこれによって形成することができる電子デバイスパッケージを提供する。このパッケージは、その表面に局所的に薄くなった領域を有する基体と、局所的に薄くなった領域中の、基体を通って延長する導電性ビアとを含む。電子デバイスが導電性ビアに電気的に接続される。電子デバイスは、局所的に薄くなった領域と導電性ビアが形成される表面とは反対側の基体表面上に配置され得る。あるいは、電子デバイスは、ビアを含んでいる基体に密封する蓋を形成する別個の基体上に配置され得る。ビアは電子デバイスに電気的に接続される。

【0016】

本明細書で用いる「マイクロ構造体」は、必ずしもウエハレベルではないが、マイクロ加工プロセスやナノ加工プロセスで形成される構造体のことであり、「ウエハレベル」とは複数のダイが形成される任意の基体により行うプロセスのことであるが、このようなダイには、例えば、複数のダイを同じ基体または基体部分を形成する場合には完全なウエハやその一部が含まれる。

【0017】

本発明による電子デバイスパッケージを形成する方法を図1〜14を参照して説明するが、図1〜14は、本発明による例示の電子デバイスパッケージを形成するさまざまな段階でのその断面図を示している。

【0018】

図1に示すように、基体4が提供される。この基体は、第1(デバイス面の、または表の)面8と、該第1面の反対側の第2(裏側の)面10を有する。基体4は、電子デバイスのパッケージングで用いられるのに適した任意の材料、例えば半導体材料、金属、セラミック及びガラスなどから形成され得る。典型的に、基体の材料には、単結晶ケイ素などの単結晶半導体材料、シリコン−オン−インシュレーターまたはケイ素ゲルマニウム基体が含まれる。この基体は、単一の構成要素、または、より典型的には複数のダイのような複数の同じ構成要素を形成することが可能な寸法の基体であり得る。典型的に基体は、複数のダイを有するウエハという形態である。この例示の方法では、<100>両面研磨シリコンウエハを基体として提供する。このウエハの厚さは、約525±25μであれば好都合であり、かつ抵抗率は、典型的には、高周波用途の場合には1000オーム−cmより大きいが、これより低い抵抗率も用いられ得る。

【0019】

ハードマスクとして用いるために、及び場合によっては基体とその上に配置される導線や電子デバイスなどの電気的構造体との間を電気的に隔離するために、基体またはその一部の前面及び裏面上に1つ以上のハードマスク層が提供され得る。典型的には、このハードマスク層は、例えば、スピンオンガラス、酸窒化ケイ素及び二酸化チタンをはじめとする、低ストレス窒化ケイ素、ドープおよび非ドープの酸化ケイ素から選ばれた誘電体層である。このような誘電体層は公知の技術、例えばプラズマ化学気相堆積(PECVD)や低圧化学気相堆積(LPCVD)、スパッタリングやイオンビーム堆積法などの物理的気相堆積(PVD)、スピンコーティング、陽極酸化、熱酸化法などの技術によって形成され得る。誘電体層の厚さは、例えば個々の材料や後続のプロセスの条件などの要因に依存する。誘電体層の典型的な厚さは、100〜250ナノメートル(nm)である。この例示の方法において、低ストレスLPCVD窒化ケイ素層は、例えば200〜500nm(例えば200〜250nmなど)の厚さで、基体の第1と第2面上に提供される。

【0020】

基体の裏面10上に配置された第1のハードマスク層12は、典型的に標準のリソグラフィ技術とドライエッチング技術を用いてパターン化されて、開口部を形成して下層の基体物質を露出させ、これが次に局所的に薄くされる。パターン化されたフォトレジストまたは他の好適な光画像形成可能な物質を、エッチングマスク13として基体の裏面10上に提供し、露光し第1のハードマスク層のこれらの領域を除去する。場合により、結晶配列(crystal alignment)工程を実行して、正確な結晶学的配列軸を決定し、これで、エッチングされるフィーチャーを要求される精度にまで結晶軸に位置合わせすることが可能となるようにしてもよい。基体の裏面上のエッチングマスク13の間の露出された第1のハードマスク層12の領域をドライエッチングで除去して、下層の基体材料を露出させることができる。エッチャントは、例えば、第1のハードマスク層12の材料によって決まる。窒化ケイ素層を用いているこの例示の方法においては、例えば50〜500mTorrの圧力での、CF4や他の好適なフッ素含有エッチャントによるプラズマドライエッチングが典型的である。

【0021】

図3を参照すると分かるように、その後、例えば、基体中にそれぞれの開口部に対して錐体状ピット14が形成されるまで第1のハードマスク層12中の開口部を介して異方性エッチングすることにより基体の裏面10の露出された領域が薄くされる。図3は、第1のハードマスク層の露出された領域を除去した後で、基体4を局所的に薄くして、かつエッチングマスクを除去することを示している。この異方性エッチングは典型的には、例えば、KOHやEDPを用いる結晶学エッチングである。典型的には、ピット14は、基体の前面8から50〜250ミクロンの距離まで伸ばされる。表面全体ではなくて、基体の選択された部分、すなわち部分15だけが薄くされる。これによって、後続の処理及び取り扱いのための機械的剛性が維持され、破損を回避する助けることを可能とする。これは、例えばボールレンズや他の光学的構成要素などの構成要素を保持するために基体の前面に正確にエッチングされた構造体を作成するために十分な厚さが必要とされるマイクロ光学プラットフォームの場合には特に有益である。かかるエッチングされた構造体は、典型的にビアのためにのみ必要とされる薄くされた領域15と同じまたはこれより深くエッチングされてもよい。

【0022】

局所的に薄くされることにより形成された典型的なピット14は、形状が四角である場合に各辺が0.5〜5ミリメートル(mm)の底面を有する。局所的に薄くされた領域は、ダイの側壁1つ以上の長さに達し得る。製造において、これらの領域が、ある寸法において、複数のダイに跨ったり、またはウエハ上の全長に渡ったりしてもよい。ピットの反対側の寸法は、必要とするマイクロビアの数と、フレックス回路および/または半田ボールもしくは半田パッドのどちらかを用いてこのマイクロビアを外部から相互接続するために必要とされるスペースとによって決定され得る。<100>ケイ素の場合、錐体状ピット14の側壁は、異方性ウエットエッチングで作成された場合には{111}結晶平面表面となる。分かっているピットの深さと側壁の角度とに基づいて、第1のハードマスク層12中に形成される目標とする開口部のサイズを計算することが可能である。場合によっては、局所的に薄くすることは、機械的な切削もしくはダイシングによって、ドライエッチングによって、またはウエットエッチングとドライエッチングの組み合わせによって実行してもよい。

【0023】

局所的に薄くする過程において、開口部に隣接している領域において第1のハードマスク層12が、開口部の側部に窒化物の棚形状(図示せず)が形成される結果となるアンダーカットの状態になる場合がある。ピットの14の表面を金属化する前に、この窒化物の棚形状を除去して、後続の金属化プロセスの過程におけるシャドーイング(shadowing)の可能性を防止するまたは抑制することが望ましい場合がある。シャドーイングは、棚形状の下方にあるピットの表面の不連続および/または不均一な金属化を招き得る。

【0024】

窒化物の棚形状は、窒化物の棚形状をエッチングするに十分な圧力(典型的には50〜1000mTorr)で、例えばCF4を用いるドライエッチング工程により除去することができる。窒化ケイ素は、エッチングプロセスにおいてフッ素イオン及びその他のフッ素含有種によって化学的に攻撃され得、かつこの圧力は近い範囲にわたって分子を有意に散乱させるに十分高いので、該窒化物の棚形状はその両面がエッチングされる。一方で、他のすべての表面上では窒化ケイ素の1つの表面だけが侵食される。これは、これらが基体の一方の側に結合されているかまたはそれ以外の方法、例えば、エッチングの反応器のプレート/電極に対向することによってシールドされた表面を有するからである。したがって、基体の残っている部分の窒化物を完全に除去することなく、窒化物の棚形状を除去することができる。この棚形状の除去は、他の段階、例えば、さらなる窒化ケイ素コーティングが実施される場合にはそのコーティング後などで実行することもできるが、金属化が確実に連続的に進行するように金属化の前に実施するのが望ましい。例えば、金属化プロセスの過程で有意な散乱がある場合や、窒化物の棚形状が小さ場合や、コンフォーマルな導線の堆積が用いられる場合には、たとえ棚形状が存在していてもこのプロセスは省略してもよい。

【0025】

局所的に薄くする処理及び任意の棚形状除去処理の後、エッチングマスクは、例えば、エッチングマスクの材料によって決まる公知の剥離技術及び化学反応を用いて除去され得る。

【0026】

図4を参照するとわかるように、局所的に薄くなった領域15の表面を絶縁するために、絶縁性材料の第2のハードマスク層16が基体上に形成される。第2のハードマスク層の材料は典型的には、第1のハードマスク層12と同じであるが、別のものでもよい。好適な材料、技術および厚さは、第1のハードマスク層に関して上記したとおりである。この例示の方法では、第2のハードマスク層16は、第1の窒化物層と同じような厚さを持った低ストレス窒化ケイ素層である。第2のハードマスク層を用いて、基体の局所的に薄くなった領域中に形成されるビアを電気的に隔離する。

【0027】

本ビア形成方法は、ウエットエッチングおよび/またはドライエッチングによって実施されるかとは無関係に、基体のデバイス表面の平面性を高く維持することができ、レジストを正確にコーティングによって及び任意にコンタクトリソグラフィ(contact lithography)によって、基体のデバイス表面上に、続いて取り付けるフィーチャー、導電性配線および配列フィーチャーのパターン化をすることが可能である。加えて、本方法では、任意の金属や半田を適用する前に第2のハードマスクをコーティングして、決まったストレス値を持つ絶縁保護コーティングを有する低ストレス窒化ケイ素及び酸化ケイ素などのLPCVDコーティングを用いることを可能とする。

【0028】

図5を参照すれば分かるように、次に、1つ以上のマイクロビア18が、基体の局所的に薄くなった領域15に形成される。このマイクロビアは、フォトリソグラフィによるパターン化技術とエッチング技術とによって形成することができ、ここで、フォトレジストまたは他の好適な光画像形成可能な材料(図示せず)が、第2のハードマスク層16上の基体の裏面上に提供され、露光され、現像されエッチングマスクを形成し、ここで、局所的にエッチングされた領域中の第2のハードマスク層のビアが形成される領域は露出している。第2のハードマスク層のこの露出領域は、第1のハードマスク材料のエッチングに関して上述したようにエッチングによって除去される。これにより、この局所的に薄くなった領域中の基体の下層領域が露出され、次いで、基体の前面上の第1のハードマスク層12に至るまでエッチングされる。この基体のエッチングは、第2のハードマスク層16中の開口部を通じて異方性エッチングによって実行され得る。例示の実施形態における局所的に薄くされた領域の場合と同様にウエット異方性エッチングが実施されかつ<100>ケイ素が基体材料であるときは、マイクロビアの側壁は、{111}結晶平面を含む。底面における典型的なマイクロビア開口部は、その形状が四角である場合に各辺は20〜200ミクロンであり、例えば、40〜200ミクロンである。

【0029】

局所的に薄くさなった領域に関し上述したように、マイクロビアのための好適なマスク開口部の決定は、知られているビアの深さと側壁の角度とに基づいておこなうことができ、所望のマイクロビアディメンジョンを得ることが可能である。基体の同じ側から異方性結晶学エッチングして、局所的に薄くなった領域とマイクロビアを形成する場合、これらのフィーチャーの側壁は同じ方向に先細(taper)にされる。ピット14とマイクロビアの同じ側をエッチングすることは、例えば、基体の反対側で精密なフィーチャーをパターン化する際の精度をより高められるので望ましい。場合によって、局所的に薄くすることは、ドライエッチングによってまたはウエットエッチングとドライエッチングを組み合わせによって実行することができる。この段階において、マイクロビアを形成する際に用いられるエッチングマスクが、周知の材料と技術を用いてウエハから除去される。その結果、図5に示すような構造体となる。例えばウエットエッチング、例えばフッ化水素酸(HF)、緩衝HFもしくは燐酸溶液によるウエットエッチング、および/またはドライエッチングによって、ハードマスク層の厚さが基体の裏面から除去される。これは、後の工程で、より大いに寸法の制御を可能にする。図示するデバイス構造体の目的上、第2のハードマスク層16に対応する厚さを、デバイスから除去される厚さとして示す。

【0030】

図6に示すように、ピット14とマイクロビア18の表面は、例えば第1及び第2のハードマスク層に関連して上述したような厚さで、第3のハードマスク層20によりコーティングされる。この第3のハードマスクは、完成されたデバイスパッケージ中で電気的隔離をもたらす。この例示の方法では、この第3のハードマスク層20は、第1及び第2のハードマスク層の厚さと同様の低ストレス窒化ケイ素層である。

【0031】

マイクロビア18を次に基体の裏面から金属化することができ、図7に示すような導体22を形成し得る。この金属化構造体を、例えばシャドーマスク、コンフォーマルリフトオフレジスト、電着レジスト、スプレイコーティングレジストまたはラミネートパターン化レジストによりパターン化する。この金属化構造体は、マイクロビアの底部で露出しているハードマスクの部分を覆い、および基体の前面8に至るまでのマイクロビアの側壁に沿った導電性をもたらす。この金属としては、基体の前面からハードマスク材料が完全にまたは部分的に除去された後で独立して立っていられるようになるに十分な機械的強度を持った金属が選ばれる。この金属化の結果として、マイクロビアの開口を渡る導電性及び密封性が実現され得る。この金属は、例えば、Cr/Ni/Au、TiW/AuまたはTi/Pt/Auであり得る。例えば、20nm厚さのCrの次に200nm厚さのNiを積層してその上を500nm厚さのAuで覆った積層層は、マイクロビアの開口を渡る例えば20〜35ミクロンの長さに対して十分な機械的強度を有する。しかしながら、これより薄いまたは厚い層を用いてもよい。加えて、強度を上げるために必要であれば、かかる金属を電気メッキしたり、電気メッキされた金属を蒸着された金属に追加して、より厚くし、これによって、膜を大きくしたり、電流をより増加させたりすることができる。

【0032】

マイクロビアを基体の裏面から金属化した後のこの時点では、基体の表面はまだ平面状である。マイクロビアの近傍で基体を局所的に薄くすると、大きくされたビア構造体、例えば、基体の厚さ全体を貫通するように延長したビア構造体に伴う寄生による影響を最小化する効果がある。したがって、ビアは、基体の厚さ全体を完全に貫通するように延長しないことが望ましい。同じ側から基体を局所的に薄くし、ビアを微細加工することによって、基体の前面を、マイクロ電子機器フィーチャーを形成するための平面状表面に維持することができ、さらなる利益をもたらす。結果的に、より高価で複雑な処理を基体のデバイス表面上に実行する前に基体にマイクロビアを作成され得る。これは、製造デバイスの経費削減に対して大きな影響を有し得る。またさらに、平面状の基体の前面は、標準的なスピンコーティングされた薄いレジストを用いることを可能にし、かつ精密な画定を必要とするパッケージの重要なフィーチャーを形成するために用いるフォトリソグラフィ技術を用いることを可能にする。このようなフィーチャーとしては、例えば、伝送ラインや薄い膜半田が挙げられる。さらに、平面状表面は、例えばマイクロ光学構成要素、例えばボールレンズのためのピット構造などのマイクロ光学構成要素の場合において必要とされる正確な微細加工を容易にする。

【0033】

基体の前面を、次に、フォトレジストまたは他の光画像形成可能な材料でコーティングし、パターン化し、平面状の前面からドライエッチングして、図8に示すようにハードマスク層12、16、20を通って下層のマイクロビア金属化物22に至る開口部24を形成する。この金属層は、プラズマエッチング技術や他の膜除去技術に対して好適なエッチングストップとして機能することができる。例えば、円形もしくは矩形の穴、格子または他の形状などの任意のパターンを前面のハードマスク材料中に開口することができ、所望により、ハードマスクが機械的安定性をさらに提供することを可能にする。ハードマスク材料は、面及び側壁上の金属が適切にパターン化することができる場合には、マイクロビアに対して複数の導線を許容するようにパターン化されてもよい。典型的には、パターン化と間隔置きを容易にするために矩形または円形形状が用いられ得る。

【0034】

図9を参照すれば分かるように、基体の平面状の前面を金属化してさまざまなフィーチャーを提供することができ、フィーチャーは例えばデバイスパッケージ内のマイクロビアの金属層22や電子デバイス28と電気的に通じる導電性配線26である。適切な材料が当該技術分野において知られており、例えば、マイクロビア金属化物22に関連して上述したような材料が含まれる。金属層を、マイクロエレクトロニクス技術分野で周知な方法のなかで、例えば、シャドーマスキング、電着されたレジストにより、またはリフトオフにより、または金属の化学的エッチングによって適用させてパターン化してもよい。金属構造体は、例えば、1以上の金属の蒸着、スパッタリング、CVDならびに電気化学的メッキおよび無電解化学的メッキなどの1以上を、例えばもし所望の場合はシードプロセス及びパターン化されたマスクを用いるなど、周知技術によって堆積することができる。メッキは、比較的厚い層に対しては特に有用であり得、この層としては、例えば、同一平面上のマイクロ波伝層ラインの作成や金の熱圧着結合のための金バンプの生成に用いられる数ミクロン厚の金層などの、厚い金含有層などが挙げられる。これらの技術の任意の組み合わせが用いられ得る。電子デバイス結合のための半田パッド27もまた、この時点で形成されてもよい。典型的な半田パッド材料には、例えば、Au−Sn共融合金、インジウム、または、その融点と機械的プロセス特性および付着プロセス特性によって選ばれた他の合金が含まれ、かつ典型的な半田パッド材料は、他の金属フィーチャーと関連して本明細書に記載する技術のうちのどれかによって形成され得る。

【0035】

この時点では、次いでデバイス表面に蓋を結合するための金属製シールリング29を提供して、電子デバイスに対する密封筐体を提供することも望ましくあり得る。前面に結合される蓋の密封表面とその形状が相補的である金属製シールリングが典型的に用いられるが、ジプトロニクス社(Ziptronics,Inc)から販売されているような半田ガラス技術や共有結合技術を用いることも想定される。この目的のため、金属を基体表面および/または蓋上に堆積してもよい。この金属製シールリングは、例えば、接着層、拡散バリアおよび可溶性の金属層を含む金属スタックから形成してもよい。例えば、クロムとチタンは一般的な接着層であり、ニッケル、プラチナおよびTiWは一般的な拡散バリアであり、および金は一般的な可溶性金属である。加えて、このリングには半田が含まれてもよく、例えばこの半田は、蓋密封表面、基体表面またはその双方上での厚さが3〜8ミクロンで、約80:20のAu−Snである。場合によっては、かかる金層をパターン化するかまたはシールリング全体をパターン化してもよく、これで、金属半田が所与の領域中を選択的に流れ、多かれ少なかれ半田を、蓋取り付け工程中に所望次第でウイッキング(wicking)するようにしてもよい。かかる処理は、変化領域や、トポロジ領域や、表面粗さが大きい領域があり、または例えばパッケージから出ることができる電気的または光学的導波路を覆って密封するようなときに、このような領域での密封のためにより厚い金属半田層が望まれる場合には有用である。

【0036】

基体の平面状の表面を金属化した後、1つ以上の電子デバイス28を、予備加工済み電子デバイスの場合には基体表面に結合する。これらの電子デバイスは、例えば、1つ以上の光電子機器、ICデバイスやMEMSデバイスであり得る。また、この電子デバイスは、少なくとも部分的には基体の一部として形成したり、または、その場で基体上に形成したりすることが可能であると予想される。これは、例えば、BAWデバイス、マイクロボロメータ焦点面アレイやRFスイッチなどのMEMSデバイス、または、レーザや、光ダイオードや、他の光電子デバイスの場合であり得る。さらに、以下でより詳述するように、電子デバイスをパッケージの蓋に取り付けることができることが予想される。予備加工済みの電子デバイスの場合、従来の技術と材料によって基体に対する結合を実行することができ、例えば、基体の前面上の予備形成済み半田パッド27に結合したり、デバイスや基体の表面上の半田に取り付けたり、またはエポキシや金バンプの溶融結合を用いたりすることができる。

【0037】

蓋30を基体の上面に取り付けて、図10に示すように電子デバイス28が収納される密封体積31を形成することができる。蓋30は、パッケージの所望の特徴、例えば、気体浸透性、光学特性及び熱膨張係数(CTE)に基づいて選択された材料から形成される。この蓋を通して光信号を送信および/受信する光電子機器または光MEMSデバイスの場合、一般的には、材料が所望の波長で光学的に透過性であることが望ましい。このような場合に蓋基体のために好適な材料には、例えば、SchottBK−7(アメリカ、ニューヨーク、エルムスフォード市、ショット北アメリカ社(Schott North America、Inc.))、Pyrex(アメリカ、ニューヨーク、コーニング市、コーニング社(Corning Inc.,))などのガラス、および単結晶ケイ素が挙げられる。この例示のデバイスパッケージでは、蓋は単結晶ケイ素で形成される。

【0038】

この蓋は、その1以上の内部表面および/または外部表面に、1以上の反射防止用コーティング剤または他の光学的コーティング剤をコーティングすることができる。さらに、他の材料を蓋上に堆積させ、または堆積してパターン化したりすることができ、この他の材料には、例えば、非蒸着性ゲッターなどのゲッターが挙げられる。蓋が光透過性であることが望ましくない場合、非透過性の蓋材料を用いたり、基体と同じ材料を用いたりしてもよい。場合によっては、エッチングしたり、スタンプしたり、多の方法で形成したりした金属が蓋として機能することができる。蓋に用いられる例示の金属にはタンタルがあり、そのCTEはケイ素のそれに近い。

【0039】

この蓋は、基体の上面の所望の部分を密閉するに十分なサイズである。矩形の蓋のシーリング部分の典型的な長さと幅は、例えば、1〜15mmのオーダーである。ベース基体の場合のように、蓋の基体はウエハ形態でよく、これで、複数の蓋を同時に製造することが可能となる。その結果得られるベース基体と蓋ウエハをウエハレベルで一緒に組み立てることができ、完全にウエハレベルでの製造プロセスを可能とすることができる。適切な蓋形成技術が当該技術分野で周知であり、前述の米国特許出願広報第US20050111797A1号に記載されている。

【0040】

蓋ウエハをプレ機械加工して、ダイシング後に追加の処理をすることなく、基体ウエハに対して電気的にコンタクトをとることが可能とすることができる。これによって、ウエハレベルでのテストを、個々のパッケージを個片切断する前に実行して、同時に、機械的ストレスと、密封作業後にこのような開口部を作成する後処理作業の経費とを最小化することが可能である。このようなプレ機械加工された蓋ウエハは、ホットモールディング、エッチングおよび/または吹き付け加工などの周知の方法で形成してもよい。これは、電気的接触を表と裏の両面でとることが望まれる場合に役に立つ。さらに、蓋をSOIウエハから作成して、蓋の上面の厚さをよりよく調整することもできる。これは、ヘリウムや他の気体の圧力が密閉体積中に密封されたり、密封されたデバイスがヘリウムや他の気体中で爆破を受けたりしたときに分かる測定可能な隆起を引き起こすような厚さを選択することにより蓋が漏れ電流センサーとして働くようにするのに役立つ。このような場合、蓋は効果的に圧力ゲージと成って、内部で密封された気体に対する正確な漏洩速度や、ある時間期間にわたってパッケージの外部で印加されたヘリウムなどの気体の圧力に対するパッケージの対抗能力を測定する際に助けとなり得る。蓋の曲がり、すなわち、たわみは、例えばワイコ社(Wyko)やザイゴ社(Zygo)製などの干渉計で測定可能である。場合によっては、蓋の特定の領域を薄くして、たわみ膜として働くようにしたり、または、エッチングして別の膜材料となるようにしたりしてもよい。

【0041】

ウエハレベルでの処理の場合、蓋を個別にデバイス基体やウエハ形態で取り付けてもよい。蓋に取り付ける場合、蓋結合材料には、半田ガラスや上述したような金属が挙げられ得る。蓋を密封するプロセスでは、管理された環境下で電子部品を結合した状態で蓋と基体を、例えば、ヘリウム、アルゴン、窒素などの不活性気体でまたは真空中でベークして、存在するあらゆる水分を除去するようにする。次に、圧力を蓋と基体の間に印加して、その部分を、金属半田のリフロー温度にまで加熱する。任意に、この圧力は、このリフロー温度に達した後で印加してもよい。冷却されたときにヘリウムの圧力下でパッケージを密封し、密封された領域の圧力が大気圧よりかなり高くなるようになり利点がある。この技術によって、密封レベルや、パッケージの漏洩速度を密封シール作成後のどの時点でも監視することが可能となる。

【0042】

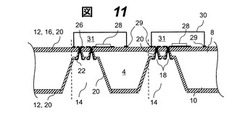

ウエハレベルでの製造プロセスの場合、複数のダイとして形成されたデバイスパッケージは、例えば、基体を隣り合ったパッケージ間を通してダイシングすることによって、個片切断される。図11に示す好適なラインは、これに沿って基体をダイシングして、破線で示すようにパッケージを個片切断するラインでありえる。図示するように、ダイシングは、局所的に薄くされた領域に沿って実行すると利点があるが、その目的とするところは、外部回路、例えば、図14に示すようなフレックス回路32との電気的接続性を促進することにある。パッケージの縁の表面が垂直であることが望ましい場合、例えば、図12に示す破線で示すように、さらにダイシングしてもよい。このような個片切断の結果を図13に示すが、この図は個片切断の結果得られるパッケージを示している。

【0043】

デバイスパッケージを個片切断した後、外部デバイスとの電気的接続のための接続を施すことができる。図14は、この目的のための導電性マイクロビアに対するフレックス回路32の接続を示す。フレックス回路は一般的にはポリイミド、LCPまたは他の適切な基体から作成される。フレキシブル回路は、1以上の金属配線(図示せず)を基体材料の上または内部に含んでいる。一般的には、フレキシブル回路は1より多い層からできている。フレックス回路は、基体の裏面から導電性ビアに容易に取り付けることができ、これは、局所的に薄くされた領域のために、そこにアクセスしやすくなっているからである。フレックス回路は、例えば、フレックス回路や基体上で錫系の半田ボールやパターン化された半田によって、半田付けなどの周知の技術によって導電性ビアに取り付けてもよい。図15は、本発明による例示の電子デバイスパッケージのベース基体の正面図と、局所的に薄くされた領域におけるマイクロビアを上から見た図である。破線の矢印は、図13の断面図を表している。デバイスの蓋などの基体の上面にあるフィーチャーは図示されていない。5個のマイクロビアとこのビアに至る金属配線が、局所的に薄くされた領域に見受けられるが、これは、パッケージの電子デバイスとの電気的接続をとるためである。

【0044】

上記の電気パッケージ形成方法に加えて、これに対する変更例が予想される。例えば、図16〜19に、マイクロビアが電子デバイスの2つ以上の側面に提供されるさまざまな形成段階における例示の電子デバイスパッケージの断面図を示す。図16で、2つのマイクロビア18が電子デバイス取り付け領域33の両側に示されている。周辺のマイクロビアをいくつでも、基体の上面の金属化物および/またはマイクロ電子部品に接続するように、または、基体表面上にまたは蓋表面上に取り付けられるまたは形成される1つ以上のデバイスに対して電気的接続を施すようにすることが可能であることは明らかである。

【0045】

図17に、基体の上面8に取り付けられた電子デバイス28を示す。この電子デバイスは、例えば、デバイスもしくはウエハ表面に堆積された半田によってまたは技術上周知の他の取り付け方法によって取り付けられ得る。この電子デバイスは、基体ウエハの頂部表面上の金属製配線に対して電気的接続を施すために取り付けられたフリップフロップでもよい。代替例では、これはボールまたはウエッジワイヤで結合するかまたはその組み合わせで結合され得る。電子デバイスは1つしか図示していないが、複数個取り付けてもよいことは明らかである。加えて、このようなデバイスは、上記したように、基体表面に取り付ける代わりに、この上や内部に形成してもよい。

【0046】

図18に示すように、上記のような蓋30を、基体の上面の金属製シールリング29に取り付けたり、または、上述したように基体上面に別様に結合したりする。典型的には、蓋の結合を含めてこれにまで至るすべての工程は、上記したように、ウエハレベルや格子レベルで実施される。

【0047】

図19に、ウエハレベルプロセスの場合における、ダイの個片切断後の図18のパッケージを示す。フレキシブル回路32を、図14を参照して上述したような仕方で、基体の裏面にパターン化された金属製配線によってマイクロビア18に対する電気的接続を施すため、局所的に薄くされた領域で基体4に取り付ける。このフレックス回路は、図示するようにパッケージに取り付けるための切り出される領域を含んでいたり、または、複数のフレックス回路を1つのパッケージに取り付けたりしてもよい。

【0048】

任意に、図18のパッケージ済みデバイスは回路基体に取り付けてもよい。この場合、図19に示すフレックス回路32が回路基体材料を表す。この回路基体は、パッケージの厚い領域を含むように切り取られている領域を含んでいたり、または、半田ボールが凹部領域を回路基体に橋渡ししたりしてもよい。さらに別のパッケージ接続の選択には、例えば、リードフレーム、ガルウイングおよび類似物がある。

【0049】

図20〜23に、本発明のさらに別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階を示す。この構造体は、図13と19を参照して説明したものと類似しており、基体には凹部領域34があって、蓋ウエハの一部である蓋30に対して取り付けられたまたはこの中もしくは上に形成された電子デバイス28のためのクリアランスとなるようにしている。図20に、電気配線26と任意の外部シールリング29を持った基体4を示す。この場合、この基体は、図21に示すような半田36などのパターン化済みの取り付け材料を有している。半田36が、基体上のマイクロビア18および配線26と蓋30上の電子機器28間に電気的接続をもたらしている。外部半田36は一般的には密封材料製のリングであり、このリングは、チップに外接していて、ベースと蓋を、一般的には両者がウエハレベルにある間に、一緒に密封する働きをする。この場合、マイクロビアを含んでいる基体4は薄くなった領域を有するが、この領域には、シールが確実に密封するようにする膜を持っている。このような構造体は、上記の曲げ/たわみ測定可能構造体に類似している。図22に示すように、ベース基体4と蓋30は外部シール領域に対して一緒に結合されて密封性を提供し、同時に、内部結合された領域が、基体4上の金属製配線とマイクロビアを蓋30に取り付けられたまたはこの中もしくは上に形成された電子デバイス28の関連の電気配線とI/Oと電気的に接続する電気的接続ポイントとなっている。図19と類似して、図23は、ウエハレベルから個片切断した後のパッケージ済みで、また、フレックス回路32または回路基体に電気的に取り付けられたデバイスを示す。

【0050】

図24に、本発明のさらに別の態様に関わる例示の電子デバイスパッケージ基体の正面図を示す。基体4の局所的に薄くなった領域15を形成する際、この領域の3つの側部上にある基体材料は除去されない。このようにして、基体に対して構造的剛性を追加することが可能である。デバイスの蓋、電子デバイス、金属製配線などの基体上面上のフィーチャーは図示されていない。この例示の基体では、4つのマイクロビア18とこのビア用の金属製配線22は、局所的に薄くされた領域で見受けられる。

【0051】

本発明をその特定の実施形態を参照して詳細に説明したが、クレームの範囲から逸脱することなく、さまざまな変更や修正が可能であり、また、等価例も可能であることが当業者には明らかである。

【図面の簡単な説明】

【0052】

本発明は、類似の参照番号が類似の特徴機能を示す以下の図面を参照して解説される:

【図1】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図2】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図3】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図4】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図5】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図6】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図7】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図8】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図9】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図10】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図11】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図12】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図13】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図14】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図15】本発明に関わる例示の電子デバイスパッケージ基体の正面図と、この基体を部分的に上から見た図である。

【図16】本発明の別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図17】本発明の別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図18】本発明の別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図19】本発明の別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図20】本発明のさらに別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図21】本発明のさらに別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図22】本発明のさらに別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図23】本発明のさらに別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図24】本発明のさらに別の態様に関わる例示の電子デバイスパッケージ基体の正面図である。

【符号の説明】

【0053】

4 基体

8 表面

10 裏面

12 第1のハードマスク層

13 エッチングマスク

14 錐体状ピット

15 薄くなった領域

16 第2のハードマスク層

18 マイクロビア

20 第3のハードマスク層

22 導体

24 開口部

26 導電性配線

27 半田パッド

28 電子デバイス

29 金属製シールリング

30 蓋

31 密封体積

32 フレックス回路

33 電子デバイス取り付け領域

34 凹部領域

36 半田

【技術分野】

【0001】

本発明は、一般的にはマイクロ加工技術に関し、詳しくは、電子デバイスパッケージとその形成方法に関する。本発明は、例えば、光電子デバイス、ICまたはMEMSデバイスなどの電子デバイスを1つ以上含んでいる密封パッケージの電子産業に応用される。

【背景技術】

【0002】

例えば、集積回路(IC)、光電子デバイス、微小電気機械システム(MEMS)などの電子デバイスを含んでいる密封されたチップスケールパッケージとウエハレベルパッケージが知られている。このようなパッケージは多くの場合、ベース基体と蓋の間に形成されて密封された封入体積を包含しており、この封入体積中に電子デバイスが配置されている。このパッケージは、封入されたデバイスを閉じこめ、パッケージの外部の環境中に存在する汚染物質や水蒸気から、封入されたデバイスの保護を提供する。パッケージ中に汚染物質や水蒸気が存在すると、例えば、金属部分の腐食や、光電子デバイス、光MEMSおよび他の光部品の場合における光学的損失などの問題が発生しかねない。加えて、このようなパッケージは時として、正しく動作させるためにまたはそのデバイスの所望の寿命を達成するために、真空または管理された環境下で密封される。

【0003】

パッケージ中に封入された電子デバイスと、外界との間の電気的接続性を提供するためには、パッケージの内部と外部との間に電気的貫通接続が必要である。密封パッケージのためのさまざまなタイプの電気的貫通接続が開示されている。例えば、シェレル(Sherrer)らによる米国特許出願公開第2005/0111797A1号には、導電性のビア(via)を密封された光電子パッケージで用いることが開示されている。光電子デバイスは、例えばケイ素基板などの基体上に配置されて、蓋を基体に取り付けて密封体積中に同封される。導電性ビアは、該基体を突き抜けて延長し、デバイスに電気的接続性を提供する。上記の公開出願の例示されたビア形成プロセスでは、ビアを一方の側から基体の厚さ全体を突き抜けて窒化ケイ素膜までエッチングし、このビアを金属化し、該窒化物はパターニ化されかつ除去され、及びビアを最上面にまで接続して、密封した電気的ビアを作成する。ビアの達成可能な最小サイズは一般に、ビアのエッチングプロセスのアスペクト比と基体の厚さによって制限される。

【0004】

電子デバイスパッケージ内に高密度で詰め込まれた金属化ビアを形成する能力を有することが望ましい。このようにすれば、縮小された形状を有するパッケージを提供することが可能である。これによって、ウエハレベルプロセス(wafer−level process)においてウエハ上に形成され得るパッケージの数を増やすことが可能となるという付加利益がもたらされ、それにより製造コストが軽減される。その上、ビアのサイズの減少が、このビアの構造に関連する寄生インダクタンスおよび/またはキャパシタンスを減少させることに役立ち得、それによりマイクロ波周波数でのビア性能が向上される。

【0005】

国際公開第2006/097842号には、前記ウエハレベルで行われる、光電子デバイスやMEMSデバイスなどの半導体部品を収納するための比較的薄いパッケージを製造する技術が開示されている。この文献では、一実施形態において、貫通接続金属化が提供されかつ裏側にウエハ薄層化技術を含む、同じウエハ上に取り付けられたまたは同じウエハにより集積されたマイクロ部品が開示されている。ケイ素/酸化物/ケイ素型ウエハがこのプロセスでは用いられる。ウエハのデバイス側のケイ素から酸化物のエッチングがストップされる層までマイクロビアが形成される。マイクロ部品が、マイクロビア間のデバイス側上の領域に取り付けられ、半導体またはガラスの蓋ウエハが最初のウエハに結合され、これで、このマイクロ部品がこの2つのウエハにより画定される領域内に収納されるようにする。ウエハを結合した後、薄層化プロセスが最初の層の裏側のケイ素層に対して実行される。

【特許文献1】米国特許出願公開第2005/0111797号明細書

【特許文献2】国際公開第2006/097842号パンフレット

【発明の開示】

【発明が解決しようとする課題】

【0006】

上記のデバイスと方法はさまざまな欠点を有する。ビア並びに精密マイクロ電子機器、例えば、伝送ライン、薄膜パターン化された半田やキャパシタなどの精密マイクロ電子機器を国際公開第2006/097842号におけるようにウエハのデバイス側上に含んでいるウエハの場合、精密リソグラフィと精密パターン化が必要となる。精密リソグラフィでは、薄いフォトレジストがコーティングされ、適切に露光されかつパターン化され得る平面またはほぼ平面の表面が求められる。ウエハの前面上にマイクロ電子機器を形成するより先に、ビアを同じ前面上からエッチングする場合及び同じ前面上に作成する場合、このビアがこのウエハ上でのフォトレジストの適切なスピンコーティングの妨げとなる。その結果、多くの場合、粗末な被覆性及び不整合なパターン化をもたらすこととなる。例えばフォトレジストを噴霧する方法及びフォトレジストを電気メッキする方法などの方法が用いられてきた。しかしながら、前者の方法ではレジストの厚さに一貫性がなくなり、後者の方法では厚さが比較的大きくなってしまうため、これらの方法では、必要とされる高精度パターン化が不可能である。これは、高い産出高でRF伝送ラインや抵抗体などの精密な機能物のパターン化を特に困難もしくは不可能にする。

【0007】

ウエハの前面上でマイクロ電子機器を作成した後に、同じ面から、またはこの面上にビアを製造する場合、このマイクロ電子機器は、このビアを形成するために用いられる処理に耐えなければならない。異方的にエッチングされるビアの場合、これは、典型的に、20分から数時間にわたって攻撃的なアルカリ性エッチに曝されことになり、多くの場合アルカリ性エッチは、マイクロ電子機器で用いられる物質、例えば、半田に用いられる錫、抵抗体で用いられるNi−CrやTaN、及び接着層の形成でしばしば用いられるチタンなどの物質を攻撃する。加えて、マイクロ電子機器の生産で必要とされる多くの処理工程の後でビアを作成すると、産出高が不充分な場合に大幅なコストが生じ得る。

【0008】

したがって、当該技術分野において、最新技術に伴う1以上のかかる問題を解決する改良された電子デバイスパッケージ及びその形成方法の必要性が存在する。

【課題を解決するための手段】

【0009】

本発明の第1の態様によれば、電子デバイスパッケージが提供される。この電子デバイスパッケージは、第1面と該第1面の反対側の第2面とを有する基体を含む。第2面は、その中に局所的に薄くなった領域を有する。この局所的に薄くなった領域中の導電性ビアは、基体を通って第1面まで延長している。この導電性ビアと局所的に薄くなった領域のそれぞれが、テーパー側壁を含み、ここで、導電性ビアの側壁のテーパーと局所的に薄くなった領域の側壁のテーパーは同じ方向である。電子デバイスは基体の第1面上に取り付けられる。この電子デバイスは、導電性ビアに電気的に接続される。

【0010】

本発明の第2の態様による電子デバイスパッケージは、第1面と該第1面の反対側の第2面とを有する基体を含む。第2面は、その中に局所的に薄くなった領域を有する。この局所的に薄くなった領域中の導電性ビアは、基体を通って第1面まで延長している。電子デバイスは基体の第1面上に取り付けられる。この電子デバイスは、導電性ビアに電気的に接続される。フレックス回路が、局所的に薄くなった領域中に少なくとも部分的に配置され、かつ導電性ビアに電気的に接続される。

【0011】

本発明のさらなる態様によれば、電子デバイスパッケージを形成する方法が提供される。本方法は(a)第1面と該第1面の反対側の第2面とを有する基体を提供する工程と;(b)前記基体の一部分を第2面から薄くして、第2面中に局所的に薄くなった領域を形成する工程と;(c)エッチングして前記局所的に薄くなった領域中に基体を通って延長するビアを形成する工程であって、前記エッチングが、その局所的に薄くなった面から第1面の方向に実施される工程と;(d)前記ビアを金属化する工程であって、導電性のビアと前記局所的に薄くなった領域のそれぞれが、テーパー側壁を含み、ここで前記導電性ビアの側壁のテーパーと前記局所的に薄くなった領域の側壁のテーパーが同じ方向である工程と;(e)電子デバイスを前記基体の前記第1面上に取り付ける工程であって、前記電子デバイスが前記導電性ビアに電気的に接続される工程;を含む。

【0012】

本発明のさらに別の態様によれば、電子デバイスパッケージを形成する方法は(a)第1面と該第1面の反対側の第2面とを有する基体を提供する工程と;(b)基体の一部分を前記第2面から薄くして、第2面中に局所的に薄くなった領域を形成する工程と;(c)基体を通って第1面に延長するビアを局所的に薄くなった領域中に形成する工程と;(d)前記ビアを金属化する工程と;(e)電子デバイスを前記基体の第1面上に取り付ける工程であって、電子デバイスが導電性のビアに電気的に接続される工程と;(f)前記局所的に薄くなった領域に少なくとも部分的に配置され、かつ導電性のビアに電気的に接続されたフレックス回路を提供する工程;を含む。

【0013】

この電子デバイスパッケージとその形成方法において、基体は、例えば半導体(例えば単結晶ケイ素など)を含み、及びシリコンウエハもしくはシリコン−オン−インシュレーター(SOI)ウエハまたはその一部という形をとり得る。この電子デバイスは、電子デバイスパッケージ中に密封され得る。1以上の導電性ビア(典型的には複数の導電性ビア)は、局所的に薄くなった領域中に形成される。この局所的に薄くなった領域は、基体の第1の縁にまで延長させてもよく、こうすると、局所的に薄くなった領域中に少なくとも部分的に配置されかつ導電性ビアに電気的に接続されるフレックス回路の提供を可能となり好都合である。蓋を第1面の上に提供して、電子デバイスを封入する密閉された体積を形成してもよい。本発明の例示の態様では、ウエハを局所的に薄くして、基体の同じ側から、複数のビアがこの局所的に薄くなった領域中に形成される。電子デバイスパッケージは、ウエハレベルで形成すると利点があり得、このウエハは、電子デバイスパッケージを各々が含む複数のダイ(die)を有している。

【0014】

本発明の他の特徴及び利点は、以下の記載、特許請求の範囲および添付の図面を読めば当業者には明らかとなる。

【発明を実施するための最良の形態】

【0015】

本発明は、電子デバイスパッケージを形成する改良された方法並びにこれによって形成することができる電子デバイスパッケージを提供する。このパッケージは、その表面に局所的に薄くなった領域を有する基体と、局所的に薄くなった領域中の、基体を通って延長する導電性ビアとを含む。電子デバイスが導電性ビアに電気的に接続される。電子デバイスは、局所的に薄くなった領域と導電性ビアが形成される表面とは反対側の基体表面上に配置され得る。あるいは、電子デバイスは、ビアを含んでいる基体に密封する蓋を形成する別個の基体上に配置され得る。ビアは電子デバイスに電気的に接続される。

【0016】

本明細書で用いる「マイクロ構造体」は、必ずしもウエハレベルではないが、マイクロ加工プロセスやナノ加工プロセスで形成される構造体のことであり、「ウエハレベル」とは複数のダイが形成される任意の基体により行うプロセスのことであるが、このようなダイには、例えば、複数のダイを同じ基体または基体部分を形成する場合には完全なウエハやその一部が含まれる。

【0017】

本発明による電子デバイスパッケージを形成する方法を図1〜14を参照して説明するが、図1〜14は、本発明による例示の電子デバイスパッケージを形成するさまざまな段階でのその断面図を示している。

【0018】

図1に示すように、基体4が提供される。この基体は、第1(デバイス面の、または表の)面8と、該第1面の反対側の第2(裏側の)面10を有する。基体4は、電子デバイスのパッケージングで用いられるのに適した任意の材料、例えば半導体材料、金属、セラミック及びガラスなどから形成され得る。典型的に、基体の材料には、単結晶ケイ素などの単結晶半導体材料、シリコン−オン−インシュレーターまたはケイ素ゲルマニウム基体が含まれる。この基体は、単一の構成要素、または、より典型的には複数のダイのような複数の同じ構成要素を形成することが可能な寸法の基体であり得る。典型的に基体は、複数のダイを有するウエハという形態である。この例示の方法では、<100>両面研磨シリコンウエハを基体として提供する。このウエハの厚さは、約525±25μであれば好都合であり、かつ抵抗率は、典型的には、高周波用途の場合には1000オーム−cmより大きいが、これより低い抵抗率も用いられ得る。

【0019】

ハードマスクとして用いるために、及び場合によっては基体とその上に配置される導線や電子デバイスなどの電気的構造体との間を電気的に隔離するために、基体またはその一部の前面及び裏面上に1つ以上のハードマスク層が提供され得る。典型的には、このハードマスク層は、例えば、スピンオンガラス、酸窒化ケイ素及び二酸化チタンをはじめとする、低ストレス窒化ケイ素、ドープおよび非ドープの酸化ケイ素から選ばれた誘電体層である。このような誘電体層は公知の技術、例えばプラズマ化学気相堆積(PECVD)や低圧化学気相堆積(LPCVD)、スパッタリングやイオンビーム堆積法などの物理的気相堆積(PVD)、スピンコーティング、陽極酸化、熱酸化法などの技術によって形成され得る。誘電体層の厚さは、例えば個々の材料や後続のプロセスの条件などの要因に依存する。誘電体層の典型的な厚さは、100〜250ナノメートル(nm)である。この例示の方法において、低ストレスLPCVD窒化ケイ素層は、例えば200〜500nm(例えば200〜250nmなど)の厚さで、基体の第1と第2面上に提供される。

【0020】

基体の裏面10上に配置された第1のハードマスク層12は、典型的に標準のリソグラフィ技術とドライエッチング技術を用いてパターン化されて、開口部を形成して下層の基体物質を露出させ、これが次に局所的に薄くされる。パターン化されたフォトレジストまたは他の好適な光画像形成可能な物質を、エッチングマスク13として基体の裏面10上に提供し、露光し第1のハードマスク層のこれらの領域を除去する。場合により、結晶配列(crystal alignment)工程を実行して、正確な結晶学的配列軸を決定し、これで、エッチングされるフィーチャーを要求される精度にまで結晶軸に位置合わせすることが可能となるようにしてもよい。基体の裏面上のエッチングマスク13の間の露出された第1のハードマスク層12の領域をドライエッチングで除去して、下層の基体材料を露出させることができる。エッチャントは、例えば、第1のハードマスク層12の材料によって決まる。窒化ケイ素層を用いているこの例示の方法においては、例えば50〜500mTorrの圧力での、CF4や他の好適なフッ素含有エッチャントによるプラズマドライエッチングが典型的である。

【0021】

図3を参照すると分かるように、その後、例えば、基体中にそれぞれの開口部に対して錐体状ピット14が形成されるまで第1のハードマスク層12中の開口部を介して異方性エッチングすることにより基体の裏面10の露出された領域が薄くされる。図3は、第1のハードマスク層の露出された領域を除去した後で、基体4を局所的に薄くして、かつエッチングマスクを除去することを示している。この異方性エッチングは典型的には、例えば、KOHやEDPを用いる結晶学エッチングである。典型的には、ピット14は、基体の前面8から50〜250ミクロンの距離まで伸ばされる。表面全体ではなくて、基体の選択された部分、すなわち部分15だけが薄くされる。これによって、後続の処理及び取り扱いのための機械的剛性が維持され、破損を回避する助けることを可能とする。これは、例えばボールレンズや他の光学的構成要素などの構成要素を保持するために基体の前面に正確にエッチングされた構造体を作成するために十分な厚さが必要とされるマイクロ光学プラットフォームの場合には特に有益である。かかるエッチングされた構造体は、典型的にビアのためにのみ必要とされる薄くされた領域15と同じまたはこれより深くエッチングされてもよい。

【0022】

局所的に薄くされることにより形成された典型的なピット14は、形状が四角である場合に各辺が0.5〜5ミリメートル(mm)の底面を有する。局所的に薄くされた領域は、ダイの側壁1つ以上の長さに達し得る。製造において、これらの領域が、ある寸法において、複数のダイに跨ったり、またはウエハ上の全長に渡ったりしてもよい。ピットの反対側の寸法は、必要とするマイクロビアの数と、フレックス回路および/または半田ボールもしくは半田パッドのどちらかを用いてこのマイクロビアを外部から相互接続するために必要とされるスペースとによって決定され得る。<100>ケイ素の場合、錐体状ピット14の側壁は、異方性ウエットエッチングで作成された場合には{111}結晶平面表面となる。分かっているピットの深さと側壁の角度とに基づいて、第1のハードマスク層12中に形成される目標とする開口部のサイズを計算することが可能である。場合によっては、局所的に薄くすることは、機械的な切削もしくはダイシングによって、ドライエッチングによって、またはウエットエッチングとドライエッチングの組み合わせによって実行してもよい。

【0023】

局所的に薄くする過程において、開口部に隣接している領域において第1のハードマスク層12が、開口部の側部に窒化物の棚形状(図示せず)が形成される結果となるアンダーカットの状態になる場合がある。ピットの14の表面を金属化する前に、この窒化物の棚形状を除去して、後続の金属化プロセスの過程におけるシャドーイング(shadowing)の可能性を防止するまたは抑制することが望ましい場合がある。シャドーイングは、棚形状の下方にあるピットの表面の不連続および/または不均一な金属化を招き得る。

【0024】

窒化物の棚形状は、窒化物の棚形状をエッチングするに十分な圧力(典型的には50〜1000mTorr)で、例えばCF4を用いるドライエッチング工程により除去することができる。窒化ケイ素は、エッチングプロセスにおいてフッ素イオン及びその他のフッ素含有種によって化学的に攻撃され得、かつこの圧力は近い範囲にわたって分子を有意に散乱させるに十分高いので、該窒化物の棚形状はその両面がエッチングされる。一方で、他のすべての表面上では窒化ケイ素の1つの表面だけが侵食される。これは、これらが基体の一方の側に結合されているかまたはそれ以外の方法、例えば、エッチングの反応器のプレート/電極に対向することによってシールドされた表面を有するからである。したがって、基体の残っている部分の窒化物を完全に除去することなく、窒化物の棚形状を除去することができる。この棚形状の除去は、他の段階、例えば、さらなる窒化ケイ素コーティングが実施される場合にはそのコーティング後などで実行することもできるが、金属化が確実に連続的に進行するように金属化の前に実施するのが望ましい。例えば、金属化プロセスの過程で有意な散乱がある場合や、窒化物の棚形状が小さ場合や、コンフォーマルな導線の堆積が用いられる場合には、たとえ棚形状が存在していてもこのプロセスは省略してもよい。

【0025】

局所的に薄くする処理及び任意の棚形状除去処理の後、エッチングマスクは、例えば、エッチングマスクの材料によって決まる公知の剥離技術及び化学反応を用いて除去され得る。

【0026】

図4を参照するとわかるように、局所的に薄くなった領域15の表面を絶縁するために、絶縁性材料の第2のハードマスク層16が基体上に形成される。第2のハードマスク層の材料は典型的には、第1のハードマスク層12と同じであるが、別のものでもよい。好適な材料、技術および厚さは、第1のハードマスク層に関して上記したとおりである。この例示の方法では、第2のハードマスク層16は、第1の窒化物層と同じような厚さを持った低ストレス窒化ケイ素層である。第2のハードマスク層を用いて、基体の局所的に薄くなった領域中に形成されるビアを電気的に隔離する。

【0027】

本ビア形成方法は、ウエットエッチングおよび/またはドライエッチングによって実施されるかとは無関係に、基体のデバイス表面の平面性を高く維持することができ、レジストを正確にコーティングによって及び任意にコンタクトリソグラフィ(contact lithography)によって、基体のデバイス表面上に、続いて取り付けるフィーチャー、導電性配線および配列フィーチャーのパターン化をすることが可能である。加えて、本方法では、任意の金属や半田を適用する前に第2のハードマスクをコーティングして、決まったストレス値を持つ絶縁保護コーティングを有する低ストレス窒化ケイ素及び酸化ケイ素などのLPCVDコーティングを用いることを可能とする。

【0028】

図5を参照すれば分かるように、次に、1つ以上のマイクロビア18が、基体の局所的に薄くなった領域15に形成される。このマイクロビアは、フォトリソグラフィによるパターン化技術とエッチング技術とによって形成することができ、ここで、フォトレジストまたは他の好適な光画像形成可能な材料(図示せず)が、第2のハードマスク層16上の基体の裏面上に提供され、露光され、現像されエッチングマスクを形成し、ここで、局所的にエッチングされた領域中の第2のハードマスク層のビアが形成される領域は露出している。第2のハードマスク層のこの露出領域は、第1のハードマスク材料のエッチングに関して上述したようにエッチングによって除去される。これにより、この局所的に薄くなった領域中の基体の下層領域が露出され、次いで、基体の前面上の第1のハードマスク層12に至るまでエッチングされる。この基体のエッチングは、第2のハードマスク層16中の開口部を通じて異方性エッチングによって実行され得る。例示の実施形態における局所的に薄くされた領域の場合と同様にウエット異方性エッチングが実施されかつ<100>ケイ素が基体材料であるときは、マイクロビアの側壁は、{111}結晶平面を含む。底面における典型的なマイクロビア開口部は、その形状が四角である場合に各辺は20〜200ミクロンであり、例えば、40〜200ミクロンである。

【0029】

局所的に薄くさなった領域に関し上述したように、マイクロビアのための好適なマスク開口部の決定は、知られているビアの深さと側壁の角度とに基づいておこなうことができ、所望のマイクロビアディメンジョンを得ることが可能である。基体の同じ側から異方性結晶学エッチングして、局所的に薄くなった領域とマイクロビアを形成する場合、これらのフィーチャーの側壁は同じ方向に先細(taper)にされる。ピット14とマイクロビアの同じ側をエッチングすることは、例えば、基体の反対側で精密なフィーチャーをパターン化する際の精度をより高められるので望ましい。場合によって、局所的に薄くすることは、ドライエッチングによってまたはウエットエッチングとドライエッチングを組み合わせによって実行することができる。この段階において、マイクロビアを形成する際に用いられるエッチングマスクが、周知の材料と技術を用いてウエハから除去される。その結果、図5に示すような構造体となる。例えばウエットエッチング、例えばフッ化水素酸(HF)、緩衝HFもしくは燐酸溶液によるウエットエッチング、および/またはドライエッチングによって、ハードマスク層の厚さが基体の裏面から除去される。これは、後の工程で、より大いに寸法の制御を可能にする。図示するデバイス構造体の目的上、第2のハードマスク層16に対応する厚さを、デバイスから除去される厚さとして示す。

【0030】

図6に示すように、ピット14とマイクロビア18の表面は、例えば第1及び第2のハードマスク層に関連して上述したような厚さで、第3のハードマスク層20によりコーティングされる。この第3のハードマスクは、完成されたデバイスパッケージ中で電気的隔離をもたらす。この例示の方法では、この第3のハードマスク層20は、第1及び第2のハードマスク層の厚さと同様の低ストレス窒化ケイ素層である。

【0031】

マイクロビア18を次に基体の裏面から金属化することができ、図7に示すような導体22を形成し得る。この金属化構造体を、例えばシャドーマスク、コンフォーマルリフトオフレジスト、電着レジスト、スプレイコーティングレジストまたはラミネートパターン化レジストによりパターン化する。この金属化構造体は、マイクロビアの底部で露出しているハードマスクの部分を覆い、および基体の前面8に至るまでのマイクロビアの側壁に沿った導電性をもたらす。この金属としては、基体の前面からハードマスク材料が完全にまたは部分的に除去された後で独立して立っていられるようになるに十分な機械的強度を持った金属が選ばれる。この金属化の結果として、マイクロビアの開口を渡る導電性及び密封性が実現され得る。この金属は、例えば、Cr/Ni/Au、TiW/AuまたはTi/Pt/Auであり得る。例えば、20nm厚さのCrの次に200nm厚さのNiを積層してその上を500nm厚さのAuで覆った積層層は、マイクロビアの開口を渡る例えば20〜35ミクロンの長さに対して十分な機械的強度を有する。しかしながら、これより薄いまたは厚い層を用いてもよい。加えて、強度を上げるために必要であれば、かかる金属を電気メッキしたり、電気メッキされた金属を蒸着された金属に追加して、より厚くし、これによって、膜を大きくしたり、電流をより増加させたりすることができる。

【0032】

マイクロビアを基体の裏面から金属化した後のこの時点では、基体の表面はまだ平面状である。マイクロビアの近傍で基体を局所的に薄くすると、大きくされたビア構造体、例えば、基体の厚さ全体を貫通するように延長したビア構造体に伴う寄生による影響を最小化する効果がある。したがって、ビアは、基体の厚さ全体を完全に貫通するように延長しないことが望ましい。同じ側から基体を局所的に薄くし、ビアを微細加工することによって、基体の前面を、マイクロ電子機器フィーチャーを形成するための平面状表面に維持することができ、さらなる利益をもたらす。結果的に、より高価で複雑な処理を基体のデバイス表面上に実行する前に基体にマイクロビアを作成され得る。これは、製造デバイスの経費削減に対して大きな影響を有し得る。またさらに、平面状の基体の前面は、標準的なスピンコーティングされた薄いレジストを用いることを可能にし、かつ精密な画定を必要とするパッケージの重要なフィーチャーを形成するために用いるフォトリソグラフィ技術を用いることを可能にする。このようなフィーチャーとしては、例えば、伝送ラインや薄い膜半田が挙げられる。さらに、平面状表面は、例えばマイクロ光学構成要素、例えばボールレンズのためのピット構造などのマイクロ光学構成要素の場合において必要とされる正確な微細加工を容易にする。

【0033】

基体の前面を、次に、フォトレジストまたは他の光画像形成可能な材料でコーティングし、パターン化し、平面状の前面からドライエッチングして、図8に示すようにハードマスク層12、16、20を通って下層のマイクロビア金属化物22に至る開口部24を形成する。この金属層は、プラズマエッチング技術や他の膜除去技術に対して好適なエッチングストップとして機能することができる。例えば、円形もしくは矩形の穴、格子または他の形状などの任意のパターンを前面のハードマスク材料中に開口することができ、所望により、ハードマスクが機械的安定性をさらに提供することを可能にする。ハードマスク材料は、面及び側壁上の金属が適切にパターン化することができる場合には、マイクロビアに対して複数の導線を許容するようにパターン化されてもよい。典型的には、パターン化と間隔置きを容易にするために矩形または円形形状が用いられ得る。

【0034】

図9を参照すれば分かるように、基体の平面状の前面を金属化してさまざまなフィーチャーを提供することができ、フィーチャーは例えばデバイスパッケージ内のマイクロビアの金属層22や電子デバイス28と電気的に通じる導電性配線26である。適切な材料が当該技術分野において知られており、例えば、マイクロビア金属化物22に関連して上述したような材料が含まれる。金属層を、マイクロエレクトロニクス技術分野で周知な方法のなかで、例えば、シャドーマスキング、電着されたレジストにより、またはリフトオフにより、または金属の化学的エッチングによって適用させてパターン化してもよい。金属構造体は、例えば、1以上の金属の蒸着、スパッタリング、CVDならびに電気化学的メッキおよび無電解化学的メッキなどの1以上を、例えばもし所望の場合はシードプロセス及びパターン化されたマスクを用いるなど、周知技術によって堆積することができる。メッキは、比較的厚い層に対しては特に有用であり得、この層としては、例えば、同一平面上のマイクロ波伝層ラインの作成や金の熱圧着結合のための金バンプの生成に用いられる数ミクロン厚の金層などの、厚い金含有層などが挙げられる。これらの技術の任意の組み合わせが用いられ得る。電子デバイス結合のための半田パッド27もまた、この時点で形成されてもよい。典型的な半田パッド材料には、例えば、Au−Sn共融合金、インジウム、または、その融点と機械的プロセス特性および付着プロセス特性によって選ばれた他の合金が含まれ、かつ典型的な半田パッド材料は、他の金属フィーチャーと関連して本明細書に記載する技術のうちのどれかによって形成され得る。

【0035】

この時点では、次いでデバイス表面に蓋を結合するための金属製シールリング29を提供して、電子デバイスに対する密封筐体を提供することも望ましくあり得る。前面に結合される蓋の密封表面とその形状が相補的である金属製シールリングが典型的に用いられるが、ジプトロニクス社(Ziptronics,Inc)から販売されているような半田ガラス技術や共有結合技術を用いることも想定される。この目的のため、金属を基体表面および/または蓋上に堆積してもよい。この金属製シールリングは、例えば、接着層、拡散バリアおよび可溶性の金属層を含む金属スタックから形成してもよい。例えば、クロムとチタンは一般的な接着層であり、ニッケル、プラチナおよびTiWは一般的な拡散バリアであり、および金は一般的な可溶性金属である。加えて、このリングには半田が含まれてもよく、例えばこの半田は、蓋密封表面、基体表面またはその双方上での厚さが3〜8ミクロンで、約80:20のAu−Snである。場合によっては、かかる金層をパターン化するかまたはシールリング全体をパターン化してもよく、これで、金属半田が所与の領域中を選択的に流れ、多かれ少なかれ半田を、蓋取り付け工程中に所望次第でウイッキング(wicking)するようにしてもよい。かかる処理は、変化領域や、トポロジ領域や、表面粗さが大きい領域があり、または例えばパッケージから出ることができる電気的または光学的導波路を覆って密封するようなときに、このような領域での密封のためにより厚い金属半田層が望まれる場合には有用である。

【0036】

基体の平面状の表面を金属化した後、1つ以上の電子デバイス28を、予備加工済み電子デバイスの場合には基体表面に結合する。これらの電子デバイスは、例えば、1つ以上の光電子機器、ICデバイスやMEMSデバイスであり得る。また、この電子デバイスは、少なくとも部分的には基体の一部として形成したり、または、その場で基体上に形成したりすることが可能であると予想される。これは、例えば、BAWデバイス、マイクロボロメータ焦点面アレイやRFスイッチなどのMEMSデバイス、または、レーザや、光ダイオードや、他の光電子デバイスの場合であり得る。さらに、以下でより詳述するように、電子デバイスをパッケージの蓋に取り付けることができることが予想される。予備加工済みの電子デバイスの場合、従来の技術と材料によって基体に対する結合を実行することができ、例えば、基体の前面上の予備形成済み半田パッド27に結合したり、デバイスや基体の表面上の半田に取り付けたり、またはエポキシや金バンプの溶融結合を用いたりすることができる。

【0037】

蓋30を基体の上面に取り付けて、図10に示すように電子デバイス28が収納される密封体積31を形成することができる。蓋30は、パッケージの所望の特徴、例えば、気体浸透性、光学特性及び熱膨張係数(CTE)に基づいて選択された材料から形成される。この蓋を通して光信号を送信および/受信する光電子機器または光MEMSデバイスの場合、一般的には、材料が所望の波長で光学的に透過性であることが望ましい。このような場合に蓋基体のために好適な材料には、例えば、SchottBK−7(アメリカ、ニューヨーク、エルムスフォード市、ショット北アメリカ社(Schott North America、Inc.))、Pyrex(アメリカ、ニューヨーク、コーニング市、コーニング社(Corning Inc.,))などのガラス、および単結晶ケイ素が挙げられる。この例示のデバイスパッケージでは、蓋は単結晶ケイ素で形成される。

【0038】

この蓋は、その1以上の内部表面および/または外部表面に、1以上の反射防止用コーティング剤または他の光学的コーティング剤をコーティングすることができる。さらに、他の材料を蓋上に堆積させ、または堆積してパターン化したりすることができ、この他の材料には、例えば、非蒸着性ゲッターなどのゲッターが挙げられる。蓋が光透過性であることが望ましくない場合、非透過性の蓋材料を用いたり、基体と同じ材料を用いたりしてもよい。場合によっては、エッチングしたり、スタンプしたり、多の方法で形成したりした金属が蓋として機能することができる。蓋に用いられる例示の金属にはタンタルがあり、そのCTEはケイ素のそれに近い。

【0039】

この蓋は、基体の上面の所望の部分を密閉するに十分なサイズである。矩形の蓋のシーリング部分の典型的な長さと幅は、例えば、1〜15mmのオーダーである。ベース基体の場合のように、蓋の基体はウエハ形態でよく、これで、複数の蓋を同時に製造することが可能となる。その結果得られるベース基体と蓋ウエハをウエハレベルで一緒に組み立てることができ、完全にウエハレベルでの製造プロセスを可能とすることができる。適切な蓋形成技術が当該技術分野で周知であり、前述の米国特許出願広報第US20050111797A1号に記載されている。

【0040】

蓋ウエハをプレ機械加工して、ダイシング後に追加の処理をすることなく、基体ウエハに対して電気的にコンタクトをとることが可能とすることができる。これによって、ウエハレベルでのテストを、個々のパッケージを個片切断する前に実行して、同時に、機械的ストレスと、密封作業後にこのような開口部を作成する後処理作業の経費とを最小化することが可能である。このようなプレ機械加工された蓋ウエハは、ホットモールディング、エッチングおよび/または吹き付け加工などの周知の方法で形成してもよい。これは、電気的接触を表と裏の両面でとることが望まれる場合に役に立つ。さらに、蓋をSOIウエハから作成して、蓋の上面の厚さをよりよく調整することもできる。これは、ヘリウムや他の気体の圧力が密閉体積中に密封されたり、密封されたデバイスがヘリウムや他の気体中で爆破を受けたりしたときに分かる測定可能な隆起を引き起こすような厚さを選択することにより蓋が漏れ電流センサーとして働くようにするのに役立つ。このような場合、蓋は効果的に圧力ゲージと成って、内部で密封された気体に対する正確な漏洩速度や、ある時間期間にわたってパッケージの外部で印加されたヘリウムなどの気体の圧力に対するパッケージの対抗能力を測定する際に助けとなり得る。蓋の曲がり、すなわち、たわみは、例えばワイコ社(Wyko)やザイゴ社(Zygo)製などの干渉計で測定可能である。場合によっては、蓋の特定の領域を薄くして、たわみ膜として働くようにしたり、または、エッチングして別の膜材料となるようにしたりしてもよい。

【0041】

ウエハレベルでの処理の場合、蓋を個別にデバイス基体やウエハ形態で取り付けてもよい。蓋に取り付ける場合、蓋結合材料には、半田ガラスや上述したような金属が挙げられ得る。蓋を密封するプロセスでは、管理された環境下で電子部品を結合した状態で蓋と基体を、例えば、ヘリウム、アルゴン、窒素などの不活性気体でまたは真空中でベークして、存在するあらゆる水分を除去するようにする。次に、圧力を蓋と基体の間に印加して、その部分を、金属半田のリフロー温度にまで加熱する。任意に、この圧力は、このリフロー温度に達した後で印加してもよい。冷却されたときにヘリウムの圧力下でパッケージを密封し、密封された領域の圧力が大気圧よりかなり高くなるようになり利点がある。この技術によって、密封レベルや、パッケージの漏洩速度を密封シール作成後のどの時点でも監視することが可能となる。

【0042】

ウエハレベルでの製造プロセスの場合、複数のダイとして形成されたデバイスパッケージは、例えば、基体を隣り合ったパッケージ間を通してダイシングすることによって、個片切断される。図11に示す好適なラインは、これに沿って基体をダイシングして、破線で示すようにパッケージを個片切断するラインでありえる。図示するように、ダイシングは、局所的に薄くされた領域に沿って実行すると利点があるが、その目的とするところは、外部回路、例えば、図14に示すようなフレックス回路32との電気的接続性を促進することにある。パッケージの縁の表面が垂直であることが望ましい場合、例えば、図12に示す破線で示すように、さらにダイシングしてもよい。このような個片切断の結果を図13に示すが、この図は個片切断の結果得られるパッケージを示している。

【0043】

デバイスパッケージを個片切断した後、外部デバイスとの電気的接続のための接続を施すことができる。図14は、この目的のための導電性マイクロビアに対するフレックス回路32の接続を示す。フレックス回路は一般的にはポリイミド、LCPまたは他の適切な基体から作成される。フレキシブル回路は、1以上の金属配線(図示せず)を基体材料の上または内部に含んでいる。一般的には、フレキシブル回路は1より多い層からできている。フレックス回路は、基体の裏面から導電性ビアに容易に取り付けることができ、これは、局所的に薄くされた領域のために、そこにアクセスしやすくなっているからである。フレックス回路は、例えば、フレックス回路や基体上で錫系の半田ボールやパターン化された半田によって、半田付けなどの周知の技術によって導電性ビアに取り付けてもよい。図15は、本発明による例示の電子デバイスパッケージのベース基体の正面図と、局所的に薄くされた領域におけるマイクロビアを上から見た図である。破線の矢印は、図13の断面図を表している。デバイスの蓋などの基体の上面にあるフィーチャーは図示されていない。5個のマイクロビアとこのビアに至る金属配線が、局所的に薄くされた領域に見受けられるが、これは、パッケージの電子デバイスとの電気的接続をとるためである。

【0044】

上記の電気パッケージ形成方法に加えて、これに対する変更例が予想される。例えば、図16〜19に、マイクロビアが電子デバイスの2つ以上の側面に提供されるさまざまな形成段階における例示の電子デバイスパッケージの断面図を示す。図16で、2つのマイクロビア18が電子デバイス取り付け領域33の両側に示されている。周辺のマイクロビアをいくつでも、基体の上面の金属化物および/またはマイクロ電子部品に接続するように、または、基体表面上にまたは蓋表面上に取り付けられるまたは形成される1つ以上のデバイスに対して電気的接続を施すようにすることが可能であることは明らかである。

【0045】

図17に、基体の上面8に取り付けられた電子デバイス28を示す。この電子デバイスは、例えば、デバイスもしくはウエハ表面に堆積された半田によってまたは技術上周知の他の取り付け方法によって取り付けられ得る。この電子デバイスは、基体ウエハの頂部表面上の金属製配線に対して電気的接続を施すために取り付けられたフリップフロップでもよい。代替例では、これはボールまたはウエッジワイヤで結合するかまたはその組み合わせで結合され得る。電子デバイスは1つしか図示していないが、複数個取り付けてもよいことは明らかである。加えて、このようなデバイスは、上記したように、基体表面に取り付ける代わりに、この上や内部に形成してもよい。

【0046】

図18に示すように、上記のような蓋30を、基体の上面の金属製シールリング29に取り付けたり、または、上述したように基体上面に別様に結合したりする。典型的には、蓋の結合を含めてこれにまで至るすべての工程は、上記したように、ウエハレベルや格子レベルで実施される。

【0047】

図19に、ウエハレベルプロセスの場合における、ダイの個片切断後の図18のパッケージを示す。フレキシブル回路32を、図14を参照して上述したような仕方で、基体の裏面にパターン化された金属製配線によってマイクロビア18に対する電気的接続を施すため、局所的に薄くされた領域で基体4に取り付ける。このフレックス回路は、図示するようにパッケージに取り付けるための切り出される領域を含んでいたり、または、複数のフレックス回路を1つのパッケージに取り付けたりしてもよい。

【0048】

任意に、図18のパッケージ済みデバイスは回路基体に取り付けてもよい。この場合、図19に示すフレックス回路32が回路基体材料を表す。この回路基体は、パッケージの厚い領域を含むように切り取られている領域を含んでいたり、または、半田ボールが凹部領域を回路基体に橋渡ししたりしてもよい。さらに別のパッケージ接続の選択には、例えば、リードフレーム、ガルウイングおよび類似物がある。

【0049】

図20〜23に、本発明のさらに別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階を示す。この構造体は、図13と19を参照して説明したものと類似しており、基体には凹部領域34があって、蓋ウエハの一部である蓋30に対して取り付けられたまたはこの中もしくは上に形成された電子デバイス28のためのクリアランスとなるようにしている。図20に、電気配線26と任意の外部シールリング29を持った基体4を示す。この場合、この基体は、図21に示すような半田36などのパターン化済みの取り付け材料を有している。半田36が、基体上のマイクロビア18および配線26と蓋30上の電子機器28間に電気的接続をもたらしている。外部半田36は一般的には密封材料製のリングであり、このリングは、チップに外接していて、ベースと蓋を、一般的には両者がウエハレベルにある間に、一緒に密封する働きをする。この場合、マイクロビアを含んでいる基体4は薄くなった領域を有するが、この領域には、シールが確実に密封するようにする膜を持っている。このような構造体は、上記の曲げ/たわみ測定可能構造体に類似している。図22に示すように、ベース基体4と蓋30は外部シール領域に対して一緒に結合されて密封性を提供し、同時に、内部結合された領域が、基体4上の金属製配線とマイクロビアを蓋30に取り付けられたまたはこの中もしくは上に形成された電子デバイス28の関連の電気配線とI/Oと電気的に接続する電気的接続ポイントとなっている。図19と類似して、図23は、ウエハレベルから個片切断した後のパッケージ済みで、また、フレックス回路32または回路基体に電気的に取り付けられたデバイスを示す。

【0050】

図24に、本発明のさらに別の態様に関わる例示の電子デバイスパッケージ基体の正面図を示す。基体4の局所的に薄くなった領域15を形成する際、この領域の3つの側部上にある基体材料は除去されない。このようにして、基体に対して構造的剛性を追加することが可能である。デバイスの蓋、電子デバイス、金属製配線などの基体上面上のフィーチャーは図示されていない。この例示の基体では、4つのマイクロビア18とこのビア用の金属製配線22は、局所的に薄くされた領域で見受けられる。

【0051】

本発明をその特定の実施形態を参照して詳細に説明したが、クレームの範囲から逸脱することなく、さまざまな変更や修正が可能であり、また、等価例も可能であることが当業者には明らかである。

【図面の簡単な説明】

【0052】

本発明は、類似の参照番号が類似の特徴機能を示す以下の図面を参照して解説される:

【図1】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図2】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図3】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図4】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図5】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図6】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図7】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図8】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図9】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図10】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図11】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図12】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図13】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図14】本発明の第1の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図15】本発明に関わる例示の電子デバイスパッケージ基体の正面図と、この基体を部分的に上から見た図である。

【図16】本発明の別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図17】本発明の別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図18】本発明の別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図19】本発明の別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図20】本発明のさらに別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図21】本発明のさらに別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図22】本発明のさらに別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図23】本発明のさらに別の態様に関わる、例示の電子デバイスパッケージを形成する際のさまざまな段階での断面図である。

【図24】本発明のさらに別の態様に関わる例示の電子デバイスパッケージ基体の正面図である。

【符号の説明】

【0053】

4 基体

8 表面

10 裏面

12 第1のハードマスク層

13 エッチングマスク

14 錐体状ピット

15 薄くなった領域

16 第2のハードマスク層

18 マイクロビア

20 第3のハードマスク層

22 導体

24 開口部

26 導電性配線

27 半田パッド

28 電子デバイス

29 金属製シールリング

30 蓋

31 密封体積

32 フレックス回路

33 電子デバイス取り付け領域

34 凹部領域

36 半田

【特許請求の範囲】

【請求項1】

第1面と該第1面の反対側の第2面とを有する基体であって、該第2面がその中に局所的に薄くなった領域を有する基体;

前記局所的に薄くなった領域中の、前記基体を通って前記第1面まで延長する導電性ビアあって、前記導電性ビアと前記局所的に薄くなった領域のそれぞれがテーパー側壁を含み、前記導電性ビアの側壁のテーパーと前記局所的に薄くなった領域の側壁のテーパーが同じ方向である、導電性ビア;及び

前記導電性ビアに接続される電子デバイス;

を含む電子デバイスパッケージ。

【請求項2】

第1面と該第1面の反対側の第2面とを有する基体であって、該第2面がその中に局所的に薄くなった領域を有する基体;

前記局所的に薄くなった領域中の、前記基体を通って前記第1面まで延長する導電性ビアと;

前記導電性ビアに電気的に接続される電子デバイスと;

前記局所的に薄くなった領域中に少なくとも部分的に配置されかつ前記導電性ビアに電気的に接続されるフレックス回路;

を備える電子デバイスパッケージ。

【請求項3】

前記基体が単結晶ケイ素を含む請求項1または2に記載の電子デバイスパッケージ。

【請求項4】

前記電子デバイスを密閉する密封体積を形成するための、前記第1面上の蓋をさらに含む、請求項1から3のいずれか一項に記載の電子デバイスパッケージ。

【請求項5】

前記電子デバイスが前記蓋に取り付けられる請求項4に記載の電子デバイスパッケージ。

【請求項6】

前記電子デバイスが前記電子デバイスパッケージ中に密封される請求項1から5のいずれか一項に記載の電子デバイスパッケージ。

【請求項7】

前記局所的に薄くなった領域が前記基体の第1の縁まで延長する請求項1から6のいずれか一項に記載の電子デバイスパッケージ。

【請求項8】

前記電子デバイスが光電子デバイスである請求項1から7のいずれか一項に記載の電子デバイスパッケージ。

【請求項9】

複数のダイを有する基体を含むウエハレベル電子デバイスパッケージであって、それぞれの前記ダイが、請求項1から8のいずれか一項に記載の電子デバイスパッケージを含む、ウエハレベル電子デバイスパッケージ。

【請求項10】

電子デバイスパッケージを形成する方法であって:

(a)第1面と該第1面の反対側の第2面とを有する基体を提供する工程と;

(b)前記基体の一部分を前記第2面から薄くして、前記第2面中に局所的に薄くなった領域を形成する工程と;

(c)エッチングして、前記局所的に薄くなった領域中に基体を通って延長するビアを形成する工程であって、前記エッチングが、その局所的に薄くなった面から第1面の方向に実施される工程と;

(d)前記ビアを金属化する工程であって、導電性のビアと前記局所的に薄くなった領域のそれぞれが、テーパー側壁を含み、ここで導電性ビアの側壁のテーパーと前記局所的に薄くなった領域の側壁のテーパーが同じ方向である工程と;

(e)導電性ビアに電気的に接続される電子デバイスを提供する工程;

を含む方法。

【請求項11】

電子デバイスパッケージを形成する方法であって:

(a)第1面と該第1面の反対側の第2面とを有する基体を提供する工程と;

(b)前記基体の一部分を前記第2面から薄くして、前記第2面中に局所的に薄くなった領域を形成する工程と;

(c)前記基体を通って前記第1面に延長するビアを前記局所的に薄くなった領域中に形成する工程と;

(d)前記ビアを金属化する工程と;

(e)導電性のビアに電気的に接続される電子デバイスを提供する工程と;

(f)前記局所的に薄くなった領域に少なくとも部分的に配置され、かつ導電性のビアに電気的に接続されたフレックス回路を提供する工程;

を含む方法。

【請求項1】

第1面と該第1面の反対側の第2面とを有する基体であって、該第2面がその中に局所的に薄くなった領域を有する基体;

前記局所的に薄くなった領域中の、前記基体を通って前記第1面まで延長する導電性ビアあって、前記導電性ビアと前記局所的に薄くなった領域のそれぞれがテーパー側壁を含み、前記導電性ビアの側壁のテーパーと前記局所的に薄くなった領域の側壁のテーパーが同じ方向である、導電性ビア;及び

前記導電性ビアに接続される電子デバイス;

を含む電子デバイスパッケージ。

【請求項2】

第1面と該第1面の反対側の第2面とを有する基体であって、該第2面がその中に局所的に薄くなった領域を有する基体;

前記局所的に薄くなった領域中の、前記基体を通って前記第1面まで延長する導電性ビアと;

前記導電性ビアに電気的に接続される電子デバイスと;

前記局所的に薄くなった領域中に少なくとも部分的に配置されかつ前記導電性ビアに電気的に接続されるフレックス回路;

を備える電子デバイスパッケージ。

【請求項3】

前記基体が単結晶ケイ素を含む請求項1または2に記載の電子デバイスパッケージ。

【請求項4】

前記電子デバイスを密閉する密封体積を形成するための、前記第1面上の蓋をさらに含む、請求項1から3のいずれか一項に記載の電子デバイスパッケージ。

【請求項5】

前記電子デバイスが前記蓋に取り付けられる請求項4に記載の電子デバイスパッケージ。

【請求項6】

前記電子デバイスが前記電子デバイスパッケージ中に密封される請求項1から5のいずれか一項に記載の電子デバイスパッケージ。

【請求項7】

前記局所的に薄くなった領域が前記基体の第1の縁まで延長する請求項1から6のいずれか一項に記載の電子デバイスパッケージ。

【請求項8】

前記電子デバイスが光電子デバイスである請求項1から7のいずれか一項に記載の電子デバイスパッケージ。

【請求項9】

複数のダイを有する基体を含むウエハレベル電子デバイスパッケージであって、それぞれの前記ダイが、請求項1から8のいずれか一項に記載の電子デバイスパッケージを含む、ウエハレベル電子デバイスパッケージ。

【請求項10】

電子デバイスパッケージを形成する方法であって:

(a)第1面と該第1面の反対側の第2面とを有する基体を提供する工程と;

(b)前記基体の一部分を前記第2面から薄くして、前記第2面中に局所的に薄くなった領域を形成する工程と;

(c)エッチングして、前記局所的に薄くなった領域中に基体を通って延長するビアを形成する工程であって、前記エッチングが、その局所的に薄くなった面から第1面の方向に実施される工程と;

(d)前記ビアを金属化する工程であって、導電性のビアと前記局所的に薄くなった領域のそれぞれが、テーパー側壁を含み、ここで導電性ビアの側壁のテーパーと前記局所的に薄くなった領域の側壁のテーパーが同じ方向である工程と;

(e)導電性ビアに電気的に接続される電子デバイスを提供する工程;

を含む方法。

【請求項11】

電子デバイスパッケージを形成する方法であって:

(a)第1面と該第1面の反対側の第2面とを有する基体を提供する工程と;

(b)前記基体の一部分を前記第2面から薄くして、前記第2面中に局所的に薄くなった領域を形成する工程と;

(c)前記基体を通って前記第1面に延長するビアを前記局所的に薄くなった領域中に形成する工程と;

(d)前記ビアを金属化する工程と;

(e)導電性のビアに電気的に接続される電子デバイスを提供する工程と;

(f)前記局所的に薄くなった領域に少なくとも部分的に配置され、かつ導電性のビアに電気的に接続されたフレックス回路を提供する工程;

を含む方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【公開番号】特開2009−10323(P2009−10323A)

【公開日】平成21年1月15日(2009.1.15)

【国際特許分類】

【外国語出願】

【出願番号】特願2008−42222(P2008−42222)

【出願日】平成20年2月22日(2008.2.22)

【出願人】(591016862)ローム・アンド・ハース・エレクトロニック・マテリアルズ,エル.エル.シー. (270)

【Fターム(参考)】

【公開日】平成21年1月15日(2009.1.15)

【国際特許分類】

【出願番号】特願2008−42222(P2008−42222)

【出願日】平成20年2月22日(2008.2.22)

【出願人】(591016862)ローム・アンド・ハース・エレクトロニック・マテリアルズ,エル.エル.シー. (270)

【Fターム(参考)】

[ Back to top ]