電子デバイス及びその製造方法

【課題】貫通電極の基板等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通電極の側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い電子デバイスを提供する。

【解決手段】基板1と、基板1の表面上方に形成された配線18と、基板1の裏面から基板1を貫通しており、基板1の深さ方向において、第1の開孔1Aaと、第1の開孔1Aaよりも開口総面積が小さい第2の開孔1Abとが接続された貫通孔1Aに形成されてなる貫通ビア30とを含み、貫通ビア30は、第1の開孔1Aaに形成された第1の電極部30aと、第2の開孔1Abに形成された第2の電極部30bとが、最外側面が一体形成される。

【解決手段】基板1と、基板1の表面上方に形成された配線18と、基板1の裏面から基板1を貫通しており、基板1の深さ方向において、第1の開孔1Aaと、第1の開孔1Aaよりも開口総面積が小さい第2の開孔1Abとが接続された貫通孔1Aに形成されてなる貫通ビア30とを含み、貫通ビア30は、第1の開孔1Aaに形成された第1の電極部30aと、第2の開孔1Abに形成された第2の電極部30bとが、最外側面が一体形成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子デバイス及びその製造方法に関する。

【背景技術】

【0002】

近年、MOS等のトランジスタ、メモリデバイス、MEMS等のセンサデバイスに代表される電子デバイスでは、その集積化が平面的(2次元)構造から立体的(3次元)構造に移行している。

例えば、携帯電話機に搭載される半導体チップは、いわゆるシステム・イン・パッケージ構造のものが主流となりつつある。半導体チップにおける3次元積層化の手法としては、パッケージレベルで行うPoP方式、半導体チップを積層してワイヤ・ボンディングで相互接続するSiP方式等が用いられている。

【0003】

近時では、電子デバイスをチップレベルで積層化する3次元集積技術が盛んに開発されている。

多数の電子デバイスを3次元集積化する場合、電子デバイス相互間で電気的に接続するには、電子デバイスに基板を貫通する貫通電極(貫通ビア)を設け、これを用いて相互接続することが必要である。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−81304号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

電子デバイスの貫通ビアの電極材料としては、多結晶シリコン、タングステン(W)、Cu等が用いられる。多結晶シリコン、Wを用いる場合には、CVD法が適用される。Cuを用いる場合には、電解メッキ法が適用される。後者は、前者よりも低温でビア形成ができることから、電極材料としてCuを用いた貫通ビアが注目されている。

【0006】

電子デバイスでは、その基板の厚みはトランジスタ等の機能素子のサイズに比べて大きい。そのため、貫通ビアはアスペクト比が極めて高くなる。このような高アスペクト比の貫通ビアは、その基板への貫通孔の形成、貫通孔への電極材料の充填のいずれも困難であり、製造コストも大きくなる。従って、基板の面積に余裕があれば、貫通ビアの径を大きくして低アスペクト比の貫通ビアを形成することが望ましい。

【0007】

ところが、貫通ビアの径を大きくすると、貫通ビアの電極材料と基板及びアクティブ層(各種の機能素子及び配線が形成される層)との熱膨張率差が増大し、貫通ビアの周辺部位における変位量が増加するという問題が生じる。

具体例を図17に示す。図17では、半導体チップにおいて、シリコン基板101と、その上に形成されたアクティブ層102と、シリコン基板101を貫通する、Cuを用いた貫通ビア103と、外部接続用のバンプボール104とを簡易に示している。貫通ビア103は、シリコン基板101を貫通してアクティブ層102の配線102aと電気的に接続されている。アクティブ層102の内部構造としては、配線102aのみを示し、機能素子の図示は省略する。

【0008】

半導体チップの製造プロセスにおいて、処理温度TがCuの結晶再配列温度T0よりも大きいと、図18(a)のように、貫通ビア103のCuが熱膨張してアクティブ層102を押し上げ、アクティブ層102が凸状に変形する。一方、処理温度TがT0よりも小さいと、図18(b)のように、貫通電極103のCuが熱収縮してアクティブ層102を引っ張り、アクティブ層102が凹状に変形する。このように、処理温度により貫通電極103がアクティブ層102を上下方向に変動させる、いわゆるポンピングリアクションが生じ、アクティブ層102の機能素子、配線が機械的に破壊されるという問題がある。

【0009】

電流量を減少させることなく上記した貫通ビアの変位を抑える構成を、図19に示す。貫通ビア111は、図19のように、大径の第1の電極部112と、小径の複数の第2の電極部113とが接続されており、第2の電極部113でアクティブ層102と接続される。特許文献1に、その一例が開示されている。

【0010】

しかしながら、上記のように形状の異なる2種類の電極部を接続形成するため、貫通ビア111の側面において、第1の電極部112の第2の電極部113との端部、及び第2の電極部113の第1の電極部112との端部に、屈曲点114が形成される。この屈曲点114では、電極金属であるCuを所期のように形成することが困難であり、Cuの非形成部分が生じることがある。このように、2種類の電極部の接続部分のエッジ形状に起因して、リーク電流等が発生し、デバイス特性の劣化を惹起する。

また、上記のように形状の異なる2種類の電極部を接続形成するには、リソグラフィー工程を少なくとも2回行うことを要し、工程数が多く製造フローも煩雑であるという問題が生じる。

【0011】

本発明は、上記の課題に鑑みてなされたものであり、貫通電極の基板等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通電極の側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い電子デバイス及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

電子デバイスの一態様は、基板と、前記基板の表面上方に形成された配線と、前記基板の裏面から前記基板を貫通しており、前記基板の深さ方向において、第1の開孔と、前記第1の開孔よりも開口総面積の小さい第2の開孔とが、最外側面で一体化してなる貫通孔に形成されてなる貫通電極とを含む。

【0013】

電子デバイスの製造方法の一態様は、基板の表面上方に配線を形成する工程と、前記基板の裏面に前記基板を貫通する貫通孔を形成する工程と、前記貫通孔に、前記配線と電気的に接続される貫通電極を形成する工程とを含み、前記貫通孔を、前記基板の深さ方向において、第1の開孔と、前記第1の開孔よりも開口総面積の小さい第2の開孔とが、最外側面で一体化するように、エッチングで一括形成する。

【発明の効果】

【0014】

上記の諸態様によれば、貫通電極の基板等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通電極の側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い電子デバイスが実現する。

【図面の簡単な説明】

【0015】

【図1】第1の実施形態による半導体チップの製造方法を工程順に示す概略断面図である。

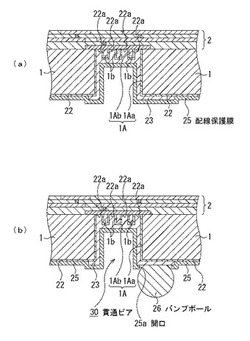

【図2】図1に引き続き、第1の実施形態による半導体チップの製造方法を工程順に示す概略断面図である。

【図3】図2に引き続き、第1の実施形態による半導体チップの製造方法を工程順に示す概略断面図である。

【図4】本実施形態において、貫通ビアの貫通孔を形成するためのレジストマスクを示す概略平面図である。

【図5】通常のレジストマスクを用いたドライエッチングを示す概略断面図である。

【図6】本実施形態のレジストマスクを用いたドライエッチングを示す概略断面図である。

【図7】本実施形態のレジストマスクの傾斜角θとレジストマスクの後退レートとの関係を示す特性図である。

【図8】本実施形態のドライエッチングについて、途中経過を含めて示す概略断面図である。

【図9】第1の実施形態の変形例1における、貫通ビア形成時に用いるレジストマスクを示す概略平面図である。

【図10】変形例1において、貫通ビアの貫通孔を形成するためのレジストマスクを示す概略平面図である。

【図11】第1の実施形態の変形例2における、貫通ビア形成時の一括ドライエッチングを行う際の工程を示す概略断面図である。

【図12】変形例2において、貫通ビアの貫通孔を形成するためのレジストマスクを示す概略平面図である。

【図13】第1の実施形態の変形例3における、貫通ビア形成時の一括ドライエッチングを行う際の工程を示す概略断面図である。

【図14】変形例3において、貫通ビアの貫通孔を形成するためのレジストマスクを示す概略平面図である。

【図15】第2の実施形態による半導体チップの製造方法の主要工程を示す概略断面図である。

【図16】第2の実施形態において、貫通ビアの貫通孔を形成するためのレジストマスクを示す概略平面図である。

【図17】従来の貫通ビアを示す概略断面図である。

【図18】貫通ビアに生じるポンピングリアクションを説明するための概略断面図である。

【図19】図18の問題を解決する一手法を説明するための概略断面図である。

【発明を実施するための形態】

【0016】

以下、電子デバイス及びその製造方法を適用した具体的な諸実施形態について、図面を参照しながら詳細に説明する。各実施形態では、電子デバイスとして、機能素子であるMOSトランジスタが搭載された半導体チップを例示する。電子デバイスとしては、当該半導体チップ以外でも、メモリデバイス、MEMS等のセンサデバイスにも適用可能である。また、基板としてはシリコン基板を例示するが、GaAs等の化合物半導体基板、樹脂等の絶縁基板、プリント基板等にも適用できる。

【0017】

(第1の実施形態)

図1〜図3は、第1の実施形態による半導体チップの製造方法を工程順に示す概略断面図である。

図1(a)に示すように、シリコン基板1の表面にアクティブ層2を形成する。

詳細には、先ず、基板としてシリコンの半導体基板を用意し、この半導体基板の裏面をバックグラインドにより所定の厚み、例えば200μm程度の厚みまで薄化する。これにより、シリコン基板1が形成される。

【0018】

シリコン基板の表面に、ゲート絶縁膜11を介して多結晶シリコン等を用いたゲート電極12を形成し、所定導電型の不純物をイオン注入してソース/ドレイン領域13を形成する。これにより、機能素子であるMOSトランジスタ10が形成される。

シリコン基板1上にMOSトランジスタ10を覆うように層間絶縁膜14を形成し、層間絶縁膜14にソース/ドレイン領域13等と電気的に接続される接続プラグ15を例えば電解メッキ法で形成する。このとき接続プラグ15と同時に、シリコン基板1上の後述する貫通ビアの形成予定部位に接続用電極16を形成する。層間絶縁膜14上に層間絶縁膜17を形成し、層間絶縁膜17に例えば電解メッキ法で接続プラグ15と電気的に接続される配線18を形成する。層間絶縁膜及び接続プラグ、層間絶縁膜及び配線の形成を数回(図示の例では1回)繰り返し行い、多層配線層20を形成する。以上により、MOSトランジスタ10及び多層配線層20を備えたアクティブ層2が形成される。

なお、アクティブ層2のうち、MOSトランジスタ10については、以下の図1(b)以降で図示を省略する。

【0019】

続いて、図1(b)に示すように、シリコン基板1の裏面に、レジストマスク21を形成する。

詳細には、シリコン基板1の裏面で後述する貫通ビアの形成予定部位(接続用電極16に位置整合する部位)にレジストを例えば10μm程度の厚みに塗布し、リソグラフィーで加工して、レジストパターン21を形成する。レジストマスク21の様子を図1(b)と共に図4の平面図に示す。図4の破線I−Iに沿った断面が図1(b)に対応する。レジストマスク21は、シリコン基板1の裏面を所定形状に露出する第1のパターン21aと、シリコン基板1の第1のパターン21aから露出する部位で柱状突起の形状とされた複数の第2のパターン21bとを有して構成される。第1のパターン21aは、例えば開口径が200μm程度の円形の開口パターンとされる。第2のパターン21bは、エッチング途中で消失するように、その縦断面において上底幅が下底幅よりも小さい台形状とされる。本実施形態では、リソグラフィーをいわゆる解調露光で行い、その光強度及び光照射角を調節することにより、第2のパターン21bを上記の縦断面台形状に形成する。第2のパターン21bは、後述するように、その傾斜角が、45°〜90°の範囲内の値に規定されている。

【0020】

ここで、第2のパターン21bを用いたドライエッチングについて説明する。

通常では、図5(a)に示すように、レジストマスク121は、縦断面形状が矩形であり、側面が被加工面122に対して垂直となる。レジストマスク121を用いて被加工面122をドライエッチングすることで、図5(b),(c)に示すように、レジストマスク121の横断面形状に倣って、レジストマスク121の上面と共に被加工面122がエッチングされてゆく。

【0021】

これに対して、図6(a)の第2のパターン21bであるレジストマスク123では、縦断面において上底幅が下底幅よりも小さい台形とされている。レジストマスク123の傾斜角をθとする。レジストマスク123を用いて被加工面122をドライエッチングすると、図6(b)に示すように、レジストマスク123の形状に倣って被加工面122がエッチングされてゆく。このとき、レジストマスク123はその上面でエッチングされてゆくが、第2のパターン21bは、側面に傾斜角を有するため、当該側面でもエッチングされて幅方向に後退してゆく。そして、傾斜角θを適宜調節したレジストマスク123を用いることで、被加工面122のエッチング途中でレジストマスク123は消失する。このとき、被加工面122には、所定高さの突起状のパターン122aが形成される。

【0022】

図7は、レジストマスクの傾斜角θとレジストマスクの後退レートとの関係を示す特性図である。

このように、レジストマスクの後退レートは、傾斜角θが45°のときに最も大きく、90°で最も小さい(ほぼ0)であることが判る。これは、傾斜角を有するレジストマスクでは、ドライエッチングのイオン性が高く、スパッタリングされたマスク材料が再付着せずイオン入射と反対方向に飛散するためにスパッタリング効率が高くなるためである。本実施形態では、この結果を利用して、レジストマスク123の後退レートを0(傾斜角θが90°のとき)から最大値(傾斜角θが45°のとき)までの値で選択し、突起状のパターン122aの高さを制御する。

【0023】

続いて、図1(c)に示すように、レジストマスク21を用いてシリコン基板1の裏面をドライエッチング(異方性ドライエッチング)し、接続用電極16の一部を露出する貫通孔1Aを形成する。ドライエッチングは、エッチングガスに例えばSF6及びC4H8の混合ガスを用い、ガス圧を例えば0.1Torr、投入電力を例えば500Wとし、20μm/分程度のエッチングレートで行う。エッチングの停止は時間制御とする。

【0024】

本実施形態のドライエッチングについて、途中経過を含めて、図8で詳細に示す。図8では、アクティブ層2について接続用電極16のみを図示する。

図8(a)の状態からドライエッチングを開始すると、図8(b),(c)のようにエッチングが進行する。エッチングが進むにつれて、シリコン基板1の裏面では、第1のパターン21aにより窪みが形成されてゆき、窪みの底面で第2のパターン21bによりシリコンが柱状に残されてゆく。それと共に、第2のパターン21bもエッチングされて後退してゆく。そして、エッチング途中で第2のパターン21bは消失する。その後、エッチングが終了するまで、シリコン基板1の窪みと柱状部分とが同様にエッチングされてゆく。第2のパターン21bがない状態でも、柱状部分が自己マスクとして機能するため、柱状部分は形状が維持されたままで窪みのエッチングが進行するが、柱状部分も窪みと同様にエッチングされ、高さが低くなる。図8(d)のように、接続用電極16の一部が露出した時点でエッチングを終了する。このとき、シリコンの柱状部分を柱状突起1bとする。柱状突起1bは、図7で示す第2のパターン21bの後退レートから規定された所期の高さに形成される。

【0025】

以上の一括ドライエッチングにより、シリコン基板1の裏面をドライエッチングし、接続用電極16の一部を露出する貫通孔1Aが自己整合的に形成される。貫通孔1Aは、第1のパターン21aで規定された大径(200μm程度)の第1の開孔1Aaと、第2のパターン21bで規定された、複数の柱状突起1bにより画定されてなる第2の開孔1Abとが連結したものである。第1の開孔1Aaは、加工し易い低アスペクト比の開口パターンである。第2の開孔1Abは、複数の柱状突起1bの存在により、その開口総面積が第1の開孔1Aaの開口面積よりも小さく、入り組んだ梁状の開口パターンとされる。本実施形態では、貫通孔1Aは、その最外側面が第1の開孔1Aaで規定される。即ち、貫通孔1Aは、当該一括ドライエッチングにより、第1の開孔1Aaの最外側面S1と第2の開孔1Abの最外側面S2とが屈曲点を持たず滑らかに一体化して形成される。

残った第1のパターン21aは、アッシング処理又は薬液を用いたウェットエッチング等により除去される。

【0026】

なお、貫通孔1Aは、その最外側面が若干テーパ状となるように、一括ドライエッチングで形成しても良い。この場合にも、貫通孔1Aは、第1の開孔1Aaの最外側面S1と第2の開孔1Abの最外側面S2とが屈曲点を持たず滑らかに一体化して形成される。

【0027】

続いて、図2(a)に示すように、貫通孔1Aの内壁面を覆う保護膜22を形成する。

詳細には、例えばCVD法により、シリコン基板1の貫通孔1Aの内壁面を覆うように、Cuのシリコン基板1内への拡散を防止する機能を持つ絶縁物、例えばSiNを500nm程度の厚みに堆積する。これにより、貫通孔1Aの内壁面を覆う保護膜22が形成される。

【0028】

続いて、図2(b)に示すように、貫通孔1Aの底部分(第2の開孔1Abの底部分)の保護膜22を除去する。

詳細には、シリコン基板1の裏面で貫通孔1A内にかけて、第2の開孔1Abの底部分の底部分に位置整合する部位に開口が形成されたレジストマスクを形成し、このレジストマスクを用いてボトムエッチングを行う。これにより、保護膜22は第2の開孔1Abの底部分のみで除去されて開口22aが形成され、開口22aから接続用電極16の表面の一部を露出する。

【0029】

続いて、図2(c)に示すように、Cu層23を形成する。

詳細には、先ず、例えば物理スパッタ法により、シリコン基板1の貫通孔1Aの内壁面を覆うように、Tiを20μm程度、Cuを100nm程度の厚みに順次成膜する。これにより、シリコン基板1の貫通孔1Aの内壁面を、保護膜22の開口22aでは直接的に、その他の部分では保護膜22を介して覆う、不図示のライナー層及びCuシード層が形成される。

【0030】

次に、Cu層23を形成する。

Cu層23の形成には、例えば電解メッキ法を用い、セミアディティブ法で行う。詳細には、シリコン基板1の裏面で貫通孔1A及びその周囲を適宜露出する開口24aを有するレジストマスク24を形成する。電解メッキ法により、レジストマスク24の開口24aから露出する部分にCuを例えば5μm〜20μm程度の厚みにメッキ成膜する。Cu層23は、貫通孔1Aを充填するように形成しても良い。これにより、貫通孔1Aのうち第2の開孔1AbをCuで充填し、第1の開孔1Aaの内壁面を覆うCu層23が形成される。以上により、貫通孔1AにCu層25が配されてなる貫通ビア30が形成される。貫通ビア30は、貫通孔1Aのうち第1の開孔1Aaに形成された第1の電極部30aと、第2の開孔1Abに形成された第2の電極部30bとが連続的に、最外側面が屈曲点を持たず滑らかに一体形成される。貫通ビア30では、第2の電極部30bが保護膜22の開口22aを通じて接続用電極16と電気的に接続される。第2の電極部30bは、第2の開孔1Abに倣って入り組んだ梁状であって、熱変形し難い形状とされており、ポンピングリアクションの発生が抑止される。

レジストマスク24は、アッシング処理又は薬液を用いたウェットエッチング等により除去される。

【0031】

なお、Cu層23をメッキ形成する代わりに、導電性ペーストを用いた金属充填方法で金属層を形成するようにしても良い。金属充填方法としては、粉体金属を圧入で貫通孔1Aに充填する手法がある。粉体金属としては、Cu,Al,In等を用いることができるが、合金としてIn,Sn,Cuを混合させたものを用いても良い。

【0032】

続いて、図3(a)に示すように、配線保護膜25を形成する。

詳細には、シリコン基板1の裏面で貫通孔1Aの内壁面を含む全面に、絶縁物、ここではTEOSを例えば2μm程度の厚みに堆積する。堆積されたTEOSの貫通孔1Aに隣接する部分を、リソグラフィー及びドライエッチングで除去する。以上により、貫通孔1A内でCu層25を覆ってシリコン基板1の裏面に延在し、シリコン基板1の裏面における貫通孔1Aの近傍でCu層25の表面の一部を露出する開口25aを有する配線保護膜27が形成される。

【0033】

続いて、図3(b)に示すように、バンプボール26を形成する。

詳細には、配線保護膜25の開口25aで露出するCu層25上に、バンプボール26を配する。

しかる後、ダイシングによりシリコン基板1からチップごとに切り出し、本実施形態による半導体チップが形成される。

【0034】

以上説明したように、本実施形態では、貫通ビア30のシリコン基板1等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通ビアの側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い半導体チップが実現する。

【0035】

−変形例−

以下、第1の実施形態の諸変形例について説明する。これらの変形例では、第1の実施形態で説明した一括ドライエッチングにおいて、上記した貫通孔1Aと異なる形状の貫通孔を形成する。その他の工程は第1の実施形態と同様である。なお、第1の実施形態と同様の構成部材等については、同符号を付して詳しい説明を省略する。

【0036】

(変形例1)

図9は、第1の実施形態の変形例1における、貫通ビア形成時に用いるレジストマスクを示す概略平面図である。

【0037】

本例では、図9(a)に示すように、シリコン基板1の裏面に、レジストマスク31を形成する。

詳細には、シリコン基板1の裏面で後述する貫通ビアの形成予定部位(接続用電極16に位置整合する部位)にレジストを例えば10μm程度の厚みに塗布し、リソグラフィーで加工して、レジストパターン31を形成する。レジストマスク31の様子を図9(a)と共に図10の平面図に示す。図10の一点鎖線I−Iに沿った断面が図9に相当する。レジストマスク31は、シリコン基板1の裏面を所定形状に露出する第1のパターン31aと、シリコン基板1の第1のパターン31aから露出する部位で柱状突起の形状とされた複数の第2のパターン31bとを有して構成される。第1のパターン31aは、各第2のパターン31bを囲む円環状の開口が全体として矩形状となって連通する開口形状とされている。

【0038】

そして、図9(b)に示すように、レジストマスク31を用いて、シリコン基板1の裏面を一括ドライエッチングする。エッチング条件は、第1の実施形態と同様とする。

以上の一括ドライエッチングにより、シリコン基板1の裏面には、接続用電極16の一部を露出する貫通孔1Bが自己整合的に形成される。第2のパターン31bは、エッチング途中で消失する。貫通孔1Bは、第1のパターン31aで規定された開口面積の大きい第1の開孔1Baと、第2のパターン31bで規定された、複数の柱状突起1cにより画定されてなる第2の開孔1Bbとが連結したものである。第1の開孔1Baは、加工し易い低アスペクト比の開口パターンである。第2の開孔1Bbは、複数の柱状突起1cの存在により、その開口総面積が第1の開孔1Baの開口面積よりも小さく、入り組んだ梁状の開口パターンとされる。本例では、貫通孔1Bは、その最外側面が第1の開孔1Baで規定される。即ち、貫通孔1Bは、当該一括ドライエッチングにより、第1の開孔1Baの最外側面S1と第2の開孔1Bbの最外側面S2とが屈曲点を持たず滑らかに一体化して形成される。

残った第1のパターン31aは、アッシング処理又は薬液を用いたウェットエッチング等により除去される。

【0039】

以上説明したように、本例では、貫通ビアのシリコン基板1等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通ビアの側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い半導体チップが実現する。

【0040】

(変形例2)

図11は、第1の実施形態の変形例2における、貫通ビア形成時に用いるレジストマスクを示す概略平面図である。

【0041】

本例では、図11(a)に示すように、シリコン基板1の裏面に、レジストマスク41を形成する。

詳細には、シリコン基板1の裏面で後述する貫通ビアの形成予定部位(接続用電極16に位置整合する部位)にレジストを例えば10μm程度の厚みに塗布し、リソグラフィーで加工して、レジストパターン41を形成する。レジストマスク41の様子を図11(a)と共に図12の平面図に示す。図12の一点鎖線I−Iに沿った断面が図11に相当する。レジストマスク41は、シリコン基板1の裏面を所定形状に露出する第1のパターン41aと、シリコン基板1の第1のパターン41aから露出する部位で柱状突起の形状とされた複数の第2のパターン41bとを有して構成される。第1のパターン41aは、各第2のパターン41bを囲む円環状の開口が全体として円形状となって連通する開口形状とされている。

【0042】

そして、図11(b)に示すように、レジストマスク41を用いて、シリコン基板1の裏面を一括ドライエッチングする。エッチング条件は、第1の実施形態と同様とする。

以上の一括ドライエッチングにより、シリコン基板1の裏面には、接続用電極16の一部を露出する貫通孔1Cが自己整合的に形成される。第2のパターン41bは、エッチング途中で消失する。貫通孔1Cは、第1のパターン41aで規定された開口面積の大きい第1の開孔1Caと、第2のパターン41bで規定された、複数の柱状突起1dにより画定されてなる第2の開孔1Cbとが連結したものである。第1の開孔1Caは、加工し易い低アスペクト比の開口パターンである。第2の開孔1Cbは、複数の柱状突起1dの存在により、その開口総面積が第1の開孔1Caの開口面積よりも小さく、入り組んだ梁状の開口パターンとされる。本例では、貫通孔1Cは、その最外側面が第1の開孔1Caで規定される。即ち、貫通孔1Cは、当該一括ドライエッチングにより、第1の開孔1Caの最外側面S1と第2の開孔1Cbの最外側面S2とが屈曲点を持たず滑らかに一体化して形成される。

残った第1のパターン41aは、アッシング処理又は薬液を用いたウェットエッチング等により除去される。

【0043】

以上説明したように、本例では、貫通ビアのシリコン基板1等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通ビアの側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い半導体チップが実現する。

【0044】

(変形例3)

図13は、第1の実施形態の変形例3における、貫通ビア形成時に用いるレジストマスクを示す概略平面図である。

【0045】

本例では、図13(a)に示すように、シリコン基板1の裏面に、レジストマスク51を形成する。

詳細には、シリコン基板1の裏面で後述する貫通ビアの形成予定部位(接続用電極16に位置整合する部位)にレジストを例えば10μm程度の厚みに塗布し、リソグラフィーで加工して、レジストパターン51を形成する。レジストマスク51の様子を図13(a)と共に図14の平面図に示す。図14の一点鎖線I−Iに沿った断面が図13に相当する。レジストマスク51は、シリコン基板1の裏面を所定形状に露出する第1のパターン51aと、シリコン基板1の第1のパターン51aから露出する部位で柱状突起の形状とされた複数の第2のパターン51bとを有して構成される。第1のパターン51aは、各第2のパターン51bを囲み、外形が矩形状となって連通する開口形状とされている。

【0046】

そして、図13(b)に示すように、レジストマスク51を用いて、シリコン基板1の裏面を一括ドライエッチングする。エッチング条件は、第1の実施形態と同様とする。

以上の一括ドライエッチングにより、シリコン基板1の裏面には、接続用電極16の一部を露出する貫通孔1Dが自己整合的に形成される。第2のパターン51bは、エッチング途中で消失する。貫通孔1Dは、第1のパターン51aで規定された開口面積の大きい第1の開孔1Daと、第2のパターン51bで規定された、複数の柱状突起1eにより画定されてなる第2の開孔1Dbとが連結したものである。第1の開孔1Daは、加工し易い低アスペクト比の開口パターンである。第2の開孔1Dbは、複数の柱状突起1eの存在により、その開口総面積が第1の開孔1Daの開口面積よりも小さく、入り組んだ梁状の開口パターンとされる。本例では、貫通孔1Dは、その最外側面が第1の開孔1Daで規定される。即ち、貫通孔1Dは、当該一括ドライエッチングにより、第1の開孔1Daの最外側面S1と第2の開孔1Dbの最外側面S2とが屈曲点を持たず滑らかに一体化して形成される。

残った第1のパターン51aは、アッシング処理又は薬液を用いたウェットエッチング等により除去される。

【0047】

以上説明したように、本例では、貫通ビアのシリコン基板1等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通ビアの側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い半導体チップが実現する。

【0048】

(第2の実施形態)

以下、第2の実施形態について説明する。本実施形態では、第1の実施形態と同様に半導体チップを作製するが、その一括ドライエッチングにおいて形成する貫通ビアが異なる点で相違する。なお、第1の実施形態と同様の構成部材等については、同符号を付して詳しい説明を省略する。

図15は、第2の実施形態による半導体チップの製造方法の主要工程を示す概略断面図である。

【0049】

先ず、第1の実施形態と同様に、図1(a)の工程を実行して、シリコン基板1の表面にアクティブ層2を形成する。

【0050】

続いて、図15(a)に示すように、シリコン基板1の裏面に、レジストマスク61を形成する。

詳細には、シリコン基板1の裏面で後述する貫通ビアの形成予定部位(接続用電極16に位置整合する部位)にレジストを例えば10μm程度の厚みに塗布し、リソグラフィーで加工して、レジストパターン61を形成する。レジストマスク61の様子を図15(a)と共に図16の平面図に示す。図16の破線I−Iに沿った断面が図15(a)に相当する。レジストマスク61は、シリコン基板1の裏面を所定形状に露出する第1のパターン61aと、シリコン基板1の第1のパターン61aから露出する部位で入り組んだ梁状とされた第2のパターン61bとを有して構成される。第1のパターン61aは、例えば開口径が200μm程度の円形の開口パターンとされる。第2のパターン61bは、エッチング途中で消失するように、その縦断面において上底幅が下底幅よりも小さい台形状とされる。本実施形態では、第1の実施形態と同様に、リソグラフィーを解調露光で行い、その光強度及び光照射角を調節することにより、第2のパターン61bを上記の縦断面台形状に形成する。第2のパターン61bは、その傾斜角が、45°〜90°の範囲内の値に規定されている。

【0051】

続いて、図15(b)に示すように、レジストマスク61を用いてシリコン基板1の裏面を一括ドライエッチングし、接続用電極16の一部を露出する貫通孔1Eを形成する。エッチング条件は、第1の実施形態における図1(c)のエッチングと同様である。

この一括ドライエッチングにより、シリコン基板1の裏面をドライエッチングし、接続用電極16の一部を露出する貫通孔1Eが自己整合的に形成される。貫通孔1Eは、第1のパターン61aで規定された大径(200μm程度)の第1の開孔1Eaと、第2のパターン61bで規定された小径(50μm程度)の複数の第2の開孔1Ebとが連結したものである。第1の開孔1Eaは、加工し易い低アスペクト比の開口パターンである。第2の開孔1Ebは、複数の梁状構造1fの存在により、その開口総面積が第1の開孔1Eaの開口面積よりも小さく、円状の開口パターンとされる。本実施形態では、貫通孔1Eは、その最外側面が第1の開孔1Eaで規定される。即ち、貫通孔1Eは、当該一括ドライエッチングにより、第1の開孔1Eaの最外側面S1と第2の開孔1Ebの最外側面S2とが屈曲点を持たず滑らかに一体化して形成される。

残った第1のパターン61aは、アッシング処理又は薬液を用いたウェットエッチング等により除去される。

【0052】

続いて、第1の実施形態と同様に、図2(a)〜図2(c)の諸工程を経た後、図3(a)の工程を実行する。これにより、図15(c)に示すように、貫通孔1EにCu層25が配されてなる貫通ビア40が形成される。貫通ビア40は、貫通孔1Eのうち第1の開孔1Eaに形成された第1の電極部40aと、第2の開孔1Ebに形成された第2の電極部40bとが連続的に、最外側面が屈曲点を持たず滑らかに一体形成される。貫通ビア40では、第2の電極部40bが保護膜22の開口22aを通じて接続用電極16と電気的に接続される。第2の電極部40bは第2の開孔1Ebに倣った小径の柱状であって、熱変形し難い形状とされており、ポンピングリアクションの発生が抑止される。

【0053】

そして、レジストマスク26を除去した後、第1の実施形態と同様に、図3(b)、図3(c)諸工程を経て、バンプボール28を形成する。

しかる後、ダイシングによりシリコン基板1からチップごとに切り出し、本実施形態による半導体チップが形成される。

【0054】

以上説明したように、本実施形態では、貫通ビア40のシリコン基板1等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通ビアの側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い半導体チップが実現する。

【0055】

なお、本実施形態でも、第1の実施形態の諸変形例と同様に、上記した貫通孔1Eと異なる形状の貫通孔を形成するようにしても良い。

【0056】

以下、電子デバイス及びその製造方法の諸態様を付記としてまとめて記載する。

【0057】

(付記1)基板と、

前記基板の表面上方に形成された配線と、

前記基板の裏面から前記基板を貫通しており、前記基板の深さ方向において、第1の開孔と、前記第1の開孔よりも開口総面積の小さい第2の開孔とが、最外側面で滑らかに一体化してなる貫通孔に形成されてなる貫通電極と

を含むことを特徴とする電子デバイス。

【0058】

(付記2)前記貫通孔は、前記第1の開孔が前記基板の所定深さまで形成され、前記第2の開孔が記貫通内に設けられた柱状突起で規制されて形成されていることを特徴とする付記1に記載の電子デバイス。

【0059】

(付記3)前記基板の材料からなる複数の前記柱状突起が並設されていることを特徴とする付記2に記載の電子デバイス。

【0060】

(付記4)前記貫通孔は、前記第1の開孔が前記基板の所定深さまで形成され、前記第2の開孔が記貫通内に設けられた梁状構造で規制されて形成されていることを特徴とする付記1に記載の電子デバイス。

【0061】

(付記5)基板の表面上方に配線を形成する工程と、

前記基板の裏面に前記基板を貫通する貫通孔を形成する工程と、

前記貫通孔に、前記配線と電気的に接続される貫通電極を形成する工程と

を含み、

前記貫通孔を、前記基板の深さ方向において、第1の開孔と、前記第1の開孔よりも開口総面積の小さい第2の開孔とが、最外側面で滑らかに一体化するように、エッチングで一括形成することを特徴とする電子デバイスの製造方法。

【0062】

(付記6)前記貫通孔を形成する工程において、

前記基板の裏面に、前記第1の開孔に対応する、開口された第1のパターンと、前記第2の開孔に対応する、エッチング途中で消失する第2のパターンとを有するマスクを形成し、

前記マスクを用いて前記半導体基板を貫通するようにエッチングし、前記第1の開孔と前記第2の開孔とを一括形成することを特徴とする付記5に記載の電子デバイスの製造方法。

【0063】

(付記7)前記第2のパターンは、柱状とされていることを特徴とする付記6に記載の電子デバイスの製造方法。

【0064】

(付記8)前記第2のパターンは、梁形状とされていることを特徴とする付記6に記載の電子デバイスの製造方法。

【0065】

(付記9)前記マスクは、前記第2のパターンは、縦断面において、上底幅が下底幅よりも小さい台形状であることを特徴とする付記6〜8のいずれか1項に記載の電子デバイスの製造方法。

【0066】

(付記10)前記第2のパターンは、前記台形状のテーパ角が45°〜90°の範囲内で規定されており、前記テーパ角により前記第2の開孔の深さを制御することを特徴とする付記9に記載の電子デバイスの製造方法。

【符号の説明】

【0067】

1,101 シリコン基板

1A,1B,1C,1D,1E 貫通孔

1Aa,1Ba,1Ca,1Da,1Ea 第1の開孔

1Ab,1Bb,1Cb,1Db,1Eb 第2の開孔

1b,1c,1d,1e,1f 柱状突起

2,102 アクティブ層

10 MOSトランジスタ

11 ゲート絶縁膜

12 ゲート電極

13 ソース/ドレイン領域

14,17 層間絶縁膜

15 接続プラグ

16 接続用電極

18,102a 配線

20 多層配線層

21,24,31,41,51,61,121,123 レジストマスク

21a,31a,41a,51a,61a 第1のパターン

21b,31b,41b,51b,61b 第2のパターン

22 保護膜

22a,24a,25a 開口

23 Cu層

25 配線保護膜

26,104 バンプボール

30,40,103,111 貫通ビア

30a,40a,112 第1の電極部

30b,40b,113 第2の電極部

114 屈曲点

122 被加工面

122a 突起状のパターン

【技術分野】

【0001】

本発明は、電子デバイス及びその製造方法に関する。

【背景技術】

【0002】

近年、MOS等のトランジスタ、メモリデバイス、MEMS等のセンサデバイスに代表される電子デバイスでは、その集積化が平面的(2次元)構造から立体的(3次元)構造に移行している。

例えば、携帯電話機に搭載される半導体チップは、いわゆるシステム・イン・パッケージ構造のものが主流となりつつある。半導体チップにおける3次元積層化の手法としては、パッケージレベルで行うPoP方式、半導体チップを積層してワイヤ・ボンディングで相互接続するSiP方式等が用いられている。

【0003】

近時では、電子デバイスをチップレベルで積層化する3次元集積技術が盛んに開発されている。

多数の電子デバイスを3次元集積化する場合、電子デバイス相互間で電気的に接続するには、電子デバイスに基板を貫通する貫通電極(貫通ビア)を設け、これを用いて相互接続することが必要である。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−81304号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

電子デバイスの貫通ビアの電極材料としては、多結晶シリコン、タングステン(W)、Cu等が用いられる。多結晶シリコン、Wを用いる場合には、CVD法が適用される。Cuを用いる場合には、電解メッキ法が適用される。後者は、前者よりも低温でビア形成ができることから、電極材料としてCuを用いた貫通ビアが注目されている。

【0006】

電子デバイスでは、その基板の厚みはトランジスタ等の機能素子のサイズに比べて大きい。そのため、貫通ビアはアスペクト比が極めて高くなる。このような高アスペクト比の貫通ビアは、その基板への貫通孔の形成、貫通孔への電極材料の充填のいずれも困難であり、製造コストも大きくなる。従って、基板の面積に余裕があれば、貫通ビアの径を大きくして低アスペクト比の貫通ビアを形成することが望ましい。

【0007】

ところが、貫通ビアの径を大きくすると、貫通ビアの電極材料と基板及びアクティブ層(各種の機能素子及び配線が形成される層)との熱膨張率差が増大し、貫通ビアの周辺部位における変位量が増加するという問題が生じる。

具体例を図17に示す。図17では、半導体チップにおいて、シリコン基板101と、その上に形成されたアクティブ層102と、シリコン基板101を貫通する、Cuを用いた貫通ビア103と、外部接続用のバンプボール104とを簡易に示している。貫通ビア103は、シリコン基板101を貫通してアクティブ層102の配線102aと電気的に接続されている。アクティブ層102の内部構造としては、配線102aのみを示し、機能素子の図示は省略する。

【0008】

半導体チップの製造プロセスにおいて、処理温度TがCuの結晶再配列温度T0よりも大きいと、図18(a)のように、貫通ビア103のCuが熱膨張してアクティブ層102を押し上げ、アクティブ層102が凸状に変形する。一方、処理温度TがT0よりも小さいと、図18(b)のように、貫通電極103のCuが熱収縮してアクティブ層102を引っ張り、アクティブ層102が凹状に変形する。このように、処理温度により貫通電極103がアクティブ層102を上下方向に変動させる、いわゆるポンピングリアクションが生じ、アクティブ層102の機能素子、配線が機械的に破壊されるという問題がある。

【0009】

電流量を減少させることなく上記した貫通ビアの変位を抑える構成を、図19に示す。貫通ビア111は、図19のように、大径の第1の電極部112と、小径の複数の第2の電極部113とが接続されており、第2の電極部113でアクティブ層102と接続される。特許文献1に、その一例が開示されている。

【0010】

しかしながら、上記のように形状の異なる2種類の電極部を接続形成するため、貫通ビア111の側面において、第1の電極部112の第2の電極部113との端部、及び第2の電極部113の第1の電極部112との端部に、屈曲点114が形成される。この屈曲点114では、電極金属であるCuを所期のように形成することが困難であり、Cuの非形成部分が生じることがある。このように、2種類の電極部の接続部分のエッジ形状に起因して、リーク電流等が発生し、デバイス特性の劣化を惹起する。

また、上記のように形状の異なる2種類の電極部を接続形成するには、リソグラフィー工程を少なくとも2回行うことを要し、工程数が多く製造フローも煩雑であるという問題が生じる。

【0011】

本発明は、上記の課題に鑑みてなされたものであり、貫通電極の基板等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通電極の側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い電子デバイス及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

電子デバイスの一態様は、基板と、前記基板の表面上方に形成された配線と、前記基板の裏面から前記基板を貫通しており、前記基板の深さ方向において、第1の開孔と、前記第1の開孔よりも開口総面積の小さい第2の開孔とが、最外側面で一体化してなる貫通孔に形成されてなる貫通電極とを含む。

【0013】

電子デバイスの製造方法の一態様は、基板の表面上方に配線を形成する工程と、前記基板の裏面に前記基板を貫通する貫通孔を形成する工程と、前記貫通孔に、前記配線と電気的に接続される貫通電極を形成する工程とを含み、前記貫通孔を、前記基板の深さ方向において、第1の開孔と、前記第1の開孔よりも開口総面積の小さい第2の開孔とが、最外側面で一体化するように、エッチングで一括形成する。

【発明の効果】

【0014】

上記の諸態様によれば、貫通電極の基板等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通電極の側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い電子デバイスが実現する。

【図面の簡単な説明】

【0015】

【図1】第1の実施形態による半導体チップの製造方法を工程順に示す概略断面図である。

【図2】図1に引き続き、第1の実施形態による半導体チップの製造方法を工程順に示す概略断面図である。

【図3】図2に引き続き、第1の実施形態による半導体チップの製造方法を工程順に示す概略断面図である。

【図4】本実施形態において、貫通ビアの貫通孔を形成するためのレジストマスクを示す概略平面図である。

【図5】通常のレジストマスクを用いたドライエッチングを示す概略断面図である。

【図6】本実施形態のレジストマスクを用いたドライエッチングを示す概略断面図である。

【図7】本実施形態のレジストマスクの傾斜角θとレジストマスクの後退レートとの関係を示す特性図である。

【図8】本実施形態のドライエッチングについて、途中経過を含めて示す概略断面図である。

【図9】第1の実施形態の変形例1における、貫通ビア形成時に用いるレジストマスクを示す概略平面図である。

【図10】変形例1において、貫通ビアの貫通孔を形成するためのレジストマスクを示す概略平面図である。

【図11】第1の実施形態の変形例2における、貫通ビア形成時の一括ドライエッチングを行う際の工程を示す概略断面図である。

【図12】変形例2において、貫通ビアの貫通孔を形成するためのレジストマスクを示す概略平面図である。

【図13】第1の実施形態の変形例3における、貫通ビア形成時の一括ドライエッチングを行う際の工程を示す概略断面図である。

【図14】変形例3において、貫通ビアの貫通孔を形成するためのレジストマスクを示す概略平面図である。

【図15】第2の実施形態による半導体チップの製造方法の主要工程を示す概略断面図である。

【図16】第2の実施形態において、貫通ビアの貫通孔を形成するためのレジストマスクを示す概略平面図である。

【図17】従来の貫通ビアを示す概略断面図である。

【図18】貫通ビアに生じるポンピングリアクションを説明するための概略断面図である。

【図19】図18の問題を解決する一手法を説明するための概略断面図である。

【発明を実施するための形態】

【0016】

以下、電子デバイス及びその製造方法を適用した具体的な諸実施形態について、図面を参照しながら詳細に説明する。各実施形態では、電子デバイスとして、機能素子であるMOSトランジスタが搭載された半導体チップを例示する。電子デバイスとしては、当該半導体チップ以外でも、メモリデバイス、MEMS等のセンサデバイスにも適用可能である。また、基板としてはシリコン基板を例示するが、GaAs等の化合物半導体基板、樹脂等の絶縁基板、プリント基板等にも適用できる。

【0017】

(第1の実施形態)

図1〜図3は、第1の実施形態による半導体チップの製造方法を工程順に示す概略断面図である。

図1(a)に示すように、シリコン基板1の表面にアクティブ層2を形成する。

詳細には、先ず、基板としてシリコンの半導体基板を用意し、この半導体基板の裏面をバックグラインドにより所定の厚み、例えば200μm程度の厚みまで薄化する。これにより、シリコン基板1が形成される。

【0018】

シリコン基板の表面に、ゲート絶縁膜11を介して多結晶シリコン等を用いたゲート電極12を形成し、所定導電型の不純物をイオン注入してソース/ドレイン領域13を形成する。これにより、機能素子であるMOSトランジスタ10が形成される。

シリコン基板1上にMOSトランジスタ10を覆うように層間絶縁膜14を形成し、層間絶縁膜14にソース/ドレイン領域13等と電気的に接続される接続プラグ15を例えば電解メッキ法で形成する。このとき接続プラグ15と同時に、シリコン基板1上の後述する貫通ビアの形成予定部位に接続用電極16を形成する。層間絶縁膜14上に層間絶縁膜17を形成し、層間絶縁膜17に例えば電解メッキ法で接続プラグ15と電気的に接続される配線18を形成する。層間絶縁膜及び接続プラグ、層間絶縁膜及び配線の形成を数回(図示の例では1回)繰り返し行い、多層配線層20を形成する。以上により、MOSトランジスタ10及び多層配線層20を備えたアクティブ層2が形成される。

なお、アクティブ層2のうち、MOSトランジスタ10については、以下の図1(b)以降で図示を省略する。

【0019】

続いて、図1(b)に示すように、シリコン基板1の裏面に、レジストマスク21を形成する。

詳細には、シリコン基板1の裏面で後述する貫通ビアの形成予定部位(接続用電極16に位置整合する部位)にレジストを例えば10μm程度の厚みに塗布し、リソグラフィーで加工して、レジストパターン21を形成する。レジストマスク21の様子を図1(b)と共に図4の平面図に示す。図4の破線I−Iに沿った断面が図1(b)に対応する。レジストマスク21は、シリコン基板1の裏面を所定形状に露出する第1のパターン21aと、シリコン基板1の第1のパターン21aから露出する部位で柱状突起の形状とされた複数の第2のパターン21bとを有して構成される。第1のパターン21aは、例えば開口径が200μm程度の円形の開口パターンとされる。第2のパターン21bは、エッチング途中で消失するように、その縦断面において上底幅が下底幅よりも小さい台形状とされる。本実施形態では、リソグラフィーをいわゆる解調露光で行い、その光強度及び光照射角を調節することにより、第2のパターン21bを上記の縦断面台形状に形成する。第2のパターン21bは、後述するように、その傾斜角が、45°〜90°の範囲内の値に規定されている。

【0020】

ここで、第2のパターン21bを用いたドライエッチングについて説明する。

通常では、図5(a)に示すように、レジストマスク121は、縦断面形状が矩形であり、側面が被加工面122に対して垂直となる。レジストマスク121を用いて被加工面122をドライエッチングすることで、図5(b),(c)に示すように、レジストマスク121の横断面形状に倣って、レジストマスク121の上面と共に被加工面122がエッチングされてゆく。

【0021】

これに対して、図6(a)の第2のパターン21bであるレジストマスク123では、縦断面において上底幅が下底幅よりも小さい台形とされている。レジストマスク123の傾斜角をθとする。レジストマスク123を用いて被加工面122をドライエッチングすると、図6(b)に示すように、レジストマスク123の形状に倣って被加工面122がエッチングされてゆく。このとき、レジストマスク123はその上面でエッチングされてゆくが、第2のパターン21bは、側面に傾斜角を有するため、当該側面でもエッチングされて幅方向に後退してゆく。そして、傾斜角θを適宜調節したレジストマスク123を用いることで、被加工面122のエッチング途中でレジストマスク123は消失する。このとき、被加工面122には、所定高さの突起状のパターン122aが形成される。

【0022】

図7は、レジストマスクの傾斜角θとレジストマスクの後退レートとの関係を示す特性図である。

このように、レジストマスクの後退レートは、傾斜角θが45°のときに最も大きく、90°で最も小さい(ほぼ0)であることが判る。これは、傾斜角を有するレジストマスクでは、ドライエッチングのイオン性が高く、スパッタリングされたマスク材料が再付着せずイオン入射と反対方向に飛散するためにスパッタリング効率が高くなるためである。本実施形態では、この結果を利用して、レジストマスク123の後退レートを0(傾斜角θが90°のとき)から最大値(傾斜角θが45°のとき)までの値で選択し、突起状のパターン122aの高さを制御する。

【0023】

続いて、図1(c)に示すように、レジストマスク21を用いてシリコン基板1の裏面をドライエッチング(異方性ドライエッチング)し、接続用電極16の一部を露出する貫通孔1Aを形成する。ドライエッチングは、エッチングガスに例えばSF6及びC4H8の混合ガスを用い、ガス圧を例えば0.1Torr、投入電力を例えば500Wとし、20μm/分程度のエッチングレートで行う。エッチングの停止は時間制御とする。

【0024】

本実施形態のドライエッチングについて、途中経過を含めて、図8で詳細に示す。図8では、アクティブ層2について接続用電極16のみを図示する。

図8(a)の状態からドライエッチングを開始すると、図8(b),(c)のようにエッチングが進行する。エッチングが進むにつれて、シリコン基板1の裏面では、第1のパターン21aにより窪みが形成されてゆき、窪みの底面で第2のパターン21bによりシリコンが柱状に残されてゆく。それと共に、第2のパターン21bもエッチングされて後退してゆく。そして、エッチング途中で第2のパターン21bは消失する。その後、エッチングが終了するまで、シリコン基板1の窪みと柱状部分とが同様にエッチングされてゆく。第2のパターン21bがない状態でも、柱状部分が自己マスクとして機能するため、柱状部分は形状が維持されたままで窪みのエッチングが進行するが、柱状部分も窪みと同様にエッチングされ、高さが低くなる。図8(d)のように、接続用電極16の一部が露出した時点でエッチングを終了する。このとき、シリコンの柱状部分を柱状突起1bとする。柱状突起1bは、図7で示す第2のパターン21bの後退レートから規定された所期の高さに形成される。

【0025】

以上の一括ドライエッチングにより、シリコン基板1の裏面をドライエッチングし、接続用電極16の一部を露出する貫通孔1Aが自己整合的に形成される。貫通孔1Aは、第1のパターン21aで規定された大径(200μm程度)の第1の開孔1Aaと、第2のパターン21bで規定された、複数の柱状突起1bにより画定されてなる第2の開孔1Abとが連結したものである。第1の開孔1Aaは、加工し易い低アスペクト比の開口パターンである。第2の開孔1Abは、複数の柱状突起1bの存在により、その開口総面積が第1の開孔1Aaの開口面積よりも小さく、入り組んだ梁状の開口パターンとされる。本実施形態では、貫通孔1Aは、その最外側面が第1の開孔1Aaで規定される。即ち、貫通孔1Aは、当該一括ドライエッチングにより、第1の開孔1Aaの最外側面S1と第2の開孔1Abの最外側面S2とが屈曲点を持たず滑らかに一体化して形成される。

残った第1のパターン21aは、アッシング処理又は薬液を用いたウェットエッチング等により除去される。

【0026】

なお、貫通孔1Aは、その最外側面が若干テーパ状となるように、一括ドライエッチングで形成しても良い。この場合にも、貫通孔1Aは、第1の開孔1Aaの最外側面S1と第2の開孔1Abの最外側面S2とが屈曲点を持たず滑らかに一体化して形成される。

【0027】

続いて、図2(a)に示すように、貫通孔1Aの内壁面を覆う保護膜22を形成する。

詳細には、例えばCVD法により、シリコン基板1の貫通孔1Aの内壁面を覆うように、Cuのシリコン基板1内への拡散を防止する機能を持つ絶縁物、例えばSiNを500nm程度の厚みに堆積する。これにより、貫通孔1Aの内壁面を覆う保護膜22が形成される。

【0028】

続いて、図2(b)に示すように、貫通孔1Aの底部分(第2の開孔1Abの底部分)の保護膜22を除去する。

詳細には、シリコン基板1の裏面で貫通孔1A内にかけて、第2の開孔1Abの底部分の底部分に位置整合する部位に開口が形成されたレジストマスクを形成し、このレジストマスクを用いてボトムエッチングを行う。これにより、保護膜22は第2の開孔1Abの底部分のみで除去されて開口22aが形成され、開口22aから接続用電極16の表面の一部を露出する。

【0029】

続いて、図2(c)に示すように、Cu層23を形成する。

詳細には、先ず、例えば物理スパッタ法により、シリコン基板1の貫通孔1Aの内壁面を覆うように、Tiを20μm程度、Cuを100nm程度の厚みに順次成膜する。これにより、シリコン基板1の貫通孔1Aの内壁面を、保護膜22の開口22aでは直接的に、その他の部分では保護膜22を介して覆う、不図示のライナー層及びCuシード層が形成される。

【0030】

次に、Cu層23を形成する。

Cu層23の形成には、例えば電解メッキ法を用い、セミアディティブ法で行う。詳細には、シリコン基板1の裏面で貫通孔1A及びその周囲を適宜露出する開口24aを有するレジストマスク24を形成する。電解メッキ法により、レジストマスク24の開口24aから露出する部分にCuを例えば5μm〜20μm程度の厚みにメッキ成膜する。Cu層23は、貫通孔1Aを充填するように形成しても良い。これにより、貫通孔1Aのうち第2の開孔1AbをCuで充填し、第1の開孔1Aaの内壁面を覆うCu層23が形成される。以上により、貫通孔1AにCu層25が配されてなる貫通ビア30が形成される。貫通ビア30は、貫通孔1Aのうち第1の開孔1Aaに形成された第1の電極部30aと、第2の開孔1Abに形成された第2の電極部30bとが連続的に、最外側面が屈曲点を持たず滑らかに一体形成される。貫通ビア30では、第2の電極部30bが保護膜22の開口22aを通じて接続用電極16と電気的に接続される。第2の電極部30bは、第2の開孔1Abに倣って入り組んだ梁状であって、熱変形し難い形状とされており、ポンピングリアクションの発生が抑止される。

レジストマスク24は、アッシング処理又は薬液を用いたウェットエッチング等により除去される。

【0031】

なお、Cu層23をメッキ形成する代わりに、導電性ペーストを用いた金属充填方法で金属層を形成するようにしても良い。金属充填方法としては、粉体金属を圧入で貫通孔1Aに充填する手法がある。粉体金属としては、Cu,Al,In等を用いることができるが、合金としてIn,Sn,Cuを混合させたものを用いても良い。

【0032】

続いて、図3(a)に示すように、配線保護膜25を形成する。

詳細には、シリコン基板1の裏面で貫通孔1Aの内壁面を含む全面に、絶縁物、ここではTEOSを例えば2μm程度の厚みに堆積する。堆積されたTEOSの貫通孔1Aに隣接する部分を、リソグラフィー及びドライエッチングで除去する。以上により、貫通孔1A内でCu層25を覆ってシリコン基板1の裏面に延在し、シリコン基板1の裏面における貫通孔1Aの近傍でCu層25の表面の一部を露出する開口25aを有する配線保護膜27が形成される。

【0033】

続いて、図3(b)に示すように、バンプボール26を形成する。

詳細には、配線保護膜25の開口25aで露出するCu層25上に、バンプボール26を配する。

しかる後、ダイシングによりシリコン基板1からチップごとに切り出し、本実施形態による半導体チップが形成される。

【0034】

以上説明したように、本実施形態では、貫通ビア30のシリコン基板1等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通ビアの側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い半導体チップが実現する。

【0035】

−変形例−

以下、第1の実施形態の諸変形例について説明する。これらの変形例では、第1の実施形態で説明した一括ドライエッチングにおいて、上記した貫通孔1Aと異なる形状の貫通孔を形成する。その他の工程は第1の実施形態と同様である。なお、第1の実施形態と同様の構成部材等については、同符号を付して詳しい説明を省略する。

【0036】

(変形例1)

図9は、第1の実施形態の変形例1における、貫通ビア形成時に用いるレジストマスクを示す概略平面図である。

【0037】

本例では、図9(a)に示すように、シリコン基板1の裏面に、レジストマスク31を形成する。

詳細には、シリコン基板1の裏面で後述する貫通ビアの形成予定部位(接続用電極16に位置整合する部位)にレジストを例えば10μm程度の厚みに塗布し、リソグラフィーで加工して、レジストパターン31を形成する。レジストマスク31の様子を図9(a)と共に図10の平面図に示す。図10の一点鎖線I−Iに沿った断面が図9に相当する。レジストマスク31は、シリコン基板1の裏面を所定形状に露出する第1のパターン31aと、シリコン基板1の第1のパターン31aから露出する部位で柱状突起の形状とされた複数の第2のパターン31bとを有して構成される。第1のパターン31aは、各第2のパターン31bを囲む円環状の開口が全体として矩形状となって連通する開口形状とされている。

【0038】

そして、図9(b)に示すように、レジストマスク31を用いて、シリコン基板1の裏面を一括ドライエッチングする。エッチング条件は、第1の実施形態と同様とする。

以上の一括ドライエッチングにより、シリコン基板1の裏面には、接続用電極16の一部を露出する貫通孔1Bが自己整合的に形成される。第2のパターン31bは、エッチング途中で消失する。貫通孔1Bは、第1のパターン31aで規定された開口面積の大きい第1の開孔1Baと、第2のパターン31bで規定された、複数の柱状突起1cにより画定されてなる第2の開孔1Bbとが連結したものである。第1の開孔1Baは、加工し易い低アスペクト比の開口パターンである。第2の開孔1Bbは、複数の柱状突起1cの存在により、その開口総面積が第1の開孔1Baの開口面積よりも小さく、入り組んだ梁状の開口パターンとされる。本例では、貫通孔1Bは、その最外側面が第1の開孔1Baで規定される。即ち、貫通孔1Bは、当該一括ドライエッチングにより、第1の開孔1Baの最外側面S1と第2の開孔1Bbの最外側面S2とが屈曲点を持たず滑らかに一体化して形成される。

残った第1のパターン31aは、アッシング処理又は薬液を用いたウェットエッチング等により除去される。

【0039】

以上説明したように、本例では、貫通ビアのシリコン基板1等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通ビアの側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い半導体チップが実現する。

【0040】

(変形例2)

図11は、第1の実施形態の変形例2における、貫通ビア形成時に用いるレジストマスクを示す概略平面図である。

【0041】

本例では、図11(a)に示すように、シリコン基板1の裏面に、レジストマスク41を形成する。

詳細には、シリコン基板1の裏面で後述する貫通ビアの形成予定部位(接続用電極16に位置整合する部位)にレジストを例えば10μm程度の厚みに塗布し、リソグラフィーで加工して、レジストパターン41を形成する。レジストマスク41の様子を図11(a)と共に図12の平面図に示す。図12の一点鎖線I−Iに沿った断面が図11に相当する。レジストマスク41は、シリコン基板1の裏面を所定形状に露出する第1のパターン41aと、シリコン基板1の第1のパターン41aから露出する部位で柱状突起の形状とされた複数の第2のパターン41bとを有して構成される。第1のパターン41aは、各第2のパターン41bを囲む円環状の開口が全体として円形状となって連通する開口形状とされている。

【0042】

そして、図11(b)に示すように、レジストマスク41を用いて、シリコン基板1の裏面を一括ドライエッチングする。エッチング条件は、第1の実施形態と同様とする。

以上の一括ドライエッチングにより、シリコン基板1の裏面には、接続用電極16の一部を露出する貫通孔1Cが自己整合的に形成される。第2のパターン41bは、エッチング途中で消失する。貫通孔1Cは、第1のパターン41aで規定された開口面積の大きい第1の開孔1Caと、第2のパターン41bで規定された、複数の柱状突起1dにより画定されてなる第2の開孔1Cbとが連結したものである。第1の開孔1Caは、加工し易い低アスペクト比の開口パターンである。第2の開孔1Cbは、複数の柱状突起1dの存在により、その開口総面積が第1の開孔1Caの開口面積よりも小さく、入り組んだ梁状の開口パターンとされる。本例では、貫通孔1Cは、その最外側面が第1の開孔1Caで規定される。即ち、貫通孔1Cは、当該一括ドライエッチングにより、第1の開孔1Caの最外側面S1と第2の開孔1Cbの最外側面S2とが屈曲点を持たず滑らかに一体化して形成される。

残った第1のパターン41aは、アッシング処理又は薬液を用いたウェットエッチング等により除去される。

【0043】

以上説明したように、本例では、貫通ビアのシリコン基板1等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通ビアの側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い半導体チップが実現する。

【0044】

(変形例3)

図13は、第1の実施形態の変形例3における、貫通ビア形成時に用いるレジストマスクを示す概略平面図である。

【0045】

本例では、図13(a)に示すように、シリコン基板1の裏面に、レジストマスク51を形成する。

詳細には、シリコン基板1の裏面で後述する貫通ビアの形成予定部位(接続用電極16に位置整合する部位)にレジストを例えば10μm程度の厚みに塗布し、リソグラフィーで加工して、レジストパターン51を形成する。レジストマスク51の様子を図13(a)と共に図14の平面図に示す。図14の一点鎖線I−Iに沿った断面が図13に相当する。レジストマスク51は、シリコン基板1の裏面を所定形状に露出する第1のパターン51aと、シリコン基板1の第1のパターン51aから露出する部位で柱状突起の形状とされた複数の第2のパターン51bとを有して構成される。第1のパターン51aは、各第2のパターン51bを囲み、外形が矩形状となって連通する開口形状とされている。

【0046】

そして、図13(b)に示すように、レジストマスク51を用いて、シリコン基板1の裏面を一括ドライエッチングする。エッチング条件は、第1の実施形態と同様とする。

以上の一括ドライエッチングにより、シリコン基板1の裏面には、接続用電極16の一部を露出する貫通孔1Dが自己整合的に形成される。第2のパターン51bは、エッチング途中で消失する。貫通孔1Dは、第1のパターン51aで規定された開口面積の大きい第1の開孔1Daと、第2のパターン51bで規定された、複数の柱状突起1eにより画定されてなる第2の開孔1Dbとが連結したものである。第1の開孔1Daは、加工し易い低アスペクト比の開口パターンである。第2の開孔1Dbは、複数の柱状突起1eの存在により、その開口総面積が第1の開孔1Daの開口面積よりも小さく、入り組んだ梁状の開口パターンとされる。本例では、貫通孔1Dは、その最外側面が第1の開孔1Daで規定される。即ち、貫通孔1Dは、当該一括ドライエッチングにより、第1の開孔1Daの最外側面S1と第2の開孔1Dbの最外側面S2とが屈曲点を持たず滑らかに一体化して形成される。

残った第1のパターン51aは、アッシング処理又は薬液を用いたウェットエッチング等により除去される。

【0047】

以上説明したように、本例では、貫通ビアのシリコン基板1等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通ビアの側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い半導体チップが実現する。

【0048】

(第2の実施形態)

以下、第2の実施形態について説明する。本実施形態では、第1の実施形態と同様に半導体チップを作製するが、その一括ドライエッチングにおいて形成する貫通ビアが異なる点で相違する。なお、第1の実施形態と同様の構成部材等については、同符号を付して詳しい説明を省略する。

図15は、第2の実施形態による半導体チップの製造方法の主要工程を示す概略断面図である。

【0049】

先ず、第1の実施形態と同様に、図1(a)の工程を実行して、シリコン基板1の表面にアクティブ層2を形成する。

【0050】

続いて、図15(a)に示すように、シリコン基板1の裏面に、レジストマスク61を形成する。

詳細には、シリコン基板1の裏面で後述する貫通ビアの形成予定部位(接続用電極16に位置整合する部位)にレジストを例えば10μm程度の厚みに塗布し、リソグラフィーで加工して、レジストパターン61を形成する。レジストマスク61の様子を図15(a)と共に図16の平面図に示す。図16の破線I−Iに沿った断面が図15(a)に相当する。レジストマスク61は、シリコン基板1の裏面を所定形状に露出する第1のパターン61aと、シリコン基板1の第1のパターン61aから露出する部位で入り組んだ梁状とされた第2のパターン61bとを有して構成される。第1のパターン61aは、例えば開口径が200μm程度の円形の開口パターンとされる。第2のパターン61bは、エッチング途中で消失するように、その縦断面において上底幅が下底幅よりも小さい台形状とされる。本実施形態では、第1の実施形態と同様に、リソグラフィーを解調露光で行い、その光強度及び光照射角を調節することにより、第2のパターン61bを上記の縦断面台形状に形成する。第2のパターン61bは、その傾斜角が、45°〜90°の範囲内の値に規定されている。

【0051】

続いて、図15(b)に示すように、レジストマスク61を用いてシリコン基板1の裏面を一括ドライエッチングし、接続用電極16の一部を露出する貫通孔1Eを形成する。エッチング条件は、第1の実施形態における図1(c)のエッチングと同様である。

この一括ドライエッチングにより、シリコン基板1の裏面をドライエッチングし、接続用電極16の一部を露出する貫通孔1Eが自己整合的に形成される。貫通孔1Eは、第1のパターン61aで規定された大径(200μm程度)の第1の開孔1Eaと、第2のパターン61bで規定された小径(50μm程度)の複数の第2の開孔1Ebとが連結したものである。第1の開孔1Eaは、加工し易い低アスペクト比の開口パターンである。第2の開孔1Ebは、複数の梁状構造1fの存在により、その開口総面積が第1の開孔1Eaの開口面積よりも小さく、円状の開口パターンとされる。本実施形態では、貫通孔1Eは、その最外側面が第1の開孔1Eaで規定される。即ち、貫通孔1Eは、当該一括ドライエッチングにより、第1の開孔1Eaの最外側面S1と第2の開孔1Ebの最外側面S2とが屈曲点を持たず滑らかに一体化して形成される。

残った第1のパターン61aは、アッシング処理又は薬液を用いたウェットエッチング等により除去される。

【0052】

続いて、第1の実施形態と同様に、図2(a)〜図2(c)の諸工程を経た後、図3(a)の工程を実行する。これにより、図15(c)に示すように、貫通孔1EにCu層25が配されてなる貫通ビア40が形成される。貫通ビア40は、貫通孔1Eのうち第1の開孔1Eaに形成された第1の電極部40aと、第2の開孔1Ebに形成された第2の電極部40bとが連続的に、最外側面が屈曲点を持たず滑らかに一体形成される。貫通ビア40では、第2の電極部40bが保護膜22の開口22aを通じて接続用電極16と電気的に接続される。第2の電極部40bは第2の開孔1Ebに倣った小径の柱状であって、熱変形し難い形状とされており、ポンピングリアクションの発生が抑止される。

【0053】

そして、レジストマスク26を除去した後、第1の実施形態と同様に、図3(b)、図3(c)諸工程を経て、バンプボール28を形成する。

しかる後、ダイシングによりシリコン基板1からチップごとに切り出し、本実施形態による半導体チップが形成される。

【0054】

以上説明したように、本実施形態では、貫通ビア40のシリコン基板1等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通ビアの側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い半導体チップが実現する。

【0055】

なお、本実施形態でも、第1の実施形態の諸変形例と同様に、上記した貫通孔1Eと異なる形状の貫通孔を形成するようにしても良い。

【0056】

以下、電子デバイス及びその製造方法の諸態様を付記としてまとめて記載する。

【0057】

(付記1)基板と、

前記基板の表面上方に形成された配線と、

前記基板の裏面から前記基板を貫通しており、前記基板の深さ方向において、第1の開孔と、前記第1の開孔よりも開口総面積の小さい第2の開孔とが、最外側面で滑らかに一体化してなる貫通孔に形成されてなる貫通電極と

を含むことを特徴とする電子デバイス。

【0058】

(付記2)前記貫通孔は、前記第1の開孔が前記基板の所定深さまで形成され、前記第2の開孔が記貫通内に設けられた柱状突起で規制されて形成されていることを特徴とする付記1に記載の電子デバイス。

【0059】

(付記3)前記基板の材料からなる複数の前記柱状突起が並設されていることを特徴とする付記2に記載の電子デバイス。

【0060】

(付記4)前記貫通孔は、前記第1の開孔が前記基板の所定深さまで形成され、前記第2の開孔が記貫通内に設けられた梁状構造で規制されて形成されていることを特徴とする付記1に記載の電子デバイス。

【0061】

(付記5)基板の表面上方に配線を形成する工程と、

前記基板の裏面に前記基板を貫通する貫通孔を形成する工程と、

前記貫通孔に、前記配線と電気的に接続される貫通電極を形成する工程と

を含み、

前記貫通孔を、前記基板の深さ方向において、第1の開孔と、前記第1の開孔よりも開口総面積の小さい第2の開孔とが、最外側面で滑らかに一体化するように、エッチングで一括形成することを特徴とする電子デバイスの製造方法。

【0062】

(付記6)前記貫通孔を形成する工程において、

前記基板の裏面に、前記第1の開孔に対応する、開口された第1のパターンと、前記第2の開孔に対応する、エッチング途中で消失する第2のパターンとを有するマスクを形成し、

前記マスクを用いて前記半導体基板を貫通するようにエッチングし、前記第1の開孔と前記第2の開孔とを一括形成することを特徴とする付記5に記載の電子デバイスの製造方法。

【0063】

(付記7)前記第2のパターンは、柱状とされていることを特徴とする付記6に記載の電子デバイスの製造方法。

【0064】

(付記8)前記第2のパターンは、梁形状とされていることを特徴とする付記6に記載の電子デバイスの製造方法。

【0065】

(付記9)前記マスクは、前記第2のパターンは、縦断面において、上底幅が下底幅よりも小さい台形状であることを特徴とする付記6〜8のいずれか1項に記載の電子デバイスの製造方法。

【0066】

(付記10)前記第2のパターンは、前記台形状のテーパ角が45°〜90°の範囲内で規定されており、前記テーパ角により前記第2の開孔の深さを制御することを特徴とする付記9に記載の電子デバイスの製造方法。

【符号の説明】

【0067】

1,101 シリコン基板

1A,1B,1C,1D,1E 貫通孔

1Aa,1Ba,1Ca,1Da,1Ea 第1の開孔

1Ab,1Bb,1Cb,1Db,1Eb 第2の開孔

1b,1c,1d,1e,1f 柱状突起

2,102 アクティブ層

10 MOSトランジスタ

11 ゲート絶縁膜

12 ゲート電極

13 ソース/ドレイン領域

14,17 層間絶縁膜

15 接続プラグ

16 接続用電極

18,102a 配線

20 多層配線層

21,24,31,41,51,61,121,123 レジストマスク

21a,31a,41a,51a,61a 第1のパターン

21b,31b,41b,51b,61b 第2のパターン

22 保護膜

22a,24a,25a 開口

23 Cu層

25 配線保護膜

26,104 バンプボール

30,40,103,111 貫通ビア

30a,40a,112 第1の電極部

30b,40b,113 第2の電極部

114 屈曲点

122 被加工面

122a 突起状のパターン

【特許請求の範囲】

【請求項1】

基板と、

前記基板の表面上方に形成された配線と、

前記基板の裏面から前記基板を貫通しており、前記基板の深さ方向において、第1の開孔と、前記第1の開孔よりも開口総面積の小さい第2の開孔とが、最外側面で一体化してなる貫通孔に形成されてなる貫通電極と

を含むことを特徴とする電子デバイス。

【請求項2】

前記貫通孔は、前記第1の開孔が前記基板の所定深さまで形成され、前記第2の開孔が記貫通内に設けられた柱状突起で規制されて形成されていることを特徴とする請求項1に記載の電子デバイス。

【請求項3】

基板の表面上方に配線を形成する工程と、

前記基板の裏面に前記基板を貫通する貫通孔を形成する工程と、

前記貫通孔に、前記配線と電気的に接続される貫通電極を形成する工程と

を含み、

前記貫通孔を、前記基板の深さ方向において、第1の開孔と、前記第1の開孔よりも開口総面積の小さい第2の開孔とが、最外側面で一体化するように、エッチングで一括形成することを特徴とする電子デバイスの製造方法。

【請求項4】

前記貫通孔を形成する工程において、

前記基板の裏面に、前記第1の開孔に対応する、開口された第1のパターンと、前記第2の開孔に対応する、エッチング途中で消失する第2のパターンとを有するマスクを形成し、

前記マスクを用いて前記半導体基板を貫通するようにエッチングし、前記第1の開孔と前記第2の開孔とを一括形成することを特徴とする請求項3に記載の電子デバイスの製造方法。

【請求項5】

前記第2のパターンは、柱状とされていることを特徴とする請求項4に記載の電子デバイスの製造方法。

【請求項6】

前記第2のパターンは、梁形状とされていることを特徴とする請求項4に記載の電子デバイスの製造方法。

【請求項1】

基板と、

前記基板の表面上方に形成された配線と、

前記基板の裏面から前記基板を貫通しており、前記基板の深さ方向において、第1の開孔と、前記第1の開孔よりも開口総面積の小さい第2の開孔とが、最外側面で一体化してなる貫通孔に形成されてなる貫通電極と

を含むことを特徴とする電子デバイス。

【請求項2】

前記貫通孔は、前記第1の開孔が前記基板の所定深さまで形成され、前記第2の開孔が記貫通内に設けられた柱状突起で規制されて形成されていることを特徴とする請求項1に記載の電子デバイス。

【請求項3】

基板の表面上方に配線を形成する工程と、

前記基板の裏面に前記基板を貫通する貫通孔を形成する工程と、

前記貫通孔に、前記配線と電気的に接続される貫通電極を形成する工程と

を含み、

前記貫通孔を、前記基板の深さ方向において、第1の開孔と、前記第1の開孔よりも開口総面積の小さい第2の開孔とが、最外側面で一体化するように、エッチングで一括形成することを特徴とする電子デバイスの製造方法。

【請求項4】

前記貫通孔を形成する工程において、

前記基板の裏面に、前記第1の開孔に対応する、開口された第1のパターンと、前記第2の開孔に対応する、エッチング途中で消失する第2のパターンとを有するマスクを形成し、

前記マスクを用いて前記半導体基板を貫通するようにエッチングし、前記第1の開孔と前記第2の開孔とを一括形成することを特徴とする請求項3に記載の電子デバイスの製造方法。

【請求項5】

前記第2のパターンは、柱状とされていることを特徴とする請求項4に記載の電子デバイスの製造方法。

【請求項6】

前記第2のパターンは、梁形状とされていることを特徴とする請求項4に記載の電子デバイスの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2013−21073(P2013−21073A)

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願番号】特願2011−152058(P2011−152058)

【出願日】平成23年7月8日(2011.7.8)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願日】平成23年7月8日(2011.7.8)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]