電子デバイス用エピタキシャル基板およびその製造方法

【課題】横方向リーク電流の低減および横方向耐圧特性を良好に両立させることができるエピタキシャル基板およびその製造方法を提供する。

【解決手段】Si単結晶基2上にバッファ3と複数層のIII族窒化物層をエピタキシャル成長させて形成した主積層体4とを具え、横方向を電流導通方向とする電子デバイス用エピタキシャル基板であって、前記バッファ3は、前記Si単結晶基板2と接する初期成長層5および該初期成長層上の超格子多層構造からなる超格子積層体6を少なくとも有し、前記初期成長層5はAlN材料からなり、かつ前記超格子積層体6はBAlGaInN材料からなる第1層6aおよび該第1層6aとはバンドギャップの異なるBAlGaInN材料からなる第2層6bを交互に積層してなり、前記超格子積層体6と、前記主積層体4の前記バッファ側の部分は、ともにC濃度が1×1018/cm3以上であることを特徴とする。

【解決手段】Si単結晶基2上にバッファ3と複数層のIII族窒化物層をエピタキシャル成長させて形成した主積層体4とを具え、横方向を電流導通方向とする電子デバイス用エピタキシャル基板であって、前記バッファ3は、前記Si単結晶基板2と接する初期成長層5および該初期成長層上の超格子多層構造からなる超格子積層体6を少なくとも有し、前記初期成長層5はAlN材料からなり、かつ前記超格子積層体6はBAlGaInN材料からなる第1層6aおよび該第1層6aとはバンドギャップの異なるBAlGaInN材料からなる第2層6bを交互に積層してなり、前記超格子積層体6と、前記主積層体4の前記バッファ側の部分は、ともにC濃度が1×1018/cm3以上であることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子デバイス用エピタキシャル基板およびその製造方法、特に、HEMT用エピタキシャル基板およびその製造方法に関する。

【背景技術】

【0002】

近年、IC用デバイス等の高速化に伴い、高速の電界効果トランジスタ(FET: Field effect transistor)として、高電子移動度トランジスタ(HEMT: High electron mobility transistor)が広く用いられるようになっている。このような電界効果型のトランジスタは、例えば図1に模式的に示されるように、基板21上にチャネル層22および電子供給層23を積層し、この電子供給層23の表面にソース電極24、ドレイン電極25およびゲート電極26を配設することにより形成され、デバイスの動作時には、ソース電極24、電子供給層23、チャネル層22、電子供給層23およびドレイン電極25の順に電子が移動して、横方向を電流導通方向とし、この横方向の電子の移動は、ゲート電極26に印加される電圧により制御される。HEMTにおいて、バンドギャップの異なる電子供給層23およびチャネル層22の接合界面に生じる電子は、通常の半導体内と比較して高速で移動することができる。

【0003】

このように、横方向の電子の移動、すなわち電流は、ゲート電圧によって制御されるが、一般に、ゲート電圧をOFFにしても電流が0になることはない。このゲート電圧OFF時に流れる電流のことをリーク電流といい、リーク電流が増えると消費電力が増大し、その結果、発熱などの問題が生じることになる。このリーク電流は、一般に、横方向リーク電流と縦方向リーク電流とに分けられ、横方向リーク電流とは、電子供給層23側表面に配置した2電極間(たとえば、ソース電極24とドレイン電極25間)に流れるリーク電流のことをいい、縦方向リーク電流とは、電子供給層23側表面と基板21側表面にそれぞれ配置した2電極間に流れるリーク電流のことをいう。

【0004】

特許文献1には、基板上に、バッファ層、炭素濃度遷移層、チャネル層および電子供給層を具えるHEMTにおいて、チャネル層からバッファ層へ向かって炭素濃度が増加するように形成することにより、バッファ層および炭素濃度遷移層中に発生する横方向リーク電流を低減すると共に、横方向の耐圧を向上させる技術が開示されている。

【0005】

また、特許文献2には、基板上に超格子バッファ層、チャネル層および電子供給層を具える半導体デバイスにおいて、超格子バッファ層に炭素を含有させることにより、半導体電子デバイスの横方向リーク電流を抑止し、横方向耐圧を向上させる技術が開示されている。

【0006】

さらに、特許文献3には、単結晶基板上に形成された第1のIII族窒化物下地層と、この第1のIII族窒化物下地層上に形成された第2のIII族窒化物下地層との界面に、アクセプタ不純物を含み、このアクセプタ不純物の濃度を、上記界面から第2のIII族窒化物下地層の厚さ方向において減少させることにより、半導体電子デバイスの横方向リーク電流を抑止する技術が開示されている。

【0007】

ところで、HEMTを高周波数で動作させる場合には、前記リーク電流を低減させた上で、かつ高周波信号印加時の損失を低減する必要がある。この損失は、基板またはその上のエピタキシャル膜に電荷が存在する場合に、空乏層が効率的に広がらず、基板表面に配置した電極と容量性あるいは誘導性の相互作用を起こすことにより生じるものである。

【0008】

そこで、特許文献4には、Si単結晶基板の比抵抗を高くして不純物の混入を防ぐことにより、キャリアを低減させ、高周波領域での半導体電子デバイスの損失を抑制する技術が開示されている。

【0009】

しかしながら、特許文献1に記載された発明においては、基板上にIII族窒化物層を成長する際、GaN系低温バッファ層を用いるため、基板にSiを用いる場合にGaとの反応によるピット等の貫通欠陥を発生し、縦方向耐圧を悪化させるという問題があった。

また、特許文献2に記載された発明は、超格子バッファ層内のリークは抑制できるものの、チャネル層と超格子バッファ層界面でのリークを十分に抑制できず、結果として、縦方向および横方向耐圧を共に劣化させる原因となっていた。

さらに、特許文献3、4は縦方向耐圧について考慮しておらず、バッファ層の耐圧に対する検討は全くされていないため、Si基板のような半導体基板に適応した場合、縦方向耐圧を確保することができなかった。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2007−251144号公報

【特許文献2】特開2005−85852号公報

【特許文献3】特開2003−282598号公報

【特許文献4】特表2008−522447号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明の目的は、横方向リーク電流の低減および横方向耐圧特性を良好に両立させ、かつ縦方向耐圧を向上させることができる電子デバイス用エピタキシャル基板およびその製造方法を提供することにある。

【課題を解決するための手段】

【0012】

上記目的を達成するため、本発明の要旨構成は以下のとおりである。

(1)Si単結晶基板と、該Si単結晶基板上に形成した絶縁層としてのバッファと、該バッファ上に複数層のIII族窒化物層をエピタキシャル成長させて形成した主積層体とを具え、横方向を電流導通方向とする電子デバイス用エピタキシャル基板であって、前記バッファは、前記Si単結晶基板と接する初期成長層および該初期成長層上の超格子多層構造からなる超格子積層体を少なくとも有し、前記初期成長層はAlN材料からなり、かつ前記超格子積層体はBa1Alb1Gac1Ind1N(0≦a1≦1, 0≦b1≦1, 0≦c1≦1, 0≦d1≦1, a1+b1+c1+d1=1)材料からなる第1層および該第1層とはバンドギャップの異なるBa2Alb2Gac2Ind2N(0≦a2≦1, 0≦b2≦1, 0≦c2≦1, 0≦d2≦1, a2+b2+c2+d2=1)材料からなる第2層を交互に積層してなり、前記超格子積層体と、前記主積層体の前記バッファ側の部分は、ともにC濃度が1×1018/cm3以上であることを特徴とする電子デバイス用エピタキシャル基板。

【0013】

(2)前記第1層がAlN材料からなり、前記第2層がAlb2Gac2N(a2=0, 0<b2≦0.5,0.5≦c2<1,d2=0)材料からなる上記(1)に記載の電子デバイス用エピタキシャル基板。

【0014】

(3)前記Si単結晶基板は、比抵抗が1000Ω・cm以上で、前記初期成長層から0.1μmの深さまでのIII族原子の合計の最大濃度が1×1016/cm3以下であり、かつ前記初期成長層から0.3μmの深さの位置でのIII族原子の合計濃度が1×1015/cm3以下である上記(1)または(2)に記載の電子デバイス用エピタキシャル基板。

【0015】

(4)Si単結晶基板上に、絶縁層としてのバッファと、該バッファ上に複数層のIII族窒化物層をエピタキシャル成長させた主積層体とを順に形成した、横方向を電流導通方向とする電子デバイス用エピタキシャル基板の製造方法であって、前記バッファは、前記Si単結晶基板と接する初期成長層および該初期成長層上の超格子多層構造からなる超格子積層体を少なくとも有し、前記初期成長層はAlN材料からなり、かつ前記超格子積層体はBa1Alb1Gac1Ind1N(0≦a1≦1, 0≦b1≦1, 0≦c1≦1, 0≦d1≦1, a1+b1+c1+d1=1)材料からなる第1層および該第1層とはバンドギャップの異なるBa2Alb2Gac2Ind2N(0≦a2≦1, 0≦b2≦1, 0≦c2≦1, 0≦d2≦1, a2+b2+c2+d2=1)材料からなる第2層を交互に積層してなり、前記超格子積層体と、前記主積層体の前記バッファ側の部分は、ともにC濃度が1018/cm3以上となるよう形成されることを特徴とする電子デバイス用エピタキシャル基板の製造方法。

【0016】

(5)前記Si単結晶基板は、比抵抗が1000Ω・cm以上で、前記初期成長層から0.1μmの深さまでのIII族原子の合計の最大濃度が1×1016/cm3以下であり、かつ前記初期成長層から0.3μmの深さの位置でのIII族原子の合計濃度が1×1015/cm3以下となるよう形成される上記(4)に記載の電子デバイス用エピタキシャル基板の製造方法。

【発明の効果】

【0017】

本発明の電子デバイス用エピタキシャル基板は、AlN材料からなる初期成長層および所定の超格子積層体を有するバッファならびに所定の主積層体を具え、これら超格子積層体と主積層体のバッファ側の部分とが、ともに1×1018/cm3以上のC濃度を有することにより、横方向リーク電流の低減および横方向耐圧特性を良好に両立させるのみでなく、縦方向耐圧を向上させることができる。

【0018】

また、本発明は、AlN材料からなる初期成長層および所定の超格子積層体を有するバッファならびに所定の主積層体を具え、これら超格子積層体と主積層体のバッファ側の部分とが、ともに1×1018/cm3以上のC濃度を有することにより、横方向リーク電流の低減および横方向耐圧特性を良好に両立させるのみでなく、縦方向耐圧を向上させることができる電子デバイス用エピタキシャル基板を製造することができる。

【0019】

さらに、本発明の電子デバイス用エピタキシャル基板は、Si単結晶基板が1000Ω・cm以上の比抵抗を有し、初期成長層から0.1μmの深さまでのIII族原子の合計の最大濃度を1×1016/cm3以下とし、かつ初期成長層から0.3μmの深さの位置でのIII族原子の合計濃度を1×1015/cm3以下とすることにより、上述した効果に加え、高周波動作時の損失を低減することができる。

【0020】

また、本発明は、Si単結晶基板を、比抵抗が1000Ω・cm以上で、前記初期成長層から0.1μmの深さまでのIII族原子の合計の最大濃度が1×1016/cm3以下であり、かつ初期成長層から0.3μmの深さの位置でのIII族原子の合計濃度が1×1015/cm3以下となるよう形成することにより、上述した効果に加え、高周波動作時の損失を低減することができる電子デバイス用エピタキシャル基板を製造することができる。

【図面の簡単な説明】

【0021】

【図1】一般的な電界効果トランジスタを示す模式的断面図である。

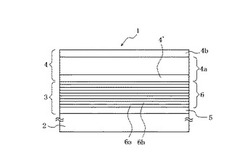

【図2】本発明に従う電子デバイス用エピタキシャル基板の模式的断面図である。

【図3】(a),(b),(c)は、横方向耐圧、横方向リーク電流および縦方向耐圧の測定結果をそれぞれ示したグラフである。

【図4】(a),(b),(c)は、横方向耐圧、横方向リーク電流および縦方向耐圧の測定結果をそれぞれ示したグラフである。

【図5】(a),(b)は、SIMSの結果およびCV測定の結果をそれぞれ示したグラフである。

【図6】(a),(b)は、SIMSの結果およびCV測定の結果をそれぞれ示したグラフである。

【図7】(a),(b)は、SIMSの結果およびCV測定の結果をそれぞれ示したグラフである。

【発明を実施するための形態】

【0022】

次に、本発明の電子デバイス用エピタキシャル基板の実施形態について図面を参照しながら説明する。図2は、本発明に従う電子デバイス用エピタキシャル基板の断面構造を模式的に示したものである。なお、図2は、説明の便宜上、厚さ方向を誇張して描いたものである。

【0023】

図2に示すように、本発明の電子デバイス用エピタキシャル基板1は、横方向を電流導通方向とする電子デバイス用エピタキシャル基板であって、Si単結晶基板2と、Si単結晶基板2上に形成した絶縁層としてのバッファ3と、バッファ3上に複数層のIII族窒化物層をエピタキシャル成長させて形成した主積層体4とを具え、バッファ3は、Si単結晶基板2と接する初期成長層5および初期成長層5上の超格子多層構造からなる超格子積層体6を少なくとも有し、初期成長層5はAlN材料からなり、かつ超格子積層体6はBa1Alb1Gac1Ind1N(0≦a1≦1, 0≦b1≦1, 0≦c1≦1, 0≦d1≦1, a1+b1+c1+d1=1)材料からなる第1層6aおよび該第1層6aとはバンドギャップの異なるBa2Alb2Gac2Ind2N(0≦a2≦1, 0≦b2≦1, 0≦c2≦1, 0≦d2≦1, a2+b2+c2+d2=1)材料からなる第2層6bを交互に積層してなり、超格子積層体6と主積層体4のバッファ3側の部分4´とは、ともにC濃度が1×1018/cm3以上であることを特徴とし、かかる構成を有することにより、横方向リーク電流の低減および横方向耐圧特性を良好に両立させのみでなく、縦方向耐圧を向上させることができるものである。

【0024】

Si単結晶基板2の面方位は特に指定されず、(111),(100),(110)面等を使用することができるが、III族窒化物の(0001)面を表面平坦性よく成長させるためには、(111)面を使用することが望ましい。また、p型、n型いずれの伝導型としてもよい。Si単結晶基板2の導電性については、10000Ω・cm以上の絶縁性の高い高比抵抗基板から、0.001Ω・cm程度までの低比抵抗基板まで、用途に応じて適宜使用することができる。このSi単結晶基板2の製法としては、CZ法・FZ法等各種方法を用いることができ、基板表面にSi、SiC等をエピタキシャル成長することもできる。また、基板表面に酸化膜・窒化膜・炭化膜からなる薄膜が形成されているものを用いることも可能である。

【0025】

特に、高周波特性の優れた電子デバイス用エピタキシャル基板を作成する際には、1000Ω・cm以上の比抵抗を持つ基板を使用するのが好ましい。このような基板は、Si結晶の高純度化が容易なFZ法で作製することが望ましい。

【0026】

また、初期成長層5をAlN材料で形成することにより、Si単結晶基板2との反応を抑制し、縦方向耐圧の向上を可能とする。これは、初期成長層5をGa, Inを含むIII族窒化物材料で形成した場合、Ga, Inが基板のSiと反応して欠陥を発生させ、エピタキシャル膜内に貫通欠陥を誘起することによる、縦方向耐圧の低下の抑制を目的としている。ただし、ここでいうAlN材料は、意図したもの意図しないものに関わらず、1%以下の微量不純物を含んでいてもよく、たとえば、上記Ga, Inを始めとして、Si, H, O, C, B, Mg, As, Pなどの不純物を含むことができる。

【0027】

特に、高周波特性の優れた電子デバイス用エピタキシャル基板を作製する際には、Si単結晶基板が1000Ω・cm以上の比抵抗を有し、初期成長層から0.1μmの深さまでのIII族原子の合計の最大濃度を1×1016/cm3以下とし、かつ初期成長層から0.3μmの深さの位置でのIII族原子の合計濃度を1×1015/cm3以下とするのが好ましい。高比抵抗の基板を使用することにより、空乏層を有効に広げることができ、基板表面に形成されるキャリアと、基板に存在する電荷の容量性あるいは誘導性の結合による電子デバイスの高周波動作時の損失を抑制できる。特に、Si単結晶基板の比抵抗値が5000Ω・cm以上の場合が好ましく、高周波動作時の損失が飽和傾向となる。また、III族原子は、Si単結晶基板内でp型不純物として機能するため、上記の濃度範囲とすることにより、基板表面に形成される電極と、前記p型不純物の容量性あるいは誘導性の結合による電子デバイスの高周波動作時の損失を抑制できる。なお、不純物濃度は、SIMS分析を用いて測定する。この場合、裏面側(基板側)からエッチングしながら、深さ方向の不純物濃度分布を測定する。この際、Alの不純物濃度がGaの不純物濃度より小さいことが望ましい。AlはGaよりも活性化エネルギーが小さく、よりp型キャリアを発生しやすいからである。

【0028】

このように、高周波特性の優れた電子デバイス用エピタキシャル基板を作製する目的で、エピタキシャル成長時、Si単結晶基板に不純物の混入を防ぐには、

1)成膜温度を下げること、および

2)初期成長層AlNの島状成長を抑制し、二次元成長を促進すること

が重要となる。上記2)を実現するためには、Si多結晶基板表面の過度な窒化を抑制し、窒化膜厚を1nmより小さくするか、または窒化しないことが望ましい。Si単結晶基板表面を過度に窒化してしまうと、基板最表面での原料拡散速度が速くなり、AlNが島状成長してしまう結果、初期成長時の基板露出部分より、Al,GaといったIII族原料が拡散してしまうと推測されるからである。

【0029】

超格子積層体6のC濃度を1×1018/cm3以上とすることにより、縦方向耐圧を向上させ、主積層体4のバッファ5側の部分4´のC濃度を1×1018/cm3以上とすることにより、横方向耐圧を向上させることができるとともに、横方向リーク電流を抑制することができる。なお、不純物を増加させすぎることによるピットの発生を防止するため、これらのC濃度は1×1020/cm3未満とするのが好ましい。その他の不純物量については、特に指定されるものではないが、比較的不純物準位の浅いドナー不純物(Si,O,Ge)の混入は抑制することが好ましいものの、こうしたドナー準位を補償できる程度Cが含有されていれば、ある程度の混入は許容される。なお、不純物濃度は、SIMS分析を用いて、表面側からエッチングしながら、深さ方向の不純物濃度分布を測定した。

【0030】

ここで、「横方向を電流導通方向とする」とは、図1で示したように、ソース電極24からドレイン電極25へ、主に積層体の幅方向に電流が流れることを意味し、例えば半導体を一対の電極で挟んだ構造のように、主に縦方向すなわち積層体の厚さ方向に電流が流れるものとは異なることを意味する。

【0031】

また、ここで、超格子積層体を交互に積層とは、第1層6aと第2層6bを周期的に含むように積層することを意味する。第1層6aと第2層6b以外の層(たとえば組成遷移層)を含むことは可能である。

【0032】

主積層体4のバッファ3側の部分4´のC濃度は、超格子積層体6のC濃度よりも高くするのが好ましい。部分4´においては、バッファ3と主積層体4との格子定数の違いによる影響により、転位が横あるいは斜め方向に屈曲する現象が見られ、リーク電流が流れやすいパスが形成される。従って、部分4´はバッファ層3よりもリーク電流が流れやすく、このリーク電流を抑制するため、上記のようなC濃度にすることが望ましい。また、この主積層体4のバッファ3側の部分4´の厚さを0.1μm未満とすると、C濃度が少ない部分でも転位の屈曲が顕著に存在するおそれがあるため、0.1μm以上の厚さに設定することが好ましい。部分4´の厚さの上限は耐圧の向上、リーク電流の低減という観点では、特に指定されるものではなく、基板の反り・クラックの抑制の観点から適宜設定する。この際、部分4´のみIII族元素の組成を変化させたり、部分4´からチャネル層4aのバッファ層とは反対側の部分のCの濃度あるいはIII族元素の組成を変化させたりする場合には、急峻に変化させることもできるし、連続的に変化させることもできる。

【0033】

超格子積層体6を構成する第1層6aがAlN材料からなり、第2層6bがAlb2Gac2N(a2=0、0<b2≦0.5, 0.5≦c2<1, d2=0)材料からなるのが好ましい。第1層6aと第2層6bのバンドギャップ差が縦方向耐圧を向上するため、組成差をできるだけ大きくし、バンドギャップ差をできるだけ大きくとることが好ましい。III族窒化物半導体材料で混晶を作る場合、最もバンドギャップ差が大きいのは、AlN(6.2eV)とGaN(3.5eV)であるため、AlGaN材料で超格子構造をつくることが好ましい。組成差の下限については、0.5より小さくなると、Si単結晶とIII族窒化物の格子定数差による応力緩和が不十分になり、クラックが発生するため、組成差は0.5以上とすることが好ましい。また、組成差の上限については、組成差は大きいほうが望ましいが、AlGaN層自身の絶縁化が進み耐圧を向上させるため、バンドギャップの小さい第2層はAlが少なくとも含まれるようにし、Alの組成差は1より小さくすることが好ましい。Alが少なくとも含まれるようにした場合、Cをより効率的に取り込むことができるからである。超格子のペア数は、少なくとも40ペア以上とすると、耐圧のばらつきを低減することができるため好ましい。

【0034】

各層の厚みに関しては、耐圧の向上という観点から考えると、バンドギャップの大きい第1層6aの厚みは、トンネル電流が抑制できる程度の厚み以上でかつ、クラックの発生しない膜厚以下とすることが好ましい。たとえば、AlNを用いた場合には、2〜10nmに設定することが好ましい。第2層6bの厚みに関しては、クラックの抑制・反りの制御の観点から適宜設定するが、超格子積層構造の歪緩衝効果を有効に発揮し、クラックの発生を抑制するために、バンドギャップの小さい層の厚みは、バンドギャップの大きい層よりも厚く、40nm以下とするのが好ましい。また、超格子積層体内で必ずしもすべて同じ膜厚、同じ組成で積層させる必要はない。

【0035】

電子デバイス用エピタキシャル基板1は、HEMTに用いるのが好ましい。図2に示すエピタキシャル基板1の主積層体4は、Ba3Alb3Gac3Ind3N(0≦a3≦1, 0≦b3≦1, 0≦c3≦1, 0≦d3≦1, a3+b3+c3+d3=1)材料からなるチャネル層4aおよびチャネル層4aよりバンドギャップの大きいBa4Alb4Gac4Ind4N(0≦a4≦1, 0≦b4≦1, 0≦c4≦1, 0≦d4≦1, a4+b4+c4+d4=1)材料からなる電子供給層4bを有することができる。この際、両層とも単一もしくは複数の組成から構成することができる。特に、合金散乱をさけ、電流導通部分の比抵抗を下げるためには、チャネル層4aの少なくとも電子供給層4bと接する部分はGaN材料とすることが好ましい。

【0036】

チャネル層4aのバッファ層とは反対側の部分は、C濃度が低いことが好ましく、4×1016/cm3以下に設定することが好ましい。この部分は、電子デバイスの電流導通部分に相当するため、導電性を阻害したり、電流コラプスを発生させたりする不純物は含まないほうが望ましいからである。また、n型不純物による残留キャリアによるリークを抑制するため、1×1015/cm3以上存在することが望ましい。

【0037】

次に、本発明の電子デバイス用エピタキシャル基板の製造方法の実施形態について図面を参照しながら説明する。

【0038】

図2に示すように、Si単結晶基板2上に、絶縁層としてのバッファ3と、バッファ3上に複数層のIII族窒化物層をエピタキシャル成長させたHEMT構造の主積層体4とを順に形成した、横方向を電流導通方向とする電子デバイス用エピタキシャル基板1の製造方法であって、バッファ3は、Si単結晶基板2と接する初期成長層5および初期成長層5上の超格子多層構造からなる超格子積層体6を有し、初期成長層5はAlN材料からなり、かつ超格子積層体6はBa1Alb1Gac1Ind1N(0≦a1≦1, 0≦b1≦1, 0≦c1≦1, 0≦d1≦1, a1+b1+c1+d1=1)材料からなる第1層6aおよび第1層6aとはバンドギャップの異なるBa2Alb2Gac2Ind2N(0≦a2≦1, 0≦b2≦1, 0≦c2≦1, 0≦d2≦1, a2+b2+c2+d2=1)材料からなる第2層6bを交互に積層してなり、超格子積層体6と主積層体4のバッファ3側の部分4´とは、ともにC濃度が1018/cm3以上となるよう形成されることを特徴とし、かかる構成を有することにより、縦方向耐圧特性および横方向耐圧特性を良好に両立させ、かつ横方向リーク電流を低減させることができる電子デバイス用エピタキシャル基板を製造することができるものである。

【0039】

超格子積層体6と主積層体4のバッファ3側の部分4´に添加されるCは、CVD法を用いて成長する場合には、以下に示すいくつかの方法により添加することができる。

第1の方法:Cを含む原料ガスを、III族窒化物成長中に別途添加する。メタン・エタン・エチレン・アセチレン・ベンゼン・シクロペンタン等が例示される。

第2の方法:有機金属中のメチル基・エチル基等を、成長III族窒化物成長条件によりエピタキシャル成長層に混入させる。有機金属の分解を抑えるように、成長温度・成長圧力・成長速度・成長時のアンモニア流量・水素流量・窒素流量等を適宜設定することにより、エピタキシャル成長層に添加されるC濃度を調整することが可能である。

なお、本願では、超格子積層体6のC濃度は、SIMSにより、超格子積層体6の厚さの1/2を除去した箇所の測定値とする。主積層体4のバッファ3側の部分4´のC濃度は、SIMSにより、前記部分4´の厚さの1/2を除去した箇所の測定値とする。

【0040】

なお、図1および図2は、代表的な実施形態の例を示したものであって、本発明はこれらの実施形態に限定されるものではない。たとえば、各層の間に本発明の効果に悪影響を与えない程度の中間層を挿入したり、他の超格子層を挿入したり、組成に傾斜をつけたりすることはできる。また、Si単結晶の表面に、窒化膜、炭化膜、Al層などを形成することもできる。

【実施例】

【0041】

(実験例1)

比抵抗がそれぞれ1×10-1Ω・cm,1×10Ω・cm,2×103Ω・cm,1×104Ω・cmの600μm厚の(111)面4インチSi単結晶基板上に、初期成長層(AlN材料:厚さ100nm)および超格子積層体(AlN:膜厚4nmとAl0.15Ga0.85N:膜厚25nm、合計85層)を成長させてバッファを形成し、この超格子積層体上にチャネル層(GaN材料:厚さ1.5μm)および電子供給層(Al0.25Ga0.75N材料:厚さ20nm)をエピタキシャル成長させてHEMT構造の主積層体を形成して試料1〜4を得た。超格子積層体のC濃度を変化させ、主積層体のバッファ側の部分のC濃度は、いずれの結果も、1.5〜2.0×1018/cm3の範囲であった。また、チャネル層の電子供給層側の部分は、C濃度が0.8〜3.5×1016/cm3の範囲であった。各層の成長温度、圧力を表1に示す。表中P1を調整することによりC濃度を調整し、成膜圧力を下げることによりC濃度を増加させている。成長方法としてはMOCVD法を使用し、III族原料としては、TMA(トリメチルアルミニウム)・TMG(トリメチルガリウム)、V族原料としてはアンモニアを用い、キャリアガスとして、水素および窒素ガスを用いた。ここでいう成膜温度は、成長中に放射温度計を用いて測定した、基板自体の温度を意味する。なお、C濃度のSIMS測定は、エピタキシャル層側からエッチングを行い、Cameca製の測定装置で、イオン源としてCs−を用い、イオンエネルギーは8keVで行った。

【0042】

【表1】

【0043】

(実験例2)

初期成長層を700℃で成長したGaN材料(厚さ:20nm)で形成し、各層の成長温度、圧力を表2に示す条件で行ったこと以外は、実験例1の試料2と同様の方法により試料5を作製した。

【0044】

【表2】

【0045】

図3(a)、図3(b)および図3(c)に、試料2および試料5の横方向耐圧、横方向リーク電流および縦方向耐圧の測定結果を示す。測定は、以下の通り行った。

縦方向:基板表面に80μmφからなるTi/Al積層構造のオーミック電極を形成し、オーミック電極外側を50nmの厚みでエッチングした後、基板裏面を金属板に接地し、両電極間に流れる電流値を電圧に対して測定した。

横方向:200μm□(四角)からなるTi/Al積層構造のオーミック電極を各々の一辺を10μmの距離を離して配置して形成し、前記オーミック電極周囲を150nmの厚みでエッチングした後、両電極間に流れる電流値を電圧に対して測定した。この際、空気中の放電を抑制するため、絶縁油で両電極間を絶縁している。また、基板裏面へのリークの影響をなくすため、基板下には絶縁板を配置している。

本実験例において、縦方向耐圧は縦方向の電流値を上記電極面積で単位面積当たりの値に換算した値が10-4A/cm2に達する電圧値で、横方向耐圧は横方向の電流値を上記電極の1辺の長さ当たりの値に換算した値が10-4A/cmに達する電圧値で、横方向リーク電流は横方向が100Vでの電流値で、それぞれ定義する。

超格子積層体6のC濃度は、SIMSにより、超格子積層体6の厚さの1/2を除去した箇所を測定することにより得た。主積層体4のバッファ3側の部分4´のC濃度は、SIMSにより、前記部分4´の厚さの1/2を除去した箇所を測定値することにより得た。

【0046】

超格子積層体のC濃度を変化させた結果、横方向耐圧、横方向リーク電流については、いずれもほとんど変化ないのに対し、試料2の縦方向耐圧については、超格子積層体のC濃度が1×1018/cm3を超えると、特異的に急激に高くなることが確認できる。また、こうした現象は、試料5を参照して分かるように、初期成長層をAlNにした場合固有の現象であることも確認できる。また、試料1,3および4についても、試料2と同様の結果が得られた。

【0047】

(実験例3)

超格子積層体の成長圧力を10kPaとして、主積層体のバッファ側の部分のC濃度を変化させ、各層の成長温度、圧力を表3に示す条件で行ったこと以外は、実験例1の試料1〜4と同様の方法により試料6〜9を作製した。表中P2を調整することによりC濃度を調整し、成膜圧力を下げることによりC濃度を増加させている。超格子積層体のC濃度は、いずれの結果も1.5〜2.5×1018/cm3の範囲であった。

【0048】

【表3】

【0049】

図4(a)、図4(b)および図4(c)に、試料6の横方向耐圧、横方向リーク電流および縦方向耐圧の測定結果を示す。主積層体のC濃度を変化させた結果、横方向耐圧、横方向リーク電流については、ほとんど変化ないのに対し、試料6の縦方向耐圧については、主積層体のバッファ側の部分のC濃度が1×1018/cm3を超えると、特異的に急激に高くなることが確認できる。また、実験例1と同様に、使用するSi単結晶基板の比抵抗が異なる試料7〜9についても、図4(a)〜図4(c)に示した結果と大きな差異は認められなかった。

【0050】

実験例1〜3において、縦方向耐圧を向上させるために、超格子積層体およびチャネル層バッファ側のC濃度を所定値以上とすることにより縦方向耐圧を向上できることを確認することができた。次の実験例4では、前記バッファ層C濃度については実験例1〜3にて好ましいと確認された所定値以上となるようとし、高周波特性の改善を試みた。

【0051】

(実験例4)

比抵抗6×103Ω・cmの600μm厚の(111)面4インチSi単結晶基板上に、初期窒化層の形成を抑制しつつ、初期成長層(AlN材料:厚さ100nm)および超格子積層体(AlN:膜厚4nmとAl0.15Ga0.85N:膜厚25nm、合計85層)を成長させてバッファを形成し、この超格子積層体上にチャネル層(GaN材料:厚さ1.5μm)および電子供給層(Al0.25Ga0.75N材料:厚さ20nm)を、成長圧力、成長温度を表4の条件でエピタキシャル成長させ、HEMT構造の主積層体を形成して試料10を得た。超格子積層体のC濃度は2.0×1018/cm3であり、主積層体のバッファ側の0.2μm厚の部分のC濃度は3.0×1018/cm3であった。また、チャネル層の電子供給層側の部分は、C濃度は1×1016/cm3としている。

【0052】

【表4】

【0053】

SIMSにてSi単結晶基板内の不純物を観察したところ、図5(a)に示すように、III族元素の不純物としては、Al、Ga以外は認められず、Al,Gaともに、1×1016/cm3以下であり、1×1015/cm3以上存在する領域は、Si単結晶と初期成長層の界面から0.2μm以内の領域であった。TEMでSi単結晶基板と初期成長層の界面を確認したが、1nm以上の厚みのSiNx膜の存在は確認されなかった。また、Si単結晶基板と初期成長層の界面から0.2μm以内の領域では平均して、Alの濃度がGaの濃度と比較して低いことも確認された。なお、Al,GaのSIMS測定は、Si単結晶側からエッチングを行い、Cameca製の測定装置で、イオン源としてO2+を用い、イオンエネルギーは3keVで行った。

【0054】

また、本基板について、水銀プローブ(MSI electronics製)および、インピーダンスアナライザ(HP4284A)を用いてCV測定を行ったところ、図5(b)に示すように、空乏層が換算膜厚にして8μm程度まで広がっていることが確認された。CV測定時の交流成分の周波数および振幅はそれぞれ100kHz,10mVである。尚、便宜上、Si単結晶と初期成長層の界面の位置は、SIMS測定において、Siの濃度が1/5以下となる位置から0.05μm基板側にシフトした位置とした。SIMS測定時のエッチング粗れの結果、Si単結晶とエピタキシャル成長層が混在して露出することによるIII族元素の見かけ上の増加を避けるためである。

【0055】

また、使用する4インチSi単結晶基板の抵抗率を、2×103Ω・cm、8×103Ω・cm、12×103Ω・cmとした以外は、試料10と同様の方法で作製された試料11,12,13についても同様の試験をおこなった。この2つの試験いずれも、上記と同様に、SIMSにてSi単結晶基板内の不純物を観察したところ、Al、Ga以外のIII族元素は認められず、Al,Gaともに、1×1016/cm3以下であり、1×1015/cm3以上存在する領域は、Si単結晶と初期成長層の界面から0.2μm以下の領域であった。TEMでSi単結晶基板と初期成長層の界面を確認したが1nm以上の厚みのSiNx膜の存在は確認されなかった。また、Si単結晶基板と初期成長層の界面から0.2μm以下の領域では平均して、Alの濃度がGaのそれと比較して低いことも確認された。また、空乏層が換算膜厚にして、それぞれ、6μm、8μm、8μm程度まで広がっていることが確認された。

【0056】

(実験例5)

比抵抗5×103Ω・cmの600μm厚の(111)面4インチSi単結晶基板上に、初期成長層成長開始前に、アンモニアガスを、キャリアガスである水素ガスに対し、10%含有したガスのみを5分間1050℃で流すことにより、初期窒化層を意図的に形成した以外は、試料2と同様に試料14を作製した。

【0057】

SIMSにてSi単結晶基板内の不純物を観察したところ、図6(a)に示すように、Al,Gaともに、1×1016/cm3以下であるものの、AlまたはGaが、1×1015/cm3以上存在する領域は、1μm以上であった。TEMでSi単結晶基板と初期成長層の界面を確認したところSiNx膜が1.5nm程度存在することが確認された。また、Alの濃度がGaのそれと比較して高いこととも確認された。また、本基板について、水銀プローブを用いたCV測定を行ったところ、図6(b)に示すように、空乏層が換算膜厚にして2μm程度までしか広がっていないことが確認された。

【0058】

(実験例6)

初期成長層からチャネル層の成長温度を表5に示す条件で上昇させた以外は、試料10と同様に試料15を作製した。

【0059】

【表5】

【0060】

SIMSにてSi単結晶基板内の不純物を観察したところ、図7(a)に示すように、Gaの濃度が、1×1016/cm3以上である部分が存在した、1×1015/cm3以上存在する領域は、0.3μm以下であった。TEMでSi単結晶基板と初期成長層の界面を確認したが1nm以上の厚みのSiNx膜の存在は確認されなかった。また、Alの濃度がGaのそれと比較して低いことも確認された。また、本基板について、図7(b)に示すように、水銀プローブを用いたCV測定を行ったところ、空乏層が換算膜厚にして2μm程度までしか広がっていないことが確認された。

【0061】

試料1〜13と試料14,15とを比較すると、Al,GaのSi単結晶への混入を抑制することが、空乏層を効果的に広げることにつながることが確認される。空乏層を効率的に広げることができることは、エピタキシャル層内およびSi単結晶基板内のキャリアの低減ができていることと同義であり、基板表面に形成される電極と、前記p型不純物の容量性あるいは誘導性の結合による電子デバイスの高周波動作時の損失を抑制できることを意味する。

特に、試料2と試料14との比較から、窒化厚を薄くすることにより、試料2と試料15との比較からエピタキシャル層の成膜温度を低くすることにより、上記効果を引き出すことができたと推察される。

【0062】

なお、全ての実験例で作製したエピタキシャル基板において、ホール効果測定法により、チャネル層部分の電気特性を評価したところ、シート抵抗値450Ω/□以下(四角)、移動度は1550cm2/Vs以上と良好な特性を示すことが確認されている。

【産業上の利用可能性】

【0063】

本発明の電子デバイス用エピタキシャル基板によれば、AlN材料からなる初期成長層および所定の超格子積層体を有するバッファならびに所定の主積層体を具え、これら超格子積層体と主積層体のバッファ側の部分とが、ともに1×1018/cm3以上のC濃度を有することにより、横方向リーク電流の低減および横方向耐圧特性を良好に両立させ、かつ縦方向耐圧を向上させることができる。更に、前記特性に加えて、前記Si単結晶基板の比抵抗を1000Ω・cm以上とし、前記Si単結晶基板の初期成長層側のIII族原子の合計の最大濃度が1×1016/cm3以下であり、かつ、0.3μm深さの位置でのIII族原子の合計濃度が1×1015/cm3以下とすることにより高周波信号印加時の損失を低減することができる。

【0064】

また、本発明によれば、AlN材料からなる初期成長層および所定の超格子積層体を有するバッファならびに所定の主積層体を具え、これら超格子積層体と主積層体のバッファ側の部分とが、ともに1×1018/cm3以上のC濃度を有することにより、横方向リーク電流の低減および横方向耐圧特性を良好に両立させ、かつ縦方向耐圧を向上させることができ、更に、前記特性に加えて、高周波信号印加時の損失を低減することができる電子デバイス用エピタキシャル基板を製造することができる。

【符号の説明】

【0065】

1 電子デバイス用エピタキシャル基板

2 Si単結晶基板

3 バッファ

4 主積層体

4a チャネル層

4b 電子供給層

5 初期成長層

6 超格子積層体

6a 第1層

6b 第2層

【技術分野】

【0001】

本発明は、電子デバイス用エピタキシャル基板およびその製造方法、特に、HEMT用エピタキシャル基板およびその製造方法に関する。

【背景技術】

【0002】

近年、IC用デバイス等の高速化に伴い、高速の電界効果トランジスタ(FET: Field effect transistor)として、高電子移動度トランジスタ(HEMT: High electron mobility transistor)が広く用いられるようになっている。このような電界効果型のトランジスタは、例えば図1に模式的に示されるように、基板21上にチャネル層22および電子供給層23を積層し、この電子供給層23の表面にソース電極24、ドレイン電極25およびゲート電極26を配設することにより形成され、デバイスの動作時には、ソース電極24、電子供給層23、チャネル層22、電子供給層23およびドレイン電極25の順に電子が移動して、横方向を電流導通方向とし、この横方向の電子の移動は、ゲート電極26に印加される電圧により制御される。HEMTにおいて、バンドギャップの異なる電子供給層23およびチャネル層22の接合界面に生じる電子は、通常の半導体内と比較して高速で移動することができる。

【0003】

このように、横方向の電子の移動、すなわち電流は、ゲート電圧によって制御されるが、一般に、ゲート電圧をOFFにしても電流が0になることはない。このゲート電圧OFF時に流れる電流のことをリーク電流といい、リーク電流が増えると消費電力が増大し、その結果、発熱などの問題が生じることになる。このリーク電流は、一般に、横方向リーク電流と縦方向リーク電流とに分けられ、横方向リーク電流とは、電子供給層23側表面に配置した2電極間(たとえば、ソース電極24とドレイン電極25間)に流れるリーク電流のことをいい、縦方向リーク電流とは、電子供給層23側表面と基板21側表面にそれぞれ配置した2電極間に流れるリーク電流のことをいう。

【0004】

特許文献1には、基板上に、バッファ層、炭素濃度遷移層、チャネル層および電子供給層を具えるHEMTにおいて、チャネル層からバッファ層へ向かって炭素濃度が増加するように形成することにより、バッファ層および炭素濃度遷移層中に発生する横方向リーク電流を低減すると共に、横方向の耐圧を向上させる技術が開示されている。

【0005】

また、特許文献2には、基板上に超格子バッファ層、チャネル層および電子供給層を具える半導体デバイスにおいて、超格子バッファ層に炭素を含有させることにより、半導体電子デバイスの横方向リーク電流を抑止し、横方向耐圧を向上させる技術が開示されている。

【0006】

さらに、特許文献3には、単結晶基板上に形成された第1のIII族窒化物下地層と、この第1のIII族窒化物下地層上に形成された第2のIII族窒化物下地層との界面に、アクセプタ不純物を含み、このアクセプタ不純物の濃度を、上記界面から第2のIII族窒化物下地層の厚さ方向において減少させることにより、半導体電子デバイスの横方向リーク電流を抑止する技術が開示されている。

【0007】

ところで、HEMTを高周波数で動作させる場合には、前記リーク電流を低減させた上で、かつ高周波信号印加時の損失を低減する必要がある。この損失は、基板またはその上のエピタキシャル膜に電荷が存在する場合に、空乏層が効率的に広がらず、基板表面に配置した電極と容量性あるいは誘導性の相互作用を起こすことにより生じるものである。

【0008】

そこで、特許文献4には、Si単結晶基板の比抵抗を高くして不純物の混入を防ぐことにより、キャリアを低減させ、高周波領域での半導体電子デバイスの損失を抑制する技術が開示されている。

【0009】

しかしながら、特許文献1に記載された発明においては、基板上にIII族窒化物層を成長する際、GaN系低温バッファ層を用いるため、基板にSiを用いる場合にGaとの反応によるピット等の貫通欠陥を発生し、縦方向耐圧を悪化させるという問題があった。

また、特許文献2に記載された発明は、超格子バッファ層内のリークは抑制できるものの、チャネル層と超格子バッファ層界面でのリークを十分に抑制できず、結果として、縦方向および横方向耐圧を共に劣化させる原因となっていた。

さらに、特許文献3、4は縦方向耐圧について考慮しておらず、バッファ層の耐圧に対する検討は全くされていないため、Si基板のような半導体基板に適応した場合、縦方向耐圧を確保することができなかった。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2007−251144号公報

【特許文献2】特開2005−85852号公報

【特許文献3】特開2003−282598号公報

【特許文献4】特表2008−522447号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明の目的は、横方向リーク電流の低減および横方向耐圧特性を良好に両立させ、かつ縦方向耐圧を向上させることができる電子デバイス用エピタキシャル基板およびその製造方法を提供することにある。

【課題を解決するための手段】

【0012】

上記目的を達成するため、本発明の要旨構成は以下のとおりである。

(1)Si単結晶基板と、該Si単結晶基板上に形成した絶縁層としてのバッファと、該バッファ上に複数層のIII族窒化物層をエピタキシャル成長させて形成した主積層体とを具え、横方向を電流導通方向とする電子デバイス用エピタキシャル基板であって、前記バッファは、前記Si単結晶基板と接する初期成長層および該初期成長層上の超格子多層構造からなる超格子積層体を少なくとも有し、前記初期成長層はAlN材料からなり、かつ前記超格子積層体はBa1Alb1Gac1Ind1N(0≦a1≦1, 0≦b1≦1, 0≦c1≦1, 0≦d1≦1, a1+b1+c1+d1=1)材料からなる第1層および該第1層とはバンドギャップの異なるBa2Alb2Gac2Ind2N(0≦a2≦1, 0≦b2≦1, 0≦c2≦1, 0≦d2≦1, a2+b2+c2+d2=1)材料からなる第2層を交互に積層してなり、前記超格子積層体と、前記主積層体の前記バッファ側の部分は、ともにC濃度が1×1018/cm3以上であることを特徴とする電子デバイス用エピタキシャル基板。

【0013】

(2)前記第1層がAlN材料からなり、前記第2層がAlb2Gac2N(a2=0, 0<b2≦0.5,0.5≦c2<1,d2=0)材料からなる上記(1)に記載の電子デバイス用エピタキシャル基板。

【0014】

(3)前記Si単結晶基板は、比抵抗が1000Ω・cm以上で、前記初期成長層から0.1μmの深さまでのIII族原子の合計の最大濃度が1×1016/cm3以下であり、かつ前記初期成長層から0.3μmの深さの位置でのIII族原子の合計濃度が1×1015/cm3以下である上記(1)または(2)に記載の電子デバイス用エピタキシャル基板。

【0015】

(4)Si単結晶基板上に、絶縁層としてのバッファと、該バッファ上に複数層のIII族窒化物層をエピタキシャル成長させた主積層体とを順に形成した、横方向を電流導通方向とする電子デバイス用エピタキシャル基板の製造方法であって、前記バッファは、前記Si単結晶基板と接する初期成長層および該初期成長層上の超格子多層構造からなる超格子積層体を少なくとも有し、前記初期成長層はAlN材料からなり、かつ前記超格子積層体はBa1Alb1Gac1Ind1N(0≦a1≦1, 0≦b1≦1, 0≦c1≦1, 0≦d1≦1, a1+b1+c1+d1=1)材料からなる第1層および該第1層とはバンドギャップの異なるBa2Alb2Gac2Ind2N(0≦a2≦1, 0≦b2≦1, 0≦c2≦1, 0≦d2≦1, a2+b2+c2+d2=1)材料からなる第2層を交互に積層してなり、前記超格子積層体と、前記主積層体の前記バッファ側の部分は、ともにC濃度が1018/cm3以上となるよう形成されることを特徴とする電子デバイス用エピタキシャル基板の製造方法。

【0016】

(5)前記Si単結晶基板は、比抵抗が1000Ω・cm以上で、前記初期成長層から0.1μmの深さまでのIII族原子の合計の最大濃度が1×1016/cm3以下であり、かつ前記初期成長層から0.3μmの深さの位置でのIII族原子の合計濃度が1×1015/cm3以下となるよう形成される上記(4)に記載の電子デバイス用エピタキシャル基板の製造方法。

【発明の効果】

【0017】

本発明の電子デバイス用エピタキシャル基板は、AlN材料からなる初期成長層および所定の超格子積層体を有するバッファならびに所定の主積層体を具え、これら超格子積層体と主積層体のバッファ側の部分とが、ともに1×1018/cm3以上のC濃度を有することにより、横方向リーク電流の低減および横方向耐圧特性を良好に両立させるのみでなく、縦方向耐圧を向上させることができる。

【0018】

また、本発明は、AlN材料からなる初期成長層および所定の超格子積層体を有するバッファならびに所定の主積層体を具え、これら超格子積層体と主積層体のバッファ側の部分とが、ともに1×1018/cm3以上のC濃度を有することにより、横方向リーク電流の低減および横方向耐圧特性を良好に両立させるのみでなく、縦方向耐圧を向上させることができる電子デバイス用エピタキシャル基板を製造することができる。

【0019】

さらに、本発明の電子デバイス用エピタキシャル基板は、Si単結晶基板が1000Ω・cm以上の比抵抗を有し、初期成長層から0.1μmの深さまでのIII族原子の合計の最大濃度を1×1016/cm3以下とし、かつ初期成長層から0.3μmの深さの位置でのIII族原子の合計濃度を1×1015/cm3以下とすることにより、上述した効果に加え、高周波動作時の損失を低減することができる。

【0020】

また、本発明は、Si単結晶基板を、比抵抗が1000Ω・cm以上で、前記初期成長層から0.1μmの深さまでのIII族原子の合計の最大濃度が1×1016/cm3以下であり、かつ初期成長層から0.3μmの深さの位置でのIII族原子の合計濃度が1×1015/cm3以下となるよう形成することにより、上述した効果に加え、高周波動作時の損失を低減することができる電子デバイス用エピタキシャル基板を製造することができる。

【図面の簡単な説明】

【0021】

【図1】一般的な電界効果トランジスタを示す模式的断面図である。

【図2】本発明に従う電子デバイス用エピタキシャル基板の模式的断面図である。

【図3】(a),(b),(c)は、横方向耐圧、横方向リーク電流および縦方向耐圧の測定結果をそれぞれ示したグラフである。

【図4】(a),(b),(c)は、横方向耐圧、横方向リーク電流および縦方向耐圧の測定結果をそれぞれ示したグラフである。

【図5】(a),(b)は、SIMSの結果およびCV測定の結果をそれぞれ示したグラフである。

【図6】(a),(b)は、SIMSの結果およびCV測定の結果をそれぞれ示したグラフである。

【図7】(a),(b)は、SIMSの結果およびCV測定の結果をそれぞれ示したグラフである。

【発明を実施するための形態】

【0022】

次に、本発明の電子デバイス用エピタキシャル基板の実施形態について図面を参照しながら説明する。図2は、本発明に従う電子デバイス用エピタキシャル基板の断面構造を模式的に示したものである。なお、図2は、説明の便宜上、厚さ方向を誇張して描いたものである。

【0023】

図2に示すように、本発明の電子デバイス用エピタキシャル基板1は、横方向を電流導通方向とする電子デバイス用エピタキシャル基板であって、Si単結晶基板2と、Si単結晶基板2上に形成した絶縁層としてのバッファ3と、バッファ3上に複数層のIII族窒化物層をエピタキシャル成長させて形成した主積層体4とを具え、バッファ3は、Si単結晶基板2と接する初期成長層5および初期成長層5上の超格子多層構造からなる超格子積層体6を少なくとも有し、初期成長層5はAlN材料からなり、かつ超格子積層体6はBa1Alb1Gac1Ind1N(0≦a1≦1, 0≦b1≦1, 0≦c1≦1, 0≦d1≦1, a1+b1+c1+d1=1)材料からなる第1層6aおよび該第1層6aとはバンドギャップの異なるBa2Alb2Gac2Ind2N(0≦a2≦1, 0≦b2≦1, 0≦c2≦1, 0≦d2≦1, a2+b2+c2+d2=1)材料からなる第2層6bを交互に積層してなり、超格子積層体6と主積層体4のバッファ3側の部分4´とは、ともにC濃度が1×1018/cm3以上であることを特徴とし、かかる構成を有することにより、横方向リーク電流の低減および横方向耐圧特性を良好に両立させのみでなく、縦方向耐圧を向上させることができるものである。

【0024】

Si単結晶基板2の面方位は特に指定されず、(111),(100),(110)面等を使用することができるが、III族窒化物の(0001)面を表面平坦性よく成長させるためには、(111)面を使用することが望ましい。また、p型、n型いずれの伝導型としてもよい。Si単結晶基板2の導電性については、10000Ω・cm以上の絶縁性の高い高比抵抗基板から、0.001Ω・cm程度までの低比抵抗基板まで、用途に応じて適宜使用することができる。このSi単結晶基板2の製法としては、CZ法・FZ法等各種方法を用いることができ、基板表面にSi、SiC等をエピタキシャル成長することもできる。また、基板表面に酸化膜・窒化膜・炭化膜からなる薄膜が形成されているものを用いることも可能である。

【0025】

特に、高周波特性の優れた電子デバイス用エピタキシャル基板を作成する際には、1000Ω・cm以上の比抵抗を持つ基板を使用するのが好ましい。このような基板は、Si結晶の高純度化が容易なFZ法で作製することが望ましい。

【0026】

また、初期成長層5をAlN材料で形成することにより、Si単結晶基板2との反応を抑制し、縦方向耐圧の向上を可能とする。これは、初期成長層5をGa, Inを含むIII族窒化物材料で形成した場合、Ga, Inが基板のSiと反応して欠陥を発生させ、エピタキシャル膜内に貫通欠陥を誘起することによる、縦方向耐圧の低下の抑制を目的としている。ただし、ここでいうAlN材料は、意図したもの意図しないものに関わらず、1%以下の微量不純物を含んでいてもよく、たとえば、上記Ga, Inを始めとして、Si, H, O, C, B, Mg, As, Pなどの不純物を含むことができる。

【0027】

特に、高周波特性の優れた電子デバイス用エピタキシャル基板を作製する際には、Si単結晶基板が1000Ω・cm以上の比抵抗を有し、初期成長層から0.1μmの深さまでのIII族原子の合計の最大濃度を1×1016/cm3以下とし、かつ初期成長層から0.3μmの深さの位置でのIII族原子の合計濃度を1×1015/cm3以下とするのが好ましい。高比抵抗の基板を使用することにより、空乏層を有効に広げることができ、基板表面に形成されるキャリアと、基板に存在する電荷の容量性あるいは誘導性の結合による電子デバイスの高周波動作時の損失を抑制できる。特に、Si単結晶基板の比抵抗値が5000Ω・cm以上の場合が好ましく、高周波動作時の損失が飽和傾向となる。また、III族原子は、Si単結晶基板内でp型不純物として機能するため、上記の濃度範囲とすることにより、基板表面に形成される電極と、前記p型不純物の容量性あるいは誘導性の結合による電子デバイスの高周波動作時の損失を抑制できる。なお、不純物濃度は、SIMS分析を用いて測定する。この場合、裏面側(基板側)からエッチングしながら、深さ方向の不純物濃度分布を測定する。この際、Alの不純物濃度がGaの不純物濃度より小さいことが望ましい。AlはGaよりも活性化エネルギーが小さく、よりp型キャリアを発生しやすいからである。

【0028】

このように、高周波特性の優れた電子デバイス用エピタキシャル基板を作製する目的で、エピタキシャル成長時、Si単結晶基板に不純物の混入を防ぐには、

1)成膜温度を下げること、および

2)初期成長層AlNの島状成長を抑制し、二次元成長を促進すること

が重要となる。上記2)を実現するためには、Si多結晶基板表面の過度な窒化を抑制し、窒化膜厚を1nmより小さくするか、または窒化しないことが望ましい。Si単結晶基板表面を過度に窒化してしまうと、基板最表面での原料拡散速度が速くなり、AlNが島状成長してしまう結果、初期成長時の基板露出部分より、Al,GaといったIII族原料が拡散してしまうと推測されるからである。

【0029】

超格子積層体6のC濃度を1×1018/cm3以上とすることにより、縦方向耐圧を向上させ、主積層体4のバッファ5側の部分4´のC濃度を1×1018/cm3以上とすることにより、横方向耐圧を向上させることができるとともに、横方向リーク電流を抑制することができる。なお、不純物を増加させすぎることによるピットの発生を防止するため、これらのC濃度は1×1020/cm3未満とするのが好ましい。その他の不純物量については、特に指定されるものではないが、比較的不純物準位の浅いドナー不純物(Si,O,Ge)の混入は抑制することが好ましいものの、こうしたドナー準位を補償できる程度Cが含有されていれば、ある程度の混入は許容される。なお、不純物濃度は、SIMS分析を用いて、表面側からエッチングしながら、深さ方向の不純物濃度分布を測定した。

【0030】

ここで、「横方向を電流導通方向とする」とは、図1で示したように、ソース電極24からドレイン電極25へ、主に積層体の幅方向に電流が流れることを意味し、例えば半導体を一対の電極で挟んだ構造のように、主に縦方向すなわち積層体の厚さ方向に電流が流れるものとは異なることを意味する。

【0031】

また、ここで、超格子積層体を交互に積層とは、第1層6aと第2層6bを周期的に含むように積層することを意味する。第1層6aと第2層6b以外の層(たとえば組成遷移層)を含むことは可能である。

【0032】

主積層体4のバッファ3側の部分4´のC濃度は、超格子積層体6のC濃度よりも高くするのが好ましい。部分4´においては、バッファ3と主積層体4との格子定数の違いによる影響により、転位が横あるいは斜め方向に屈曲する現象が見られ、リーク電流が流れやすいパスが形成される。従って、部分4´はバッファ層3よりもリーク電流が流れやすく、このリーク電流を抑制するため、上記のようなC濃度にすることが望ましい。また、この主積層体4のバッファ3側の部分4´の厚さを0.1μm未満とすると、C濃度が少ない部分でも転位の屈曲が顕著に存在するおそれがあるため、0.1μm以上の厚さに設定することが好ましい。部分4´の厚さの上限は耐圧の向上、リーク電流の低減という観点では、特に指定されるものではなく、基板の反り・クラックの抑制の観点から適宜設定する。この際、部分4´のみIII族元素の組成を変化させたり、部分4´からチャネル層4aのバッファ層とは反対側の部分のCの濃度あるいはIII族元素の組成を変化させたりする場合には、急峻に変化させることもできるし、連続的に変化させることもできる。

【0033】

超格子積層体6を構成する第1層6aがAlN材料からなり、第2層6bがAlb2Gac2N(a2=0、0<b2≦0.5, 0.5≦c2<1, d2=0)材料からなるのが好ましい。第1層6aと第2層6bのバンドギャップ差が縦方向耐圧を向上するため、組成差をできるだけ大きくし、バンドギャップ差をできるだけ大きくとることが好ましい。III族窒化物半導体材料で混晶を作る場合、最もバンドギャップ差が大きいのは、AlN(6.2eV)とGaN(3.5eV)であるため、AlGaN材料で超格子構造をつくることが好ましい。組成差の下限については、0.5より小さくなると、Si単結晶とIII族窒化物の格子定数差による応力緩和が不十分になり、クラックが発生するため、組成差は0.5以上とすることが好ましい。また、組成差の上限については、組成差は大きいほうが望ましいが、AlGaN層自身の絶縁化が進み耐圧を向上させるため、バンドギャップの小さい第2層はAlが少なくとも含まれるようにし、Alの組成差は1より小さくすることが好ましい。Alが少なくとも含まれるようにした場合、Cをより効率的に取り込むことができるからである。超格子のペア数は、少なくとも40ペア以上とすると、耐圧のばらつきを低減することができるため好ましい。

【0034】

各層の厚みに関しては、耐圧の向上という観点から考えると、バンドギャップの大きい第1層6aの厚みは、トンネル電流が抑制できる程度の厚み以上でかつ、クラックの発生しない膜厚以下とすることが好ましい。たとえば、AlNを用いた場合には、2〜10nmに設定することが好ましい。第2層6bの厚みに関しては、クラックの抑制・反りの制御の観点から適宜設定するが、超格子積層構造の歪緩衝効果を有効に発揮し、クラックの発生を抑制するために、バンドギャップの小さい層の厚みは、バンドギャップの大きい層よりも厚く、40nm以下とするのが好ましい。また、超格子積層体内で必ずしもすべて同じ膜厚、同じ組成で積層させる必要はない。

【0035】

電子デバイス用エピタキシャル基板1は、HEMTに用いるのが好ましい。図2に示すエピタキシャル基板1の主積層体4は、Ba3Alb3Gac3Ind3N(0≦a3≦1, 0≦b3≦1, 0≦c3≦1, 0≦d3≦1, a3+b3+c3+d3=1)材料からなるチャネル層4aおよびチャネル層4aよりバンドギャップの大きいBa4Alb4Gac4Ind4N(0≦a4≦1, 0≦b4≦1, 0≦c4≦1, 0≦d4≦1, a4+b4+c4+d4=1)材料からなる電子供給層4bを有することができる。この際、両層とも単一もしくは複数の組成から構成することができる。特に、合金散乱をさけ、電流導通部分の比抵抗を下げるためには、チャネル層4aの少なくとも電子供給層4bと接する部分はGaN材料とすることが好ましい。

【0036】

チャネル層4aのバッファ層とは反対側の部分は、C濃度が低いことが好ましく、4×1016/cm3以下に設定することが好ましい。この部分は、電子デバイスの電流導通部分に相当するため、導電性を阻害したり、電流コラプスを発生させたりする不純物は含まないほうが望ましいからである。また、n型不純物による残留キャリアによるリークを抑制するため、1×1015/cm3以上存在することが望ましい。

【0037】

次に、本発明の電子デバイス用エピタキシャル基板の製造方法の実施形態について図面を参照しながら説明する。

【0038】

図2に示すように、Si単結晶基板2上に、絶縁層としてのバッファ3と、バッファ3上に複数層のIII族窒化物層をエピタキシャル成長させたHEMT構造の主積層体4とを順に形成した、横方向を電流導通方向とする電子デバイス用エピタキシャル基板1の製造方法であって、バッファ3は、Si単結晶基板2と接する初期成長層5および初期成長層5上の超格子多層構造からなる超格子積層体6を有し、初期成長層5はAlN材料からなり、かつ超格子積層体6はBa1Alb1Gac1Ind1N(0≦a1≦1, 0≦b1≦1, 0≦c1≦1, 0≦d1≦1, a1+b1+c1+d1=1)材料からなる第1層6aおよび第1層6aとはバンドギャップの異なるBa2Alb2Gac2Ind2N(0≦a2≦1, 0≦b2≦1, 0≦c2≦1, 0≦d2≦1, a2+b2+c2+d2=1)材料からなる第2層6bを交互に積層してなり、超格子積層体6と主積層体4のバッファ3側の部分4´とは、ともにC濃度が1018/cm3以上となるよう形成されることを特徴とし、かかる構成を有することにより、縦方向耐圧特性および横方向耐圧特性を良好に両立させ、かつ横方向リーク電流を低減させることができる電子デバイス用エピタキシャル基板を製造することができるものである。

【0039】

超格子積層体6と主積層体4のバッファ3側の部分4´に添加されるCは、CVD法を用いて成長する場合には、以下に示すいくつかの方法により添加することができる。

第1の方法:Cを含む原料ガスを、III族窒化物成長中に別途添加する。メタン・エタン・エチレン・アセチレン・ベンゼン・シクロペンタン等が例示される。

第2の方法:有機金属中のメチル基・エチル基等を、成長III族窒化物成長条件によりエピタキシャル成長層に混入させる。有機金属の分解を抑えるように、成長温度・成長圧力・成長速度・成長時のアンモニア流量・水素流量・窒素流量等を適宜設定することにより、エピタキシャル成長層に添加されるC濃度を調整することが可能である。

なお、本願では、超格子積層体6のC濃度は、SIMSにより、超格子積層体6の厚さの1/2を除去した箇所の測定値とする。主積層体4のバッファ3側の部分4´のC濃度は、SIMSにより、前記部分4´の厚さの1/2を除去した箇所の測定値とする。

【0040】

なお、図1および図2は、代表的な実施形態の例を示したものであって、本発明はこれらの実施形態に限定されるものではない。たとえば、各層の間に本発明の効果に悪影響を与えない程度の中間層を挿入したり、他の超格子層を挿入したり、組成に傾斜をつけたりすることはできる。また、Si単結晶の表面に、窒化膜、炭化膜、Al層などを形成することもできる。

【実施例】

【0041】

(実験例1)

比抵抗がそれぞれ1×10-1Ω・cm,1×10Ω・cm,2×103Ω・cm,1×104Ω・cmの600μm厚の(111)面4インチSi単結晶基板上に、初期成長層(AlN材料:厚さ100nm)および超格子積層体(AlN:膜厚4nmとAl0.15Ga0.85N:膜厚25nm、合計85層)を成長させてバッファを形成し、この超格子積層体上にチャネル層(GaN材料:厚さ1.5μm)および電子供給層(Al0.25Ga0.75N材料:厚さ20nm)をエピタキシャル成長させてHEMT構造の主積層体を形成して試料1〜4を得た。超格子積層体のC濃度を変化させ、主積層体のバッファ側の部分のC濃度は、いずれの結果も、1.5〜2.0×1018/cm3の範囲であった。また、チャネル層の電子供給層側の部分は、C濃度が0.8〜3.5×1016/cm3の範囲であった。各層の成長温度、圧力を表1に示す。表中P1を調整することによりC濃度を調整し、成膜圧力を下げることによりC濃度を増加させている。成長方法としてはMOCVD法を使用し、III族原料としては、TMA(トリメチルアルミニウム)・TMG(トリメチルガリウム)、V族原料としてはアンモニアを用い、キャリアガスとして、水素および窒素ガスを用いた。ここでいう成膜温度は、成長中に放射温度計を用いて測定した、基板自体の温度を意味する。なお、C濃度のSIMS測定は、エピタキシャル層側からエッチングを行い、Cameca製の測定装置で、イオン源としてCs−を用い、イオンエネルギーは8keVで行った。

【0042】

【表1】

【0043】

(実験例2)

初期成長層を700℃で成長したGaN材料(厚さ:20nm)で形成し、各層の成長温度、圧力を表2に示す条件で行ったこと以外は、実験例1の試料2と同様の方法により試料5を作製した。

【0044】

【表2】

【0045】

図3(a)、図3(b)および図3(c)に、試料2および試料5の横方向耐圧、横方向リーク電流および縦方向耐圧の測定結果を示す。測定は、以下の通り行った。

縦方向:基板表面に80μmφからなるTi/Al積層構造のオーミック電極を形成し、オーミック電極外側を50nmの厚みでエッチングした後、基板裏面を金属板に接地し、両電極間に流れる電流値を電圧に対して測定した。

横方向:200μm□(四角)からなるTi/Al積層構造のオーミック電極を各々の一辺を10μmの距離を離して配置して形成し、前記オーミック電極周囲を150nmの厚みでエッチングした後、両電極間に流れる電流値を電圧に対して測定した。この際、空気中の放電を抑制するため、絶縁油で両電極間を絶縁している。また、基板裏面へのリークの影響をなくすため、基板下には絶縁板を配置している。

本実験例において、縦方向耐圧は縦方向の電流値を上記電極面積で単位面積当たりの値に換算した値が10-4A/cm2に達する電圧値で、横方向耐圧は横方向の電流値を上記電極の1辺の長さ当たりの値に換算した値が10-4A/cmに達する電圧値で、横方向リーク電流は横方向が100Vでの電流値で、それぞれ定義する。

超格子積層体6のC濃度は、SIMSにより、超格子積層体6の厚さの1/2を除去した箇所を測定することにより得た。主積層体4のバッファ3側の部分4´のC濃度は、SIMSにより、前記部分4´の厚さの1/2を除去した箇所を測定値することにより得た。

【0046】

超格子積層体のC濃度を変化させた結果、横方向耐圧、横方向リーク電流については、いずれもほとんど変化ないのに対し、試料2の縦方向耐圧については、超格子積層体のC濃度が1×1018/cm3を超えると、特異的に急激に高くなることが確認できる。また、こうした現象は、試料5を参照して分かるように、初期成長層をAlNにした場合固有の現象であることも確認できる。また、試料1,3および4についても、試料2と同様の結果が得られた。

【0047】

(実験例3)

超格子積層体の成長圧力を10kPaとして、主積層体のバッファ側の部分のC濃度を変化させ、各層の成長温度、圧力を表3に示す条件で行ったこと以外は、実験例1の試料1〜4と同様の方法により試料6〜9を作製した。表中P2を調整することによりC濃度を調整し、成膜圧力を下げることによりC濃度を増加させている。超格子積層体のC濃度は、いずれの結果も1.5〜2.5×1018/cm3の範囲であった。

【0048】

【表3】

【0049】

図4(a)、図4(b)および図4(c)に、試料6の横方向耐圧、横方向リーク電流および縦方向耐圧の測定結果を示す。主積層体のC濃度を変化させた結果、横方向耐圧、横方向リーク電流については、ほとんど変化ないのに対し、試料6の縦方向耐圧については、主積層体のバッファ側の部分のC濃度が1×1018/cm3を超えると、特異的に急激に高くなることが確認できる。また、実験例1と同様に、使用するSi単結晶基板の比抵抗が異なる試料7〜9についても、図4(a)〜図4(c)に示した結果と大きな差異は認められなかった。

【0050】

実験例1〜3において、縦方向耐圧を向上させるために、超格子積層体およびチャネル層バッファ側のC濃度を所定値以上とすることにより縦方向耐圧を向上できることを確認することができた。次の実験例4では、前記バッファ層C濃度については実験例1〜3にて好ましいと確認された所定値以上となるようとし、高周波特性の改善を試みた。

【0051】

(実験例4)

比抵抗6×103Ω・cmの600μm厚の(111)面4インチSi単結晶基板上に、初期窒化層の形成を抑制しつつ、初期成長層(AlN材料:厚さ100nm)および超格子積層体(AlN:膜厚4nmとAl0.15Ga0.85N:膜厚25nm、合計85層)を成長させてバッファを形成し、この超格子積層体上にチャネル層(GaN材料:厚さ1.5μm)および電子供給層(Al0.25Ga0.75N材料:厚さ20nm)を、成長圧力、成長温度を表4の条件でエピタキシャル成長させ、HEMT構造の主積層体を形成して試料10を得た。超格子積層体のC濃度は2.0×1018/cm3であり、主積層体のバッファ側の0.2μm厚の部分のC濃度は3.0×1018/cm3であった。また、チャネル層の電子供給層側の部分は、C濃度は1×1016/cm3としている。

【0052】

【表4】

【0053】

SIMSにてSi単結晶基板内の不純物を観察したところ、図5(a)に示すように、III族元素の不純物としては、Al、Ga以外は認められず、Al,Gaともに、1×1016/cm3以下であり、1×1015/cm3以上存在する領域は、Si単結晶と初期成長層の界面から0.2μm以内の領域であった。TEMでSi単結晶基板と初期成長層の界面を確認したが、1nm以上の厚みのSiNx膜の存在は確認されなかった。また、Si単結晶基板と初期成長層の界面から0.2μm以内の領域では平均して、Alの濃度がGaの濃度と比較して低いことも確認された。なお、Al,GaのSIMS測定は、Si単結晶側からエッチングを行い、Cameca製の測定装置で、イオン源としてO2+を用い、イオンエネルギーは3keVで行った。

【0054】

また、本基板について、水銀プローブ(MSI electronics製)および、インピーダンスアナライザ(HP4284A)を用いてCV測定を行ったところ、図5(b)に示すように、空乏層が換算膜厚にして8μm程度まで広がっていることが確認された。CV測定時の交流成分の周波数および振幅はそれぞれ100kHz,10mVである。尚、便宜上、Si単結晶と初期成長層の界面の位置は、SIMS測定において、Siの濃度が1/5以下となる位置から0.05μm基板側にシフトした位置とした。SIMS測定時のエッチング粗れの結果、Si単結晶とエピタキシャル成長層が混在して露出することによるIII族元素の見かけ上の増加を避けるためである。

【0055】

また、使用する4インチSi単結晶基板の抵抗率を、2×103Ω・cm、8×103Ω・cm、12×103Ω・cmとした以外は、試料10と同様の方法で作製された試料11,12,13についても同様の試験をおこなった。この2つの試験いずれも、上記と同様に、SIMSにてSi単結晶基板内の不純物を観察したところ、Al、Ga以外のIII族元素は認められず、Al,Gaともに、1×1016/cm3以下であり、1×1015/cm3以上存在する領域は、Si単結晶と初期成長層の界面から0.2μm以下の領域であった。TEMでSi単結晶基板と初期成長層の界面を確認したが1nm以上の厚みのSiNx膜の存在は確認されなかった。また、Si単結晶基板と初期成長層の界面から0.2μm以下の領域では平均して、Alの濃度がGaのそれと比較して低いことも確認された。また、空乏層が換算膜厚にして、それぞれ、6μm、8μm、8μm程度まで広がっていることが確認された。

【0056】

(実験例5)

比抵抗5×103Ω・cmの600μm厚の(111)面4インチSi単結晶基板上に、初期成長層成長開始前に、アンモニアガスを、キャリアガスである水素ガスに対し、10%含有したガスのみを5分間1050℃で流すことにより、初期窒化層を意図的に形成した以外は、試料2と同様に試料14を作製した。

【0057】

SIMSにてSi単結晶基板内の不純物を観察したところ、図6(a)に示すように、Al,Gaともに、1×1016/cm3以下であるものの、AlまたはGaが、1×1015/cm3以上存在する領域は、1μm以上であった。TEMでSi単結晶基板と初期成長層の界面を確認したところSiNx膜が1.5nm程度存在することが確認された。また、Alの濃度がGaのそれと比較して高いこととも確認された。また、本基板について、水銀プローブを用いたCV測定を行ったところ、図6(b)に示すように、空乏層が換算膜厚にして2μm程度までしか広がっていないことが確認された。

【0058】

(実験例6)

初期成長層からチャネル層の成長温度を表5に示す条件で上昇させた以外は、試料10と同様に試料15を作製した。

【0059】

【表5】

【0060】

SIMSにてSi単結晶基板内の不純物を観察したところ、図7(a)に示すように、Gaの濃度が、1×1016/cm3以上である部分が存在した、1×1015/cm3以上存在する領域は、0.3μm以下であった。TEMでSi単結晶基板と初期成長層の界面を確認したが1nm以上の厚みのSiNx膜の存在は確認されなかった。また、Alの濃度がGaのそれと比較して低いことも確認された。また、本基板について、図7(b)に示すように、水銀プローブを用いたCV測定を行ったところ、空乏層が換算膜厚にして2μm程度までしか広がっていないことが確認された。

【0061】

試料1〜13と試料14,15とを比較すると、Al,GaのSi単結晶への混入を抑制することが、空乏層を効果的に広げることにつながることが確認される。空乏層を効率的に広げることができることは、エピタキシャル層内およびSi単結晶基板内のキャリアの低減ができていることと同義であり、基板表面に形成される電極と、前記p型不純物の容量性あるいは誘導性の結合による電子デバイスの高周波動作時の損失を抑制できることを意味する。

特に、試料2と試料14との比較から、窒化厚を薄くすることにより、試料2と試料15との比較からエピタキシャル層の成膜温度を低くすることにより、上記効果を引き出すことができたと推察される。

【0062】

なお、全ての実験例で作製したエピタキシャル基板において、ホール効果測定法により、チャネル層部分の電気特性を評価したところ、シート抵抗値450Ω/□以下(四角)、移動度は1550cm2/Vs以上と良好な特性を示すことが確認されている。

【産業上の利用可能性】

【0063】

本発明の電子デバイス用エピタキシャル基板によれば、AlN材料からなる初期成長層および所定の超格子積層体を有するバッファならびに所定の主積層体を具え、これら超格子積層体と主積層体のバッファ側の部分とが、ともに1×1018/cm3以上のC濃度を有することにより、横方向リーク電流の低減および横方向耐圧特性を良好に両立させ、かつ縦方向耐圧を向上させることができる。更に、前記特性に加えて、前記Si単結晶基板の比抵抗を1000Ω・cm以上とし、前記Si単結晶基板の初期成長層側のIII族原子の合計の最大濃度が1×1016/cm3以下であり、かつ、0.3μm深さの位置でのIII族原子の合計濃度が1×1015/cm3以下とすることにより高周波信号印加時の損失を低減することができる。

【0064】

また、本発明によれば、AlN材料からなる初期成長層および所定の超格子積層体を有するバッファならびに所定の主積層体を具え、これら超格子積層体と主積層体のバッファ側の部分とが、ともに1×1018/cm3以上のC濃度を有することにより、横方向リーク電流の低減および横方向耐圧特性を良好に両立させ、かつ縦方向耐圧を向上させることができ、更に、前記特性に加えて、高周波信号印加時の損失を低減することができる電子デバイス用エピタキシャル基板を製造することができる。

【符号の説明】

【0065】

1 電子デバイス用エピタキシャル基板

2 Si単結晶基板

3 バッファ

4 主積層体

4a チャネル層

4b 電子供給層

5 初期成長層

6 超格子積層体

6a 第1層

6b 第2層

【特許請求の範囲】

【請求項1】

Si単結晶基板と、該Si単結晶基板上に形成した絶縁層としてのバッファと、該バッファ上に複数層のIII族窒化物層をエピタキシャル成長させて形成した主積層体とを具え、横方向を電流導通方向とする電子デバイス用エピタキシャル基板であって、

前記バッファは、前記Si単結晶基板と接する初期成長層および該初期成長層上の超格子多層構造からなる超格子積層体を少なくとも有し、

前記初期成長層はAlN材料からなり、かつ前記超格子積層体はBa1Alb1Gac1Ind1N(0≦a1≦1, 0≦b1≦1, 0≦c1≦1, 0≦d1≦1, a1+b1+c1+d1=1)材料からなる第1層および該第1層とはバンドギャップの異なるBa2Alb2Gac2Ind2N(0≦a2≦1, 0≦b2≦1, 0≦c2≦1, 0≦d2≦1, a2+b2+c2+d2=1)材料からなる第2層を交互に積層してなり、

前記超格子積層体と、前記主積層体の前記バッファ側の部分は、ともにC濃度が1×1018/cm3以上であることを特徴とする電子デバイス用エピタキシャル基板。

【請求項2】

前記第1層がAlN材料からなり、前記第2層がAlb2Gac2N(a2=0, 0<b2≦0.5,0.5≦c2<1,d2=0)材料からなる請求項1に記載の電子デバイス用エピタキシャル基板。

【請求項3】

前記Si単結晶基板は、比抵抗が1000Ω・cm以上で、前記初期成長層から0.1μmの深さまでのIII族原子の合計の最大濃度が1×1016/cm3以下であり、かつ前記初期成長層から0.3μmの深さの位置でのIII族原子の合計濃度が1×1015/cm3以下である請求項1または2に記載の電子デバイス用エピタキシャル基板。

【請求項4】

Si単結晶基板上に、絶縁層としてのバッファと、該バッファ上に複数層のIII族窒化物層をエピタキシャル成長させた主積層体とを順に形成した、横方向を電流導通方向とする電子デバイス用エピタキシャル基板の製造方法であって、

前記バッファは、前記Si単結晶基板と接する初期成長層および該初期成長層上の超格子多層構造からなる超格子積層体を少なくとも有し、

前記初期成長層はAlN材料からなり、かつ前記超格子積層体はBa1Alb1Gac1Ind1N(0≦a1≦1, 0≦b1≦1, 0≦c1≦1, 0≦d1≦1, a1+b1+c1+d1=1)材料からなる第1層および該第1層とはバンドギャップの異なるBa2Alb2Gac2Ind2N(0≦a2≦1, 0≦b2≦1, 0≦c2≦1, 0≦d2≦1, a2+b2+c2+d2=1)材料からなる第2層を交互に積層してなり、

前記超格子積層体と、前記主積層体の前記バッファ側の部分は、ともにC濃度が1018/cm3以上となるよう形成されることを特徴とする電子デバイス用エピタキシャル基板の製造方法。

【請求項5】

前記Si単結晶基板は、比抵抗が1000Ω・cm以上で、前記初期成長層から0.1μmの深さまでのIII族原子の合計の最大濃度が1×1016/cm3以下であり、かつ前記初期成長層から0.3μmの深さの位置でのIII族原子の合計濃度が1×1015/cm3以下となるよう形成される請求項4に記載の電子デバイス用エピタキシャル基板の製造方法。

【請求項1】

Si単結晶基板と、該Si単結晶基板上に形成した絶縁層としてのバッファと、該バッファ上に複数層のIII族窒化物層をエピタキシャル成長させて形成した主積層体とを具え、横方向を電流導通方向とする電子デバイス用エピタキシャル基板であって、

前記バッファは、前記Si単結晶基板と接する初期成長層および該初期成長層上の超格子多層構造からなる超格子積層体を少なくとも有し、

前記初期成長層はAlN材料からなり、かつ前記超格子積層体はBa1Alb1Gac1Ind1N(0≦a1≦1, 0≦b1≦1, 0≦c1≦1, 0≦d1≦1, a1+b1+c1+d1=1)材料からなる第1層および該第1層とはバンドギャップの異なるBa2Alb2Gac2Ind2N(0≦a2≦1, 0≦b2≦1, 0≦c2≦1, 0≦d2≦1, a2+b2+c2+d2=1)材料からなる第2層を交互に積層してなり、

前記超格子積層体と、前記主積層体の前記バッファ側の部分は、ともにC濃度が1×1018/cm3以上であることを特徴とする電子デバイス用エピタキシャル基板。

【請求項2】

前記第1層がAlN材料からなり、前記第2層がAlb2Gac2N(a2=0, 0<b2≦0.5,0.5≦c2<1,d2=0)材料からなる請求項1に記載の電子デバイス用エピタキシャル基板。

【請求項3】

前記Si単結晶基板は、比抵抗が1000Ω・cm以上で、前記初期成長層から0.1μmの深さまでのIII族原子の合計の最大濃度が1×1016/cm3以下であり、かつ前記初期成長層から0.3μmの深さの位置でのIII族原子の合計濃度が1×1015/cm3以下である請求項1または2に記載の電子デバイス用エピタキシャル基板。

【請求項4】

Si単結晶基板上に、絶縁層としてのバッファと、該バッファ上に複数層のIII族窒化物層をエピタキシャル成長させた主積層体とを順に形成した、横方向を電流導通方向とする電子デバイス用エピタキシャル基板の製造方法であって、

前記バッファは、前記Si単結晶基板と接する初期成長層および該初期成長層上の超格子多層構造からなる超格子積層体を少なくとも有し、

前記初期成長層はAlN材料からなり、かつ前記超格子積層体はBa1Alb1Gac1Ind1N(0≦a1≦1, 0≦b1≦1, 0≦c1≦1, 0≦d1≦1, a1+b1+c1+d1=1)材料からなる第1層および該第1層とはバンドギャップの異なるBa2Alb2Gac2Ind2N(0≦a2≦1, 0≦b2≦1, 0≦c2≦1, 0≦d2≦1, a2+b2+c2+d2=1)材料からなる第2層を交互に積層してなり、

前記超格子積層体と、前記主積層体の前記バッファ側の部分は、ともにC濃度が1018/cm3以上となるよう形成されることを特徴とする電子デバイス用エピタキシャル基板の製造方法。

【請求項5】

前記Si単結晶基板は、比抵抗が1000Ω・cm以上で、前記初期成長層から0.1μmの深さまでのIII族原子の合計の最大濃度が1×1016/cm3以下であり、かつ前記初期成長層から0.3μmの深さの位置でのIII族原子の合計濃度が1×1015/cm3以下となるよう形成される請求項4に記載の電子デバイス用エピタキシャル基板の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2010−245504(P2010−245504A)

【公開日】平成22年10月28日(2010.10.28)

【国際特許分類】

【出願番号】特願2009−280860(P2009−280860)

【出願日】平成21年12月10日(2009.12.10)

【出願人】(506334182)DOWAエレクトロニクス株式会社 (336)

【Fターム(参考)】

【公開日】平成22年10月28日(2010.10.28)

【国際特許分類】

【出願日】平成21年12月10日(2009.12.10)

【出願人】(506334182)DOWAエレクトロニクス株式会社 (336)

【Fターム(参考)】

[ Back to top ]