電子ビーム描画方法および装置

【課題】 描画装置により半導体デバイス製品のパターン形成を行う際に、下地パターンと重ね合わせ描画を行うためのアライメントマーク検出精度を向上させる。

【解決手段】 アライメントマーク検出シミュレーションによりデバイス製品・工程ごと、およびマークの検出条件ごと、さらにマークがプロセス誤差を持つ場合についてテンプレート波形を作成する。あるデバイス製品・工程において重ねあわせ描画を行う際に、取得されたアライメント検出波形に対し、上記で作成された複数のテンプレート波形によるマッチング処理をそれぞれ行い、その中から相関係数最大となったテンプレートでの検出結果をアライメントマーク検出位置とする。

【解決手段】 アライメントマーク検出シミュレーションによりデバイス製品・工程ごと、およびマークの検出条件ごと、さらにマークがプロセス誤差を持つ場合についてテンプレート波形を作成する。あるデバイス製品・工程において重ねあわせ描画を行う際に、取得されたアライメント検出波形に対し、上記で作成された複数のテンプレート波形によるマッチング処理をそれぞれ行い、その中から相関係数最大となったテンプレートでの検出結果をアライメントマーク検出位置とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体デバイスの製造等において使用する電子ビーム描画方法および装置に関するものである。

【背景技術】

【0002】

近年の半導体デバイスの高集積化、高機能化に伴い、これを実現するためのプロセスには更なる微細化、高精度化が求められている。半導体デバイスの製造ではリソグラフィ工程により、半導体ウエハ(以下、ウエハと省略)上に塗布されたフォトレジストにパターンを転写して回路パターンを形成する。半導体デバイスは複数層の回路パターンにより構成され、ある層のパターンは、それより下層の回路パターンに位置合わせ(アライメント)して露光が行われる。

【0003】

電子ビーム描画装置は、このリソグラフィ工程でウエハ上にパターンを転写するために用いられる。装置の構成について図2により説明する。制御計算機201は全体システムの制御とともにマンマシンインターフェイス、外部からのデータ入力を分担している。描画データ202は描画を行うパターンを、繰り返し性などを利用して圧縮したファイルである。描画データ処理部203では描画データを電子ビームでショット可能な矩形図形データ(形状および位置データ)に分解する。補正演算部204はステージ測長系222から入力されるステージの位置データを元に、常に電子ビームが試料上の目標位置に照射されるように電子ビームの偏向を計算するとともに、電子光学系の偏向歪みを補正し、電子ビームが所望の目標位置に偏向するように補正を行う。ビ−ム制御部205はディジタルで計算された前段までの値を、偏向器を駆動するためのアナログ信号に変換する部分である。電子光学系210の最上部に設置された電子銃211から放射された電子ビームは与えられたデータにしたがってビーム偏向器212により偏向され、同時に真空チャンバ230内でウエハ251を載置したステージ221を移動させることにより、試料上の所定の位置に所望のパターンが描画される。ステージ制御系223は制御計算機201からのステージ位置制御信号と、ステージ測長系222からのステージ位置計測信号を元に、ステージを所定の位置に制御する機能を持つ。

【0004】

描画対象であるウエハ251上には半導体デバイスのチップ252が形成されており、それぞれのチップの4隅には合わせ描画のためのアライメントマーク253が形成されている。描画に先立って電子ビームによりアライメントマークの位置検出が行われる。これは電子ビームでアライメントマークを走査して、反射電子検出器231でアライメントマークからの反射電子を検出して、信号処理部232でアライメントマーク検出波形から位置検出を行うものである。その結果を補正演算部204にフィードバックして下層パターンの位置に対応してビーム偏向を制御することで合わせ描画が行われる。

【0005】

下層との合わせ描画のフローについて図3にて説明する。露光を行うウエハには下層の回路パターンとともにアライメントマークが形成されている、(300)、この上に回路パターンを形成する材料をCVD(Chemical Vaper Deposition・化学気相成長法)などにより成膜する。その上にさらにレジストを塗布(302)した後、描画装置にて描画を行う。チップ4隅に設けられたアライメントマークを電子ビームで走査して反射電子を検出し(303)、アライメントマーク検出波形を得る(304)。波形を信号処理してマーク位置を検出する(305)ことにより下地チップの形状歪みが測定される。下地チップの形状に合わせて描画を行うためのアライメント補正係数を算出(306)して、それに基づいてパターン描画を行う(307)。描画後はレジスト現像(308)により、回路パターンの転写されたレジストパターンが形成され、これをマスクとして、回路パターン材料をエッチング(309)して半導体デバイスの回路パターンを作成する。エッチング後は残ったレジストの除去、洗浄(310)などを行って1層分の回路パターンの作成が完了し、次の層も同様な工程で回路パターンを形成する。

【0006】

次に図4にて、アライメントマーク検出時のビーム走査と、検出波形について説明する。401は走査する電子ビームであり、矩形断面(ショットサイズ、幅:w/高さ:h)を持つ。ビームはショットとして離散的に試料に照射する。ショットサイズを一定に保ったまま、一定のショットピッチ(402)でマーク上を走査する。このときの各ショットの照射によるマークからの反射電子を反射電子検出器(図2−231)でそれぞれ検出する。走査する際のショット位置(ビーム偏向量)に対して反射電子検出出力をプロットすることにより、アライメントマークと周囲の材質差に対応したアライメントマーク検出波形(410)が得られる。

【0007】

次に図5および6にて、得られた検出信号からアライメントマークの位置検出を行うための波形処理について説明する。

【0008】

図5はテンプレートマッチング法による位置検出の例を示す。図で510は検出波形、511はテンプレート波形である。ここで、位置をx、検出波形をf(x)、テンプレート波形をp(x)、テンプレートの幅をWtとおいたときに、位置xでの検出波形とテンプレート波形の相関係数M(x)513をたとえば以下の式(1)で表す。

【0009】

【数1】

【0010】

テンプレートを移動させながらそれぞれの位置でM(x)を計算する。このときの移動量の単位はショットピッチで定義されるサンプリング間隔になる。こうして求められた各位置ごとの相関係数をたとえば2次近似曲線513で補間し、その頂点となる位置514をマーク検出位置とする。

【0011】

以上のようにして検出されたアライメントマークの位置を元に下地チップの形状歪みが測定した後、図7に示すようにチップ形状の設計値60に対する実際のチップの位置シフト61、回転62、拡大縮小63、台形歪64などの歪み成分に分解し、それぞれに応じて補正係数を設定して下層パターンに対する合わせ描画を実施する。

【0012】

図7は半導体デバイスの断面構造を示す。素子分離層(701)からゲート層(702)がトランジスタを形成する層であり、その上層(703〜708)が配線層である。これらの各層はそれぞれ、先に図3で説明したようなプロセスを経て、各層のパターンはリソグラフィ工程で形成される。この際のアライメントマークの断面は711、712、713に示すように各層で異なった構造を持つことになる。また、図8に示すように、たとえば配線層の平坦化のため使用されるCMP(Chemical Mechanical Polishing・化学機械的研磨)プロセスの影響により、アライメントマークを形成するメタル層801が非対称になり、それによりアライメントマーク検出波形も非対称になって下地層との合わせ誤差を生じる場合がある。このようなプロセスのバラツキによって生じる誤差をプロセス起因誤差と呼ぶ。

【0013】

アライメントマークのプロセス起因誤差に対応する技術としては以下のようなものが知られている。たとえば特開2000−275010号ではプロセス起因誤差によるアライメントマーク検出波形の形状歪みを補正して位置検出を行う例が開示されている。また特開2002−15980号では、アライメントマーク検出波形の非対称性と検出誤差の関係をあらかじめデータベース化しておき、補正を行って位置検出精度を向上させる技術が開示されている。

【0014】

【特許文献1】特開2000−275010号公報

【特許文献2】特開2002−15980号公報

【発明の開示】

【発明が解決しようとする課題】

【0015】

ところで、特開2000−275010号で開示された例では、アライメントマークの形状歪みの補正により却って誤差を重畳させてしまう可能性がある。また、特開2002−15980号で開示された例では検出波形の非対称性と検出誤差の関係を示すシグナルデータベースを、実ウエハおよび露光結果から作成するものであるが、製品および工程ごとにデータベースを作成する場合、その作業量が非常に大きなものとなる可能性がある。また、特に電子ビーム描画装置においては、図9に示すようにアライメントマーク検出波形は走査する電子ビームのサイズによっても変化する。電子ビーム描画装置ではビームのサイズは可変であり、アライメントマーク検出時にも検出出力と分解能を最適にするようにアライメント検出のジョブでビームサイズが設定される。図10中で921、922はアライメントマークであり、911、912はアライメントマーク検出時の電子ビームのビームサイズである。911はビームサイズが大きい場合、912はビームサイズが小さい場合の例を示している。また、それぞれのビームサイズに対応したアライメントマーク検出波形が931、932である。図に示したようにビームサイズと、アライメントマーク幅との関係により検出波形の形状は変化する。

【0016】

以上に示したように、電子ビーム描画におけるアライメントマーク検出波形は検出条件により異なるため、これらのそれぞれに対応し、さらにプロセス起因誤差にも対応して精度良くアライメントマークの位置検出を行うことが課題となっている。

【課題を解決するための手段】

【0017】

上記課題を解決するために、本発明における描画方法および装置では、下地パターンと重ね合わせ描画を行うためのアライメントマーク検出精度向上のために、アライメントマーク検出シミュレーションによりデバイス製品・工程ごと、およびマークの検出条件ごと、さらにマークがプロセス誤差を持つ場合についてテンプレート波形を作成し、あるデバイス製品・工程において重ねあわせ描画を行う際に、取得されたアライメント検出波形に対し、上記で作成された複数のテンプレート波形によるマッチング処理をそれぞれ行い、その中から相関係数最大となったテンプレートでの検出結果をアライメントマーク検出位置とすることにより、下地パターンに対する重ね合わせ精度を向上させるものである。

【発明の効果】

【0018】

本発明は描画装置により半導体デバイス製品のパターン形成を行う際に、下地パターンと重ね合わせ描画を行うためのアライメントマーク検出精度向上のために、アライメントマーク検出シミュレーションによりデバイス製品・工程ごと、およびマークの検出条件ごと、さらにマークがプロセス誤差を持つ場合についてテンプレート波形を作成し、あるデバイス製品・工程において重ねあわせ描画を行う際に、取得されたアライメント検出波形に対し、上記で作成された複数のテンプレート波形によるマッチング処理をそれぞれ行い、その中から相関係数最大となったテンプレートでの検出結果をアライメントマーク検出位置とすることにより、描画装置により半導体デバイス製品のパターン形成を行う際に、下地パターンに対する重ね合わせ精度を向上させるものである。

【発明を実施するための最良の形態】

【0019】

本発明に係る、電子ビーム描画方法および装置の実施の形態について、以下図面を用いて説明する。

【実施例1】

【0020】

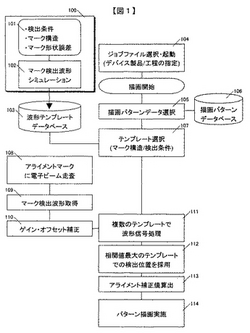

図1は本発明における第1の実施例である電子ビーム描画方法に関わる実施例を説明する図である。100はアライメントマーク検出波形のシミュレーションを実施するステップであり、ビームサイズ、ショットピッチなどの検出条件、半導体デバイスの製品および描画の対象となる層(工程)に対応したマークの構造(材質、寸法、層構造)、さらにはマーク形状誤差などの計算パラメータ101をもとに、102のステップでシミュレーションを行うものである。この場合のシミュレーション手法にはモンテカルロシミュレーションを用いることが一般的に考えられる。以上の計算はオフラインで実施され、計算結果は先に述べた計算パラメータと関連付けて、描画装置のテンプレート波形データベースに格納される(103)。描画を行う際には、まずジョブファイルを選択・起動し描画を行うデバイス製品、工程を指定する(104)。描画が開始されるとジョブで指定された描画パターンデータを描画パターンデータベース106から選択する(105)。次にアライメントに使用するテンプレート波形をテンプレート波形データベースから選択する(107)。ジョブファイル中にはデバイス製品/工程と、アライメントマーク検出条件(ビームサイズ・ショットピッチ)が指定されており、それらとの関連付けによりデータベースからテンプレート波形が選択される。また、この際にはマークのプロセス誤差を変化させたシミュレーションから得られた複数のテンプレート波形を選択する。

【0021】

アライメントマーク検出時には、アライメントマークに電子ビームを照射し(108)、マーク検出波形を取得(109)した後、テンプレートマッチングを行うため波形のオフセット・ゲイン補正を行う(110)。オフセット・ゲイン補正については図11について説明する。

【0022】

反射電子検出器からの出力は、デバイス製品/工程によって異なるアライメントマークの種類の違いにより信号レベルは非常に広いレンジで異なるものとなる。これはアライメントマークとその周囲を構成する材質により、マークからの反射もバックグラウンドからの反射も様々に異なるからである。これらに対して精度よくテンプレートマッチングを行うためにオフセット・ゲイン補正を行う。図10中で1001は反射電子検出器から得られたアライメントマーク検出信号である。これをオフセット補正によりバックグラウンドレベルをゼロにする(1002)。さらにゲイン補正により波形のピークを所定の信号レベルにまで増幅する(1003)。このようにして、アライメント検出波形を規格化することにより精度よくテンプレートマッチングを行うことが可能となる。

【0023】

そのように規格化された検出波形を107で選択された複数のテンプレートでそれぞれ波形処理を行う(111)。それによって得られた複数の処理結果のうち、相関係数(図6−613のピーク値)が最も高かったテンプレートでの結果をマークの検出位置として採用する。

【0024】

波形処理をこのように構成することにより、ステップ108〜109で検出する実際のアライメントマークが持つプロセス起因誤差に対応して、最適なテンプレートで波形処理した結果を採用することでき、アライメントマーク位置検出の精度を向上させることが可能となる。

【0025】

以上の処理によりチップの4隅に配置されたそれぞれのアライメントマークの位置検出を行って下地チップ歪みを求め、図7にて説明した各歪み成分に応じてアライメント補正値を算出して(113)、パターン描画を実施する(114)。

【実施例2】

【0026】

図11本発明における第2実施例である電子ビーム描画装置に関わる実施例を説明する図である。1101は制御計算機で全体システムの制御を行う。オフラインで計算されたテンプレート波形は制御計算機1101を経て波形テンプレートデータベースに保持される。各テンプレート波形はそれに対応するデバイス製品および工程名称と関連付けて保持される。

【0027】

基板載置手段1114には、描画対象である基板1120が載置され、基板上に形成されたチップ1121に形成されたアライメントマーク1122にビームを照射する手段1111(電子銃)、1112(偏向器)とにより、電子ビームでアライメントマークを走査し、反射電子検出器1113でアライメントマークからの反射電子を検出してアライメントマーク検出波形を得る。

【0028】

描画時には制御計算機1101からジョブファイルを選択・起動し描画を行うデバイス製品、工程を指定する。ジョブファイル中にはデバイス製品/工程と、アライメントマーク検出条件(ビームサイズ・ショットピッチ)が指定されており、それらとの関連付けにより波形テンプレートデータベース1102から、テンプレート選択手段1104により、そのジョブにおける描画に使用するテンプレート波形を選択する。この際にはマークのプロセス誤差を変化させたシミュレーションから得られた複数のテンプレート波形を選択する。

【0029】

アライメントマーク検出波形は波形処理手段1105により、先に選択されたそれぞれのテンプレートによりマッチング処理を行い、得られた複数の波形処理結果からもっともマッチング相関の高かったテンプレートでの検出結果を選択する。それらの処理結果は、たとえば前記波形処理に用いたテンプレートと、実際のアライメントマーク検出波形とを重ね合わせて制御計算機の表示部11012に表示される。選択された結果を用いて補正演算部1106でアライメント補正係数を算出してそのデータをビーム制御部に送り、重ね合わせ描画を行う。

【産業上の利用可能性】

【0030】

以上、本発明者によってなされた以上の説明は、発明の背景となった利用分野である半導体デバイスの製造に関して行ったが、それに限定されるものではなく、液晶ディスプレイ基板や磁気ヘッドの製造など、描画装置により、基板上の下地パターンに重ね合わせて微細パターンを形成する製品の製造に適用することが可能である。

【図面の簡単な説明】

【0031】

【図1】本発明の第1の実施例に関して説明する図。

【図2】電子ビーム描画装置の校正について説明する図。

【図3】合わせ描画のフローについて説明する図。

【図4】アライメントマーク検出時のビーム走査と検出波形を説明する図。

【図5】テンプレートマッチング法で位置検出を行う際の波形処理を説明する図。

【図6】下地チップ歪みの成分を説明する図。

【図7】半導体デバイスとアライメントマークの断面構造を説明する図。

【図8】アライメントマークのプロセス起因誤差の例を説明する図。

【図9】ビームサイズによるアライメントマーク検出波形の違いを説明する図。

【図10】アライメント波形のゲイン・オフセット補正について説明する図。

【図11】本発明の第2の実施例に関して説明する図。

【符号の説明】

【0032】

201…制御計算機、203…描画データ処理部、204…補正演算部、222…ステージ測長系、205…ビ−ム制御部、210…電子光学系、211…電子銃、212…ビーム偏向器230…真空チャンバ内、251…ウエハ、221…ステージ、223…ステージ制御系、253…アライメントマーク、232…信号処理部。

【技術分野】

【0001】

本発明は、半導体デバイスの製造等において使用する電子ビーム描画方法および装置に関するものである。

【背景技術】

【0002】

近年の半導体デバイスの高集積化、高機能化に伴い、これを実現するためのプロセスには更なる微細化、高精度化が求められている。半導体デバイスの製造ではリソグラフィ工程により、半導体ウエハ(以下、ウエハと省略)上に塗布されたフォトレジストにパターンを転写して回路パターンを形成する。半導体デバイスは複数層の回路パターンにより構成され、ある層のパターンは、それより下層の回路パターンに位置合わせ(アライメント)して露光が行われる。

【0003】

電子ビーム描画装置は、このリソグラフィ工程でウエハ上にパターンを転写するために用いられる。装置の構成について図2により説明する。制御計算機201は全体システムの制御とともにマンマシンインターフェイス、外部からのデータ入力を分担している。描画データ202は描画を行うパターンを、繰り返し性などを利用して圧縮したファイルである。描画データ処理部203では描画データを電子ビームでショット可能な矩形図形データ(形状および位置データ)に分解する。補正演算部204はステージ測長系222から入力されるステージの位置データを元に、常に電子ビームが試料上の目標位置に照射されるように電子ビームの偏向を計算するとともに、電子光学系の偏向歪みを補正し、電子ビームが所望の目標位置に偏向するように補正を行う。ビ−ム制御部205はディジタルで計算された前段までの値を、偏向器を駆動するためのアナログ信号に変換する部分である。電子光学系210の最上部に設置された電子銃211から放射された電子ビームは与えられたデータにしたがってビーム偏向器212により偏向され、同時に真空チャンバ230内でウエハ251を載置したステージ221を移動させることにより、試料上の所定の位置に所望のパターンが描画される。ステージ制御系223は制御計算機201からのステージ位置制御信号と、ステージ測長系222からのステージ位置計測信号を元に、ステージを所定の位置に制御する機能を持つ。

【0004】

描画対象であるウエハ251上には半導体デバイスのチップ252が形成されており、それぞれのチップの4隅には合わせ描画のためのアライメントマーク253が形成されている。描画に先立って電子ビームによりアライメントマークの位置検出が行われる。これは電子ビームでアライメントマークを走査して、反射電子検出器231でアライメントマークからの反射電子を検出して、信号処理部232でアライメントマーク検出波形から位置検出を行うものである。その結果を補正演算部204にフィードバックして下層パターンの位置に対応してビーム偏向を制御することで合わせ描画が行われる。

【0005】

下層との合わせ描画のフローについて図3にて説明する。露光を行うウエハには下層の回路パターンとともにアライメントマークが形成されている、(300)、この上に回路パターンを形成する材料をCVD(Chemical Vaper Deposition・化学気相成長法)などにより成膜する。その上にさらにレジストを塗布(302)した後、描画装置にて描画を行う。チップ4隅に設けられたアライメントマークを電子ビームで走査して反射電子を検出し(303)、アライメントマーク検出波形を得る(304)。波形を信号処理してマーク位置を検出する(305)ことにより下地チップの形状歪みが測定される。下地チップの形状に合わせて描画を行うためのアライメント補正係数を算出(306)して、それに基づいてパターン描画を行う(307)。描画後はレジスト現像(308)により、回路パターンの転写されたレジストパターンが形成され、これをマスクとして、回路パターン材料をエッチング(309)して半導体デバイスの回路パターンを作成する。エッチング後は残ったレジストの除去、洗浄(310)などを行って1層分の回路パターンの作成が完了し、次の層も同様な工程で回路パターンを形成する。

【0006】

次に図4にて、アライメントマーク検出時のビーム走査と、検出波形について説明する。401は走査する電子ビームであり、矩形断面(ショットサイズ、幅:w/高さ:h)を持つ。ビームはショットとして離散的に試料に照射する。ショットサイズを一定に保ったまま、一定のショットピッチ(402)でマーク上を走査する。このときの各ショットの照射によるマークからの反射電子を反射電子検出器(図2−231)でそれぞれ検出する。走査する際のショット位置(ビーム偏向量)に対して反射電子検出出力をプロットすることにより、アライメントマークと周囲の材質差に対応したアライメントマーク検出波形(410)が得られる。

【0007】

次に図5および6にて、得られた検出信号からアライメントマークの位置検出を行うための波形処理について説明する。

【0008】

図5はテンプレートマッチング法による位置検出の例を示す。図で510は検出波形、511はテンプレート波形である。ここで、位置をx、検出波形をf(x)、テンプレート波形をp(x)、テンプレートの幅をWtとおいたときに、位置xでの検出波形とテンプレート波形の相関係数M(x)513をたとえば以下の式(1)で表す。

【0009】

【数1】

【0010】

テンプレートを移動させながらそれぞれの位置でM(x)を計算する。このときの移動量の単位はショットピッチで定義されるサンプリング間隔になる。こうして求められた各位置ごとの相関係数をたとえば2次近似曲線513で補間し、その頂点となる位置514をマーク検出位置とする。

【0011】

以上のようにして検出されたアライメントマークの位置を元に下地チップの形状歪みが測定した後、図7に示すようにチップ形状の設計値60に対する実際のチップの位置シフト61、回転62、拡大縮小63、台形歪64などの歪み成分に分解し、それぞれに応じて補正係数を設定して下層パターンに対する合わせ描画を実施する。

【0012】

図7は半導体デバイスの断面構造を示す。素子分離層(701)からゲート層(702)がトランジスタを形成する層であり、その上層(703〜708)が配線層である。これらの各層はそれぞれ、先に図3で説明したようなプロセスを経て、各層のパターンはリソグラフィ工程で形成される。この際のアライメントマークの断面は711、712、713に示すように各層で異なった構造を持つことになる。また、図8に示すように、たとえば配線層の平坦化のため使用されるCMP(Chemical Mechanical Polishing・化学機械的研磨)プロセスの影響により、アライメントマークを形成するメタル層801が非対称になり、それによりアライメントマーク検出波形も非対称になって下地層との合わせ誤差を生じる場合がある。このようなプロセスのバラツキによって生じる誤差をプロセス起因誤差と呼ぶ。

【0013】

アライメントマークのプロセス起因誤差に対応する技術としては以下のようなものが知られている。たとえば特開2000−275010号ではプロセス起因誤差によるアライメントマーク検出波形の形状歪みを補正して位置検出を行う例が開示されている。また特開2002−15980号では、アライメントマーク検出波形の非対称性と検出誤差の関係をあらかじめデータベース化しておき、補正を行って位置検出精度を向上させる技術が開示されている。

【0014】

【特許文献1】特開2000−275010号公報

【特許文献2】特開2002−15980号公報

【発明の開示】

【発明が解決しようとする課題】

【0015】

ところで、特開2000−275010号で開示された例では、アライメントマークの形状歪みの補正により却って誤差を重畳させてしまう可能性がある。また、特開2002−15980号で開示された例では検出波形の非対称性と検出誤差の関係を示すシグナルデータベースを、実ウエハおよび露光結果から作成するものであるが、製品および工程ごとにデータベースを作成する場合、その作業量が非常に大きなものとなる可能性がある。また、特に電子ビーム描画装置においては、図9に示すようにアライメントマーク検出波形は走査する電子ビームのサイズによっても変化する。電子ビーム描画装置ではビームのサイズは可変であり、アライメントマーク検出時にも検出出力と分解能を最適にするようにアライメント検出のジョブでビームサイズが設定される。図10中で921、922はアライメントマークであり、911、912はアライメントマーク検出時の電子ビームのビームサイズである。911はビームサイズが大きい場合、912はビームサイズが小さい場合の例を示している。また、それぞれのビームサイズに対応したアライメントマーク検出波形が931、932である。図に示したようにビームサイズと、アライメントマーク幅との関係により検出波形の形状は変化する。

【0016】

以上に示したように、電子ビーム描画におけるアライメントマーク検出波形は検出条件により異なるため、これらのそれぞれに対応し、さらにプロセス起因誤差にも対応して精度良くアライメントマークの位置検出を行うことが課題となっている。

【課題を解決するための手段】

【0017】

上記課題を解決するために、本発明における描画方法および装置では、下地パターンと重ね合わせ描画を行うためのアライメントマーク検出精度向上のために、アライメントマーク検出シミュレーションによりデバイス製品・工程ごと、およびマークの検出条件ごと、さらにマークがプロセス誤差を持つ場合についてテンプレート波形を作成し、あるデバイス製品・工程において重ねあわせ描画を行う際に、取得されたアライメント検出波形に対し、上記で作成された複数のテンプレート波形によるマッチング処理をそれぞれ行い、その中から相関係数最大となったテンプレートでの検出結果をアライメントマーク検出位置とすることにより、下地パターンに対する重ね合わせ精度を向上させるものである。

【発明の効果】

【0018】

本発明は描画装置により半導体デバイス製品のパターン形成を行う際に、下地パターンと重ね合わせ描画を行うためのアライメントマーク検出精度向上のために、アライメントマーク検出シミュレーションによりデバイス製品・工程ごと、およびマークの検出条件ごと、さらにマークがプロセス誤差を持つ場合についてテンプレート波形を作成し、あるデバイス製品・工程において重ねあわせ描画を行う際に、取得されたアライメント検出波形に対し、上記で作成された複数のテンプレート波形によるマッチング処理をそれぞれ行い、その中から相関係数最大となったテンプレートでの検出結果をアライメントマーク検出位置とすることにより、描画装置により半導体デバイス製品のパターン形成を行う際に、下地パターンに対する重ね合わせ精度を向上させるものである。

【発明を実施するための最良の形態】

【0019】

本発明に係る、電子ビーム描画方法および装置の実施の形態について、以下図面を用いて説明する。

【実施例1】

【0020】

図1は本発明における第1の実施例である電子ビーム描画方法に関わる実施例を説明する図である。100はアライメントマーク検出波形のシミュレーションを実施するステップであり、ビームサイズ、ショットピッチなどの検出条件、半導体デバイスの製品および描画の対象となる層(工程)に対応したマークの構造(材質、寸法、層構造)、さらにはマーク形状誤差などの計算パラメータ101をもとに、102のステップでシミュレーションを行うものである。この場合のシミュレーション手法にはモンテカルロシミュレーションを用いることが一般的に考えられる。以上の計算はオフラインで実施され、計算結果は先に述べた計算パラメータと関連付けて、描画装置のテンプレート波形データベースに格納される(103)。描画を行う際には、まずジョブファイルを選択・起動し描画を行うデバイス製品、工程を指定する(104)。描画が開始されるとジョブで指定された描画パターンデータを描画パターンデータベース106から選択する(105)。次にアライメントに使用するテンプレート波形をテンプレート波形データベースから選択する(107)。ジョブファイル中にはデバイス製品/工程と、アライメントマーク検出条件(ビームサイズ・ショットピッチ)が指定されており、それらとの関連付けによりデータベースからテンプレート波形が選択される。また、この際にはマークのプロセス誤差を変化させたシミュレーションから得られた複数のテンプレート波形を選択する。

【0021】

アライメントマーク検出時には、アライメントマークに電子ビームを照射し(108)、マーク検出波形を取得(109)した後、テンプレートマッチングを行うため波形のオフセット・ゲイン補正を行う(110)。オフセット・ゲイン補正については図11について説明する。

【0022】

反射電子検出器からの出力は、デバイス製品/工程によって異なるアライメントマークの種類の違いにより信号レベルは非常に広いレンジで異なるものとなる。これはアライメントマークとその周囲を構成する材質により、マークからの反射もバックグラウンドからの反射も様々に異なるからである。これらに対して精度よくテンプレートマッチングを行うためにオフセット・ゲイン補正を行う。図10中で1001は反射電子検出器から得られたアライメントマーク検出信号である。これをオフセット補正によりバックグラウンドレベルをゼロにする(1002)。さらにゲイン補正により波形のピークを所定の信号レベルにまで増幅する(1003)。このようにして、アライメント検出波形を規格化することにより精度よくテンプレートマッチングを行うことが可能となる。

【0023】

そのように規格化された検出波形を107で選択された複数のテンプレートでそれぞれ波形処理を行う(111)。それによって得られた複数の処理結果のうち、相関係数(図6−613のピーク値)が最も高かったテンプレートでの結果をマークの検出位置として採用する。

【0024】

波形処理をこのように構成することにより、ステップ108〜109で検出する実際のアライメントマークが持つプロセス起因誤差に対応して、最適なテンプレートで波形処理した結果を採用することでき、アライメントマーク位置検出の精度を向上させることが可能となる。

【0025】

以上の処理によりチップの4隅に配置されたそれぞれのアライメントマークの位置検出を行って下地チップ歪みを求め、図7にて説明した各歪み成分に応じてアライメント補正値を算出して(113)、パターン描画を実施する(114)。

【実施例2】

【0026】

図11本発明における第2実施例である電子ビーム描画装置に関わる実施例を説明する図である。1101は制御計算機で全体システムの制御を行う。オフラインで計算されたテンプレート波形は制御計算機1101を経て波形テンプレートデータベースに保持される。各テンプレート波形はそれに対応するデバイス製品および工程名称と関連付けて保持される。

【0027】

基板載置手段1114には、描画対象である基板1120が載置され、基板上に形成されたチップ1121に形成されたアライメントマーク1122にビームを照射する手段1111(電子銃)、1112(偏向器)とにより、電子ビームでアライメントマークを走査し、反射電子検出器1113でアライメントマークからの反射電子を検出してアライメントマーク検出波形を得る。

【0028】

描画時には制御計算機1101からジョブファイルを選択・起動し描画を行うデバイス製品、工程を指定する。ジョブファイル中にはデバイス製品/工程と、アライメントマーク検出条件(ビームサイズ・ショットピッチ)が指定されており、それらとの関連付けにより波形テンプレートデータベース1102から、テンプレート選択手段1104により、そのジョブにおける描画に使用するテンプレート波形を選択する。この際にはマークのプロセス誤差を変化させたシミュレーションから得られた複数のテンプレート波形を選択する。

【0029】

アライメントマーク検出波形は波形処理手段1105により、先に選択されたそれぞれのテンプレートによりマッチング処理を行い、得られた複数の波形処理結果からもっともマッチング相関の高かったテンプレートでの検出結果を選択する。それらの処理結果は、たとえば前記波形処理に用いたテンプレートと、実際のアライメントマーク検出波形とを重ね合わせて制御計算機の表示部11012に表示される。選択された結果を用いて補正演算部1106でアライメント補正係数を算出してそのデータをビーム制御部に送り、重ね合わせ描画を行う。

【産業上の利用可能性】

【0030】

以上、本発明者によってなされた以上の説明は、発明の背景となった利用分野である半導体デバイスの製造に関して行ったが、それに限定されるものではなく、液晶ディスプレイ基板や磁気ヘッドの製造など、描画装置により、基板上の下地パターンに重ね合わせて微細パターンを形成する製品の製造に適用することが可能である。

【図面の簡単な説明】

【0031】

【図1】本発明の第1の実施例に関して説明する図。

【図2】電子ビーム描画装置の校正について説明する図。

【図3】合わせ描画のフローについて説明する図。

【図4】アライメントマーク検出時のビーム走査と検出波形を説明する図。

【図5】テンプレートマッチング法で位置検出を行う際の波形処理を説明する図。

【図6】下地チップ歪みの成分を説明する図。

【図7】半導体デバイスとアライメントマークの断面構造を説明する図。

【図8】アライメントマークのプロセス起因誤差の例を説明する図。

【図9】ビームサイズによるアライメントマーク検出波形の違いを説明する図。

【図10】アライメント波形のゲイン・オフセット補正について説明する図。

【図11】本発明の第2の実施例に関して説明する図。

【符号の説明】

【0032】

201…制御計算機、203…描画データ処理部、204…補正演算部、222…ステージ測長系、205…ビ−ム制御部、210…電子光学系、211…電子銃、212…ビーム偏向器230…真空チャンバ内、251…ウエハ、221…ステージ、223…ステージ制御系、253…アライメントマーク、232…信号処理部。

【特許請求の範囲】

【請求項1】

下層に回路パターンが形成された基板に対し、アライメントマークにビームを照射してマーク検出波形を取得し、波形処理によりアライメントマークの位置検出を行って重ね合わせ描画を行う電子ビーム描画方法において、波形処理に使用するテンプレートを複数用意し、それぞれのテンプレートで得られた処理結果のうち、最もマッチング相関の高かったテンプレートでの検出結果を用いてアライメント補正を行い、重ね合わせ描画を行うことを特徴とする電子ビーム描画方法。

【請求項2】

前記テンプレートは電子線シミュレーションにより作成されたことを特徴とする、請求項1記載の電子ビーム描画方法。

【請求項3】

前記複数のテンプレートはアライメントマークのプロセス誤差を反映して作成したことを特徴とする、請求項1記載の電子ビーム描画方法。

【請求項4】

基板を載置する手段と、基板上に形成されたアライメントマークにビームを照射する手段と、アライメントマークからの反射電子を検出してアライメントマーク検出波形を生成する手段と、波形処理によりアライメントマークの位置検出を行う手段と、位置検出の結果からアライメント補正を行って描画を行う手段を有する電子ビーム描画装置において、

波形処理のための複数のテンプレートを保持する記憶手段と、該記憶手段から所定のテンプレートを選択する手段と、選択されたそれぞれのテンプレートにより波形処理を行う手段と、得られた複数の波形処理結果からもっともマッチング相関の高かったテンプレートでの検出結果を用いてアライメント補正係数を算出する手段とを備えることを特徴とする電子ビーム描画装置。

【請求項5】

前記テンプレートを保持する記憶手段には、各テンプレート波形がそれに対応するデバイス製品および工程名称と関連付けて保持されていることを特徴とする請求項4記載の電子ビーム描画装置。

【請求項6】

前記波形処理に用いたテンプレートと、実際のアライメントマーク検出波形とを重ね合わせて表示する手段を備えたことを特徴とする請求項4記載の電子ビーム描画装置。

【請求項1】

下層に回路パターンが形成された基板に対し、アライメントマークにビームを照射してマーク検出波形を取得し、波形処理によりアライメントマークの位置検出を行って重ね合わせ描画を行う電子ビーム描画方法において、波形処理に使用するテンプレートを複数用意し、それぞれのテンプレートで得られた処理結果のうち、最もマッチング相関の高かったテンプレートでの検出結果を用いてアライメント補正を行い、重ね合わせ描画を行うことを特徴とする電子ビーム描画方法。

【請求項2】

前記テンプレートは電子線シミュレーションにより作成されたことを特徴とする、請求項1記載の電子ビーム描画方法。

【請求項3】

前記複数のテンプレートはアライメントマークのプロセス誤差を反映して作成したことを特徴とする、請求項1記載の電子ビーム描画方法。

【請求項4】

基板を載置する手段と、基板上に形成されたアライメントマークにビームを照射する手段と、アライメントマークからの反射電子を検出してアライメントマーク検出波形を生成する手段と、波形処理によりアライメントマークの位置検出を行う手段と、位置検出の結果からアライメント補正を行って描画を行う手段を有する電子ビーム描画装置において、

波形処理のための複数のテンプレートを保持する記憶手段と、該記憶手段から所定のテンプレートを選択する手段と、選択されたそれぞれのテンプレートにより波形処理を行う手段と、得られた複数の波形処理結果からもっともマッチング相関の高かったテンプレートでの検出結果を用いてアライメント補正係数を算出する手段とを備えることを特徴とする電子ビーム描画装置。

【請求項5】

前記テンプレートを保持する記憶手段には、各テンプレート波形がそれに対応するデバイス製品および工程名称と関連付けて保持されていることを特徴とする請求項4記載の電子ビーム描画装置。

【請求項6】

前記波形処理に用いたテンプレートと、実際のアライメントマーク検出波形とを重ね合わせて表示する手段を備えたことを特徴とする請求項4記載の電子ビーム描画装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2006−165140(P2006−165140A)

【公開日】平成18年6月22日(2006.6.22)

【国際特許分類】

【出願番号】特願2004−352155(P2004−352155)

【出願日】平成16年12月6日(2004.12.6)

【出願人】(501387839)株式会社日立ハイテクノロジーズ (4,325)

【Fターム(参考)】

【公開日】平成18年6月22日(2006.6.22)

【国際特許分類】

【出願日】平成16年12月6日(2004.12.6)

【出願人】(501387839)株式会社日立ハイテクノロジーズ (4,325)

【Fターム(参考)】

[ Back to top ]