電子・電気回路の製造方法

【課題】 より簡便な印刷装置を用いて、大型な電子・電気回路をアライメント精度良く製造可能な電子・電気回路の製造方法を提供する。

【解決手段】 印刷法を用いて複数の構成要素を有する素子から成る電子・電気回路を製造するための製造方法である。特定の波長の光又は電磁波を透過する基板100の裏面に、光又は電磁波の透過率の低いアライメントマーク11〜19(マークパターン)を配置し、基板100の上面から光又は電磁波を照射し、アライメントマーク11〜19の位置を検出することによりアライメントを行い、素子の各構成要素を印刷法を用いて形成する。

【解決手段】 印刷法を用いて複数の構成要素を有する素子から成る電子・電気回路を製造するための製造方法である。特定の波長の光又は電磁波を透過する基板100の裏面に、光又は電磁波の透過率の低いアライメントマーク11〜19(マークパターン)を配置し、基板100の上面から光又は電磁波を照射し、アライメントマーク11〜19の位置を検出することによりアライメントを行い、素子の各構成要素を印刷法を用いて形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、印刷法を用いた電子・電気回路の製造方法に関する。

【背景技術】

【0002】

薄膜トランジスタ(TFT)は液晶ディスプレイやELディスプレイなどの表示装置用の画素スイッチング素子として広く用いられている。また、近年では同一基板上で画素アレイのドライバ回路もTFTによって形成される例が増えている。

【0003】

従来、こうしたTFTはアモルファスや多結晶のシリコンを用いてガラス基板上に作成されていた。しかし、こうしたシリコンを用いたTFTの作成に用いられるCVD装置は非常に高額であり、TFTを用いた表示装置などの大面積化は製造コストの大幅な増加を伴うという問題点があった。

【0004】

また、アモルファスや多結晶のシリコンを成膜するプロセスは極めて高い温度で行われるため、基板として使用可能な材料が限られており、軽量な樹脂基板等が使用できないといった制限があった。

【0005】

さらに、こうした従来型のTFTの作製工程では、真空成膜、フォトリソグラフィー、エッチングなどの技術が多用されている。このような技術を用いたデバイス製造では、投入した材料の一部分のみがデバイスを形成するために使用され、大部分の材料は廃棄される。また、フォトレジスト、現像液、剥離液などデバイスの構成材料ではない間接的な資材が大量に使用されて廃棄される。

【0006】

このように従来の技術に基づくデバイス製造では、製造時の環境負荷が大きい。こうした課題に対処する方法として、印刷手法を応用したデバイス製造の試みが始まっている。印刷手法では、デバイスを形成するために必要な部分のみに材料が投入され、必要最小限の材料使用量と最小限の廃棄物量で、環境負荷の小さなデバイス製造が可能になると期待されている。これに関連する技術として、例えば、特開平9−226224号公報(特許文献1)がある。

【0007】

印刷法で作製されるTFTの半導体チャネルの材料としては、従来のアモルファスや多結晶のシリコンに代えて、有機半導体、カーボンナノチューブ(CNT)あるいは酸化物ナノワイヤなどが候補として提案されている。

【0008】

これらの候補とされる半導体材料のうち、CNTは、以下のような特徴を有している。CNTは炭素のみからなる筒状炭素分子であり、炭素原子の六員環で構成されるグラフェンシートを巻いた構造をとっている。1枚のグラフェンシートを丸めて筒状になったCNTは、単層ナノチューブ(SWNT)とよばれ、直径の異なる円筒状のカーボンナノチューブが複数層積層されたCNTは、多層ナノチューブ(MWNT)と呼ばれる。

【0009】

SWNTの直径は約1nm、MWNTは数十nm程度である。CNTでは、直径の違い以外に、グラフェンシートを丸める向きの違い、即ち、円周方向に対する炭素原子の六員環の配向の違いによって、らせん度(カイラリティ)の異なる種々のカーボンナノチューブ、例えば、らせん型カーボンナノチューブ、ジグザグ型カーボンナノチューブ、アームチェア型カーボンナノチューブ等がある。SWNTでは、らせん度(カイラリティ)の違いにより、金属性と半導体性の両方の性質が現れる。

【0010】

SWNTは、例えば化学的気相成長法(CVD)によって合成することができる。合成されたCNTは、機械的にも、化学的にも安定である。したがって、成長したCNTを取り出してきて、適当な溶液中に分散させ、CNTインクを作製することができる。このCNTインクを、基板上に塗布・印刷することによって、CNTのランダムネットワークを堆積し、チャネル層を形成することが可能である。

【0011】

E. S. Snow et al., Applied Physics Letters, vol. 82, p.2145, (2003)(非特許文献1)では、このようにして形成されたCNTのランダムネットワークでは、多くの接触が形成されてカーボンナノチューブ間の接続が発生し、薄膜トランジスタのチャネル層に利用することができると報告している。

【0012】

非特許文献1によれば、チャネル層における単層カーボンナノチューブの密度が1本/μm2程度の時には、on/off比が5桁、移動度が7cm2/Vsが得られ、良好な薄膜トランジスタ(TFT)が実現できたとしている。

【0013】

また、最近では結晶性に優れ、半導体性を有する酸化亜鉛のナノワイヤを複数本用いてチャネルを構成したTFTについて、Duk-Il Suh, Seung-Yong Lee, Jung-Hwan Hyung, Tae-Hong Kim, Sang-Kwon Lee, J. Phys. Chem. C, vol. 112, p. 1276-1281, (2008) (非特許文献2)などで報告がなされている。

【0014】

CNTのランダムネットワークは、前述したように、CNTの分散液を塗布あるいは印刷することで形成できる。このプロセスは大面積化が安価に実現可能であると共に、そのプロセス温度が低く、基板として用いる材料を選択する際の制限が少ない。そのため、従来から用いられている、ガラス基板上に形成されたシリコン系のTFTに比べて、大幅に製造コストを抑えることが可能である。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開平9−226224号公報

【非特許文献】

【0016】

【非特許文献1】E. S. Snow et al., Applied Physics Letters, vol. 82, p.2145, (2003)

【非特許文献2】Duk-Il Suh, Seung-Yong Lee, Jung-Hwan Hyung, Tae-Hong Kim, Sang-Kwon Lee, J. Phys. Chem. C, vol. 112, p. 1276-1281, (2008)

【発明の概要】

【発明が解決しようとする課題】

【0017】

大面積の半導体装置を安価に製造するためには、チャネルを形成する半導体材料のみならず、配線、電極、絶縁体など半導体素子を構成する全ての要素を印刷法で形成することが望ましい。印刷法を用い、必要最小限の材料で必要な箇所のみにパターンを形成することで、従来の半導体製造に比較して、製造時の投入資材とエネルギーを大幅に低減することができる。また、製造時に生じる廃棄物も大幅に低減することができ、環境負荷が小さくなる。しかしながら、半導体素子を構成する全ての要素を印刷法で形成するには課題がある。

【0018】

製造上の最も大きな課題として、半導体素子の各構成要素を形成する際のアライメントが挙げられる。1つのTFTを作成する場合でも、ゲート電極、ゲート絶縁膜、ソース・ドレイン電極、チャネル層のそれぞれの要素を正確にアライメントし、形成する必要がある。精度の高いアライメントが必要な場合には、通常、アライメントずれは回転とオフセットの主に2つの成分に分解して補正される。

【0019】

このうち、回転によるずれは、製造する製品の大きさに依存する。同じ精度の回転ずれが生じているとして、サイズが10cmの製品に対し、1mの製品では10倍のパターンずれが生じる。フォトリソグラフィーでは、こうした回転ずれは、基板ステージあるいはマスクステージの回転機構により補正される。しかし、より大型な基板の使用が前提である印刷装置で、このような回転機構を設けることは装置を複雑化し、印刷装置のコストを増大させるため得策ではない。

【0020】

そこで、本発明は、上記従来技術の問題点に鑑みて成されたものであり、その目的は、より簡便な印刷装置を用いて、大型な電子・電気回路をアライメント精度良く製造可能な電子・電気回路の製造方法を提供することにある。

【課題を解決するための手段】

【0021】

本発明の一態様では、印刷法を用いて複数の構成要素を有する素子から成る電子・電気回路を製造するための製造方法であって、

特定の波長の光又は電磁波を透過する基板の裏面に、上記光又は電磁波の透過率の低いマークパターンを配置し、

上記基板の上面から上記光又は電磁波を照射し、

上記マークパターンの位置を検出することによりアライメントを行い、

上記素子の各構成要素を、上記印刷法を用いて形成することを特徴とする。

【0022】

また、本発明の他の態様では、印刷法を用いて複数の構成要素を有する素子から成る電子・電気回路を製造するための製造方法であって、

特定の波長の光又は電磁波を透過する基板の裏面に、上記光又は電磁波の透過率の低いマークパターンが形成された支持基板を配置し、

上記基板の上面から上記光又は電磁波を照射し、

上記マークパターンの位置を検出することによりアライメントを行い、

上記電子・電気素子の各構成要素を、上記印刷法を用いて形成することを特徴とする。

【発明の効果】

【0023】

本発明によれば、より簡便な印刷装置を用いて、大型な電子・電気回路をアライメント精度良く製造することができる。この結果、低コストで、歩留まりが高く、大型な電子・電気回路を提供することができる。

【図面の簡単な説明】

【0024】

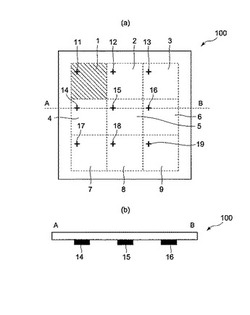

【図1】本発明の第1の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図であり、(a)は平面図、(b)は図1(a)中のA−Bで示される断面図である。

【図2】本発明の第1の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図である。

【図3】本発明の第1の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図である。

【図4】本発明の第1の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図である。

【図5】本発明の第1の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図である。

【図6】本発明の第1の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図である。

【図7】本発明の第1の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図である。

【図8】本発明の第2の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図である。

【発明を実施するための形態】

【0025】

最初に、本発明の理解を容易にするために、本発明の原理について説明する。

【0026】

例えば、TFTに代表される、複数の構成要素からなる電子素子を製造する際に、各構成要素を相対的に正確な位置に配置することが重要である。例えば、前記のTFTの場合には、ゲート電極、ゲート絶縁膜、ソース・ドレイン電極、チャネル層のそれぞれの要素をアライメントし、正確に配置しなければ性能が低下するのみならず、機能する素子の歩留まりが低下する。

【0027】

アライメントずれの成分は、主にオフセットによるものと、回転によるものに分解することができる。このうち、オフセットの成分は基板あるいはマスクパターンの前後・左右の微小な調整により除去することができる。回転によるずれは、ある基準点をとり、その基準点からの距離Lと、基板とマスクパターンの相対的な角度差θを用いると、前後方向には、

Δy=L×sin(θ) (1)

左右方向には、

Δx=L×cos(θ) (2)

それぞれ、(1)式、(2)式で規定される変位が生じる。この変位量は、製品基板上で、前述のある基準点からの距離Lにより異なっていることに注意する必要がる。製品の基板サイズが小さく、製造上許容されるずれ量より、これらの変位量が充分小さいときには、前述のオフセットの一部として、オフセットによる補正の中に押し込めることも可能である。

【0028】

しかしながら、基板サイズが大きくなり、(1)、(2)式中のLが大きくなると、これらの変位量は無視できない。通常、これらの回転による変位量を補正するためには、基板あるいはマスクパターンの少なくとも一方を回転させる機構を設けて、調整する必要がある。一般に、回転機構は、基板およびマスクパンが大きくなるにつれて、装置が大型化し複雑化する。

【0029】

大型な基板の中で、形成する電子・電気回路を一定の領域に区切って分割し、一度に印刷する範囲を小さくすることにより、前記の(1)、(2)式中のLを実効的に小さくすることは可能である。しかしこの方法を用いる場合には、領域分割する分割数に応じてアライメントマークの数を増やす必要がある。

【0030】

印刷では、液体材料インクを使用するため、パターン形成の精度は、下地の微小な段差あるいは下地と材料インクの濡れ性など、下地の表面状態に強く依存する。一般に、アライメントマークは、基板上に基板とは異なる材料を用いて形成する。このアライメントマークと印刷形成する回路要素と接する、あるいはオーバーラップするなどの干渉が生じると、印刷不良を引き起こす。

【0031】

したがって、アライメントマークは、このような、素子・回路パターンと干渉することがないように、細心の注意を払って、形状、配置などを決定する必要がある。領域分割して、複数のアライメントマークを設ける場合には、アライメントマークの占有面積が増大するので、マークの形状、配置が非常に困難になってくる。

【0032】

本発明の印刷法による電子・電気回路の製造では、こうしたアライメントマークを基板の裏面に形成する。そのため、分割印刷のために、多数のアライメントマークを配置する場合においても、素子・回路パターンとアライメントマークの干渉による印刷不良のリスクを低減させることができる。

【0033】

この製造方法は、多数のアライメントマークを使用する分割印刷において、特に効果が大きい。また、分割印刷を行うことで、回転ずれによるアライメントずれの許容量が大きくなり、製造歩留まりが向上する。

【0034】

また、回転ずれを補正する場合にも、1回の分割印刷による回転補正を行うことで、対応できる。特に、インクジェット法、インクディスペンス法などに代表される印刷データが数値で与えられる無版印刷法を用いる場合には、ずれ補正に伴う座標変換の演算の規模を小さくすることができる。この結果、製造時のスループットが向上し、結果として製造コストを低減することができる。

【0035】

このように、本発明によれば、高性能でかつ均一性、信頼性に優れた半導体素子を低コストで供給することができる。また、本発明の製造方法は、大面積である電子・電気回路の印刷製造に適しており、大規模な表示装置、センサアレイなどを低コストで製造することが可能となる。

【0036】

次に、本発明の実施の形態を図面を参照して説明する。

【0037】

(第1の実施の形態)

本発明の第1の実施の形態に係る電子・電気回路の印刷製造法では、図1に示すように、裏面に複数のアライメントマーク11〜19を設けた基板100を使用する。ここで、図1(a)は平面図、図1(b)は、図1(a)中のA−Bで示される断面図を示している。

【0038】

第1の実施の形態では、電子・電気回路の基板100は9つの領域1〜9に分割されている。このような構成の下、それぞれの領域1〜9に、アライメントマーク11〜19が配置されている。

【0039】

そして、第1の実施の形態では、特定の波長の光又は電磁波を透過する基板100の裏面に、光又は電磁波の透過率の低いアライメントマーク11〜19(マークパターン)を配置し、基板100の上面から光又は電磁波を照射する。そして、アライメントマーク11〜19の位置を検出することによりアライメントを行い、素子(例えば、TFT)の各構成要素を印刷法を用いて形成する。このようにして、印刷法を用いて複数の構成要素を有する素子から成る電子・電気回路(例えば、TFTアレイ)を製造する。

【0040】

次に、第1の実施の形態に係る電子・電気回路の製造方法について詳細に説明する。

【0041】

まず、図2に示すように、各領域1〜9において、それぞれ領域1〜9内に設けたアライメントマーク11〜19を用いてゲート電極21〜24を印刷する。図2は、第1から第4の領域1〜4までゲート電極21〜24を印刷形成した例を示している。

【0042】

例えば、第1の領域1では、第1のアライメントマーク11を用いて位置決めし、第1のゲート電極21を印刷形成する。また、第2の領域2では、第2のアライメントマーク12を用いて位置決めし、第2のゲート電極22を印刷形成する。そして、順次、第4のゲート電極24まで形成した。同様に、第9のゲート電極29(図示せず)を印刷形成した後に、ゲート絶縁膜を印刷形成する。

【0043】

図3では、第1から第4の領域1〜4までゲート絶縁膜31〜34を印刷形成した例を示している。

【0044】

例えば、第1の領域1では、第1のアライメントマーク11を用いてアライメントし、第1のゲート絶縁膜31を印刷形成する。第2の領域2では、第2のアライメントマーク12を用いてアライメントし、第2のゲート絶縁膜32を印刷形成する。そして、順次、第4のゲート絶縁膜24まで形成した。

【0045】

ここで、例えば、第1のゲート絶縁膜31と第1のアライメントマーク11は、平面図的には接して干渉しているように見えるが、実際には、アライメントマーク11は基板100の裏面に設けられており(図1(b)参照)、パターン干渉による印刷不良は生じない。同様に、第9のゲート絶縁膜39(図示せず)を印刷形成した後に、チャネル層を形成する。

【0046】

図4では、第1から第4の領域1〜4までチャネル層42〜44を印刷形成した例を示している。

【0047】

例えば、第1の領域1では、第1のアライメントマーク11を用いてアライメントし、第1のチャネル層41を印刷形成する。第2の領域2では、第2のアライメントマーク12を用いてアライメントし、第2のチャネル層42を印刷形成する。そして、順次、第4のチャネル層44まで形成した。同様に、第9のチャネル層49(図示せず)を印刷形成した後に、ソース・ドレイン電極を形成する。

【0048】

図5では、第1から第4の領域1〜4までに、ソース・ドレイン電極51〜54を印刷形成した例を示している。

【0049】

例えば、第1の領域1では、第1のアライメントマーク11を用いてアライメントし、第1のソース・ドレイン電極51を印刷形成する。第2の領域2では、第2のアライメントマーク12を用いてアライメントし、第2のソース・ドレイン電極52を印刷形成する。そして、順次、第4のソース・ドレイン電極54まで形成した。同様に、第9のソース・ドレイン電極59(図示せず)を印刷形成した後に、各領域1〜9の素子を接続するためにグローバル配線を形成する。

【0050】

図6のグローバル配線61は、領域1と領域2のソース電極とを接続している。これは、領域1と領域2のアライメントマーク11とアライメントマーク12を用いて位置決めされている。同様にグローバル配線62は領域2と領域3のアライメントマーク12とアライメントマーク13を用いて位置決めされ、領域2と領域3のソース電極とを接続している。

【0051】

グローバル配線65は、領域1と領域4のゲート電極を接続している。これは、領域1と領域4のアライメントマーク11とアライメントマーク14を用いて位置決めされている。同様にグローバル配線66は領域2と領域5のアライメントマーク12とアライメントマーク15を用いて位置決めされ、領域2と領域5のゲート電極とを接続している。同様にして、図7に示すように、3x3のTFTアレイを製造することができる。

【0052】

尚、これらのグローバル配線の印刷形成の手段としては、インクジェット法、インクディスペンス法などに代表される印刷データが数値で与えられる無版印刷法が適していることは自明である。

【0053】

(第2の実施の形態)

本発明の第2の実施の形態に係る電子・電気回路の印刷製造法では、図8に示すように、分割された領域1〜9に対して、複数のアライメントマーク81,82を配置する。このとき、複数のアライメントマーク81、82から、分割された領域1〜9の回転ずれを見積もることができる。

【0054】

印刷形成する手段が、インクジェット法、インクディスペンス法などに代表される印刷データが数値で与えられる無版印刷法を用いる場合に、ここで見積もられた回転ずれの量を補正した座標を演算しなおすことで、アライメント精度を向上させることができる。このとき、演算するべき座標のデータは、分割された領域1〜9内に限られるため、計算量を少なくし、印刷のスループットを向上させることができる。

【0055】

また、全ての分割された領域1〜9の回転ずれをあらかじめ計測しおき、平均値を算出し、全ての分割された領域1〜9で同一の補正データを用いれば、さらに、印刷のスループットが向上できる。

【0056】

(第3の実施の形態)

本発明の第3の実施の形態に係る電子・電気回路の印刷製造法では、分割された領域1〜9の印刷形成手法として、小型のスタンプを用いる。小型のスタンプを用いる場合には、スタンプに回転機構(図示せず)を設けておき、スタンプの回転機構により回転ずれを補正する方法も有効である。

【0057】

このときに、各領域1〜9に形成された複数のアライメントマーク81、82(図8参照)により計測された回転ずれを、各領域1〜9毎に補正しても、あるいは、全領域1〜9の平均値を算出して全ての領域1〜9を回転ずれの平均値で補正して印刷しても、どちらの場合にも同様にアライメント精度の向上が期待できる。

【0058】

(第4の実施の形態)

上記第1の実施の形態では、基板100の裏面に、光又は電磁波の透過率の低いアライメントマーク11〜19(マークパターン)を配置したが、第4の実施の形態では、アライメントマーク11〜19が設けられた支持基板(図示せず)を使用する。

【0059】

具体的には、第4の実施の形態では、印刷法を用いて複数の構成要素を有する素子から成る電子・電気回路を製造する。この際、特定の波長の光又は電磁波を透過する基板100の裏面に、光又は電磁波の透過率の低いアライメントマーク11〜19(マークパターン)が形成された支持基板(図示せず)を配置する。そして、基板100の上面から光又は電磁波を照射し、アライメントマーク11〜19の位置を検出することによりアライメントを行う。このようにして、電子・電気素子の各構成要素を、印刷法を用いて形成可能である。

【0060】

(第5の実施の形態)

本発明の第5の実施の形態に係る電子・電気回路の印刷製造法では、製造される電気・電子回路が表示装置のように透過性が重要な場合には、製造時に使用したアライメントマーク11〜19を除去する。

【0061】

上記本発明の実施の形態によれば、より簡便な印刷装置を用いて、大型な電子・電気回路をアライメント精度良く製造することができる。この結果、低コストで、歩留まりが高く、大型な電子・電気回路を提供することができる。

【0062】

また、電子・電気回路を形成した後に、アライメントに使用したマークパターンを選択的に除去することが可能になり、ディスプレイなどの光透過特性が重要となる応用に対して効果がある。

【0063】

このように、本発明の実施の形態では、電子・電気回路の製造では、アライメントマークを基板の裏面に形成する。そのため、分割印刷のために、多数のアライメントマークを配置する場合においても、素子・回路パターンとアライメントマークの干渉による印刷不良のリスクを低減させることができる。

【0064】

この製造方法は、多数のアライメントマークを使用する分割印刷において、特に効果が大きい。また、分割印刷を行うことで、回転ずれによるアライメントずれの許容量が大きくなり、製造歩留まりが向上する。

【0065】

また、回転ずれを補正する場合にも、1回の分割印刷による回転補正を行うことで対応できる。特に、インクジェット法、インクディスペンス法などに代表される印刷データが数値で与えられる無版印刷法を用いる場合には、ずれ補正に伴う座標変換の演算の規模を小さくすることができる。この結果、製造時のスループットが向上し、結果として製造コストを低減することができる。

【0066】

このようにして、本発明の実施の形態によれば、高性能でかつ均一性、信頼性に優れた半導体素子を低コストで供給することができる。また、本発明の実施の形態に係る製造方法は、大面積である電子・電気回路の印刷製造に適しており、大規模な表示装置、センサアレイなどを低コストで製造することが可能となる。

【0067】

以上、本発明の実施例について説明したが、上述の例は、本発明の技術的思想に基づき種々に変形が可能である。

【符号の説明】

【0068】

1 分割領域

2 分割領域

3 分割領域

4 分割領域

5 分割領域

6 分割領域

7 分割領域

8 分割領域

9 分割領域

11 アライメントマーク

12 アライメントマーク

13 アライメントマーク

14 アライメントマーク

15 アライメントマーク

16 アライメントマーク

17 アライメントマーク

18 アライメントマーク

19 アライメントマーク

21 ゲート電極

22 ゲート電極

23 ゲート電極

24 ゲート電極

31 ゲート絶縁膜

32 ゲート絶縁膜

33 ゲート絶縁膜

34 ゲート絶縁膜

41 チャネル層

42 チャネル層

43 チャネル層

44 チャネル層

51 ソース・ドレイン電極

52 ソース・ドレイン電極

53 ソース・ドレイン電極

54 ソース・ドレイン電極

61 グローバル配線

62 グローバル配線

63 グローバル配線

64 グローバル配線

65 グローバル配線

66 グローバル配線

81 アライメントマーク

82 アライメントマーク

100 基板

【技術分野】

【0001】

本発明は、印刷法を用いた電子・電気回路の製造方法に関する。

【背景技術】

【0002】

薄膜トランジスタ(TFT)は液晶ディスプレイやELディスプレイなどの表示装置用の画素スイッチング素子として広く用いられている。また、近年では同一基板上で画素アレイのドライバ回路もTFTによって形成される例が増えている。

【0003】

従来、こうしたTFTはアモルファスや多結晶のシリコンを用いてガラス基板上に作成されていた。しかし、こうしたシリコンを用いたTFTの作成に用いられるCVD装置は非常に高額であり、TFTを用いた表示装置などの大面積化は製造コストの大幅な増加を伴うという問題点があった。

【0004】

また、アモルファスや多結晶のシリコンを成膜するプロセスは極めて高い温度で行われるため、基板として使用可能な材料が限られており、軽量な樹脂基板等が使用できないといった制限があった。

【0005】

さらに、こうした従来型のTFTの作製工程では、真空成膜、フォトリソグラフィー、エッチングなどの技術が多用されている。このような技術を用いたデバイス製造では、投入した材料の一部分のみがデバイスを形成するために使用され、大部分の材料は廃棄される。また、フォトレジスト、現像液、剥離液などデバイスの構成材料ではない間接的な資材が大量に使用されて廃棄される。

【0006】

このように従来の技術に基づくデバイス製造では、製造時の環境負荷が大きい。こうした課題に対処する方法として、印刷手法を応用したデバイス製造の試みが始まっている。印刷手法では、デバイスを形成するために必要な部分のみに材料が投入され、必要最小限の材料使用量と最小限の廃棄物量で、環境負荷の小さなデバイス製造が可能になると期待されている。これに関連する技術として、例えば、特開平9−226224号公報(特許文献1)がある。

【0007】

印刷法で作製されるTFTの半導体チャネルの材料としては、従来のアモルファスや多結晶のシリコンに代えて、有機半導体、カーボンナノチューブ(CNT)あるいは酸化物ナノワイヤなどが候補として提案されている。

【0008】

これらの候補とされる半導体材料のうち、CNTは、以下のような特徴を有している。CNTは炭素のみからなる筒状炭素分子であり、炭素原子の六員環で構成されるグラフェンシートを巻いた構造をとっている。1枚のグラフェンシートを丸めて筒状になったCNTは、単層ナノチューブ(SWNT)とよばれ、直径の異なる円筒状のカーボンナノチューブが複数層積層されたCNTは、多層ナノチューブ(MWNT)と呼ばれる。

【0009】

SWNTの直径は約1nm、MWNTは数十nm程度である。CNTでは、直径の違い以外に、グラフェンシートを丸める向きの違い、即ち、円周方向に対する炭素原子の六員環の配向の違いによって、らせん度(カイラリティ)の異なる種々のカーボンナノチューブ、例えば、らせん型カーボンナノチューブ、ジグザグ型カーボンナノチューブ、アームチェア型カーボンナノチューブ等がある。SWNTでは、らせん度(カイラリティ)の違いにより、金属性と半導体性の両方の性質が現れる。

【0010】

SWNTは、例えば化学的気相成長法(CVD)によって合成することができる。合成されたCNTは、機械的にも、化学的にも安定である。したがって、成長したCNTを取り出してきて、適当な溶液中に分散させ、CNTインクを作製することができる。このCNTインクを、基板上に塗布・印刷することによって、CNTのランダムネットワークを堆積し、チャネル層を形成することが可能である。

【0011】

E. S. Snow et al., Applied Physics Letters, vol. 82, p.2145, (2003)(非特許文献1)では、このようにして形成されたCNTのランダムネットワークでは、多くの接触が形成されてカーボンナノチューブ間の接続が発生し、薄膜トランジスタのチャネル層に利用することができると報告している。

【0012】

非特許文献1によれば、チャネル層における単層カーボンナノチューブの密度が1本/μm2程度の時には、on/off比が5桁、移動度が7cm2/Vsが得られ、良好な薄膜トランジスタ(TFT)が実現できたとしている。

【0013】

また、最近では結晶性に優れ、半導体性を有する酸化亜鉛のナノワイヤを複数本用いてチャネルを構成したTFTについて、Duk-Il Suh, Seung-Yong Lee, Jung-Hwan Hyung, Tae-Hong Kim, Sang-Kwon Lee, J. Phys. Chem. C, vol. 112, p. 1276-1281, (2008) (非特許文献2)などで報告がなされている。

【0014】

CNTのランダムネットワークは、前述したように、CNTの分散液を塗布あるいは印刷することで形成できる。このプロセスは大面積化が安価に実現可能であると共に、そのプロセス温度が低く、基板として用いる材料を選択する際の制限が少ない。そのため、従来から用いられている、ガラス基板上に形成されたシリコン系のTFTに比べて、大幅に製造コストを抑えることが可能である。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開平9−226224号公報

【非特許文献】

【0016】

【非特許文献1】E. S. Snow et al., Applied Physics Letters, vol. 82, p.2145, (2003)

【非特許文献2】Duk-Il Suh, Seung-Yong Lee, Jung-Hwan Hyung, Tae-Hong Kim, Sang-Kwon Lee, J. Phys. Chem. C, vol. 112, p. 1276-1281, (2008)

【発明の概要】

【発明が解決しようとする課題】

【0017】

大面積の半導体装置を安価に製造するためには、チャネルを形成する半導体材料のみならず、配線、電極、絶縁体など半導体素子を構成する全ての要素を印刷法で形成することが望ましい。印刷法を用い、必要最小限の材料で必要な箇所のみにパターンを形成することで、従来の半導体製造に比較して、製造時の投入資材とエネルギーを大幅に低減することができる。また、製造時に生じる廃棄物も大幅に低減することができ、環境負荷が小さくなる。しかしながら、半導体素子を構成する全ての要素を印刷法で形成するには課題がある。

【0018】

製造上の最も大きな課題として、半導体素子の各構成要素を形成する際のアライメントが挙げられる。1つのTFTを作成する場合でも、ゲート電極、ゲート絶縁膜、ソース・ドレイン電極、チャネル層のそれぞれの要素を正確にアライメントし、形成する必要がある。精度の高いアライメントが必要な場合には、通常、アライメントずれは回転とオフセットの主に2つの成分に分解して補正される。

【0019】

このうち、回転によるずれは、製造する製品の大きさに依存する。同じ精度の回転ずれが生じているとして、サイズが10cmの製品に対し、1mの製品では10倍のパターンずれが生じる。フォトリソグラフィーでは、こうした回転ずれは、基板ステージあるいはマスクステージの回転機構により補正される。しかし、より大型な基板の使用が前提である印刷装置で、このような回転機構を設けることは装置を複雑化し、印刷装置のコストを増大させるため得策ではない。

【0020】

そこで、本発明は、上記従来技術の問題点に鑑みて成されたものであり、その目的は、より簡便な印刷装置を用いて、大型な電子・電気回路をアライメント精度良く製造可能な電子・電気回路の製造方法を提供することにある。

【課題を解決するための手段】

【0021】

本発明の一態様では、印刷法を用いて複数の構成要素を有する素子から成る電子・電気回路を製造するための製造方法であって、

特定の波長の光又は電磁波を透過する基板の裏面に、上記光又は電磁波の透過率の低いマークパターンを配置し、

上記基板の上面から上記光又は電磁波を照射し、

上記マークパターンの位置を検出することによりアライメントを行い、

上記素子の各構成要素を、上記印刷法を用いて形成することを特徴とする。

【0022】

また、本発明の他の態様では、印刷法を用いて複数の構成要素を有する素子から成る電子・電気回路を製造するための製造方法であって、

特定の波長の光又は電磁波を透過する基板の裏面に、上記光又は電磁波の透過率の低いマークパターンが形成された支持基板を配置し、

上記基板の上面から上記光又は電磁波を照射し、

上記マークパターンの位置を検出することによりアライメントを行い、

上記電子・電気素子の各構成要素を、上記印刷法を用いて形成することを特徴とする。

【発明の効果】

【0023】

本発明によれば、より簡便な印刷装置を用いて、大型な電子・電気回路をアライメント精度良く製造することができる。この結果、低コストで、歩留まりが高く、大型な電子・電気回路を提供することができる。

【図面の簡単な説明】

【0024】

【図1】本発明の第1の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図であり、(a)は平面図、(b)は図1(a)中のA−Bで示される断面図である。

【図2】本発明の第1の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図である。

【図3】本発明の第1の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図である。

【図4】本発明の第1の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図である。

【図5】本発明の第1の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図である。

【図6】本発明の第1の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図である。

【図7】本発明の第1の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図である。

【図8】本発明の第2の実施の形態に係る電子・電気回路の印刷製造法の一工程を示す図である。

【発明を実施するための形態】

【0025】

最初に、本発明の理解を容易にするために、本発明の原理について説明する。

【0026】

例えば、TFTに代表される、複数の構成要素からなる電子素子を製造する際に、各構成要素を相対的に正確な位置に配置することが重要である。例えば、前記のTFTの場合には、ゲート電極、ゲート絶縁膜、ソース・ドレイン電極、チャネル層のそれぞれの要素をアライメントし、正確に配置しなければ性能が低下するのみならず、機能する素子の歩留まりが低下する。

【0027】

アライメントずれの成分は、主にオフセットによるものと、回転によるものに分解することができる。このうち、オフセットの成分は基板あるいはマスクパターンの前後・左右の微小な調整により除去することができる。回転によるずれは、ある基準点をとり、その基準点からの距離Lと、基板とマスクパターンの相対的な角度差θを用いると、前後方向には、

Δy=L×sin(θ) (1)

左右方向には、

Δx=L×cos(θ) (2)

それぞれ、(1)式、(2)式で規定される変位が生じる。この変位量は、製品基板上で、前述のある基準点からの距離Lにより異なっていることに注意する必要がる。製品の基板サイズが小さく、製造上許容されるずれ量より、これらの変位量が充分小さいときには、前述のオフセットの一部として、オフセットによる補正の中に押し込めることも可能である。

【0028】

しかしながら、基板サイズが大きくなり、(1)、(2)式中のLが大きくなると、これらの変位量は無視できない。通常、これらの回転による変位量を補正するためには、基板あるいはマスクパターンの少なくとも一方を回転させる機構を設けて、調整する必要がある。一般に、回転機構は、基板およびマスクパンが大きくなるにつれて、装置が大型化し複雑化する。

【0029】

大型な基板の中で、形成する電子・電気回路を一定の領域に区切って分割し、一度に印刷する範囲を小さくすることにより、前記の(1)、(2)式中のLを実効的に小さくすることは可能である。しかしこの方法を用いる場合には、領域分割する分割数に応じてアライメントマークの数を増やす必要がある。

【0030】

印刷では、液体材料インクを使用するため、パターン形成の精度は、下地の微小な段差あるいは下地と材料インクの濡れ性など、下地の表面状態に強く依存する。一般に、アライメントマークは、基板上に基板とは異なる材料を用いて形成する。このアライメントマークと印刷形成する回路要素と接する、あるいはオーバーラップするなどの干渉が生じると、印刷不良を引き起こす。

【0031】

したがって、アライメントマークは、このような、素子・回路パターンと干渉することがないように、細心の注意を払って、形状、配置などを決定する必要がある。領域分割して、複数のアライメントマークを設ける場合には、アライメントマークの占有面積が増大するので、マークの形状、配置が非常に困難になってくる。

【0032】

本発明の印刷法による電子・電気回路の製造では、こうしたアライメントマークを基板の裏面に形成する。そのため、分割印刷のために、多数のアライメントマークを配置する場合においても、素子・回路パターンとアライメントマークの干渉による印刷不良のリスクを低減させることができる。

【0033】

この製造方法は、多数のアライメントマークを使用する分割印刷において、特に効果が大きい。また、分割印刷を行うことで、回転ずれによるアライメントずれの許容量が大きくなり、製造歩留まりが向上する。

【0034】

また、回転ずれを補正する場合にも、1回の分割印刷による回転補正を行うことで、対応できる。特に、インクジェット法、インクディスペンス法などに代表される印刷データが数値で与えられる無版印刷法を用いる場合には、ずれ補正に伴う座標変換の演算の規模を小さくすることができる。この結果、製造時のスループットが向上し、結果として製造コストを低減することができる。

【0035】

このように、本発明によれば、高性能でかつ均一性、信頼性に優れた半導体素子を低コストで供給することができる。また、本発明の製造方法は、大面積である電子・電気回路の印刷製造に適しており、大規模な表示装置、センサアレイなどを低コストで製造することが可能となる。

【0036】

次に、本発明の実施の形態を図面を参照して説明する。

【0037】

(第1の実施の形態)

本発明の第1の実施の形態に係る電子・電気回路の印刷製造法では、図1に示すように、裏面に複数のアライメントマーク11〜19を設けた基板100を使用する。ここで、図1(a)は平面図、図1(b)は、図1(a)中のA−Bで示される断面図を示している。

【0038】

第1の実施の形態では、電子・電気回路の基板100は9つの領域1〜9に分割されている。このような構成の下、それぞれの領域1〜9に、アライメントマーク11〜19が配置されている。

【0039】

そして、第1の実施の形態では、特定の波長の光又は電磁波を透過する基板100の裏面に、光又は電磁波の透過率の低いアライメントマーク11〜19(マークパターン)を配置し、基板100の上面から光又は電磁波を照射する。そして、アライメントマーク11〜19の位置を検出することによりアライメントを行い、素子(例えば、TFT)の各構成要素を印刷法を用いて形成する。このようにして、印刷法を用いて複数の構成要素を有する素子から成る電子・電気回路(例えば、TFTアレイ)を製造する。

【0040】

次に、第1の実施の形態に係る電子・電気回路の製造方法について詳細に説明する。

【0041】

まず、図2に示すように、各領域1〜9において、それぞれ領域1〜9内に設けたアライメントマーク11〜19を用いてゲート電極21〜24を印刷する。図2は、第1から第4の領域1〜4までゲート電極21〜24を印刷形成した例を示している。

【0042】

例えば、第1の領域1では、第1のアライメントマーク11を用いて位置決めし、第1のゲート電極21を印刷形成する。また、第2の領域2では、第2のアライメントマーク12を用いて位置決めし、第2のゲート電極22を印刷形成する。そして、順次、第4のゲート電極24まで形成した。同様に、第9のゲート電極29(図示せず)を印刷形成した後に、ゲート絶縁膜を印刷形成する。

【0043】

図3では、第1から第4の領域1〜4までゲート絶縁膜31〜34を印刷形成した例を示している。

【0044】

例えば、第1の領域1では、第1のアライメントマーク11を用いてアライメントし、第1のゲート絶縁膜31を印刷形成する。第2の領域2では、第2のアライメントマーク12を用いてアライメントし、第2のゲート絶縁膜32を印刷形成する。そして、順次、第4のゲート絶縁膜24まで形成した。

【0045】

ここで、例えば、第1のゲート絶縁膜31と第1のアライメントマーク11は、平面図的には接して干渉しているように見えるが、実際には、アライメントマーク11は基板100の裏面に設けられており(図1(b)参照)、パターン干渉による印刷不良は生じない。同様に、第9のゲート絶縁膜39(図示せず)を印刷形成した後に、チャネル層を形成する。

【0046】

図4では、第1から第4の領域1〜4までチャネル層42〜44を印刷形成した例を示している。

【0047】

例えば、第1の領域1では、第1のアライメントマーク11を用いてアライメントし、第1のチャネル層41を印刷形成する。第2の領域2では、第2のアライメントマーク12を用いてアライメントし、第2のチャネル層42を印刷形成する。そして、順次、第4のチャネル層44まで形成した。同様に、第9のチャネル層49(図示せず)を印刷形成した後に、ソース・ドレイン電極を形成する。

【0048】

図5では、第1から第4の領域1〜4までに、ソース・ドレイン電極51〜54を印刷形成した例を示している。

【0049】

例えば、第1の領域1では、第1のアライメントマーク11を用いてアライメントし、第1のソース・ドレイン電極51を印刷形成する。第2の領域2では、第2のアライメントマーク12を用いてアライメントし、第2のソース・ドレイン電極52を印刷形成する。そして、順次、第4のソース・ドレイン電極54まで形成した。同様に、第9のソース・ドレイン電極59(図示せず)を印刷形成した後に、各領域1〜9の素子を接続するためにグローバル配線を形成する。

【0050】

図6のグローバル配線61は、領域1と領域2のソース電極とを接続している。これは、領域1と領域2のアライメントマーク11とアライメントマーク12を用いて位置決めされている。同様にグローバル配線62は領域2と領域3のアライメントマーク12とアライメントマーク13を用いて位置決めされ、領域2と領域3のソース電極とを接続している。

【0051】

グローバル配線65は、領域1と領域4のゲート電極を接続している。これは、領域1と領域4のアライメントマーク11とアライメントマーク14を用いて位置決めされている。同様にグローバル配線66は領域2と領域5のアライメントマーク12とアライメントマーク15を用いて位置決めされ、領域2と領域5のゲート電極とを接続している。同様にして、図7に示すように、3x3のTFTアレイを製造することができる。

【0052】

尚、これらのグローバル配線の印刷形成の手段としては、インクジェット法、インクディスペンス法などに代表される印刷データが数値で与えられる無版印刷法が適していることは自明である。

【0053】

(第2の実施の形態)

本発明の第2の実施の形態に係る電子・電気回路の印刷製造法では、図8に示すように、分割された領域1〜9に対して、複数のアライメントマーク81,82を配置する。このとき、複数のアライメントマーク81、82から、分割された領域1〜9の回転ずれを見積もることができる。

【0054】

印刷形成する手段が、インクジェット法、インクディスペンス法などに代表される印刷データが数値で与えられる無版印刷法を用いる場合に、ここで見積もられた回転ずれの量を補正した座標を演算しなおすことで、アライメント精度を向上させることができる。このとき、演算するべき座標のデータは、分割された領域1〜9内に限られるため、計算量を少なくし、印刷のスループットを向上させることができる。

【0055】

また、全ての分割された領域1〜9の回転ずれをあらかじめ計測しおき、平均値を算出し、全ての分割された領域1〜9で同一の補正データを用いれば、さらに、印刷のスループットが向上できる。

【0056】

(第3の実施の形態)

本発明の第3の実施の形態に係る電子・電気回路の印刷製造法では、分割された領域1〜9の印刷形成手法として、小型のスタンプを用いる。小型のスタンプを用いる場合には、スタンプに回転機構(図示せず)を設けておき、スタンプの回転機構により回転ずれを補正する方法も有効である。

【0057】

このときに、各領域1〜9に形成された複数のアライメントマーク81、82(図8参照)により計測された回転ずれを、各領域1〜9毎に補正しても、あるいは、全領域1〜9の平均値を算出して全ての領域1〜9を回転ずれの平均値で補正して印刷しても、どちらの場合にも同様にアライメント精度の向上が期待できる。

【0058】

(第4の実施の形態)

上記第1の実施の形態では、基板100の裏面に、光又は電磁波の透過率の低いアライメントマーク11〜19(マークパターン)を配置したが、第4の実施の形態では、アライメントマーク11〜19が設けられた支持基板(図示せず)を使用する。

【0059】

具体的には、第4の実施の形態では、印刷法を用いて複数の構成要素を有する素子から成る電子・電気回路を製造する。この際、特定の波長の光又は電磁波を透過する基板100の裏面に、光又は電磁波の透過率の低いアライメントマーク11〜19(マークパターン)が形成された支持基板(図示せず)を配置する。そして、基板100の上面から光又は電磁波を照射し、アライメントマーク11〜19の位置を検出することによりアライメントを行う。このようにして、電子・電気素子の各構成要素を、印刷法を用いて形成可能である。

【0060】

(第5の実施の形態)

本発明の第5の実施の形態に係る電子・電気回路の印刷製造法では、製造される電気・電子回路が表示装置のように透過性が重要な場合には、製造時に使用したアライメントマーク11〜19を除去する。

【0061】

上記本発明の実施の形態によれば、より簡便な印刷装置を用いて、大型な電子・電気回路をアライメント精度良く製造することができる。この結果、低コストで、歩留まりが高く、大型な電子・電気回路を提供することができる。

【0062】

また、電子・電気回路を形成した後に、アライメントに使用したマークパターンを選択的に除去することが可能になり、ディスプレイなどの光透過特性が重要となる応用に対して効果がある。

【0063】

このように、本発明の実施の形態では、電子・電気回路の製造では、アライメントマークを基板の裏面に形成する。そのため、分割印刷のために、多数のアライメントマークを配置する場合においても、素子・回路パターンとアライメントマークの干渉による印刷不良のリスクを低減させることができる。

【0064】

この製造方法は、多数のアライメントマークを使用する分割印刷において、特に効果が大きい。また、分割印刷を行うことで、回転ずれによるアライメントずれの許容量が大きくなり、製造歩留まりが向上する。

【0065】

また、回転ずれを補正する場合にも、1回の分割印刷による回転補正を行うことで対応できる。特に、インクジェット法、インクディスペンス法などに代表される印刷データが数値で与えられる無版印刷法を用いる場合には、ずれ補正に伴う座標変換の演算の規模を小さくすることができる。この結果、製造時のスループットが向上し、結果として製造コストを低減することができる。

【0066】

このようにして、本発明の実施の形態によれば、高性能でかつ均一性、信頼性に優れた半導体素子を低コストで供給することができる。また、本発明の実施の形態に係る製造方法は、大面積である電子・電気回路の印刷製造に適しており、大規模な表示装置、センサアレイなどを低コストで製造することが可能となる。

【0067】

以上、本発明の実施例について説明したが、上述の例は、本発明の技術的思想に基づき種々に変形が可能である。

【符号の説明】

【0068】

1 分割領域

2 分割領域

3 分割領域

4 分割領域

5 分割領域

6 分割領域

7 分割領域

8 分割領域

9 分割領域

11 アライメントマーク

12 アライメントマーク

13 アライメントマーク

14 アライメントマーク

15 アライメントマーク

16 アライメントマーク

17 アライメントマーク

18 アライメントマーク

19 アライメントマーク

21 ゲート電極

22 ゲート電極

23 ゲート電極

24 ゲート電極

31 ゲート絶縁膜

32 ゲート絶縁膜

33 ゲート絶縁膜

34 ゲート絶縁膜

41 チャネル層

42 チャネル層

43 チャネル層

44 チャネル層

51 ソース・ドレイン電極

52 ソース・ドレイン電極

53 ソース・ドレイン電極

54 ソース・ドレイン電極

61 グローバル配線

62 グローバル配線

63 グローバル配線

64 グローバル配線

65 グローバル配線

66 グローバル配線

81 アライメントマーク

82 アライメントマーク

100 基板

【特許請求の範囲】

【請求項1】

印刷法を用いて複数の構成要素を有する素子から成る電子・電気回路を製造するための製造方法であって、

特定の波長の光又は電磁波を透過する基板の裏面に、上記光又は電磁波の透過率の低いマークパターンを配置し、

上記基板の上面から上記光又は電磁波を照射し、

上記マークパターンの位置を検出することによりアライメントを行い、

上記素子の各構成要素を、上記印刷法を用いて形成することを特徴とする電子・電気回路の製造方法。

【請求項2】

前記マークパターンを前記基板の裏面に配置することにより、前記構成要素の回路パターンと前記マークパターンとの干渉を防止することを特徴とする請求項1に記載の電子・電気回路の製造方法。

【請求項3】

前記基板を複数の領域に分割し、

前記分割された領域毎に前記マークパターンを配置し、

前記マークパターンを用いて前記領域毎にアライメントを行い、

前記領域毎に部分印刷を行うことを特徴とする請求項1又は2に記載の電子・電気回路の製造方法。

【請求項4】

前記マークパターンを用いて前記領域毎に部分印刷を行うことにより、回転ずれを補正することを特徴とする請求項3に記載の電子・電気回路の製造方法。

【請求項5】

前記部分印刷を行う印刷法が、印刷データが数値で与えられる無版印刷法であることを特徴とする請求項3又は4に記載の電子・電気回路の製造方法。

【請求項6】

前記無版印刷法は、インクジェット法又はインクディスペンス法であることを特徴とする請求項5に記載の電子・電気回路の製造方法。

【請求項7】

前記部分印刷を行う印刷法において、印刷パターンが前記基板のサイズより小型な版又はマスクで提供されることを特徴とする請求項3又は4に記載の電子・電気回路の製造方法。

【請求項8】

前記部分印刷を行う印刷法が、スタンプ法である特徴とする請求項7に記載の電子・電気回路の製造方法。

【請求項9】

前記スタンプ法では、スタンプに回転機構を設けておき、前記回転機構により前記回転ずれを補正することを特徴とする請求項8に記載の電子・電気回路の製造方法。

【請求項10】

前記分割された領域毎に前記マークパターンを複数配置したことを特徴とする請求項3から9のいずれか1項に記載の電子・電気回路の製造方法。

【請求項11】

前記複数のマークパターンから前記分割された領域の回転ずれを見積もることを特徴とする請求項10に記載の電子・電気回路の製造方法。

【請求項12】

前記無版印刷法を用いて、前記分割された領域をグローバルな配線で相互に接続することを特徴とする請求項5又は6に記載の電子・電気回路の製造方法。

【請求項13】

前記電子・電気回路を形成した後に、前記マークパターンを除去することを特徴とする請求項1から12のいずれか1項に記載の電子・電気回路の製造方法。

【請求項14】

印刷法を用いて複数の構成要素を有する素子から成る電子・電気回路を製造するための製造方法であって、

特定の波長の光又は電磁波を透過する基板の裏面に、上記光又は電磁波の透過率の低いマークパターンが形成された支持基板を配置し、

上記基板の上面から上記光又は電磁波を照射し、

上記マークパターンの位置を検出することによりアライメントを行い、

上記電子・電気素子の各構成要素を、上記印刷法を用いて形成することを特徴とする電子・電気回路の製造方法。

【請求項15】

前記マークパターンを前記支持基板に配置することにより、前記構成要素の回路パターンと前記マークパターンとの干渉を防止することを特徴とする請求項14に記載の電子・電気回路の製造方法。

【請求項16】

前記電子・電気回路はTFTアレイであり、前記素子はTFTであり、前記構成要素はゲート電極、ゲート絶縁膜、チャネル層、ソース・ドレイン電極又は配線であることを特徴とする請求項1から15のいずれか1項に記載の電子・電気回路の製造方法。

【請求項1】

印刷法を用いて複数の構成要素を有する素子から成る電子・電気回路を製造するための製造方法であって、

特定の波長の光又は電磁波を透過する基板の裏面に、上記光又は電磁波の透過率の低いマークパターンを配置し、

上記基板の上面から上記光又は電磁波を照射し、

上記マークパターンの位置を検出することによりアライメントを行い、

上記素子の各構成要素を、上記印刷法を用いて形成することを特徴とする電子・電気回路の製造方法。

【請求項2】

前記マークパターンを前記基板の裏面に配置することにより、前記構成要素の回路パターンと前記マークパターンとの干渉を防止することを特徴とする請求項1に記載の電子・電気回路の製造方法。

【請求項3】

前記基板を複数の領域に分割し、

前記分割された領域毎に前記マークパターンを配置し、

前記マークパターンを用いて前記領域毎にアライメントを行い、

前記領域毎に部分印刷を行うことを特徴とする請求項1又は2に記載の電子・電気回路の製造方法。

【請求項4】

前記マークパターンを用いて前記領域毎に部分印刷を行うことにより、回転ずれを補正することを特徴とする請求項3に記載の電子・電気回路の製造方法。

【請求項5】

前記部分印刷を行う印刷法が、印刷データが数値で与えられる無版印刷法であることを特徴とする請求項3又は4に記載の電子・電気回路の製造方法。

【請求項6】

前記無版印刷法は、インクジェット法又はインクディスペンス法であることを特徴とする請求項5に記載の電子・電気回路の製造方法。

【請求項7】

前記部分印刷を行う印刷法において、印刷パターンが前記基板のサイズより小型な版又はマスクで提供されることを特徴とする請求項3又は4に記載の電子・電気回路の製造方法。

【請求項8】

前記部分印刷を行う印刷法が、スタンプ法である特徴とする請求項7に記載の電子・電気回路の製造方法。

【請求項9】

前記スタンプ法では、スタンプに回転機構を設けておき、前記回転機構により前記回転ずれを補正することを特徴とする請求項8に記載の電子・電気回路の製造方法。

【請求項10】

前記分割された領域毎に前記マークパターンを複数配置したことを特徴とする請求項3から9のいずれか1項に記載の電子・電気回路の製造方法。

【請求項11】

前記複数のマークパターンから前記分割された領域の回転ずれを見積もることを特徴とする請求項10に記載の電子・電気回路の製造方法。

【請求項12】

前記無版印刷法を用いて、前記分割された領域をグローバルな配線で相互に接続することを特徴とする請求項5又は6に記載の電子・電気回路の製造方法。

【請求項13】

前記電子・電気回路を形成した後に、前記マークパターンを除去することを特徴とする請求項1から12のいずれか1項に記載の電子・電気回路の製造方法。

【請求項14】

印刷法を用いて複数の構成要素を有する素子から成る電子・電気回路を製造するための製造方法であって、

特定の波長の光又は電磁波を透過する基板の裏面に、上記光又は電磁波の透過率の低いマークパターンが形成された支持基板を配置し、

上記基板の上面から上記光又は電磁波を照射し、

上記マークパターンの位置を検出することによりアライメントを行い、

上記電子・電気素子の各構成要素を、上記印刷法を用いて形成することを特徴とする電子・電気回路の製造方法。

【請求項15】

前記マークパターンを前記支持基板に配置することにより、前記構成要素の回路パターンと前記マークパターンとの干渉を防止することを特徴とする請求項14に記載の電子・電気回路の製造方法。

【請求項16】

前記電子・電気回路はTFTアレイであり、前記素子はTFTであり、前記構成要素はゲート電極、ゲート絶縁膜、チャネル層、ソース・ドレイン電極又は配線であることを特徴とする請求項1から15のいずれか1項に記載の電子・電気回路の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2010−171160(P2010−171160A)

【公開日】平成22年8月5日(2010.8.5)

【国際特許分類】

【出願番号】特願2009−11625(P2009−11625)

【出願日】平成21年1月22日(2009.1.22)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

【公開日】平成22年8月5日(2010.8.5)

【国際特許分類】

【出願日】平成21年1月22日(2009.1.22)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

[ Back to top ]