電子回路の作動の監視

【課題】本発明は、電子回路の所与の機能又は動作の実行を監視するための方法及び回路を提供する。

【解決手段】デジタル信号(EN)を監視する方法は、第1のP チャネルMOS トランジスタ(P1)を、監視されるべき前記信号が第1の状態にある期間に負バイアス温度不安定性(NBTI)タイプの劣化状態に置くステップと、前記第1のP チャネルMOS トランジスタ(P1)の飽和電流を表す第1の量(VMES)を、監視されるべき前記信号が第2の状態に切り替わるとき測定するステップと、前記第1の量が閾値(TH)を超えるとき、監視結果を示す検出信号(DET) を与えるステップとを備えている。

【解決手段】デジタル信号(EN)を監視する方法は、第1のP チャネルMOS トランジスタ(P1)を、監視されるべき前記信号が第1の状態にある期間に負バイアス温度不安定性(NBTI)タイプの劣化状態に置くステップと、前記第1のP チャネルMOS トランジスタ(P1)の飽和電流を表す第1の量(VMES)を、監視されるべき前記信号が第2の状態に切り替わるとき測定するステップと、前記第1の量が閾値(TH)を超えるとき、監視結果を示す検出信号(DET) を与えるステップとを備えている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般的には電子回路に関し、具体的には回路若しくは要素の起動又は電子回路の機能の作動の経時的な監視に関する。

【0002】

本発明は、より具体的にはハッキング行為の影響による回路の誤動作の検出に適用される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】米国特許出願公開第2008/309396号明細書

【発明の概要】

【発明が解決しようとする課題】

【0004】

機密性の点で重要とみなされるデータを処理するほとんどの回路又は要素では、このようなデータをハッキングしようとする行為に対する対策が望まれている。

【0005】

特に一般的な攻撃は、いわゆるサイドチャネル攻撃であり、サイドチャネル攻撃では、集積回路が機密データを処理する動作を行っている間に、前記集積回路の電力消費が分析される(DPA −差分電力解析)。

【0006】

サイドチャネル攻撃の検出は、一般的には、重要なアルゴリズムの実行回数を監視することにより行なわれる。実際には、アタッカは、データ及び/又は鍵に関して多くの仮定を作成し、作成した多くの仮定に基づき、アルゴリズムの実行を何回も引き起こして集積回路の電力消費を分析する。

【0007】

従って、通常の技術は、動作の実行回数が余りにも多いときを検出して、その後適切な対策を講じるために、動作が新たに実行される度に増大又は減少されるカウンタを用いている。カウンタを用いてカウントされた動作の実行回数が、集積回路の不揮発性記憶領域(EEPROM)に記憶される。実際には、集積回路は通常、連続攻撃の攻撃と攻撃との間でリセットされるが、データは消去されるべきではない。様々なタイプの対策があり得るが、最もよく用いられている対策は、集積回路の動作を無効化することである。

【0008】

この技術の欠点は、攻撃された場合に重要である時間的要因を考慮に入れていないことである。実際には、同一のアルゴリズムの多数回の実行は、攻撃が行われているかもしれないという徴候を示すが、高頻度に亘り繰り返される攻撃は、攻撃のより確かな徴候である。

【0009】

集積回路(電子回路)の所与の機能又は動作の実行を監視するための解決策が望まれている。

【0010】

特に、電子回路のデータに対するハッキング行為を意味する短時間内に繰り返される動作を、同数の動作であるが正常な使用に相当する時間内で十分に間隔が置かれている動作から区別するために、時間的要因を考慮することが更に望まれている。

【0011】

従って、本発明の目的は、公知のハッキング行為の検出技術の欠点の全て又は一部を克服することである。

【0012】

本発明の別の目的は、実施が簡単であるように小型化という解決策を提供することである。

【0013】

本発明の別の目的は、同一の電子回路の異なる機能又は動作のために実行され得る解決策を提供することである。

【0014】

より一般的には、本発明は、経時的な実行回数の点から、電子回路(集積回路)の機能又は動作の作動を監視することを目的とする。

【課題を解決するための手段】

【0015】

これらの目的及び他の目的の全て又は一部を達成するために、本発明は、デジタル信号を監視する方法において、

第1のP チャネルMOS トランジスタを、監視されるべき前記信号が第1の状態にある期間に負バイアス温度不安定性(NBTI)タイプの劣化状態に置くステップと、

前記第1のP チャネルMOS トランジスタの飽和電流を表す第1の量を、監視されるべき前記信号が第2の状態に切り替わるとき測定するステップと、

前記第1の量が閾値を超えるとき、監視結果を示す検出信号を与えるステップと

を備えていることを特徴とする方法

を提供する。

【0016】

本発明によれば、前記第1の量は、少なくとも前記第1のP チャネルMOS トランジスタと抵抗素子とを直列に備える第1のブランチの中間点における電圧である。

【0017】

本発明によれば、前記第1の量を、第2のトランジスタの飽和電流を表す第2の量と比較するステップを更に備えており、前記検出信号は、前記第1の量と前記第2の量との差が閾値を超えるとき与えられる。

【0018】

本発明によれば、監視されるべき前記信号は、暗号化動作の状態を示す信号である。

【0019】

本発明は、更に、デジタル信号を監視するための回路において、

供給電圧が印加される2つの端子間に、

第1のP チャネルMOS トランジスタ、第1のスイッチ及び第1の抵抗素子を直列に含む第1のブランチと、

第2のP チャネルMOS トランジスタ、第2のスイッチ、第3のスイッチ及び第2の抵抗素子を直列に含む第2のブランチと、

前記第1及び第2のブランチの第1及び第2のP チャネルMOS トランジスタにバイアスを印加することが可能な第3のブランチと、

前記第1及び第2のブランチの第1及び第2の抵抗素子の夫々の電圧を比較する比較器と、

監視されるべき前記信号が第1の状態にあるとき、前記第1のブランチのP チャネルMOS トランジスタのソース及びドレインを短絡させることが可能な要素と

を備えていることを特徴とする回路

を提供する。

【0020】

本発明によれば、前記第1及び第3のスイッチはN チャネルMOS トランジスタである。

【0021】

本発明によれば、監視されるべき前記信号は、インバータを介して、前記第1のブランチ及び第2のブランチのN チャネルMOS トランジスタの夫々のゲートと、前記要素を構成するP チャネルMOS トランジスタのゲートとに夫々与えられる。

【0022】

本発明によれば、前記第3のブランチは、供給電圧が印加される前記端子間に、第4のスイッチ、P チャネルMOS トランジスタ及び電流源を直列に含んでいる。

【0023】

本発明によれば、前記第2及び第4のスイッチはP チャネルMOS トランジスタである。

【0024】

本発明は、更に、暗号化機能を実行する少なくとも1つの暗号化部と、

前記機能の状態を示す信号を監視するための上記の少なくとも1つの回路と

を備えていることを特徴とする電子回路

を提供する。

【0025】

本発明の前述及び他の目的、特徴及び利点を、本発明を限定するものではない具体的な実施形態について添付図面を参照して以下に詳細に説明する。

【図面の簡単な説明】

【0026】

【図1】本発明が一例として適用されるタイプの電子回路を示すブロック図である。

【図2】図1に示された電子回路の機能の起動に関する信号の通常の動作状態及び攻撃が存在する状態での夫々の形状の例を示すタイミング図である。

【図3】本発明の実施形態を示すブロック図である。

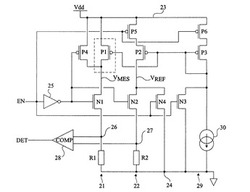

【図4】図3に示された監視回路を詳細に示す図である。

【図5】図4に示された監視回路の動作を示すタイミング図である。

【発明を実施するための形態】

【0027】

同一の要素は、異なる図面において同一の参照番号で示されている。

【0028】

明瞭にするために、本発明の理解に有用なステップ及び要素のみが示され、説明されている。特に、説明されている実施形態に係る監視回路及び又は監視方法によって監視される機能又は動作は詳述されておらず、本発明は、デジタル信号により起動されて電子回路(集積回路)によって実行され得るあらゆる機能又は動作と適合し、該機能又は動作に関して、閾値に対する実行頻度の変化を監視することが望まれている。更に、起こり得る攻撃を監視する適用例では、対策が詳述されておらず、本発明はここでもまた、攻撃行為が検出されたときに講じられるあらゆる通常の対策と適合する。

【0029】

図1は、本発明が適用されるタイプの集積回路(電子回路)1 の実施形態を示すブロック図である。このような電子回路1 は、一般的に、処理部11(PU)と一又は複数のメモリ12,13,14とを備えており、例えば、メモリ12はRAM 又は処理レジスタであり、メモリ13は一又は複数の書き換え可能な不揮発性メモリ(NVM) であり、メモリ14は一又は複数の書き換え不可能な不揮発性メモリ(ROM) である。電子回路1 は、異なる要素が相互に通信可能であるための一又は複数の制御バス、アドレスバス及びデータバス15と、電子回路1 の外部と通信するための入出力インタフェース16(I/O) とを更に備えている。本発明が意図される適用例によれば、電子回路1 は、他の機能を実行するための他の要素又は回路17(FCT) を備えている。(例えば、スマートカードタイプの)要素を保護する好ましい適用例では、回路1 は、例えば、暗号化し、復号し、スクランブルする署名演算機能等の秘密量(鍵)を実行する機能を行なうための暗号化プロセッサ18(CP)を特に備えている。別の適用例によれば、作動の監視が望まれる電子回路は、メモリと(中央処理部を備えていない)暗号化プロセッサとを備えている。

【0030】

本発明は、起こり得る攻撃を検出するために回路の暗号化機能の作動を監視する適用例と関連して以下に説明される。しかしながら、本発明は、より一般的には、動作の実行頻度が閾値に照らし合わせて検査されることが望まれるあらゆる要素又は回路の作動の監視に適用される。例えば、適切な適用例が、必要であれば、メモリに対する負荷を減少してメモリの寿命を向上すべく複数の削除/プログラミング動作を後回しにするために、不揮発性メモリにおける削除/プログラミング動作の頻度を検査することであってもよい。

【0031】

図2(a) 及び(b) は、監視されるべき信号ENの(任意に状態1として示されている)有効化期間と(任意に状態0として示されている)休止期間とを示すタイミング図である。例えば、信号ENは暗号化機能のイネーブル信号である。変形例として、信号ENはこのような機能がアクティブであることを示す状態信号であってもよい。

【0032】

図2(a) は、動作が比較的長い休止期間を介して一回又は複数回実行される通常の動作状態を示す。実際には、休止期間は作動期間より長く、残りの時間は、このような機能によって与えられるデータを利用するために電子回路の残りの要素によって用いられる。

【0033】

図2(b) は、(例えば、攻撃が存在する状態である)異常動作がある場合の信号ENの形状を示す。暗号化動作が繰り返される頻度が非常に高く、特に動作が休止期間によって分離されていない。これは、ハッカーがデータ及び/又は鍵に関する連続的な仮定で暗号化動作を実行し、データが更に処理されるのを待たずに電子回路をリセットするためである。実際には、攻撃は、鍵に関する情報を導き出すために暗号化処理の実行中に電子回路の電力消費を監視することを含んでいる。他のデータ又は仮定で電子回路を実行するために電子回路を即座にリセットするということは、対策が起動されることを回避するためでもある。

【0034】

図3は、本発明の実施形態を示すブロック図である。例えば図1に示された暗号化プロセッサ18によって実行される動作の監視が望まれていると仮定する。監視されるべき動作は、イネーブル信号ENの受信であると仮定する。このイネーブル信号ENはサンプリングされて監視回路2 に送られて、監視回路2 は、起こり得る異常動作を示す検出信号DET を与える。変形例として、状態信号ENが、機能内からサンプリングされる。監視回路2 は、異常動作を検出するために、信号ENの有効化期間の頻度を閾値に照らし合わせて分析する。

【0035】

上記の実施形態では、P チャネルMOS トランジスタの寄生効果、すなわち負バイアス温度不安定性(NBTI)を利用する。特定のバイアスを印加した状態では、電荷はトランジスタのゲートに捕捉される。これは、トランジスタの閾値電圧(VT)、従って飽和電流を変更することを意味する。このような劣化が時間の関数になる。NBTI現象を受けたトランジスタの劣化又は負荷が、トランジスタのドレイン、ソース及びバルクがアースされている一方、ゲートに負の電圧をバイアスとして印加することにより、又は、トランジスタのドレイン、ソース及びバルクが正の供給電圧を印加されている一方、ゲートに零電圧を印加することにより生じる。このNBTI現象は、通常、電子回路でトランジスタを切り替える段階で生じるが、一時的なものに過ぎない。NBTI現象は公知であり、CMOS技術におけるトランジスタの通常の動作では回避されることが一般的に望まれている。

【0036】

このNBTI現象は、ここでは、監視されるべき機能がアクティブである期間にトランジスタの検出の劣化を引き起こすために用いられる。従って、特に劣化の程度によって決まるある時間の後、トランジスタが正常な(劣化していない)状態に戻るということが利用される。

【0037】

NBTI現象は当技術で公知である。NBTI現象は、例えば、ダイエター ケー.シュローダー(Dieter K. Schroder)及びジェフ エー.バブコック(Jeff A. Babcock )著,論文「負バイアス温度不安定性:深いサブミクロンのシリコン半導体製造で組み合わせるための手段(Negative bias temperature instability:Road to cross in deep submicron silicon semiconductor manufacturing)」,応用物理学会誌(Journal of Applied Physics),2003年7月,94巻,p.1-18、及び、エム.アラム(M. Alam )及びエス.マハパトラ(S. Mahapatra)著,「PMOSのNBTI劣化の包括的なモデル(A comprehensive model of PMOS NBTI degradation)」,マイクロ電子工学の信頼性(Microelectronic Reliability),2005年1月,45巻,第1号,p.71−81に述べられている。

【0038】

図4は、図3に示されている監視回路2 の詳細な電気回路図である。

【0039】

原理は、監視されるべき機能が有効である期間にNBTIタイプの劣化を受けるP チャネルMOS トランジスタP1の挙動を、このような期間に劣化を受けていないP チャネルMOS トランジスタP2と比較することである。このために、第1のブランチ21及び第2のブランチ22の2つブランチが、正の供給電圧Vdd が印加される2つの端子23,24 間に並列して設けられており、第1及び第2のブランチ21,22 は、トランジスタP1,P2 、スイッチ(例えば、N チャネルMOS トランジスタ)N1,N2 及び抵抗素子R1,R2 を夫々直列に含んでいる。第2のブランチ22は、トランジスタP2と端子23との間に、監視対象の機能をイネーブルにするための信号ENによって制御されるスイッチ(例えば、P チャネルMOS トランジスタP5)を更に含んでいる。トランジスタN1,N2 のゲートは、監視対象の機能をイネーブルにするための信号ENのインバータ25を介した逆特性を受ける。トランジスタN1と抵抗素子R1との間の相互接続ノード26、トランジスタN2と抵抗素子R2との間の相互接続ノード27、従ってトランジスタN1,N2 のソースが、検出結果(監視結果)を示す検出信号DET を与える比較器28(COMP)の入力に接続されている。実際には、比較器28は、トランジスタP1,P2 の飽和電流に関するデータを間接的に比較する。

【0040】

トランジスタP1,P2 は第3のブランチ29によって確実にバイアスを印加され、第3のブランチ29は、端子23と端子24との間に、信号ENによって制御されるスイッチ(例えばP チャネルMOS トランジスタP6)、P チャネルMOS トランジスタP3及び電流源30を直列に含んでおり、トランジスタP3は(ゲート及びドレインが相互に接続されている)ダイオードとして組み立てられており、トランジスタP3のゲートはトランジスタP1,P2 の夫々のゲートに接続されている。

【0041】

バイアスを印加するための第3のブランチ29は、(電流源30に接続されている)トランジスタP3のドレインをアース24に接続するN チャネルMOS トランジスタN3によって制御可能である。トランジスタN3のゲートはイネーブル信号ENを受信する。更に、ゲートがイネーブル信号ENを受信するトランジスタN4が、トランジスタP2のドレインを接地する。

【0042】

測定用のトランジスタP1は、信号ENが高状態にあるときトランジスタP1のソース及びドレインを短絡させるP チャネルMOS トランジスタP4により劣化段階に置かれる。このために、トランジスタP4のゲートはインバータ25の出力に接続されている。組立体の全てのP チャネルトランジスタのバルクに加えてトランジスタP2のバルクが、構成によりソース(従って電圧Vdd )に接続されている。

【0043】

図5(a),(b),(c) 及び(d) は、図4に示された監視回路の動作を示すタイミング図である。図5(a) は、監視されるべき信号ENの形状の一例を示す。図5(b) 及び(c) は、トランジスタP1のドレインの電圧VMES、及びトランジスタP2のドレインの電圧VREFの夫々の形状を示す。図5(d) は、比較器28によって与えられる検出信号DET の形状を示す。

【0044】

測定用のトランジスタP1は最初は負荷を受けていないと仮定される。信号ENの最初の有効化(時間t1、図5(a) )で、トランジスタN3,N4 がオンされる。このため、トランジスタP2のドレインに加えてトランジスタP1,P2 のゲートが接地されることになる。夫々のゲートで信号ENを受信するトランジスタP5,P6 はオフされる。従って、電圧VREFは、(オン状態にあるトランジスタN4の電圧降下を無視して)零である。更に、インバータ25はトランジスタN1,N2 を遮断する。従って、第1のブランチ21及び第2のブランチ22 の両方がオフされる。測定用のトランジスタP1の側では、トランジスタP4がインバータ25によってオンされる。従って、トランジスタP1のゲートが接地されている一方、トランジスタP1のソース、バルク及びドレインは、(オン状態にあるトランジスタP4の電圧降下を無視して)電圧Vdd を印加される。そのため、トランジスタP1はNBTI劣化状態に置かれて、電荷がトランジスタP1のゲート酸化膜で増大する。

【0045】

時間t2で、イネーブル信号ENが無効化されると、この負荷はトランジスタP4をオフすることにより消える。同時に、トランジスタN1,N2 及びトランジスタP5,P6 はオンされて、トランジスタN3,N4 はオフされる。その後、測定段階が開始されて、第1のブランチ21及び第2のブランチ22 の両方が有効になる。比較器28は、測定段階では(オン状態にあるトランジスタN1,N2 の電圧降下を無視した)電圧VMES,VREF のレベルに夫々相当するノード26,27 における電圧レベルを比較する。バイアスを印加するための第3のブランチ29はトランジスタN3をオフすることにより有効になる。従って、トランジスタP1,P2 はオンされる。図5(b) のタイミング図に示されているように、トランジスタP1がオフされている間に生じた電荷の増大がトランジスタP1のより低い電流として変換されて、この結果、(抵抗素子R1の値が固定されている状態で)公称値V1より小さい電圧VMESになる。第2のブランチ22の側では、電圧VREFが、抵抗素子R2の値によって調整される値V2になる。値V1,V2 は必ずしも同一ではない。これらは、切替閾値、すなわち、比較器28の電圧VMESと電圧VREFとの間のレベル差(又はその逆数)が、比較器28内のオフセット又は抵抗素子R1,R2 の値によって設定されているか否かにより決まる。電圧VREFが測定期間の間変わらないので、閾値は電圧VMESの値THに相当し、電圧VMESの値TH未満で、トランジスタP1は、異常動作を検討すべく十分な劣化が累積されているとみなされる。

【0046】

タイミング図の左側部分では、NBTI寄生効果が時間t3から消えていると仮定されて、時間t3で、トランジスタP1,P2 は、再度同一になり、電圧VMESは値V1になる。

【0047】

タイミング図の右側部分は、電子回路の異常動作(例えばハッキング行為)を示す。このような場合、信号ENの有効化期間が互いに非常に近い。その結果、トランジスタP1は公称状態に戻る時間がない。トランジスタP1のゲート酸化膜における電荷の増大が、電圧VMESが閾値TH未満になるとき(時間t4)、比較器28は検出信号DET を切り替える(図5(d) )。

【0048】

検出信号DET は、電子回路のブロッキング、制御の作動、(例えば、不揮発性メモリに書き込む場合の)別の動作の後回し等のために利用されてもよい。

【0049】

上記の実施形態の利点は、電子回路の起動期間の頻度を考慮することが可能であり、起動期間の回数のみを考慮するのではないことである。

【0050】

別の利点は、トランジスタP1の劣化が、電源供給電圧のあらゆるノイズ又は妨害とは無関係である(トランジスタP1の2つの導電性端子−ドレイン及びソース−が劣化期間に同一の電圧になる)ことである。更に、この劣化は、異なる性質の起こり得る攻撃、例えばレーザー攻撃に反応しない。

【0051】

別の利点は、EEPROMへの連続的な書込み動作を行う必要がなくなり、これによりEEPROMに対する負荷が減少することである。

【0052】

別の利点は、監視回路がスペースをほとんどとらないことである。従って、複数の監視回路2 が、同一の電子回路内で、適用例に応じて異なるイネーブル信号の監視に割り当てられてもよい。

【0053】

本発明の様々な実施形態が説明されており、様々な変更及び調整が当業者に想起される。特に、本発明の実施形態の実際的な実施、特には検出信号を起動させるための閾値の選択は、適用例に応じて決まり、上記の機能に関する表示に基づく当業者の技能の範囲内である。更に、本発明の実施形態が、暗号化機能の起動に関する信号を監視する例に関連して説明されているが、本発明はより一般的には、デジタル信号の有効化期間の頻度の変化を監視することが望まれる場合に適用される。更に、他の測定回路が想起されてもよい。例えば、所与の回路では、比較器28によって用いられる基準値が、抵抗性分割ブリッジによって与えられてもよい。しかしながら、トランジスタP1のブランチと同様のブランチを用いる利点は、起こり得る分散を回避することである。

【符号の説明】

【0054】

1 電子回路

2 監視回路

18 暗号化部,暗号化プロセッサ

21 第1のブランチ

22 第2のブランチ

23 端子

24 端子

25 インバータ

26 ノード,中間点

28 比較器

29 第3のブランチ

30 電流源

N1 第1のスイッチ,N チャネルMOS トランジスタ

N2 第3のスイッチ,N チャネルMOS トランジスタ

P1 第1のP チャネルMOS トランジスタ

P2 第2のP チャネルMOS トランジスタ

P3 P チャネルMOS トランジスタ

P4 P チャネルMOS トランジスタ

P5 第2のスイッチ,P チャネルMOS トランジスタ

P6 第4のスイッチ,P チャネルMOS トランジスタ

R1 第1の抵抗素子

R2 第2の抵抗素子

【技術分野】

【0001】

本発明は、一般的には電子回路に関し、具体的には回路若しくは要素の起動又は電子回路の機能の作動の経時的な監視に関する。

【0002】

本発明は、より具体的にはハッキング行為の影響による回路の誤動作の検出に適用される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】米国特許出願公開第2008/309396号明細書

【発明の概要】

【発明が解決しようとする課題】

【0004】

機密性の点で重要とみなされるデータを処理するほとんどの回路又は要素では、このようなデータをハッキングしようとする行為に対する対策が望まれている。

【0005】

特に一般的な攻撃は、いわゆるサイドチャネル攻撃であり、サイドチャネル攻撃では、集積回路が機密データを処理する動作を行っている間に、前記集積回路の電力消費が分析される(DPA −差分電力解析)。

【0006】

サイドチャネル攻撃の検出は、一般的には、重要なアルゴリズムの実行回数を監視することにより行なわれる。実際には、アタッカは、データ及び/又は鍵に関して多くの仮定を作成し、作成した多くの仮定に基づき、アルゴリズムの実行を何回も引き起こして集積回路の電力消費を分析する。

【0007】

従って、通常の技術は、動作の実行回数が余りにも多いときを検出して、その後適切な対策を講じるために、動作が新たに実行される度に増大又は減少されるカウンタを用いている。カウンタを用いてカウントされた動作の実行回数が、集積回路の不揮発性記憶領域(EEPROM)に記憶される。実際には、集積回路は通常、連続攻撃の攻撃と攻撃との間でリセットされるが、データは消去されるべきではない。様々なタイプの対策があり得るが、最もよく用いられている対策は、集積回路の動作を無効化することである。

【0008】

この技術の欠点は、攻撃された場合に重要である時間的要因を考慮に入れていないことである。実際には、同一のアルゴリズムの多数回の実行は、攻撃が行われているかもしれないという徴候を示すが、高頻度に亘り繰り返される攻撃は、攻撃のより確かな徴候である。

【0009】

集積回路(電子回路)の所与の機能又は動作の実行を監視するための解決策が望まれている。

【0010】

特に、電子回路のデータに対するハッキング行為を意味する短時間内に繰り返される動作を、同数の動作であるが正常な使用に相当する時間内で十分に間隔が置かれている動作から区別するために、時間的要因を考慮することが更に望まれている。

【0011】

従って、本発明の目的は、公知のハッキング行為の検出技術の欠点の全て又は一部を克服することである。

【0012】

本発明の別の目的は、実施が簡単であるように小型化という解決策を提供することである。

【0013】

本発明の別の目的は、同一の電子回路の異なる機能又は動作のために実行され得る解決策を提供することである。

【0014】

より一般的には、本発明は、経時的な実行回数の点から、電子回路(集積回路)の機能又は動作の作動を監視することを目的とする。

【課題を解決するための手段】

【0015】

これらの目的及び他の目的の全て又は一部を達成するために、本発明は、デジタル信号を監視する方法において、

第1のP チャネルMOS トランジスタを、監視されるべき前記信号が第1の状態にある期間に負バイアス温度不安定性(NBTI)タイプの劣化状態に置くステップと、

前記第1のP チャネルMOS トランジスタの飽和電流を表す第1の量を、監視されるべき前記信号が第2の状態に切り替わるとき測定するステップと、

前記第1の量が閾値を超えるとき、監視結果を示す検出信号を与えるステップと

を備えていることを特徴とする方法

を提供する。

【0016】

本発明によれば、前記第1の量は、少なくとも前記第1のP チャネルMOS トランジスタと抵抗素子とを直列に備える第1のブランチの中間点における電圧である。

【0017】

本発明によれば、前記第1の量を、第2のトランジスタの飽和電流を表す第2の量と比較するステップを更に備えており、前記検出信号は、前記第1の量と前記第2の量との差が閾値を超えるとき与えられる。

【0018】

本発明によれば、監視されるべき前記信号は、暗号化動作の状態を示す信号である。

【0019】

本発明は、更に、デジタル信号を監視するための回路において、

供給電圧が印加される2つの端子間に、

第1のP チャネルMOS トランジスタ、第1のスイッチ及び第1の抵抗素子を直列に含む第1のブランチと、

第2のP チャネルMOS トランジスタ、第2のスイッチ、第3のスイッチ及び第2の抵抗素子を直列に含む第2のブランチと、

前記第1及び第2のブランチの第1及び第2のP チャネルMOS トランジスタにバイアスを印加することが可能な第3のブランチと、

前記第1及び第2のブランチの第1及び第2の抵抗素子の夫々の電圧を比較する比較器と、

監視されるべき前記信号が第1の状態にあるとき、前記第1のブランチのP チャネルMOS トランジスタのソース及びドレインを短絡させることが可能な要素と

を備えていることを特徴とする回路

を提供する。

【0020】

本発明によれば、前記第1及び第3のスイッチはN チャネルMOS トランジスタである。

【0021】

本発明によれば、監視されるべき前記信号は、インバータを介して、前記第1のブランチ及び第2のブランチのN チャネルMOS トランジスタの夫々のゲートと、前記要素を構成するP チャネルMOS トランジスタのゲートとに夫々与えられる。

【0022】

本発明によれば、前記第3のブランチは、供給電圧が印加される前記端子間に、第4のスイッチ、P チャネルMOS トランジスタ及び電流源を直列に含んでいる。

【0023】

本発明によれば、前記第2及び第4のスイッチはP チャネルMOS トランジスタである。

【0024】

本発明は、更に、暗号化機能を実行する少なくとも1つの暗号化部と、

前記機能の状態を示す信号を監視するための上記の少なくとも1つの回路と

を備えていることを特徴とする電子回路

を提供する。

【0025】

本発明の前述及び他の目的、特徴及び利点を、本発明を限定するものではない具体的な実施形態について添付図面を参照して以下に詳細に説明する。

【図面の簡単な説明】

【0026】

【図1】本発明が一例として適用されるタイプの電子回路を示すブロック図である。

【図2】図1に示された電子回路の機能の起動に関する信号の通常の動作状態及び攻撃が存在する状態での夫々の形状の例を示すタイミング図である。

【図3】本発明の実施形態を示すブロック図である。

【図4】図3に示された監視回路を詳細に示す図である。

【図5】図4に示された監視回路の動作を示すタイミング図である。

【発明を実施するための形態】

【0027】

同一の要素は、異なる図面において同一の参照番号で示されている。

【0028】

明瞭にするために、本発明の理解に有用なステップ及び要素のみが示され、説明されている。特に、説明されている実施形態に係る監視回路及び又は監視方法によって監視される機能又は動作は詳述されておらず、本発明は、デジタル信号により起動されて電子回路(集積回路)によって実行され得るあらゆる機能又は動作と適合し、該機能又は動作に関して、閾値に対する実行頻度の変化を監視することが望まれている。更に、起こり得る攻撃を監視する適用例では、対策が詳述されておらず、本発明はここでもまた、攻撃行為が検出されたときに講じられるあらゆる通常の対策と適合する。

【0029】

図1は、本発明が適用されるタイプの集積回路(電子回路)1 の実施形態を示すブロック図である。このような電子回路1 は、一般的に、処理部11(PU)と一又は複数のメモリ12,13,14とを備えており、例えば、メモリ12はRAM 又は処理レジスタであり、メモリ13は一又は複数の書き換え可能な不揮発性メモリ(NVM) であり、メモリ14は一又は複数の書き換え不可能な不揮発性メモリ(ROM) である。電子回路1 は、異なる要素が相互に通信可能であるための一又は複数の制御バス、アドレスバス及びデータバス15と、電子回路1 の外部と通信するための入出力インタフェース16(I/O) とを更に備えている。本発明が意図される適用例によれば、電子回路1 は、他の機能を実行するための他の要素又は回路17(FCT) を備えている。(例えば、スマートカードタイプの)要素を保護する好ましい適用例では、回路1 は、例えば、暗号化し、復号し、スクランブルする署名演算機能等の秘密量(鍵)を実行する機能を行なうための暗号化プロセッサ18(CP)を特に備えている。別の適用例によれば、作動の監視が望まれる電子回路は、メモリと(中央処理部を備えていない)暗号化プロセッサとを備えている。

【0030】

本発明は、起こり得る攻撃を検出するために回路の暗号化機能の作動を監視する適用例と関連して以下に説明される。しかしながら、本発明は、より一般的には、動作の実行頻度が閾値に照らし合わせて検査されることが望まれるあらゆる要素又は回路の作動の監視に適用される。例えば、適切な適用例が、必要であれば、メモリに対する負荷を減少してメモリの寿命を向上すべく複数の削除/プログラミング動作を後回しにするために、不揮発性メモリにおける削除/プログラミング動作の頻度を検査することであってもよい。

【0031】

図2(a) 及び(b) は、監視されるべき信号ENの(任意に状態1として示されている)有効化期間と(任意に状態0として示されている)休止期間とを示すタイミング図である。例えば、信号ENは暗号化機能のイネーブル信号である。変形例として、信号ENはこのような機能がアクティブであることを示す状態信号であってもよい。

【0032】

図2(a) は、動作が比較的長い休止期間を介して一回又は複数回実行される通常の動作状態を示す。実際には、休止期間は作動期間より長く、残りの時間は、このような機能によって与えられるデータを利用するために電子回路の残りの要素によって用いられる。

【0033】

図2(b) は、(例えば、攻撃が存在する状態である)異常動作がある場合の信号ENの形状を示す。暗号化動作が繰り返される頻度が非常に高く、特に動作が休止期間によって分離されていない。これは、ハッカーがデータ及び/又は鍵に関する連続的な仮定で暗号化動作を実行し、データが更に処理されるのを待たずに電子回路をリセットするためである。実際には、攻撃は、鍵に関する情報を導き出すために暗号化処理の実行中に電子回路の電力消費を監視することを含んでいる。他のデータ又は仮定で電子回路を実行するために電子回路を即座にリセットするということは、対策が起動されることを回避するためでもある。

【0034】

図3は、本発明の実施形態を示すブロック図である。例えば図1に示された暗号化プロセッサ18によって実行される動作の監視が望まれていると仮定する。監視されるべき動作は、イネーブル信号ENの受信であると仮定する。このイネーブル信号ENはサンプリングされて監視回路2 に送られて、監視回路2 は、起こり得る異常動作を示す検出信号DET を与える。変形例として、状態信号ENが、機能内からサンプリングされる。監視回路2 は、異常動作を検出するために、信号ENの有効化期間の頻度を閾値に照らし合わせて分析する。

【0035】

上記の実施形態では、P チャネルMOS トランジスタの寄生効果、すなわち負バイアス温度不安定性(NBTI)を利用する。特定のバイアスを印加した状態では、電荷はトランジスタのゲートに捕捉される。これは、トランジスタの閾値電圧(VT)、従って飽和電流を変更することを意味する。このような劣化が時間の関数になる。NBTI現象を受けたトランジスタの劣化又は負荷が、トランジスタのドレイン、ソース及びバルクがアースされている一方、ゲートに負の電圧をバイアスとして印加することにより、又は、トランジスタのドレイン、ソース及びバルクが正の供給電圧を印加されている一方、ゲートに零電圧を印加することにより生じる。このNBTI現象は、通常、電子回路でトランジスタを切り替える段階で生じるが、一時的なものに過ぎない。NBTI現象は公知であり、CMOS技術におけるトランジスタの通常の動作では回避されることが一般的に望まれている。

【0036】

このNBTI現象は、ここでは、監視されるべき機能がアクティブである期間にトランジスタの検出の劣化を引き起こすために用いられる。従って、特に劣化の程度によって決まるある時間の後、トランジスタが正常な(劣化していない)状態に戻るということが利用される。

【0037】

NBTI現象は当技術で公知である。NBTI現象は、例えば、ダイエター ケー.シュローダー(Dieter K. Schroder)及びジェフ エー.バブコック(Jeff A. Babcock )著,論文「負バイアス温度不安定性:深いサブミクロンのシリコン半導体製造で組み合わせるための手段(Negative bias temperature instability:Road to cross in deep submicron silicon semiconductor manufacturing)」,応用物理学会誌(Journal of Applied Physics),2003年7月,94巻,p.1-18、及び、エム.アラム(M. Alam )及びエス.マハパトラ(S. Mahapatra)著,「PMOSのNBTI劣化の包括的なモデル(A comprehensive model of PMOS NBTI degradation)」,マイクロ電子工学の信頼性(Microelectronic Reliability),2005年1月,45巻,第1号,p.71−81に述べられている。

【0038】

図4は、図3に示されている監視回路2 の詳細な電気回路図である。

【0039】

原理は、監視されるべき機能が有効である期間にNBTIタイプの劣化を受けるP チャネルMOS トランジスタP1の挙動を、このような期間に劣化を受けていないP チャネルMOS トランジスタP2と比較することである。このために、第1のブランチ21及び第2のブランチ22の2つブランチが、正の供給電圧Vdd が印加される2つの端子23,24 間に並列して設けられており、第1及び第2のブランチ21,22 は、トランジスタP1,P2 、スイッチ(例えば、N チャネルMOS トランジスタ)N1,N2 及び抵抗素子R1,R2 を夫々直列に含んでいる。第2のブランチ22は、トランジスタP2と端子23との間に、監視対象の機能をイネーブルにするための信号ENによって制御されるスイッチ(例えば、P チャネルMOS トランジスタP5)を更に含んでいる。トランジスタN1,N2 のゲートは、監視対象の機能をイネーブルにするための信号ENのインバータ25を介した逆特性を受ける。トランジスタN1と抵抗素子R1との間の相互接続ノード26、トランジスタN2と抵抗素子R2との間の相互接続ノード27、従ってトランジスタN1,N2 のソースが、検出結果(監視結果)を示す検出信号DET を与える比較器28(COMP)の入力に接続されている。実際には、比較器28は、トランジスタP1,P2 の飽和電流に関するデータを間接的に比較する。

【0040】

トランジスタP1,P2 は第3のブランチ29によって確実にバイアスを印加され、第3のブランチ29は、端子23と端子24との間に、信号ENによって制御されるスイッチ(例えばP チャネルMOS トランジスタP6)、P チャネルMOS トランジスタP3及び電流源30を直列に含んでおり、トランジスタP3は(ゲート及びドレインが相互に接続されている)ダイオードとして組み立てられており、トランジスタP3のゲートはトランジスタP1,P2 の夫々のゲートに接続されている。

【0041】

バイアスを印加するための第3のブランチ29は、(電流源30に接続されている)トランジスタP3のドレインをアース24に接続するN チャネルMOS トランジスタN3によって制御可能である。トランジスタN3のゲートはイネーブル信号ENを受信する。更に、ゲートがイネーブル信号ENを受信するトランジスタN4が、トランジスタP2のドレインを接地する。

【0042】

測定用のトランジスタP1は、信号ENが高状態にあるときトランジスタP1のソース及びドレインを短絡させるP チャネルMOS トランジスタP4により劣化段階に置かれる。このために、トランジスタP4のゲートはインバータ25の出力に接続されている。組立体の全てのP チャネルトランジスタのバルクに加えてトランジスタP2のバルクが、構成によりソース(従って電圧Vdd )に接続されている。

【0043】

図5(a),(b),(c) 及び(d) は、図4に示された監視回路の動作を示すタイミング図である。図5(a) は、監視されるべき信号ENの形状の一例を示す。図5(b) 及び(c) は、トランジスタP1のドレインの電圧VMES、及びトランジスタP2のドレインの電圧VREFの夫々の形状を示す。図5(d) は、比較器28によって与えられる検出信号DET の形状を示す。

【0044】

測定用のトランジスタP1は最初は負荷を受けていないと仮定される。信号ENの最初の有効化(時間t1、図5(a) )で、トランジスタN3,N4 がオンされる。このため、トランジスタP2のドレインに加えてトランジスタP1,P2 のゲートが接地されることになる。夫々のゲートで信号ENを受信するトランジスタP5,P6 はオフされる。従って、電圧VREFは、(オン状態にあるトランジスタN4の電圧降下を無視して)零である。更に、インバータ25はトランジスタN1,N2 を遮断する。従って、第1のブランチ21及び第2のブランチ22 の両方がオフされる。測定用のトランジスタP1の側では、トランジスタP4がインバータ25によってオンされる。従って、トランジスタP1のゲートが接地されている一方、トランジスタP1のソース、バルク及びドレインは、(オン状態にあるトランジスタP4の電圧降下を無視して)電圧Vdd を印加される。そのため、トランジスタP1はNBTI劣化状態に置かれて、電荷がトランジスタP1のゲート酸化膜で増大する。

【0045】

時間t2で、イネーブル信号ENが無効化されると、この負荷はトランジスタP4をオフすることにより消える。同時に、トランジスタN1,N2 及びトランジスタP5,P6 はオンされて、トランジスタN3,N4 はオフされる。その後、測定段階が開始されて、第1のブランチ21及び第2のブランチ22 の両方が有効になる。比較器28は、測定段階では(オン状態にあるトランジスタN1,N2 の電圧降下を無視した)電圧VMES,VREF のレベルに夫々相当するノード26,27 における電圧レベルを比較する。バイアスを印加するための第3のブランチ29はトランジスタN3をオフすることにより有効になる。従って、トランジスタP1,P2 はオンされる。図5(b) のタイミング図に示されているように、トランジスタP1がオフされている間に生じた電荷の増大がトランジスタP1のより低い電流として変換されて、この結果、(抵抗素子R1の値が固定されている状態で)公称値V1より小さい電圧VMESになる。第2のブランチ22の側では、電圧VREFが、抵抗素子R2の値によって調整される値V2になる。値V1,V2 は必ずしも同一ではない。これらは、切替閾値、すなわち、比較器28の電圧VMESと電圧VREFとの間のレベル差(又はその逆数)が、比較器28内のオフセット又は抵抗素子R1,R2 の値によって設定されているか否かにより決まる。電圧VREFが測定期間の間変わらないので、閾値は電圧VMESの値THに相当し、電圧VMESの値TH未満で、トランジスタP1は、異常動作を検討すべく十分な劣化が累積されているとみなされる。

【0046】

タイミング図の左側部分では、NBTI寄生効果が時間t3から消えていると仮定されて、時間t3で、トランジスタP1,P2 は、再度同一になり、電圧VMESは値V1になる。

【0047】

タイミング図の右側部分は、電子回路の異常動作(例えばハッキング行為)を示す。このような場合、信号ENの有効化期間が互いに非常に近い。その結果、トランジスタP1は公称状態に戻る時間がない。トランジスタP1のゲート酸化膜における電荷の増大が、電圧VMESが閾値TH未満になるとき(時間t4)、比較器28は検出信号DET を切り替える(図5(d) )。

【0048】

検出信号DET は、電子回路のブロッキング、制御の作動、(例えば、不揮発性メモリに書き込む場合の)別の動作の後回し等のために利用されてもよい。

【0049】

上記の実施形態の利点は、電子回路の起動期間の頻度を考慮することが可能であり、起動期間の回数のみを考慮するのではないことである。

【0050】

別の利点は、トランジスタP1の劣化が、電源供給電圧のあらゆるノイズ又は妨害とは無関係である(トランジスタP1の2つの導電性端子−ドレイン及びソース−が劣化期間に同一の電圧になる)ことである。更に、この劣化は、異なる性質の起こり得る攻撃、例えばレーザー攻撃に反応しない。

【0051】

別の利点は、EEPROMへの連続的な書込み動作を行う必要がなくなり、これによりEEPROMに対する負荷が減少することである。

【0052】

別の利点は、監視回路がスペースをほとんどとらないことである。従って、複数の監視回路2 が、同一の電子回路内で、適用例に応じて異なるイネーブル信号の監視に割り当てられてもよい。

【0053】

本発明の様々な実施形態が説明されており、様々な変更及び調整が当業者に想起される。特に、本発明の実施形態の実際的な実施、特には検出信号を起動させるための閾値の選択は、適用例に応じて決まり、上記の機能に関する表示に基づく当業者の技能の範囲内である。更に、本発明の実施形態が、暗号化機能の起動に関する信号を監視する例に関連して説明されているが、本発明はより一般的には、デジタル信号の有効化期間の頻度の変化を監視することが望まれる場合に適用される。更に、他の測定回路が想起されてもよい。例えば、所与の回路では、比較器28によって用いられる基準値が、抵抗性分割ブリッジによって与えられてもよい。しかしながら、トランジスタP1のブランチと同様のブランチを用いる利点は、起こり得る分散を回避することである。

【符号の説明】

【0054】

1 電子回路

2 監視回路

18 暗号化部,暗号化プロセッサ

21 第1のブランチ

22 第2のブランチ

23 端子

24 端子

25 インバータ

26 ノード,中間点

28 比較器

29 第3のブランチ

30 電流源

N1 第1のスイッチ,N チャネルMOS トランジスタ

N2 第3のスイッチ,N チャネルMOS トランジスタ

P1 第1のP チャネルMOS トランジスタ

P2 第2のP チャネルMOS トランジスタ

P3 P チャネルMOS トランジスタ

P4 P チャネルMOS トランジスタ

P5 第2のスイッチ,P チャネルMOS トランジスタ

P6 第4のスイッチ,P チャネルMOS トランジスタ

R1 第1の抵抗素子

R2 第2の抵抗素子

【特許請求の範囲】

【請求項1】

デジタル信号を監視する方法において、

第1のP チャネルMOS トランジスタを、監視されるべき前記信号が第1の状態にある期間に負バイアス温度不安定性(NBTI)タイプの劣化状態に置くステップと、

前記第1のP チャネルMOS トランジスタの飽和電流を表す第1の量を、監視されるべき前記信号が第2の状態に切り替わるとき測定するステップと、

前記第1の量が閾値を超えるとき、監視結果を示す検出信号を与えるステップと

を備えていることを特徴とする方法。

【請求項2】

前記第1の量は、少なくとも前記第1のP チャネルMOS トランジスタと抵抗素子とを直列に備える第1のブランチの中間点における電圧であることを特徴とする請求項1に記載の方法。

【請求項3】

前記第1の量を、第2のトランジスタの飽和電流を表す第2の量と比較するステップを更に備えており、

前記検出信号は、前記第1の量と前記第2の量との差が閾値を超えるとき与えられることを特徴とする請求項1又は2に記載の方法。

【請求項4】

監視されるべき前記信号は、暗号化動作の状態を示す信号であることを特徴とする請求項1乃至3のいずれかに記載の方法。

【請求項5】

デジタル信号を監視するための回路において、

供給電圧が印加される2つの端子間に、

第1のP チャネルMOS トランジスタ、第1のスイッチ及び第1の抵抗素子を直列に含む第1のブランチと、

第2のP チャネルMOS トランジスタ、第2のスイッチ、第3のスイッチ及び第2の抵抗素子を直列に含む第2のブランチと、

前記第1及び第2のブランチの第1及び第2のP チャネルMOS トランジスタにバイアスを印加することが可能な第3のブランチと、

前記第1のブランチの第1の抵抗素子の電圧と、前記第2のブランチの第2の抵抗素子の電圧とを比較する比較器と、

監視されるべき前記信号が第1の状態にあるとき、前記第1のブランチの第1のP チャネルMOS トランジスタのソース及びドレインを短絡させることが可能な要素と

を備えていることを特徴とする回路。

【請求項6】

前記第1及び第3のスイッチはN チャネルMOS トランジスタであることを特徴とする請求項5に記載の回路。

【請求項7】

監視されるべき前記信号は、インバータを介して、前記第1のブランチ及び第2のブランチのN チャネルMOS トランジスタの夫々のゲートと、前記要素を構成するP チャネルMOS トランジスタのゲートとに夫々与えられることを特徴とする請求項6に記載の回路。

【請求項8】

前記第3のブランチは、供給電圧が印加される前記端子間に、第4のスイッチ、P チャネルMOS トランジスタ及び電流源を直列に含んでいることを特徴とする請求項5乃至7のいずれかに記載の回路。

【請求項9】

前記第2及び第4のスイッチはP チャネルMOS トランジスタであることを特徴とする請求項8に記載の回路。

【請求項10】

暗号化機能を実行する少なくとも1つの暗号化部と、

前記暗号化機能の状態を示す信号を監視するための請求項5乃至9のいずれかに記載の少なくとも1つの回路と

を備えていることを特徴とする電子回路。

【請求項1】

デジタル信号を監視する方法において、

第1のP チャネルMOS トランジスタを、監視されるべき前記信号が第1の状態にある期間に負バイアス温度不安定性(NBTI)タイプの劣化状態に置くステップと、

前記第1のP チャネルMOS トランジスタの飽和電流を表す第1の量を、監視されるべき前記信号が第2の状態に切り替わるとき測定するステップと、

前記第1の量が閾値を超えるとき、監視結果を示す検出信号を与えるステップと

を備えていることを特徴とする方法。

【請求項2】

前記第1の量は、少なくとも前記第1のP チャネルMOS トランジスタと抵抗素子とを直列に備える第1のブランチの中間点における電圧であることを特徴とする請求項1に記載の方法。

【請求項3】

前記第1の量を、第2のトランジスタの飽和電流を表す第2の量と比較するステップを更に備えており、

前記検出信号は、前記第1の量と前記第2の量との差が閾値を超えるとき与えられることを特徴とする請求項1又は2に記載の方法。

【請求項4】

監視されるべき前記信号は、暗号化動作の状態を示す信号であることを特徴とする請求項1乃至3のいずれかに記載の方法。

【請求項5】

デジタル信号を監視するための回路において、

供給電圧が印加される2つの端子間に、

第1のP チャネルMOS トランジスタ、第1のスイッチ及び第1の抵抗素子を直列に含む第1のブランチと、

第2のP チャネルMOS トランジスタ、第2のスイッチ、第3のスイッチ及び第2の抵抗素子を直列に含む第2のブランチと、

前記第1及び第2のブランチの第1及び第2のP チャネルMOS トランジスタにバイアスを印加することが可能な第3のブランチと、

前記第1のブランチの第1の抵抗素子の電圧と、前記第2のブランチの第2の抵抗素子の電圧とを比較する比較器と、

監視されるべき前記信号が第1の状態にあるとき、前記第1のブランチの第1のP チャネルMOS トランジスタのソース及びドレインを短絡させることが可能な要素と

を備えていることを特徴とする回路。

【請求項6】

前記第1及び第3のスイッチはN チャネルMOS トランジスタであることを特徴とする請求項5に記載の回路。

【請求項7】

監視されるべき前記信号は、インバータを介して、前記第1のブランチ及び第2のブランチのN チャネルMOS トランジスタの夫々のゲートと、前記要素を構成するP チャネルMOS トランジスタのゲートとに夫々与えられることを特徴とする請求項6に記載の回路。

【請求項8】

前記第3のブランチは、供給電圧が印加される前記端子間に、第4のスイッチ、P チャネルMOS トランジスタ及び電流源を直列に含んでいることを特徴とする請求項5乃至7のいずれかに記載の回路。

【請求項9】

前記第2及び第4のスイッチはP チャネルMOS トランジスタであることを特徴とする請求項8に記載の回路。

【請求項10】

暗号化機能を実行する少なくとも1つの暗号化部と、

前記暗号化機能の状態を示す信号を監視するための請求項5乃至9のいずれかに記載の少なくとも1つの回路と

を備えていることを特徴とする電子回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2011−41280(P2011−41280A)

【公開日】平成23年2月24日(2011.2.24)

【国際特許分類】

【出願番号】特願2010−180256(P2010−180256)

【出願日】平成22年8月11日(2010.8.11)

【出願人】(509096153)エス テ マイクロエレクトロニクス(ローセット)エス アー エス (15)

【Fターム(参考)】

【公開日】平成23年2月24日(2011.2.24)

【国際特許分類】

【出願日】平成22年8月11日(2010.8.11)

【出願人】(509096153)エス テ マイクロエレクトロニクス(ローセット)エス アー エス (15)

【Fターム(参考)】

[ Back to top ]