電子回路及びそのタイミング調整方法

【課題】電子回路及びそのタイミング調整方法において、フリップフロップのホールドエラーを防止すること。

【解決手段】クロック信号CLKに同期してテストパターンTPを出力する送信側フリップフロップFFt1〜FFt3と、テストパターンTPを遅延させる遅延回路41〜43と、遅延回路41〜43から出力されたテストパターンTPをラッチすると共に、テストパターンTPを出力する受信側フリップフロップFFr1〜FFr3と、受信側フリップフロップFFr1〜FFr3から出力されたテストパターンTPと期待値とを比較して、それらが一致するか否かを示す比較信号Sp1〜Sp3を出力する比較器46と、比較信号Sp1〜Sp3によってテストパターンTPと期待値とが一致していないときに、遅延回路41〜43の遅延時間を調整するタイミング調整器45とを有する電子回路による。

【解決手段】クロック信号CLKに同期してテストパターンTPを出力する送信側フリップフロップFFt1〜FFt3と、テストパターンTPを遅延させる遅延回路41〜43と、遅延回路41〜43から出力されたテストパターンTPをラッチすると共に、テストパターンTPを出力する受信側フリップフロップFFr1〜FFr3と、受信側フリップフロップFFr1〜FFr3から出力されたテストパターンTPと期待値とを比較して、それらが一致するか否かを示す比較信号Sp1〜Sp3を出力する比較器46と、比較信号Sp1〜Sp3によってテストパターンTPと期待値とが一致していないときに、遅延回路41〜43の遅延時間を調整するタイミング調整器45とを有する電子回路による。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子回路及びそのタイミング調整方法に関する。

【背景技術】

【0002】

複数のフリップフロップを備えた電子回路では、配線遅延等が原因で各フリップフロップに異なるタイミングでクロック信号が到達することがある。そのような現象は、クロックスキューと呼ばれる。

【0003】

クロックスキューが発生すると、フリップフロップへの入力信号とクロック信号の入力タイミングが略同時になり、入力信号とは逆のレベルの信号がフリップフロップにおいてラッチされるホールドエラーが生じてしまう。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002−204222号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

電子回路及びそのタイミング調整方法において、フリップフロップのホールドエラーを防止することを目的とする。

【課題を解決するための手段】

【0006】

以下の開示の一観点によれば、クロック信号に同期してテストパターンを出力する送信側フリップフロップと、前記送信側フリップフロップから出力された前記テストパターンを所定の遅延時間だけ遅延させて出力する遅延回路と、前記遅延回路から出力された前記テストパターンをラッチすると共に、前記クロック信号に同期して前記テストパターンを出力する受信側フリップフロップと、前記受信側フリップフロップから出力された前記テストパターンと、該テストパターンの期待値とを比較して、前記テストパターンと前記期待値とが一致するか否かを示す比較信号を出力する比較器と、前記比較信号が入力され、該比較信号によって前記テストパターンと前記期待値とが一致していないことが判った場合に、前記遅延回路における前記遅延時間を調整するタイミング調整器とを有する電子回路が提供される。

【0007】

また、その開示の一観点によれば、送信側フリップフロップが遅延回路にテストパターンを出力して、前記遅延回路において所定の遅延時間だけ遅延された前記テストパターンを受信側フリップフロップがラッチするステップと、クロック信号に同期して前記受信側フリップフロップから出力された前記テストパターンと、該テストパターンの期待値とが一致するか否かを調べるステップと、前記テストパターンと前記期待値とが一致しないことが判った場合に、前記遅延回路における前記遅延時間を調整するステップとを有する電子回路のタイミング調整方法が提供される。

【発明の効果】

【0008】

以下の開示によれば、ホールドエラーが原因で受信側フリップフロップから出力されたテストパターンが期待値と一致していないとき、遅延回路における遅延時間を調整することにより、ホールドエラーを解消することができる。

【図面の簡単な説明】

【0009】

【図1】図1は、予備的事項に係る電子回路の回路図である。

【図2】図2は、ホールドエラーについて説明するためのタイミングチャートである。

【図3】図3は、本実施形態に係る電子回路の回路図である。

【図4】図4は、本実施形態に係る第1の半導体素子の機能ブロック図である。

【図5】図5は、本実施形態に係る第2の半導体素子の機能ブロック図である。

【図6】図6は、本実施形態に係る第1の遅延回路の回路図である。

【図7】図7は、本実施形態に係るタイミング調整器の回路図である。

【図8】図8は、本実施形態に係る第1〜第3のタイミング指定器の回路図である。

【図9】図9は、本実施形態に係るタイミング調整方法について説明するためのフローチャートである。

【図10】図10は、本実施形態において、受信側フリップフロップの各々に出力されるテストパターンの一例を示す模式図である。

【図11】図11は、本実施形態に係る第1の送信側フリップフロップと第1の受信側フリップフロップのタイミングチャートである。

【図12】図12は、本実施形態に係る電子回路の模式図(その1)である。

【図13】図13は、本実施形態に係る電子回路の模式図(その2)である。

【発明を実施するための形態】

【0010】

本実施形態の説明に先立ち、本実施形態の基礎となる予備的事項について説明する。

【0011】

図1は、予備的事項に係る電子回路1の回路図である。

【0012】

この電子回路1は、配線基板2に実装された第1の半導体素子3と第2の半導体素子4と有する。

【0013】

このうち、第1の半導体素子3は第1のフリップフロップFF1と第2のフリップフロップFF2を有し、第2の半導体素子4は第3のフリップフロップFF3と第4のフリップフロップFF4を有する。

【0014】

これらのフリップフロップFF1〜FF4は、DQフリップフロップであって、ラッチしていたデータをクロック信号CLKに同期してQ端子から出力する。

【0015】

この電子回路1では、配線基板2を介して第1の半導体素子3と第2の半導体素子4との間でデータの送受信が行われる。

【0016】

例えば、第1のフリップフロップFF1から送信された第1のデータD1が第3のフリップフロップFF3に受信され、第4のフリップフロップFF4から送信された第2のデータD2が第2のフリップフロップFF2に受信される。

【0017】

図2は、電子回路1で発生し得るホールドエラーについて説明するためのタイミングチャートである。

【0018】

図2に示すように、第1のフリップフロップFF1は、クロック信号CLKの立ち上がりにより、ラッチしていた第1のデータD1を後段の第3のフリップフロップFF3に出力する。

【0019】

そして、第3のフリップフロップFF3は、クロック信号CLKの立ち上がりで上記の第1のデータD1を取り込んでラッチする。

【0020】

このとき、配線基板2における配線遅延が原因で、第1のフリップフロップFF1と第3のフリップフロップFF3にクロック信号CLKが異なるタイミングで到達することがある。

【0021】

こうなると、第3のフリップフロップFF3に入力される第1のデータD1の反転タイミングとクロック信号CLKの立ち上がりとが略同時となる。そのため、ラッチすべき第1のデータD1がHレベルであるにも関わらずLレベルにラッチしたり、逆にLレベルの第1のデータD1をHレベルにラッチしたりして、第3のフリップフロップFF3においてホールドエラーが発生する。

【0022】

その結果、第3のフリップフロップFF3から後段に出力される第1のデータD1が本来の論理レベルとは逆になり、電子回路1が正常に動作しなくなるという不都合を招いてしまう。

【0023】

また、ホールドエラーが発生したフリップフロップを特定するには、配線基板2の配線を外部に電気的に引き出して電子回路1をしらみつぶしに解析する必要があり、即座に不良解析を行うことも難しい。

【0024】

本願発明者は、このような知見に鑑み、以下に説明するような本実施形態に想到した。

【0025】

(本実施形態)

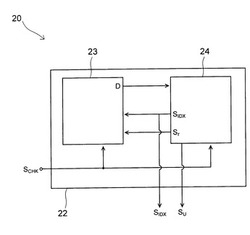

図3は、本実施形態に係る電子回路の回路図である。

【0026】

この電子回路20は、配線基板22に実装された第1の半導体素子23と第2の半導体素子24とを有し、通常モードと診断モードの二種類の動作を行うことができる。

【0027】

このうち、通常モードは、電子回路20が製品仕様に従って動作している状態であり、診断モードは、ホールドエラーが発生しているかどうかを電子回路20自身が診断する状態である。

【0028】

通常モードと診断モードの切り替えは、第1の半導体素子23と第2の半導体素子24の各々に診断モード信号SCHKを入力することで行われる。

【0029】

その診断モード信号SCHKが「0」のときに電子回路20は通常モードとなり、第1の半導体素子23から第2の半導体素子24に通常データDが送信される。通常データDは、通常モード時に第2の半導体素子24で処理の対象となるデータであって、所定のビット数を有する。

【0030】

一方、診断モード信号SCHKが「1」になると電子回路20は診断モードとなる。そして、第2の半導体素子24から第1の半導体素子23に対して後述のインデックス制御信号SIDXと開始信号Srが送信される。

【0031】

図4は、第1の半導体素子23の機能ブロック図である。

【0032】

図4に示すように、第1の半導体素子23は、第1の論理回路27、テストパターン生成器28、セレクタ制御回路29、第1〜第3のセレクタ31〜33、及び第1〜第3の送信側フリップフロップFFt1〜FFt3を有する。

【0033】

第1の論理回路27は、通常モード時に要する通常データDの各ビットD[0]〜D[2]を生成し、それらを第1〜第3のセレクタ31〜33に出力する。

【0034】

また、テストパターン生成器28は、診断モード信号SCHKが「1」になったときにイネーブルになる。イネーブルになったテストパターン生成器28は、開始信号Srが「1」になったときに診断モード時に要するテストパターンTPを生成し、それを第1〜第3のセレクタ31〜33に出力する。

【0035】

なお、開始信号Srが「0」のときは、テストパターン生成器28はテストパターンTPの生成を停止する。

【0036】

そのテストパターンTPはシリアルデータであり、本実施形態では〔010〕の配列を有する。テストパターンTPの各ビット「0」、「1」、「0」は、クロック信号CLKに同期してテストパターン生成器28から出力される。

【0037】

セレクタ制御回路29には、上記のインデックス制御信号SIDXと診断モード信号SCHKが入力される。

【0038】

インデックス制御信号SIDXは、第1〜第3の送信側フリップフロップFFt1〜FFt3のいずれか一を指定するための2ビットの信号である。例えば、インデックス制御信号SIDXが「01」のときは第1の送信側フリップフロップFFt1が指定され、「10」のときは第2の送信側フリップフロップFFt2が指定され、「11」のときは第3の送信側フリップフロップFFt3が指定される。

【0039】

セレクタ制御回路29は、診断モード信号SCHKが「1」のときにイネーブルとなり、第1〜第3のセレクタ31〜33の各々に2ビットの選択信号SSELを出力する。

【0040】

そして、第1〜第3のセレクタ31〜33の各々は、この選択信号SSELに応じて、各ビットD[0]〜D[2]とテストパターンTPのいずれか一方を選択して後段に出力する。その選択により、第1〜第3のセレクタ31〜33のうち、インデックス制御信号SIDXで指定されるフリップフロップFFt1〜FFtに接続されているセレクタではテストパターンTPが出力され、残りのセレクタでは各ビットD[0]〜D[2]が出力される。

【0041】

この結果、診断モード時では、第1〜第3の送信側フリップフロップFFt1〜FFt3のうち、インデックス制御信号SIDXで指定されるフリップフロップにはテストパターンTPが入力され、残りのフリップフロップには各ビットD[0]〜D[2]が入力される。

【0042】

第1〜第3の送信側フリップフロップFFt1〜FFt3はDQフリップフロップであって、これらの各々に同一のクロック信号CLKが入力される。

【0043】

そして、第1〜第3の送信側フリップフロップFFt1〜FFt3は、上記の各ビットD[0]〜D[2]とテストパターンTPのいずれかをラッチし、クロック信号CLKの立ち上がりを受けて各ビットD[0]〜D[2]とテストパターンTPを第2の半導体素子24に出力する。

【0044】

図5は、第2の半導体素子24の機能ブロック図である。

【0045】

図5に示すように、第2の半導体素子24は、第1〜第3の遅延回路41〜43、フリップフロップ群44、タイミング調整器45、比較器46、結果通知器47、及び3ステートカウンタ48を有する。

【0046】

このうち、第1〜第3の遅延回路41〜43の入力端子は、それぞれ第1〜第3の送信側フリップフロップFFt1〜FFt3のQ端子と電気的に接続される。

【0047】

図6は、第1の遅延回路41の回路図である。なお、第2の遅延回路42と第3の調整器43の回路図は、第1の遅延回路41と同じなので、ここでは省略する。

【0048】

図6に示すように、第1の遅延回路41は、チェインバッファ51とセレクタ55とを有する。

【0049】

診断モード時のチェインバッファ51には、上記の第1の送信側フリップフロップFFt1から出力された通常データDのビットD[0]が入力される。なお、通常モード時のチェインバッファ51には、第1の送信側フリップフロップFFt1からテストパターンTPが入力される。

【0050】

そのチェインバッファ51は、互いに直列に接続された第1〜第3のバッファ52〜54と、第1〜第4の出力線51a〜51dとを有する。これらのうち、第1〜第3の出力線51a〜51cは第1〜第3のバッファ52〜54の入力端に接続され、第4の出力線51dは第3のバッファ54の出力端に接続される。

【0051】

各々のバッファ52〜54においては、入力端から所定の遅延時間αをおいて出力端にデータが現れる。その結果、第1〜第4の出力線51a〜51dの各々には、第1のバッファ52の入力端から計ってそれぞれα、2α、3αの遅延が生じることになる。

【0052】

そして、セレクタ55の入力側は、第1〜第4の出力線51a〜51dが接続される。また、第1〜第4の出力線51a〜51dのいずれか一が2ビットのタイミング指定信号Scにより選択され、セレクタ55の出力側から出力される。

【0053】

図の例では、タイミング指定信号Scの各々の値「00」、「01」、「10」、「11」に対応し、第1〜第4の出力線51a〜51dのいずれか一が選択され、ビットD[0]を所定の遅延時間だけ遅延して出力することができる。

【0054】

これと同様に、第2の遅延回路42はと第3の遅延回路43の各々では、第2の送信側フリップフロップFFt2と第3の送信側フリップフロップFFt3から出力されたビットD[1]、D[2]を遅延させることができる。

【0055】

再び図5を参照する。

【0056】

フリップフロップ群44は、第1〜第3の受信側フリップフロップFFr1〜FFr3を有する。

【0057】

第1〜第3の受信側フリップフロップFFr1〜FFr3は、DQフリップフロップであって、各々のD端子に第1〜第3の遅延回路41〜43の各々の出力が入力されると共に、クロック端子に同一のクロック信号CLKが入力される。

【0058】

そして、第1〜第3の受信側フリップフロップFFr1〜FFr3は、第1〜第3の遅延回路41〜43の各々の出力データをラッチし、クロック信号CLKの立ち上がりを受けてその出力データを後段に出力する。

【0059】

既述のように、電子回路20が診断モードの場合には、第1の遅延回路41にはテストパターンTPが入力される。よって、この場合は、第1の遅延回路41において0、α、2α、3αのいずれかの遅延時間だけ遅延されたテストパターンTPが第1の受信側フリップフロップFFr1にラッチされる。

【0060】

また、通常モードのときは、第1の遅延回路41には通常データDのビットD[0]が入力され、第1の遅延回路41で遅延時間0、α、2α、3αのいずれかだけ遅延されたビットD[0]が第1の受信側フリップフロップFFr1にラッチされる。

【0061】

これと同様に、第2の受信側フリップフロップFFr2と第3の受信側フリップフロップFFr3においても、各調整器42、43のいずれかで遅延時間0、α、2α、3αだけ遅延されたデータ(D[1]、D[2]、TP)がラッチされる。

【0062】

そして、第1〜第3の受信側フリップフロップFFr1〜FFr3にラッチされていたデータは、第2の論理回路75とセレクタ76に出力される。

【0063】

このうち、第2の論理回路75は、第1〜第3の受信側フリップフロップFFr1〜FFr3から出力される通常データDの各ビット各ビットD[0]〜D[2]を受けて、通常モード時に通常データDに対して所定の処理を行う。

【0064】

一方、セレクタ76は、インデックス制御信号SIDXを受けて、第1〜第3の受信側フリップフロップFFr1〜FFr3のいずれかから出力されたデータを後段に出力する。

【0065】

インデックス制御信号SIDXは、既述のように第1〜第3の送信側フリップフロップFFt1〜FFt3を指定する他、第1〜第3の受信側フリップフロップFFr1〜FFr3のいずれか一を指定するための信号でもある。

【0066】

例えば、インデックス制御信号SIDXが「01」のときは第1の受信側フリップフロップFFr1が指定され、「10」のときは第2の受信側フリップフロップFFr2が指定され、「11」のときは第3の受信側フリップフロップFFr3が指定される。

【0067】

この結果、セレクタ76の出力側には、インデックス制御信号SIDXで指定された第1〜第3の受信側フリップフロップFFr1〜FFr3のいずれか一の出力信号が出力されることになる。

【0068】

一方、比較器46は、第1〜第3の遅延フリップフロップFFD1〜FFD3と、第1〜第3のXORゲート77〜79を有する。

【0069】

第1〜第3の遅延フリップフロップFFD1〜FFD3は、例えばDQフリップフロップであって、それぞれに共通のクロック信号CLKの立ち上がりによってラッチしていたデータを後段に出力する。

【0070】

これにより、第1〜第3の遅延フリップフロップFFD1〜FFD3の各々には、クロック信号CLKに同期して、セレクタ76から出力されたデータがシリアルに取り込まれる。

【0071】

そして、XORゲート77〜79の各々は、上記の第1〜第3の遅延フリップフロップFFD1〜FFD3の各々の出力信号と、テストパターンTPの期待値「0」、「1」、「0」との排他的論理和をとる。これらの期待値は、遅延フリップフロップFFD1〜FFD3の各々にラッチされるテストパターンTPの各ビットの期待値である。

【0072】

そして、XORゲート77〜79の各々は、排他的論理和をとることで得られた第1〜第3の比較信号Sp1〜Sp3を結果比較器47に出力する。

【0073】

結果比較器47は、ORゲート81とANDゲート82とを備える。

【0074】

このうち、ORゲート81は、第1〜第3の比較信号Sp1〜Sp3の論理和をとり、その結果をANDゲート82に出力する。

【0075】

そのANDゲート82は、3ステートカウンタ48から出力された状態信号Ssと上記のORゲート81の出力信号との論理和をとり、それを結果信号Shとして後段に出力する。

【0076】

3ステートカウンタ48は、診断モード信号SCHKが「1」のときにイネーブルとなり、クロック信号CLKに同期して内部状態が「0」、「1」、「0」の順に遷移する。その3ステートカウンタ48から出力される状態信号Ssは、内部状態が最初の「0」と「1」のときには「0」であり、内部状態が最後の「0」になったときに「1」となる。

【0077】

また、3ステートカウンタ48には、結果信号Shと開始信号Srが入力される。3ステートカウンタ48は、結果信号Shが「1」になったときに状態遷移が停止し、再開信号Srが「1」になったときに状態遷移が再開する。

【0078】

その3ステートカウンタ48から出力された状態信号Ssは、インデックスカウンタ85に入力される。

【0079】

インデックスカウンタ85は、診断モード信号SCHKが「1」のときにイネーブルとなる。そして、イネーブル時のインデックスカウンタ85は、状態信号Ssを計数し、その計数結果を既述の2ビットのインデックス制御信号SIDXとして出力する。

【0080】

更に、3ステートカウンタ48から出力された上記の状態信号Ssはタイミング調整器45にも入力される。

【0081】

図7は、タイミング調整器45の回路図である。

【0082】

図7に示すように、タイミング調整器45は、第1〜第3のタイミング指定器101〜103と、第1〜第6のANDゲート111〜116と、ORゲート120とを備える。

【0083】

このうち、第1のANDゲート111は、2ビットのインデックス制御信号SIDXの下位ビットSIDX[0]の反転信号と、そのインデックス制御信号SIDXの上位ビットSIDX[1]との論理積をとり、その結果をイネーブル信号Seとして出力する。

【0084】

また、第2のANDゲート112は、下位ビットSIDX[0]と上位ビットSIDX[1]の反転信号との論理積をとり、その結果をイネーブル信号Seとして出力する。

【0085】

そして、第3のANDゲート113は、下位ビットSIDX[0]と上位ビットSIDX[1]との論理積をとり、その結果をイネーブル信号Seとして出力する。

【0086】

これにより、同一のインデックス制御信号SIDXの下では、第1〜第3のANDゲート111〜113のうちの一つのみのイネーブル信号Seが「1」となり、それ以外のイネーブル信号Seは「0」となる。

【0087】

例えば、インデックス制御信号SIDXが「01」のときは第1のANDゲート111が「1」となり、他のANDゲート112、113の出力は「0」となる。

【0088】

そして、第1〜第3のタイミング指定器101〜103のうち、「1」となったイネーブル信号Seが入力されたタイミング指定器のみがイネーブルとなる。

【0089】

また、ORゲート120は、各タイミング指定器101〜103から出力される後述の比較信号Stの論理和をとり、その結果を開始信号Srとして出力する。その開始信号Srは、各タイミング指定器101〜103の比較信号Stのいずれか一が「1」のときに「1」となり、それ以外のときには「0」となる。

【0090】

更に、第4〜第6のANDゲート114〜116は、それぞれ状態信号Ssと第1〜第3の比較信号Sp1〜Sp3との論理積をとり、その結果をそれぞれ第1〜第3のタイミング指定器101〜103に出力する。

【0091】

図8は、第1〜第3のタイミング指定器101〜103の回路図である。

【0092】

図8に示すように、第1〜第3のタイミング指定器101〜103は、タイミングコード生成器61と、第1〜第3のフリップフロップFF1〜FF3と、比較器67とを備える。

【0093】

このうち、タイミングコード生成器61には、上記した第4〜第6のANDゲート114〜116の出力が入力される。

【0094】

そのタイミングコード生成器61は、ORゲート62とカウンタ63とを有する。

【0095】

ORゲート62は、第4〜第6のANDゲート114〜116の各々の出力信号の論理和をとり、それをカウンタ63に出力する。

【0096】

カウンタ63は、イネーブル信号Seによりイネーブル状態となる。イネーブル状態となったカウンタ63は、ORゲート62の出力が「1」になったときにカウントアップし、その計数結果を2ビットのタイミング指定信号Scとして出力する。

【0097】

第1〜第3のフリップフロップFF1〜FF3は、2ビットの信号をラッチするものであって、クロック信号CLKの立ち上がりによってラッチしていた信号を後段に出力する。

【0098】

これにより、第1〜第3のフリップフロップFF1〜FF3の各々には、クロック信号CLKに同期して、タイミング指定信号Scが順に取り込まれる。

【0099】

比較器67は、上記の第2のフリップフロップFF2と第3のフリップフロップFF3の出力信号を比較し、これらが異なる値であれば比較信号Stを「1」にし、これらが同じ値であれば比較信号Stを「0」にする。

【0100】

このように複数のフリップフロップFF1〜FF3を接続し、最終のフリップフロップFF3の入力と出力とを比較することで、カウンタ63においてタイミング指定信号Scが切り替わってから時間をおいて比較信号Stを切り替えることができる。これにより、タイミング指定信号Scによってセレクタ55(図6参照)が確実に切り替わった後に、タイミング調整器45(図7参照)から開始信号Srを出力することができる。

【0101】

再び図5を参照する。

【0102】

上記した第1〜第3のタイミング指定器101〜103から出力されたタイミング指定信号Scは、それぞれ第1〜第3の遅延回路41〜43に入力される。

【0103】

一方、ANDゲート82から出力された結果信号Shは、ANDゲート90に入力される。

【0104】

ANDゲート90の入力側には、その結果信号Shの他に、回数カウンタ91から出力された計数信号SNも入力される。

【0105】

回数カウンタ91は、インデックス制御信号SIDXに基づいて、第1〜第3の受信側フリップフロップFFr1〜FFr3の全てにテストパターンTPが1回供給されたら計数結果を1だけインクリメントする。例えば、第1〜第3の受信側フリップフロップFFr1〜FFr3の全てにテストパターンTPが2回供給されたら回数カウンタ91の計数値nは2となり、3回供給されたら計数値nは3となる。

【0106】

このように、回数カウンタ91は、第1〜第3の受信側フリップフロップFFr1〜FFr3の全てにテストパターンTPが供給された回数nを計数するものであり、その回数nが予定回数Nよりも少ないときは、回数カウンタ91は計数信号SNを「0」とする。そして、その回数nが予定回数Nに等しくなったとき、回数は計数信号SNを「1」とする。

【0107】

ANDゲート90は、これらの信号SN、Shの論理積をとり、その結果をユーザへの通知信号SUとして出力する。

【0108】

次に、この電子回路20を用いたタイミング調整方法について説明する。

【0109】

図9は、本実施形態に係るタイミング調整方法について説明するためのフローチャートである。

【0110】

最初のステップP1では、電子回路20を通常モードから診断モードに切り替える。

【0111】

本ステップは、ユーザが診断モード信号SCHKを「0」から「1」に切り替えることで行われる。

【0112】

次に、ステップP2に移り、上記の診断モード信号SCHKによってイネーブルとなったテストパターン生成器28(図4参照)が、クロック信号CLKに同期してテストパターンTPの各ビット「0」、「1」、「0」を生成する。

【0113】

そのテストパターンTPは、第1〜第3の送信側フリップフロップFFt1〜FFt3の各々にラッチされる。その後、クロック信号CLKの立ち上がりを受けた送信側フリップフロップFFt1〜FFt3が、テストパターンTPを第1〜第3の受信側フリップフロップFFr1〜FFr3(図5参照)の各々に出力する。

【0114】

図10は、各受信側フリップフロップFFr1〜FFr3の各々に出力されるテストパターンTPの一例を示す模式図である。

【0115】

図10において、「FF Index」とは、インデックス制御信号SIDXを10進数で表したときの値である。図10に示されるように、テストパターンTPは、各受信側フリップフロップFFr1〜FFr3の各々において同一のシリアルデータ〔010〕である。そして、テストパターンTPの各ビット「0」、「1」、「0」は、クロック信号CLKに同期して、各受信側フリップフロップFFr1〜FFr3にラッチされる。

【0116】

また、各受信側フリップフロップFFr1〜FFr3のうちの一つに対して診断が行われているときは、他の受信側フリップフロップはdon't care (X)となる。

【0117】

本実施形態では、図6に示したように、第1〜第3の遅延回路41〜43によってテストパターンTPに0、α、2α、3αのいずれかの遅延時間が生ずることになる。これらのいずれの遅延時間が生ずるかは第1〜第3の受信側フリップフロップFFr1〜FFr3の各々に個別に設定されるが、診断モードの開始直後では全てのフリップフロップFFr1〜FFr3について遅延時間は0とされる。

【0118】

なお、このように遅延時間を0にするには、予めカウンタ63(図8参照)をリセットしてタイミング指定信号Scを「00」にしておけばよい。

【0119】

また、診断モードの開始前にインデックスカウンタ85(図5参照)は予めリセットされており、インデックスカウンタ85から出力されるインデックス制御信号SIDXは「01」となっている。

【0120】

そのため、セレクタ76(図5参照)では、「01」に対応する第1の受信側フリップフロップFFr1の出力信号が選択され、第1の受信側フリップフロップFFr1に対するホールドエラーの有無の判断とタイミング調整とが最初に行われる。なお、第2の受信側フリップフロップFFr2と第3の受信側フリップフロップFFr3に対するタイミング調整は、インデックス制御信号SIDXがインクリメントすることにより、第1の受信側フリップフロップFFr1と同様にして行われる。

【0121】

次に、ステップP3に移り、比較器46において、第1の受信側フリップフロップFFr1から出力されたテストパターンTPと、そのテストパターンTPの期待値「0」、「1」、「0」とが一致するか否かを調べる。

【0122】

ここで、診断モード時においては、第1の受信側フリップフロップFFr1にラッチされていたテストパターンTP(〔010〕)の各ビットがクロック信号CLKに同期して各第1〜第3の遅延フリップフロップFFD1〜FFD3にシリアルに取り込まれる。

【0123】

よって、第1の受信側フリップフロップFFr1においてホールドエラーが発生していなければ、第1〜第3の遅延フリップフロップFFD1〜FFD3には、それぞれテストパターンTPの各ビット「0」、「1」、「0」が取り込まれるはずである。

【0124】

一方、第1の受信側フリップフロップFFr1においてホールドエラーが発生している場合は、第1の受信側フリップフロップFFr1から出力されるテストパターンTPのいずれかのビットにおいてデータが反転する。

【0125】

そこで、本ステップでは、そのようなビットの反転の有無を調べるために、XORゲート77〜79の各々において、第1〜第3の遅延フリップフロップFFD1〜FFD3の各々の出力信号と期待値「0」、「1」、「0」との排他的論理和をとる。

【0126】

ここで、ホールドエラーが原因のデータの反転がテストパターンTPのいずれかのビットで発生している場合(NG時)は、第1〜第3の比較結果信号Sp1〜Sp3のいずれかが「1」となる。

【0127】

そして、そのようなデータの反転がない場合(OK時)には、第1〜第3の比較結果信号Sp1〜Sp3の全てが「0」となる。

【0128】

また、データの反転の有無によらず、上記のように第1〜第3の遅延フリップフロップFFD1〜FFD3の各々にテストパターンTPの三つの全てのビットがラッチされたときは、3ステートカウンタ48の状態信号Ssが「1」となる。

【0129】

よって、ホールドエラーが発生しているときはANDゲート82の結果信号Shが「1」となり、ホールドエラーが発生していないときはその結果信号Shが「0」となる。

【0130】

上記のように結果信号Shが「1」となった場合(NG時)であって、且つ、回数カウンタ91による計数nが予定回数Nを越えていない場合はステップP4に移る。

【0131】

本ステップでは、「1」となった結果信号Shを受けて3ステートカウンタ48がその動作を停止する。また、このタイミングではカウンタ63(図8参照)のカウント値が変わっていないため、第1〜第3のフリップフロップFF1〜FF3に同一のタイミング指定信号Scがラッチされている。このため、本ステップでは、各タイミング指定器101〜103から出力される比較信号Stが「0」になるため開始信号Srも「0」になり、テストパターン生成器28におけるテストパターンTPの生成が停止する。

【0132】

次に、ステップP5に移り、第1の受信側フリップフロップFFr1がデータを受け取るタイミングを調整する。

【0133】

その調整は、タイミング調整器45の第1〜第3のタイミング指定器101〜103(図8参照)において次のように行われる。

【0134】

ホールドエラーが発生したときは、上記のように、第1〜第3の比較結果信号Sp1〜Sp3のいずれかが「1」となる。また、各遅延フリップフロップFFD1〜FFD3の各々にテストパターンTPの三つの全てのビットがラッチされたときには状態信号Ssが「1」となる。

【0135】

よって、この場合は、第4〜第6のANDゲート114〜116のいずれかの出力が1となり、カウンタ63が1だけカウントアップされる。これにより、予め「00」にリセットされていたタイミング指定信号Scが「01」となるため、第1の遅延回路41(図6参照)のセレクタ55が第2の出力線51bを選択するようになる。

【0136】

その結果、第1の遅延回路41に入力される信号が、遅延時間αだけ遅れて第1の受信側フリップフロップFFr1に出力されるようになり、信号のタイミング調整が行われる。

【0137】

この後は、上記したステップP2に再び戻る。

【0138】

ここで、上記のステップP4では3ステートカウンタ48がその動作を停止していたので、インデックス制御信号SIDXは前回と変わっておらず、前回と同一の第1の受信側フリップフロップFFr1に対してタイミング調整が行われる。

【0139】

そして、ステップP5を行う度にタイミング調整器45のカウンタ63が1ずつカウントアップし、第1の遅延回路41における遅延時間をα、2α、3αの順に長くすることができる。

【0140】

一方、ステップP3において結果信号Shが「0」となった場合(OK時)であって、且つ、回数カウンタ91による計数nが予定回数Nを越えていない場合もステップP2に戻る。

【0141】

そして、上記のようにステップP3を繰り返し行い、回数カウンタ91による計数nが予定回数Nに等しくなった場合には、ステップP6に移る。

【0142】

ステップP6では、n=Nとなったため回数カウンタ91から出力される計数信号SNが「1」となる。その結果、ANDゲート90から出力される通知信号SUは、結果信号Shと同一となる。

【0143】

上記のように、結果信号Shは、第1〜第3の受信側フリップフロップFFr1〜FFr3のいずれかにおいてホールドエラーが発生したときに「1」となる。

【0144】

よって、ユーザは、通知信号SUが「1」のときに第1〜第3の受信側フリップフロップFFr1〜FFr3のいずれかにおいてホールドエラーが発生したことを認識できる。

【0145】

以上により、本実施形態に係るタイミング調整方法に基本ステップを終了する。

【0146】

上記した本実施形態によれば、図6に示したように、第1〜第3の遅延回路41〜43によって、各第1〜第3の受信側フリップフロップFFr1〜FFr3に入力される通常データDの各ビットD[0]、D[1]、D[2]を遅延させる。

【0147】

図11は、このようにビットD[0]を遅延させた場合における、第1の送信側フリップフロップFFt1と第1の受信側フリップフロップFFr1のタイミングチャートである。

【0148】

図11に示すように、タイミング調整をしたことで、第1の受信側フリップフロップFFr1がビットD[0]を受信するタイミングは、第1の送信側フリップフロップFFt1がビットD[0]を送信するタイミングよりも所定の時間(例えばα)だけ遅れる。

【0149】

よって、クロックスキューが原因で第1の受信側フリップフロップFFr1にクロック信号CLKが遅れて入力されても、クロック信号CLKの立ち上がりから十分に長い期間Tを経過した後に、フリップフロップFFr1に入力されるビットD[0]が反転する。その結果、当該期間Tが短い場合に発生するホールドエラーを防止でき、電子回路20の信頼性を高めることができる。

【0150】

更に、上記したステップP3では、ホールドエラーが発生していない場合(OK時)であっても、各第1〜第3の受信側フリップフロップFFr1〜FFr3のそれぞれの診断回数が予め定めた回数Nを越えていない場合には診断を続ける。

【0151】

これにより、OKと判断された受信側フリップフロップが、その後の温度変化によってNGとなるのを見落とす危険性を低減でき、診断の正確性を期することができる。

【0152】

また、電子回路20の外部に通知信号SUとインデックス制御信号SIDXと出力し、ユーザがこれらの信号を監視できるようにしてもよい。

【0153】

この場合、通知信号SUが「1」で受信側フリップフロップFFr1〜FFr3のいずれかにホールドエラーがある場合、どの受信側フリップフロップにホールドエラーがあるかをユーザがインデックス制御信号SIDXに基づいて判断することができる。

【0154】

図12は、これらの信号SU、SIDXを外部に引き出す第1の端子150と第2の端子151を設けた場合の電子回路20の模式図である。

【0155】

この場合、電子回路20に第3の端子153を設け、その第3の端子153から電子回路20に診断モード信号SCHKを入力するのが好ましい。

【0156】

図13は、上記とは別の方法による各信号SU、SIDXの外部への引き出し方を説明するための電子回路20の模式図である。

【0157】

この例では、上記の図12のように各信号SU、SIDXに専用の端子150、151を設けるのではなく、第2の論理回路75(図5参照)の出力データDiを外部に出力するのに使用される第4の端子154と第5の端子155を流用する。なお、出力データDiは、第1の半導体素子23から出力された通常データDに対し、第2の論理回路75で所定の処理を施してなるデータである。

【0158】

この場合、各端子154、155から各信号SU、SIDXと出力データDiのどちらを出力するかは、第1のセレクタ161と第2のセレクタ162により選択される。

【0159】

第1のセレクタ161は、診断モード信号SCHKが「0」のときに出力データDiを選択し、診断モード信号SCHKが「1」のときに通知信号SUを選択する。

【0160】

そして、第2のセレクタ162は、診断モード信号SCHKが「0」のときに出力データDiを選択し、診断モード信号SCHKが「1」のときにインデックス制御信号SIDXを選択する。

【0161】

このように、第4の端子154と第5の端子155に対して出力データDiの他に各信号SU、SIDXの出力機能を担わせることにより、端子数が増大するのを防止して電子回路20が大型化するのを抑制することができる。

【0162】

以上説明した各実施形態に関し、更に以下の付記を開示する。

【0163】

(付記1) クロック信号に同期してテストパターンを出力する送信側フリップフロップと、

前記送信側フリップフロップから出力された前記テストパターンを所定の遅延時間だけ遅延させて出力する遅延回路と、

前記遅延回路から出力された前記テストパターンをラッチすると共に、前記クロック信号に同期して前記テストパターンを出力する受信側フリップフロップと、

前記受信側フリップフロップから出力された前記テストパターンと、該テストパターンの期待値とを比較して、前記テストパターンと前記期待値とが一致するか否かを示す比較信号を出力する比較器と、

前記比較信号が入力され、該比較信号によって前記テストパターンと前記期待値とが一致していないことが判った場合に、前記遅延回路における前記遅延時間を調整するタイミング調整器と、

を有することを特徴とする電子回路。

【0164】

(付記2) 前記受信側フリップフロップが複数設けられ、

制御信号に基づいて、前記受信側フリップフロップのいずれか一の出力を選択して前記比較器に出力する第1のセレクタと、

前記第1のセレクタに対して前記制御信号を出力する第1のカウンタとを更に有することを特徴とする付記1に記載の電子回路。

【0165】

(付記3) 前記テストパターンはシリアルデータであり、

前記比較器は、前記テストパターンの各々のビットをラッチする複数のフリップフロップを備え、

前記複数のフリップフロップの全てに前記テストパターンの全てのビットがラッチされたときに「1」となり、それ以外のときに「0」となる状態信号を出力するステートカウンタとを更に有し、

前記第1のカウンタは、前記状態信号を計数し、該計数結果を前記制御信号として出力することを特徴とする付記2に記載の電子回路。

【0166】

(付記4) 前記比較器は、複数の前記フリップフロップの各々の出力と、前記期待値の各々のビットとの排他的論理和を複数の前記比較信号として出力する複数の排他的論理和回路とを有し、

複数の前記比較信号の論理和をとる論理和回路と、

前記論理和回路の出力と前記状態信号との論理積をとる第1の論理積回路と、

複数の前記受信側フリップフロップの全てが前記テストパターンを受けたときに1だけインクリメントして、計数結果が予め定められた予定回数になったときに「1」になる計数信号を出力する第2のカウンタと、

前記第1の論理積回路の出力と前記計数信号との論理積を通知信号として外部に出力する第2の論理積回路とを更に有することを特徴とする付記3に記載の電子回路。

【0167】

(付記5) 前記通知信号が出力される第1の端子と、

前記制御信号が出力される第2の端子とを更に有することを特徴とする付記4に記載の電子回路。

【0168】

(付記6) 前記遅延回路は、前記テストパターンが入力される直列に接続された複数のバッファと、タイミング指定信号によって複数の前記バッファの各々の出力のいずれか一を選択して前記受信側フリップフロップに出力する第2のセレクタとを有することを特徴とする付記1〜5のいずれかに記載の電子回路。

【0169】

(付記7) 前記タイミング調整器は、前記比較信号によって前記テストパターンと前記期待値とが一致しないことが判った場合にカウントアップする第3のカウンタを備え、

前記第3のカウンタの計数結果が前記タイミング指定信号として前記第2のセレクタに出力されることを特徴とする付記6に記載の電子回路。

【0170】

(付記8) 通常モード時に通常データを生成する第1の論理回路と、

診断モード時に前記テストパターンを生成するテストパターン生成器と、

前記通常モード時に前記通常データを選択して前記送信側フリップフロップに出力し、前記診断モード時に前記テストパターンを選択して前記送信側フリップフロップに出力する第3のセレクタと、

前記通常モード時において、前記受信側フリップフロップから出力された前記通常データが入力される第2の論理回路とを更に有することを特徴とする付記1〜7のいずれかに記載の電子回路。

【0171】

(付記9) 配線基板と、

前記配線基板に実装された第1の半導体素子と第2の半導体素子とを更に有し、

前記第1の半導体素子に前記送信側フリップフロップが設けられ、

前記第2の半導体素子に、前記遅延回路、前記受信側フリップフロップ、前記比較器、及び前記タイミング調整器が設けられたことを特徴とする付記1〜8のいずれかに記載の電子回路。

【0172】

(付記10) 送信側フリップフロップが遅延回路にテストパターンを出力して、前記遅延回路において所定の遅延時間だけ遅延された前記テストパターンを受信側フリップフロップがラッチするステップと、

クロック信号に同期して前記受信側フリップフロップから出力された前記テストパターンと、該テストパターンの期待値とが一致するか否かを調べるステップと、

前記テストパターンと前記期待値とが一致しないことが判った場合に、前記遅延回路における前記遅延時間を調整するステップと、

を有することを特徴とする電子回路のタイミング調整方法。

【符号の説明】

【0173】

1、20…電子回路、2、22…配線基板、3、23…第1の半導体素子、4、24…第2の半導体素子、27…第1の論理回路、28…テストパターン生成器、29…セレクタ制御回路、31〜33…第1〜第3のセレクタ、41〜43…第1〜第3の遅延回路、44…フリップフロップ群、45…タイミング調整器、46…比較器、47…結果通知器、48…3ステートカウンタ、51…チェインバッファ、51a〜51c…第1〜第3の出力線、52〜54…第1〜第3のバッファ、55…セレクタ、61…タイミングコード生成器、62…ORゲート、63…カウンタ、67…比較器、75…第2の論理回路、76…セレクタ、77〜79…第1〜第3のXORゲート、81…ORゲート、82…ANDゲート、85…インデックスカウンタ、90…ANDゲート、91…回数カウンタ、101〜103…第1〜第3のタイミング指定器、111〜116…第1〜第6のANDゲート、120…ORゲート、150…第1の端子、151…第2の端子、153…第3の端子、154…第4の端子、155…第5の端子、161…第1のセレクタ、162…第2のセレクタ。

【技術分野】

【0001】

本発明は、電子回路及びそのタイミング調整方法に関する。

【背景技術】

【0002】

複数のフリップフロップを備えた電子回路では、配線遅延等が原因で各フリップフロップに異なるタイミングでクロック信号が到達することがある。そのような現象は、クロックスキューと呼ばれる。

【0003】

クロックスキューが発生すると、フリップフロップへの入力信号とクロック信号の入力タイミングが略同時になり、入力信号とは逆のレベルの信号がフリップフロップにおいてラッチされるホールドエラーが生じてしまう。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002−204222号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

電子回路及びそのタイミング調整方法において、フリップフロップのホールドエラーを防止することを目的とする。

【課題を解決するための手段】

【0006】

以下の開示の一観点によれば、クロック信号に同期してテストパターンを出力する送信側フリップフロップと、前記送信側フリップフロップから出力された前記テストパターンを所定の遅延時間だけ遅延させて出力する遅延回路と、前記遅延回路から出力された前記テストパターンをラッチすると共に、前記クロック信号に同期して前記テストパターンを出力する受信側フリップフロップと、前記受信側フリップフロップから出力された前記テストパターンと、該テストパターンの期待値とを比較して、前記テストパターンと前記期待値とが一致するか否かを示す比較信号を出力する比較器と、前記比較信号が入力され、該比較信号によって前記テストパターンと前記期待値とが一致していないことが判った場合に、前記遅延回路における前記遅延時間を調整するタイミング調整器とを有する電子回路が提供される。

【0007】

また、その開示の一観点によれば、送信側フリップフロップが遅延回路にテストパターンを出力して、前記遅延回路において所定の遅延時間だけ遅延された前記テストパターンを受信側フリップフロップがラッチするステップと、クロック信号に同期して前記受信側フリップフロップから出力された前記テストパターンと、該テストパターンの期待値とが一致するか否かを調べるステップと、前記テストパターンと前記期待値とが一致しないことが判った場合に、前記遅延回路における前記遅延時間を調整するステップとを有する電子回路のタイミング調整方法が提供される。

【発明の効果】

【0008】

以下の開示によれば、ホールドエラーが原因で受信側フリップフロップから出力されたテストパターンが期待値と一致していないとき、遅延回路における遅延時間を調整することにより、ホールドエラーを解消することができる。

【図面の簡単な説明】

【0009】

【図1】図1は、予備的事項に係る電子回路の回路図である。

【図2】図2は、ホールドエラーについて説明するためのタイミングチャートである。

【図3】図3は、本実施形態に係る電子回路の回路図である。

【図4】図4は、本実施形態に係る第1の半導体素子の機能ブロック図である。

【図5】図5は、本実施形態に係る第2の半導体素子の機能ブロック図である。

【図6】図6は、本実施形態に係る第1の遅延回路の回路図である。

【図7】図7は、本実施形態に係るタイミング調整器の回路図である。

【図8】図8は、本実施形態に係る第1〜第3のタイミング指定器の回路図である。

【図9】図9は、本実施形態に係るタイミング調整方法について説明するためのフローチャートである。

【図10】図10は、本実施形態において、受信側フリップフロップの各々に出力されるテストパターンの一例を示す模式図である。

【図11】図11は、本実施形態に係る第1の送信側フリップフロップと第1の受信側フリップフロップのタイミングチャートである。

【図12】図12は、本実施形態に係る電子回路の模式図(その1)である。

【図13】図13は、本実施形態に係る電子回路の模式図(その2)である。

【発明を実施するための形態】

【0010】

本実施形態の説明に先立ち、本実施形態の基礎となる予備的事項について説明する。

【0011】

図1は、予備的事項に係る電子回路1の回路図である。

【0012】

この電子回路1は、配線基板2に実装された第1の半導体素子3と第2の半導体素子4と有する。

【0013】

このうち、第1の半導体素子3は第1のフリップフロップFF1と第2のフリップフロップFF2を有し、第2の半導体素子4は第3のフリップフロップFF3と第4のフリップフロップFF4を有する。

【0014】

これらのフリップフロップFF1〜FF4は、DQフリップフロップであって、ラッチしていたデータをクロック信号CLKに同期してQ端子から出力する。

【0015】

この電子回路1では、配線基板2を介して第1の半導体素子3と第2の半導体素子4との間でデータの送受信が行われる。

【0016】

例えば、第1のフリップフロップFF1から送信された第1のデータD1が第3のフリップフロップFF3に受信され、第4のフリップフロップFF4から送信された第2のデータD2が第2のフリップフロップFF2に受信される。

【0017】

図2は、電子回路1で発生し得るホールドエラーについて説明するためのタイミングチャートである。

【0018】

図2に示すように、第1のフリップフロップFF1は、クロック信号CLKの立ち上がりにより、ラッチしていた第1のデータD1を後段の第3のフリップフロップFF3に出力する。

【0019】

そして、第3のフリップフロップFF3は、クロック信号CLKの立ち上がりで上記の第1のデータD1を取り込んでラッチする。

【0020】

このとき、配線基板2における配線遅延が原因で、第1のフリップフロップFF1と第3のフリップフロップFF3にクロック信号CLKが異なるタイミングで到達することがある。

【0021】

こうなると、第3のフリップフロップFF3に入力される第1のデータD1の反転タイミングとクロック信号CLKの立ち上がりとが略同時となる。そのため、ラッチすべき第1のデータD1がHレベルであるにも関わらずLレベルにラッチしたり、逆にLレベルの第1のデータD1をHレベルにラッチしたりして、第3のフリップフロップFF3においてホールドエラーが発生する。

【0022】

その結果、第3のフリップフロップFF3から後段に出力される第1のデータD1が本来の論理レベルとは逆になり、電子回路1が正常に動作しなくなるという不都合を招いてしまう。

【0023】

また、ホールドエラーが発生したフリップフロップを特定するには、配線基板2の配線を外部に電気的に引き出して電子回路1をしらみつぶしに解析する必要があり、即座に不良解析を行うことも難しい。

【0024】

本願発明者は、このような知見に鑑み、以下に説明するような本実施形態に想到した。

【0025】

(本実施形態)

図3は、本実施形態に係る電子回路の回路図である。

【0026】

この電子回路20は、配線基板22に実装された第1の半導体素子23と第2の半導体素子24とを有し、通常モードと診断モードの二種類の動作を行うことができる。

【0027】

このうち、通常モードは、電子回路20が製品仕様に従って動作している状態であり、診断モードは、ホールドエラーが発生しているかどうかを電子回路20自身が診断する状態である。

【0028】

通常モードと診断モードの切り替えは、第1の半導体素子23と第2の半導体素子24の各々に診断モード信号SCHKを入力することで行われる。

【0029】

その診断モード信号SCHKが「0」のときに電子回路20は通常モードとなり、第1の半導体素子23から第2の半導体素子24に通常データDが送信される。通常データDは、通常モード時に第2の半導体素子24で処理の対象となるデータであって、所定のビット数を有する。

【0030】

一方、診断モード信号SCHKが「1」になると電子回路20は診断モードとなる。そして、第2の半導体素子24から第1の半導体素子23に対して後述のインデックス制御信号SIDXと開始信号Srが送信される。

【0031】

図4は、第1の半導体素子23の機能ブロック図である。

【0032】

図4に示すように、第1の半導体素子23は、第1の論理回路27、テストパターン生成器28、セレクタ制御回路29、第1〜第3のセレクタ31〜33、及び第1〜第3の送信側フリップフロップFFt1〜FFt3を有する。

【0033】

第1の論理回路27は、通常モード時に要する通常データDの各ビットD[0]〜D[2]を生成し、それらを第1〜第3のセレクタ31〜33に出力する。

【0034】

また、テストパターン生成器28は、診断モード信号SCHKが「1」になったときにイネーブルになる。イネーブルになったテストパターン生成器28は、開始信号Srが「1」になったときに診断モード時に要するテストパターンTPを生成し、それを第1〜第3のセレクタ31〜33に出力する。

【0035】

なお、開始信号Srが「0」のときは、テストパターン生成器28はテストパターンTPの生成を停止する。

【0036】

そのテストパターンTPはシリアルデータであり、本実施形態では〔010〕の配列を有する。テストパターンTPの各ビット「0」、「1」、「0」は、クロック信号CLKに同期してテストパターン生成器28から出力される。

【0037】

セレクタ制御回路29には、上記のインデックス制御信号SIDXと診断モード信号SCHKが入力される。

【0038】

インデックス制御信号SIDXは、第1〜第3の送信側フリップフロップFFt1〜FFt3のいずれか一を指定するための2ビットの信号である。例えば、インデックス制御信号SIDXが「01」のときは第1の送信側フリップフロップFFt1が指定され、「10」のときは第2の送信側フリップフロップFFt2が指定され、「11」のときは第3の送信側フリップフロップFFt3が指定される。

【0039】

セレクタ制御回路29は、診断モード信号SCHKが「1」のときにイネーブルとなり、第1〜第3のセレクタ31〜33の各々に2ビットの選択信号SSELを出力する。

【0040】

そして、第1〜第3のセレクタ31〜33の各々は、この選択信号SSELに応じて、各ビットD[0]〜D[2]とテストパターンTPのいずれか一方を選択して後段に出力する。その選択により、第1〜第3のセレクタ31〜33のうち、インデックス制御信号SIDXで指定されるフリップフロップFFt1〜FFtに接続されているセレクタではテストパターンTPが出力され、残りのセレクタでは各ビットD[0]〜D[2]が出力される。

【0041】

この結果、診断モード時では、第1〜第3の送信側フリップフロップFFt1〜FFt3のうち、インデックス制御信号SIDXで指定されるフリップフロップにはテストパターンTPが入力され、残りのフリップフロップには各ビットD[0]〜D[2]が入力される。

【0042】

第1〜第3の送信側フリップフロップFFt1〜FFt3はDQフリップフロップであって、これらの各々に同一のクロック信号CLKが入力される。

【0043】

そして、第1〜第3の送信側フリップフロップFFt1〜FFt3は、上記の各ビットD[0]〜D[2]とテストパターンTPのいずれかをラッチし、クロック信号CLKの立ち上がりを受けて各ビットD[0]〜D[2]とテストパターンTPを第2の半導体素子24に出力する。

【0044】

図5は、第2の半導体素子24の機能ブロック図である。

【0045】

図5に示すように、第2の半導体素子24は、第1〜第3の遅延回路41〜43、フリップフロップ群44、タイミング調整器45、比較器46、結果通知器47、及び3ステートカウンタ48を有する。

【0046】

このうち、第1〜第3の遅延回路41〜43の入力端子は、それぞれ第1〜第3の送信側フリップフロップFFt1〜FFt3のQ端子と電気的に接続される。

【0047】

図6は、第1の遅延回路41の回路図である。なお、第2の遅延回路42と第3の調整器43の回路図は、第1の遅延回路41と同じなので、ここでは省略する。

【0048】

図6に示すように、第1の遅延回路41は、チェインバッファ51とセレクタ55とを有する。

【0049】

診断モード時のチェインバッファ51には、上記の第1の送信側フリップフロップFFt1から出力された通常データDのビットD[0]が入力される。なお、通常モード時のチェインバッファ51には、第1の送信側フリップフロップFFt1からテストパターンTPが入力される。

【0050】

そのチェインバッファ51は、互いに直列に接続された第1〜第3のバッファ52〜54と、第1〜第4の出力線51a〜51dとを有する。これらのうち、第1〜第3の出力線51a〜51cは第1〜第3のバッファ52〜54の入力端に接続され、第4の出力線51dは第3のバッファ54の出力端に接続される。

【0051】

各々のバッファ52〜54においては、入力端から所定の遅延時間αをおいて出力端にデータが現れる。その結果、第1〜第4の出力線51a〜51dの各々には、第1のバッファ52の入力端から計ってそれぞれα、2α、3αの遅延が生じることになる。

【0052】

そして、セレクタ55の入力側は、第1〜第4の出力線51a〜51dが接続される。また、第1〜第4の出力線51a〜51dのいずれか一が2ビットのタイミング指定信号Scにより選択され、セレクタ55の出力側から出力される。

【0053】

図の例では、タイミング指定信号Scの各々の値「00」、「01」、「10」、「11」に対応し、第1〜第4の出力線51a〜51dのいずれか一が選択され、ビットD[0]を所定の遅延時間だけ遅延して出力することができる。

【0054】

これと同様に、第2の遅延回路42はと第3の遅延回路43の各々では、第2の送信側フリップフロップFFt2と第3の送信側フリップフロップFFt3から出力されたビットD[1]、D[2]を遅延させることができる。

【0055】

再び図5を参照する。

【0056】

フリップフロップ群44は、第1〜第3の受信側フリップフロップFFr1〜FFr3を有する。

【0057】

第1〜第3の受信側フリップフロップFFr1〜FFr3は、DQフリップフロップであって、各々のD端子に第1〜第3の遅延回路41〜43の各々の出力が入力されると共に、クロック端子に同一のクロック信号CLKが入力される。

【0058】

そして、第1〜第3の受信側フリップフロップFFr1〜FFr3は、第1〜第3の遅延回路41〜43の各々の出力データをラッチし、クロック信号CLKの立ち上がりを受けてその出力データを後段に出力する。

【0059】

既述のように、電子回路20が診断モードの場合には、第1の遅延回路41にはテストパターンTPが入力される。よって、この場合は、第1の遅延回路41において0、α、2α、3αのいずれかの遅延時間だけ遅延されたテストパターンTPが第1の受信側フリップフロップFFr1にラッチされる。

【0060】

また、通常モードのときは、第1の遅延回路41には通常データDのビットD[0]が入力され、第1の遅延回路41で遅延時間0、α、2α、3αのいずれかだけ遅延されたビットD[0]が第1の受信側フリップフロップFFr1にラッチされる。

【0061】

これと同様に、第2の受信側フリップフロップFFr2と第3の受信側フリップフロップFFr3においても、各調整器42、43のいずれかで遅延時間0、α、2α、3αだけ遅延されたデータ(D[1]、D[2]、TP)がラッチされる。

【0062】

そして、第1〜第3の受信側フリップフロップFFr1〜FFr3にラッチされていたデータは、第2の論理回路75とセレクタ76に出力される。

【0063】

このうち、第2の論理回路75は、第1〜第3の受信側フリップフロップFFr1〜FFr3から出力される通常データDの各ビット各ビットD[0]〜D[2]を受けて、通常モード時に通常データDに対して所定の処理を行う。

【0064】

一方、セレクタ76は、インデックス制御信号SIDXを受けて、第1〜第3の受信側フリップフロップFFr1〜FFr3のいずれかから出力されたデータを後段に出力する。

【0065】

インデックス制御信号SIDXは、既述のように第1〜第3の送信側フリップフロップFFt1〜FFt3を指定する他、第1〜第3の受信側フリップフロップFFr1〜FFr3のいずれか一を指定するための信号でもある。

【0066】

例えば、インデックス制御信号SIDXが「01」のときは第1の受信側フリップフロップFFr1が指定され、「10」のときは第2の受信側フリップフロップFFr2が指定され、「11」のときは第3の受信側フリップフロップFFr3が指定される。

【0067】

この結果、セレクタ76の出力側には、インデックス制御信号SIDXで指定された第1〜第3の受信側フリップフロップFFr1〜FFr3のいずれか一の出力信号が出力されることになる。

【0068】

一方、比較器46は、第1〜第3の遅延フリップフロップFFD1〜FFD3と、第1〜第3のXORゲート77〜79を有する。

【0069】

第1〜第3の遅延フリップフロップFFD1〜FFD3は、例えばDQフリップフロップであって、それぞれに共通のクロック信号CLKの立ち上がりによってラッチしていたデータを後段に出力する。

【0070】

これにより、第1〜第3の遅延フリップフロップFFD1〜FFD3の各々には、クロック信号CLKに同期して、セレクタ76から出力されたデータがシリアルに取り込まれる。

【0071】

そして、XORゲート77〜79の各々は、上記の第1〜第3の遅延フリップフロップFFD1〜FFD3の各々の出力信号と、テストパターンTPの期待値「0」、「1」、「0」との排他的論理和をとる。これらの期待値は、遅延フリップフロップFFD1〜FFD3の各々にラッチされるテストパターンTPの各ビットの期待値である。

【0072】

そして、XORゲート77〜79の各々は、排他的論理和をとることで得られた第1〜第3の比較信号Sp1〜Sp3を結果比較器47に出力する。

【0073】

結果比較器47は、ORゲート81とANDゲート82とを備える。

【0074】

このうち、ORゲート81は、第1〜第3の比較信号Sp1〜Sp3の論理和をとり、その結果をANDゲート82に出力する。

【0075】

そのANDゲート82は、3ステートカウンタ48から出力された状態信号Ssと上記のORゲート81の出力信号との論理和をとり、それを結果信号Shとして後段に出力する。

【0076】

3ステートカウンタ48は、診断モード信号SCHKが「1」のときにイネーブルとなり、クロック信号CLKに同期して内部状態が「0」、「1」、「0」の順に遷移する。その3ステートカウンタ48から出力される状態信号Ssは、内部状態が最初の「0」と「1」のときには「0」であり、内部状態が最後の「0」になったときに「1」となる。

【0077】

また、3ステートカウンタ48には、結果信号Shと開始信号Srが入力される。3ステートカウンタ48は、結果信号Shが「1」になったときに状態遷移が停止し、再開信号Srが「1」になったときに状態遷移が再開する。

【0078】

その3ステートカウンタ48から出力された状態信号Ssは、インデックスカウンタ85に入力される。

【0079】

インデックスカウンタ85は、診断モード信号SCHKが「1」のときにイネーブルとなる。そして、イネーブル時のインデックスカウンタ85は、状態信号Ssを計数し、その計数結果を既述の2ビットのインデックス制御信号SIDXとして出力する。

【0080】

更に、3ステートカウンタ48から出力された上記の状態信号Ssはタイミング調整器45にも入力される。

【0081】

図7は、タイミング調整器45の回路図である。

【0082】

図7に示すように、タイミング調整器45は、第1〜第3のタイミング指定器101〜103と、第1〜第6のANDゲート111〜116と、ORゲート120とを備える。

【0083】

このうち、第1のANDゲート111は、2ビットのインデックス制御信号SIDXの下位ビットSIDX[0]の反転信号と、そのインデックス制御信号SIDXの上位ビットSIDX[1]との論理積をとり、その結果をイネーブル信号Seとして出力する。

【0084】

また、第2のANDゲート112は、下位ビットSIDX[0]と上位ビットSIDX[1]の反転信号との論理積をとり、その結果をイネーブル信号Seとして出力する。

【0085】

そして、第3のANDゲート113は、下位ビットSIDX[0]と上位ビットSIDX[1]との論理積をとり、その結果をイネーブル信号Seとして出力する。

【0086】

これにより、同一のインデックス制御信号SIDXの下では、第1〜第3のANDゲート111〜113のうちの一つのみのイネーブル信号Seが「1」となり、それ以外のイネーブル信号Seは「0」となる。

【0087】

例えば、インデックス制御信号SIDXが「01」のときは第1のANDゲート111が「1」となり、他のANDゲート112、113の出力は「0」となる。

【0088】

そして、第1〜第3のタイミング指定器101〜103のうち、「1」となったイネーブル信号Seが入力されたタイミング指定器のみがイネーブルとなる。

【0089】

また、ORゲート120は、各タイミング指定器101〜103から出力される後述の比較信号Stの論理和をとり、その結果を開始信号Srとして出力する。その開始信号Srは、各タイミング指定器101〜103の比較信号Stのいずれか一が「1」のときに「1」となり、それ以外のときには「0」となる。

【0090】

更に、第4〜第6のANDゲート114〜116は、それぞれ状態信号Ssと第1〜第3の比較信号Sp1〜Sp3との論理積をとり、その結果をそれぞれ第1〜第3のタイミング指定器101〜103に出力する。

【0091】

図8は、第1〜第3のタイミング指定器101〜103の回路図である。

【0092】

図8に示すように、第1〜第3のタイミング指定器101〜103は、タイミングコード生成器61と、第1〜第3のフリップフロップFF1〜FF3と、比較器67とを備える。

【0093】

このうち、タイミングコード生成器61には、上記した第4〜第6のANDゲート114〜116の出力が入力される。

【0094】

そのタイミングコード生成器61は、ORゲート62とカウンタ63とを有する。

【0095】

ORゲート62は、第4〜第6のANDゲート114〜116の各々の出力信号の論理和をとり、それをカウンタ63に出力する。

【0096】

カウンタ63は、イネーブル信号Seによりイネーブル状態となる。イネーブル状態となったカウンタ63は、ORゲート62の出力が「1」になったときにカウントアップし、その計数結果を2ビットのタイミング指定信号Scとして出力する。

【0097】

第1〜第3のフリップフロップFF1〜FF3は、2ビットの信号をラッチするものであって、クロック信号CLKの立ち上がりによってラッチしていた信号を後段に出力する。

【0098】

これにより、第1〜第3のフリップフロップFF1〜FF3の各々には、クロック信号CLKに同期して、タイミング指定信号Scが順に取り込まれる。

【0099】

比較器67は、上記の第2のフリップフロップFF2と第3のフリップフロップFF3の出力信号を比較し、これらが異なる値であれば比較信号Stを「1」にし、これらが同じ値であれば比較信号Stを「0」にする。

【0100】

このように複数のフリップフロップFF1〜FF3を接続し、最終のフリップフロップFF3の入力と出力とを比較することで、カウンタ63においてタイミング指定信号Scが切り替わってから時間をおいて比較信号Stを切り替えることができる。これにより、タイミング指定信号Scによってセレクタ55(図6参照)が確実に切り替わった後に、タイミング調整器45(図7参照)から開始信号Srを出力することができる。

【0101】

再び図5を参照する。

【0102】

上記した第1〜第3のタイミング指定器101〜103から出力されたタイミング指定信号Scは、それぞれ第1〜第3の遅延回路41〜43に入力される。

【0103】

一方、ANDゲート82から出力された結果信号Shは、ANDゲート90に入力される。

【0104】

ANDゲート90の入力側には、その結果信号Shの他に、回数カウンタ91から出力された計数信号SNも入力される。

【0105】

回数カウンタ91は、インデックス制御信号SIDXに基づいて、第1〜第3の受信側フリップフロップFFr1〜FFr3の全てにテストパターンTPが1回供給されたら計数結果を1だけインクリメントする。例えば、第1〜第3の受信側フリップフロップFFr1〜FFr3の全てにテストパターンTPが2回供給されたら回数カウンタ91の計数値nは2となり、3回供給されたら計数値nは3となる。

【0106】

このように、回数カウンタ91は、第1〜第3の受信側フリップフロップFFr1〜FFr3の全てにテストパターンTPが供給された回数nを計数するものであり、その回数nが予定回数Nよりも少ないときは、回数カウンタ91は計数信号SNを「0」とする。そして、その回数nが予定回数Nに等しくなったとき、回数は計数信号SNを「1」とする。

【0107】

ANDゲート90は、これらの信号SN、Shの論理積をとり、その結果をユーザへの通知信号SUとして出力する。

【0108】

次に、この電子回路20を用いたタイミング調整方法について説明する。

【0109】

図9は、本実施形態に係るタイミング調整方法について説明するためのフローチャートである。

【0110】

最初のステップP1では、電子回路20を通常モードから診断モードに切り替える。

【0111】

本ステップは、ユーザが診断モード信号SCHKを「0」から「1」に切り替えることで行われる。

【0112】

次に、ステップP2に移り、上記の診断モード信号SCHKによってイネーブルとなったテストパターン生成器28(図4参照)が、クロック信号CLKに同期してテストパターンTPの各ビット「0」、「1」、「0」を生成する。

【0113】

そのテストパターンTPは、第1〜第3の送信側フリップフロップFFt1〜FFt3の各々にラッチされる。その後、クロック信号CLKの立ち上がりを受けた送信側フリップフロップFFt1〜FFt3が、テストパターンTPを第1〜第3の受信側フリップフロップFFr1〜FFr3(図5参照)の各々に出力する。

【0114】

図10は、各受信側フリップフロップFFr1〜FFr3の各々に出力されるテストパターンTPの一例を示す模式図である。

【0115】

図10において、「FF Index」とは、インデックス制御信号SIDXを10進数で表したときの値である。図10に示されるように、テストパターンTPは、各受信側フリップフロップFFr1〜FFr3の各々において同一のシリアルデータ〔010〕である。そして、テストパターンTPの各ビット「0」、「1」、「0」は、クロック信号CLKに同期して、各受信側フリップフロップFFr1〜FFr3にラッチされる。

【0116】

また、各受信側フリップフロップFFr1〜FFr3のうちの一つに対して診断が行われているときは、他の受信側フリップフロップはdon't care (X)となる。

【0117】

本実施形態では、図6に示したように、第1〜第3の遅延回路41〜43によってテストパターンTPに0、α、2α、3αのいずれかの遅延時間が生ずることになる。これらのいずれの遅延時間が生ずるかは第1〜第3の受信側フリップフロップFFr1〜FFr3の各々に個別に設定されるが、診断モードの開始直後では全てのフリップフロップFFr1〜FFr3について遅延時間は0とされる。

【0118】

なお、このように遅延時間を0にするには、予めカウンタ63(図8参照)をリセットしてタイミング指定信号Scを「00」にしておけばよい。

【0119】

また、診断モードの開始前にインデックスカウンタ85(図5参照)は予めリセットされており、インデックスカウンタ85から出力されるインデックス制御信号SIDXは「01」となっている。

【0120】

そのため、セレクタ76(図5参照)では、「01」に対応する第1の受信側フリップフロップFFr1の出力信号が選択され、第1の受信側フリップフロップFFr1に対するホールドエラーの有無の判断とタイミング調整とが最初に行われる。なお、第2の受信側フリップフロップFFr2と第3の受信側フリップフロップFFr3に対するタイミング調整は、インデックス制御信号SIDXがインクリメントすることにより、第1の受信側フリップフロップFFr1と同様にして行われる。

【0121】

次に、ステップP3に移り、比較器46において、第1の受信側フリップフロップFFr1から出力されたテストパターンTPと、そのテストパターンTPの期待値「0」、「1」、「0」とが一致するか否かを調べる。

【0122】

ここで、診断モード時においては、第1の受信側フリップフロップFFr1にラッチされていたテストパターンTP(〔010〕)の各ビットがクロック信号CLKに同期して各第1〜第3の遅延フリップフロップFFD1〜FFD3にシリアルに取り込まれる。

【0123】

よって、第1の受信側フリップフロップFFr1においてホールドエラーが発生していなければ、第1〜第3の遅延フリップフロップFFD1〜FFD3には、それぞれテストパターンTPの各ビット「0」、「1」、「0」が取り込まれるはずである。

【0124】

一方、第1の受信側フリップフロップFFr1においてホールドエラーが発生している場合は、第1の受信側フリップフロップFFr1から出力されるテストパターンTPのいずれかのビットにおいてデータが反転する。

【0125】

そこで、本ステップでは、そのようなビットの反転の有無を調べるために、XORゲート77〜79の各々において、第1〜第3の遅延フリップフロップFFD1〜FFD3の各々の出力信号と期待値「0」、「1」、「0」との排他的論理和をとる。

【0126】

ここで、ホールドエラーが原因のデータの反転がテストパターンTPのいずれかのビットで発生している場合(NG時)は、第1〜第3の比較結果信号Sp1〜Sp3のいずれかが「1」となる。

【0127】

そして、そのようなデータの反転がない場合(OK時)には、第1〜第3の比較結果信号Sp1〜Sp3の全てが「0」となる。

【0128】

また、データの反転の有無によらず、上記のように第1〜第3の遅延フリップフロップFFD1〜FFD3の各々にテストパターンTPの三つの全てのビットがラッチされたときは、3ステートカウンタ48の状態信号Ssが「1」となる。

【0129】

よって、ホールドエラーが発生しているときはANDゲート82の結果信号Shが「1」となり、ホールドエラーが発生していないときはその結果信号Shが「0」となる。

【0130】

上記のように結果信号Shが「1」となった場合(NG時)であって、且つ、回数カウンタ91による計数nが予定回数Nを越えていない場合はステップP4に移る。

【0131】

本ステップでは、「1」となった結果信号Shを受けて3ステートカウンタ48がその動作を停止する。また、このタイミングではカウンタ63(図8参照)のカウント値が変わっていないため、第1〜第3のフリップフロップFF1〜FF3に同一のタイミング指定信号Scがラッチされている。このため、本ステップでは、各タイミング指定器101〜103から出力される比較信号Stが「0」になるため開始信号Srも「0」になり、テストパターン生成器28におけるテストパターンTPの生成が停止する。

【0132】

次に、ステップP5に移り、第1の受信側フリップフロップFFr1がデータを受け取るタイミングを調整する。

【0133】

その調整は、タイミング調整器45の第1〜第3のタイミング指定器101〜103(図8参照)において次のように行われる。

【0134】

ホールドエラーが発生したときは、上記のように、第1〜第3の比較結果信号Sp1〜Sp3のいずれかが「1」となる。また、各遅延フリップフロップFFD1〜FFD3の各々にテストパターンTPの三つの全てのビットがラッチされたときには状態信号Ssが「1」となる。

【0135】

よって、この場合は、第4〜第6のANDゲート114〜116のいずれかの出力が1となり、カウンタ63が1だけカウントアップされる。これにより、予め「00」にリセットされていたタイミング指定信号Scが「01」となるため、第1の遅延回路41(図6参照)のセレクタ55が第2の出力線51bを選択するようになる。

【0136】

その結果、第1の遅延回路41に入力される信号が、遅延時間αだけ遅れて第1の受信側フリップフロップFFr1に出力されるようになり、信号のタイミング調整が行われる。

【0137】

この後は、上記したステップP2に再び戻る。

【0138】

ここで、上記のステップP4では3ステートカウンタ48がその動作を停止していたので、インデックス制御信号SIDXは前回と変わっておらず、前回と同一の第1の受信側フリップフロップFFr1に対してタイミング調整が行われる。

【0139】

そして、ステップP5を行う度にタイミング調整器45のカウンタ63が1ずつカウントアップし、第1の遅延回路41における遅延時間をα、2α、3αの順に長くすることができる。

【0140】

一方、ステップP3において結果信号Shが「0」となった場合(OK時)であって、且つ、回数カウンタ91による計数nが予定回数Nを越えていない場合もステップP2に戻る。

【0141】

そして、上記のようにステップP3を繰り返し行い、回数カウンタ91による計数nが予定回数Nに等しくなった場合には、ステップP6に移る。

【0142】

ステップP6では、n=Nとなったため回数カウンタ91から出力される計数信号SNが「1」となる。その結果、ANDゲート90から出力される通知信号SUは、結果信号Shと同一となる。

【0143】

上記のように、結果信号Shは、第1〜第3の受信側フリップフロップFFr1〜FFr3のいずれかにおいてホールドエラーが発生したときに「1」となる。

【0144】

よって、ユーザは、通知信号SUが「1」のときに第1〜第3の受信側フリップフロップFFr1〜FFr3のいずれかにおいてホールドエラーが発生したことを認識できる。

【0145】

以上により、本実施形態に係るタイミング調整方法に基本ステップを終了する。

【0146】

上記した本実施形態によれば、図6に示したように、第1〜第3の遅延回路41〜43によって、各第1〜第3の受信側フリップフロップFFr1〜FFr3に入力される通常データDの各ビットD[0]、D[1]、D[2]を遅延させる。

【0147】

図11は、このようにビットD[0]を遅延させた場合における、第1の送信側フリップフロップFFt1と第1の受信側フリップフロップFFr1のタイミングチャートである。

【0148】

図11に示すように、タイミング調整をしたことで、第1の受信側フリップフロップFFr1がビットD[0]を受信するタイミングは、第1の送信側フリップフロップFFt1がビットD[0]を送信するタイミングよりも所定の時間(例えばα)だけ遅れる。

【0149】

よって、クロックスキューが原因で第1の受信側フリップフロップFFr1にクロック信号CLKが遅れて入力されても、クロック信号CLKの立ち上がりから十分に長い期間Tを経過した後に、フリップフロップFFr1に入力されるビットD[0]が反転する。その結果、当該期間Tが短い場合に発生するホールドエラーを防止でき、電子回路20の信頼性を高めることができる。

【0150】

更に、上記したステップP3では、ホールドエラーが発生していない場合(OK時)であっても、各第1〜第3の受信側フリップフロップFFr1〜FFr3のそれぞれの診断回数が予め定めた回数Nを越えていない場合には診断を続ける。

【0151】

これにより、OKと判断された受信側フリップフロップが、その後の温度変化によってNGとなるのを見落とす危険性を低減でき、診断の正確性を期することができる。

【0152】

また、電子回路20の外部に通知信号SUとインデックス制御信号SIDXと出力し、ユーザがこれらの信号を監視できるようにしてもよい。

【0153】

この場合、通知信号SUが「1」で受信側フリップフロップFFr1〜FFr3のいずれかにホールドエラーがある場合、どの受信側フリップフロップにホールドエラーがあるかをユーザがインデックス制御信号SIDXに基づいて判断することができる。

【0154】

図12は、これらの信号SU、SIDXを外部に引き出す第1の端子150と第2の端子151を設けた場合の電子回路20の模式図である。

【0155】

この場合、電子回路20に第3の端子153を設け、その第3の端子153から電子回路20に診断モード信号SCHKを入力するのが好ましい。

【0156】

図13は、上記とは別の方法による各信号SU、SIDXの外部への引き出し方を説明するための電子回路20の模式図である。

【0157】

この例では、上記の図12のように各信号SU、SIDXに専用の端子150、151を設けるのではなく、第2の論理回路75(図5参照)の出力データDiを外部に出力するのに使用される第4の端子154と第5の端子155を流用する。なお、出力データDiは、第1の半導体素子23から出力された通常データDに対し、第2の論理回路75で所定の処理を施してなるデータである。

【0158】

この場合、各端子154、155から各信号SU、SIDXと出力データDiのどちらを出力するかは、第1のセレクタ161と第2のセレクタ162により選択される。

【0159】

第1のセレクタ161は、診断モード信号SCHKが「0」のときに出力データDiを選択し、診断モード信号SCHKが「1」のときに通知信号SUを選択する。

【0160】

そして、第2のセレクタ162は、診断モード信号SCHKが「0」のときに出力データDiを選択し、診断モード信号SCHKが「1」のときにインデックス制御信号SIDXを選択する。

【0161】

このように、第4の端子154と第5の端子155に対して出力データDiの他に各信号SU、SIDXの出力機能を担わせることにより、端子数が増大するのを防止して電子回路20が大型化するのを抑制することができる。

【0162】

以上説明した各実施形態に関し、更に以下の付記を開示する。

【0163】

(付記1) クロック信号に同期してテストパターンを出力する送信側フリップフロップと、

前記送信側フリップフロップから出力された前記テストパターンを所定の遅延時間だけ遅延させて出力する遅延回路と、

前記遅延回路から出力された前記テストパターンをラッチすると共に、前記クロック信号に同期して前記テストパターンを出力する受信側フリップフロップと、

前記受信側フリップフロップから出力された前記テストパターンと、該テストパターンの期待値とを比較して、前記テストパターンと前記期待値とが一致するか否かを示す比較信号を出力する比較器と、

前記比較信号が入力され、該比較信号によって前記テストパターンと前記期待値とが一致していないことが判った場合に、前記遅延回路における前記遅延時間を調整するタイミング調整器と、

を有することを特徴とする電子回路。

【0164】

(付記2) 前記受信側フリップフロップが複数設けられ、

制御信号に基づいて、前記受信側フリップフロップのいずれか一の出力を選択して前記比較器に出力する第1のセレクタと、

前記第1のセレクタに対して前記制御信号を出力する第1のカウンタとを更に有することを特徴とする付記1に記載の電子回路。

【0165】

(付記3) 前記テストパターンはシリアルデータであり、

前記比較器は、前記テストパターンの各々のビットをラッチする複数のフリップフロップを備え、

前記複数のフリップフロップの全てに前記テストパターンの全てのビットがラッチされたときに「1」となり、それ以外のときに「0」となる状態信号を出力するステートカウンタとを更に有し、

前記第1のカウンタは、前記状態信号を計数し、該計数結果を前記制御信号として出力することを特徴とする付記2に記載の電子回路。

【0166】

(付記4) 前記比較器は、複数の前記フリップフロップの各々の出力と、前記期待値の各々のビットとの排他的論理和を複数の前記比較信号として出力する複数の排他的論理和回路とを有し、

複数の前記比較信号の論理和をとる論理和回路と、

前記論理和回路の出力と前記状態信号との論理積をとる第1の論理積回路と、

複数の前記受信側フリップフロップの全てが前記テストパターンを受けたときに1だけインクリメントして、計数結果が予め定められた予定回数になったときに「1」になる計数信号を出力する第2のカウンタと、

前記第1の論理積回路の出力と前記計数信号との論理積を通知信号として外部に出力する第2の論理積回路とを更に有することを特徴とする付記3に記載の電子回路。

【0167】

(付記5) 前記通知信号が出力される第1の端子と、

前記制御信号が出力される第2の端子とを更に有することを特徴とする付記4に記載の電子回路。

【0168】

(付記6) 前記遅延回路は、前記テストパターンが入力される直列に接続された複数のバッファと、タイミング指定信号によって複数の前記バッファの各々の出力のいずれか一を選択して前記受信側フリップフロップに出力する第2のセレクタとを有することを特徴とする付記1〜5のいずれかに記載の電子回路。

【0169】

(付記7) 前記タイミング調整器は、前記比較信号によって前記テストパターンと前記期待値とが一致しないことが判った場合にカウントアップする第3のカウンタを備え、

前記第3のカウンタの計数結果が前記タイミング指定信号として前記第2のセレクタに出力されることを特徴とする付記6に記載の電子回路。

【0170】

(付記8) 通常モード時に通常データを生成する第1の論理回路と、

診断モード時に前記テストパターンを生成するテストパターン生成器と、

前記通常モード時に前記通常データを選択して前記送信側フリップフロップに出力し、前記診断モード時に前記テストパターンを選択して前記送信側フリップフロップに出力する第3のセレクタと、

前記通常モード時において、前記受信側フリップフロップから出力された前記通常データが入力される第2の論理回路とを更に有することを特徴とする付記1〜7のいずれかに記載の電子回路。

【0171】

(付記9) 配線基板と、

前記配線基板に実装された第1の半導体素子と第2の半導体素子とを更に有し、

前記第1の半導体素子に前記送信側フリップフロップが設けられ、

前記第2の半導体素子に、前記遅延回路、前記受信側フリップフロップ、前記比較器、及び前記タイミング調整器が設けられたことを特徴とする付記1〜8のいずれかに記載の電子回路。

【0172】

(付記10) 送信側フリップフロップが遅延回路にテストパターンを出力して、前記遅延回路において所定の遅延時間だけ遅延された前記テストパターンを受信側フリップフロップがラッチするステップと、

クロック信号に同期して前記受信側フリップフロップから出力された前記テストパターンと、該テストパターンの期待値とが一致するか否かを調べるステップと、

前記テストパターンと前記期待値とが一致しないことが判った場合に、前記遅延回路における前記遅延時間を調整するステップと、

を有することを特徴とする電子回路のタイミング調整方法。

【符号の説明】

【0173】

1、20…電子回路、2、22…配線基板、3、23…第1の半導体素子、4、24…第2の半導体素子、27…第1の論理回路、28…テストパターン生成器、29…セレクタ制御回路、31〜33…第1〜第3のセレクタ、41〜43…第1〜第3の遅延回路、44…フリップフロップ群、45…タイミング調整器、46…比較器、47…結果通知器、48…3ステートカウンタ、51…チェインバッファ、51a〜51c…第1〜第3の出力線、52〜54…第1〜第3のバッファ、55…セレクタ、61…タイミングコード生成器、62…ORゲート、63…カウンタ、67…比較器、75…第2の論理回路、76…セレクタ、77〜79…第1〜第3のXORゲート、81…ORゲート、82…ANDゲート、85…インデックスカウンタ、90…ANDゲート、91…回数カウンタ、101〜103…第1〜第3のタイミング指定器、111〜116…第1〜第6のANDゲート、120…ORゲート、150…第1の端子、151…第2の端子、153…第3の端子、154…第4の端子、155…第5の端子、161…第1のセレクタ、162…第2のセレクタ。

【特許請求の範囲】

【請求項1】

クロック信号に同期してテストパターンを出力する送信側フリップフロップと、

前記送信側フリップフロップから出力された前記テストパターンを所定の遅延時間だけ遅延させて出力する遅延回路と、

前記遅延回路から出力された前記テストパターンをラッチすると共に、前記クロック信号に同期して前記テストパターンを出力する受信側フリップフロップと、

前記受信側フリップフロップから出力された前記テストパターンと、該テストパターンの期待値とを比較して、前記テストパターンと前記期待値とが一致するか否かを示す比較信号を出力する比較器と、

前記比較信号が入力され、該比較信号によって前記テストパターンと前記期待値とが一致していないことが判った場合に、前記遅延回路における前記遅延時間を調整するタイミング調整器と、

を有することを特徴とする電子回路。

【請求項2】

前記受信側フリップフロップが複数設けられ、

制御信号に基づいて、前記受信側フリップフロップのいずれか一の出力を選択して前記比較器に出力する第1のセレクタと、

前記第1のセレクタに対して前記制御信号を出力するカウンタとを更に有することを特徴とする請求項1に記載の電子回路。

【請求項3】

前記テストパターンはシリアルデータであり、

前記比較器は、前記テストパターンの各々のビットをラッチする複数のフリップフロップを備え、

前記複数のフリップフロップの全てに前記テストパターンの全てのビットがラッチされたときに「1」となり、それ以外のときに「0」となる状態信号を出力するステートカウンタとを更に有し、

前記カウンタは、前記状態信号を計数し、該計数結果を前記制御信号として出力することを特徴とする請求項2に記載の電子回路。

【請求項4】

前記遅延回路は、前記テストパターンが入力される直列に接続された複数のバッファと、タイミング指定信号によって複数の前記バッファの各々の出力のいずれか一を選択して前記受信側フリップフロップに出力する第2のセレクタとを有することを特徴とする請求項1乃至請求項3のいずれか1項に記載の電子回路。

【請求項5】

送信側フリップフロップが遅延回路にテストパターンを出力して、前記遅延回路において所定の遅延時間だけ遅延された前記テストパターンを受信側フリップフロップがラッチするステップと、

クロック信号に同期して前記受信側フリップフロップから出力された前記テストパターンと、該テストパターンの期待値とが一致するか否かを調べるステップと、

前記テストパターンと前記期待値とが一致しないことが判った場合に、前記遅延回路における前記遅延時間を調整するステップと、

を有することを特徴とする電子回路のタイミング調整方法。

【請求項1】

クロック信号に同期してテストパターンを出力する送信側フリップフロップと、

前記送信側フリップフロップから出力された前記テストパターンを所定の遅延時間だけ遅延させて出力する遅延回路と、

前記遅延回路から出力された前記テストパターンをラッチすると共に、前記クロック信号に同期して前記テストパターンを出力する受信側フリップフロップと、

前記受信側フリップフロップから出力された前記テストパターンと、該テストパターンの期待値とを比較して、前記テストパターンと前記期待値とが一致するか否かを示す比較信号を出力する比較器と、

前記比較信号が入力され、該比較信号によって前記テストパターンと前記期待値とが一致していないことが判った場合に、前記遅延回路における前記遅延時間を調整するタイミング調整器と、

を有することを特徴とする電子回路。

【請求項2】

前記受信側フリップフロップが複数設けられ、

制御信号に基づいて、前記受信側フリップフロップのいずれか一の出力を選択して前記比較器に出力する第1のセレクタと、

前記第1のセレクタに対して前記制御信号を出力するカウンタとを更に有することを特徴とする請求項1に記載の電子回路。

【請求項3】

前記テストパターンはシリアルデータであり、

前記比較器は、前記テストパターンの各々のビットをラッチする複数のフリップフロップを備え、

前記複数のフリップフロップの全てに前記テストパターンの全てのビットがラッチされたときに「1」となり、それ以外のときに「0」となる状態信号を出力するステートカウンタとを更に有し、

前記カウンタは、前記状態信号を計数し、該計数結果を前記制御信号として出力することを特徴とする請求項2に記載の電子回路。

【請求項4】

前記遅延回路は、前記テストパターンが入力される直列に接続された複数のバッファと、タイミング指定信号によって複数の前記バッファの各々の出力のいずれか一を選択して前記受信側フリップフロップに出力する第2のセレクタとを有することを特徴とする請求項1乃至請求項3のいずれか1項に記載の電子回路。

【請求項5】

送信側フリップフロップが遅延回路にテストパターンを出力して、前記遅延回路において所定の遅延時間だけ遅延された前記テストパターンを受信側フリップフロップがラッチするステップと、

クロック信号に同期して前記受信側フリップフロップから出力された前記テストパターンと、該テストパターンの期待値とが一致するか否かを調べるステップと、

前記テストパターンと前記期待値とが一致しないことが判った場合に、前記遅延回路における前記遅延時間を調整するステップと、

を有することを特徴とする電子回路のタイミング調整方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2012−231290(P2012−231290A)

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願番号】特願2011−98211(P2011−98211)

【出願日】平成23年4月26日(2011.4.26)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願日】平成23年4月26日(2011.4.26)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]