電子放出素子、電子源および画像形成装置の製造方法

【課題】 カソード電極2とゲート電極4とを絶縁層3を間に挟んで積層し、ゲート電極4と絶縁層3を貫通するゲートホール内に位置するカソード電極2上に電子放出膜5を配置した電子放出素子の製造方法において、開口内の絶縁層3の壁面に付着した電子放出膜5の材料を除去できるようにし、リーク電流の少ない高効率な電界放出型の電子放出素子を容易に製造できるようにする。

【解決手段】 絶縁層3とゲート電極4のうち、少なくともゲート電極4を貫通し、ゲートホールである第1開口6に並設される第2開口を形成し、前記第2開口と、内部に前記電子放出膜5が堆積された前記第1開口6との間に存在する絶縁層3を、前記第1開口6と第2開口7とが連通するまでエッチングする工程を有する電子放出素子の製造方法とする。

【解決手段】 絶縁層3とゲート電極4のうち、少なくともゲート電極4を貫通し、ゲートホールである第1開口6に並設される第2開口を形成し、前記第2開口と、内部に前記電子放出膜5が堆積された前記第1開口6との間に存在する絶縁層3を、前記第1開口6と第2開口7とが連通するまでエッチングする工程を有する電子放出素子の製造方法とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子放出素子、電子源および画像形成装置の製造方法に関する。

【背景技術】

【0002】

電子放出素子には、電界放出型(以下、「FE型」と称する)などがある。FE型には、カソード電極とゲート電極とを絶縁層を間に挟んで積層し、ゲート電極と絶縁層を貫通する開口(ゲートホール)内に位置するカソード電極上に電子放出部材を配置した形態がある。このような形態の代表的な例として上記開口内に円錐状の電子放出部材を設けたスピント型がある。

【0003】

従来、上記電子放出素子の製造方法として、以下のようなものが知られている。

【0004】

(1)開口を形成した後に、リフトオフプロセスにより開口内に電子放出部材を堆積させる方法(例えば、特許文献1参照)。

【0005】

(2)開口内に電子放出部材を堆積させた後、開口内にエッチング液を導入し、絶縁層の開口周壁面に付着した電子放出膜の一部を除去する方法(例えば、特許文献2参照)。

【0006】

(3)カソード電極上に予め電子放出部材を堆積させた後に絶縁層およびゲート電極を形成し、その後に開口を形成する方法(例えば、特許文献3参照)。

【0007】

【特許文献1】特開平8−96704号公報

【特許文献2】特開2000-195448号公報

【特許文献3】特開平8−264109号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、特許文献1のように、電子放出部材の堆積にリフトオフプロセスを用いた場合、開口内への電子放出部材の堆積時に開口内の絶縁層の側壁部に導電性材料である電子放出部材の付着が生じやすい。また、リフトオフ時にも、開口内の絶縁層の側壁部に電子放出部材の付着が生じやすい。このため、ゲート電極とカソード電極間のリーク電流が増大する恐れがある。

【0009】

また、特許文献1には、開口を形成した後に、ウエットエッチングなどによって、開口内に露出する絶縁層の一部を除去することでオーバーハング部を形成しておくことも開示されている。これは、オーバーハング部を形成した開口をマスクとして用いることで、開口内の絶縁層側壁部への電子放出部材の付着を解消しようとするものである。しかし、このようにすると、電子放出部材の成膜方法が指向性の高い成膜方法に限られてしまい、プロセスマージンが小さくなる問題を生じる。

【0010】

特許文献2のように、内部に電子放出部材が堆積された開口内にエッチング液を導入しても、付着している電子放出部材の面積やその付着量にもよるが、付着物自体が障壁となり、十分なエッチングができない。つまり、付着物(電子放出部材の一部)と絶縁層の側壁との間にエッチャントが侵入せずに十分に付着物を取り除くことができず、ゲート電極とカソード電極間のリーク電流を解消できない場合がある。また、開口毎に付着している形態が異なるため、リーク電流のバラツキも生じる。

【0011】

特許文献3の方法によれば、上記付着物によるリーク電流の問題については、解決できる。しかし、この方法では、開口を作製するプロセスにおいて、電子放出部材がエッチングのストップ層となる。そのため、電子放出部材がエッチングに対して十分に遅いエッチングレートを持つ必要がある。このことが、絶縁層および電子放出部材の材料の選択やエッチングプロセスの選択等のプロセスマージンを小さくしてしまう。さらに、長時間エッチングプロセスに電子放出部材が曝されているために、プラズマ等により電子放出部材の劣化が起こってしまう。さらには、この様な方法で製造すると、ゲート電極の直下に電子放出膜の一部が存在することを回避することが難しい。そのため、ゲート電極の直下の電子放出部材の部分から放出された電子は、直接、直上のゲート電極に照射する。このため、このような方法で作成された電子放出素子は無効電流が増加してしまう。

【0012】

本発明はこのような従来技術の課題を解決するためになされたもので、その目的とするところは、リーク電流の少ない高効率な電界放出型の電子放出素子、電子源、および画像表示装置を容易に得ることができるこれらの製造方法を提供することにある。

【課題を解決するための手段】

【0013】

本発明の第1は、(A)第1導電層と該第1導電層上に配置された絶縁層と該絶縁層上に配置された第2導電層とを備え、該絶縁層と該第2導電層とを貫通した第1開口を有する構造体を用意する工程と、

(B)前記第1開口内に電子放出部材を構成する材料を堆積する工程と、

(C)前記絶縁層と第2導電層のうち、少なくとも第2導電層を貫通し、前記第1開口に並設される第2開口を形成する工程と、

(D)前記第2開口と、内部に前記電子放出部材を構成する材料が堆積された前記第1開口との間に存在する絶縁層を、前記第1開口と第2開口とが連通するまでエッチングする工程と、

を有することを特徴とする電子放出素子の製造方法である。

【0014】

本発明の第2は、複数の電子放出素子を備える電子源の製造方法であって、前記複数の電子放出素子の各々が本発明の第1の製造方法により製造されることを特徴とする電子源の製造方法である。

【0015】

本発明の第3は、電子源と該電子源から放出された電子が照射されることにより発光する発光体とを備える画像表示装置の製造方法であって、前記電子源が本発明の第2の製造方法により製造されることを特徴とする画像表示装置の製造方法である。

【発明の効果】

【0016】

本発明によれば、電子放出部材の堆積時に第1開口の周壁に付着した当該電子放出部材が、第2開口側からのエッチングにより、第1開口の周壁の除去と共に除去することができる。したがって、リーク電流の減少、プロセスマージンの増加によるディスプレイ画面内での輝度ムラの減少により、低消費電力のディスプレイを歩留まり良く製造することができる。

【発明を実施するための最良の形態】

【0017】

以下に図面を参照して、この発明の好適な実施の形態を例示的に詳しく説明する。

【0018】

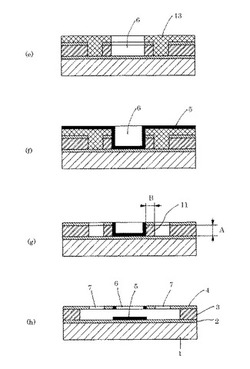

図1および図2は本発明に係る電子放出素子の製造方法のフローの一例を示す図で、以下に、図1および図2の(a)〜(h)の各工程の説明を行う。

【0019】

(1)図1(a)の工程

まず、基板1上にカソード電極2を積層する。基板1としては、予めその表面を十分に洗浄した、石英ガラス、Na等の不純物含有量を減少させたガラス、青板ガラス、シリコン板等にスパッタ法等によりSiO2を積層した積層体、アルミナ等セラミックスの絶縁性基板等を用いることができる。

【0020】

カソード電極2は、一般的に導電性を有しており、蒸着法、スパッタ法等の一般的真空成膜技術、フォトリソグラフィー技術により形成される。カソード電極2の構成材料としては、例えば、Be、Mg、Ti、Zr、Hf、V、Nb、Ta、Mo、W、Al、Cu、Ni、Cr、Au、Pt、Pd等の金属または合金材料、TiC、ZrC、HfC、TaC、SiC、WC等の炭化物、HfB2、ZrB2、LaB6、CeB6、YB4、GdB4等の硼化物、TiN、ZrN、HfN等の窒化物、Si、Ge等の半導体等を用いることができる。カソード電極2の厚さは、通常、10nmから100μmの範囲で設定される。好ましくは100nmから10μmの範囲で選択される。

【0021】

次に、絶縁層3を堆積する。絶縁層3は、スパッタ法等の一般的な真空成膜法、CVD法、真空蒸着法で形成される。厚さは、通常、10nmから100μmの範囲で設定され、好ましくは10nmから5μmの範囲から選択される。構成材料としては、酸化シリコン(典型的にはSiO2)、SiN、酸化アルミニウム(Al2O3)、CaF、アンドープダイヤモンド等、高電界に絶えられる耐圧の高い材料が好ましい。また、絶縁層3の構成材料としては、後述する工程8におけるエッチングによって、後述する工程6で形成する電子放出膜5の構成材料よりもエッチングされやすい材料を選択することが好ましい。

【0022】

さらに、絶縁層3に続いて、ゲート電極4を堆積する。ゲート電極4は、カソード電極2と同様に導電性を有しており、蒸着法、スパッタ法等の一般的真空成膜技術、フォトリソグラフィー技術により形成することができる。ゲート電極7の構成材料としては、例えば、Be、Mg、Ti、Zr、Hf、V、Nb、Ta、Mo、W、Al、Cu、Ni、Cr、Au、Pt、Pd等の金属または合金材料、TiC、ZrC、HfC、TaC、SiC、WC等の炭化物、HfB2、ZrB2、LaB6、CeB6、YB4、GdB4等の硼化物、TiN、ZrN、HfN等の窒化物、Si、Ge等の半導体等を用いることができる。ゲート電極4の厚さは、通常、1nmから100μmの範囲で設定され、好ましくは10nmから1μmの範囲で選択される。

【0023】

なお、カソード電極2とゲート電極4は、同一材料でも異種材料でも良く、また、同一形成方法でも異種方法でも良い。

【0024】

(2)図1(b)の工程

フォトリソグラフィー技術などを使用し、ゲート電極4上に所望のパターンのマスク12を形成する。マスク12の材料としては公知のレジスト材料を用いることができる。マスク12のパターン(開口)は、工程3で形成する第1開口6および第2開口7の形状に応じて適宜選択される。

【0025】

(3)図1(c)の工程

ドライエッチング等のエッチングにより、マスク12に覆われていないゲート電極4と絶縁層3を貫通してカソード電極2に到達する、第1開口6および第1開口6に並ぶ第2開口7を形成する。第1および第2開口6,7の形状は、マスク12の開口形状と同等の形状で形成される。また、第1開口6と第2開口7の作製順序はどちらが先であっても、同時でも良い。また、第2開口7の形成は、下記工程5と工程6の間で行っても良い。

【0026】

第2開口7は、図3に示されるように、第1開口6を囲む位置に間隔をあけて複数設けることができる他、図4(a)に示されるように、第1開口6を連続的に囲む環状に設けることもできる。

【0027】

なお、図1においては、第1開口6と第2開口7の双方ともに、ゲート電極4と絶縁層3を貫通する形態を示した。しかしながら、第2開口7は、図5に示されるように、後述する工程8で行う絶縁層3のエッチングができるよう、少なくともゲート電極4を貫通していれば良い。

【0028】

(4)図1(d)の工程

マスク12を取り除く。

【0029】

(5)図2(e)の工程

第1開口6内のみに電子放出膜5を形成するために、第1開口6に連通した開口を備えるマスク13を形成する。マスク13はフォトリソグラフィー技術などを用いて形成することができる。

【0030】

(6)図2(f)の工程

続いて、第1開口6内に電子放出膜5を形成する。電子放出膜5の形成は、図1のように、リフトオフ技術で行うことができる。また、インクジェット技術を用いれば、電子放出膜5の構成材料を第1開口6内に選択的に堆積させることもできるので、上記マスク13は必ずしも必要としない。電子放出膜5を構成する材料は、例えば、グラファイト、フラーレン、カーボンナノチューブ、ダイヤモンドライクカーボン、ダイヤモンドを分散した炭素および炭素化合物等から適宜選択することができる。好ましくは仕事関数の低いダイヤモンド膜、ダイヤモンドライクカーボン等が良い。電子放出膜5の膜厚は、通常、1nmから5μmの範囲で設定され、好ましくは5nmから100nmの範囲で選択される。

【0031】

(7)図2(g)の工程

マスク13を取り除く。

【0032】

(8)図2(h)の工程

次に、絶縁層3のエッチングを行う。エッチングは指向性の少ないエッチング方法を用いることが好ましい。具体的には等方的なエッチングが好ましく、特にはウエットエッチングが好ましい。上記等方的なエッチング方法としては、ウエットエッチングだけでなくケミカルドライエッチングのように、ラジカルを主エッチング種として利用するドライエッチングも用いることができる。

【0033】

ウエットエッチングに使用される溶液(エッチャント)としては、絶縁層3がエッチングでき、カソード電極2、ゲート電極4、電子放出膜5が実質的にエッチングあるいは劣化されないものが望ましい。ウエットエッチングに使用される溶液のカソード電極2とゲート電極4に対するエッチングレート比は、1/20以下が望ましく、1/100が好適である。また、電子放出膜5に対するエッチングレートは1/50が望ましく、1/200が好適である。このとき使用されるエッチング溶液は、4〜100℃の温度範囲で使用され、好ましくは、20〜50℃の範囲で使用される。このエッチング工程では、少なくとも第1開口6と第2開口7とが連通するまで、第1開口7側から、第2開口7と第1開口6間の絶縁層の壁11〔図2(g)参照〕の一部または全部をエッチングして除去する。

【0034】

カソード電極2とゲート電極4間での電気的なリークは、第1開口6の側壁についた電子放出膜5を構成する材料が主原因である。このため、これを取り除くことで、リーク電流を大幅に減少させることができる。その減少量は、第1開口6の側壁に付着した電子放出膜5を構成する材料を取り除いた量に比例する。そのため、第1開口6の側壁の一部または全部を取り除き、パターン(開口形状)を変化させることで、リーク電流を制御することができる。

【0035】

第2開口7の開口形状は、主として、開口6の形状と大きさ、絶縁層3の厚さから規定できる。このウエットエッチング工程を行った場合、行わなかった場合に比してリーク電流量を8割以上減少することがきる。

【0036】

第2開口7の形状は、どのような形でも良いが、例えば、直線または屈曲したスリット、矩形孔、円形孔、同心円形スリット、矩形環状スリットなどから選択することができる。第2開口7の大きさは、ウエットエッチングを用いる場合においてはエッチャントが十分に入り込む大きさであればよく、例えば矩形形状とした場合の幅、円形とした場合の直径は0.5〜1000μmの範囲であり、好ましくは1μm〜10μmの範囲で使用される。

【0037】

図3に示されるように、複数設けた第2開口7に大きさの大小がある場合、第1開口6と第2開口7との最近接距離B〔図2(g)参照〕は、小さい第2開口7についてはこれを大きい第2開口7についてより小さくすることが好ましい。また、第2開口7が総て同じ大きさである場合、上記最近接距離Bは実質的に一定であることが望ましい。エッチング条件は、絶縁層3の厚さA〔図2(g)参照〕と、絶縁層3をエッチングする速度であるエッチングレートRと、エッチングする時間tとにより実質的に決めることができる。図2(g)に示されるように、第2開口7が第1開口6と同様にゲート電極4と絶縁層3を貫通している場合、第1開口6と第2開口7との間にある絶縁層3を取り除くには、B≦R×tとなるような条件のもとでエッチングを行うことが好ましい。また、図5に示されるように、第2開口7がゲート電極4のみを貫通している場合、第1開口6と第2開口7との間にある絶縁層3の壁11を取り除くためには、(A2+B2)1/2≦R×tとなるような条件のもとでエッチングを行うことが好ましい。

【0038】

また、図3に示されるように、1個の第1開口6に対して、第2開口7が2個以上設けられる場合、第2開口7とその隣に存在する別の第2開口7間の最近接距離Cは、第1開口6と第2開口7との最近接距離Bより大きくしておくこともできるが、最近接距離Bより小さくすることが好ましい。このようにすることによって、図3において破線で囲まれた領域の絶縁層3全体を除去しやすくなり、第1開口6の周壁を全周に亘って連続して除去することが可能となる。この場合、第1開口6周囲のゲート電極4は、第2開口7同士間で連続しているので、図2(h)に示されるようにひさし状に張り出した状態で残されることになる。また、図4(a)に示されるように、第2開口7を第1開口6を囲む環状に形成した場合、図4(a)において破線で囲まれた領域の絶縁層3全体を除去しやすくなり、第1開口6の周壁を全周に亘って連続して除去しやすくなる。この場合、図4(b)に示されるように、第1開口6と第2開口7との間のゲート電極4は、第1開口6の周壁除去と共に除去されることになる。

【0039】

図6は、絶縁層3を設ける場合の他の例を示す図で、を図1(a)においては、絶縁層3を1層形成しているが、図6(a)に示されるように、絶縁層3の上に、該絶縁層3よりもエッチングされにくいもう一つの絶縁層3’を設けることもできる。このようにすると、図6(b)に示されるように、エッチング後に、第1開口6と第2開口7間に残されるゲート電極4の下に絶縁層3’が残されるので、ひさし状に突き出た第1開口6周囲のゲート電極4部分を補強することができる。

【0040】

図7は、電子放出膜5を形成する場合の他の例を示す図で、図7(a)に示されるように、第1開口部6は電子放出膜5の形成材料が入り込みやすい大きさとし、第2開口7は電子放出膜5の形成材料が入り込めない大きさとしておき、その上に電子放出膜5の形成材料を例えば塗布して電子放出膜5を形成することができる。この場合、第2開口7が電子放出膜5で覆われた状態となることもあるが、第2開口7上の電子放出膜5は下側が支持されていないので、エッチング時に超音波振動などで容易に除去することができる。したがって、第2開口7上の電子放出膜5を除去して、第2開口7からの絶縁層3のエッチング除去を行えば、図7(b)のように、第1開口6と第2開口7間の絶縁層3を除去した状態が得られる。

【0041】

図1および図2で説明した本発明の方法で得られる電子放出素子は、例えば図8のように、高圧電源10が接続されたアノード電極8を対向させ、カソード電極2ゲート電極4間に駆動のための電源9から電圧を印加することによって、電子放出膜5から電子を放出させることができる。なお、図8において、1は基板、2はカソード電極、3は絶縁層、4はゲート電極、5は電子放出膜、6は第1開口、7は第1開口6に並設された第2開口である。また、Vgはゲート電極4とカソード電極2の間に印加される電圧、Vaはゲート電極4とアノード電極8間に印加される電圧である。

【0042】

なお、以上説明した例においては、電子放出部材として電子放出膜5を用いた例としたが、本発明の電子放出部材は膜状のものに限られず、いわゆるスピント型のような円錐状のものなども適用することができる。本発明は、カソード電極2とゲート電極4との間に配置される絶縁層3とゲート電極4とを貫通する開口(ゲートホール)を形成した後に、開口内に電子放出部材を堆積させる工程を備える電子放出素子の製造に好ましく適用できる。また、ここでは、カソード電極2上に電子放出膜5を直接配置した形態を示したが、カソード電極2と電子放出膜5との間に電流制限などの目的のために抵抗膜が配置されていてもよい。カソード電極2にはこのような抵抗膜を有する電極も含まれる。

【0043】

次に、本発明の製造方法で作成した電子放出素子を適用した応用例について以下に述べる。

【0044】

本発明の電子放出素子は、その複数個を基体上に配列することによって、例えば電子源、あるいは画像表示装置を構成することができる。

【0045】

図9は、本発明の電子放出素子を複数配して得られる電子源の模式図である。図9において、電子源基体801上に、m本のX方向配線802と、n本のY方向配線803と、多数(m×n個)の電子放出素子804が配設されている。各電子放出素子804は、X方向配線802の一つとY方向配線803の一つとに接続されている。配線802,803と電子放出素子804との接続は、前記したカソード電極とゲート電極を介して行われる。

【0046】

X方向配線802は、Dx1、Dx2、…Dxmのm本の配線から成り、真空蒸着法、印刷法、スパッタ法等を用いて形成された導電性材料で構成することができる。配線の材料、膜厚、幅は適宜設計される。Y方向配線803は、Dy1、Dy2、…Dynのn本の配線から成り、X方向配線802と同様に形成される。これらm本のX方向配線802とn本のY方向配線803との間には、不図示の層間絶縁層が設けられており、両者を電気的に分離している。ここで、mおよびnは共に正の整数である。

【0047】

不図示の層間絶縁層は、真空蒸着法、印刷法、スパッタ法等を用いて形成されたSiO2 等で構成される。不図示の層間絶縁層は、例えば、X方向配線802を形成した基体801の全面或いはその一部に所望の形状で形成され、特にX方向配線802とY方向配線803との交差部の電位差に耐え得るように、膜厚、材料、製法が適宜設定される。X方向配線802とY方向配線803は、それぞれ外部端子として引き出されている。

【0048】

X方向配線802、Y方向配線803、および一対の電極(カソード電極2、ゲート電極4)を構成する材料は、その構成元素の一部あるいは全部が同一であっても、またそれぞれ異なっていても良い。電極を構成する材料と配線材料が同一である場合には、素子電極に接続した配線は素子電極ということもできる。また、素子電極を配線電極として用いることもできる。

【0049】

X方向配線802には、X方向に配列した電子放出素子804の行を選択するための、走査信号を印加する不図示の走査信号印加手段が接続される。一方、Y方向配線803には、Y方向に配列した電子放出素子804の各列を入力信号に応じて変調するための、不図示の変調信号発生手段が接続される。各電子放出素子に印加される駆動電圧は、当該素子に印加される走査信号と変調信号の差電圧として供給される。

【0050】

上記構成においては、単純なマトリクス配線を用いて、個別の電子放出素子を選択し、独立に駆動可能とすることができる。このような単純マトリクス配置の電子源を用いて構成した画像形成装置について、図10を用いて説明する。図10は、画像形成装置の表示パネルの一例を示す模式図である。

【0051】

図10において、801は電子放出素子を複数配した電子源基体、901は電子源基体801を固定したリアプレート、906はガラス基体903の内面に画像形成部材である蛍光体としての蛍光膜904とメタルバック905等が形成されたフェースプレートである。902は支持枠であり、支持枠902には、リアプレート901、フェースプレート906がフリットガラス等を用いて接続されている。907は外囲器であり、例えば、大気中あるいは窒素中で、400〜500℃の温度範囲で10分以上焼成することで、封着して構成される。

【0052】

外囲器907は、上述した通り、フェースプレート906、支持枠902、リアプレート901で構成される。リアプレート901は主に基体801の強度を補強する目的で設けられるため、基体801自体で十分な強度を持つ場合は、別体のリアプレート901は不要とすることができる。即ち、基体801に直接支持枠902を封着し、フェースプレート906、支持枠902および基体801で外囲器907を構成しても良い。一方、フェースプレート906、リアプレート901間に、スペーサーとよばれる不図示の支持体を設置することにより、大気圧に対して十分な強度をもつ外囲器907を構成することもできる。

【0053】

なお、本発明の電子放出素子を用いた画像形成装置では、放出した電子軌道を考慮して、電子放出素子804上部に蛍光体(蛍光膜904)をアライメントして配置する。

【0054】

図11は、本件のパネルに使用した蛍光膜904を示す模式図である。カラーの蛍光膜の場合は、蛍光体の配列により図10(a)に示すブラックストライプあるいは図10(b)に示すブラックマトリクスなどと呼ばれる黒色導電材1001と蛍光体1002とから構成した。

【0055】

本発明の画像形成装置は、テレビジョン放送の表示装置、テレビ会議システムやコンピューター等の表示装置の他、感光性ドラム等を用いて構成された光プリンターとしての画像形成装置等としても用いることができる。

【実施例】

【0056】

以下、本発明の実施例を詳細に説明する。

【0057】

実施例1

図1および図2を用いて本実施例の電子放出素子の製造工程を詳細に説明する。

【0058】

〔工程1−1:図1(a)〕

まず、基板1に石英を用い、十分洗浄を行った後、抵抗加熱蒸着により、基板1上に、カソード電極材料2として厚さ300nmのAlを成膜した。

【0059】

次に、絶縁層3の作製のために、原料ガスとしてSiH4、NO2を使用してプラズマCVD法により、SiO2を約1000nm成膜した。

【0060】

次に、絶縁層3上に、ゲート電極4として、Taを100nmの厚さになるようにスパッタ法により成膜した。

【0061】

〔工程1−2:図1(b)〕

次に、フォトリソグラフィーで、ポジ型フォトレジストのスピンコーティング、フォトマスクパターンを露光、現像し、マスクパターン12を形成した。このときの第1開口6の開口径は3μmとした。また、並設した第2開口7の開口も同時に形成した。このときの第2開口7の開口径は2μm、第1開口6と第2開口7間に挟まれる絶縁層3の厚さは1μmとなるようにした。

【0062】

〔工程1−3:図1(c)〕

次に、エッチングガスとしてCF4、H2の混合ガス、エッチングパワーとして150W、エッチング圧力として、5Paの条件で、ドライエッチングを行い、カソード電極2上面でエッチングをストップした。

【0063】

〔工程1−4:図1(d)〕

次に、残ったマスクパターン12を、剥離液にて除去した。

【0064】

〔工程1−5:図2(e)〕

次に、フォトリソグラフィーで、ポジ型フォトレジストのスピンコーティング、フォトマスクパターンを露光、現像し、第1開口6が露出するマスクパターン13を形成した。

【0065】

〔工程1−6:図2(f)〕

次にプラズマCVD法を用いて、ダイヤモンドライクカーボン膜を約30nm堆積させ、電子放出膜5とした。

【0066】

〔工程1−7:図2(g)〕

次に、マスクパターン13を、剥離液にてリフトオフした。

【0067】

〔工程1−8:図2(h)〕

次に、BHF(エッチングレート:100nm/min)に、11分間浸すことにより、SiO2をウエットエッチングし、水洗を10分行い、本実施例の電子放出素子を完成させた。

【0068】

実施例2

工程2−1〜工程2−6を経て電子放出素子を完成させた。

【0069】

工程2−1〜工程2−4は実施例1の工程1−1〜工程1−4と同様であり、それ以降の工程2−5および工程2−6を説明する。

【0070】

〔工程2−5〕

図2(g)における第1開口6付近に感光性ポリマーをパターニングし、その後、真空中で500℃で熱処理を行うことで、上記ポリマーをカーボン化し、電子放出膜5とした。

【0071】

〔工程2−6〕

次に、BHF(エッチングレート:100nm/min)に、11分間浸すことにより、SiO2を、ウエットエッチングし、水洗10分行い、本実施例の電子放出素子を完成させた。

【0072】

実施例3

工程3−1〜工程3−6を経て電子放出素子を完成させた。

【0073】

工程3−1〜工程3−4は実施例1の工程1−1〜工程1−4と同様であり、それ以降の工程3−5および工程3−6を説明する。

【0074】

〔工程3−5〕

感光性ポリマーの粘度とスピンコートの回転数を調整し、開口部の大きい第1開口6には感光性ポリマーが進入するが、開口部の小さい並設された第2開口7には感光性ポリマーが進入しない条件で、感光性ポリマーを塗布した。今回の条件では、感光性ポリマーの粘度を20cp、スピンコートの回転数を3000rpmとした。その後、真空中で550℃で熱処理を行うことで、ポリマーをカーボン化し、数十nmの厚さの電子放出膜5とした〔図7(a)参照〕。

【0075】

〔工程3−6〕

次に、BHF(エッチングレート:100nm/min)中に、超音波をかけながら1分浸し、その後10分間BHF(エッチングレート:100nm/min)中に浸すことにより、SiO2を、ウエットエッチングし、水洗10分行い、本実施例の電子放出素子を完成させた。このとき、並設された第2開口7上に覆われた電子放出膜5は、下側に支持体がないため、完全に取り除かれていた〔図7(b)参照〕。

【0076】

実施例4

図1、図2および図6を用いて本実施例の電子放出素子の製造工程を詳細に説明する。

【0077】

〔工程4−1:図6(a)〕

まず、基板1に石英を用い、十分洗浄を行った後、スパッタ法により、基板1上に、カソード電極材料2として厚さ300nmのPtを成膜した。

【0078】

次に、絶縁層3の作製のために、原料ガスとしてSiH4、NO2を使用してプラズマCVD法により、SiO2を約500nm成膜した。

【0079】

次に、スパッタ法を用いて、絶縁層3’の作製のために原料ガスとしてSiH4、NH4、N2を使用してプラズマCVD法により、SiNxを約500nm成膜した。

【0080】

次に、絶縁層3’上に、ゲート電極4として、Taを100nmの厚さになるように抵抗加熱蒸着により成膜した。

【0081】

〔工程4−2〕

次に、フォトリソグラフィーで、ポジ型フォトレジストのスピンコーティング、フォトマスクパターンを露光、現像し、図1(b)に示されるようなマスクパターン12を形成した。このときの第1開口6の開口径は3μmとした。また、並設した第2開口7の開口も同時に形成した。このときの第2開口7の開口径は2μm、第1開口6と第2開口7間に挟まれた絶縁層3の厚さは1μmとなるようにした。

【0082】

〔工程4−3〕

次に、エッチングガスとしてCF4、H2の混合ガス、エッチングパワーとして150W、エッチング圧力として、5Paの条件で、ドライエッチングを行い、カソード電極2上面でエッチングをストップし、図1(c)と同様の状態とした。

【0083】

〔工程4−4〕

次に、残ったマスクパターン12を、剥離液にて除去し、図1(d)と同様の状態とした。

【0084】

〔工程4−5〕

次に、フォトリソグラフィーで、ポジ型フォトレジストのスピンコーティング、フォトマスクパターンを露光、現像し、図2(e)と同様に、第1開口6が露出するマスクパターン13を形成した。

【0085】

〔工程4−6〕

次に、図2(f)と同様に、プラズマCVD法を用いて、ダイヤモンドライクカーボン膜を約30nm堆積させ、電子放出膜5とした。

【0086】

〔工程4−7〕

次に、マスクパターン13を、剥離液にてリフトオフし、図2(g)の状態とした。

【0087】

〔工程4−8:図6(b)〕

次に、BHF(SiO2のエッチングレート:100nm/min)に、11分間浸すことにより、SiO2を、ウエットエッチングし、水洗10分行い、本実施例の電子放出素子を完成させた。

【0088】

実施例5

工程5−1〜工程5−7を経て電子放出素子を完成させた。

【0089】

工程5−1〜工程5−4は実施例1の工程1−1〜工程1−4と同様であり、それ以降の工程3−5〜工程3−7を説明する。

【0090】

〔工程5−1〕

スパッタ法を用いて、Co膜を10nm成膜した。

【0091】

〔工程5−6〕

次に、BHF(エッチングレート:100nm/min)に、11分間浸すことにより、SiO2を、ウエットエッチングし、水洗10分おこない、図2(h)の電子放出膜5の代わりにCo膜が付着した状態とした。

【0092】

〔工程5−7〕

次に、大気圧のC2H4中で600℃で加熱することで、Coから繊維状炭素を100nm以下の高さになるように成長させ、これを図2(h)の電子放出膜5とすることで、素子を完成させた。なお、繊維状炭素の成長条件はこの条件に限定されるものではない。

【0093】

実施例6

工程は実施例3と同様とした。ただし、第2開口7は図4(a)に示す環状の平面形状とし、第1開口6と第2開口7が一体となった部分の中央部に電子放出層5を有する図4(b)の電子放出素子を作製した。

【0094】

実施例7

本実施例により作製した電子放出素子を図8に示されるように接続し、当該電子放出素子を駆動させるために、Vg、Vaを印加すると、形成された孔の中に強い電界が形成され、Vgや絶縁層3の厚さ、形状、絶縁層の誘電率などにより孔内部の等電位面の形状が定められる。孔の開口の外では主にアノード電極8との距離Hにもよるが、Vaによりほぼ平行な等電位面となる。

【0095】

電子放出膜5にかかる電界がある閾値を超えると、電子放出膜5から電子が放出される。孔の開口から出た電子はアノード電極8に設けられている蛍光体(不図示)に衝突し発光する。

【0096】

実施例1において作製した電子放出素子の上方にアノード電極8を配置して、カソード電極2とゲート電極4との間に電圧を印加し駆動した。

【0097】

印加電圧はVa=10kVで、電子放出膜5とアノード電極との距離Hを2mmとした。

【0098】

ここで、アノード電極8として蛍光体を塗布した電極を用い、電子ビームのサイズを観察した。ここで言う電子ビームサイズとは、発光した蛍光体のピーク輝度が10%の領域までのサイズのことをいう。電子ビーム径は径80μm/80μm(x/y)となった。

【0099】

同様の素子を10回作製し、ビーム径のばらつきを観察したところ、ばらつき幅は±2%以内に収まった。

【0100】

実施例8

上記実施例3で作製した電子放出素子を用いて画像表示装置を作製した。実施例3で示した素子を100×100のマトリクス状に配置した。配線は図9のようにX側をカソード電極2に、Y側をゲート電極4に接続した。素子は、横300μm、縦300μmのピッチで配置した。素子上部には蛍光体を配置した。この結果、マトリクス駆動が可能な高輝度で高精細な画像表示装置が形成できた。

【図面の簡単な説明】

【0101】

【図1】本発明に係る電子放出素子の製造方法の手順の一例を(a)〜(d)の順に示す説明図である。

【図2】本発明に係る電子放出素子の製造方法の手順の一例を図1に続く(e)〜(h)の順に示す説明図である。

【図3】第1開口と第2開口の一例を示す平面図である。

【図4】第1開口と第2開口の他の例を示す図で、(a)は平面図、(b)は第2開口側からのエッチング後の断面図である。

【図5】第2の開口の他の例を示す断面図である。

【図6】絶縁層の他の例を示す図で、(a)は第1開口および第2開口形成前の断面図、(b)は第2開口側からのエッチング後の断面図である。

【図7】電子放出膜の形成手順の他の例を示す図で、(a)は第2開口側からのエッチング前の断面図、(b)は第2開口側からのエッチング後の断面図である。

【図8】本発明の方法で得られた電子放出素子を駆動する時の説明図である。

【図9】本発明の方法で得られた単純マトリックス配置の電子源を示す構成図である。

【図10】本発明の方法で得られた単純マトリックス配置の電子源を用いた画像表示装置を示す概略構成図である。

【図11】本発明にかかる画像形成装置における蛍光膜の説明図である。

【符号の説明】

【0102】

1 基板

2 カソード電極

3 絶縁層

4 ゲート電極

5 電子放出膜

6 第1開口

7 第2開口

8 アノード電極

9 駆動電源

10 高圧電源

11 第1開口6と第2開口7の間の絶縁層

12 マスクパターン

13 マスクパターン

801 電子源基体

802 X方向配線

803 Y方向配線

804 電子放出素子

805 結線

901 リアプレート

902 支持枠

903 ガラス基体

904 蛍光体

905 メタルバック

906 フェースプレート

907 外囲器

1001 黒色導電材

1002 蛍光体

【技術分野】

【0001】

本発明は、電子放出素子、電子源および画像形成装置の製造方法に関する。

【背景技術】

【0002】

電子放出素子には、電界放出型(以下、「FE型」と称する)などがある。FE型には、カソード電極とゲート電極とを絶縁層を間に挟んで積層し、ゲート電極と絶縁層を貫通する開口(ゲートホール)内に位置するカソード電極上に電子放出部材を配置した形態がある。このような形態の代表的な例として上記開口内に円錐状の電子放出部材を設けたスピント型がある。

【0003】

従来、上記電子放出素子の製造方法として、以下のようなものが知られている。

【0004】

(1)開口を形成した後に、リフトオフプロセスにより開口内に電子放出部材を堆積させる方法(例えば、特許文献1参照)。

【0005】

(2)開口内に電子放出部材を堆積させた後、開口内にエッチング液を導入し、絶縁層の開口周壁面に付着した電子放出膜の一部を除去する方法(例えば、特許文献2参照)。

【0006】

(3)カソード電極上に予め電子放出部材を堆積させた後に絶縁層およびゲート電極を形成し、その後に開口を形成する方法(例えば、特許文献3参照)。

【0007】

【特許文献1】特開平8−96704号公報

【特許文献2】特開2000-195448号公報

【特許文献3】特開平8−264109号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、特許文献1のように、電子放出部材の堆積にリフトオフプロセスを用いた場合、開口内への電子放出部材の堆積時に開口内の絶縁層の側壁部に導電性材料である電子放出部材の付着が生じやすい。また、リフトオフ時にも、開口内の絶縁層の側壁部に電子放出部材の付着が生じやすい。このため、ゲート電極とカソード電極間のリーク電流が増大する恐れがある。

【0009】

また、特許文献1には、開口を形成した後に、ウエットエッチングなどによって、開口内に露出する絶縁層の一部を除去することでオーバーハング部を形成しておくことも開示されている。これは、オーバーハング部を形成した開口をマスクとして用いることで、開口内の絶縁層側壁部への電子放出部材の付着を解消しようとするものである。しかし、このようにすると、電子放出部材の成膜方法が指向性の高い成膜方法に限られてしまい、プロセスマージンが小さくなる問題を生じる。

【0010】

特許文献2のように、内部に電子放出部材が堆積された開口内にエッチング液を導入しても、付着している電子放出部材の面積やその付着量にもよるが、付着物自体が障壁となり、十分なエッチングができない。つまり、付着物(電子放出部材の一部)と絶縁層の側壁との間にエッチャントが侵入せずに十分に付着物を取り除くことができず、ゲート電極とカソード電極間のリーク電流を解消できない場合がある。また、開口毎に付着している形態が異なるため、リーク電流のバラツキも生じる。

【0011】

特許文献3の方法によれば、上記付着物によるリーク電流の問題については、解決できる。しかし、この方法では、開口を作製するプロセスにおいて、電子放出部材がエッチングのストップ層となる。そのため、電子放出部材がエッチングに対して十分に遅いエッチングレートを持つ必要がある。このことが、絶縁層および電子放出部材の材料の選択やエッチングプロセスの選択等のプロセスマージンを小さくしてしまう。さらに、長時間エッチングプロセスに電子放出部材が曝されているために、プラズマ等により電子放出部材の劣化が起こってしまう。さらには、この様な方法で製造すると、ゲート電極の直下に電子放出膜の一部が存在することを回避することが難しい。そのため、ゲート電極の直下の電子放出部材の部分から放出された電子は、直接、直上のゲート電極に照射する。このため、このような方法で作成された電子放出素子は無効電流が増加してしまう。

【0012】

本発明はこのような従来技術の課題を解決するためになされたもので、その目的とするところは、リーク電流の少ない高効率な電界放出型の電子放出素子、電子源、および画像表示装置を容易に得ることができるこれらの製造方法を提供することにある。

【課題を解決するための手段】

【0013】

本発明の第1は、(A)第1導電層と該第1導電層上に配置された絶縁層と該絶縁層上に配置された第2導電層とを備え、該絶縁層と該第2導電層とを貫通した第1開口を有する構造体を用意する工程と、

(B)前記第1開口内に電子放出部材を構成する材料を堆積する工程と、

(C)前記絶縁層と第2導電層のうち、少なくとも第2導電層を貫通し、前記第1開口に並設される第2開口を形成する工程と、

(D)前記第2開口と、内部に前記電子放出部材を構成する材料が堆積された前記第1開口との間に存在する絶縁層を、前記第1開口と第2開口とが連通するまでエッチングする工程と、

を有することを特徴とする電子放出素子の製造方法である。

【0014】

本発明の第2は、複数の電子放出素子を備える電子源の製造方法であって、前記複数の電子放出素子の各々が本発明の第1の製造方法により製造されることを特徴とする電子源の製造方法である。

【0015】

本発明の第3は、電子源と該電子源から放出された電子が照射されることにより発光する発光体とを備える画像表示装置の製造方法であって、前記電子源が本発明の第2の製造方法により製造されることを特徴とする画像表示装置の製造方法である。

【発明の効果】

【0016】

本発明によれば、電子放出部材の堆積時に第1開口の周壁に付着した当該電子放出部材が、第2開口側からのエッチングにより、第1開口の周壁の除去と共に除去することができる。したがって、リーク電流の減少、プロセスマージンの増加によるディスプレイ画面内での輝度ムラの減少により、低消費電力のディスプレイを歩留まり良く製造することができる。

【発明を実施するための最良の形態】

【0017】

以下に図面を参照して、この発明の好適な実施の形態を例示的に詳しく説明する。

【0018】

図1および図2は本発明に係る電子放出素子の製造方法のフローの一例を示す図で、以下に、図1および図2の(a)〜(h)の各工程の説明を行う。

【0019】

(1)図1(a)の工程

まず、基板1上にカソード電極2を積層する。基板1としては、予めその表面を十分に洗浄した、石英ガラス、Na等の不純物含有量を減少させたガラス、青板ガラス、シリコン板等にスパッタ法等によりSiO2を積層した積層体、アルミナ等セラミックスの絶縁性基板等を用いることができる。

【0020】

カソード電極2は、一般的に導電性を有しており、蒸着法、スパッタ法等の一般的真空成膜技術、フォトリソグラフィー技術により形成される。カソード電極2の構成材料としては、例えば、Be、Mg、Ti、Zr、Hf、V、Nb、Ta、Mo、W、Al、Cu、Ni、Cr、Au、Pt、Pd等の金属または合金材料、TiC、ZrC、HfC、TaC、SiC、WC等の炭化物、HfB2、ZrB2、LaB6、CeB6、YB4、GdB4等の硼化物、TiN、ZrN、HfN等の窒化物、Si、Ge等の半導体等を用いることができる。カソード電極2の厚さは、通常、10nmから100μmの範囲で設定される。好ましくは100nmから10μmの範囲で選択される。

【0021】

次に、絶縁層3を堆積する。絶縁層3は、スパッタ法等の一般的な真空成膜法、CVD法、真空蒸着法で形成される。厚さは、通常、10nmから100μmの範囲で設定され、好ましくは10nmから5μmの範囲から選択される。構成材料としては、酸化シリコン(典型的にはSiO2)、SiN、酸化アルミニウム(Al2O3)、CaF、アンドープダイヤモンド等、高電界に絶えられる耐圧の高い材料が好ましい。また、絶縁層3の構成材料としては、後述する工程8におけるエッチングによって、後述する工程6で形成する電子放出膜5の構成材料よりもエッチングされやすい材料を選択することが好ましい。

【0022】

さらに、絶縁層3に続いて、ゲート電極4を堆積する。ゲート電極4は、カソード電極2と同様に導電性を有しており、蒸着法、スパッタ法等の一般的真空成膜技術、フォトリソグラフィー技術により形成することができる。ゲート電極7の構成材料としては、例えば、Be、Mg、Ti、Zr、Hf、V、Nb、Ta、Mo、W、Al、Cu、Ni、Cr、Au、Pt、Pd等の金属または合金材料、TiC、ZrC、HfC、TaC、SiC、WC等の炭化物、HfB2、ZrB2、LaB6、CeB6、YB4、GdB4等の硼化物、TiN、ZrN、HfN等の窒化物、Si、Ge等の半導体等を用いることができる。ゲート電極4の厚さは、通常、1nmから100μmの範囲で設定され、好ましくは10nmから1μmの範囲で選択される。

【0023】

なお、カソード電極2とゲート電極4は、同一材料でも異種材料でも良く、また、同一形成方法でも異種方法でも良い。

【0024】

(2)図1(b)の工程

フォトリソグラフィー技術などを使用し、ゲート電極4上に所望のパターンのマスク12を形成する。マスク12の材料としては公知のレジスト材料を用いることができる。マスク12のパターン(開口)は、工程3で形成する第1開口6および第2開口7の形状に応じて適宜選択される。

【0025】

(3)図1(c)の工程

ドライエッチング等のエッチングにより、マスク12に覆われていないゲート電極4と絶縁層3を貫通してカソード電極2に到達する、第1開口6および第1開口6に並ぶ第2開口7を形成する。第1および第2開口6,7の形状は、マスク12の開口形状と同等の形状で形成される。また、第1開口6と第2開口7の作製順序はどちらが先であっても、同時でも良い。また、第2開口7の形成は、下記工程5と工程6の間で行っても良い。

【0026】

第2開口7は、図3に示されるように、第1開口6を囲む位置に間隔をあけて複数設けることができる他、図4(a)に示されるように、第1開口6を連続的に囲む環状に設けることもできる。

【0027】

なお、図1においては、第1開口6と第2開口7の双方ともに、ゲート電極4と絶縁層3を貫通する形態を示した。しかしながら、第2開口7は、図5に示されるように、後述する工程8で行う絶縁層3のエッチングができるよう、少なくともゲート電極4を貫通していれば良い。

【0028】

(4)図1(d)の工程

マスク12を取り除く。

【0029】

(5)図2(e)の工程

第1開口6内のみに電子放出膜5を形成するために、第1開口6に連通した開口を備えるマスク13を形成する。マスク13はフォトリソグラフィー技術などを用いて形成することができる。

【0030】

(6)図2(f)の工程

続いて、第1開口6内に電子放出膜5を形成する。電子放出膜5の形成は、図1のように、リフトオフ技術で行うことができる。また、インクジェット技術を用いれば、電子放出膜5の構成材料を第1開口6内に選択的に堆積させることもできるので、上記マスク13は必ずしも必要としない。電子放出膜5を構成する材料は、例えば、グラファイト、フラーレン、カーボンナノチューブ、ダイヤモンドライクカーボン、ダイヤモンドを分散した炭素および炭素化合物等から適宜選択することができる。好ましくは仕事関数の低いダイヤモンド膜、ダイヤモンドライクカーボン等が良い。電子放出膜5の膜厚は、通常、1nmから5μmの範囲で設定され、好ましくは5nmから100nmの範囲で選択される。

【0031】

(7)図2(g)の工程

マスク13を取り除く。

【0032】

(8)図2(h)の工程

次に、絶縁層3のエッチングを行う。エッチングは指向性の少ないエッチング方法を用いることが好ましい。具体的には等方的なエッチングが好ましく、特にはウエットエッチングが好ましい。上記等方的なエッチング方法としては、ウエットエッチングだけでなくケミカルドライエッチングのように、ラジカルを主エッチング種として利用するドライエッチングも用いることができる。

【0033】

ウエットエッチングに使用される溶液(エッチャント)としては、絶縁層3がエッチングでき、カソード電極2、ゲート電極4、電子放出膜5が実質的にエッチングあるいは劣化されないものが望ましい。ウエットエッチングに使用される溶液のカソード電極2とゲート電極4に対するエッチングレート比は、1/20以下が望ましく、1/100が好適である。また、電子放出膜5に対するエッチングレートは1/50が望ましく、1/200が好適である。このとき使用されるエッチング溶液は、4〜100℃の温度範囲で使用され、好ましくは、20〜50℃の範囲で使用される。このエッチング工程では、少なくとも第1開口6と第2開口7とが連通するまで、第1開口7側から、第2開口7と第1開口6間の絶縁層の壁11〔図2(g)参照〕の一部または全部をエッチングして除去する。

【0034】

カソード電極2とゲート電極4間での電気的なリークは、第1開口6の側壁についた電子放出膜5を構成する材料が主原因である。このため、これを取り除くことで、リーク電流を大幅に減少させることができる。その減少量は、第1開口6の側壁に付着した電子放出膜5を構成する材料を取り除いた量に比例する。そのため、第1開口6の側壁の一部または全部を取り除き、パターン(開口形状)を変化させることで、リーク電流を制御することができる。

【0035】

第2開口7の開口形状は、主として、開口6の形状と大きさ、絶縁層3の厚さから規定できる。このウエットエッチング工程を行った場合、行わなかった場合に比してリーク電流量を8割以上減少することがきる。

【0036】

第2開口7の形状は、どのような形でも良いが、例えば、直線または屈曲したスリット、矩形孔、円形孔、同心円形スリット、矩形環状スリットなどから選択することができる。第2開口7の大きさは、ウエットエッチングを用いる場合においてはエッチャントが十分に入り込む大きさであればよく、例えば矩形形状とした場合の幅、円形とした場合の直径は0.5〜1000μmの範囲であり、好ましくは1μm〜10μmの範囲で使用される。

【0037】

図3に示されるように、複数設けた第2開口7に大きさの大小がある場合、第1開口6と第2開口7との最近接距離B〔図2(g)参照〕は、小さい第2開口7についてはこれを大きい第2開口7についてより小さくすることが好ましい。また、第2開口7が総て同じ大きさである場合、上記最近接距離Bは実質的に一定であることが望ましい。エッチング条件は、絶縁層3の厚さA〔図2(g)参照〕と、絶縁層3をエッチングする速度であるエッチングレートRと、エッチングする時間tとにより実質的に決めることができる。図2(g)に示されるように、第2開口7が第1開口6と同様にゲート電極4と絶縁層3を貫通している場合、第1開口6と第2開口7との間にある絶縁層3を取り除くには、B≦R×tとなるような条件のもとでエッチングを行うことが好ましい。また、図5に示されるように、第2開口7がゲート電極4のみを貫通している場合、第1開口6と第2開口7との間にある絶縁層3の壁11を取り除くためには、(A2+B2)1/2≦R×tとなるような条件のもとでエッチングを行うことが好ましい。

【0038】

また、図3に示されるように、1個の第1開口6に対して、第2開口7が2個以上設けられる場合、第2開口7とその隣に存在する別の第2開口7間の最近接距離Cは、第1開口6と第2開口7との最近接距離Bより大きくしておくこともできるが、最近接距離Bより小さくすることが好ましい。このようにすることによって、図3において破線で囲まれた領域の絶縁層3全体を除去しやすくなり、第1開口6の周壁を全周に亘って連続して除去することが可能となる。この場合、第1開口6周囲のゲート電極4は、第2開口7同士間で連続しているので、図2(h)に示されるようにひさし状に張り出した状態で残されることになる。また、図4(a)に示されるように、第2開口7を第1開口6を囲む環状に形成した場合、図4(a)において破線で囲まれた領域の絶縁層3全体を除去しやすくなり、第1開口6の周壁を全周に亘って連続して除去しやすくなる。この場合、図4(b)に示されるように、第1開口6と第2開口7との間のゲート電極4は、第1開口6の周壁除去と共に除去されることになる。

【0039】

図6は、絶縁層3を設ける場合の他の例を示す図で、を図1(a)においては、絶縁層3を1層形成しているが、図6(a)に示されるように、絶縁層3の上に、該絶縁層3よりもエッチングされにくいもう一つの絶縁層3’を設けることもできる。このようにすると、図6(b)に示されるように、エッチング後に、第1開口6と第2開口7間に残されるゲート電極4の下に絶縁層3’が残されるので、ひさし状に突き出た第1開口6周囲のゲート電極4部分を補強することができる。

【0040】

図7は、電子放出膜5を形成する場合の他の例を示す図で、図7(a)に示されるように、第1開口部6は電子放出膜5の形成材料が入り込みやすい大きさとし、第2開口7は電子放出膜5の形成材料が入り込めない大きさとしておき、その上に電子放出膜5の形成材料を例えば塗布して電子放出膜5を形成することができる。この場合、第2開口7が電子放出膜5で覆われた状態となることもあるが、第2開口7上の電子放出膜5は下側が支持されていないので、エッチング時に超音波振動などで容易に除去することができる。したがって、第2開口7上の電子放出膜5を除去して、第2開口7からの絶縁層3のエッチング除去を行えば、図7(b)のように、第1開口6と第2開口7間の絶縁層3を除去した状態が得られる。

【0041】

図1および図2で説明した本発明の方法で得られる電子放出素子は、例えば図8のように、高圧電源10が接続されたアノード電極8を対向させ、カソード電極2ゲート電極4間に駆動のための電源9から電圧を印加することによって、電子放出膜5から電子を放出させることができる。なお、図8において、1は基板、2はカソード電極、3は絶縁層、4はゲート電極、5は電子放出膜、6は第1開口、7は第1開口6に並設された第2開口である。また、Vgはゲート電極4とカソード電極2の間に印加される電圧、Vaはゲート電極4とアノード電極8間に印加される電圧である。

【0042】

なお、以上説明した例においては、電子放出部材として電子放出膜5を用いた例としたが、本発明の電子放出部材は膜状のものに限られず、いわゆるスピント型のような円錐状のものなども適用することができる。本発明は、カソード電極2とゲート電極4との間に配置される絶縁層3とゲート電極4とを貫通する開口(ゲートホール)を形成した後に、開口内に電子放出部材を堆積させる工程を備える電子放出素子の製造に好ましく適用できる。また、ここでは、カソード電極2上に電子放出膜5を直接配置した形態を示したが、カソード電極2と電子放出膜5との間に電流制限などの目的のために抵抗膜が配置されていてもよい。カソード電極2にはこのような抵抗膜を有する電極も含まれる。

【0043】

次に、本発明の製造方法で作成した電子放出素子を適用した応用例について以下に述べる。

【0044】

本発明の電子放出素子は、その複数個を基体上に配列することによって、例えば電子源、あるいは画像表示装置を構成することができる。

【0045】

図9は、本発明の電子放出素子を複数配して得られる電子源の模式図である。図9において、電子源基体801上に、m本のX方向配線802と、n本のY方向配線803と、多数(m×n個)の電子放出素子804が配設されている。各電子放出素子804は、X方向配線802の一つとY方向配線803の一つとに接続されている。配線802,803と電子放出素子804との接続は、前記したカソード電極とゲート電極を介して行われる。

【0046】

X方向配線802は、Dx1、Dx2、…Dxmのm本の配線から成り、真空蒸着法、印刷法、スパッタ法等を用いて形成された導電性材料で構成することができる。配線の材料、膜厚、幅は適宜設計される。Y方向配線803は、Dy1、Dy2、…Dynのn本の配線から成り、X方向配線802と同様に形成される。これらm本のX方向配線802とn本のY方向配線803との間には、不図示の層間絶縁層が設けられており、両者を電気的に分離している。ここで、mおよびnは共に正の整数である。

【0047】

不図示の層間絶縁層は、真空蒸着法、印刷法、スパッタ法等を用いて形成されたSiO2 等で構成される。不図示の層間絶縁層は、例えば、X方向配線802を形成した基体801の全面或いはその一部に所望の形状で形成され、特にX方向配線802とY方向配線803との交差部の電位差に耐え得るように、膜厚、材料、製法が適宜設定される。X方向配線802とY方向配線803は、それぞれ外部端子として引き出されている。

【0048】

X方向配線802、Y方向配線803、および一対の電極(カソード電極2、ゲート電極4)を構成する材料は、その構成元素の一部あるいは全部が同一であっても、またそれぞれ異なっていても良い。電極を構成する材料と配線材料が同一である場合には、素子電極に接続した配線は素子電極ということもできる。また、素子電極を配線電極として用いることもできる。

【0049】

X方向配線802には、X方向に配列した電子放出素子804の行を選択するための、走査信号を印加する不図示の走査信号印加手段が接続される。一方、Y方向配線803には、Y方向に配列した電子放出素子804の各列を入力信号に応じて変調するための、不図示の変調信号発生手段が接続される。各電子放出素子に印加される駆動電圧は、当該素子に印加される走査信号と変調信号の差電圧として供給される。

【0050】

上記構成においては、単純なマトリクス配線を用いて、個別の電子放出素子を選択し、独立に駆動可能とすることができる。このような単純マトリクス配置の電子源を用いて構成した画像形成装置について、図10を用いて説明する。図10は、画像形成装置の表示パネルの一例を示す模式図である。

【0051】

図10において、801は電子放出素子を複数配した電子源基体、901は電子源基体801を固定したリアプレート、906はガラス基体903の内面に画像形成部材である蛍光体としての蛍光膜904とメタルバック905等が形成されたフェースプレートである。902は支持枠であり、支持枠902には、リアプレート901、フェースプレート906がフリットガラス等を用いて接続されている。907は外囲器であり、例えば、大気中あるいは窒素中で、400〜500℃の温度範囲で10分以上焼成することで、封着して構成される。

【0052】

外囲器907は、上述した通り、フェースプレート906、支持枠902、リアプレート901で構成される。リアプレート901は主に基体801の強度を補強する目的で設けられるため、基体801自体で十分な強度を持つ場合は、別体のリアプレート901は不要とすることができる。即ち、基体801に直接支持枠902を封着し、フェースプレート906、支持枠902および基体801で外囲器907を構成しても良い。一方、フェースプレート906、リアプレート901間に、スペーサーとよばれる不図示の支持体を設置することにより、大気圧に対して十分な強度をもつ外囲器907を構成することもできる。

【0053】

なお、本発明の電子放出素子を用いた画像形成装置では、放出した電子軌道を考慮して、電子放出素子804上部に蛍光体(蛍光膜904)をアライメントして配置する。

【0054】

図11は、本件のパネルに使用した蛍光膜904を示す模式図である。カラーの蛍光膜の場合は、蛍光体の配列により図10(a)に示すブラックストライプあるいは図10(b)に示すブラックマトリクスなどと呼ばれる黒色導電材1001と蛍光体1002とから構成した。

【0055】

本発明の画像形成装置は、テレビジョン放送の表示装置、テレビ会議システムやコンピューター等の表示装置の他、感光性ドラム等を用いて構成された光プリンターとしての画像形成装置等としても用いることができる。

【実施例】

【0056】

以下、本発明の実施例を詳細に説明する。

【0057】

実施例1

図1および図2を用いて本実施例の電子放出素子の製造工程を詳細に説明する。

【0058】

〔工程1−1:図1(a)〕

まず、基板1に石英を用い、十分洗浄を行った後、抵抗加熱蒸着により、基板1上に、カソード電極材料2として厚さ300nmのAlを成膜した。

【0059】

次に、絶縁層3の作製のために、原料ガスとしてSiH4、NO2を使用してプラズマCVD法により、SiO2を約1000nm成膜した。

【0060】

次に、絶縁層3上に、ゲート電極4として、Taを100nmの厚さになるようにスパッタ法により成膜した。

【0061】

〔工程1−2:図1(b)〕

次に、フォトリソグラフィーで、ポジ型フォトレジストのスピンコーティング、フォトマスクパターンを露光、現像し、マスクパターン12を形成した。このときの第1開口6の開口径は3μmとした。また、並設した第2開口7の開口も同時に形成した。このときの第2開口7の開口径は2μm、第1開口6と第2開口7間に挟まれる絶縁層3の厚さは1μmとなるようにした。

【0062】

〔工程1−3:図1(c)〕

次に、エッチングガスとしてCF4、H2の混合ガス、エッチングパワーとして150W、エッチング圧力として、5Paの条件で、ドライエッチングを行い、カソード電極2上面でエッチングをストップした。

【0063】

〔工程1−4:図1(d)〕

次に、残ったマスクパターン12を、剥離液にて除去した。

【0064】

〔工程1−5:図2(e)〕

次に、フォトリソグラフィーで、ポジ型フォトレジストのスピンコーティング、フォトマスクパターンを露光、現像し、第1開口6が露出するマスクパターン13を形成した。

【0065】

〔工程1−6:図2(f)〕

次にプラズマCVD法を用いて、ダイヤモンドライクカーボン膜を約30nm堆積させ、電子放出膜5とした。

【0066】

〔工程1−7:図2(g)〕

次に、マスクパターン13を、剥離液にてリフトオフした。

【0067】

〔工程1−8:図2(h)〕

次に、BHF(エッチングレート:100nm/min)に、11分間浸すことにより、SiO2をウエットエッチングし、水洗を10分行い、本実施例の電子放出素子を完成させた。

【0068】

実施例2

工程2−1〜工程2−6を経て電子放出素子を完成させた。

【0069】

工程2−1〜工程2−4は実施例1の工程1−1〜工程1−4と同様であり、それ以降の工程2−5および工程2−6を説明する。

【0070】

〔工程2−5〕

図2(g)における第1開口6付近に感光性ポリマーをパターニングし、その後、真空中で500℃で熱処理を行うことで、上記ポリマーをカーボン化し、電子放出膜5とした。

【0071】

〔工程2−6〕

次に、BHF(エッチングレート:100nm/min)に、11分間浸すことにより、SiO2を、ウエットエッチングし、水洗10分行い、本実施例の電子放出素子を完成させた。

【0072】

実施例3

工程3−1〜工程3−6を経て電子放出素子を完成させた。

【0073】

工程3−1〜工程3−4は実施例1の工程1−1〜工程1−4と同様であり、それ以降の工程3−5および工程3−6を説明する。

【0074】

〔工程3−5〕

感光性ポリマーの粘度とスピンコートの回転数を調整し、開口部の大きい第1開口6には感光性ポリマーが進入するが、開口部の小さい並設された第2開口7には感光性ポリマーが進入しない条件で、感光性ポリマーを塗布した。今回の条件では、感光性ポリマーの粘度を20cp、スピンコートの回転数を3000rpmとした。その後、真空中で550℃で熱処理を行うことで、ポリマーをカーボン化し、数十nmの厚さの電子放出膜5とした〔図7(a)参照〕。

【0075】

〔工程3−6〕

次に、BHF(エッチングレート:100nm/min)中に、超音波をかけながら1分浸し、その後10分間BHF(エッチングレート:100nm/min)中に浸すことにより、SiO2を、ウエットエッチングし、水洗10分行い、本実施例の電子放出素子を完成させた。このとき、並設された第2開口7上に覆われた電子放出膜5は、下側に支持体がないため、完全に取り除かれていた〔図7(b)参照〕。

【0076】

実施例4

図1、図2および図6を用いて本実施例の電子放出素子の製造工程を詳細に説明する。

【0077】

〔工程4−1:図6(a)〕

まず、基板1に石英を用い、十分洗浄を行った後、スパッタ法により、基板1上に、カソード電極材料2として厚さ300nmのPtを成膜した。

【0078】

次に、絶縁層3の作製のために、原料ガスとしてSiH4、NO2を使用してプラズマCVD法により、SiO2を約500nm成膜した。

【0079】

次に、スパッタ法を用いて、絶縁層3’の作製のために原料ガスとしてSiH4、NH4、N2を使用してプラズマCVD法により、SiNxを約500nm成膜した。

【0080】

次に、絶縁層3’上に、ゲート電極4として、Taを100nmの厚さになるように抵抗加熱蒸着により成膜した。

【0081】

〔工程4−2〕

次に、フォトリソグラフィーで、ポジ型フォトレジストのスピンコーティング、フォトマスクパターンを露光、現像し、図1(b)に示されるようなマスクパターン12を形成した。このときの第1開口6の開口径は3μmとした。また、並設した第2開口7の開口も同時に形成した。このときの第2開口7の開口径は2μm、第1開口6と第2開口7間に挟まれた絶縁層3の厚さは1μmとなるようにした。

【0082】

〔工程4−3〕

次に、エッチングガスとしてCF4、H2の混合ガス、エッチングパワーとして150W、エッチング圧力として、5Paの条件で、ドライエッチングを行い、カソード電極2上面でエッチングをストップし、図1(c)と同様の状態とした。

【0083】

〔工程4−4〕

次に、残ったマスクパターン12を、剥離液にて除去し、図1(d)と同様の状態とした。

【0084】

〔工程4−5〕

次に、フォトリソグラフィーで、ポジ型フォトレジストのスピンコーティング、フォトマスクパターンを露光、現像し、図2(e)と同様に、第1開口6が露出するマスクパターン13を形成した。

【0085】

〔工程4−6〕

次に、図2(f)と同様に、プラズマCVD法を用いて、ダイヤモンドライクカーボン膜を約30nm堆積させ、電子放出膜5とした。

【0086】

〔工程4−7〕

次に、マスクパターン13を、剥離液にてリフトオフし、図2(g)の状態とした。

【0087】

〔工程4−8:図6(b)〕

次に、BHF(SiO2のエッチングレート:100nm/min)に、11分間浸すことにより、SiO2を、ウエットエッチングし、水洗10分行い、本実施例の電子放出素子を完成させた。

【0088】

実施例5

工程5−1〜工程5−7を経て電子放出素子を完成させた。

【0089】

工程5−1〜工程5−4は実施例1の工程1−1〜工程1−4と同様であり、それ以降の工程3−5〜工程3−7を説明する。

【0090】

〔工程5−1〕

スパッタ法を用いて、Co膜を10nm成膜した。

【0091】

〔工程5−6〕

次に、BHF(エッチングレート:100nm/min)に、11分間浸すことにより、SiO2を、ウエットエッチングし、水洗10分おこない、図2(h)の電子放出膜5の代わりにCo膜が付着した状態とした。

【0092】

〔工程5−7〕

次に、大気圧のC2H4中で600℃で加熱することで、Coから繊維状炭素を100nm以下の高さになるように成長させ、これを図2(h)の電子放出膜5とすることで、素子を完成させた。なお、繊維状炭素の成長条件はこの条件に限定されるものではない。

【0093】

実施例6

工程は実施例3と同様とした。ただし、第2開口7は図4(a)に示す環状の平面形状とし、第1開口6と第2開口7が一体となった部分の中央部に電子放出層5を有する図4(b)の電子放出素子を作製した。

【0094】

実施例7

本実施例により作製した電子放出素子を図8に示されるように接続し、当該電子放出素子を駆動させるために、Vg、Vaを印加すると、形成された孔の中に強い電界が形成され、Vgや絶縁層3の厚さ、形状、絶縁層の誘電率などにより孔内部の等電位面の形状が定められる。孔の開口の外では主にアノード電極8との距離Hにもよるが、Vaによりほぼ平行な等電位面となる。

【0095】

電子放出膜5にかかる電界がある閾値を超えると、電子放出膜5から電子が放出される。孔の開口から出た電子はアノード電極8に設けられている蛍光体(不図示)に衝突し発光する。

【0096】

実施例1において作製した電子放出素子の上方にアノード電極8を配置して、カソード電極2とゲート電極4との間に電圧を印加し駆動した。

【0097】

印加電圧はVa=10kVで、電子放出膜5とアノード電極との距離Hを2mmとした。

【0098】

ここで、アノード電極8として蛍光体を塗布した電極を用い、電子ビームのサイズを観察した。ここで言う電子ビームサイズとは、発光した蛍光体のピーク輝度が10%の領域までのサイズのことをいう。電子ビーム径は径80μm/80μm(x/y)となった。

【0099】

同様の素子を10回作製し、ビーム径のばらつきを観察したところ、ばらつき幅は±2%以内に収まった。

【0100】

実施例8

上記実施例3で作製した電子放出素子を用いて画像表示装置を作製した。実施例3で示した素子を100×100のマトリクス状に配置した。配線は図9のようにX側をカソード電極2に、Y側をゲート電極4に接続した。素子は、横300μm、縦300μmのピッチで配置した。素子上部には蛍光体を配置した。この結果、マトリクス駆動が可能な高輝度で高精細な画像表示装置が形成できた。

【図面の簡単な説明】

【0101】

【図1】本発明に係る電子放出素子の製造方法の手順の一例を(a)〜(d)の順に示す説明図である。

【図2】本発明に係る電子放出素子の製造方法の手順の一例を図1に続く(e)〜(h)の順に示す説明図である。

【図3】第1開口と第2開口の一例を示す平面図である。

【図4】第1開口と第2開口の他の例を示す図で、(a)は平面図、(b)は第2開口側からのエッチング後の断面図である。

【図5】第2の開口の他の例を示す断面図である。

【図6】絶縁層の他の例を示す図で、(a)は第1開口および第2開口形成前の断面図、(b)は第2開口側からのエッチング後の断面図である。

【図7】電子放出膜の形成手順の他の例を示す図で、(a)は第2開口側からのエッチング前の断面図、(b)は第2開口側からのエッチング後の断面図である。

【図8】本発明の方法で得られた電子放出素子を駆動する時の説明図である。

【図9】本発明の方法で得られた単純マトリックス配置の電子源を示す構成図である。

【図10】本発明の方法で得られた単純マトリックス配置の電子源を用いた画像表示装置を示す概略構成図である。

【図11】本発明にかかる画像形成装置における蛍光膜の説明図である。

【符号の説明】

【0102】

1 基板

2 カソード電極

3 絶縁層

4 ゲート電極

5 電子放出膜

6 第1開口

7 第2開口

8 アノード電極

9 駆動電源

10 高圧電源

11 第1開口6と第2開口7の間の絶縁層

12 マスクパターン

13 マスクパターン

801 電子源基体

802 X方向配線

803 Y方向配線

804 電子放出素子

805 結線

901 リアプレート

902 支持枠

903 ガラス基体

904 蛍光体

905 メタルバック

906 フェースプレート

907 外囲器

1001 黒色導電材

1002 蛍光体

【特許請求の範囲】

【請求項1】

(A)第1導電層と該第1導電層上に配置された絶縁層と該絶縁層上に配置された第2導電層とを備え、該絶縁層と該第2導電層とを貫通した第1開口を有する構造体を用意する工程と、

(B)前記第1開口内に電子放出部材を構成する材料を堆積する工程と、

(C)前記絶縁層と第2導電層のうち、少なくとも第2導電層を貫通し、前記第1開口に並設される第2開口を形成する工程と、

(D)前記第2開口と、内部に前記電子放出部材を構成する材料が堆積された前記第1開口との間に存在する絶縁層を、前記第1開口と第2開口とが連通するまでエッチングする工程と、

を有することを特徴とする電子放出素子の製造方法。

【請求項2】

前記工程Bは、前記電子放出部材を構成する材料を含む膜を塗布法を用いて行う工程を含むことを特徴とする請求項1に記載の電子放出素子の製造方法。

【請求項3】

前記工程Dにおけるエッチングがウエットエッチングであることを特徴とする請求項1または2に記載の電子放出素子の製造方法。

【請求項4】

複数の電子放出素子を備える電子源の製造方法であって、前記複数の電子放出素子の各々が請求項1乃至3のいずれか1項に記載の製造方法により製造されることを特徴とする電子源の製造方法。

【請求項5】

電子源と該電子源から放出された電子が照射されることにより発光する発光体とを備える画像表示装置の製造方法であって、前記電子源が請求項3に記載の製造方法により製造されることを特徴とする画像表示装置の製造方法。

【請求項1】

(A)第1導電層と該第1導電層上に配置された絶縁層と該絶縁層上に配置された第2導電層とを備え、該絶縁層と該第2導電層とを貫通した第1開口を有する構造体を用意する工程と、

(B)前記第1開口内に電子放出部材を構成する材料を堆積する工程と、

(C)前記絶縁層と第2導電層のうち、少なくとも第2導電層を貫通し、前記第1開口に並設される第2開口を形成する工程と、

(D)前記第2開口と、内部に前記電子放出部材を構成する材料が堆積された前記第1開口との間に存在する絶縁層を、前記第1開口と第2開口とが連通するまでエッチングする工程と、

を有することを特徴とする電子放出素子の製造方法。

【請求項2】

前記工程Bは、前記電子放出部材を構成する材料を含む膜を塗布法を用いて行う工程を含むことを特徴とする請求項1に記載の電子放出素子の製造方法。

【請求項3】

前記工程Dにおけるエッチングがウエットエッチングであることを特徴とする請求項1または2に記載の電子放出素子の製造方法。

【請求項4】

複数の電子放出素子を備える電子源の製造方法であって、前記複数の電子放出素子の各々が請求項1乃至3のいずれか1項に記載の製造方法により製造されることを特徴とする電子源の製造方法。

【請求項5】

電子源と該電子源から放出された電子が照射されることにより発光する発光体とを備える画像表示装置の製造方法であって、前記電子源が請求項3に記載の製造方法により製造されることを特徴とする画像表示装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2007−73208(P2007−73208A)

【公開日】平成19年3月22日(2007.3.22)

【国際特許分類】

【出願番号】特願2005−255835(P2005−255835)

【出願日】平成17年9月5日(2005.9.5)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成19年3月22日(2007.3.22)

【国際特許分類】

【出願日】平成17年9月5日(2005.9.5)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]