電子機器の保守装置、方法、及びプログラム

【課題】電子機器の通常動作を妨げることなく、CPUの経時劣化を保障し、電子機器の性能を維持することができるようにする。

【解決手段】保守装置1は、CPU11に内蔵されるセンサ回路12からCPU11の劣化に応じて変化する劣化情報をCPU11の通常動作時に取得する劣化情報取得部2と、劣化情報に基づいてCPU11の劣化の進行度を示す劣化レベルを判定する劣化レベル判定部3と、劣化レベルの増大に伴いCPU11に印加される電源電圧を増加させるように電源13を制御する電源制御部4とを備える。

【解決手段】保守装置1は、CPU11に内蔵されるセンサ回路12からCPU11の劣化に応じて変化する劣化情報をCPU11の通常動作時に取得する劣化情報取得部2と、劣化情報に基づいてCPU11の劣化の進行度を示す劣化レベルを判定する劣化レベル判定部3と、劣化レベルの増大に伴いCPU11に印加される電源電圧を増加させるように電源13を制御する電源制御部4とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子機器の性能を維持するための保守装置に関し、特にCPU(Central Processing Unit)の経時劣化に対応するものに関する。

【背景技術】

【0002】

コンピュータ等の電子機器の性能は、内蔵されるCPUの劣化に応じて低下する。CPUの劣化の原因として、トランジスタ等の半導体デバイスの経時劣化によるホットキャリア効果が知られている。

【0003】

特許文献1は、劣化診断装置において、診断動作が適切な時期に行われるようにすることを目的として、検査対象となる処理装置と相関的に劣化する被検体の劣化(相関劣化)を検出し、当該相関劣化が検出された場合に処理装置の検査を行う構成を開示している。

【0004】

特許文献2は、機械の劣化を診断するシステムにおいて、劣化を示す事象(失火等)を計測し、当該計測値を劣化診断のパラメータとして演算する構成を開示している。

【0005】

特許文献3は、筺体等に設置される気相吸着用フィルタの経時的な劣化を監視するシステムにおいて、筺体内の気相物質の量を検出し、当該検出量と所定の相関関係を示す情報とに基づいてフィルタの劣化を判断する構成を開示している。

【0006】

特許文献4は、ハードディスク装置を備えた画像処理装置において、ハードディスク装置が所定の基準以上に劣化していると判定された場合には、当該基準以上に劣化していないと判定された場合と異なる制御でジョブの実行を制御する構成を開示している。

【0007】

特許文献5は、マイクロプロセサにおいて、消費電力を増大させずに特定の回路ブロックを高速に動作させることができるようにすることを目的として、各回路ブロックに、値が異なる複数の電源電圧を切り換えて供給し、周波数が異なる複数のクロックを切り換えて供給する構成を開示している。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2010−203816号公報

【特許文献2】特開2007−278105号公報

【特許文献3】特開2009−250959号公報

【特許文献4】特開2009−267660号公報

【特許文献5】特許第3857052号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

上記ホットキャリア効果に起因するCPUの劣化(処理能力の低下)は、多くの場合、当該CPUに印加される電源電圧を増加させることにより解決することができる。従って、例えば、CPUの劣化に起因する障害が検知された場合、電子機器を再起動させる際にCPUへの電源電圧を増加させるような制御を行うことにより、CPU(電子機器)の機能を回復させることができると考えられる。

【0010】

しかしながら、このような再起動を要する処置では、電子機器の使用の円滑性が大きく損なわれる。

【0011】

また、従来の技術においては、ジョブスケジューラによるジョブ管理処理が上述のようなCPUの劣化を考慮せずに行われていた。そのため、劣化により処理能力が低下したCPUに対して、劣化前の状態と同様にジョブの割り当て等が行われる。このことは、電子機器の動作に更なる不具合が生ずる原因になると考えられる。

【0012】

そこで、本発明は、電子機器の通常動作を妨げることなく、CPUの経時劣化を保障し、電子機器の性能を維持することができるようにすることを目的とする。

【課題を解決するための手段】

【0013】

本発明の第1の態様は、CPUに内蔵されるセンサから前記CPUの劣化に応じて変化する劣化情報を前記CPUの通常動作時に取得する劣化情報取得手段と、前記劣化情報に基づいて前記CPUの劣化の進行度を示す劣化レベルを判定する劣化レベル判定手段と、前記劣化レベルの増大に伴い前記CPUに印加される電源電圧を増加させるように電源を制御する電源制御手段とを備える電子機器の保守装置である。

【0014】

また、第2の態様は、CPUに内蔵されるセンサから前記CPUの劣化に応じて変化する劣化情報を前記CPUの通常動作時に取得する劣化情報取得ステップと、前記劣化情報に基づいて前記CPUの劣化の進行度を示す劣化レベルを判定する劣化レベル判定ステップと、前記劣化レベルの増大に伴い前記CPUに印加される電源電圧を大きくするように電源を制御する電源制御ステップとを備える電子機器の保守方法である。

【0015】

また、第3の態様は、コンピュータに、上記保守方法を実行させる電子機器の保守プログラムである。

【発明の効果】

【0016】

本発明によれば、電子機器の通常動作時においてCPUの劣化レベルが判定され、当該劣化レベルに応じてCPUの機能を維持又は回復するための処置が施される。これにより、CPUに経時劣化が生じても、電子機器の通常動作を妨げることなく、その機能の維持又は回復をすることが可能となる。

【図面の簡単な説明】

【0017】

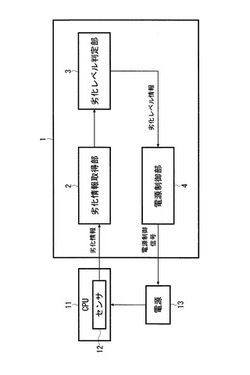

【図1】本発明の実施の形態1に係る電子機器の保守装置の構成を示す図である。

【図2】実施の形態1に係る保守装置が適用される電子機器の構成を示す図である。

【図3】実施の形態1に係るCPUの構成を示す図である。

【図4】実施の形態1に係る診断プロセサの機能的な構成を示す図である。

【図5】実施の形態1に係る保守装置による動作を示すフローチャートである。

【図6】本発明の実施の形態2に係る電子機器の保守装置の構成を示す図である。

【図7】実施の形態2に係る保守装置が適用される電子機器の構成を示す図である。

【図8】実施の形態2に係る診断プロセサの機能的な構成を示す図である。

【図9】実施の形態2に係る保守装置による動作を示すフローチャートである。

【図10】本発明の実施の形態3に係る電子機器の保守装置の構成を示す図である。

【図11】実施の形態3に係る診断プロセサの機能的な構成を示す図である。

【図12】実施の形態3に係る保守装置による動作を示すフローチャートである。

【発明を実施するための形態】

【0018】

実施の形態1

以下、図面を参照して本発明の実施の形態について説明する。尚、同一又は同様の作用効果を奏する箇所については同一の符号を付してその説明を省略する。図1は、本発明の実施の形態1に係る電子機器の保守装置1の構成を示している。保守装置1は、劣化情報取得部2、劣化レベル判定部3、及び電源制御部4を有する。

【0019】

劣化情報取得部2は、電子機器が備えるCPU11に内蔵されるセンサ回路12からCPU11の劣化に応じて変化する劣化情報を取得するものである。劣化情報取得部2は、当該劣化情報の取得動作を、電子機器(CPU11)の通常動作時(起動時を含む)に実行する。即ち、劣化情報の取得は、電子機器が通常動作を実行している間に、例えば定期的に実行される。劣化情報は、センサ回路12から読み出される情報であって、例えば、CPU11の経時劣化の進行度合いに応じて変化する遅延時間、当該遅延時間に相関する情報等が好適である。劣化情報取得部2は、代表的には、マイクロプロセサ、制御・演算プログラム、信号伝達用デバイス等の協働により構成される。尚、本発明は、CPU11が1つの場合に限定されるものではない。また、センサ回路12の数も、CPU11内に1つであることに限定されない。

【0020】

劣化レベル判定部3は、上記劣化情報取得部2により取得された劣化情報に基づいて、CPU11の劣化の進行度を示す劣化レベルを判定するものである。劣化レベル判定部3は、劣化情報取得部2と同様、マイクロプロセサ、制御・演算プログラム等の協働により構成することができる。劣化レベル判定部3は、例えば、劣化情報取得部2から供給される劣化情報を、予め用意した変換テーブル等を用いて劣化レベルに換算する処理等を行う。本明細書及び特許請求の範囲の記載においては、劣化レベルが大きいときCPU11の劣化が大きく、劣化レベルが小さいときCPU11の劣化が小さいものとする。

【0021】

電源制御部4は、上記劣化レベルの増大に伴い、CPU11に印加される電源電圧を増加させるように、電源13を制御するものである。電源制御部4は、劣化情報取得部2及び劣化レベル判定部3と同様、マイクロプロセサ、制御・演算プログラム等の協働により構成することができる。

【0022】

上記構成によれば、CPU11の劣化が進行するに従い、CPU11に供給される電源電圧が増加されていく。これにより、ホットキャリア等に起因する性能低下が発生しても、CPU11の性能を良好な状態に維持することが可能となる。また、当該電源電圧の適正化の処理は、電子機器の通常動作中においても実行可能であるため、電子機器の再起動等を要することなく、性能の維持又は回復を実現することができる。

【0023】

図2は、上記保守装置1が適用される電子機器21の構成を例示している。電子機器21は、複数のCPU11、電源13、及び診断プロセサ15を有する。

【0024】

診断プロセサ15は、制御・演算プログラムに従って動作するマイクロプロセサである。診断プロセサ15は、上記劣化情報(センサ回路12からの出力信号)を入力し、電源制御信号を生成して出力する。

【0025】

図3は、図2に示す例におけるCPU11の構成を示している。当該CPU11は、内部に複数のセンサ回路12を備えている。各センサ回路12は、例えばCPU11の機能ブロック毎に設けられる。各センサ回路12からの出力信号は、上記劣化情報として診断プロセサ15に供給される。これにより、診断プロセサ15は、機能ブロック毎の劣化情報を取得することができる。

【0026】

図4は、診断プロセサ15の機能的な構成を示している。診断プロセサ15は、劣化情報読出部25、変換テーブル保持部26、及び制御部27を有する。

【0027】

劣化情報読出部25は、上記劣化情報(各センサ回路12からの出力信号)を定期的に入力し、これらを制御部27に出力する。

【0028】

変換テーブル保持部26は、劣化情報を上記劣化レベルに変換する変換テーブルを保持する。変換テーブルは、例えば、CPU11の経時劣化の進行度合いに応じて変化する遅延時間と劣化レベルとの相関関係を示すものである。このような変換テーブルは、例えば、トランジスタ等の半導体素子の加速劣化試験の結果、周知の劣化メカニズムに基づく論理的計算式等に基づいて作成することができる。当該変換テーブルを用いれば、CPU11から取得した劣化情報を劣化レベルに変換することができる。尚、当該劣化レベルの判定手法は一例であり、CPU11の劣化を適切に表現できる他の手法を用いても、本発明の技術的目的(CPUの劣化に応じて電源電圧を調整し、CPUの機能を維持すること)を果たすことができる。

【0029】

制御部27は、上記劣化情報及び上記変換テーブルに基づいて、上記劣化レベルを決定する。その後、制御部27は、当該劣化レベルに応じた電源電圧の目標値を算出し、当該目標値を実現するための電源制御信号を生成して電源13に出力する。

【0030】

図5は、上記保守装置1による処理の流れを示している。先ず、診断プロセサ15が各CPU11の劣化情報を読み出す(S1)。当該読み出し処理は、CPU11の通常動作時に、例えば定期的に実行される。

【0031】

次いで、読み出された劣化情報及び変換テーブルに基づいて、CPU11の劣化レベルが判定される(S2)。当該劣化レベルは、CPU11毎に判定される。

【0032】

次いで、判定された劣化レベルが所定レベル以上であるか否かが判定される(S3)。当該所定レベルは、電源電圧の増加が必要とされる劣化レベルの最低値を示す。当該ステップS3において、所定レベル以上でないと判定された場合(NO)には、当該ルーチンを終了する。一方、ステップS3において、所定レベル以上であると判定された場合(YES)には、劣化レベルに応じた電源電圧の目標値を算出し(S4)、当該目標値を実現するための電源制御信号を電源13に出力する(S5)。

【0033】

上記構成及び動作により、複数のCPU11のうち劣化が認められるCPU11の電源電圧が、その劣化レベルに応じて増加される。これにより、ホットキャリア等に起因する性能低下を保障して、CPU11の機能を良好な状態に維持することが可能となる。また、当該電源電圧の適正化処理は、各CPU11の通常動作時においても実行可能であるため、電子機器21の再起動等を要することなく、その性能の維持又は回復を実現することができる。

【0034】

実施の形態2

図6は、本発明の実施の形態2に係る電子機器の保守装置31の構成を示している。保守装置31は、上述した劣化情報取得部2、劣化レベル判定部3、及び電源制御部4に加え、スケジューラ制御部32を有する。

【0035】

スケジューラ制御部32は、電子機器に備えられるジョブスケジューラ35を制御するものである。スケジューラ制御部32は、劣化情報取得部2、劣化レベル判定部3、及び電源制御部4と同様、マイクロプロセサ、制御・演算プログラム等の協働により構成することができる。スケジューラ制御部32は、上記劣化レベルの増大に伴い、CPU11の演算的負荷が小さくなるように、ジョブスケジューラ35を制御する。

【0036】

上記構成によれば、CPU11の劣化が進行すると、上記電源制御部4による電源電圧の増加に加え、スケジューラ制御部32によるCPU11の演算的付加の軽減がなされる。このような構成によれば、CPU11が複数存在する場合に、劣化が認められるCPU11の負荷を軽減し、当該軽減されたジョブの一部又は全部を他の劣化が認められないCPU11に割り当てることにより、電子機器全体としての性能を維持することが可能となる。

【0037】

図7は、上記保守装置31が適用される電子機器41の構成を例示している。電子機器41は、複数のCPU11、電源13、ジョブスケジューラ35、及び診断プロセサ36を有する。

【0038】

診断プロセサ36は、CPU11からの劣化情報を入力し、電源制御信号及び上記スケジューラ制御信号を生成して出力する。ジョブスケジューラ35は、通常のジョブ管理ルール及び診断プロセサ36からのスケジューラ制御信号に基づいて、ジョブ管理情報を生成してCPU11に出力する。

【0039】

図8は、診断プロセサ36の機能的な構成を示している。診断プロセサ36は、劣化情報読出部25、変換テーブル保持部26、及び制御部37を有する。診断プロセサ36の制御部37は、上記実施の形態1に係る診断プロセサ15の制御部27と同様に、劣化情報及び変換テーブルに基づいて劣化レベルを判定する。制御部37と制御部27との相違点は、制御部37が劣化レベルに応じて上記スケジューラ制御信号を生成して出力する点にある。

【0040】

図9は、上記保守装置31による処理の流れを示している。先ず、診断プロセサ36が各CPU11の劣化情報を読み出す(S11)。当該読み出し処理は、CPU11の通常動作時に、例えば定期的に実行される。

【0041】

次いで、読み出された劣化情報及び変換テーブルに基づいて、CPU11の劣化レベルが判定される(S12)。当該劣化レベルは、CPU11毎に判定される。

【0042】

次いで、判定された劣化レベルが所定レベル以上であるか否かが判定される(S13)。当該ステップS13において、所定レベル以上でないと判定された場合(NO)には、当該ルーチンを終了する。一方、ステップS13において、所定レベル以上であると判定された場合(YES)には、劣化レベルに応じた電源電圧の目標値を算出し(S14)、当該目標値を実現するための電源制御信号を電源13に出力する(S15)。

【0043】

更に、劣化レベルに応じて劣化が認められたCPU11の演算的負荷を軽減させるためのスケジューラ制御信号を生成し、ジョブスケジューラ35に出力する(S16)。

【0044】

最後に、ジョブスケジューラ35は、スケジューラ制御信号に従って劣化が認められたCPU11の負荷軽減処理を加味したジョブ管理を実行する(S17)。

【0045】

上記構成及び動作によれば、劣化が認められるCPU11に対して、上述の電源電圧の適正化に加え、演算的負荷の軽減がなされる。そして、当該軽減されたジョブの一部又は全部を他の劣化が認められないCPU11に割り当てることにより、電子機器41全体としての性能を維持することが可能となる。

【0046】

実施の形態3

図10は、本発明の実施の形態3に係る電子機器の保守装置51の構成を示している。保守装置51は、上記実施の形態2に係る保守装置31と比較して、制御選択部52を有する点で相違する。

【0047】

制御選択部52は、電源制御部4により劣化レベルに応じて算出された電源電圧の目標値が、省電力モード等の電源モードに応じて決定される電源電圧の上限値より大きい場合に、電源制御部4による制御(劣化レベルの増大に応じて電源電圧を増大させる制御)を行わず、スケジューラ制御部32による制御(劣化レベルに応じてCPU11の演算的負荷を軽減させる制御)を行わせるものである。制御選択部52は、劣化情報取得部2、劣化レベル判定部3、電源制御部4、及びスケジューラ制御部32と同様、マイクロプロセサ、制御・演算プログラム等の協働により構成することができる。

【0048】

上記構成によれば、電源制御部4による制御が実行できない場合にのみ、スケジューラ制御部32による制御が実行される。例えば、電子機器が省電力モードを実行している場合等には、電源電圧の増加に制約が課される。このような場合には、電源電圧の制御ではなく、ジョブスケジューリングの制御により問題の解決が図られる。

【0049】

図11は、本実施の形態に係る診断プロセサ55の機能的な構成を示している。当該診断プロセサ55は、図7に示す実施の形態2に係る電子機器41の診断プロセサ36に替えて使用される。

【0050】

図11に示す診断プロセサ55は、劣化情報読出部25、変換テーブル保持部26、電源モード情報保持部57、及び制御部58を有する。

【0051】

電源モード情報保持部57は、電源電圧に制約を課す電源モード(省電力モード等)に関する情報を保持する。実行中の電源モードに応じて、電源電圧の上限値が決定される。

【0052】

制御部58は、上述のように劣化レベルに基づいて電源電圧の目標値を算出し、当該目標値が上記電源電圧の上限値を超えるか否かを判定する。制御部58は、当該目標値が当該上限値を超える場合には、上記電源制御信号の生成及び出力を行わず、スケジューラ制御信号の生成及び出力のみを行う。

【0053】

図12は、上記保守装置51による処理の流れを示している。先ず、診断プロセサ55が各CPU11の劣化情報を読み出す(S21)。当該読み出し処理は、CPU11の通常動作時に、例えば定期的に実行される。

【0054】

次いで、読み出された劣化情報及び変換テーブルに基づいて、CPU11の劣化レベルが判定される(S22)。当該劣化レベルは、CPU11毎に判定される。

【0055】

次いで、判定された劣化レベルが所定レベル以上であるか否かが判定される(S23)。当該ステップS23において、所定レベル以上でないと判定された場合(NO)には、当該ルーチンを終了する。一方、ステップS23において、所定レベル以上であると判定された場合(YES)には、劣化レベルに応じた電源電圧の目標値Vaを算出し(S24)、電源モードに応じた電源電圧の上限値Vmaxを算出する(S25)。

【0056】

次いで、Va>Vmaxであるか否かを判定する(S26)。当該ステップS26において、Va>Vmaxでないと判定された場合(NO)には、診断プロセサ55は電源電圧を目標値Vaにするための電源制御信号を電源13に出力する(S27)。

【0057】

一方、ステップS26において、Va>Vmaxであると判定された場合(YES)には、診断プロセサ55は上述したスケジューラ制御信号をジョブスケジューラ35に出力し(S28)、ジョブスケジューラ35は上述したCPU11の負荷軽減を加味したジョブ管理を実行する(S29)。

【0058】

上記構成及び動作によれば、CPU11の劣化が認められる場合に、原則として電源制御部4による制御が行われるが、省電力モードの実行等により当該電源制御の実行が困難である場合には、スケジューラ制御部32によるCPU11の負荷軽減処理が実行される。これにより、省電力モードへの切り換え機能等を有する電子機器において、CPU11の劣化に対する効率的な保守動作を行うことが可能となる。

【0059】

尚、本発明は上記実施の形態に限られるものではなく、趣旨を逸脱しない範囲で適宜変更することが可能なものである。

【符号の説明】

【0060】

1,31,51 保守装置

2 劣化情報取得部

3 劣化レベル判定部

4 電源制御部

11 CPU

12 センサ回路

13 電源

15,36,55 診断プロセサ

21,41,51 電子機器

25 劣化情報読出部

26 変換テーブル保持部

27,37,58 制御部

32 スケジューラ制御部

35 ジョブスケジューラ

57 電源モード情報保持部

【技術分野】

【0001】

本発明は、電子機器の性能を維持するための保守装置に関し、特にCPU(Central Processing Unit)の経時劣化に対応するものに関する。

【背景技術】

【0002】

コンピュータ等の電子機器の性能は、内蔵されるCPUの劣化に応じて低下する。CPUの劣化の原因として、トランジスタ等の半導体デバイスの経時劣化によるホットキャリア効果が知られている。

【0003】

特許文献1は、劣化診断装置において、診断動作が適切な時期に行われるようにすることを目的として、検査対象となる処理装置と相関的に劣化する被検体の劣化(相関劣化)を検出し、当該相関劣化が検出された場合に処理装置の検査を行う構成を開示している。

【0004】

特許文献2は、機械の劣化を診断するシステムにおいて、劣化を示す事象(失火等)を計測し、当該計測値を劣化診断のパラメータとして演算する構成を開示している。

【0005】

特許文献3は、筺体等に設置される気相吸着用フィルタの経時的な劣化を監視するシステムにおいて、筺体内の気相物質の量を検出し、当該検出量と所定の相関関係を示す情報とに基づいてフィルタの劣化を判断する構成を開示している。

【0006】

特許文献4は、ハードディスク装置を備えた画像処理装置において、ハードディスク装置が所定の基準以上に劣化していると判定された場合には、当該基準以上に劣化していないと判定された場合と異なる制御でジョブの実行を制御する構成を開示している。

【0007】

特許文献5は、マイクロプロセサにおいて、消費電力を増大させずに特定の回路ブロックを高速に動作させることができるようにすることを目的として、各回路ブロックに、値が異なる複数の電源電圧を切り換えて供給し、周波数が異なる複数のクロックを切り換えて供給する構成を開示している。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2010−203816号公報

【特許文献2】特開2007−278105号公報

【特許文献3】特開2009−250959号公報

【特許文献4】特開2009−267660号公報

【特許文献5】特許第3857052号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

上記ホットキャリア効果に起因するCPUの劣化(処理能力の低下)は、多くの場合、当該CPUに印加される電源電圧を増加させることにより解決することができる。従って、例えば、CPUの劣化に起因する障害が検知された場合、電子機器を再起動させる際にCPUへの電源電圧を増加させるような制御を行うことにより、CPU(電子機器)の機能を回復させることができると考えられる。

【0010】

しかしながら、このような再起動を要する処置では、電子機器の使用の円滑性が大きく損なわれる。

【0011】

また、従来の技術においては、ジョブスケジューラによるジョブ管理処理が上述のようなCPUの劣化を考慮せずに行われていた。そのため、劣化により処理能力が低下したCPUに対して、劣化前の状態と同様にジョブの割り当て等が行われる。このことは、電子機器の動作に更なる不具合が生ずる原因になると考えられる。

【0012】

そこで、本発明は、電子機器の通常動作を妨げることなく、CPUの経時劣化を保障し、電子機器の性能を維持することができるようにすることを目的とする。

【課題を解決するための手段】

【0013】

本発明の第1の態様は、CPUに内蔵されるセンサから前記CPUの劣化に応じて変化する劣化情報を前記CPUの通常動作時に取得する劣化情報取得手段と、前記劣化情報に基づいて前記CPUの劣化の進行度を示す劣化レベルを判定する劣化レベル判定手段と、前記劣化レベルの増大に伴い前記CPUに印加される電源電圧を増加させるように電源を制御する電源制御手段とを備える電子機器の保守装置である。

【0014】

また、第2の態様は、CPUに内蔵されるセンサから前記CPUの劣化に応じて変化する劣化情報を前記CPUの通常動作時に取得する劣化情報取得ステップと、前記劣化情報に基づいて前記CPUの劣化の進行度を示す劣化レベルを判定する劣化レベル判定ステップと、前記劣化レベルの増大に伴い前記CPUに印加される電源電圧を大きくするように電源を制御する電源制御ステップとを備える電子機器の保守方法である。

【0015】

また、第3の態様は、コンピュータに、上記保守方法を実行させる電子機器の保守プログラムである。

【発明の効果】

【0016】

本発明によれば、電子機器の通常動作時においてCPUの劣化レベルが判定され、当該劣化レベルに応じてCPUの機能を維持又は回復するための処置が施される。これにより、CPUに経時劣化が生じても、電子機器の通常動作を妨げることなく、その機能の維持又は回復をすることが可能となる。

【図面の簡単な説明】

【0017】

【図1】本発明の実施の形態1に係る電子機器の保守装置の構成を示す図である。

【図2】実施の形態1に係る保守装置が適用される電子機器の構成を示す図である。

【図3】実施の形態1に係るCPUの構成を示す図である。

【図4】実施の形態1に係る診断プロセサの機能的な構成を示す図である。

【図5】実施の形態1に係る保守装置による動作を示すフローチャートである。

【図6】本発明の実施の形態2に係る電子機器の保守装置の構成を示す図である。

【図7】実施の形態2に係る保守装置が適用される電子機器の構成を示す図である。

【図8】実施の形態2に係る診断プロセサの機能的な構成を示す図である。

【図9】実施の形態2に係る保守装置による動作を示すフローチャートである。

【図10】本発明の実施の形態3に係る電子機器の保守装置の構成を示す図である。

【図11】実施の形態3に係る診断プロセサの機能的な構成を示す図である。

【図12】実施の形態3に係る保守装置による動作を示すフローチャートである。

【発明を実施するための形態】

【0018】

実施の形態1

以下、図面を参照して本発明の実施の形態について説明する。尚、同一又は同様の作用効果を奏する箇所については同一の符号を付してその説明を省略する。図1は、本発明の実施の形態1に係る電子機器の保守装置1の構成を示している。保守装置1は、劣化情報取得部2、劣化レベル判定部3、及び電源制御部4を有する。

【0019】

劣化情報取得部2は、電子機器が備えるCPU11に内蔵されるセンサ回路12からCPU11の劣化に応じて変化する劣化情報を取得するものである。劣化情報取得部2は、当該劣化情報の取得動作を、電子機器(CPU11)の通常動作時(起動時を含む)に実行する。即ち、劣化情報の取得は、電子機器が通常動作を実行している間に、例えば定期的に実行される。劣化情報は、センサ回路12から読み出される情報であって、例えば、CPU11の経時劣化の進行度合いに応じて変化する遅延時間、当該遅延時間に相関する情報等が好適である。劣化情報取得部2は、代表的には、マイクロプロセサ、制御・演算プログラム、信号伝達用デバイス等の協働により構成される。尚、本発明は、CPU11が1つの場合に限定されるものではない。また、センサ回路12の数も、CPU11内に1つであることに限定されない。

【0020】

劣化レベル判定部3は、上記劣化情報取得部2により取得された劣化情報に基づいて、CPU11の劣化の進行度を示す劣化レベルを判定するものである。劣化レベル判定部3は、劣化情報取得部2と同様、マイクロプロセサ、制御・演算プログラム等の協働により構成することができる。劣化レベル判定部3は、例えば、劣化情報取得部2から供給される劣化情報を、予め用意した変換テーブル等を用いて劣化レベルに換算する処理等を行う。本明細書及び特許請求の範囲の記載においては、劣化レベルが大きいときCPU11の劣化が大きく、劣化レベルが小さいときCPU11の劣化が小さいものとする。

【0021】

電源制御部4は、上記劣化レベルの増大に伴い、CPU11に印加される電源電圧を増加させるように、電源13を制御するものである。電源制御部4は、劣化情報取得部2及び劣化レベル判定部3と同様、マイクロプロセサ、制御・演算プログラム等の協働により構成することができる。

【0022】

上記構成によれば、CPU11の劣化が進行するに従い、CPU11に供給される電源電圧が増加されていく。これにより、ホットキャリア等に起因する性能低下が発生しても、CPU11の性能を良好な状態に維持することが可能となる。また、当該電源電圧の適正化の処理は、電子機器の通常動作中においても実行可能であるため、電子機器の再起動等を要することなく、性能の維持又は回復を実現することができる。

【0023】

図2は、上記保守装置1が適用される電子機器21の構成を例示している。電子機器21は、複数のCPU11、電源13、及び診断プロセサ15を有する。

【0024】

診断プロセサ15は、制御・演算プログラムに従って動作するマイクロプロセサである。診断プロセサ15は、上記劣化情報(センサ回路12からの出力信号)を入力し、電源制御信号を生成して出力する。

【0025】

図3は、図2に示す例におけるCPU11の構成を示している。当該CPU11は、内部に複数のセンサ回路12を備えている。各センサ回路12は、例えばCPU11の機能ブロック毎に設けられる。各センサ回路12からの出力信号は、上記劣化情報として診断プロセサ15に供給される。これにより、診断プロセサ15は、機能ブロック毎の劣化情報を取得することができる。

【0026】

図4は、診断プロセサ15の機能的な構成を示している。診断プロセサ15は、劣化情報読出部25、変換テーブル保持部26、及び制御部27を有する。

【0027】

劣化情報読出部25は、上記劣化情報(各センサ回路12からの出力信号)を定期的に入力し、これらを制御部27に出力する。

【0028】

変換テーブル保持部26は、劣化情報を上記劣化レベルに変換する変換テーブルを保持する。変換テーブルは、例えば、CPU11の経時劣化の進行度合いに応じて変化する遅延時間と劣化レベルとの相関関係を示すものである。このような変換テーブルは、例えば、トランジスタ等の半導体素子の加速劣化試験の結果、周知の劣化メカニズムに基づく論理的計算式等に基づいて作成することができる。当該変換テーブルを用いれば、CPU11から取得した劣化情報を劣化レベルに変換することができる。尚、当該劣化レベルの判定手法は一例であり、CPU11の劣化を適切に表現できる他の手法を用いても、本発明の技術的目的(CPUの劣化に応じて電源電圧を調整し、CPUの機能を維持すること)を果たすことができる。

【0029】

制御部27は、上記劣化情報及び上記変換テーブルに基づいて、上記劣化レベルを決定する。その後、制御部27は、当該劣化レベルに応じた電源電圧の目標値を算出し、当該目標値を実現するための電源制御信号を生成して電源13に出力する。

【0030】

図5は、上記保守装置1による処理の流れを示している。先ず、診断プロセサ15が各CPU11の劣化情報を読み出す(S1)。当該読み出し処理は、CPU11の通常動作時に、例えば定期的に実行される。

【0031】

次いで、読み出された劣化情報及び変換テーブルに基づいて、CPU11の劣化レベルが判定される(S2)。当該劣化レベルは、CPU11毎に判定される。

【0032】

次いで、判定された劣化レベルが所定レベル以上であるか否かが判定される(S3)。当該所定レベルは、電源電圧の増加が必要とされる劣化レベルの最低値を示す。当該ステップS3において、所定レベル以上でないと判定された場合(NO)には、当該ルーチンを終了する。一方、ステップS3において、所定レベル以上であると判定された場合(YES)には、劣化レベルに応じた電源電圧の目標値を算出し(S4)、当該目標値を実現するための電源制御信号を電源13に出力する(S5)。

【0033】

上記構成及び動作により、複数のCPU11のうち劣化が認められるCPU11の電源電圧が、その劣化レベルに応じて増加される。これにより、ホットキャリア等に起因する性能低下を保障して、CPU11の機能を良好な状態に維持することが可能となる。また、当該電源電圧の適正化処理は、各CPU11の通常動作時においても実行可能であるため、電子機器21の再起動等を要することなく、その性能の維持又は回復を実現することができる。

【0034】

実施の形態2

図6は、本発明の実施の形態2に係る電子機器の保守装置31の構成を示している。保守装置31は、上述した劣化情報取得部2、劣化レベル判定部3、及び電源制御部4に加え、スケジューラ制御部32を有する。

【0035】

スケジューラ制御部32は、電子機器に備えられるジョブスケジューラ35を制御するものである。スケジューラ制御部32は、劣化情報取得部2、劣化レベル判定部3、及び電源制御部4と同様、マイクロプロセサ、制御・演算プログラム等の協働により構成することができる。スケジューラ制御部32は、上記劣化レベルの増大に伴い、CPU11の演算的負荷が小さくなるように、ジョブスケジューラ35を制御する。

【0036】

上記構成によれば、CPU11の劣化が進行すると、上記電源制御部4による電源電圧の増加に加え、スケジューラ制御部32によるCPU11の演算的付加の軽減がなされる。このような構成によれば、CPU11が複数存在する場合に、劣化が認められるCPU11の負荷を軽減し、当該軽減されたジョブの一部又は全部を他の劣化が認められないCPU11に割り当てることにより、電子機器全体としての性能を維持することが可能となる。

【0037】

図7は、上記保守装置31が適用される電子機器41の構成を例示している。電子機器41は、複数のCPU11、電源13、ジョブスケジューラ35、及び診断プロセサ36を有する。

【0038】

診断プロセサ36は、CPU11からの劣化情報を入力し、電源制御信号及び上記スケジューラ制御信号を生成して出力する。ジョブスケジューラ35は、通常のジョブ管理ルール及び診断プロセサ36からのスケジューラ制御信号に基づいて、ジョブ管理情報を生成してCPU11に出力する。

【0039】

図8は、診断プロセサ36の機能的な構成を示している。診断プロセサ36は、劣化情報読出部25、変換テーブル保持部26、及び制御部37を有する。診断プロセサ36の制御部37は、上記実施の形態1に係る診断プロセサ15の制御部27と同様に、劣化情報及び変換テーブルに基づいて劣化レベルを判定する。制御部37と制御部27との相違点は、制御部37が劣化レベルに応じて上記スケジューラ制御信号を生成して出力する点にある。

【0040】

図9は、上記保守装置31による処理の流れを示している。先ず、診断プロセサ36が各CPU11の劣化情報を読み出す(S11)。当該読み出し処理は、CPU11の通常動作時に、例えば定期的に実行される。

【0041】

次いで、読み出された劣化情報及び変換テーブルに基づいて、CPU11の劣化レベルが判定される(S12)。当該劣化レベルは、CPU11毎に判定される。

【0042】

次いで、判定された劣化レベルが所定レベル以上であるか否かが判定される(S13)。当該ステップS13において、所定レベル以上でないと判定された場合(NO)には、当該ルーチンを終了する。一方、ステップS13において、所定レベル以上であると判定された場合(YES)には、劣化レベルに応じた電源電圧の目標値を算出し(S14)、当該目標値を実現するための電源制御信号を電源13に出力する(S15)。

【0043】

更に、劣化レベルに応じて劣化が認められたCPU11の演算的負荷を軽減させるためのスケジューラ制御信号を生成し、ジョブスケジューラ35に出力する(S16)。

【0044】

最後に、ジョブスケジューラ35は、スケジューラ制御信号に従って劣化が認められたCPU11の負荷軽減処理を加味したジョブ管理を実行する(S17)。

【0045】

上記構成及び動作によれば、劣化が認められるCPU11に対して、上述の電源電圧の適正化に加え、演算的負荷の軽減がなされる。そして、当該軽減されたジョブの一部又は全部を他の劣化が認められないCPU11に割り当てることにより、電子機器41全体としての性能を維持することが可能となる。

【0046】

実施の形態3

図10は、本発明の実施の形態3に係る電子機器の保守装置51の構成を示している。保守装置51は、上記実施の形態2に係る保守装置31と比較して、制御選択部52を有する点で相違する。

【0047】

制御選択部52は、電源制御部4により劣化レベルに応じて算出された電源電圧の目標値が、省電力モード等の電源モードに応じて決定される電源電圧の上限値より大きい場合に、電源制御部4による制御(劣化レベルの増大に応じて電源電圧を増大させる制御)を行わず、スケジューラ制御部32による制御(劣化レベルに応じてCPU11の演算的負荷を軽減させる制御)を行わせるものである。制御選択部52は、劣化情報取得部2、劣化レベル判定部3、電源制御部4、及びスケジューラ制御部32と同様、マイクロプロセサ、制御・演算プログラム等の協働により構成することができる。

【0048】

上記構成によれば、電源制御部4による制御が実行できない場合にのみ、スケジューラ制御部32による制御が実行される。例えば、電子機器が省電力モードを実行している場合等には、電源電圧の増加に制約が課される。このような場合には、電源電圧の制御ではなく、ジョブスケジューリングの制御により問題の解決が図られる。

【0049】

図11は、本実施の形態に係る診断プロセサ55の機能的な構成を示している。当該診断プロセサ55は、図7に示す実施の形態2に係る電子機器41の診断プロセサ36に替えて使用される。

【0050】

図11に示す診断プロセサ55は、劣化情報読出部25、変換テーブル保持部26、電源モード情報保持部57、及び制御部58を有する。

【0051】

電源モード情報保持部57は、電源電圧に制約を課す電源モード(省電力モード等)に関する情報を保持する。実行中の電源モードに応じて、電源電圧の上限値が決定される。

【0052】

制御部58は、上述のように劣化レベルに基づいて電源電圧の目標値を算出し、当該目標値が上記電源電圧の上限値を超えるか否かを判定する。制御部58は、当該目標値が当該上限値を超える場合には、上記電源制御信号の生成及び出力を行わず、スケジューラ制御信号の生成及び出力のみを行う。

【0053】

図12は、上記保守装置51による処理の流れを示している。先ず、診断プロセサ55が各CPU11の劣化情報を読み出す(S21)。当該読み出し処理は、CPU11の通常動作時に、例えば定期的に実行される。

【0054】

次いで、読み出された劣化情報及び変換テーブルに基づいて、CPU11の劣化レベルが判定される(S22)。当該劣化レベルは、CPU11毎に判定される。

【0055】

次いで、判定された劣化レベルが所定レベル以上であるか否かが判定される(S23)。当該ステップS23において、所定レベル以上でないと判定された場合(NO)には、当該ルーチンを終了する。一方、ステップS23において、所定レベル以上であると判定された場合(YES)には、劣化レベルに応じた電源電圧の目標値Vaを算出し(S24)、電源モードに応じた電源電圧の上限値Vmaxを算出する(S25)。

【0056】

次いで、Va>Vmaxであるか否かを判定する(S26)。当該ステップS26において、Va>Vmaxでないと判定された場合(NO)には、診断プロセサ55は電源電圧を目標値Vaにするための電源制御信号を電源13に出力する(S27)。

【0057】

一方、ステップS26において、Va>Vmaxであると判定された場合(YES)には、診断プロセサ55は上述したスケジューラ制御信号をジョブスケジューラ35に出力し(S28)、ジョブスケジューラ35は上述したCPU11の負荷軽減を加味したジョブ管理を実行する(S29)。

【0058】

上記構成及び動作によれば、CPU11の劣化が認められる場合に、原則として電源制御部4による制御が行われるが、省電力モードの実行等により当該電源制御の実行が困難である場合には、スケジューラ制御部32によるCPU11の負荷軽減処理が実行される。これにより、省電力モードへの切り換え機能等を有する電子機器において、CPU11の劣化に対する効率的な保守動作を行うことが可能となる。

【0059】

尚、本発明は上記実施の形態に限られるものではなく、趣旨を逸脱しない範囲で適宜変更することが可能なものである。

【符号の説明】

【0060】

1,31,51 保守装置

2 劣化情報取得部

3 劣化レベル判定部

4 電源制御部

11 CPU

12 センサ回路

13 電源

15,36,55 診断プロセサ

21,41,51 電子機器

25 劣化情報読出部

26 変換テーブル保持部

27,37,58 制御部

32 スケジューラ制御部

35 ジョブスケジューラ

57 電源モード情報保持部

【特許請求の範囲】

【請求項1】

CPUに内蔵されるセンサから前記CPUの劣化に応じて変化する劣化情報を前記CPUの通常動作時に取得する劣化情報取得手段と、

前記劣化情報に基づいて前記CPUの劣化の進行度を示す劣化レベルを判定する劣化レベル判定手段と、

前記劣化レベルの増大に伴い前記CPUに印加される電源電圧を増加させるように電源を制御する電源制御手段と、

を備える電子機器の保守装置。

【請求項2】

前記劣化レベルの増大に伴い前記CPUの演算的負荷が小さくなるようにジョブスケジューラを制御するスケジューラ制御手段、

を更に備える請求項1に記載の電子機器の保守装置。

【請求項3】

前記CPUを複数備える電子機器に用いられ、

前記スケジューラ制御手段は、前記劣化レベルが比較的低い前記CPUに対して優先的にジョブが割り当てられるように前記ジョブスケジューラを制御する、

請求項2に記載の電子機器の保守方法。

【請求項4】

前記劣化レベルに応じて算出された前記電源電圧の目標値が電源モードに応じて決定される前記電源電圧の上限値より大きい場合に、前記電源制御手段による制御を行わず、前記スケジューラ制御手段による制御を行わせる制御選択手段、

を更に備える請求項2又は3に記載の電子機器の保守装置。

【請求項5】

CPUに内蔵されるセンサから前記CPUの劣化に応じて変化する劣化情報を前記CPUの通常動作時に取得する劣化情報取得ステップと、

前記劣化情報に基づいて前記CPUの劣化の進行度を示す劣化レベルを判定する劣化レベル判定ステップと、

前記劣化レベルの増大に伴い前記CPUに印加される電源電圧を大きくするように電源を制御する電源制御ステップと、

を備える電子機器の保守方法。

【請求項6】

前記劣化レベルの増大に伴い前記CPUの演算的負荷が小さくなるようにジョブスケジューラを制御するスケジューラ制御ステップ、

を更に備える請求項5に記載の電子機器の保守方法。

【請求項7】

前記CPUを複数備える電子機器に用いられ、

前記スケジューラ制御ステップは、前記劣化レベルが比較的低い前記CPUに対して優先的にジョブが割り当てられるように前記ジョブスケジューラを制御する、

請求項6に記載の電子機器の保守方法。

【請求項8】

前記劣化レベルに応じて算出された前記電源電圧の目標値が電源モードに応じて決定される前記電源電圧の上限値より大きい場合に、前記電源制御ステップによる制御を行わず、前記スケジューラ制御ステップによる制御を行わせる制御選択ステップ、

を更に備える請求項6又は7に記載の電子機器の保守方法。

【請求項9】

コンピュータに、請求項5〜8のいずれか1項に記載の方法を実行させる電子機器の保守プログラム。

【請求項1】

CPUに内蔵されるセンサから前記CPUの劣化に応じて変化する劣化情報を前記CPUの通常動作時に取得する劣化情報取得手段と、

前記劣化情報に基づいて前記CPUの劣化の進行度を示す劣化レベルを判定する劣化レベル判定手段と、

前記劣化レベルの増大に伴い前記CPUに印加される電源電圧を増加させるように電源を制御する電源制御手段と、

を備える電子機器の保守装置。

【請求項2】

前記劣化レベルの増大に伴い前記CPUの演算的負荷が小さくなるようにジョブスケジューラを制御するスケジューラ制御手段、

を更に備える請求項1に記載の電子機器の保守装置。

【請求項3】

前記CPUを複数備える電子機器に用いられ、

前記スケジューラ制御手段は、前記劣化レベルが比較的低い前記CPUに対して優先的にジョブが割り当てられるように前記ジョブスケジューラを制御する、

請求項2に記載の電子機器の保守方法。

【請求項4】

前記劣化レベルに応じて算出された前記電源電圧の目標値が電源モードに応じて決定される前記電源電圧の上限値より大きい場合に、前記電源制御手段による制御を行わず、前記スケジューラ制御手段による制御を行わせる制御選択手段、

を更に備える請求項2又は3に記載の電子機器の保守装置。

【請求項5】

CPUに内蔵されるセンサから前記CPUの劣化に応じて変化する劣化情報を前記CPUの通常動作時に取得する劣化情報取得ステップと、

前記劣化情報に基づいて前記CPUの劣化の進行度を示す劣化レベルを判定する劣化レベル判定ステップと、

前記劣化レベルの増大に伴い前記CPUに印加される電源電圧を大きくするように電源を制御する電源制御ステップと、

を備える電子機器の保守方法。

【請求項6】

前記劣化レベルの増大に伴い前記CPUの演算的負荷が小さくなるようにジョブスケジューラを制御するスケジューラ制御ステップ、

を更に備える請求項5に記載の電子機器の保守方法。

【請求項7】

前記CPUを複数備える電子機器に用いられ、

前記スケジューラ制御ステップは、前記劣化レベルが比較的低い前記CPUに対して優先的にジョブが割り当てられるように前記ジョブスケジューラを制御する、

請求項6に記載の電子機器の保守方法。

【請求項8】

前記劣化レベルに応じて算出された前記電源電圧の目標値が電源モードに応じて決定される前記電源電圧の上限値より大きい場合に、前記電源制御ステップによる制御を行わず、前記スケジューラ制御ステップによる制御を行わせる制御選択ステップ、

を更に備える請求項6又は7に記載の電子機器の保守方法。

【請求項9】

コンピュータに、請求項5〜8のいずれか1項に記載の方法を実行させる電子機器の保守プログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−54691(P2013−54691A)

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願番号】特願2011−194241(P2011−194241)

【出願日】平成23年9月6日(2011.9.6)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願日】平成23年9月6日(2011.9.6)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]