電子機器の製造方法

【課題】低コストで、かつ短時間で、EMC対策が精度よくなされた電子機器を設計、製造できる電子機器の製造方法を提供する。

【解決手段】金属材料または導電性セラミックスを含む厚さ5〜200nmのノイズ抑制層10を有する電子機器(プリント配線板20)の製造方法であって、(a)ノイズ抑制層を有する電子機器を設計する工程と、(b)設計された電子機器について、電磁界シミュレータを用いて電磁界解析を行い、シミュレーション結果を得る工程と、(c)シミュレーション結果に基づいて、電子機器のEMCを評価し、設計を検証する工程と、(d)設計を検証した結果に基づいて、電子機器を製造する工程とを有し、(b)工程において、複数の周波数におけるノイズ抑制層の複素誘電率および複素透磁率を電磁界シミュレータに入力する、電子機器の製造方法。

【解決手段】金属材料または導電性セラミックスを含む厚さ5〜200nmのノイズ抑制層10を有する電子機器(プリント配線板20)の製造方法であって、(a)ノイズ抑制層を有する電子機器を設計する工程と、(b)設計された電子機器について、電磁界シミュレータを用いて電磁界解析を行い、シミュレーション結果を得る工程と、(c)シミュレーション結果に基づいて、電子機器のEMCを評価し、設計を検証する工程と、(d)設計を検証した結果に基づいて、電子機器を製造する工程とを有し、(b)工程において、複数の周波数におけるノイズ抑制層の複素誘電率および複素透磁率を電磁界シミュレータに入力する、電子機器の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子機器の製造方法に関する。

【背景技術】

【0002】

近年、ユビキタス社会が訪れ、情報処理機器(パソコン、ゲーム機器等。)、通信機器(携帯電話等。)等の電子機器においては、MPUの高速化、多機能化、複合化、およびメモリ等の記録装置の高速化が進行している。これに伴い、電子機器には、電子機器から放射されるノイズ、または電子機器内の導体を伝導するノイズによって、電子機器自身または他の電子機器が影響を受けないこと、すなわちEMC(Electromagnetic Compatibility、電磁環境両立性)が求められている。

これらノイズとしては、MPU、電子部品等が実装されたプリント配線板内の導体のインピーダンス不整合によるノイズ、導体間のクロストークによるノイズ、MPU等の半導体素子の同時スイッチングによる電源層とグランド層との間の平行平板共振によって誘起されるノイズ等がある。

【0003】

電源層とグランド層との間の平行平板共振によって誘起されるノイズが抑えられた電子機器としては、下記プリント配線板が提案されている。

(1)電源層、グランド層の少なくとも一方に、あらかじめ定められた範囲の表面抵抗率を有する抵抗性導体膜を一体化したプリント配線板(特許文献1)。

(2)電源層とグランド層との間に、金属材料を含み、かつ所定の表面抵抗を有する、厚さ5〜200nmのノイズ抑制層を、絶縁層を介して配置したプリント配線板(特許文献2)。

【0004】

電子機器を設計するに際しては、仮設計された電子機器について電磁界シミュレータを用いて電磁界解析を行い、シミュレーション結果に基づいて電子機器のEMCを評価し、該設計がEMC対策として最適なものかどうかを検討することが行われる。具体的には、信号品質に関わるSI(signal integrity)系の検証、電源の電流、電圧変動に関わるPI(power integrity)系の検証、放射ノイズに関わるEMI(electro magnetic interference)系の検証を行い、電子機器を最適設計することが求められている。

【0005】

しかし、(1)、(2)のプリント配線板のように、抵抗性導体膜、ノイズ抑制層といった新規の抵抗性材料を用いた電子機器については、電磁界シミュレータを用いた電子機器のEMCの評価方法が確立されていない。

そのため、(1)、(2)のプリント配線板を製造するに際しては、仮設計されたプリント配線板を実際に試作し、試作されたプリント配線板について、実測にてEMCを評価し、該設計がEMC対策として最適なものかどうかを検討する必要がある。そして、仮設計が過剰な設計または未熟な設計の場合は、何度も設計をやり直し、何度もプリント配線板を試作する必要がある。このように、(1)、(2)のプリント配線板を製造する場合には、設計の段階でコストおよび時間の問題がある。

【0006】

なお、特許文献1においては、EMIを低減するのに最適な抵抗性導体膜の表面抵抗率を求めるために、電磁界シミュレータを用い、一定の比誘電率における電磁界解析が行われている。しかし、プリント配線板として簡易的なモデルを用いており、EMIが問題となる周波数の範囲における比誘電率の周波数依存データを用いることがなく、また、実測データを求め、シミュレーション結果との整合性も確認していない。そのため、該電磁界解析によるシミュレーション結果は、必ずしも実際のプリント配線板に対して良好な結果をもたらすことを保証するものではなく、特許文献1に記載の電磁界解析は、充分に信頼のおける設計手法とはなっていない。

【特許文献1】特開2006−049496号公報

【特許文献2】特開2006−297628号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は、低コストで、かつ短時間で、EMC対策が精度よくなされた電子機器を設計、製造できる電子機器の製造方法を提供する。

【課題を解決するための手段】

【0008】

本発明の電子機器の製造方法は、金属材料または導電性セラミックスを含む厚さ5〜200nmのノイズ抑制層を有する電子機器の製造方法であって、(a)ノイズ抑制層を有する電子機器を設計する工程と、(b)設計された電子機器について、電磁界シミュレータを用いて電磁界解析を行い、シミュレーション結果を得る工程と、(c)シミュレーション結果に基づいて、電子機器のEMCを評価し、設計を検証する工程と、(d)設計を検証した結果に基づいて、電子機器を製造する工程とを有し、(b)工程において、複数の周波数におけるノイズ抑制層の複素誘電率および複素透磁率を電磁界シミュレータに入力することを特徴とする。

【0009】

(b)工程においては、電磁界シミュレータで得られたSパラメータデータを回路シミュレータに入力し、電子機器の回路解析を行ってもよい。

(b)工程においては、ノイズ抑制層の複素誘電率および複素透磁率の実部および虚部を電磁界シミュレータに入力することが好ましい。

ノイズ抑制層の複素誘電率および複素透磁率の実部および虚部の絶対値が1000よりも大きい場合に、本発明は特に有用である。

【発明の効果】

【0010】

本発明の電子機器の製造方法によれば、低コストで、かつ短時間で、EMC対策が精度よくなされた電子機器を設計、製造できる。

【発明を実施するための最良の形態】

【0011】

<電子機器>

電子機器としては、半導体素子、電子部品;半導体素子、電子部品等が実装されたプリント配線板;プリント配線板を備えた各種機器(パソコン、ゲーム機器、携帯電話等。)等が挙げられる。

【0012】

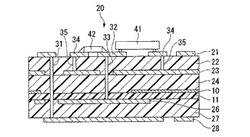

図1は、プリント配線板の一例を示す断面図である。プリント配線板20は、上から順に、信号伝送層21、誘電体層22、グランド層23、誘電体層24、ノイズ抑制層10、誘電体基材11、電源層26、誘電体層27、信号伝送層28を有して構成される。信号伝送層21と信号伝送層28とは、スルーホール31を介して接続され、電源ライン32と電源層26とは、ビアホール33を介して接続され、グランドライン34とグランド層23とは、ビアホール35を介して接続されている。電源ライン32およびグランドライン34には、半導体素子41およびバイパスコンデンサ42が搭載されている。

【0013】

(信号伝送層、グランド層、電源層)

信号伝送層、グランド層、電源層は、銅箔等の金属箔からなる導体層である。

銅箔としては、電解銅箔、圧延銅箔等が挙げられる。

【0014】

(誘電体層)

誘電体層は、例えば、エポキシ樹脂等をガラス繊維等に含浸させてなるプリプレグを硬化させた層である。

【0015】

(ノイズ抑制層)

ノイズ抑制層は、金属材料または導電性セラミックスを含む、厚さ5〜200nmの薄膜である。

ノイズ抑制層の厚さが5nm以上であれば、充分なノイズ抑制効果が得られる。一方、ノイズ抑制層の厚さが200nmを超えると、後述のナノクラスターが成長し、金属材料等からなる均質な薄膜が形成され、表面抵抗が小さくなって、金属反射が強まり、ノイズ抑制効果も小さくなる。

ノイズ抑制層の厚さは、ノイズ抑制層の厚さ方向断面の高分解能透過型電子顕微鏡像をもとにして、5箇所のノイズ抑制層の厚さを電子顕微鏡像上で測定し、平均することにより求める。

【0016】

図2は、ノイズ抑制層の表面を観察したフィールドエミッション走査電子顕微鏡像であり、図3、図4は、ノイズ抑制層の表面の原子間力顕微鏡像であり、図5は、ノイズ抑制層の表面の模式図である。ノイズ抑制層10は、複数のナノクラスター12の集合体として観察される。ナノクラスター12の間には物理的な欠陥があって均質な薄膜になっていない。

【0017】

不均質な薄膜であることは、ノイズ抑制層の表面抵抗の実測値から換算した体積抵抗率R1(Ω・cm)と金属材料(または導電性セラミックス)の体積抵抗率R0(Ω・cm)(文献値)との関係から確認できる。すなわち、体積抵抗率R1と体積抵抗率R0とが、0.5≦logR1−logR0≦3を満足する場合に、優れたノイズ抑制効果が発揮される。

【0018】

ノイズ抑制層の表面抵抗は、50〜500Ωが好ましい。ノイズ抑制層の表面抵抗は、下記方法にて測定する。

石英ガラス上に金等を蒸着して形成した、2本の薄膜金属電極(長さ10mm、幅5mm、電極間距離10mm)を用い、該電極上に被測定物を置き、被測定物上に、大きさ10mm×20mmの押さえ板を50gの荷重で押し付け、1mA以下の測定電流で電極間の抵抗を測定する。この値を持って表面抵抗とする。

【0019】

金属材料としては、強磁性金属、常磁性金属が挙げられる。強磁性金属としては、鉄、カルボニル鉄;Fe−Ni、Fe−Co、Fe−Cr、Fe−Si、Fe−Al、Fe−Cr−Si、Fe−Cr−Al、Fe−Al−Si、Fe−Pt等の鉄合金;コバルト、ニッケル;これらの合金等が挙げられる。常磁性金属としては、金、銀、銅、錫、鉛、タングステン、ケイ素、アルミニウム、チタン、クロム、タンタル、モリブデン、これらの合金、アモルファス合金、強磁性金属との合金等が挙げられる。これらのうち、酸化に対して抵抗力のある点から、ニッケル、鉄クロム合金、タングステン、クロム、タンタル、貴金属が好ましい。なお、貴金属は高価であるため、実用的にはニッケル、ニッケルクロム合金、鉄クロム合金、タングステン、クロム、タンタルが好ましく、ニッケルまたはニッケル合金が特に好ましい。

【0020】

導電性セラミックスとしては、金属と、ホウ素、炭素、窒素、ケイ素、リンおよび硫黄からなる群から選ばれる1種以上の元素とからなる、合金、金属間化合物、固溶体等が挙げられる。具体的には、窒化ニッケル、窒化チタン、窒化タンタル、窒化クロム、炭化チタン、炭化ケイ素、炭化クロム、炭化バナジウム、炭化ジルコニウム、炭化モリブデン、炭化タングステン、ホウ化クロム、ホウ化モリブデン、ケイ化クロム、ケイ化ジルコニウム等が挙げられる。

【0021】

導電性セラミックスは、金属よりも体積抵抗率が高いため、導電性セラミックスを含むノイズ抑制層は、特定の共鳴周波数を有さない、ノイズ抑制効果を発揮する周波数が広帯域化する、保存安定性が高い等の利点を有する。導電性セラミックスは、後述の物理的蒸着法における反応性ガスとして窒素、炭素、ケイ素、ホウ素、リンおよび硫黄からなる群から選ばれる1種以上の元素を含むガスを用いることによって容易に得られる。

【0022】

ノイズ抑制層は、非常に薄い複数のナノクラスターの集合体からなる層であるため、ノイズ抑制層に含まれる材料が強磁性金属であっても、バルクの強磁性金属の特性を示さなくなり、常磁性を示す。一方、ノイズ抑制層に含まれる材料が常磁性体であっても、後述するノイズ抑制層のナノクラスター集合体から、または該集合体と誘電体を介して対向したグランド層とから、人工磁性体が形成された場合は、磁気特性を有する。

【0023】

ノイズ抑制層は、誘電体層を介してグランド層と対向するように配置されることによって、ノイズ抑制層に接して配置された波源、またはノイズ抑制層から離れて配置された波源からの電磁界に影響を及ぼす。

波源が、信号伝送層または電源層である場合、ノイズ抑制層は、信号伝送層または電源層に流れる高周波電流(伝導ノイズ)を抑制する効果を有する。すなわち、ローパスフィルターと同様の効果を有する。

波源が、点波源の場合、ノイズ抑制層は、電磁波(放射ノイズ)を吸収する効果を有する。

このように、導電性または抵抗性のナノクラスター集合体が誘電体でグランド層と隔置された構造は、伝送線路型のメタマテリアルとなる可能性があり、ナノクラスターを構成する材料の特性に依存せずに、人工誘電体または人工磁性体として特異な性能を発現するようになる。

【0024】

(誘電体基材)

ノイズ抑制層は、各層を積層してプリント配線板とする前に、あらかじめ誘電体基材の表面に形成される。

誘電体基材は、表面抵抗が1×106Ω以上の誘電体からなる。

誘電体基材の厚さは、ノイズ抑制層と導体層との間の絶縁性が保たれる厚さであればよく、0.1μm以上が好ましい。

【0025】

誘電体基材の材料としては、誘電体セラミックス、有機高分子材料が挙げられる。

誘電体セラミックスとしては、酸化ケイ素、窒化ケイ素、酸化チタン、酸化アルミニウム等が挙げられる。誘電体セラミックスは、発泡セラミックスであってもよい。

有機高分子材料としては、ポリオレフィン、ポリアミド、ポリエステル、ポリエーテル、ポリケトン、ポリイミド、ポリウレタン、ポリシロキサン、フェノール系樹脂、エポキシ系樹脂、アクリル系樹脂、ポリアクリレート、塩化ビニル系樹脂、塩素化ポリエチレン等の樹脂;天然ゴム;イソプレンゴム、ブタジエンゴム、スチレンブタジエンゴム等のジエン系ゴム;ブチル系ゴム、エチレンプロピレンゴム、ウレタンゴム、シリコーンゴム等の非ジエン系ゴム等が挙げられる。これらは熱可塑性であっても、熱硬化性であってもよく、その未硬化物であってよい。また、これらの樹脂、ゴム等の変性物、混合物、共重合体であってもよい。

【0026】

(ノイズ抑制層の形成方法)

誘電体基材の表面に、金属材料または導電性セラミックスを非常に薄く物理的に蒸着させることにより、ナノクラスターからなる不均質な薄膜からなるノイズ抑制層が形成される。

物理的蒸着法は、真空にした容器の中でターゲット(金属材料または導電性セラミックス)を何らかの方法で気化させ、気化した金属材料等を近傍に置いた誘電体基材上に堆積させる方法である。ターゲットの気化方法の違いで、蒸発系とスパッタリング系とに分けられる。蒸発系としては、EB蒸着法、イオンプレーティング法等が挙げられる。スパッタリング系としては、高周波スパッタリング法、マグネトロンスパッタリング法、対向ターゲット型マグネトロンスパッタリング法、イオン注入法等が挙げられる。

物理的蒸着法においては、反応性ガスとして窒素、炭素、ケイ素、ホウ素、リンおよび硫黄からなる群から選ばれる1種以上の元素を含むガスを用いることによって、金属材料と反応性ガスとを反応させて、金属材料を導電性セラッミクスにすることができる。

【0027】

(ノイズ抑制層の材料定数の測定方法)

材料定数(複素誘電率、複素透磁率等。)の測定方法としては、平行金属板法、共振器法、導波管法、自由空間法等が挙げられる。

【0028】

平行金属板法は、被測定物と2枚の金属板からコンデンサー構造を形成して、LCRメータ等により測定した静電容量から複素誘電率を求める方法である。測定可能な対応周波数は低く、1GHz以下である。

【0029】

共振器法は、共振器(空洞共振器、誘電体共振器、平面回路共振器等。)に、被測定物を挿入し、共振器の前後での共振周波数やQ値変化を測定し、複素誘電率や複素透磁率を求める方法である。共振器法は、低損失材料の材料定数を精度よく測定できる。しかし、1種類の共振器では、特定周波数の測定しかできないため、材料定数の周波数依存性のデータを得るためには、多数の共振器を準備する必要がある。共振器の種類を変えることにより、1GHzから100GHz程度まで測定できる。

【0030】

導波管法は、伝送線路(導波管、同軸管等。)内に被測定材料を挿入して反射係数や透過係数を測定する方法である。

マクスウェル方程式の電界および磁界と、電信方程式の電圧および電流とを比較すると、複素誘電率の実部および虚部、複素透磁率の実部および虚部は、それぞれキャパシタンス、コンダクタンス、インダクタンス、レジスタンスに対応しているため、導波管法においては、被測定物の挿入前後の電磁界の変化を伝送線路理論として単純化して扱うことができる。導波管法によれば、ある周波数において計算して得た反射係数および透過係数と、ネットワークアナライザーを用いて測定した反射係数および透過係数とから、複素誘電率や複素透磁率を導くことができる。

【0031】

導波管法は、反射係数の測定方法の違いにより、反射波法と透過波法とに分類される。

反射波法は、導波管の終端に短絡板を設け、1ポートで反射係数を測定する方法である。透過波法は、導波管の両端をネットワークアナライザーに接続し、2ポートで透過係数を測定する方法である。通常、反射波法にて反射係数を測定することは、透過係数を測定するよりも難しく、精度の点で不利とされている。しかし、高損失材料を被測定物とする場合は、透過波が微弱となるため、透過波法よりも反射波法が好ましい。

【0032】

導波管法は、伝送線路の違いにより、方形導波管法と同軸管法とに分類される。

方形導波管法は、通常、TE10モードが伝播する、断面が矩形状の導波管を用い、管内に被測定物を設置し、定在波測定器によりインピーダンスを測定し、ネットワークアナライザーで反射係数または透過係数を測定し、測定結果と、伝送理論からの計算結果とから材料定数を求める方法である。測定波長が短くなると、導波管の機械的精度、被測定物の加工精度、配置精度等に影響されやすくなることから、測定可能な対応周波数は数GHzから数10GHzとなる。

【0033】

同軸管法は、TEMモードが伝播する伝送線路を用いる方法である。方形導波管と同様にして複素誘電率や複素透磁率を求めることができる。また、カットオフ周波数がないことから、より低い周波数においても測定でき、また1種類の同軸管で広い周波数範囲にて測定できることから効率的である。

【0034】

自由空間法は、導波管法と原理は同じであるが、自由空間を伝送線路とする方法であり、被測定物に電波を照射し、反射波もしくは透過波、または偏波特性を測定する方法である。被測定物としては、平板状で、数GHzの低い周波数における測定には、やや大きなサイズのものが必要となる。エネルギー効率と、測定機器や被測定物のサイズ効果とから、ホーンアンテナやレンズアンテナを用い、収束した電波を用いることが好ましい。

【0035】

材料定数の他の測定方法としては、被測定物を磁界中に入れ、磁気センサーの電圧およびインピーダンスを測定し、複素透磁率を求める方法(特開2004−69337号公報)、反射波法と同様に伝送線路としてマイクロストリップ線路を用い、被測定物の装荷前後のSパラメータ複素透磁率を求める短絡マイクロストリップ線路法等が挙げられる。

以上の材料定数の測定方法のうち、広い周波数範囲において、連続的に測定できる導波管法が好ましく、大掛かりな測定機器を用いず、高精度に複素誘電率等を求めることができることから、同軸管法が特に好ましい。

【0036】

ノイズ抑制層はそれ自体では自立性がないため、ノイズ抑制層の材料定数(複素誘電率および複素透磁率)を測定する際には、誘電体基材の表面にノイズ抑制層を形成したノイズ抑制シートを、被測定物として用いる。この際、誘電体基材のみの複素誘電率および複素透磁率を測定しておき、ノイズ抑制シートの複素誘電率および複素透磁率から差し引く補正を行うことにより、高い精度でノイズ抑制層の複素誘電率および複素透磁率を求めることができる。なお、ノイズ抑制シートの誘電体基材の厚さおよび材料が、後述の電磁界解析を行う対象の電子機器に含まれる誘電体基材の厚さおよび材料と同じ場合には、この補正を行う必要はない。

【0037】

図6に示すような、誘電体基材11の表面にノイズ抑制層10が形成され、誘電体基材11の裏面に導体層13が設けられた積層シート14の複素誘電率および複素透磁率を測定する場合、導体層13において測定のための入力信号が反射し、導体層13を透過しない。そのため、測定方法としては、積層シート14の導体層13を測定機器のグランドとして用い、導体層13を除いた誘電体基材11およびノイズ抑制層10からなるノイズ抑制シートを被測定物として用いることができる反射波法が好ましい。また、反射波法によれば、透過状態により誘電率を同時に測定できることから、効率的である。また、導体層13が付いたまま、導波管中に適当な空隙を有して被測定物を設置し、透過波法で測定できる部分装荷法は、積層シート14の測定方法として好ましい。また、従来の導波管法においては、高周波領域では被測定物の大きさを小さくする必要があり、被測定物の寸法精度、被測定物と導波管との接触に留意する必要があったが、部分装荷法においては、これらに留意することなく透過係数を容易に測定できる。

【0038】

<電子機器の製造方法>

本発明の電子機器の製造方法は、下記工程を有する製造方法である。

(a)ノイズ抑制層を有する電子機器を設計する工程。

(b)設計された電子機器について、電磁界シミュレータを用いて電磁界解析を行い、シミュレーション結果を得る工程。

(c)シミュレーション結果に基づいて、電子機器のEMCを評価し、設計を検証する工程。

(d)設計を検証した結果に基づいて、電子機器を製造する工程。

【0039】

((a)工程)

目標とするEMCの程度、電子機器の用途、性能等に応じて、ノイズ抑制層を有する電子機器の設計を行う。

【0040】

((b)工程)

設計された電子機器の構造、材料等の情報を電磁界シミュレータに入力し、電磁界解析を行い、シミュレーション結果を得る。この際、複数の周波数におけるノイズ抑制層の複素誘電率および複素透磁率も同時に電磁界シミュレータに入力する。

【0041】

電磁界シミュレータは、マクスウェルの方程式をもとに、伝搬する電磁波の振る舞いを解くものである。アルゴリズムの違いから大きく、有限要素法(FEM:finite element method)、差分法(FDM:finite difference method)、境界要素法(モーメント法(MoM:method of moments)等。)の3つに分類される。

【0042】

有限要素法は、解析対象の構造モデルを三角形または四面体の要素に分割し、要素内の電界、磁界に関係する物理値は一定として、各頂点の物理値で近似する方法であり、各頂点の物理値、頂点座標、境界条件から連立方程式を解く方法である。特徴として、要素が四面体であるため、構造モデルの形状にフィットした要素分割が行われ、周波数依存の複素誘電率等の材料定数を直接扱える。

【0043】

差分法は、解析対象の構造モデルを格子状に分割し、各格子点に未知の電界、磁界の変数を置き、各格子点でのマクスウェルの方程式の差分を求め、連立させ、大規模な線形連立方程式を立て、該連立方程式を、境界条件を入力して解く方法である。差分法を時間および空間の領域まで拡張し、電磁界を時間領域で解析する方法として、時間領域差分(FDTD:finite difference time domain)法等がある。電界、磁界を計算する格子点を空間的に交互に配置し、時間的に交互に計算するため、直感的に理解しやすく、高速に計算が行われるため、大規模な線形連立方程式も解くことができる。

【0044】

モーメント法は、導体の境界を分割し、すなわち電圧を境界条件として導体上の電流分布をマクスウェルの方程式をもとに計算する方法である。構造モデルを細かく分割する必要がなく、未知変数の数が少ないため、計算が容易である。

これらのうち、有限要素法は、周波数依存の複素誘電率および複素透磁率を直接入力でき、簡便である。

【0045】

周波数に大きく依存する複素誘電率および複素透磁率は、周波数によりその値が大きく変化するため、電磁界シミュレーションの結果を正しくするためには、なるべく多くの周波数における複素誘電率および複素透磁率を測定し、入力することが好ましい。

複素誘電率および複素透磁率の測定点の数は、対象とする周波数範囲のうち、100点以上がこのましく、200点以上がより好ましい。必要であれば、測定点間を補間しデータ数を増してもかまわない。また、複素誘電率および複素透磁率を入力する際には、実部たけではなく、虚部を入力することが、各成分の損失項としての効果を計算に関与させることができる点から好ましい。虚部の入力に際しては、直接虚部の値を入力してもよく、虚部を実部で除した正接(tanδ)等として入力してもよい。

【0046】

誘電体基材の表面に形成されたノイズ抑制層は、媒質型のメタマテリアルとして考えられ、また、誘電体基材の裏面に導体層がある場合は、伝送線路型のメタマテリアルとして機能するものと考えられる。そのため、周波数に依存するが、複素誘電率および複素透磁率の実部および虚部の絶対値は、それぞれ1000以上の大きな値を示す。そのため、このような大きな値を入力することにより、ノイズ抑制層を電磁界シミュレーションにより正しく評価できる。

【0047】

((c)工程)

電磁界シミュレータによる電磁界解析によって得られるシミュレーション結果から、電子機器のEMCを評価し、設計を検証する。具体的には、電子機器のEMCについてPI系、EMI系、またはSI系の検証を行い、電子機器の設計が、目標とするEMCのレベルに達しているかどうかを判断し、EMCに関して過剰な設計または未熟な設計であると判断される場合には、(a)工程に戻って電子機器の設計を見直し、再度(b)工程を行う。

【0048】

PI系の検証においては、電子機器の電源およびグランドに着目し、高周波電流(伝導ノイズ)、電圧変動の解析を行う。例えば、ノイズ抑制層の配置、電源系に接続されるビアまたは半導体素子の電源ピン、バイパスコンデンサ等の電子部品の特性値および配置について、交流解析や過渡解析を行う。

【0049】

EMI系の検証においては、電子機器から放射される電磁波(放射ノイズ)の解析を行う。放射される電磁波が、VCCI規格による規制値内に納まっているかを確認する、または、電子機器のノイズ発生部位を断定し、PI系の検証結果を総合して、特定部位での電磁界強度の変化を確認することによって、設計の改善効果予測等を行う。

【0050】

SI系の検証においては、信号伝送路における信号の減衰、遅延、反射、クロストークの影響を確認する。この際、電磁界シミュレータで得られたSパラメータデータを回路シミュレータに入力し、電子機器の回路解析を行い、ノイズ抑制層が装荷された回路基板への影響を確認してもよい。なお、Sパラメータデータを回路シミュレータに入力する場合、Sパラメータデータ回路シミュレータへ入力できる言語に変換する必要がある。

【0051】

回路シミュレータとしては、SPICE(simulation program with integrated circuit emphasis)、IBIS(i/o buffer information specifications)、IMIC(i/o interface model for integrated circuit)等が挙げられる。SPICEは、電磁界シミュレータの結果として出力されたSパラメータデータをもとに、R、L、G、Cのパラメータからなるネットリスト等をキルヒホッフの法則に基づいて計算するシミュレータである。

【0052】

((d)工程)

(c)工程における設計の検証の結果、電子機器の設計が、目標とするEMCのレベルに達していると判断された場合、目標とするEMCのレベルに達した電子機器の設計に基づいて、電子機器を公知の方法にて製造する。

【0053】

以上説明した本発明の電子機器の製造方法によれば、設計された電子機器について、電磁界シミュレータを用いて電磁界解析を行い、シミュレーション結果を得る際に、ノイズ抑制層の複素誘電率および複素透磁率を電磁界シミュレータに入力しているため、これまで電磁界シミュレータを用いた電子機器のEMCの評価方法が確立されていなかった、ノイズ抑制層を有する電子機器の電磁界シミュレータを用いた電磁界解析が可能となる。そのため、ノイズ抑制層を有する電子機器の設計を低コストで、かつ短時間で行うことができる。また、ノイズ抑制層の複素誘電率および複素透磁率を電磁界シミュレータに入力する際には、複数の周波数における複素誘電率および複素透磁率を入力しているため、対象とする周波数範囲にわたって正確なシミュレーション結果を得ることができる。

よって、本発明の電子機器の製造方法によれば、低コストで、かつ短時間で、EMC対策が精度よくなされた電子機器を設計、製造できる。

【実施例】

【0054】

(ノイズ抑制層の厚さ)

日立製作所社製、透過型電子顕微鏡H9000NARを用いてノイズ抑制層の断面を観察し、5箇所のノイズ抑制層の厚さを測定し、平均した。

【0055】

(表面抵抗)

石英ガラス上に金を蒸着して形成した、2本の薄膜金属電極(長さ10mm、幅5mm、電極間距離10mm)を用い、該電極上に被測定物を置き、被測定物上に、大きさ10mm×20mmの押さえ板を50gの荷重で押し付け、0.1mAの測定電流で電極間の抵抗を測定し、この値を持って表面抵抗とした。

【0056】

〔ノイズ抑制層の材料定数の測定〕

厚さ25μmのポリイミドフィルム(東レデュポン社製、カプトンHタイプ)の表面に、ニッケル金属を、窒素ガスを流入しながら反応性スパッタリング法にて蒸着して、図2のフィールドエミッション走査電子顕微鏡像に示す、窒化ニッケルを含む不均質な薄膜からなるノイズ抑制層を形成し、ノイズ抑制シートを得た。ノイズ抑制層の厚さは25nmであった。

【0057】

材料定数測定装置としては、Sパラメータ方式反射法による透磁率、誘電率測定用の同軸管タイプ測定キット(キーコム社製、39Dタイプ)と、該測定キットに接続されたベクトルネットワークアナライザー(アンリツ社製、37247C)と、該ベクトルネットワークアナライザーに接続された、測定用ソフト(キーコム社製)がインストールされたパソコンとを有するシステムを用いた。

【0058】

ノイズ抑制シートを、キーコム社の39Dタイプ(45MHz〜3GHz)の形状(外径D=38.97mm−0.02mm、−0.06mm、内径d=16.00mm+0.06mm、+0.02mm)に加工し、被測定物とした。

同じく、厚さ25μmのポリイミドフィルム(東レデュポン社製、カプトンHタイプ)を39Dタイプの形状に加工し、リファレンスとした。

【0059】

リファレンスを測定キットにセットして、校正短絡および校正開放のデータを取得した。ついで、被測定物を測定キットにセットし、試料開放および試料短絡のデータを取得した。パソコンに被測定物の厚さを入力し、4組の測定データから被測定物の振幅および位相の周波数特性値を得た。

【0060】

以上の測定結果から、被測定物およびリファレンスの複素誘電率および複素透磁率の周波数依存性のデータを得た。被測定物の複素誘電率および複素透磁率からリファレンスの複素誘電率および複素透磁率を差し引く補正を行い、ノイズ抑制層の複素誘電率および複素透磁率の周波数依存性のデータ(周波数の測定点=800点)を得た。ノイズ抑制層の複素誘電率の周波数依存性のグラフを図7に示す。ノイズ抑制層の複素透磁率の周波数依存性のグラフを図8に示す。

【0061】

〔実施例1〕

(a)工程:

プリント配線板のモデルとして、図9および図10に示す、グランド層と電源層とを有する2層基板を設計した。該2層基板50は、上から順に、電源層26、誘電体基材11、ノイズ抑制層10、誘電体層24、グランド層23を有して構成される。電源層26とグランド層23とは、2層基板50の長手方向の両端にてスルーホール51を介してSMA端子52で接続されている。

【0062】

2層基板50の長さは、232mmであり、幅は、102mmである。

誘電体基材11、ノイズ抑制層10、誘電体層24、グランド層23の長さおよび幅は、2層基板50と同じである。

電源層26の長さは、2層基板50と同じである。電源層26の幅は、長手方向に沿った両側部が2層基板50に比べ幅L(7mm)だけ短くされている。

【0063】

2層基板50の厚さは、1103μmである。

電源層26の厚さは、12μmである。

誘電体基材11の厚さは、3μmである。

ノイズ抑制層10の厚さは、25nmである。

誘電体層24の厚さは、1070μmである。

グランド層23の厚さは、18μmである。

【0064】

電源層26およびグランド層23の材料は、銅箔である。

誘電体基材11の材料は、エポキシ樹脂である。

ノイズ抑制層10の材料は、前記ノイズ抑制シートのノイズ抑制層と同じ窒化ニッケルである。

誘電体層24の材料は、ガラス繊維強化エポキシ樹脂である。

【0065】

(b)工程:

2層基板50の構造、材料等の情報を、有限要素法による電磁界シミュレータ(アンソフト(Ansoft)社製、HFSS)に入力し、電磁界解析を行い、Sパラメータ(S11(反射減衰量)およびS21(透過減衰量))を得た。この際、前記ノイズ抑制層の材料定数の測定にて得られた、ノイズ抑制層の複素誘電率(実部、虚部、tanδ)および複素透磁率(実部、虚部、tanδ)の周波数依存性のデータも同時に電磁界シミュレータに入力した。

シミュレーションによるSパラメータの周波数依存性のグラフを図11に示す。

【0066】

(c)工程:

共振周波数におけるS21(透過減衰量)が大きく、充分なノイズ抑制効果があることが確認された。よって、2層基板50は、充分なEMC対策がなされていると予測された。

【0067】

(d)工程:

図9および図10に示す2層基板50を実際に製造した。

厚さ12μmの銅箔(電源層26)の表面に、エポキシ系ワニスを塗布し、乾燥、硬化させ、厚さ3μmの誘電体基材11を形成した。

ついで、誘電体基材11の表面に、窒素ガス雰囲気下でニッケル金属を反応性スパッタリング法により物理的に蒸着し、窒化ニッケルを含む不均質な薄膜からなるノイズ抑制層10を形成した。ノイズ抑制層10の厚さは25nmであり、ノイズ抑制層10の表面抵抗は25Ωであった。

【0068】

ノイズ抑制層10の表面に、厚さ1070μmのエポキシ系プリプレグ(誘電体層24)および厚さ18μmの銅箔(グランド層23)を積層し、プリプレグを硬化させ、基板を製造した。

該基板から232mm×102mmの大きさの基板を切り出し、該基板の電源層26の銅箔の長手方向に沿った両側部を、幅L(7mm)にわたってエッチングし、除去した。

【0069】

該基板の長手方向の両末端に、電源層26およびグランド層23にスルーホール51を介して繋がるSMAコネクタ52を接続し、2層基板50を製造した。

SMAコネクタ52にベクトルネットワークアナライザー(アンリツ社製、37247D)を接続して、周波数50MHzから3GHzまでの400点でSパラメータを測定した。

実測によるSパラメータの周波数依存性のグラフを図11に示す。シミュレーションによるSパラメータと実測によるSパラメータとが、ほぼ一致することが確認された。

【産業上の利用可能性】

【0070】

本発明の電子機器の製造方法は、金属材料または導電性セラミックスを含む厚さ5〜200nmのノイズ抑制層を有する電子機器の設計、製造に有用である。

【図面の簡単な説明】

【0071】

【図1】プリント配線板(電子機器)の一例を示す断面図である。

【図2】ノイズ抑制層の表面を観察したフィールドエミッション走査電子顕微鏡像である。

【図3】ノイズ抑制層の表面の原子間力顕微鏡像である。

【図4】ノイズ抑制層の表面の原子間力顕微鏡像である。

【図5】ノイズ抑制層の表面の模式図である。

【図6】ノイズ抑制層の材料定数の測定に用いられる積層シート(被測定物)の一例を示す断面図である。

【図7】ノイズ抑制層の複素誘電率の周波数依存性を示すグラフである。

【図8】ノイズ抑制層の複素透磁率の周波数依存性を示すグラフである。

【図9】実施例で用いた2層基板の上面図である。

【図10】図9のX−X断面図である。

【図11】シミュレーションおよび実測によるSパラメータの周波数依存性を示すグラフである。

【符号の説明】

【0072】

10 ノイズ抑制層

20 プリント配線板(電子機器)

50 2層基板(電子機器)

【技術分野】

【0001】

本発明は、電子機器の製造方法に関する。

【背景技術】

【0002】

近年、ユビキタス社会が訪れ、情報処理機器(パソコン、ゲーム機器等。)、通信機器(携帯電話等。)等の電子機器においては、MPUの高速化、多機能化、複合化、およびメモリ等の記録装置の高速化が進行している。これに伴い、電子機器には、電子機器から放射されるノイズ、または電子機器内の導体を伝導するノイズによって、電子機器自身または他の電子機器が影響を受けないこと、すなわちEMC(Electromagnetic Compatibility、電磁環境両立性)が求められている。

これらノイズとしては、MPU、電子部品等が実装されたプリント配線板内の導体のインピーダンス不整合によるノイズ、導体間のクロストークによるノイズ、MPU等の半導体素子の同時スイッチングによる電源層とグランド層との間の平行平板共振によって誘起されるノイズ等がある。

【0003】

電源層とグランド層との間の平行平板共振によって誘起されるノイズが抑えられた電子機器としては、下記プリント配線板が提案されている。

(1)電源層、グランド層の少なくとも一方に、あらかじめ定められた範囲の表面抵抗率を有する抵抗性導体膜を一体化したプリント配線板(特許文献1)。

(2)電源層とグランド層との間に、金属材料を含み、かつ所定の表面抵抗を有する、厚さ5〜200nmのノイズ抑制層を、絶縁層を介して配置したプリント配線板(特許文献2)。

【0004】

電子機器を設計するに際しては、仮設計された電子機器について電磁界シミュレータを用いて電磁界解析を行い、シミュレーション結果に基づいて電子機器のEMCを評価し、該設計がEMC対策として最適なものかどうかを検討することが行われる。具体的には、信号品質に関わるSI(signal integrity)系の検証、電源の電流、電圧変動に関わるPI(power integrity)系の検証、放射ノイズに関わるEMI(electro magnetic interference)系の検証を行い、電子機器を最適設計することが求められている。

【0005】

しかし、(1)、(2)のプリント配線板のように、抵抗性導体膜、ノイズ抑制層といった新規の抵抗性材料を用いた電子機器については、電磁界シミュレータを用いた電子機器のEMCの評価方法が確立されていない。

そのため、(1)、(2)のプリント配線板を製造するに際しては、仮設計されたプリント配線板を実際に試作し、試作されたプリント配線板について、実測にてEMCを評価し、該設計がEMC対策として最適なものかどうかを検討する必要がある。そして、仮設計が過剰な設計または未熟な設計の場合は、何度も設計をやり直し、何度もプリント配線板を試作する必要がある。このように、(1)、(2)のプリント配線板を製造する場合には、設計の段階でコストおよび時間の問題がある。

【0006】

なお、特許文献1においては、EMIを低減するのに最適な抵抗性導体膜の表面抵抗率を求めるために、電磁界シミュレータを用い、一定の比誘電率における電磁界解析が行われている。しかし、プリント配線板として簡易的なモデルを用いており、EMIが問題となる周波数の範囲における比誘電率の周波数依存データを用いることがなく、また、実測データを求め、シミュレーション結果との整合性も確認していない。そのため、該電磁界解析によるシミュレーション結果は、必ずしも実際のプリント配線板に対して良好な結果をもたらすことを保証するものではなく、特許文献1に記載の電磁界解析は、充分に信頼のおける設計手法とはなっていない。

【特許文献1】特開2006−049496号公報

【特許文献2】特開2006−297628号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は、低コストで、かつ短時間で、EMC対策が精度よくなされた電子機器を設計、製造できる電子機器の製造方法を提供する。

【課題を解決するための手段】

【0008】

本発明の電子機器の製造方法は、金属材料または導電性セラミックスを含む厚さ5〜200nmのノイズ抑制層を有する電子機器の製造方法であって、(a)ノイズ抑制層を有する電子機器を設計する工程と、(b)設計された電子機器について、電磁界シミュレータを用いて電磁界解析を行い、シミュレーション結果を得る工程と、(c)シミュレーション結果に基づいて、電子機器のEMCを評価し、設計を検証する工程と、(d)設計を検証した結果に基づいて、電子機器を製造する工程とを有し、(b)工程において、複数の周波数におけるノイズ抑制層の複素誘電率および複素透磁率を電磁界シミュレータに入力することを特徴とする。

【0009】

(b)工程においては、電磁界シミュレータで得られたSパラメータデータを回路シミュレータに入力し、電子機器の回路解析を行ってもよい。

(b)工程においては、ノイズ抑制層の複素誘電率および複素透磁率の実部および虚部を電磁界シミュレータに入力することが好ましい。

ノイズ抑制層の複素誘電率および複素透磁率の実部および虚部の絶対値が1000よりも大きい場合に、本発明は特に有用である。

【発明の効果】

【0010】

本発明の電子機器の製造方法によれば、低コストで、かつ短時間で、EMC対策が精度よくなされた電子機器を設計、製造できる。

【発明を実施するための最良の形態】

【0011】

<電子機器>

電子機器としては、半導体素子、電子部品;半導体素子、電子部品等が実装されたプリント配線板;プリント配線板を備えた各種機器(パソコン、ゲーム機器、携帯電話等。)等が挙げられる。

【0012】

図1は、プリント配線板の一例を示す断面図である。プリント配線板20は、上から順に、信号伝送層21、誘電体層22、グランド層23、誘電体層24、ノイズ抑制層10、誘電体基材11、電源層26、誘電体層27、信号伝送層28を有して構成される。信号伝送層21と信号伝送層28とは、スルーホール31を介して接続され、電源ライン32と電源層26とは、ビアホール33を介して接続され、グランドライン34とグランド層23とは、ビアホール35を介して接続されている。電源ライン32およびグランドライン34には、半導体素子41およびバイパスコンデンサ42が搭載されている。

【0013】

(信号伝送層、グランド層、電源層)

信号伝送層、グランド層、電源層は、銅箔等の金属箔からなる導体層である。

銅箔としては、電解銅箔、圧延銅箔等が挙げられる。

【0014】

(誘電体層)

誘電体層は、例えば、エポキシ樹脂等をガラス繊維等に含浸させてなるプリプレグを硬化させた層である。

【0015】

(ノイズ抑制層)

ノイズ抑制層は、金属材料または導電性セラミックスを含む、厚さ5〜200nmの薄膜である。

ノイズ抑制層の厚さが5nm以上であれば、充分なノイズ抑制効果が得られる。一方、ノイズ抑制層の厚さが200nmを超えると、後述のナノクラスターが成長し、金属材料等からなる均質な薄膜が形成され、表面抵抗が小さくなって、金属反射が強まり、ノイズ抑制効果も小さくなる。

ノイズ抑制層の厚さは、ノイズ抑制層の厚さ方向断面の高分解能透過型電子顕微鏡像をもとにして、5箇所のノイズ抑制層の厚さを電子顕微鏡像上で測定し、平均することにより求める。

【0016】

図2は、ノイズ抑制層の表面を観察したフィールドエミッション走査電子顕微鏡像であり、図3、図4は、ノイズ抑制層の表面の原子間力顕微鏡像であり、図5は、ノイズ抑制層の表面の模式図である。ノイズ抑制層10は、複数のナノクラスター12の集合体として観察される。ナノクラスター12の間には物理的な欠陥があって均質な薄膜になっていない。

【0017】

不均質な薄膜であることは、ノイズ抑制層の表面抵抗の実測値から換算した体積抵抗率R1(Ω・cm)と金属材料(または導電性セラミックス)の体積抵抗率R0(Ω・cm)(文献値)との関係から確認できる。すなわち、体積抵抗率R1と体積抵抗率R0とが、0.5≦logR1−logR0≦3を満足する場合に、優れたノイズ抑制効果が発揮される。

【0018】

ノイズ抑制層の表面抵抗は、50〜500Ωが好ましい。ノイズ抑制層の表面抵抗は、下記方法にて測定する。

石英ガラス上に金等を蒸着して形成した、2本の薄膜金属電極(長さ10mm、幅5mm、電極間距離10mm)を用い、該電極上に被測定物を置き、被測定物上に、大きさ10mm×20mmの押さえ板を50gの荷重で押し付け、1mA以下の測定電流で電極間の抵抗を測定する。この値を持って表面抵抗とする。

【0019】

金属材料としては、強磁性金属、常磁性金属が挙げられる。強磁性金属としては、鉄、カルボニル鉄;Fe−Ni、Fe−Co、Fe−Cr、Fe−Si、Fe−Al、Fe−Cr−Si、Fe−Cr−Al、Fe−Al−Si、Fe−Pt等の鉄合金;コバルト、ニッケル;これらの合金等が挙げられる。常磁性金属としては、金、銀、銅、錫、鉛、タングステン、ケイ素、アルミニウム、チタン、クロム、タンタル、モリブデン、これらの合金、アモルファス合金、強磁性金属との合金等が挙げられる。これらのうち、酸化に対して抵抗力のある点から、ニッケル、鉄クロム合金、タングステン、クロム、タンタル、貴金属が好ましい。なお、貴金属は高価であるため、実用的にはニッケル、ニッケルクロム合金、鉄クロム合金、タングステン、クロム、タンタルが好ましく、ニッケルまたはニッケル合金が特に好ましい。

【0020】

導電性セラミックスとしては、金属と、ホウ素、炭素、窒素、ケイ素、リンおよび硫黄からなる群から選ばれる1種以上の元素とからなる、合金、金属間化合物、固溶体等が挙げられる。具体的には、窒化ニッケル、窒化チタン、窒化タンタル、窒化クロム、炭化チタン、炭化ケイ素、炭化クロム、炭化バナジウム、炭化ジルコニウム、炭化モリブデン、炭化タングステン、ホウ化クロム、ホウ化モリブデン、ケイ化クロム、ケイ化ジルコニウム等が挙げられる。

【0021】

導電性セラミックスは、金属よりも体積抵抗率が高いため、導電性セラミックスを含むノイズ抑制層は、特定の共鳴周波数を有さない、ノイズ抑制効果を発揮する周波数が広帯域化する、保存安定性が高い等の利点を有する。導電性セラミックスは、後述の物理的蒸着法における反応性ガスとして窒素、炭素、ケイ素、ホウ素、リンおよび硫黄からなる群から選ばれる1種以上の元素を含むガスを用いることによって容易に得られる。

【0022】

ノイズ抑制層は、非常に薄い複数のナノクラスターの集合体からなる層であるため、ノイズ抑制層に含まれる材料が強磁性金属であっても、バルクの強磁性金属の特性を示さなくなり、常磁性を示す。一方、ノイズ抑制層に含まれる材料が常磁性体であっても、後述するノイズ抑制層のナノクラスター集合体から、または該集合体と誘電体を介して対向したグランド層とから、人工磁性体が形成された場合は、磁気特性を有する。

【0023】

ノイズ抑制層は、誘電体層を介してグランド層と対向するように配置されることによって、ノイズ抑制層に接して配置された波源、またはノイズ抑制層から離れて配置された波源からの電磁界に影響を及ぼす。

波源が、信号伝送層または電源層である場合、ノイズ抑制層は、信号伝送層または電源層に流れる高周波電流(伝導ノイズ)を抑制する効果を有する。すなわち、ローパスフィルターと同様の効果を有する。

波源が、点波源の場合、ノイズ抑制層は、電磁波(放射ノイズ)を吸収する効果を有する。

このように、導電性または抵抗性のナノクラスター集合体が誘電体でグランド層と隔置された構造は、伝送線路型のメタマテリアルとなる可能性があり、ナノクラスターを構成する材料の特性に依存せずに、人工誘電体または人工磁性体として特異な性能を発現するようになる。

【0024】

(誘電体基材)

ノイズ抑制層は、各層を積層してプリント配線板とする前に、あらかじめ誘電体基材の表面に形成される。

誘電体基材は、表面抵抗が1×106Ω以上の誘電体からなる。

誘電体基材の厚さは、ノイズ抑制層と導体層との間の絶縁性が保たれる厚さであればよく、0.1μm以上が好ましい。

【0025】

誘電体基材の材料としては、誘電体セラミックス、有機高分子材料が挙げられる。

誘電体セラミックスとしては、酸化ケイ素、窒化ケイ素、酸化チタン、酸化アルミニウム等が挙げられる。誘電体セラミックスは、発泡セラミックスであってもよい。

有機高分子材料としては、ポリオレフィン、ポリアミド、ポリエステル、ポリエーテル、ポリケトン、ポリイミド、ポリウレタン、ポリシロキサン、フェノール系樹脂、エポキシ系樹脂、アクリル系樹脂、ポリアクリレート、塩化ビニル系樹脂、塩素化ポリエチレン等の樹脂;天然ゴム;イソプレンゴム、ブタジエンゴム、スチレンブタジエンゴム等のジエン系ゴム;ブチル系ゴム、エチレンプロピレンゴム、ウレタンゴム、シリコーンゴム等の非ジエン系ゴム等が挙げられる。これらは熱可塑性であっても、熱硬化性であってもよく、その未硬化物であってよい。また、これらの樹脂、ゴム等の変性物、混合物、共重合体であってもよい。

【0026】

(ノイズ抑制層の形成方法)

誘電体基材の表面に、金属材料または導電性セラミックスを非常に薄く物理的に蒸着させることにより、ナノクラスターからなる不均質な薄膜からなるノイズ抑制層が形成される。

物理的蒸着法は、真空にした容器の中でターゲット(金属材料または導電性セラミックス)を何らかの方法で気化させ、気化した金属材料等を近傍に置いた誘電体基材上に堆積させる方法である。ターゲットの気化方法の違いで、蒸発系とスパッタリング系とに分けられる。蒸発系としては、EB蒸着法、イオンプレーティング法等が挙げられる。スパッタリング系としては、高周波スパッタリング法、マグネトロンスパッタリング法、対向ターゲット型マグネトロンスパッタリング法、イオン注入法等が挙げられる。

物理的蒸着法においては、反応性ガスとして窒素、炭素、ケイ素、ホウ素、リンおよび硫黄からなる群から選ばれる1種以上の元素を含むガスを用いることによって、金属材料と反応性ガスとを反応させて、金属材料を導電性セラッミクスにすることができる。

【0027】

(ノイズ抑制層の材料定数の測定方法)

材料定数(複素誘電率、複素透磁率等。)の測定方法としては、平行金属板法、共振器法、導波管法、自由空間法等が挙げられる。

【0028】

平行金属板法は、被測定物と2枚の金属板からコンデンサー構造を形成して、LCRメータ等により測定した静電容量から複素誘電率を求める方法である。測定可能な対応周波数は低く、1GHz以下である。

【0029】

共振器法は、共振器(空洞共振器、誘電体共振器、平面回路共振器等。)に、被測定物を挿入し、共振器の前後での共振周波数やQ値変化を測定し、複素誘電率や複素透磁率を求める方法である。共振器法は、低損失材料の材料定数を精度よく測定できる。しかし、1種類の共振器では、特定周波数の測定しかできないため、材料定数の周波数依存性のデータを得るためには、多数の共振器を準備する必要がある。共振器の種類を変えることにより、1GHzから100GHz程度まで測定できる。

【0030】

導波管法は、伝送線路(導波管、同軸管等。)内に被測定材料を挿入して反射係数や透過係数を測定する方法である。

マクスウェル方程式の電界および磁界と、電信方程式の電圧および電流とを比較すると、複素誘電率の実部および虚部、複素透磁率の実部および虚部は、それぞれキャパシタンス、コンダクタンス、インダクタンス、レジスタンスに対応しているため、導波管法においては、被測定物の挿入前後の電磁界の変化を伝送線路理論として単純化して扱うことができる。導波管法によれば、ある周波数において計算して得た反射係数および透過係数と、ネットワークアナライザーを用いて測定した反射係数および透過係数とから、複素誘電率や複素透磁率を導くことができる。

【0031】

導波管法は、反射係数の測定方法の違いにより、反射波法と透過波法とに分類される。

反射波法は、導波管の終端に短絡板を設け、1ポートで反射係数を測定する方法である。透過波法は、導波管の両端をネットワークアナライザーに接続し、2ポートで透過係数を測定する方法である。通常、反射波法にて反射係数を測定することは、透過係数を測定するよりも難しく、精度の点で不利とされている。しかし、高損失材料を被測定物とする場合は、透過波が微弱となるため、透過波法よりも反射波法が好ましい。

【0032】

導波管法は、伝送線路の違いにより、方形導波管法と同軸管法とに分類される。

方形導波管法は、通常、TE10モードが伝播する、断面が矩形状の導波管を用い、管内に被測定物を設置し、定在波測定器によりインピーダンスを測定し、ネットワークアナライザーで反射係数または透過係数を測定し、測定結果と、伝送理論からの計算結果とから材料定数を求める方法である。測定波長が短くなると、導波管の機械的精度、被測定物の加工精度、配置精度等に影響されやすくなることから、測定可能な対応周波数は数GHzから数10GHzとなる。

【0033】

同軸管法は、TEMモードが伝播する伝送線路を用いる方法である。方形導波管と同様にして複素誘電率や複素透磁率を求めることができる。また、カットオフ周波数がないことから、より低い周波数においても測定でき、また1種類の同軸管で広い周波数範囲にて測定できることから効率的である。

【0034】

自由空間法は、導波管法と原理は同じであるが、自由空間を伝送線路とする方法であり、被測定物に電波を照射し、反射波もしくは透過波、または偏波特性を測定する方法である。被測定物としては、平板状で、数GHzの低い周波数における測定には、やや大きなサイズのものが必要となる。エネルギー効率と、測定機器や被測定物のサイズ効果とから、ホーンアンテナやレンズアンテナを用い、収束した電波を用いることが好ましい。

【0035】

材料定数の他の測定方法としては、被測定物を磁界中に入れ、磁気センサーの電圧およびインピーダンスを測定し、複素透磁率を求める方法(特開2004−69337号公報)、反射波法と同様に伝送線路としてマイクロストリップ線路を用い、被測定物の装荷前後のSパラメータ複素透磁率を求める短絡マイクロストリップ線路法等が挙げられる。

以上の材料定数の測定方法のうち、広い周波数範囲において、連続的に測定できる導波管法が好ましく、大掛かりな測定機器を用いず、高精度に複素誘電率等を求めることができることから、同軸管法が特に好ましい。

【0036】

ノイズ抑制層はそれ自体では自立性がないため、ノイズ抑制層の材料定数(複素誘電率および複素透磁率)を測定する際には、誘電体基材の表面にノイズ抑制層を形成したノイズ抑制シートを、被測定物として用いる。この際、誘電体基材のみの複素誘電率および複素透磁率を測定しておき、ノイズ抑制シートの複素誘電率および複素透磁率から差し引く補正を行うことにより、高い精度でノイズ抑制層の複素誘電率および複素透磁率を求めることができる。なお、ノイズ抑制シートの誘電体基材の厚さおよび材料が、後述の電磁界解析を行う対象の電子機器に含まれる誘電体基材の厚さおよび材料と同じ場合には、この補正を行う必要はない。

【0037】

図6に示すような、誘電体基材11の表面にノイズ抑制層10が形成され、誘電体基材11の裏面に導体層13が設けられた積層シート14の複素誘電率および複素透磁率を測定する場合、導体層13において測定のための入力信号が反射し、導体層13を透過しない。そのため、測定方法としては、積層シート14の導体層13を測定機器のグランドとして用い、導体層13を除いた誘電体基材11およびノイズ抑制層10からなるノイズ抑制シートを被測定物として用いることができる反射波法が好ましい。また、反射波法によれば、透過状態により誘電率を同時に測定できることから、効率的である。また、導体層13が付いたまま、導波管中に適当な空隙を有して被測定物を設置し、透過波法で測定できる部分装荷法は、積層シート14の測定方法として好ましい。また、従来の導波管法においては、高周波領域では被測定物の大きさを小さくする必要があり、被測定物の寸法精度、被測定物と導波管との接触に留意する必要があったが、部分装荷法においては、これらに留意することなく透過係数を容易に測定できる。

【0038】

<電子機器の製造方法>

本発明の電子機器の製造方法は、下記工程を有する製造方法である。

(a)ノイズ抑制層を有する電子機器を設計する工程。

(b)設計された電子機器について、電磁界シミュレータを用いて電磁界解析を行い、シミュレーション結果を得る工程。

(c)シミュレーション結果に基づいて、電子機器のEMCを評価し、設計を検証する工程。

(d)設計を検証した結果に基づいて、電子機器を製造する工程。

【0039】

((a)工程)

目標とするEMCの程度、電子機器の用途、性能等に応じて、ノイズ抑制層を有する電子機器の設計を行う。

【0040】

((b)工程)

設計された電子機器の構造、材料等の情報を電磁界シミュレータに入力し、電磁界解析を行い、シミュレーション結果を得る。この際、複数の周波数におけるノイズ抑制層の複素誘電率および複素透磁率も同時に電磁界シミュレータに入力する。

【0041】

電磁界シミュレータは、マクスウェルの方程式をもとに、伝搬する電磁波の振る舞いを解くものである。アルゴリズムの違いから大きく、有限要素法(FEM:finite element method)、差分法(FDM:finite difference method)、境界要素法(モーメント法(MoM:method of moments)等。)の3つに分類される。

【0042】

有限要素法は、解析対象の構造モデルを三角形または四面体の要素に分割し、要素内の電界、磁界に関係する物理値は一定として、各頂点の物理値で近似する方法であり、各頂点の物理値、頂点座標、境界条件から連立方程式を解く方法である。特徴として、要素が四面体であるため、構造モデルの形状にフィットした要素分割が行われ、周波数依存の複素誘電率等の材料定数を直接扱える。

【0043】

差分法は、解析対象の構造モデルを格子状に分割し、各格子点に未知の電界、磁界の変数を置き、各格子点でのマクスウェルの方程式の差分を求め、連立させ、大規模な線形連立方程式を立て、該連立方程式を、境界条件を入力して解く方法である。差分法を時間および空間の領域まで拡張し、電磁界を時間領域で解析する方法として、時間領域差分(FDTD:finite difference time domain)法等がある。電界、磁界を計算する格子点を空間的に交互に配置し、時間的に交互に計算するため、直感的に理解しやすく、高速に計算が行われるため、大規模な線形連立方程式も解くことができる。

【0044】

モーメント法は、導体の境界を分割し、すなわち電圧を境界条件として導体上の電流分布をマクスウェルの方程式をもとに計算する方法である。構造モデルを細かく分割する必要がなく、未知変数の数が少ないため、計算が容易である。

これらのうち、有限要素法は、周波数依存の複素誘電率および複素透磁率を直接入力でき、簡便である。

【0045】

周波数に大きく依存する複素誘電率および複素透磁率は、周波数によりその値が大きく変化するため、電磁界シミュレーションの結果を正しくするためには、なるべく多くの周波数における複素誘電率および複素透磁率を測定し、入力することが好ましい。

複素誘電率および複素透磁率の測定点の数は、対象とする周波数範囲のうち、100点以上がこのましく、200点以上がより好ましい。必要であれば、測定点間を補間しデータ数を増してもかまわない。また、複素誘電率および複素透磁率を入力する際には、実部たけではなく、虚部を入力することが、各成分の損失項としての効果を計算に関与させることができる点から好ましい。虚部の入力に際しては、直接虚部の値を入力してもよく、虚部を実部で除した正接(tanδ)等として入力してもよい。

【0046】

誘電体基材の表面に形成されたノイズ抑制層は、媒質型のメタマテリアルとして考えられ、また、誘電体基材の裏面に導体層がある場合は、伝送線路型のメタマテリアルとして機能するものと考えられる。そのため、周波数に依存するが、複素誘電率および複素透磁率の実部および虚部の絶対値は、それぞれ1000以上の大きな値を示す。そのため、このような大きな値を入力することにより、ノイズ抑制層を電磁界シミュレーションにより正しく評価できる。

【0047】

((c)工程)

電磁界シミュレータによる電磁界解析によって得られるシミュレーション結果から、電子機器のEMCを評価し、設計を検証する。具体的には、電子機器のEMCについてPI系、EMI系、またはSI系の検証を行い、電子機器の設計が、目標とするEMCのレベルに達しているかどうかを判断し、EMCに関して過剰な設計または未熟な設計であると判断される場合には、(a)工程に戻って電子機器の設計を見直し、再度(b)工程を行う。

【0048】

PI系の検証においては、電子機器の電源およびグランドに着目し、高周波電流(伝導ノイズ)、電圧変動の解析を行う。例えば、ノイズ抑制層の配置、電源系に接続されるビアまたは半導体素子の電源ピン、バイパスコンデンサ等の電子部品の特性値および配置について、交流解析や過渡解析を行う。

【0049】

EMI系の検証においては、電子機器から放射される電磁波(放射ノイズ)の解析を行う。放射される電磁波が、VCCI規格による規制値内に納まっているかを確認する、または、電子機器のノイズ発生部位を断定し、PI系の検証結果を総合して、特定部位での電磁界強度の変化を確認することによって、設計の改善効果予測等を行う。

【0050】

SI系の検証においては、信号伝送路における信号の減衰、遅延、反射、クロストークの影響を確認する。この際、電磁界シミュレータで得られたSパラメータデータを回路シミュレータに入力し、電子機器の回路解析を行い、ノイズ抑制層が装荷された回路基板への影響を確認してもよい。なお、Sパラメータデータを回路シミュレータに入力する場合、Sパラメータデータ回路シミュレータへ入力できる言語に変換する必要がある。

【0051】

回路シミュレータとしては、SPICE(simulation program with integrated circuit emphasis)、IBIS(i/o buffer information specifications)、IMIC(i/o interface model for integrated circuit)等が挙げられる。SPICEは、電磁界シミュレータの結果として出力されたSパラメータデータをもとに、R、L、G、Cのパラメータからなるネットリスト等をキルヒホッフの法則に基づいて計算するシミュレータである。

【0052】

((d)工程)

(c)工程における設計の検証の結果、電子機器の設計が、目標とするEMCのレベルに達していると判断された場合、目標とするEMCのレベルに達した電子機器の設計に基づいて、電子機器を公知の方法にて製造する。

【0053】

以上説明した本発明の電子機器の製造方法によれば、設計された電子機器について、電磁界シミュレータを用いて電磁界解析を行い、シミュレーション結果を得る際に、ノイズ抑制層の複素誘電率および複素透磁率を電磁界シミュレータに入力しているため、これまで電磁界シミュレータを用いた電子機器のEMCの評価方法が確立されていなかった、ノイズ抑制層を有する電子機器の電磁界シミュレータを用いた電磁界解析が可能となる。そのため、ノイズ抑制層を有する電子機器の設計を低コストで、かつ短時間で行うことができる。また、ノイズ抑制層の複素誘電率および複素透磁率を電磁界シミュレータに入力する際には、複数の周波数における複素誘電率および複素透磁率を入力しているため、対象とする周波数範囲にわたって正確なシミュレーション結果を得ることができる。

よって、本発明の電子機器の製造方法によれば、低コストで、かつ短時間で、EMC対策が精度よくなされた電子機器を設計、製造できる。

【実施例】

【0054】

(ノイズ抑制層の厚さ)

日立製作所社製、透過型電子顕微鏡H9000NARを用いてノイズ抑制層の断面を観察し、5箇所のノイズ抑制層の厚さを測定し、平均した。

【0055】

(表面抵抗)

石英ガラス上に金を蒸着して形成した、2本の薄膜金属電極(長さ10mm、幅5mm、電極間距離10mm)を用い、該電極上に被測定物を置き、被測定物上に、大きさ10mm×20mmの押さえ板を50gの荷重で押し付け、0.1mAの測定電流で電極間の抵抗を測定し、この値を持って表面抵抗とした。

【0056】

〔ノイズ抑制層の材料定数の測定〕

厚さ25μmのポリイミドフィルム(東レデュポン社製、カプトンHタイプ)の表面に、ニッケル金属を、窒素ガスを流入しながら反応性スパッタリング法にて蒸着して、図2のフィールドエミッション走査電子顕微鏡像に示す、窒化ニッケルを含む不均質な薄膜からなるノイズ抑制層を形成し、ノイズ抑制シートを得た。ノイズ抑制層の厚さは25nmであった。

【0057】

材料定数測定装置としては、Sパラメータ方式反射法による透磁率、誘電率測定用の同軸管タイプ測定キット(キーコム社製、39Dタイプ)と、該測定キットに接続されたベクトルネットワークアナライザー(アンリツ社製、37247C)と、該ベクトルネットワークアナライザーに接続された、測定用ソフト(キーコム社製)がインストールされたパソコンとを有するシステムを用いた。

【0058】

ノイズ抑制シートを、キーコム社の39Dタイプ(45MHz〜3GHz)の形状(外径D=38.97mm−0.02mm、−0.06mm、内径d=16.00mm+0.06mm、+0.02mm)に加工し、被測定物とした。

同じく、厚さ25μmのポリイミドフィルム(東レデュポン社製、カプトンHタイプ)を39Dタイプの形状に加工し、リファレンスとした。

【0059】

リファレンスを測定キットにセットして、校正短絡および校正開放のデータを取得した。ついで、被測定物を測定キットにセットし、試料開放および試料短絡のデータを取得した。パソコンに被測定物の厚さを入力し、4組の測定データから被測定物の振幅および位相の周波数特性値を得た。

【0060】

以上の測定結果から、被測定物およびリファレンスの複素誘電率および複素透磁率の周波数依存性のデータを得た。被測定物の複素誘電率および複素透磁率からリファレンスの複素誘電率および複素透磁率を差し引く補正を行い、ノイズ抑制層の複素誘電率および複素透磁率の周波数依存性のデータ(周波数の測定点=800点)を得た。ノイズ抑制層の複素誘電率の周波数依存性のグラフを図7に示す。ノイズ抑制層の複素透磁率の周波数依存性のグラフを図8に示す。

【0061】

〔実施例1〕

(a)工程:

プリント配線板のモデルとして、図9および図10に示す、グランド層と電源層とを有する2層基板を設計した。該2層基板50は、上から順に、電源層26、誘電体基材11、ノイズ抑制層10、誘電体層24、グランド層23を有して構成される。電源層26とグランド層23とは、2層基板50の長手方向の両端にてスルーホール51を介してSMA端子52で接続されている。

【0062】

2層基板50の長さは、232mmであり、幅は、102mmである。

誘電体基材11、ノイズ抑制層10、誘電体層24、グランド層23の長さおよび幅は、2層基板50と同じである。

電源層26の長さは、2層基板50と同じである。電源層26の幅は、長手方向に沿った両側部が2層基板50に比べ幅L(7mm)だけ短くされている。

【0063】

2層基板50の厚さは、1103μmである。

電源層26の厚さは、12μmである。

誘電体基材11の厚さは、3μmである。

ノイズ抑制層10の厚さは、25nmである。

誘電体層24の厚さは、1070μmである。

グランド層23の厚さは、18μmである。

【0064】

電源層26およびグランド層23の材料は、銅箔である。

誘電体基材11の材料は、エポキシ樹脂である。

ノイズ抑制層10の材料は、前記ノイズ抑制シートのノイズ抑制層と同じ窒化ニッケルである。

誘電体層24の材料は、ガラス繊維強化エポキシ樹脂である。

【0065】

(b)工程:

2層基板50の構造、材料等の情報を、有限要素法による電磁界シミュレータ(アンソフト(Ansoft)社製、HFSS)に入力し、電磁界解析を行い、Sパラメータ(S11(反射減衰量)およびS21(透過減衰量))を得た。この際、前記ノイズ抑制層の材料定数の測定にて得られた、ノイズ抑制層の複素誘電率(実部、虚部、tanδ)および複素透磁率(実部、虚部、tanδ)の周波数依存性のデータも同時に電磁界シミュレータに入力した。

シミュレーションによるSパラメータの周波数依存性のグラフを図11に示す。

【0066】

(c)工程:

共振周波数におけるS21(透過減衰量)が大きく、充分なノイズ抑制効果があることが確認された。よって、2層基板50は、充分なEMC対策がなされていると予測された。

【0067】

(d)工程:

図9および図10に示す2層基板50を実際に製造した。

厚さ12μmの銅箔(電源層26)の表面に、エポキシ系ワニスを塗布し、乾燥、硬化させ、厚さ3μmの誘電体基材11を形成した。

ついで、誘電体基材11の表面に、窒素ガス雰囲気下でニッケル金属を反応性スパッタリング法により物理的に蒸着し、窒化ニッケルを含む不均質な薄膜からなるノイズ抑制層10を形成した。ノイズ抑制層10の厚さは25nmであり、ノイズ抑制層10の表面抵抗は25Ωであった。

【0068】

ノイズ抑制層10の表面に、厚さ1070μmのエポキシ系プリプレグ(誘電体層24)および厚さ18μmの銅箔(グランド層23)を積層し、プリプレグを硬化させ、基板を製造した。

該基板から232mm×102mmの大きさの基板を切り出し、該基板の電源層26の銅箔の長手方向に沿った両側部を、幅L(7mm)にわたってエッチングし、除去した。

【0069】

該基板の長手方向の両末端に、電源層26およびグランド層23にスルーホール51を介して繋がるSMAコネクタ52を接続し、2層基板50を製造した。

SMAコネクタ52にベクトルネットワークアナライザー(アンリツ社製、37247D)を接続して、周波数50MHzから3GHzまでの400点でSパラメータを測定した。

実測によるSパラメータの周波数依存性のグラフを図11に示す。シミュレーションによるSパラメータと実測によるSパラメータとが、ほぼ一致することが確認された。

【産業上の利用可能性】

【0070】

本発明の電子機器の製造方法は、金属材料または導電性セラミックスを含む厚さ5〜200nmのノイズ抑制層を有する電子機器の設計、製造に有用である。

【図面の簡単な説明】

【0071】

【図1】プリント配線板(電子機器)の一例を示す断面図である。

【図2】ノイズ抑制層の表面を観察したフィールドエミッション走査電子顕微鏡像である。

【図3】ノイズ抑制層の表面の原子間力顕微鏡像である。

【図4】ノイズ抑制層の表面の原子間力顕微鏡像である。

【図5】ノイズ抑制層の表面の模式図である。

【図6】ノイズ抑制層の材料定数の測定に用いられる積層シート(被測定物)の一例を示す断面図である。

【図7】ノイズ抑制層の複素誘電率の周波数依存性を示すグラフである。

【図8】ノイズ抑制層の複素透磁率の周波数依存性を示すグラフである。

【図9】実施例で用いた2層基板の上面図である。

【図10】図9のX−X断面図である。

【図11】シミュレーションおよび実測によるSパラメータの周波数依存性を示すグラフである。

【符号の説明】

【0072】

10 ノイズ抑制層

20 プリント配線板(電子機器)

50 2層基板(電子機器)

【特許請求の範囲】

【請求項1】

金属材料または導電性セラミックスを含む厚さ5〜200nmのノイズ抑制層を有する電子機器の製造方法であって、

(a)ノイズ抑制層を有する電子機器を設計する工程と、

(b)設計された電子機器について、電磁界シミュレータを用いて電磁界解析を行い、シミュレーション結果を得る工程と、

(c)シミュレーション結果に基づいて、電子機器のEMCを評価し、設計を検証する工程と、

(d)設計を検証した結果に基づいて、電子機器を製造する工程とを有し、

(b)工程において、複数の周波数におけるノイズ抑制層の複素誘電率および複素透磁率を電磁界シミュレータに入力する、電子機器の製造方法。

【請求項2】

(b)工程において、電磁界シミュレータで得られたSパラメータデータを回路シミュレータに入力し、電子機器の回路解析を行う、請求項1に記載の電子機器の製造方法。

【請求項3】

(b)工程において、ノイズ抑制層の複素誘電率および複素透磁率の実部および虚部を電磁界シミュレータに入力する、請求項1または2に記載の電子機器の製造方法。

【請求項4】

ノイズ抑制層の複素誘電率および複素透磁率の実部および虚部の絶対値が、1000よりも大きい、請求項3に記載の電子機器の製造方法。

【請求項1】

金属材料または導電性セラミックスを含む厚さ5〜200nmのノイズ抑制層を有する電子機器の製造方法であって、

(a)ノイズ抑制層を有する電子機器を設計する工程と、

(b)設計された電子機器について、電磁界シミュレータを用いて電磁界解析を行い、シミュレーション結果を得る工程と、

(c)シミュレーション結果に基づいて、電子機器のEMCを評価し、設計を検証する工程と、

(d)設計を検証した結果に基づいて、電子機器を製造する工程とを有し、

(b)工程において、複数の周波数におけるノイズ抑制層の複素誘電率および複素透磁率を電磁界シミュレータに入力する、電子機器の製造方法。

【請求項2】

(b)工程において、電磁界シミュレータで得られたSパラメータデータを回路シミュレータに入力し、電子機器の回路解析を行う、請求項1に記載の電子機器の製造方法。

【請求項3】

(b)工程において、ノイズ抑制層の複素誘電率および複素透磁率の実部および虚部を電磁界シミュレータに入力する、請求項1または2に記載の電子機器の製造方法。

【請求項4】

ノイズ抑制層の複素誘電率および複素透磁率の実部および虚部の絶対値が、1000よりも大きい、請求項3に記載の電子機器の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2008−204086(P2008−204086A)

【公開日】平成20年9月4日(2008.9.4)

【国際特許分類】

【出願番号】特願2007−38305(P2007−38305)

【出願日】平成19年2月19日(2007.2.19)

【出願人】(000190116)信越ポリマー株式会社 (1,394)

【Fターム(参考)】

【公開日】平成20年9月4日(2008.9.4)

【国際特許分類】

【出願日】平成19年2月19日(2007.2.19)

【出願人】(000190116)信越ポリマー株式会社 (1,394)

【Fターム(参考)】

[ Back to top ]