電子機器用基板及び電子機器

【課題】電気抵抗の低い貫通電極構造、または、放熱特性に優れた熱伝導路を有する電子機器用基板及びそれを用いた電子機器を提供すること。

【解決手段】基板1は、複数の貫通電極2及び柱状ヒートシンク3の少なくとも一方を有する。貫通電極2は、カーボンナノチューブを含有し、基板1に設けられたビア20を鋳型とする鋳込み成形体でなる。柱状ヒートシンク3は、基板に設けられたビア30を鋳型とする鋳込み成形体でなり、炭素原子構造体を含有する。

【解決手段】基板1は、複数の貫通電極2及び柱状ヒートシンク3の少なくとも一方を有する。貫通電極2は、カーボンナノチューブを含有し、基板1に設けられたビア20を鋳型とする鋳込み成形体でなる。柱状ヒートシンク3は、基板に設けられたビア30を鋳型とする鋳込み成形体でなり、炭素原子構造体を含有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子機器用基板及び電子機器に関する。

【背景技術】

【0002】

例えば、各種スケールの集積回路、各種半導体素子もしくはそのチップ等の電子機器においては、基板上に素子を配置し、その間をワイヤ・ボンディングなどの手段で接続する方法がとられてきた。しかし、この方法では、ワイヤ・ボンディング工程が必要な上に、実装面積が素子の数とともに増加し、配線長の増加から信号遅延が大きくなる。

【0003】

そこで、基板に貫通電極を設け、従来のワイヤ・ボンディングを、この貫通電極によって置き換えるTSV(Through−Silicon−Via)技術が提案されている。特許文献1(特開平11−298138号公報)、特許文献2(特開2000−228410号公報)、特許文献3(特開2002−158191号公報)及び特許文献4(特開2003−257891号公報)には、TSV技術に不可欠な貫通電極形成技術が開示されている。ワイヤ・ボンディングに対するTSV技術の優位性は、次のように言われている。

【0004】

まず、ワイヤ・ボンディングでは、100〜200本と接続本数が限られていたが、TSV技術を使えば、μmオーダの間隔で接続用貫通電極を配列できるため、数千本単位での接続本数が可能となる。

【0005】

また、接続距離が最短になるので、ノイズを受けにくくなること、寄生容量や抵抗が小さくて済むため遅延や減衰、波形の劣化が少なくなること、増幅や静電破壊保護のための余分な回路が不要になること、これらによって、回路の高速動作と低消費電力化が実現されることなどの利点が得られる。

【0006】

TSV技術を用いることにより、アナログやデジタルの回路、DRAMのようなメモリ回路、CPUのようなロジック回路などを含む電子デバイスは勿論のこと、アナログ高周波回路と低周波で低消費電力の回路といった異種の回路を、別々のプロセスによって作り、それらを積層した電子デバイスを得ることもできる。

【0007】

3次元集積回路(3D−IC)にTSV技術を使用すれば、大量の機能を小さな占有面積の中に詰め込めるようになる。加えて、素子同士の重要な電気経路が劇的に短く出来るために、処理の高速化が導かれる。

【0008】

TSV技術の適用に当たっては、ビア(貫通電極)を形成しなければならない。その手段として、貫通電極を、Cu電気メッキによって形成する方法が一般的である。

【0009】

しかし、電気めっきの処理時間がどうしても長くなるから、製造効率が悪くなる。しかも、ビアは、通常、アスペクト比が5以上にもなり、また、ビアの内壁面に凹凸が生じるのが普通であるため、めっき下地膜をビア内壁面の全面に均一に形成することが困難である。このため、ビアの内壁面と貫通電極となるめっき膜との間に空洞や隙間が発生してしまい、電気抵抗の増大、及び、信頼性低下等の原因となる。また、電気抵抗を、Cuの有する電気抵抗値以下にはなしえないという限界も生じる。

【0010】

更に、TSV技術の適用によって、電子機器の高密度化、高性能化、高速化、小型化、薄型化及び軽量化が進展すると、動作によって発生する熱量が増大するのに加えて、その放熱構造の構築が難しくなり、いかにして放熱するかが、大きな問題となる。放熱が不十分であると、発生した熱が蓄積され、異常発熱に至り、電子部品の接合強度が失われ、電気的接続の信頼性が損なわれたり、あるいは、電子部品の電気的特性が変動し、最悪の場合には、熱暴走、熱破壊等を招きかねない。

【0011】

このような放熱手段として、従来より種々の技術が知られている。例えば、特許文献5(特開2008−294253号公報)は、Ag粉末を含む導電性ペーストを充填して伝熱ビア導体を形成する技術を開示している。また、特許文献6(特開2005−158957号公報)は、熱伝導率の優れた金属(銅、はんだ、金)製であるか、発光素子サブマウント構造体の上面からビアを空け、ビアの側面に金メッキを施して、はんだを充填することで、サーマルビアを形成する技術を開示している。特許文献7(特開平10−098127号公報)は、銀ペースト、銅ペースト等の金属粉含有樹脂や、金属棒と金属粉含有樹脂の複合体等を用いた導熱体を開示している。更に、特許文献8(特開2007−294834号公報)は、Cu、Niなどの金属を用いたサーマルビアを開示している。しかし、何れの従来技術の場合も、放熱特性の向上や、製造コスト低減等、改善すべき問題を抱えている。

【0012】

又、貫通電極の工程時に、基板にクラックなどのダメージを与えてしまうという問題がある。原因の1つとして、柱状晶による応力が挙げられる。貫通電極中に柱状晶が形成された場合、柱状晶は、もともと大きく粒成長するものであるため、容易に亀裂の伝播経路となり得るからである。又、他の原因として、貫通電極が、製造工程における熱工程を経ている場合、金属一般が持つ正の体積変化率により、一般には、貫通電極を膨張させる方向に働き、その後、収縮するということが挙げられる。この熱膨張・収縮に伴い、基板に応力が発生し、クラックなどのダメージを与えてしまうからである。

【0013】

原因の1つである、熱工程での金属一般が持つ正の体積変化率に対して、特許文献9(特表2011−520286)では、熱導電に優れたカーボンナノチューブをTSVの材料として使用することが開示されている。

【0014】

しかし、特許文献9では、もう1つの原因である柱状晶についての記載はなく、又、基板表面に放熱層を設け、発生した熱を内層部から移動させるため、必ず放熱層を設ける必要があった。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開平11−298138号公報

【特許文献2】特開2000−228410号公報

【特許文献3】特開2002−158191号公報

【特許文献4】特開2003−257891号公報

【特許文献5】特開2008−294253号公報

【特許文献6】特開2005−158957号公報

【特許文献7】特開平10−098127号公報

【特許文献8】特開2007−294834号公報

【特許文献9】特表2011−520286

【発明の概要】

【発明が解決しようとする課題】

【0016】

本発明の課題は、電気抵抗の低い貫通電極構造を有する電子機器用基板及びそれを用いた電子機器を提供することである。

【0017】

本発明のもう一つの課題は、放熱特性に優れた熱伝導路を有する電子機器用基板及びそれを用いた電子機器を提供することである。

【0018】

本発明の更にもう一つの課題は、電気抵抗の低い貫通電極構造、及び、放熱特性に優れた熱伝導路を短時間で、効率よく形成することができる電子機器用基板及びそれを用いた電子機器を提供することである。

【0019】

本発明の更にもう一つの課題は、基板に対する応力を低減する貫通電極を提供することである。

【課題を解決するための手段】

【0020】

上述した課題を解決するため、本発明に係る電子機器用の基板は、複数の貫通電極を有しており、前記貫通電極は、カーボンナノチューブ、及び、ナノコンポジット結晶構造の金属/合金成分を含む。

【0021】

上述したように、本発明に係る基板において、貫通電極は、複数であるから、基板に搭載される電子部品や電子デバイスに対して、貫通電極を、正極及び負極として活用することができる。このため、ワイヤ・ボンディング等の電気配線が不要になり、高価なワイヤボンディング装置等に費やされていた生産設備費をカットし、製品コストを低減させることができる。

【0022】

貫通電極は、カーボンナノチューブ(Carbon nanotube)を含有する。カーボンナノチューブは、電流密度耐性が、109A/cm2で、銅の1、000倍以上の高電流密度耐性を有する。しかも、カーボンナノチューブ内では、電気良導体の銅との対比において、電子散乱が少ないため、電気抵抗が小さい。したがって、カーボンナノチューブを含有する貫通電極によれば、銅との対比において、電気抵抗が小さく、大きな電流を流しても、抵抗発熱量を低減することができる。更に、カーボンナノチューブは、その優れた弾性によって、応力低減作用を奏する。そのため、貫通電極に用いた場合、基板に亀裂・クラックが入るのを抑制することもできる。

【0023】

貫通電極は、カーボンナノチューブ自体によって構成してもよいし、カーボンナノチューブと、ナノコンポジット結晶構造の金属/合金成分を含む複合材料によって構成してもよい。カーボンナノチューブ、及び、ナノコンポジット結晶構造の金属/合金成分を含む貫通電極は、大きさが、ナノレベルに制限された組織(結晶)を含むから、その効果として、貫通電極に発生する応力が小さくなる。

【0024】

カーボンナノチューブと有機材料とを混合し、必要であれば、第3成分として、無機粉末を混合又はナノコンポジット結晶構造の金属/合金成分を添加して、ペースト化した複合材料で構成してもよい。

【0025】

更に、貫通電極は、ナノコンポジット結晶構造の金属/合金成分を含有する。ナノコンポジット結晶構造の金属/合金成分を含有する貫通電極は、応力が小さくなる。しかも、ナノコンポジット結晶構造には、柱状晶の発生を抑制し、柱状ヒートシンクの等軸晶化を促進する働きがあるため、より応力低減効果を奏することができる。

【0026】

上述したように、ナノコンポジット結晶構造には、柱状晶の発生を抑制し、等軸晶化を促進する働きはあるが、柱状晶の生成は零ではない。ナノコンポジット結晶構造とともに、カーボンナノチューブを共存させる構成によれば、ナノコンポジット結晶構造に発生することのある柱状晶による応力の増大を、カーボンナノチューブの有する弾性により、緩和することができる。よって、前記基板に加わる応力、ストレス、又は、特性・劣化を、更に確実に抑制することができる。

【0027】

上述したナノコンポジット結晶構造の有する特有の特性により、半導体基板(ウエハ)に形成された半導体回路の特性劣化が抑制される。また、半導体基板に亀裂・クラックが入るのを抑制することもできる。

【0028】

貫通電極を支持する基板は、セラミック等の無機基板、銅張り基板等に見られる有機基板又は半導体基板の少なくとも一種を含むことができる。基板を構成する無機基板、有機基板が導電性を有する場合、及び、半導体基板でなる場合は、貫通電極は、導電性の無機基板、導電性の有機基板及び半導体基板に対して、電気絶縁膜または電気絶縁層によって電気絶縁される。そのような絶縁構造は、貫通孔の鋳型となる孔の内壁面を酸化又は窒化して得られた絶縁膜、孔の内壁面に付着させた絶縁層によって実現することができる。上述した絶縁構造は、孔から微小間隔を隔ててその周りにリング状に設けてもよい。

【0029】

本発明に係る貫通電極は、基板に設けられたビアを鋳型とする鋳込み成形体であっても良い。鋳込み成形体は、ビアの側壁面に対する密着力が高く、巣、空隙、空洞のない緻密な構造を持ち、電気抵抗が小さく、電気伝導性に優れた貫通電極を有する基板が得られる。ビアの内壁面に凹凸があっても、貫通電極は、その凹凸に倣うように鋳込まれるから、ビアに対する密着強度の高い貫通電極が得られる。

【0030】

しかも、貫通電極が、ビアの内壁面の凹凸に倣うように鋳込まれる結果、貫通電極とビアの内壁面の凹凸が、貫通電極の抜けを阻止するアンカー部として働くので、基板に対する貫通電極の接合強度が高くなる。このことは、めっきによって貫通電極を形成する場合と異なって、ビアの内壁面に凹凸精度が要求されず、むしろ、若干の凹凸があった方が好ましい結果になるということを意味する。このため、ビアの形成が容易になる。

【0031】

本発明に係る基板は、上記貫通電極とは別に、または、貫通電極とともに、複数の柱状ヒートシンクを有する。前記柱状ヒートシンクは、前記基板に設けられたビアを鋳型とする鋳込み成形体でなる。

【0032】

柱状ヒートシンクも、基板に設けられたビアを鋳型とする鋳込み成形体でなるから、ビアの側壁面に対する密着力が高く、巣、空隙、空洞のない緻密な構造を持ち、熱伝導性及び放熱特性に優れた柱状ヒートシンクを有する基板が得られる。

【0033】

しかも、めっき法等、他の方法によって形成した場合と比較して、ビアの側壁面に対する密着力が高く、巣、空隙、空洞のない緻密な構造を持つ柱状ヒートシンクを、短時間で、効率よく形成することができる。

【0034】

柱状ヒートシンクは、熱伝導性の高い炭素原子構造体を含んでいる。このような炭素原子構造体には、ダイヤモンド、フラーレン又はカーボンナノチューブから選択された少なくとも一種が含まれる。

【0035】

上述した柱状ヒートシンクは、炭素原子構造体の有する高い熱伝導性により、放熱性に優れたものとなる。特に、カーボンナノチューブは、銅の約10倍の高熱伝導特性を有するから、極めて高い放熱特性を確保することができる。更に、必要であれば、第3成分として、有機成分を添加し、ペースト化した複合材料で構成してもよい。

【0036】

柱状ヒートシンクは、炭素原子構造体とともに、ナノコンポジット結晶構造の金属/合金成分を含む複合材料で構成されてもよい。

【0037】

本発明に係る基板は、上述した貫通電極及び柱状ヒートシンクを併せ持っていてもよい。具体的には、次のような構成になる。

(a)貫通電極がカーボンナノチューブを含有し、前記基板に設けられたビアを鋳型とする鋳込み成形体でなり、前記柱状ヒートシンクが前記基板に設けられたビアを鋳型とする鋳込み成形体でなる構成。

(b)上記(a)において、前記貫通電極及び前記柱状ヒートシンクの少なくとも一方が、ナノコンポジット結晶構造の金属/合金成分を含む構成。

(c)上記(a)において、前記柱状ヒートシンクが、熱伝導性の高い炭素原子構造体(ダイヤモンド、フラーレン又はカーボンナノチューブ等)を含有する構成。

(d)上記(a)において、前記柱状ヒートシンクが、ナノコンポジット結晶構造の金属/合金成分と、熱伝導性の高い炭素原子構造体とを含有する複合材料でなる構成。

(e)前記貫通電極が、前記基板に設けられたビアを鋳型とする鋳込み成形体でなり、前記柱状ヒートシンクが、熱伝導性の高い炭素原子構造体(ダイヤモンド、フラーレン又はカーボンナノチューブ等)を含有する構成。

【0038】

上述した基板は、電子部品と組み合わされて電子機器を構成する。この場合、電子部品は、前記基板に取り付けられる。これにより、電子部品に対して、電気抵抗の低い貫通電極による電気回路を構成するとともに、電子部品の動作によって発生した熱を、柱状ヒートシンクによって効率よく放熱し、電子部品の発熱による特性変動、誤動作、更には、熱暴走等を回避することができる。

【0039】

本発明において、電子部品には、能動素子、受動部品またはそれらを組み合わせた複合素子を含むことができる。また、電子機器には、電子工学の技術を応用した電気製品のほとんど全てが含まれる。電子機器には、更に、TSV技術を適用して、3次元積層構造としたもの、又は、インターポーザと各種素子と組み合わせて3次元積層構造としたものも含まれる。

【発明の効果】

【0040】

以上述べたように、本発明によれば、次のような効果を得ることができる。

(a)電気抵抗の低い貫通電極構造を有する電子機器用基板及びそれを用いた電子機器を提供することができる。

(b)放熱特性に優れた熱伝導路を有する電子機器用基板及びそれを用いた電子機器を提供することができる。

(c)電気抵抗の低い貫通電極構造、及び、放熱特性に優れた熱伝導路を短時間で、効率よく形成することができる電子機器用基板及びそれを用いた電子機器を提供することができる。

【0041】

本発明の他の目的、構成及び利点については、添付図面を参照し、更に詳しく説明する。添付図面は、単に、例示に過ぎない。

【図面の簡単な説明】

【0042】

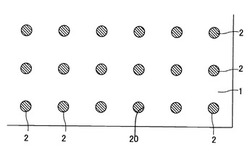

【図1】本発明に係る基板の一部を示す平面図である。

【図2】図1に示した基板の断面図である。

【図3】本発明に係るナノコンポジット結晶構造の金属/合金成分を含む複合材料を模式的に示す図である。

【図4】本発明に係るナノコンポジット結晶構造の金属/合金成分を含む複合材料を模式的に示す図である。

【図5】本発明に係るナノコンポジット結晶構造の金属/合金成分を含む複合材料を模式的に示す図である。

【図6】本発明に係るナノコンポジット結晶構造の金属/合金成分を含む複合材料を模式的に示す図である。

【図7】本発明に係る基板の断面のSEM像である。

【図8】本発明に係る基板の製造方法を示す図である。

【図9】本発明に係る基板を用いた電子機器の部分断面図である。

【図10】本発明に係る基板の他の実施例を示す図である。

【図11】図10に示した基板を用いた電子機器の部分断面図である。

【図12】本発明に係る基板の他の実施例を示す図である。

【図13】図12に示した基板を用いた電子機器の部分断面図である。

【図14】本発明に係る発光デバイスの一形態を示す部分断面図である。

【図15】図14に示した発光デバイスに用いられている支持体の平面図である。

【図16】図15の12−12線断面図である。

【図17】図14に示した発光デバイスに用いられる発光素子の外観を示す図である。

【図18】図17に示した発光素子の底面図である。

【図19】本発明に係る発光デバイスの他の形態を示す部分断面図である。

【図20】本発明に係る発光デバイスの更に別の一形態を示す部分断面図である。

【図21】本発明に係る照明装置の平面図である。

【図22】図21に示された照明装置の一部における拡大断面図である。

【図23】図22の断面図から発光素子と蛍光体とを除いた断面図である。

【図24】他の形態に係る発光デバイスの断面図である。

【図25】図24の断面図から発光素子と蛍光体とを除いた断面図である。

【図26】本発明に係る液晶ディスプレイの断面図である。

【図27】画素の平面図である。

【図28】本発明に係る発光ダイオードディスプレイの平面図である。

【図29】本発明に係る基板の他の形態を示す断面図である。

【図30】図29に示した基板を用いた電子デバイスの部分断面図である。

【図31】本発明に係る基板の他の形態を示す部分断面図である。

【図32】図31に示した基板を用いた電子デバイスの部分断面図である。

【図33】本発明に係る電子デバイスの他の形態を示す部分断面図である。

【図34】本発明に係る電子デバイスの他の形態を示す部分断面図である。

【図35】本発明に係る電子デバイスの他の形態を示す部分断面図である。

【図36】本発明に係る電子デバイスの他の形態を示す部分断面図である。

【図37】本発明に係る放熱用基板の一部を示す断面図である。

【図38】本発明に係る放熱用基板の他の形態における一部を示す断面図である。

【図39】本発明に係る放熱用基板の他の形態における一部を示す断面図である。

【図40】本発明に係る放熱用基板の他の形態における一部を示す断面図である。

【図41】本発明に係る放熱用基板の他の形態における一部を示す断面図である。

【図42】本発明に係る放熱用基板の他の形態における一部を示す断面図である。

【図43】本発明に係る放熱用基板の他の形態における一部を示す平面図である。

【図44】図43に示した放熱用基板の断面図である。

【図45】本発明に係る放熱用基板の他の形態における一部を示す断面図である。

【図46】本発明に係る放熱用基板の他の形態における一部を示す断面図である。

【図47】車載電子機器の回路図である。

【図48】図47に示した車載電子機器の放熱構造を示す部分断面図である。

【図49】パーソナル・コンピュータや携帯電話機等の電子機器に採用し得る放熱構造を示す部分断面図である。

【図50】パーソナル・コンピュータや携帯電話機等の電子機器に採用し得る放熱構造を示す部分断面図である。

【発明を実施するための形態】

【0043】

図1及び図2を参照すると、本発明に係る電子機器用基板1は、μmオーダの所定ピッチをもって配置された複数の貫通電極2を有している。貫通電極2のビア径も、μmオーダである。貫通電極2は、カーボンナノチューブを含有し、基板1に設けられたビア20を鋳型とする鋳込み成形体でなる。

【0044】

好ましくは、貫通電極2は、基板1に設けられたビア20を鋳型とする鋳込み成形体である。貫通電極2が鋳込み成形体である場合、ビア20の側壁面に対する密着力が高く、巣、空隙、空洞のない緻密な構造を持ち、電気抵抗が小さく、電気伝導性に優れた貫通電極2を有する基板1が得られる。ビア20の内壁面に凹凸があっても、貫通電極2は、その凹凸に倣うように鋳込まれるから、ビア20に対する密着強度の高い貫通電極2が得られる。

【0045】

しかも、貫通電極2が、ビア20の内壁面の凹凸に倣うように鋳込まれる結果、貫通電極2とビア20の内壁面の凹凸が、貫通電極2の抜けを阻止するアンカー部として働くので、基板1に対する貫通電極2の結合強度が高くなる。このことは、めっきによって貫通電極2を形成する場合と異なって、ビア20の内壁面に凹凸精度が要求されず、むしろ、若干の凹凸があった方が好ましいということを意味する。このため、ビア20の形成が容易になる。

【0046】

SEM像を示す図7を参照すると、基板1に設けられたビア20内に、貫通電極2が、巣、空隙、空洞のない緻密な構造を保って充填され、ビア20の側壁面が凹凸を有するにも関わらず、貫通電極2がビア20の側壁面に密着している。

【0047】

ビア20は、レーザ、ケミカル・エッチング又はプラズマエッチング等によって穿ビアされるものであり、その内壁面に穿ビア工程に付随する凹凸が生じるのであるが、図7に示すように、貫通電極2は、ビア20の内壁面が凹凸面となっているにも関わらず、その凹凸面を倣うように充填されて、ビア20の内壁面に密着し、巣、空隙、空洞のない緻密な構造となっている。しかも、ビア20の内壁面の凹凸が一種のアンカー効果を生じるので、柱状ヒートシンク3がビア20から浮き上がったり、あるは浮動したりすることなく、ビア20内に確実に固定される。これは、裏返せば、スパッタ及びめっきの併用によって形成する一般的技術と比較して、ビア20の形成に当たって、その内壁面の平面度に気を使わずに済み、却って、ビア20をある程度ラフに形成した方がよい結果を生むということでもある。

【0048】

貫通電極2は、カーボンナノチューブ(Carbon nanotube)を含有する。カーボンナノチューブは、炭素によって作られる六員環ネットワーク(グラフェンシート)が単層あるいは多層の同軸管状になった物質である。単層のシングルウォールナノチューブ (SWNT)、多層のマルチウォールナノチューブ (MWNT) の何れを用いてもよい。具体的には、カーボンナノチューブをフィラーとして、アルミニュウム合金中に配向して添加した複合材料を用いることができる。

【0049】

カーボンナノチューブは、電流密度耐性が、109A/cm2で、銅の1、000倍以上の高電流密度耐性を有する。しかも、カーボンナノチューブ内では、電気良導体である銅との対比において、電子散乱が少ないため、電気抵抗が小さい。したがって、カーボンナノチューブを含有する貫通電極2によれば、銅との対比において、電気抵抗が小さく、大きな電流を流しても、抵抗発熱量を低減することができる。

【0050】

貫通電極2は、カーボンナノチューブ自体によって構成してもよいし、カーボンナノチューブと、ナノコンポジット結晶構造の金属/合金成分を含む複合材料によって構成してもよい。本発明において、「ナノ」とは、1μm未満のサイズをいう。

【0051】

カーボンナノチューブ及びナノコンポジット結晶構造の金属/合金成分を含む貫通電極2は、大きさが、ナノレベルに制限された組織(結晶)を含むから、その効果として、貫通電極2に発生する応力が小さくなる。

【0052】

図3〜図6は、本発明に係るナノコンポジット結晶構造を模式的に示す図である。図3に示す形態は、第1結晶組織80の内部に、ナノサイズである第2結晶組織81を分散させたものである。このほか、図4〜図6に模式的に示すように、第1結晶組織80の粒界に、ナノサイズである第2結晶組織81を分散させたもの(図4)、これとは逆に、第2結晶組織81の粒界に、ナノサイズである第1結晶組織80を分散させたもの、第1結晶組織80の内部に、ナノサイズである第2結晶組織81を分散させるとともに、第1結晶組織80の粒界に、ナノサイズである第2結晶組織81を分散させたもの(図5)、第1結晶組織80及び第2結晶組織81の両者がナノサイズであるもの(図6)などの形態をとることができる。図示は省略するけれども、図3〜図6の形態を組み合せたものであってもよい。さらに、上述した第1結晶組織80及び第2結晶組織81によるナノコンポジット結晶構造とは、異なる他種のナノコンポジット結晶構造を形成させてもよい。

【0053】

第1結晶組織80及び第2結晶組織81は、金属成分が部分的に重なっていてもよいし、全く異なっていてもよい。第1結晶組織80及び第2結晶組織81の別は、含まれている金属元素の融点の違いや、共晶化や合金化の有無などによって生まれる。また、このナノコンポジット結晶構造は、ナノ金属/合金粒子の溶融充填方法や、スパッタ併用めっき法などによって実現することができる。

【0054】

第1結晶組織80及び第2結晶組織81の代表的な例は、非共晶組織と共晶組織の組み合わせである。共晶は、合金などの結晶組織の1つであって、たとえば2種類の金属Aと金属Bを溶解して合金をつくる場合、金属Aと金属Bの比率が金属Aに対する金属Bの固溶限(固溶体をつくる限界)までの範囲や、金属Bに対する金属Aの固溶限までの範囲にないと、合金は、それぞれ違った成分比の固溶体の結晶がまじりあったものになり、共晶組織を構成する。金属Aと金属Bとが、上記条件を満たさない場合や、溶解温度が共晶点まで達しなかった場合には、本来、共晶となりえる金属A,Bであっても、非共晶組織となる。非共晶組織は、共晶化のための金属元素とは異なる第3の金属元素を添加することによっても得られる。

【0055】

第1結晶組織80を非共晶組織とした場合、第2結晶組織81は共晶組織である。この組み合わせを前提としたナノコンポジット結晶構造には、図3〜図6を参照すると明らかなように、

(a)非共晶組織の内部に共晶組織でなるナノ粒子を分散させたもの、

(b)非共晶組織の粒界に共晶組織でなるナノ粒子を分散させたもの、

(c)共晶組織の粒界に非共晶組織でなるナノ粒子を分散させたもの、

(d)非共晶組織の内部に共晶組織でなるナノ粒子を分散させるとともに、非共晶組織の粒界に共晶組織でなるナノ粒子を分散させたもの、

(e)共晶組織及び非共晶組織が、共にナノサイズであるもの

などが含まれる。

【0056】

貫通電極の材質特性を決定づける重要な因子として、柱状晶と等軸晶とがある。柱状晶は、もともと大きく粒成長するものである。そのため、容易に亀裂の伝播経路となり、基板のクラックなどを招く。

【0057】

これに対して、等軸晶は粒成長が等方的で粒径自体も小さいから、基板に発生する応力も小さくなる。

【0058】

又、貫通電極が、製造工程における熱工程を経ている場合、金属一般が持つ正の体積変化率により、一般には、貫通電極を膨張させる方向に働き、その後、収縮する。この熱膨張・収縮に伴い、基板に応力が発生する。等軸晶は、この金属膨張による応力発生に対しても抑制効果を奏する。

【0059】

上述したように本発明に係るナノコンポジット結晶は、上述した構成を有するので、柱状晶化を抑制し、等軸晶化を促進する。よって、基板に加わる応力、ストレス、又は、特性・劣化を抑制する。

【0060】

しかも、ナノコンポジット結晶構造には、縦導体の等軸晶化を促進する働きがある。上述したカーボンナノチューブ及びナノコンポジット結晶構造の有する特有の特性により、特に、半導体基板において、半導体回路の特性劣化が抑制される。また、基板に亀裂・クラックが入るのを抑制することもできる。

【0061】

上述したように、ナノコンポジット結晶構造には、柱状晶の発生を抑制し、等軸晶化を促進する働きはあるが、柱状晶の生成は零ではない。柱状晶が発生することもある。ナノコンポジット結晶構造とともに、カーボンナノチューブを共存させる構成によれば、ナノコンポジット結晶構造に発生することのある柱状晶による応力の増大を、カーボンナノチューブの有する弾性により、緩和することができる。よって、前記基板に加わる応力、ストレス、又は、特性・劣化を、更に確実に抑制することができる。

【0062】

ナノコンポジット結晶構造の金属/合金成分としては、Bi、In、Sn及びCuを例示することができる。特に、Biを含有させると、Biの持つ凝固時の体積膨張特性により、ビア20の内部で、空洞や空隙を生じることのない緻密な貫通電極2を形成することができる。もっとも、Bi等を含有させると、電気抵抗が増大する傾向にあるので、要求される電気抵抗値を満たす限度で、Biを使用することが好ましい。

【0063】

更に、カーボンナノチューブと、有機材料とを混合し、必要であれば、セラミック又はガラス等の無機粉末又はナノコンポジット結晶構造の金属/合金成分を添加した複合材料で構成してもよい。

【0064】

貫通電極2を形成する基板1は、セラミック等の無機基板、銅張り基板等に見られる有機基板又は半導体基板の少なくとも一種を含むことができる。用い得る半導体基板には、特に制限はない。Si基板(シリコン基板)、SiC基板 (シリコンカーバイド基板)、GaN基板 (窒化ガリウム基板)、ZnO基板 (酸化亜鉛基板)等は勿論のこと、SOI基板(Silicon on insulator)等を用いることができる。基板1を構成する無機基板、有機基板が導電性を有する場合、及び、基板1が上述したような半導体基板でなる場合は、貫通電極2は、導電性の無機基板、導電性の有機基板及び半導体基板に対して、電気絶縁膜または電気絶縁層によって電気絶縁される。そのような絶縁構造は、貫通電極2の鋳型となる孔20の内壁面を酸化又は窒化して得られた絶縁膜、孔20の内壁面に付着させた絶縁層によって実現することができる。上述した絶縁層は、孔20から微小間隔を隔ててその周りにリング状に設けてもよい。

【0065】

貫通電極2の成形にあたっては、まず、図8(A)に図示するように、予め、厚み方向に貫通する微細なビア20を多数設けた基板1を、支持台S1の上に搭載する。ビア20の下側は、支持台S1によって閉塞されている。もっとも、ビア20は、非貫通孔であってもよい。

【0066】

次に、図8(B)に示すように、基板1に設けられたビア20を鋳型として、その内部に液状、ペースト状または粉体状の電極材料2を鋳込む。その後、図8(C)に図示するように、ビア20内に鋳込まれた電極材料2に、機械的な力F1、例えばプレス板P1を用いたプレス圧、射出圧または転圧を印加しながら凝固させる。これによって、図8(D)に示すように、巣、空隙、空洞のない緻密な構造を持ち、ビア20の側壁面に密着した鋳込み成形体たる貫通電極2が成形される。そして、この成形体の構造は、図7のSEM像によって明らかにされている。

【0067】

基板1に設けられたビア20内に電極材料2を鋳込む工程は、減圧された真空チャンバ内で実行することが好ましい。この減圧と、その後の印加圧力によって、差圧充填を行うことができるからである。

【0068】

電極材料2が、カーボンナノチューブ及びナノコンポジット結晶構造の金属/合金成分を含む複合材料を含む場合は、これらの金属/合金成分の溶融金属にカーボンナノチューブを混ぜた液状複合材料2をビア20内に鋳込み、鋳込まれた液状複合材料2に、プレス板P1を用いたプレス圧、射出圧または転圧を印加しながら、冷却し、凝固させる。

【0069】

また、電極材料2が、カーボンナノチューブと、有機材料と、溶剤とを含有するペースト状材料である場合には、プレス板P1を用いたプレス圧、射出圧または転圧を印加しながら、加熱硬化させる。電極材料2が粉体の場合は、溶融状態でビア20内に注入充填するか、粉体の状態でビア20内に注入した後、加熱溶融させるとよい。

【0070】

図9は、図1及び図2に示した基板を、インターポーザとして用いた電子機器の一例を示している。基板1は、インターポーザとして、例えば半導体チップ等でなる電子デバイス6、6の間に配置されている。電子デバイス6、6は、電極が、接合膜4、4によって、貫通電極2にそれぞれ接続されている。

【0071】

貫通電極2は、複数備えられているから、これらの独立する複数の貫通電極2を、基板1に搭載される電子デバイス6、6に対する正極、負極として活用することができる。このため、ワイヤ・ボンディング等の電気配線が不要になり、高価なワイヤボンディング装置等に費やされていた生産設備費をカットし、製品コストを低減させることができる。

【0072】

基板1は、上記貫通電極2とは別に、または、貫通電極2とともに、柱状ヒートシンクを有していてもよい。まず、図10を参照すると、基板1は、柱状ヒートシンク3を有する。柱状ヒートシンク3は、基板1に設けられたビア30を鋳型とする鋳込み成形体でなる。

柱状ヒートシンク3は、その両端が基板1の厚み方向に貫通し、互いに微小間隔を隔てて、例えばマトリクス状に多数配置されている。柱状ヒートシンク3は、その一端(下端)が基板1の裏面(他面)に設けられた放熱層31によって共通に接続され、他端(上端)が、基板1の表面に導出されている。表面側にも、放熱層を設けることができる。

【0073】

柱状ヒートシンク3も、基板1に設けられたビア30を鋳型とする鋳込み成形体でなるから、ビア30の側壁面に対する密着力が高く、巣、空隙、空洞のない緻密な構造を持ち、熱伝導性及び放熱特性に優れた柱状ヒートシンク3を有する基板1が得られる。

【0074】

しかも、めっき法等、他の方法によって形成した場合と比較して、ビアの側壁面に対する密着力が高く、巣、空隙、空洞のない緻密な構造を持つ柱状ヒートシンク3を、短時間で、効率よく形成することができる。

【0075】

柱状ヒートシンク3を形成する技術として、ビア30の側面にメッキを施した上で、サーマルビアを形成するとすれば、連続しためっき膜を形成ためには、ビア30の内壁面を、凹凸の極めて小さい平滑な面にしなければならず、ビア形成工程に長時間を費やさなければならなくなる。しかも、ビア30のアスペクト比が高くなれば、めっきのための下地膜を連続する均質な膜として形成することが、極めて困難になる。

【0076】

これに対して、柱状ヒートシンク3を、基板1に設けられたビア30を鋳型とする鋳込み成形体として構成する本発明では、ビア30の内壁面(側壁面)が凹凸面となっていても、柱状ヒートシンク3は、鋳込みの過程で、その凹凸面を倣うように充填されてゆく。したがって、巣、空隙、空洞のない緻密な構造を持ち、ビア30の側壁面に密着した構造の柱状ヒートシンク3が得られる。よって、熱伝導性及び放熱特性に優れた柱状ヒートシンク3が実現される。

【0077】

しかも、ビア30の内壁面の凹凸が一種のアンカー効果を生じるので、柱状ヒートシンク3がビア30から浮き上がったり、あるいは浮動したりすることなく、ビア30の内部に確実に固定される。これは、裏返せば、従来技術との対比において、ビア30の形成に当たって、その内壁面の平面度に気を使わずに済み、却って、ビア30をある程度ラフに形成した方がよい結果を生むということでもある。

【0078】

柱状ヒートシンク3は、複数であって、それぞれは、基板1の面内に分布させてあり、その一端(下端)が基板1の裏面(他面)に設けられた放熱層31によって共通に接続されているから、柱状ヒートシンク3から基板1の厚み方向に伝達されてきた熱を、厚み方向と直交する面と並行な方向に拡散しながら放熱する3次元的な放熱経路が形成される。これにより、放熱性を向上させることができる。柱状ヒートシンク3を構成する材料の熱抵抗、及び、柱状ヒートシンク3の占有率を適切に選ぶことにより、電子部品又は電子デバイス6の動作によって生じた熱を、柱状ヒートシンク3によって、一層効率よく、基板1の外部に放熱しえる。

【0079】

柱状ヒートシンク3の放熱特性は、基本的には、その組成材料の持つ熱伝導率(又は熱抵抗)と、基板1の平面積に対して、柱状ヒートシンク3の全体が占める占有率とによって定まる。例えば、柱状ヒートシンク3として、熱抵抗の低い材料を用いた場合には、占有率を低下させ、熱抵抗の高い材料を用いた場合には、占有率を上げる。即ち、柱状ヒートシンク3の占有率は、その組成材料の熱伝導率を考慮して定めることになる。逆に、占有率に制限がある場合には、求められる放熱特性を考慮して、適合する熱伝導率の材料を選択することになる。

【0080】

柱状ヒートシンク3は、熱伝導性の高い炭素原子構造体を含んでいる。このような炭素原子構造体の具体例としては、ダイヤモンド、フラーレン又はカーボンナノチューブから選択された少なくとも一種を挙げることができる。

【0081】

炭素原子構造体を用いた柱状ヒートシンク3は、炭素原子構造体の有する高い熱伝導性により、放熱性に優れたものとなる。特に、カーボンナノチューブは、銅の10倍の高熱伝導特性を有するから、極めて高い放熱特性を確保することができる。具体例として、カーボンナノチューブをフィラーとして、アルミニュウム合金中に配向して添加したものを用いることができる。この複合材の熱伝導率は、アルミニュウム合金の熱伝導率の3倍を超える。この具体例に示されるように、カーボンナノチューブは、フィラーとして用いることが望ましい。カーボンナノチューブとともに、それよりも繊維が太い気相成長カーボンファイバを、フィラーとして併用してもよい。

【0082】

柱状ヒートシンク3は、ナノコンポジット結晶構造の金属/合金成分を含むことができる。この場合、柱状ヒートシンク3は、炭素原子構造体とナノコンポジット結晶構造の金属/合金成分との複合材料でなる。

【0083】

この複合材料でなる柱状ヒートシンク3は、炭素原子構造体を含むことによる上記効果とともに、ナノコンポジット結晶構造の金属/合金成分を含むことの効果として、柱状ヒートシンク3に発生する応力が小さくなるという効果を奏する。しかも、ナノコンポジット結晶構造には、柱状ヒートシンク3の等軸晶化を促進する働きがあるから、応力が更に小さくなる。

【0084】

上述したナノコンポジット結晶構造の有する特有の特性により、基板1に形成された半導体回路の特性劣化が抑制される。また、基板1に亀裂・クラックが入るのを抑制することもできる。

【0085】

柱状ヒートシンク3の構成するナノコンポジット結晶構造材料の具体例としては、限定するものではないが、Al、Au、Cu、Ag、Sn等を例示することができる。もっとも、柱状ヒートシンク3は、熱抵抗ができるだけ小さいこと好ましいから、材料及び組成比等は、そのような視点から選定する必要がある。図示実施例では、柱状ヒートシンク3は、中身の詰まった中実柱状体であって、断面円形状であるが、角形状であってもよい。

【0086】

本発明に係る放熱用基板は、電子機器への適用において、発熱を伴う電子部品を取り付け、その熱を外部に放出するために用いられる。図11には、そのような電子機器の一例が示されている。図10に示した基板1の一面に、発熱を伴う電子部品又は電子デバイス6が、熱伝導性結合剤層51を介して搭載されている。放熱層31には、好ましくは、放熱ブロックを熱結合させる。電子部品又は電子デバイス6は、例えば、半導体チップ等の能動素子、又は、コンデンサ、インダクタ等の受動部品もしくはそれらの複合素子である。電子部品又は電子デバイス6は、半導体素子と受動部品とを併せ持つものであってもよいし、メモリ素子、論理回路素子またはアナログ回路素子であってもよい。これらの素子の単層であってもよいし、積層されたものであってもよい。

【0087】

ここで、本発明に係る基板1は、ビア30を鋳型とする鋳込み成形体でなる柱状ヒートシンク3を有しており、柱状ヒートシンク3により、ビア30の側壁面に密着し、巣、空隙、空洞のない緻密な構造を持ち、熱伝導性及び放熱特性に優れた放熱路が形成される。このため、電子機器への適用において、電子部品又は電子デバイス6に発生した熱を、熱伝導性及び放熱特性に優れた柱状ヒートシンク3を通して、効率よく、確実に放熱し、電子部品又は電子デバイス6の異常発熱、熱暴走、誤動作を回避することができる。

【0088】

次に、図12を参照すると、貫通電極2と、柱状ヒートシンク3とを併せ持つ基板1が図示されている。この場合、貫通電極2と、柱状ヒートシンク3との間には、次のような組合せが存在し得る。

(a)貫通電極2が、カーボンナノチューブを含有し、基板1に設けられたビア20を鋳型とする鋳込み成形体でなり、柱状ヒートシンク3が、基板1に設けられたビア30を鋳型とする鋳込み成形体でなる構成。

(b)上記(a)において、貫通電極2及び柱状ヒートシンク3が、ナノコンポジット結晶構造の金属/合金成分を含む構成。

(c)上記(a)において、柱状ヒートシンク3が、熱伝導性の高い炭素原子構造体(ダイヤモンド、フラーレン又はカーボンナノチューブ等)を含有する構成。

(d)上記(a)において、柱状ヒートシンク3が、ナノコンポジット結晶構造の金属/合金成分と、熱伝導性の高い炭素原子構造体(ダイヤモンド、フラーレン又はカーボンナノチューブ等)を含有する複合材料でなる構成。

(e)貫通電極2が、基板1に設けられたビア20を鋳型とする鋳込み成形体でなり、柱状ヒートシンク3は、ナノコンポジット結晶構造の金属/合金成分を含み、基板1に設けられたビア30を鋳型とする鋳込み成形体でなる構成。貫通電極2がカーボンナノチューブを含有することは、必ずしも必要ではない。

(f)上記(e)において、柱状ヒートシンク3が、熱伝導性の高い炭素原子構造体(ダイヤモンド、フラーレン又はカーボンナノチューブ等)を含有する複合材料でなる構成。

(g)貫通電極2が、基板1に設けられたビア20を鋳型とする鋳込み成形体でなり、柱状ヒートシンク3が熱伝導性の高い炭素原子構造体(ダイヤモンド、フラーレン又はカーボンナノチューブ等)を含有する構成。貫通電極2がカーボンナノチューブを含有することは、必ずしも必要ではない。

【0089】

上述した基板1は、図13に図示するように、電子部品6と組み合わされて電子機器を構成する。電子部品6は、電極が貫通電極2に接合された状態で、基板1に取り付けられる。これにより、電子部品6に対して、電気抵抗の低い貫通電極2による電気回路を構成するとともに、電子部品6の動作によって発生した熱を、柱状ヒートシンク3によって効率よく放熱し、電子部品6の発熱による特性変動、誤動作、更には、熱暴走等を回避することができる。

【0090】

本発明において、電子部品には、能動素子、受動部品またはそれらを組み合わせた複合素子を含むことができる。能動素子の代表例として、発光ダイオード、各種メモリ、各種論理ICまたはアナログ回路素子等を例示することができる。受動部品には、キャパシタ、インダクタもしくは抵抗またはそれらを組み合わせた複合素子が含まれる。

【0091】

本発明において、電子機器には、電子工学の技術を応用した電気製品のほとんど全てが含まれる。具体例としては、パーソナル・コンピュータ、携帯電話機、デジタル家電、発光ダイオードを用いた発光装置、照明装置、交通信号灯、画像処理装置、イメージ・センサまたは車載電子機器等が含まれる。更には、TSV技術を適用して、3次元積層構造としたもの、又は、インターポーザと各種素子と組み合わせて3次元積層構造としたものも含まれる。次に、電子部品及び電子機器の具体的な実施例について説明する。例示する全ての実施例において、貫通電極及び柱状ヒートシンクは、既に述べた特徴を有し、作用効果を奏するので、それらの重複説明は省略する。

【0092】

実施例1:発光ダイオード及び発光デバイス

図14〜図16に図示された発光デバイスは、基板1と、発光素子6とを含む。発光素子6は蛍光層7によって覆われている。基板1は、いわゆるパッケージとなるものであって、2つの貫通電極2、2と、複数の柱状ヒートシンク3とを含み、一面に凹部11を有している。基板1の好ましい例は、Siを主成分とするものである。これとは異なって、基板1は、絶縁樹脂基板又は絶縁性セラミック基板で構成してもよい。基板1は、図示では、4角形状の外形を有するが、その形状は任意である。基板1の凹部11は、貫通電極2、2を、間隔をおいて囲むように形成されていて、その内側面のほぼ全周に、例えば、Al膜、Ag膜又はCr膜等でなる反射膜8がスパッタ等によって形成されている。反射膜8の下側には酸化膜等の絶縁膜を設けられることがある。

【0093】

貫通電極2、2のそれぞれは、凹部11を形成した領域内において、基板1を厚み方向に貫通し、一端が凹部11の内面に露出し、他端が基板1の他面に露出する。貫通電極2、2は、中身の詰まった中実柱状体であって、角形状、円形状等、任意の断面形状をとることができる。貫通電極2、2は、基板1を貫通する部分と、基板1の一面にあって、発光素子6と接合される部分との間で、その平面形状を異ならせてもよい。例えば、基板1を貫通する部分の断面形状を、角形状又は円形状等の形状とし、発光素子6と接合される部分を平面積の拡大されたパターンとするなどである。また、貫通電極2、2は、その端面形状を、接続される発光素子6の電極形状と対応させることが好ましい。このような観点から、実施例では、貫通電極2、2の一方の端面形状を、円形状とし、他方の端面形状を四角形状としてある。

【0094】

柱状ヒートシンク3は、その両端が基板1の厚み方向に貫通し、互いに微小間隔を隔てて、マトリクス状に多数配置されている。柱状ヒートシンク3は、基板1の裏面(他面)に設けられた放熱層31によって共通に接続されている。貫通電極2、2は、放熱層31から独立させてある。放熱層31の形態は、図示の膜状に限らず、拡大された放熱面積を有する3次元的構造であってもよい。

【0095】

発光素子6は、発光ダイオードであって、図17、図18に例示するものは、透明結晶層62の光出射面60とは反対側の他面に、P型半導体層611及びN型半導体層613を積層した半導体積層構造61を含んでいる。P型半導体層611及びN型半導体層613の間には活性層612が設けられる。

【0096】

P型半導体層611及びN型半導体層613のうち、透明結晶層62の側に位置するN型半導体層613は、P型半導体層611と重ならない部分614を有しており、N側電極63が、その重ならない部分614の表面に設けられている。P側電極64は、重なる部分において、P型半導体層611の表面に設けられている。N側電極63は、円形状に限らず、角形状であってもよい。

【0097】

実施例において、重ならない部分614に設けられたN側電極63の平面積は、重なる部分に設けられたP側電極64の平面積よりも小さい。より詳しくは、N側電極63及びP側電極64の配置方向で見た電極幅について、N側電極63の電極幅がP側電極64の電極幅よりも小さい。このような電極配置によれば、重ならない部分614の幅を小さくし、反射的に、発光領域となる重なる部分の幅及び面積を拡大できるから、発光量を増大することができる。

【0098】

もっとも、図17、図18は、本発明において適用可能な発光素子6の一例を示すものであって、これに限定されるものではない。例えば、透明結晶層62と半導体積層構造61との上下関係が逆転した構造であってもよい。また、電極面積は電流拡散を考慮して定められる。

【0099】

発光素子6は、図14に示したように、基板1の凹部11内に配置され、P型半導体層611のP側電極64が、貫通電極2の一端に接続され、N型半導体層613のN側電極63が、貫通電極2の一端に接続されている。発光素子6は、凹部11の内部に配置されたとき、その上面が凹部11の周りの基板1の表面よりも、低くなるように配置される。そして、その段差を埋めるように、蛍光層7を充填してある。

【0100】

P側電極64及びN側電極63は、間隔を隔てて互いに対向している。P側電極64と貫通電極2との接合、及び、N側電極63と貫通電極2との接合にあたっては、両者の接合界面に接合膜を介在させる。接合膜は、Sn、In、Bi、Ga又はSbの群から選択された少なくても1種の低融点金属成分と、Cr、Ag、Cu、Au、Pt、Pd、Ni、Ni−P合金、Ni−B合金の群から選択された少なくとも1種を含む高融点金属材料からなる。低融点金属は、P側電極64及び貫通電極2、N側電極63及び貫通電極2と反応して、金属間化合物を形成して消費され、接合後は融点が大幅に上昇する。

【0101】

透明結晶層62は、代表的にはサファイアであり、その一面が光出射面60となる。透明結晶層62の一面上には、バッファ層(図示しない)があり、半導体積層構造61は、バッファ層を介して、透明結晶層62の上に成長させてある。

【0102】

半導体積層構造61は、発光素子6において周知である。PN接合を持ち、代表的にはIII−V族化合物半導体が用いられる。もっとも、公知技術に限らず、これから提案されることのある化合物半導体を含むことができる。

【0103】

本発明において、発光素子6は、赤色発光素子、緑色発光素子、青色発光素子、橙色発光素子の何れであってもよいし、白色発光素子であってもよい。それらの発光素子において、半導体積層構造61を構成する半導体材料及びその製造方法は既に知られている。

【0104】

図示の発光デバイスでは、基板1は、2つの貫通電極2、2を含み、一面に凹部11を有している。貫通電極2、2のそれぞれは、基板1を厚み方向に貫通し、一端が凹部11の内面に露出している。この基板1の凹部11内に発光素子6が配置されている。発光素子6は、実施例では、透明結晶層62の光出射面となる一面60とは反対側の他面に、P型半導体層611及びN型半導体層613を積層した構造である。そして、凹部11の内部で、P型半導体層611のP側電極64が貫通電極2の一端に接続され、N型半導体層613のN側電極63が、貫通電極2、2の他方の一端に接続されている。したがって、実施例によれば、発光素子6に対しては、透明結晶層62のある側とは反対側から、電流が注入されることになり、発光素子6のための電極が、光出射面60に現れない構造が実現されることになる。よって、発生した光を、効率よく外部に放射させ得る。

【0105】

基板1は、複数の柱状ヒートシンク3を含んでいる。柱状ヒートシンク3は、基板1の厚み方向に設けられている。したがって、発光素子6の発光動作によって生じた熱を、柱状ヒートシンク3によって、基板1の外部に放熱し、発光素子6の電極63、64と貫通電極2、2とを接続する接合部分の接合強度を保存し、電気的接続の信頼性を維持することができる。また、発熱による発光素子6の発光特性の変動を回避することができる。

【0106】

柱状ヒートシンク3は、その一端が、基板1の他面側に導出され、基板1の他面に設けられた放熱層31に接続されている。この構造によれば、放熱特性が更に向上する。

【0107】

実施例では、凹部11の内面と発光素子6の側面との間に、反射膜8が設けられている。これにより、半導体層61で生じた光を、透明結晶層62における光散乱・吸収作用を抑えながら、透明結晶層62の光出射面60に導くことができる。

【0108】

反射膜8は、凹部11の内面に付着されていてもよいし、発光素子6の側面に付着されていてもよい。図14〜図16の実施例では、発光素子6は、凹部11に対して、微小なクリアランスを有して、嵌めこまれている。この構造によれば、基板1に対する発光素子6の位置決め・配置を、容易、かつ、確実に実行することができる。

【0109】

図示はされていないが、光出射面60に、微細凹凸形状を有する透明光学部品を配置することができる。これにより、光出射面60で、光を拡散又は分散させ、均一な面発光を実現することができる。透明光学部品を設ける代わりに、光出射面60に、微細凹凸形状が形成されていてもよい。さらに、図示は省略するけれども、微細凹凸とともに、あるいは、微細凹凸を設けることなく、光出射面60に蛍光体を設けてもよい。

【0110】

さらに、図19を参照すると、図14〜図16の実施の形態との対比において、凹部11の平面積を拡大した発光デバイスが図示されている。この凹部11は、発光素子6の平面積よりもかなり大きく、発光素子6の外周と、凹部11の内周面との間に蛍光層7等が充填されている。また、凹部11の内壁面に反射膜8が付着されている。柱状ヒートシンク3は、一端(上端)が凹部11の底面位置と略同じ位置で止まっていて、他端が基板1の裏面に導かれ、放熱層31に接続されている。

【0111】

図20を参照すると、図19と略同じような構造において、凹部11の中央部分に、突出部12を設け、この突出部12に発光素子6を搭載した発光デバイスが図示されている。

図19及び図20の実施の形態も、図14〜図17を参照して説明した作用効果を奏する。

【0112】

本発明に係る発光デバイスは、単一の発光素子である発光ダイオード、複数の発光素子を、例えばマトリクス状に配置した面発光装置、照明装置、液晶ディスプレイ用バックライト、信号灯等、広範な用途を持っている。以下に、その内の例を示す。

【0113】

図21は、発光ダイオードを用いた照明装置の平面図である。図示の照明装置は、矩形状の基板1と、この基板1にマトリックス状に配列された複数の発光デバイスQR、QG、QBとを含む。

【0114】

各発光デバイスQR、QG、QBは、所定の色相の光を発する発光素子6と、発光素子6を電気的に接続するための2個の貫通電極2、2と、発光素子6の周囲に配置された複数の柱状ヒートシンク3とを有する。各発光素子6は、基板1の板面に形成された凹部11内に配置されている。基板1の形状、発光デバイスQR、QG、QBの数、及び、配置形態、並びに柱状ヒートシンク3の数、及び配置形態は、図21に示された形態に限られず、適宜に決定すべきものである。

【0115】

図22〜図24には上記の発光デバイスQR、QG、QBが詳細に示されている。基板1は、いわゆるパッケージとなるものであって、複数の貫通電極2、2と、複数の柱状ヒートシンク3とを含み、板面に凹部11を有している。基板1は、Siを主成分とするものを採用すると好適であるが、これに限られず、絶縁樹脂基板、又は絶縁性セラミック基板を採用してもよい。更には、金属基板等の導電性基板であってもよい。本実施形態では、基板1がSi基板で構成されている場合を例にとって説明する。

【0116】

基板1の凹部11の形状は、図21に示されるような直方体形状に限られることはなく、他の形状であってもよい。この凹部11は、基板1を平面視したときに、貫通電極2、2を、間隔をおいて囲むように形成されていて、その内側面のほぼ全周に、反射膜8がスパッタ等によって形成されている。反射膜8は、上述した形態に限定されず、例えば発光素子6の側面に付着されてもよく、また、反射膜8の下側に酸化膜等の絶縁膜を設けてもよい。

【0117】

発光素子6は、凹部11に、微小なクリアランスをもって嵌めこまれている。この構造によれば、基板1に対する発光素子6の位置決め・配置を、容易、かつ、確実に実行することができる。また、発光素子6は、凹部11内において、上面を蛍光層7により覆われている。これにより、発光素子6の発する光の輝度を向上することができる。蛍光層7に用いられる蛍光物質としては、例えばリン酸カルシウムがある。また、蛍光層7の色相は、用途に応じて適宜に決定すべきものである。

【0118】

貫通電極2、2のそれぞれは、凹部11の底面内において、基板1を厚み方向に貫通し、一端が凹部11の内面に露出し、他端が基板1の他面に露出する。貫通電極2、2の端面形状を、接続される発光素子6の電極形状と対応させてもよく、この場合、貫通電極2、2の端面形状は、それぞれ円形状と四角形状になる。

【0119】

本実施形態における基板1は、導電性を有するSi基板でなるので、貫通電極2、2は基板1から電気絶縁されている。電気絶縁の手段として、貫通電極2、2の外周面と、貫通電極2、2が配置されたビアの内周面との間に、電気絶縁層9が設けられている。電気絶縁層9は、Si基板でなる基板1のビア内壁面を酸化または窒化して得られた酸化膜または窒化膜であってもよいし、ビア内に充填された有機絶縁物またはガラス等の無機絶縁物から構成された層であってもよい。

【0120】

柱状ヒートシンク3は、基板1の厚み方向に貫通し、互いに微小間隔を隔てて、マトリクス状に多数配置され、基板1の裏面(他面)に設けられた放熱層31に接続されている。これにより、柱状ヒートシンク3は、基板1から効果的に熱を逃がすことができる。

【0121】

放熱層31は、例えばアルミニウムなどの比較的に熱伝導率の高い物質からなり、基板1の裏面に、複数個に分けて設けてもよいし、あるいは、全てのヒートシンク3に対して共通に接続される単一の部材として設けてもよい。また、放熱層31の形態は、図示の膜状に限らず、拡大された放熱面積を有する3次元的構造であってもよい。

【0122】

図24には、発光デバイスQR、QG、QBの他の形態が示されている。本形態の発光デバイスと、先に述べた実施形態の相違点は、基板1が3つの層101〜103から構成されている点、及び、凹部11の平面積が拡張されている点である。

【0123】

本実施形態において、基板1は、SOI基板であり、第1基板層を構成する第1シリコン層101、絶縁層を構成する酸化層102、及び、第2基板層を構成する第2シリコン層103を、この順序で積層した構造となっている。

【0124】

凹部11は、第2シリコン層103の表面を切り抜いて形成されており、その内側面は、開口端に向かうに従って開口面積の拡大する傾斜面となっている。この凹部11は、発光素子6の平面積よりかなり大きい平面積を有しており、発光素子6の外周と、凹部11の内周面との間に蛍光層7が充填されている。また、凹部11の内壁面には、先の実施形態と同様に、反射膜8が付着されている。

【0125】

貫通電極2、2は、電気絶縁層9によって電気絶縁された状態で、第1シリコン層101を貫通しており、その凹部11側の端部は、酸化層102を貫通する接続部41、42とそれぞれ接続されている。接続部41、42は、発光素子6の両端子601、602と接続される。接続部41、42の形状は、円柱状に限られず、四角柱などの他の形状も採り得る。

【0126】

柱状ヒートシンク3は、貫通電極2、2と同様に、基板1の厚み方向において、第1シリコン層101を貫通するように設けられて、放熱層31に接続されている。すなわち、柱状ヒートシンク3は、基板1の裏面から第1シリコン層101と酸化層102との境界まで延在するように設けられている。この構成によると、柱状ヒートシンク3の形成にあたって、酸化層102をエッチング阻止層として機能させることができる。このため、柱状ヒートシンク3の深さ寸法が、第1シリコン層101の層厚により画定されるので、エッチングの工程管理が極めて容易になるという利点が得られる。

【0127】

上述した照明装置は、基板1を含んでおり、この基板1は、複数の柱状ヒートシンク3を含んでいる。柱状ヒートシンク3は、基板1の厚み方向に設けられているため、発光素子6の発光動作によって生じた熱を、柱状ヒートシンク3によって、基板1の外部に放熱し、発光素子6の端子601、602と貫通電極2、2とを接続する接合部分の接合強度を保存し、電気的接続の信頼性を維持することができ、また、発熱による発光素子6の発光特性の変動を回避することもできる。

【0128】

柱状ヒートシンク3は、その一端が基板1の他面側に導出され、基板1の他面に設けられた放熱層31に接続されているため、基板1の放熱特性は更に向上し得る。

【0129】

発光素子6は、図17及び図18に示したものである。したがって、発光素子6は、積層方向における透明結晶層32の反対側から電流が注入され、発光素子6の端子601、602が光出射面に現れない構造を有するから、出射した光を効率よく外部に放射させ得る。さらに、半導体層31で生じた光は、反射膜8によって透明結晶層62における光散乱・吸収作用が抑制され、透明結晶層32の光出射面に効果的に導かれる。

【0130】

次に、本発明に係る液晶ディスプレイを、図26を参照して説明する。液晶ディスプレイは、液晶パネル120と、バックライト130とを含む。この液晶ディスプレイは、概念上、一般的なコンピュータ用の表示装置や汎用電化製品の液晶表示部に限られず、液晶テレビ、あるいは携帯電話機、携帯ゲーム機、携帯情報端末といった携帯型電子機器にも適用され得る。

【0131】

液晶パネル120は、偏向フィルタ、ガラス基板、及び液晶層などから構成された液晶モジュールであって、画像信号に基づき、駆動回路(図示せず)からの電気信号によって駆動される。バックライト130は、図21〜図25に示された照明装置であり、複数の発光デバイスQR、QG、QBにより液晶パネル120をその背面側から照明する。もっとも、バックライト130の形態は、これに限定されず、例えば図14〜図20に示された照明装置でもよく、本発明に係る照明装置の何れの形態も取り得ることは言うまでもない。

【0132】

バックライト130において、貫通電極2、2はバンプ電極や配線基板を介して電源部と接続され、これにより電力を供給された発光素子6が液晶パネル120に対して光を照射する。また、柱状ヒートシンク3は、放熱層31と接続されて、基板1内部の熱を液晶ディスプレイの背面側へと排出する。

【0133】

本発明に係る液晶ディスプレイは、上述した照明装置を含むから、既に述べた作用効果を奏する。

【0134】

次に、本発明に係る発光ダイオードディスプレイを、図27及び図28を参照して説明する。発光ダイオードディスプレイは、発光素子自体を画素として用いることから、バックライトを必要とせず、消費電力を低減し得るという利点を有する。

【0135】

図27には、発光ダイオードディスプレイの画素Qが平面視で示されており、一方、図11には、この画素Qを基板1にマトリックス状に配置した発光ダイオードディスプレイが示されている。

【0136】

1個の画素Qは、3個の発光デバイスQR、QG、QBを有しており、これらの発光デバイスQR、QG、QBは、赤色光を発する発光素子6R、緑色光を発する発光素子6G、及び青色光を発する発光素子6Bをそれぞれ有している。本実施形態の発光ダイオードディスプレイは、フルカラー表示を前提としているため、このように3色の発光素子6R、6G、6Bを有するが、これに限定されるものではない。例えば、1色のみの表示を前提とする場合、画素Qは、3色の発光素子6R、6G、6Bのいずれか1個で構成すればよい。すなわち、画素Qは、表示機能に応じた発光素子を有する発光デバイスQR、QG、QBを、適宜に選択して構成される。

【0137】

また、本実施形態の画素Qは、図示されるように、3個の発光デバイスQR、QG、QBが三角形の各頂点の位置に配置されているが、これに限定されず、3色の発光素子6R、6G、6Bの特性に応じて適宜な配置態様を採り得る。

【0138】

本発明に係る発光ダイオードディスプレイは、各発光素子6R、6G、6Bの貫通電極2、2が薄膜トランジスタ(TFT)などと接続され、これにより、各画素Qは、画像信号に基づき、駆動回路によって発光制御される。また、柱状ヒートシンク3は、図22〜図27に示された構成と同様に、放熱層31と接続されて、基板1内部の熱をディスプレイの背面側へと放出する。

【0139】

本発明に係る発光ダイオードディスプレイは、上述した照明装置と同じ構成を含むから、既に述べた作用効果を奏する。

【0140】

また、本発明に係る信号灯は、例えば鉄道信号機や交通信号機に適用されるものであり、上述した発光ダイオードディスプレイのように、複数の発光デバイスQR、QG、QB0が配列されて構成され、例えば複数色の発光素子6R、6G、6Bを備える。

【0141】

本発明に係る信号灯は、上述した照明装置と同様の構成を含むから、既に述べた作用効果を奏する。

【0142】

図29に図示された基板1は、貫通電極2と、柱状ヒートシンク3と、凹部11とを含む。実施例に示す基板1はSOI基板であり、第1基板層を構成する第1シリコン層101、絶縁層を構成する酸化層102、及び、第2基板層を構成する第2シリコン層103を、この順序で積層した構造となっている。

【0143】

SOI基板としては、その製造法により、SIMOX(Separation by IMplantation of OXygen)方式のものと、張り合わせ方式の2種類のものが知られている。何れの方式のSOI基板を用いてもよい。 SIMOX方式のSOI基板として、酸素分子をイオン注入によりシリコン結晶表面から埋め込み、それを高熱で酸化させることにより、シリコン結晶中に酸化シリコンの絶縁層を形成する手法が知られている。このような絶縁層は、埋め込み酸化(BOX;Buried Oxide)層と称される。

【0144】

凹部11は、電子素子を取り付ける部分であって、第2シリコン層103の表面の面内に設けられている。図示の凹部11は、第2シリコン層103の中央部を切り抜いて4角形状に形成されていて、その内側面は、開口端に向かうに従って開口面積の拡大する傾斜面となっている。第2シリコン層103及び凹部11の内面は、絶縁膜132によって覆われている。この絶縁膜132は、シリコン酸化膜またはシリコン窒化膜で構成することができる。

【0145】

貫通電極2は、第1シリコン層101及び酸化層102を貫通し、端部が凹部11の底面から若干突出して露出している。貫通電極2は、具体的には、外部との接続部となる端子部(バンプ)21、第1シリコン層101を貫通する貫通部22、及び、電子素子の端子電極と接続される素子接続部23を含んでいる。端子部21は、貫通部22の一端面に付着されており、例えば、Ti―Au等の無電解メッキ膜でなる。

【0146】

基板1として、SOI基板を用いた実施例では、第1シリコン層101と貫通電極2との間、及び、第1シリコン層101の表面に、絶縁膜111を設けることになる。この絶縁膜111は、シリコン酸化膜またはシリコン窒化膜で構成することができる。

【0147】

素子接続部23は、一端が貫通部22の端部に付着され、他端が、絶縁膜111、酸化層102、及び、凹部11の底面に付着されている絶縁膜132を貫通して、凹部11の内部に突出して露出している。素子接続部23も、端子部21と同様に、Ti―Au等の無電解メッキ膜でなる。

【0148】

次に、柱状ヒートシンク3のそれぞれは、第1シリコン層101の厚み方向に設けたビア113の内部に充填されている。柱状ヒートシンク3は、その主要部をなす柱状部301と、その端面に付着された端子部302とからなる。端子部302は、端子部21と同様に、Ti―Au等の無電解メッキ膜でなる。柱状部301のあるビア113は、第1シリコン層101を貫通して、第1シリコン層101と酸化層102との境界で止まるように設けられ、基板1を平面視して、所定の面積占有率をもって、凹部11の周りに分布している。

【0149】

柱状ヒートシンク3と第1シリコン層101との間には、シリコン酸化膜またはシリコン窒化膜でなる絶縁膜111が設けられている。

【0150】

図30を参照すると、図29に示した基板1を用いた発光デバイスが図示されている。この発光デバイスでは、回路基板の凹部11に、電子素子たる発光素子(LED)6が取り付けられている。発光素子6の電極は、貫通電極2を構成する素子接続部23に接合5されている。図示はしないけれども、凹部11内の絶縁膜132に光反射膜を設けることが好ましい。

【0151】

ここで、基板1は、凹部11と、貫通電極2とを含んでおり、凹部11は、第2シリコン層103の表面の面内に設けられ、貫通電極2は、第1シリコン層101及び酸化層102を貫通し、端部が凹部11の底面に露出している。したがって、回路基板の凹部11内に電子素子たる発光素子6を配置し、凹部11の内部で、発光素子6の一面に設けられた電極を、貫通電極2の一端を構成する素子接続部23に接合5することができる。これによって、発光素子6は、フリップ・チップ・ボンディング方式によって、貫通電極2に接続されることになる。

【0152】

また、本発明に係る回路基板は、柱状ヒートシンク3を含んでおり、柱状ヒートシンク3は、ビア113内に充填されている。このビア113は、第1シリコン層101を貫通している。したがって、発光素子6の動作によって生じた熱を、柱状ヒートシンク3によって、基板1の外部に放熱し、発光素子6と貫通電極2とを接合5する部分の接合強度を保存し、電気的接続の信頼性を維持することができる。更に、発熱による発光素子6の電気的特性の変動を回避することができる。

【0153】

ビア113は、第1シリコン層101を貫通して、第1シリコン層101と酸化層102との境界で止まるように設けられている。このような構成であれば、ビア113を形成する場合に、酸化層102を、エッチング阻止層として機能させることができる。このため、ビア113の深さが、第1シリコン層101から酸化層102までの深さ、即ち、第1シリコン層101の層厚によって定まる画一的な値になるので、ビア113の深さの工程管理が極めて容易になる。

【0154】

ビア113は、基板1を平面視して、所定の面積占有率をもって凹部11の周りに分布している。したがって、凹部11の内部に収納された電子素子、即ち、発光素子6を、その全周から、柱状ヒートシンク3によって取り囲む放熱領域が形成されることになるから、発光素子6に発生した熱を集熱し、効率よく放熱することができる。

【0155】

また、柱状ヒートシンク3を構成する材料の熱抵抗、及び、柱状ヒートシンク3の占有率を適切に選ぶことにより、発光素子6の動作によって生じた熱を、柱状ヒートシンク3によって、基板1の外部に効率よく放熱しえる。

【0156】

実施例2:電子デバイス又は電子機器

電子素子としては、上述した発光素子6に限らず、能動素子、受動部品またはそれらを組み合わせた複合素子を含むことができる。更には、TSV技術を適用して、上述した各種素子自体を3次元積層構造としたもの、又は、インターポーザと各種素子と組み合わせて3次元積層構造としたものも含まれる。

【0157】

図31を参照すると、そのような電子素子を搭載するのに適した回路基板が図示されている。図において、先に示した図面に現れた構成部分と同一または類似の構成部分には、同一の参照符号を付してある。図31において、貫通電極2は、凹部11の内部に搭載される電子素子の有する端子電極に合わせて、その個数を増加させてある。また、凹部11は、内側面が略垂直に立ち上がる面となっている。

【0158】

図32は、図31に示した回路基板に電子素子6を組み込んだ電子デバイスの例を示している。電子素子6は、TSV技術を適用した3次元積層構造であって、例えば、LSI等の論理素子6Aと、DRAM等のメモリ素子6Cとを、インターポーザ6Bを介して積層し、接合した構造となっている。このような電子デバイスは、情報処理システムの基本要素として用いられる。より具体的には、例えば、モバイル、携帯電話機、デジタル家電、サーバ等における画像処理システムの構成要素として用いることができる。その他にも、イメージ・センサ・モジュールとしての適用例も考えられる。

【0159】

論理素子6Aは、所謂ロジックICであって、一面に設けた電極を、基板1に設けられた貫通電極2の素子接続部23に接合してある。論理素子6Aは、チップ状であって、その内部にLSIなどの半導体論理回路を有している。論理素子6Aは、内蔵された半導体論理回路を、TSV技術の適用によって、電極に導く3次元積層構造を採用することができる。

【0160】

インターポーザ6Bは、複数の貫通電極を有しており、貫通電極の一端を、論理素子6Aの電極に接続し、貫通電極2他端をメモリ素子6Cの電極に接続してある。インターポーザ6Bは、Si基板、樹脂基板又はセラミック基板に、回路基板の貫通電極と同様の組成、製造方法を適用し、貫通電極を形成することによって得られる。

【0161】

メモリ素子6Cは、内蔵されたメモリセルが電極に接続されている。メモリ素子6Cにおいても、論理素子6Aと同様に、TSV技術の適用によって、メモリセルを電極に導く3次元配置を採用することができる。

【0162】

もっとも、電子素子6を構成する素子6A〜6Cの積層数、種類、その電極配置等は、適用される電子素子6によって、さまざまに変化するもので、図32は、3次元積層構造の一例を概念的に示すものに過ぎない。

【0163】

図32に示す電子デバイスの場合も、基本的には、図30に示した電子デバイスと同様の作用効果を奏する。ただ、図32の電子デバイスでは、3次元積層構造を採ることにより、高密度化、高性能化、高速化、小型化、薄型化、軽量化が図られているから、動作によって発生する熱を、いかにして放熱するかが、更に重要な課題となる。

【0164】

図32に示す実施例では、基板1の厚み方向に柱状ヒートシンク3が設けられている基板1を用い、この基板に設けられた凹部11の内部に電子素子6を配置してある。したがって、電子素子6の動作によって生じた熱を、柱状ヒートシンク3によって、基板1の外部に放熱し、蓄熱による異常発熱を回避し、基板1の貫通電極2と論理素子6Aの電極との接合強度、論理素子6Aの電極とインターポーザ6Bの貫通電極との接合強度、及び、インターポーザ6Bの貫通電極とメモリ素子6Cの電極との接合強度を保存し、電気的接続の信頼性を維持することができる。また、発熱による論理素子6A及びメモリ素子6Cの電気的特性の変動を回避することができる。

【0165】

基板1は、一面に凹部11を有しており、その内部に3次元積層構造を有する電子素子6が収納されている。柱状ヒートシンク3のそれぞれは、凹部11の周囲において、凹部11を取り囲むように配置され、基板1の厚み方向に貫通し、互いに微小間隔を隔てて多数配置されている。したがって、平面視して、凹部11の内部に収納された電子素子6を、その全周から、柱状ヒートシンク3によって取り囲む放熱路が形成されることになるから、電子素子6に発生した熱を集熱し、効率よく放熱することができる。

【0166】

図33には、更に別の電子デバイスが図示されている。図において、先に示した図面に現れた構成部分と対応する部分については、同一の参照符号を付し、重複説明は省略することがある。図示の電子デバイスにおいて、貫通電極2は、複数設けられ、それぞれは、凹部11を形成した領域内において、基板1を厚み方向に貫通し、一端が凹部11の内面に露出し、他端が基板1の他面に露出する。

【0167】

柱状ヒートシンク3は、凹部11の周囲において、その両端が基板1の厚み方向に貫通し、互いに微小間隔を隔てて、マトリクス状に多数配置されている。柱状ヒートシンク3は、その一端(下端)が基板1の裏面(他面)に設けられた放熱層31によって共通に接続され、他端(上端)が、基板1の表面に導出されている。放熱層31の形態は、図示の膜状に限らず、拡大された放熱面積を有する3次元的構造であってもよい。

【0168】

電子素子6は、例えば、半導体チップ等の能動素子、又は、コンデンサ、インダクタ等の受動部品もしくはそれらの複合素子である。電子素子6は、半導体素子と受動部品とを併せ持つものであってもよいし、メモリ素子、論理回路素子またはアナログ回路素子であってもよい。これらの素子の単層であってもよいし、積層されたものであってもよい。

【0169】

図に示す電子素子6は、取り付け面となる一面に、複数の電極601を有するフリップ・チップの形態を有し、基板1の凹部11内に配置され、電極601のそれぞれが、貫通電極2の一端に接合されている。

【0170】

図示の電子デバイスは、基板1を含んでおり、この基板1は、複数の柱状ヒートシンク3を含んでいる。柱状ヒートシンク3は、基板1の厚み方向に設けられている。したがって、電子素子6の動作によって生じた熱を、柱状ヒートシンク3によって、基板1の外部に放熱し、電子素子6の電極601と貫通電極2とを接続する接合部分の接合強度を保存し、電気的接続の信頼性を維持することができる。また、発熱による電子素子6の電気的特性の変動を回避することができる。

【0171】

基板1は、一面に凹部11を有しており、その内部に電子素子6が収納されている。柱状ヒートシンク3のそれぞれは、凹部11の周囲において、凹部11を取り囲むように配置され、基板1の厚み方向に貫通し、互いに微小間隔を隔てて多数配置されている。したがって、凹部11の内部に収納された電子素子6を、その全周から、柱状ヒートシンク3によって立体的に取り囲む放熱路が形成されることになるから、電子素子6に発生した熱を、3次元的に集熱し、効率よく放熱することができる。

【0172】

柱状ヒートシンク3は、基板1の厚み方向に貫通し、その一端が、基板1の他面側に導出され、基板1の他面に設けられた放熱層31に接続されている。この構造によれば、放熱特性が更に向上する。

【0173】

図33の実施例では、電子素子6は、凹部11に対して、微小なクリアランスを有して、嵌めこまれている。この構造によれば、基板1に対する電子素子6の位置決め・配置を、容易、かつ、確実に実行することができる。

【0174】

次に、図34を参照して説明する。図において、先に示した図面に現れた構成部分と対応する部分については、同一の参照符号を付し、重複説明は省略することがある。図において、電子素子6は、TSV技術を適用した3次元積層構造であって、例えば、LSI等の論理素子6Aと、DRAM等のメモリ素子6Cとを、インターポーザ6Bを介して積層し、接合した構造となっている。即ち、図32に示したものと類似の構成を持つ。

【0175】

インターポーザ6Bは、間隔をおいて配置された複数の貫通電極2Bを有しており、貫通電極2Bの一端を、論理素子6Aのもう一つの電極612に接続し、貫通電極2Bの他端をメモリ素子6Cの電極631に接続してある。インターポーザ6Bは、Si基板、樹脂基板又はセラミック基板に、貫通電極2と同様の組成、製造方法を適用し、貫通電極2Bを形成することによって得られる。

【0176】

基板1は、一面に凹部11を有しており、その内部に3次元積層構造を有する電子素子6が収納されている。柱状ヒートシンク3のそれぞれは、凹部11の周囲において、凹部11を取り囲むように配置され、基板1の厚み方向に貫通し、互いに微小間隔を隔てて多数配置されている。したがって、凹部11の内部に収納された電子素子6を、その全周から、柱状ヒートシンク3によって立体的に取り囲む放熱路が形成されることになるから、電子素子6に発生した熱を、3次元的に集熱し、効率よく放熱することができる。

【0177】

柱状ヒートシンク3は、基板1の厚み方向に貫通し、その一端が、基板1の他面側に導出され、基板1の他面に設けられた放熱層31に接続されている。この構造によれば、放熱特性が更に向上する。

【0178】

実施例3:積層電子デバイス

次に、図35に図示された電子デバイス1は、積層された複数枚の基板101〜103を含む。図中の最下層にある第1の基板101は、Si基板、セラミック基板、あるいはガラエポ(ガラス・エポキシ)基板などであり、他の基板102、103を支持するものである。また、第2の基板102は、第1の基板101と第3の基板103の間に位置するインターポーザであって、例えば、デカップリング・コンデンサ等のコンデンサ素子230を含んでいる。第3の基板103は、ICチップであって、演算素子などの集積回路233を含んでいる。第2及び第3の基板102、13は、Si基板によって構成することができる。なお、図35は、一部の積層構造を拡大して示したものであるため、一部のICチップのみが示されている。

【0179】

第1〜第3の基板101〜103は、それぞれ、板面を重ね合わせて積層され、1以上の貫通電極2を含んでいる。貫通電極2は、第1〜第3の基板101〜103にわたって延在する連続導体である。具体的には、貫通電極2は、積層方向において第1〜第3の基板101〜103に埋設された状態で、それらを連続して貫通するように設けられている。

【0180】

本実施形態では、貫通電極2の全てが、第1〜第3の基板101〜103を連続して貫通しているが、そのいくつかは、一部の基板のみを貫通するものであってもよい。例えば、第1の基板101と第2の基板102を貫通するが、第3の基板103を貫通しないような形態の貫通電極を含んでいてもよい。

【0181】

貫通電極2は、コンデンサ素子230、及び集積回路233の各々と電気的に接続されている。コンデンサ素子230は、誘電体層234と、上部電極層232と、下部電極層236とを含んでいる。上部電極層232、及び下部電極層236は、誘電体層234を挟む込み、図中の左右にある貫通電極2までそれぞれ延在して、これと電気的に接続されている。同様に、集積回路233も、左右にある貫通電極2までそれぞれ延在する電極231、235が設けられており、貫通電極2と電気的に接続されている。このような接続形態は、例えば、コンデンサ素子230を、集積回路233の電源ノイズ除去用のデカップリングコンデンサとして用いる場合に採用され得る。

【0182】

本発明に係る電子デバイスは、このように、各基板101〜103の板面同士が重ね合わせられ、2枚以上の基板101〜103にわたって延在する連続導体である貫通電極2を備えている。即ち、本発明に係る電子デバイスは、複数枚の基板101〜103が、バンプを用いることなく、積層された構造を有している。よって、本発明によれば、バンプ接合構造を採る場合に生じていた位置合わせの困難性、接合強度の担保、及び耐熱性の担保といった問題を全て解決した高品質、高信頼度の電子デバイスを実現することができる。

【0183】

図36には、別の形態が図示されている。図36に図示された実施形態では、貫通電極2に代えて、又は、貫通電極2とともに、柱状ヒートシンク3が設けられている。柱状ヒートシンク3は、集積回路233の周辺に配置されている。したがって、第3の基板103を平面視した場合、集積回路233を、その全周から、柱状ヒートシンク3によって取り囲む放熱路が形成されることになるから、集積回路233に発生した熱を集熱し、効率よく放熱することができる。集積回路233が、発熱量の多いCPUなどに使用される演算素子であった場合、柱状ヒートシンク3を備えることは、その動作の安定性確保等の観点から、格別の効果がある。

【0184】

柱状ヒートシンク3は、所定の占有率をもって分布している。したがって、柱状ヒートシンク3を構成する材料の熱抵抗を考慮したうえで、柱状ヒートシンク3の占有率を適切に選ぶことにより、集積回路233の動作によって生じた熱を、柱状ヒートシンク3によって、電子デバイス1の外部に効率よく放熱し、異常発熱を回避することができる。

【0185】

柱状ヒートシンク3も、複数枚の基板101〜103のうち、2枚以上の基板にわたって延在する連続体であるので、柱状ヒートシンク3についてバンプ接合構造を採る場合に不可避な位置合わせの困難性、接合強度の担保、及び耐熱性の担保といった問題を、全て解決し得る。

【0186】

実施例 4:その他

図37を参照すると、多数の柱状ヒートシンク3を有する基板が図示されている。この基板1では、柱状ヒートシンク3の先端を、耐熱性絶縁有機基板又は無機基板1の内部に留め、その上方に、厚みΔH1の絶縁層を残してある。即ち、柱状ヒートシンク3は、貫通させる必要はない。厚みΔH1の寸法は任意である。

【0187】

次に、図38を参照すると、有機絶縁基板によって構成した基板1が図示されている。有機基板1としては、耐熱性材料で構成されたものが適している。特に、300℃以上の耐熱性を有するものが適している。有機基板1は、少なくとも一面に、Cu箔等でなる金属層31、32を有している。図示の有機基板1は、その両面にCu箔でなる金属層31、32を有する両面銅張基板である。このような両面銅張基板は、例えば、高耐熱ガラスエポキシ銅張基板、高耐熱低熱膨張ガラス布基材エポキシ樹脂銅張基板、高熱伝導性ガラスコンポジット基板、高耐熱性 紙フェノール銅張基板、紙基材フェノール樹脂銅張基板等の名称で、各基板メーカから、さまざまなタイプのものが供給され、市販されている。

【0188】

有機基板1を用いることの利点は、既に、回路基板して実用化され、市販されているものを利用できること、基板材料費が安価になること及び柱状ヒートシンク3のための穿ビア工程が短時間で済むこと等である。

【0189】

しかも、少なくとも一面に金属層31、32を有するので、柱状ヒートシンク形成工程に熱処理工程が含まれる一般的な工程において、金属層31又は32のある側から溶融金属を供給することにより、有機基板1の表面が、溶融金属に直接接触するのを回避し、その熱的ダメージを回避することができる。

【0190】

また、金属層31、32は、柱状ヒートシンク3に対して直交する面に設けられることになるから、柱状ヒートシンク3による厚み方向への放熱経路と、この放熱経路に直交する金属層31、32による放熱拡散面が生じる。即ち、三次元的な放熱経路が形成されるから、放熱特性が向上する。

【0191】

更に、図35を参照すると、少なくとも一面に金属層31、32を有する複数枚の有機基板101を、積層面に金属層31、32が位置するようにして積層した構造を持つ放熱用基板が図示されている。積層される有機基板1の枚数は任意である。隣接する有機基板1は、耐熱性・熱伝導性に優れた接合材によって接合されていることが好ましい。

【0192】

この構造によれば、積層された有機基板101の中間部に放熱路となる金属層31、32が介在することになるから、柱状ヒートシンク3による放熱とともに、柱状ヒートシンク3から伝達される熱を、基板1の中間部で面方向に拡散する三次元的な放熱構造となる。このため、基板1の内部に熱が籠るのを回避し、基板1に搭載される電子部品の温度上昇を抑制することができる。柱状ヒートシンク3は、金属層31、32に連なり、直接的な熱結合関係にあることが好ましい。

【0193】

図37〜図39に図示された基板は、放熱基板として有用なものであって、図37〜図39に示した形態の他にも、様々な形態を採ることができる。その一例を、図40〜図42に示してある。図において、図37〜図39に現れた構成部分と対応する部分については、同一の参照符号を付し、重複説明は省略する。まず、図40は、互いに積層された2枚の有機基板1において、柱状ヒートシンク3の配置ピッチを異ならせた形態を示している。

【0194】

次に、図41は、互いに積層された2枚の有機基板1の一方にのみ、柱状ヒートシンク3を設け、他方は、柱状ヒートシンクを持たない耐熱性絶縁基板とした例を示している。

【0195】

図42では、両面に金属層31、32を有するとともに、柱状ヒートシンク3を有する複数枚の有機基板1を積層し、更に、その上に、柱状ヒートシンク3を持たない有機基板1を積層した放熱用基板を示している。

【0196】

本発明に係る放熱用基板は、専ら、放熱手段として用いてもよいし、マザーボード又はサブマウント・ボード等の回路基板として用いることもできる。図43及び図44を参照すると、両面に金属層31、32を有する任意複数枚(図では2枚)の有機基板1を積層し、かつ、接合した有機基板1に、電子部品を搭載する領域A1、A2を画定するとともに、その領域A1、A2内に露出する貫通電極2を、2枚の有機基板1を貫通するように設けてある。貫通電極2の少なくとも一端には、バンプが設けられる。領域A1、A2及び貫通電極2は、搭載すべき電子部品の種類に応じて設計される。

【0197】

図45及び図46には、更に別の形態が示されている。まず、図45を参照すると、基板1は、導電性基板によって構成されており、柱状ヒートシンク3は、ビア30の内壁面及び導電性基板の一面(下面)に形成された有機又は無機の絶縁膜35によって、導電性基板1から電気絶縁されている。導電性基板1は、金属板であってもよいし、Si基板であってもよい。

【0198】

次に、図46を参照すると、柱状ヒートシンク3の他に、貫通電極2が配置されている。貫通電極2は、絶縁膜35によって導電性基板1から電気絶縁されている。

【0199】

本発明の適用される電子機器には、電子工学技術を応用した電気製品のほとんど全てが含まれること、その具体例としては、車載電子機器が含まれることは先に述べたとおりである。車載電子機器としては、HV車、又は、EV車に搭載されるモータ駆動用インバータ、LEDランプ制御用大規模集積回路装置(LSI)等を例示することができる。次に、その具体例を説明する。

【0200】

図47は、モータ駆動用インバータを含むモータ駆動装置の回路図である。図47を参照すると、モータ駆動装置は、直流電源装置710と、インバータ730と、制御装置750とを備え、三相交流回転電機でなるモータ(またはジェネレータ)770を駆動する構成となっている。直流電源装置710は、たとえばニッケル水素電池やリチウムイオン電池などの2次電池、キャパシタ、コンデンサあるいは燃料電池などで構成される。

【0201】

インバータ730は、U相アーム73Uと、V相アーム73Vと、W相アーム73Wとからなる。U相アーム73Uは、直列接続されたスイッチング素子Q1、Q2からなり、V相アーム73Vは、直列接続されたスイッチング素子Q3、Q4からなり、W相アーム73Wは、直列接続されたスイッチング素子Q5、Q6からなる。また、各スイッチング素子Q1〜Q6のコレクタ−エミッタ間には、エミッタ側からコレクタ側へ電流を流すダイオードD1〜D6がそれぞれ接続されている。

【0202】

各相アームの中間点は、モータ770の各相コイルU、V、Wの相端に接続されている。すなわち、モータ770は、U、V、W相の3つのコイルの一端が中性点に共通接続されて構成され、U相コイルの他端がスイッチング素子Q1、Q2の中間点に、V相コイルの他端がスイッチング素子Q3、Q4の中間点に、W相コイルの他端がスイッチング素子Q5、Q6の中間点にそれぞれ接続されている。

【0203】

インバータ730は、直流電源装置710から供給される直流電圧を、制御装置750からの信号S1に基づいて、交流電圧に変換し、この交流電圧によってモータ770を駆動する。これにより、モータ770は、トルク指令値に従ったトルクを発生するように駆動される。

【0204】

図48は、図47に示したモータ駆動装置のインバータを構成するスイッチング素子の実装状態を示す図である。インバータ730は、本発明に係る放熱用基板1の一面上に実装されている。インバータ730のU相アーム73Uは、スイッチング素子Q1、Q2と、P電極層63と、中間電極層62と、N電極層61とを含む。V相アーム73V、W相アーム73Wも同様の構成であるので、以下、U相アーム73Uを中心に説明する。

【0205】

U相アーム73Uは、スイッチング素子Q1、Q2と、P電極層63と、中間電極層62と、N電極層61とを含み、本発明に係る放熱用基板50の一面上に搭載されている。

【0206】

P電極層63、中間電極層62およびN電極層61は、共に、放熱用基板1上にパターンとして形成される。P電極層63は、一方端が電源ラインLN1を構成するバスバーに結合される。N電極層61は、一方端がアースラインLN2を構成するバスバーに結合される。中間電極層62は、図47のU相アーム73Uの中間点に相当する。図示はされていないが、バスバーも、放熱用基板る放熱用基板1の一面上に配置される。

【0207】

スイッチング素子Q1は、コレクタが中間電極層62に導通するように中間電極層62に固着される。スイッチング素子Q1のエミッタは、ワイヤWL1によりP電極層63に接続される。

【0208】

スイッチング素子Q2は、コレクタがN電極層61に導通するようにN電極層61に固着される。スイッチング素子Q2のエミッタは、ワイヤWL1により中間電極層62に接続される。

【0209】

放熱用基板1は、スイッチング素子Q1、Q2、P電極層63、中間電極層62、及び、N電極層61を搭載する一面側(上面側)に、絶縁層を有するタイプのものが用いられ、下面側の金属層31が、シリコングリス62を介して放熱ブロック50上に配置される。

【0210】

放熱ブロック50は、複数の溝501を有する。インバータ730の冷却系として水冷系を採用した場合、外部に配されたラジエータ(図示せず)から供給された冷却水は、放熱ブロック50の複数の溝501を紙面に垂直な方向に流れることによって、放熱用基板1を介してスイッチング素子Q1、Q2を冷却する。スイッチング素子Q3〜Q6でも、同様の冷却作用が行われる。

【0211】

HV自動車やEV自動車では、インバータ730を用い、直流電源装置710から供給された直流電圧を交流電圧に変換してモータ770を駆動するので、インバータ730を構成するスイッチング素子Q1〜Q6やバスバーに、大きな電流が流れる。したがって、このような発熱部分をいかにして冷却するかが大きな問題である。

【0212】

本発明に係る放熱用基板1は、スイッチング素子Q1、Q2、P電極層63、中間電極層62、及び、N電極層61等に対する電気絶縁とともに、柱状ヒートシンク3による放熱経路によって、インバータ730を構成するスイッチング素子Q1〜Q6やバスバーの熱を効率よく放熱ブロック50に伝達し、スイッチング素子Q1〜Q6やバスバー等の冷却に資することができる。

【0213】

次に、本発明に係る放熱用基板を、パーソナル・コンピュータ、携帯電話機又はデジタル家電等の適用した例を、図49及び図48を参照して説明する。まず、図48を参照すると、本発明に係る放熱用基板1の一面上に、電子部品6が搭載されている。

【0214】

電子部品6は、例えば、LSI等の論理素子7Aと、DRAM等のメモリ素子7Bとを、インターポーザ7Cを介して積層し、接合した構造となっている。このような電子デバイスは、情報処理システムの基本要素として用いられる。より具体的には、例えば、モバイル、携帯電話機、デジタル家電、サーバ等における画像処理システムの構成要素として用いることができる。その他にも、イメージ・センサ・モジュールとしての適用例も考えられる。

【0215】

論理素子7Aは、チップ状であって、その内部にLSIなどの半導体論理回路を有している。インターポーザ7Cは、デカップリング・コンデンサや、貫通電極を有しており、貫通電極の一端を、論理素子7Aに接続し、貫通電極の他端をメモリ素子7Bに接続してある。これによって、TSV技術を利用した3次元配置の電子部品が得られている。インターポーザ7Cは、Si基板、樹脂基板又はセラミック基板に、貫通電極を形成することによって得られる。もっとも、電子部品6を構成する素子の積層数、種類、その電極配置等は、適用される電子部品6によって、さまざまに変化するもので、図49は、3次元積層構造の一例を概念的に示すものに過ぎない。

【0216】

この構造によれば、積層された有機基板101の中間部に放熱路となる金属層31、32が介在することになるから、柱状ヒートシンク3による放熱とともに、柱状ヒートシンク3から伝達される熱を、基板1の中間部で面方向に拡散する三次元的な放熱構造となる。このため、基板1の内部に熱が籠るのを回避し、基板1に搭載される電子部品6の温度上昇を抑制することができる。

【0217】

図示はされていないが、論理素子7A、メモリ素子7B及びインターポーザ7Cにも、同様の柱状ヒートシンクを内蔵させることができ、その柱状ヒートシンクを、一連に連続させて、マザーボード1の柱状ヒートシンク3に熱結合させることにより、更に放熱効果を上げることができる。

【0218】

次に、図50を参照すると、マザーボード1Aの一面上に、電子部品6を内蔵するサブマウント・ボード1Bを搭載した例が図示されている。マザーボード1Aは、図19に示したもので、両面に金属層31A、32Aを有する2枚の有機基板1A、1Aを、積層面に金属層31A、32Aが位置するようにして積層した構造になる。

【0219】

サブマウント・ボード1Bには、柱状ヒートシンク3Bの他に、貫通電極2Bが配置されている。サブマウント・ボード1Bは、その一面側に凹部11を有しており、凹部11の周囲の肉厚部に、絶縁層35Bによって電気絶縁された柱状ヒートシンク3Bが備えられている。柱状ヒートシンク3Bは、一端が金属層31Bに連続している。貫通電極2Bは、凹部11の底部に備えられ、絶縁層35Bによって電気絶縁されている。

【0220】

電子部品6は、凹部11の内部に収納されており、論理素子7Aの下面に備えられた電極(バンプ)が貫通電極2Bの一端に接合されている。

【0221】

図50の場合、マザーボード1A及びサブマウント・ボード1Bに柱状ヒートシンク3A、3Bが設けられているから、電子部品6の動作によって生じた熱を、柱状ヒートシンク3A、3Bによって、サブマウント・ボード1Bから、マザーボード1Aに伝達し、その外部に放熱し得る。したがって、蓄熱による異常発熱を回避し、発熱による電子部品6の電気的特性の変動を回避することができる。

【0222】

サブマウント・ボード1Bは、一面に凹部11を有しており、その内部に電子部品6が収納されている。柱状ヒートシンク3Bのそれぞれは、凹部11を取り囲むように配置され、基板1の厚み方向に貫通し、互いに微小間隔を隔てて多数配置されている。したがって、凹部11の内部に収納された電子部品6を、その全周から、柱状ヒートシンク3Bによって立体的に取り囲む放熱路が形成されることになるから、電子部品6に発生した熱を、3次元的に集熱し、効率よく放熱することができる。

【0223】

以上、好ましい実施例を参照して本発明の内容を具体的に説明したが、本発明の基本的技術思想及び教示に基づいて、当業者であれば、種種の変形態様を採り得ることは自明である。

【符号の説明】

【0224】

1 基板

2 貫通電極

3 柱状ヒートシンク

【技術分野】

【0001】

本発明は、電子機器用基板及び電子機器に関する。

【背景技術】

【0002】

例えば、各種スケールの集積回路、各種半導体素子もしくはそのチップ等の電子機器においては、基板上に素子を配置し、その間をワイヤ・ボンディングなどの手段で接続する方法がとられてきた。しかし、この方法では、ワイヤ・ボンディング工程が必要な上に、実装面積が素子の数とともに増加し、配線長の増加から信号遅延が大きくなる。

【0003】

そこで、基板に貫通電極を設け、従来のワイヤ・ボンディングを、この貫通電極によって置き換えるTSV(Through−Silicon−Via)技術が提案されている。特許文献1(特開平11−298138号公報)、特許文献2(特開2000−228410号公報)、特許文献3(特開2002−158191号公報)及び特許文献4(特開2003−257891号公報)には、TSV技術に不可欠な貫通電極形成技術が開示されている。ワイヤ・ボンディングに対するTSV技術の優位性は、次のように言われている。

【0004】

まず、ワイヤ・ボンディングでは、100〜200本と接続本数が限られていたが、TSV技術を使えば、μmオーダの間隔で接続用貫通電極を配列できるため、数千本単位での接続本数が可能となる。

【0005】

また、接続距離が最短になるので、ノイズを受けにくくなること、寄生容量や抵抗が小さくて済むため遅延や減衰、波形の劣化が少なくなること、増幅や静電破壊保護のための余分な回路が不要になること、これらによって、回路の高速動作と低消費電力化が実現されることなどの利点が得られる。

【0006】

TSV技術を用いることにより、アナログやデジタルの回路、DRAMのようなメモリ回路、CPUのようなロジック回路などを含む電子デバイスは勿論のこと、アナログ高周波回路と低周波で低消費電力の回路といった異種の回路を、別々のプロセスによって作り、それらを積層した電子デバイスを得ることもできる。

【0007】

3次元集積回路(3D−IC)にTSV技術を使用すれば、大量の機能を小さな占有面積の中に詰め込めるようになる。加えて、素子同士の重要な電気経路が劇的に短く出来るために、処理の高速化が導かれる。

【0008】

TSV技術の適用に当たっては、ビア(貫通電極)を形成しなければならない。その手段として、貫通電極を、Cu電気メッキによって形成する方法が一般的である。

【0009】

しかし、電気めっきの処理時間がどうしても長くなるから、製造効率が悪くなる。しかも、ビアは、通常、アスペクト比が5以上にもなり、また、ビアの内壁面に凹凸が生じるのが普通であるため、めっき下地膜をビア内壁面の全面に均一に形成することが困難である。このため、ビアの内壁面と貫通電極となるめっき膜との間に空洞や隙間が発生してしまい、電気抵抗の増大、及び、信頼性低下等の原因となる。また、電気抵抗を、Cuの有する電気抵抗値以下にはなしえないという限界も生じる。

【0010】

更に、TSV技術の適用によって、電子機器の高密度化、高性能化、高速化、小型化、薄型化及び軽量化が進展すると、動作によって発生する熱量が増大するのに加えて、その放熱構造の構築が難しくなり、いかにして放熱するかが、大きな問題となる。放熱が不十分であると、発生した熱が蓄積され、異常発熱に至り、電子部品の接合強度が失われ、電気的接続の信頼性が損なわれたり、あるいは、電子部品の電気的特性が変動し、最悪の場合には、熱暴走、熱破壊等を招きかねない。

【0011】

このような放熱手段として、従来より種々の技術が知られている。例えば、特許文献5(特開2008−294253号公報)は、Ag粉末を含む導電性ペーストを充填して伝熱ビア導体を形成する技術を開示している。また、特許文献6(特開2005−158957号公報)は、熱伝導率の優れた金属(銅、はんだ、金)製であるか、発光素子サブマウント構造体の上面からビアを空け、ビアの側面に金メッキを施して、はんだを充填することで、サーマルビアを形成する技術を開示している。特許文献7(特開平10−098127号公報)は、銀ペースト、銅ペースト等の金属粉含有樹脂や、金属棒と金属粉含有樹脂の複合体等を用いた導熱体を開示している。更に、特許文献8(特開2007−294834号公報)は、Cu、Niなどの金属を用いたサーマルビアを開示している。しかし、何れの従来技術の場合も、放熱特性の向上や、製造コスト低減等、改善すべき問題を抱えている。

【0012】

又、貫通電極の工程時に、基板にクラックなどのダメージを与えてしまうという問題がある。原因の1つとして、柱状晶による応力が挙げられる。貫通電極中に柱状晶が形成された場合、柱状晶は、もともと大きく粒成長するものであるため、容易に亀裂の伝播経路となり得るからである。又、他の原因として、貫通電極が、製造工程における熱工程を経ている場合、金属一般が持つ正の体積変化率により、一般には、貫通電極を膨張させる方向に働き、その後、収縮するということが挙げられる。この熱膨張・収縮に伴い、基板に応力が発生し、クラックなどのダメージを与えてしまうからである。

【0013】

原因の1つである、熱工程での金属一般が持つ正の体積変化率に対して、特許文献9(特表2011−520286)では、熱導電に優れたカーボンナノチューブをTSVの材料として使用することが開示されている。

【0014】

しかし、特許文献9では、もう1つの原因である柱状晶についての記載はなく、又、基板表面に放熱層を設け、発生した熱を内層部から移動させるため、必ず放熱層を設ける必要があった。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開平11−298138号公報

【特許文献2】特開2000−228410号公報

【特許文献3】特開2002−158191号公報

【特許文献4】特開2003−257891号公報

【特許文献5】特開2008−294253号公報

【特許文献6】特開2005−158957号公報

【特許文献7】特開平10−098127号公報

【特許文献8】特開2007−294834号公報

【特許文献9】特表2011−520286

【発明の概要】

【発明が解決しようとする課題】

【0016】

本発明の課題は、電気抵抗の低い貫通電極構造を有する電子機器用基板及びそれを用いた電子機器を提供することである。

【0017】

本発明のもう一つの課題は、放熱特性に優れた熱伝導路を有する電子機器用基板及びそれを用いた電子機器を提供することである。

【0018】

本発明の更にもう一つの課題は、電気抵抗の低い貫通電極構造、及び、放熱特性に優れた熱伝導路を短時間で、効率よく形成することができる電子機器用基板及びそれを用いた電子機器を提供することである。

【0019】

本発明の更にもう一つの課題は、基板に対する応力を低減する貫通電極を提供することである。

【課題を解決するための手段】

【0020】

上述した課題を解決するため、本発明に係る電子機器用の基板は、複数の貫通電極を有しており、前記貫通電極は、カーボンナノチューブ、及び、ナノコンポジット結晶構造の金属/合金成分を含む。

【0021】

上述したように、本発明に係る基板において、貫通電極は、複数であるから、基板に搭載される電子部品や電子デバイスに対して、貫通電極を、正極及び負極として活用することができる。このため、ワイヤ・ボンディング等の電気配線が不要になり、高価なワイヤボンディング装置等に費やされていた生産設備費をカットし、製品コストを低減させることができる。

【0022】

貫通電極は、カーボンナノチューブ(Carbon nanotube)を含有する。カーボンナノチューブは、電流密度耐性が、109A/cm2で、銅の1、000倍以上の高電流密度耐性を有する。しかも、カーボンナノチューブ内では、電気良導体の銅との対比において、電子散乱が少ないため、電気抵抗が小さい。したがって、カーボンナノチューブを含有する貫通電極によれば、銅との対比において、電気抵抗が小さく、大きな電流を流しても、抵抗発熱量を低減することができる。更に、カーボンナノチューブは、その優れた弾性によって、応力低減作用を奏する。そのため、貫通電極に用いた場合、基板に亀裂・クラックが入るのを抑制することもできる。

【0023】

貫通電極は、カーボンナノチューブ自体によって構成してもよいし、カーボンナノチューブと、ナノコンポジット結晶構造の金属/合金成分を含む複合材料によって構成してもよい。カーボンナノチューブ、及び、ナノコンポジット結晶構造の金属/合金成分を含む貫通電極は、大きさが、ナノレベルに制限された組織(結晶)を含むから、その効果として、貫通電極に発生する応力が小さくなる。

【0024】

カーボンナノチューブと有機材料とを混合し、必要であれば、第3成分として、無機粉末を混合又はナノコンポジット結晶構造の金属/合金成分を添加して、ペースト化した複合材料で構成してもよい。

【0025】

更に、貫通電極は、ナノコンポジット結晶構造の金属/合金成分を含有する。ナノコンポジット結晶構造の金属/合金成分を含有する貫通電極は、応力が小さくなる。しかも、ナノコンポジット結晶構造には、柱状晶の発生を抑制し、柱状ヒートシンクの等軸晶化を促進する働きがあるため、より応力低減効果を奏することができる。

【0026】

上述したように、ナノコンポジット結晶構造には、柱状晶の発生を抑制し、等軸晶化を促進する働きはあるが、柱状晶の生成は零ではない。ナノコンポジット結晶構造とともに、カーボンナノチューブを共存させる構成によれば、ナノコンポジット結晶構造に発生することのある柱状晶による応力の増大を、カーボンナノチューブの有する弾性により、緩和することができる。よって、前記基板に加わる応力、ストレス、又は、特性・劣化を、更に確実に抑制することができる。

【0027】

上述したナノコンポジット結晶構造の有する特有の特性により、半導体基板(ウエハ)に形成された半導体回路の特性劣化が抑制される。また、半導体基板に亀裂・クラックが入るのを抑制することもできる。

【0028】

貫通電極を支持する基板は、セラミック等の無機基板、銅張り基板等に見られる有機基板又は半導体基板の少なくとも一種を含むことができる。基板を構成する無機基板、有機基板が導電性を有する場合、及び、半導体基板でなる場合は、貫通電極は、導電性の無機基板、導電性の有機基板及び半導体基板に対して、電気絶縁膜または電気絶縁層によって電気絶縁される。そのような絶縁構造は、貫通孔の鋳型となる孔の内壁面を酸化又は窒化して得られた絶縁膜、孔の内壁面に付着させた絶縁層によって実現することができる。上述した絶縁構造は、孔から微小間隔を隔ててその周りにリング状に設けてもよい。

【0029】

本発明に係る貫通電極は、基板に設けられたビアを鋳型とする鋳込み成形体であっても良い。鋳込み成形体は、ビアの側壁面に対する密着力が高く、巣、空隙、空洞のない緻密な構造を持ち、電気抵抗が小さく、電気伝導性に優れた貫通電極を有する基板が得られる。ビアの内壁面に凹凸があっても、貫通電極は、その凹凸に倣うように鋳込まれるから、ビアに対する密着強度の高い貫通電極が得られる。

【0030】

しかも、貫通電極が、ビアの内壁面の凹凸に倣うように鋳込まれる結果、貫通電極とビアの内壁面の凹凸が、貫通電極の抜けを阻止するアンカー部として働くので、基板に対する貫通電極の接合強度が高くなる。このことは、めっきによって貫通電極を形成する場合と異なって、ビアの内壁面に凹凸精度が要求されず、むしろ、若干の凹凸があった方が好ましい結果になるということを意味する。このため、ビアの形成が容易になる。

【0031】

本発明に係る基板は、上記貫通電極とは別に、または、貫通電極とともに、複数の柱状ヒートシンクを有する。前記柱状ヒートシンクは、前記基板に設けられたビアを鋳型とする鋳込み成形体でなる。

【0032】

柱状ヒートシンクも、基板に設けられたビアを鋳型とする鋳込み成形体でなるから、ビアの側壁面に対する密着力が高く、巣、空隙、空洞のない緻密な構造を持ち、熱伝導性及び放熱特性に優れた柱状ヒートシンクを有する基板が得られる。

【0033】

しかも、めっき法等、他の方法によって形成した場合と比較して、ビアの側壁面に対する密着力が高く、巣、空隙、空洞のない緻密な構造を持つ柱状ヒートシンクを、短時間で、効率よく形成することができる。

【0034】

柱状ヒートシンクは、熱伝導性の高い炭素原子構造体を含んでいる。このような炭素原子構造体には、ダイヤモンド、フラーレン又はカーボンナノチューブから選択された少なくとも一種が含まれる。

【0035】

上述した柱状ヒートシンクは、炭素原子構造体の有する高い熱伝導性により、放熱性に優れたものとなる。特に、カーボンナノチューブは、銅の約10倍の高熱伝導特性を有するから、極めて高い放熱特性を確保することができる。更に、必要であれば、第3成分として、有機成分を添加し、ペースト化した複合材料で構成してもよい。

【0036】

柱状ヒートシンクは、炭素原子構造体とともに、ナノコンポジット結晶構造の金属/合金成分を含む複合材料で構成されてもよい。

【0037】

本発明に係る基板は、上述した貫通電極及び柱状ヒートシンクを併せ持っていてもよい。具体的には、次のような構成になる。

(a)貫通電極がカーボンナノチューブを含有し、前記基板に設けられたビアを鋳型とする鋳込み成形体でなり、前記柱状ヒートシンクが前記基板に設けられたビアを鋳型とする鋳込み成形体でなる構成。

(b)上記(a)において、前記貫通電極及び前記柱状ヒートシンクの少なくとも一方が、ナノコンポジット結晶構造の金属/合金成分を含む構成。

(c)上記(a)において、前記柱状ヒートシンクが、熱伝導性の高い炭素原子構造体(ダイヤモンド、フラーレン又はカーボンナノチューブ等)を含有する構成。

(d)上記(a)において、前記柱状ヒートシンクが、ナノコンポジット結晶構造の金属/合金成分と、熱伝導性の高い炭素原子構造体とを含有する複合材料でなる構成。

(e)前記貫通電極が、前記基板に設けられたビアを鋳型とする鋳込み成形体でなり、前記柱状ヒートシンクが、熱伝導性の高い炭素原子構造体(ダイヤモンド、フラーレン又はカーボンナノチューブ等)を含有する構成。

【0038】

上述した基板は、電子部品と組み合わされて電子機器を構成する。この場合、電子部品は、前記基板に取り付けられる。これにより、電子部品に対して、電気抵抗の低い貫通電極による電気回路を構成するとともに、電子部品の動作によって発生した熱を、柱状ヒートシンクによって効率よく放熱し、電子部品の発熱による特性変動、誤動作、更には、熱暴走等を回避することができる。

【0039】

本発明において、電子部品には、能動素子、受動部品またはそれらを組み合わせた複合素子を含むことができる。また、電子機器には、電子工学の技術を応用した電気製品のほとんど全てが含まれる。電子機器には、更に、TSV技術を適用して、3次元積層構造としたもの、又は、インターポーザと各種素子と組み合わせて3次元積層構造としたものも含まれる。

【発明の効果】

【0040】

以上述べたように、本発明によれば、次のような効果を得ることができる。

(a)電気抵抗の低い貫通電極構造を有する電子機器用基板及びそれを用いた電子機器を提供することができる。

(b)放熱特性に優れた熱伝導路を有する電子機器用基板及びそれを用いた電子機器を提供することができる。

(c)電気抵抗の低い貫通電極構造、及び、放熱特性に優れた熱伝導路を短時間で、効率よく形成することができる電子機器用基板及びそれを用いた電子機器を提供することができる。

【0041】

本発明の他の目的、構成及び利点については、添付図面を参照し、更に詳しく説明する。添付図面は、単に、例示に過ぎない。

【図面の簡単な説明】

【0042】

【図1】本発明に係る基板の一部を示す平面図である。

【図2】図1に示した基板の断面図である。

【図3】本発明に係るナノコンポジット結晶構造の金属/合金成分を含む複合材料を模式的に示す図である。

【図4】本発明に係るナノコンポジット結晶構造の金属/合金成分を含む複合材料を模式的に示す図である。

【図5】本発明に係るナノコンポジット結晶構造の金属/合金成分を含む複合材料を模式的に示す図である。

【図6】本発明に係るナノコンポジット結晶構造の金属/合金成分を含む複合材料を模式的に示す図である。

【図7】本発明に係る基板の断面のSEM像である。

【図8】本発明に係る基板の製造方法を示す図である。

【図9】本発明に係る基板を用いた電子機器の部分断面図である。

【図10】本発明に係る基板の他の実施例を示す図である。

【図11】図10に示した基板を用いた電子機器の部分断面図である。

【図12】本発明に係る基板の他の実施例を示す図である。

【図13】図12に示した基板を用いた電子機器の部分断面図である。

【図14】本発明に係る発光デバイスの一形態を示す部分断面図である。

【図15】図14に示した発光デバイスに用いられている支持体の平面図である。

【図16】図15の12−12線断面図である。

【図17】図14に示した発光デバイスに用いられる発光素子の外観を示す図である。

【図18】図17に示した発光素子の底面図である。

【図19】本発明に係る発光デバイスの他の形態を示す部分断面図である。

【図20】本発明に係る発光デバイスの更に別の一形態を示す部分断面図である。

【図21】本発明に係る照明装置の平面図である。

【図22】図21に示された照明装置の一部における拡大断面図である。

【図23】図22の断面図から発光素子と蛍光体とを除いた断面図である。

【図24】他の形態に係る発光デバイスの断面図である。

【図25】図24の断面図から発光素子と蛍光体とを除いた断面図である。

【図26】本発明に係る液晶ディスプレイの断面図である。

【図27】画素の平面図である。

【図28】本発明に係る発光ダイオードディスプレイの平面図である。

【図29】本発明に係る基板の他の形態を示す断面図である。

【図30】図29に示した基板を用いた電子デバイスの部分断面図である。

【図31】本発明に係る基板の他の形態を示す部分断面図である。

【図32】図31に示した基板を用いた電子デバイスの部分断面図である。

【図33】本発明に係る電子デバイスの他の形態を示す部分断面図である。

【図34】本発明に係る電子デバイスの他の形態を示す部分断面図である。

【図35】本発明に係る電子デバイスの他の形態を示す部分断面図である。

【図36】本発明に係る電子デバイスの他の形態を示す部分断面図である。

【図37】本発明に係る放熱用基板の一部を示す断面図である。

【図38】本発明に係る放熱用基板の他の形態における一部を示す断面図である。

【図39】本発明に係る放熱用基板の他の形態における一部を示す断面図である。

【図40】本発明に係る放熱用基板の他の形態における一部を示す断面図である。

【図41】本発明に係る放熱用基板の他の形態における一部を示す断面図である。

【図42】本発明に係る放熱用基板の他の形態における一部を示す断面図である。

【図43】本発明に係る放熱用基板の他の形態における一部を示す平面図である。

【図44】図43に示した放熱用基板の断面図である。

【図45】本発明に係る放熱用基板の他の形態における一部を示す断面図である。

【図46】本発明に係る放熱用基板の他の形態における一部を示す断面図である。

【図47】車載電子機器の回路図である。

【図48】図47に示した車載電子機器の放熱構造を示す部分断面図である。

【図49】パーソナル・コンピュータや携帯電話機等の電子機器に採用し得る放熱構造を示す部分断面図である。

【図50】パーソナル・コンピュータや携帯電話機等の電子機器に採用し得る放熱構造を示す部分断面図である。

【発明を実施するための形態】

【0043】

図1及び図2を参照すると、本発明に係る電子機器用基板1は、μmオーダの所定ピッチをもって配置された複数の貫通電極2を有している。貫通電極2のビア径も、μmオーダである。貫通電極2は、カーボンナノチューブを含有し、基板1に設けられたビア20を鋳型とする鋳込み成形体でなる。

【0044】

好ましくは、貫通電極2は、基板1に設けられたビア20を鋳型とする鋳込み成形体である。貫通電極2が鋳込み成形体である場合、ビア20の側壁面に対する密着力が高く、巣、空隙、空洞のない緻密な構造を持ち、電気抵抗が小さく、電気伝導性に優れた貫通電極2を有する基板1が得られる。ビア20の内壁面に凹凸があっても、貫通電極2は、その凹凸に倣うように鋳込まれるから、ビア20に対する密着強度の高い貫通電極2が得られる。

【0045】

しかも、貫通電極2が、ビア20の内壁面の凹凸に倣うように鋳込まれる結果、貫通電極2とビア20の内壁面の凹凸が、貫通電極2の抜けを阻止するアンカー部として働くので、基板1に対する貫通電極2の結合強度が高くなる。このことは、めっきによって貫通電極2を形成する場合と異なって、ビア20の内壁面に凹凸精度が要求されず、むしろ、若干の凹凸があった方が好ましいということを意味する。このため、ビア20の形成が容易になる。

【0046】

SEM像を示す図7を参照すると、基板1に設けられたビア20内に、貫通電極2が、巣、空隙、空洞のない緻密な構造を保って充填され、ビア20の側壁面が凹凸を有するにも関わらず、貫通電極2がビア20の側壁面に密着している。

【0047】

ビア20は、レーザ、ケミカル・エッチング又はプラズマエッチング等によって穿ビアされるものであり、その内壁面に穿ビア工程に付随する凹凸が生じるのであるが、図7に示すように、貫通電極2は、ビア20の内壁面が凹凸面となっているにも関わらず、その凹凸面を倣うように充填されて、ビア20の内壁面に密着し、巣、空隙、空洞のない緻密な構造となっている。しかも、ビア20の内壁面の凹凸が一種のアンカー効果を生じるので、柱状ヒートシンク3がビア20から浮き上がったり、あるは浮動したりすることなく、ビア20内に確実に固定される。これは、裏返せば、スパッタ及びめっきの併用によって形成する一般的技術と比較して、ビア20の形成に当たって、その内壁面の平面度に気を使わずに済み、却って、ビア20をある程度ラフに形成した方がよい結果を生むということでもある。

【0048】

貫通電極2は、カーボンナノチューブ(Carbon nanotube)を含有する。カーボンナノチューブは、炭素によって作られる六員環ネットワーク(グラフェンシート)が単層あるいは多層の同軸管状になった物質である。単層のシングルウォールナノチューブ (SWNT)、多層のマルチウォールナノチューブ (MWNT) の何れを用いてもよい。具体的には、カーボンナノチューブをフィラーとして、アルミニュウム合金中に配向して添加した複合材料を用いることができる。

【0049】

カーボンナノチューブは、電流密度耐性が、109A/cm2で、銅の1、000倍以上の高電流密度耐性を有する。しかも、カーボンナノチューブ内では、電気良導体である銅との対比において、電子散乱が少ないため、電気抵抗が小さい。したがって、カーボンナノチューブを含有する貫通電極2によれば、銅との対比において、電気抵抗が小さく、大きな電流を流しても、抵抗発熱量を低減することができる。

【0050】

貫通電極2は、カーボンナノチューブ自体によって構成してもよいし、カーボンナノチューブと、ナノコンポジット結晶構造の金属/合金成分を含む複合材料によって構成してもよい。本発明において、「ナノ」とは、1μm未満のサイズをいう。

【0051】

カーボンナノチューブ及びナノコンポジット結晶構造の金属/合金成分を含む貫通電極2は、大きさが、ナノレベルに制限された組織(結晶)を含むから、その効果として、貫通電極2に発生する応力が小さくなる。

【0052】

図3〜図6は、本発明に係るナノコンポジット結晶構造を模式的に示す図である。図3に示す形態は、第1結晶組織80の内部に、ナノサイズである第2結晶組織81を分散させたものである。このほか、図4〜図6に模式的に示すように、第1結晶組織80の粒界に、ナノサイズである第2結晶組織81を分散させたもの(図4)、これとは逆に、第2結晶組織81の粒界に、ナノサイズである第1結晶組織80を分散させたもの、第1結晶組織80の内部に、ナノサイズである第2結晶組織81を分散させるとともに、第1結晶組織80の粒界に、ナノサイズである第2結晶組織81を分散させたもの(図5)、第1結晶組織80及び第2結晶組織81の両者がナノサイズであるもの(図6)などの形態をとることができる。図示は省略するけれども、図3〜図6の形態を組み合せたものであってもよい。さらに、上述した第1結晶組織80及び第2結晶組織81によるナノコンポジット結晶構造とは、異なる他種のナノコンポジット結晶構造を形成させてもよい。

【0053】

第1結晶組織80及び第2結晶組織81は、金属成分が部分的に重なっていてもよいし、全く異なっていてもよい。第1結晶組織80及び第2結晶組織81の別は、含まれている金属元素の融点の違いや、共晶化や合金化の有無などによって生まれる。また、このナノコンポジット結晶構造は、ナノ金属/合金粒子の溶融充填方法や、スパッタ併用めっき法などによって実現することができる。

【0054】

第1結晶組織80及び第2結晶組織81の代表的な例は、非共晶組織と共晶組織の組み合わせである。共晶は、合金などの結晶組織の1つであって、たとえば2種類の金属Aと金属Bを溶解して合金をつくる場合、金属Aと金属Bの比率が金属Aに対する金属Bの固溶限(固溶体をつくる限界)までの範囲や、金属Bに対する金属Aの固溶限までの範囲にないと、合金は、それぞれ違った成分比の固溶体の結晶がまじりあったものになり、共晶組織を構成する。金属Aと金属Bとが、上記条件を満たさない場合や、溶解温度が共晶点まで達しなかった場合には、本来、共晶となりえる金属A,Bであっても、非共晶組織となる。非共晶組織は、共晶化のための金属元素とは異なる第3の金属元素を添加することによっても得られる。

【0055】

第1結晶組織80を非共晶組織とした場合、第2結晶組織81は共晶組織である。この組み合わせを前提としたナノコンポジット結晶構造には、図3〜図6を参照すると明らかなように、

(a)非共晶組織の内部に共晶組織でなるナノ粒子を分散させたもの、

(b)非共晶組織の粒界に共晶組織でなるナノ粒子を分散させたもの、

(c)共晶組織の粒界に非共晶組織でなるナノ粒子を分散させたもの、

(d)非共晶組織の内部に共晶組織でなるナノ粒子を分散させるとともに、非共晶組織の粒界に共晶組織でなるナノ粒子を分散させたもの、

(e)共晶組織及び非共晶組織が、共にナノサイズであるもの

などが含まれる。

【0056】

貫通電極の材質特性を決定づける重要な因子として、柱状晶と等軸晶とがある。柱状晶は、もともと大きく粒成長するものである。そのため、容易に亀裂の伝播経路となり、基板のクラックなどを招く。

【0057】

これに対して、等軸晶は粒成長が等方的で粒径自体も小さいから、基板に発生する応力も小さくなる。

【0058】

又、貫通電極が、製造工程における熱工程を経ている場合、金属一般が持つ正の体積変化率により、一般には、貫通電極を膨張させる方向に働き、その後、収縮する。この熱膨張・収縮に伴い、基板に応力が発生する。等軸晶は、この金属膨張による応力発生に対しても抑制効果を奏する。

【0059】

上述したように本発明に係るナノコンポジット結晶は、上述した構成を有するので、柱状晶化を抑制し、等軸晶化を促進する。よって、基板に加わる応力、ストレス、又は、特性・劣化を抑制する。

【0060】

しかも、ナノコンポジット結晶構造には、縦導体の等軸晶化を促進する働きがある。上述したカーボンナノチューブ及びナノコンポジット結晶構造の有する特有の特性により、特に、半導体基板において、半導体回路の特性劣化が抑制される。また、基板に亀裂・クラックが入るのを抑制することもできる。

【0061】

上述したように、ナノコンポジット結晶構造には、柱状晶の発生を抑制し、等軸晶化を促進する働きはあるが、柱状晶の生成は零ではない。柱状晶が発生することもある。ナノコンポジット結晶構造とともに、カーボンナノチューブを共存させる構成によれば、ナノコンポジット結晶構造に発生することのある柱状晶による応力の増大を、カーボンナノチューブの有する弾性により、緩和することができる。よって、前記基板に加わる応力、ストレス、又は、特性・劣化を、更に確実に抑制することができる。

【0062】

ナノコンポジット結晶構造の金属/合金成分としては、Bi、In、Sn及びCuを例示することができる。特に、Biを含有させると、Biの持つ凝固時の体積膨張特性により、ビア20の内部で、空洞や空隙を生じることのない緻密な貫通電極2を形成することができる。もっとも、Bi等を含有させると、電気抵抗が増大する傾向にあるので、要求される電気抵抗値を満たす限度で、Biを使用することが好ましい。

【0063】

更に、カーボンナノチューブと、有機材料とを混合し、必要であれば、セラミック又はガラス等の無機粉末又はナノコンポジット結晶構造の金属/合金成分を添加した複合材料で構成してもよい。

【0064】

貫通電極2を形成する基板1は、セラミック等の無機基板、銅張り基板等に見られる有機基板又は半導体基板の少なくとも一種を含むことができる。用い得る半導体基板には、特に制限はない。Si基板(シリコン基板)、SiC基板 (シリコンカーバイド基板)、GaN基板 (窒化ガリウム基板)、ZnO基板 (酸化亜鉛基板)等は勿論のこと、SOI基板(Silicon on insulator)等を用いることができる。基板1を構成する無機基板、有機基板が導電性を有する場合、及び、基板1が上述したような半導体基板でなる場合は、貫通電極2は、導電性の無機基板、導電性の有機基板及び半導体基板に対して、電気絶縁膜または電気絶縁層によって電気絶縁される。そのような絶縁構造は、貫通電極2の鋳型となる孔20の内壁面を酸化又は窒化して得られた絶縁膜、孔20の内壁面に付着させた絶縁層によって実現することができる。上述した絶縁層は、孔20から微小間隔を隔ててその周りにリング状に設けてもよい。

【0065】

貫通電極2の成形にあたっては、まず、図8(A)に図示するように、予め、厚み方向に貫通する微細なビア20を多数設けた基板1を、支持台S1の上に搭載する。ビア20の下側は、支持台S1によって閉塞されている。もっとも、ビア20は、非貫通孔であってもよい。

【0066】

次に、図8(B)に示すように、基板1に設けられたビア20を鋳型として、その内部に液状、ペースト状または粉体状の電極材料2を鋳込む。その後、図8(C)に図示するように、ビア20内に鋳込まれた電極材料2に、機械的な力F1、例えばプレス板P1を用いたプレス圧、射出圧または転圧を印加しながら凝固させる。これによって、図8(D)に示すように、巣、空隙、空洞のない緻密な構造を持ち、ビア20の側壁面に密着した鋳込み成形体たる貫通電極2が成形される。そして、この成形体の構造は、図7のSEM像によって明らかにされている。

【0067】

基板1に設けられたビア20内に電極材料2を鋳込む工程は、減圧された真空チャンバ内で実行することが好ましい。この減圧と、その後の印加圧力によって、差圧充填を行うことができるからである。

【0068】

電極材料2が、カーボンナノチューブ及びナノコンポジット結晶構造の金属/合金成分を含む複合材料を含む場合は、これらの金属/合金成分の溶融金属にカーボンナノチューブを混ぜた液状複合材料2をビア20内に鋳込み、鋳込まれた液状複合材料2に、プレス板P1を用いたプレス圧、射出圧または転圧を印加しながら、冷却し、凝固させる。

【0069】

また、電極材料2が、カーボンナノチューブと、有機材料と、溶剤とを含有するペースト状材料である場合には、プレス板P1を用いたプレス圧、射出圧または転圧を印加しながら、加熱硬化させる。電極材料2が粉体の場合は、溶融状態でビア20内に注入充填するか、粉体の状態でビア20内に注入した後、加熱溶融させるとよい。

【0070】

図9は、図1及び図2に示した基板を、インターポーザとして用いた電子機器の一例を示している。基板1は、インターポーザとして、例えば半導体チップ等でなる電子デバイス6、6の間に配置されている。電子デバイス6、6は、電極が、接合膜4、4によって、貫通電極2にそれぞれ接続されている。

【0071】

貫通電極2は、複数備えられているから、これらの独立する複数の貫通電極2を、基板1に搭載される電子デバイス6、6に対する正極、負極として活用することができる。このため、ワイヤ・ボンディング等の電気配線が不要になり、高価なワイヤボンディング装置等に費やされていた生産設備費をカットし、製品コストを低減させることができる。

【0072】

基板1は、上記貫通電極2とは別に、または、貫通電極2とともに、柱状ヒートシンクを有していてもよい。まず、図10を参照すると、基板1は、柱状ヒートシンク3を有する。柱状ヒートシンク3は、基板1に設けられたビア30を鋳型とする鋳込み成形体でなる。

柱状ヒートシンク3は、その両端が基板1の厚み方向に貫通し、互いに微小間隔を隔てて、例えばマトリクス状に多数配置されている。柱状ヒートシンク3は、その一端(下端)が基板1の裏面(他面)に設けられた放熱層31によって共通に接続され、他端(上端)が、基板1の表面に導出されている。表面側にも、放熱層を設けることができる。

【0073】

柱状ヒートシンク3も、基板1に設けられたビア30を鋳型とする鋳込み成形体でなるから、ビア30の側壁面に対する密着力が高く、巣、空隙、空洞のない緻密な構造を持ち、熱伝導性及び放熱特性に優れた柱状ヒートシンク3を有する基板1が得られる。

【0074】

しかも、めっき法等、他の方法によって形成した場合と比較して、ビアの側壁面に対する密着力が高く、巣、空隙、空洞のない緻密な構造を持つ柱状ヒートシンク3を、短時間で、効率よく形成することができる。

【0075】

柱状ヒートシンク3を形成する技術として、ビア30の側面にメッキを施した上で、サーマルビアを形成するとすれば、連続しためっき膜を形成ためには、ビア30の内壁面を、凹凸の極めて小さい平滑な面にしなければならず、ビア形成工程に長時間を費やさなければならなくなる。しかも、ビア30のアスペクト比が高くなれば、めっきのための下地膜を連続する均質な膜として形成することが、極めて困難になる。

【0076】

これに対して、柱状ヒートシンク3を、基板1に設けられたビア30を鋳型とする鋳込み成形体として構成する本発明では、ビア30の内壁面(側壁面)が凹凸面となっていても、柱状ヒートシンク3は、鋳込みの過程で、その凹凸面を倣うように充填されてゆく。したがって、巣、空隙、空洞のない緻密な構造を持ち、ビア30の側壁面に密着した構造の柱状ヒートシンク3が得られる。よって、熱伝導性及び放熱特性に優れた柱状ヒートシンク3が実現される。

【0077】

しかも、ビア30の内壁面の凹凸が一種のアンカー効果を生じるので、柱状ヒートシンク3がビア30から浮き上がったり、あるいは浮動したりすることなく、ビア30の内部に確実に固定される。これは、裏返せば、従来技術との対比において、ビア30の形成に当たって、その内壁面の平面度に気を使わずに済み、却って、ビア30をある程度ラフに形成した方がよい結果を生むということでもある。

【0078】

柱状ヒートシンク3は、複数であって、それぞれは、基板1の面内に分布させてあり、その一端(下端)が基板1の裏面(他面)に設けられた放熱層31によって共通に接続されているから、柱状ヒートシンク3から基板1の厚み方向に伝達されてきた熱を、厚み方向と直交する面と並行な方向に拡散しながら放熱する3次元的な放熱経路が形成される。これにより、放熱性を向上させることができる。柱状ヒートシンク3を構成する材料の熱抵抗、及び、柱状ヒートシンク3の占有率を適切に選ぶことにより、電子部品又は電子デバイス6の動作によって生じた熱を、柱状ヒートシンク3によって、一層効率よく、基板1の外部に放熱しえる。

【0079】

柱状ヒートシンク3の放熱特性は、基本的には、その組成材料の持つ熱伝導率(又は熱抵抗)と、基板1の平面積に対して、柱状ヒートシンク3の全体が占める占有率とによって定まる。例えば、柱状ヒートシンク3として、熱抵抗の低い材料を用いた場合には、占有率を低下させ、熱抵抗の高い材料を用いた場合には、占有率を上げる。即ち、柱状ヒートシンク3の占有率は、その組成材料の熱伝導率を考慮して定めることになる。逆に、占有率に制限がある場合には、求められる放熱特性を考慮して、適合する熱伝導率の材料を選択することになる。

【0080】

柱状ヒートシンク3は、熱伝導性の高い炭素原子構造体を含んでいる。このような炭素原子構造体の具体例としては、ダイヤモンド、フラーレン又はカーボンナノチューブから選択された少なくとも一種を挙げることができる。

【0081】

炭素原子構造体を用いた柱状ヒートシンク3は、炭素原子構造体の有する高い熱伝導性により、放熱性に優れたものとなる。特に、カーボンナノチューブは、銅の10倍の高熱伝導特性を有するから、極めて高い放熱特性を確保することができる。具体例として、カーボンナノチューブをフィラーとして、アルミニュウム合金中に配向して添加したものを用いることができる。この複合材の熱伝導率は、アルミニュウム合金の熱伝導率の3倍を超える。この具体例に示されるように、カーボンナノチューブは、フィラーとして用いることが望ましい。カーボンナノチューブとともに、それよりも繊維が太い気相成長カーボンファイバを、フィラーとして併用してもよい。

【0082】

柱状ヒートシンク3は、ナノコンポジット結晶構造の金属/合金成分を含むことができる。この場合、柱状ヒートシンク3は、炭素原子構造体とナノコンポジット結晶構造の金属/合金成分との複合材料でなる。

【0083】

この複合材料でなる柱状ヒートシンク3は、炭素原子構造体を含むことによる上記効果とともに、ナノコンポジット結晶構造の金属/合金成分を含むことの効果として、柱状ヒートシンク3に発生する応力が小さくなるという効果を奏する。しかも、ナノコンポジット結晶構造には、柱状ヒートシンク3の等軸晶化を促進する働きがあるから、応力が更に小さくなる。

【0084】

上述したナノコンポジット結晶構造の有する特有の特性により、基板1に形成された半導体回路の特性劣化が抑制される。また、基板1に亀裂・クラックが入るのを抑制することもできる。

【0085】

柱状ヒートシンク3の構成するナノコンポジット結晶構造材料の具体例としては、限定するものではないが、Al、Au、Cu、Ag、Sn等を例示することができる。もっとも、柱状ヒートシンク3は、熱抵抗ができるだけ小さいこと好ましいから、材料及び組成比等は、そのような視点から選定する必要がある。図示実施例では、柱状ヒートシンク3は、中身の詰まった中実柱状体であって、断面円形状であるが、角形状であってもよい。

【0086】

本発明に係る放熱用基板は、電子機器への適用において、発熱を伴う電子部品を取り付け、その熱を外部に放出するために用いられる。図11には、そのような電子機器の一例が示されている。図10に示した基板1の一面に、発熱を伴う電子部品又は電子デバイス6が、熱伝導性結合剤層51を介して搭載されている。放熱層31には、好ましくは、放熱ブロックを熱結合させる。電子部品又は電子デバイス6は、例えば、半導体チップ等の能動素子、又は、コンデンサ、インダクタ等の受動部品もしくはそれらの複合素子である。電子部品又は電子デバイス6は、半導体素子と受動部品とを併せ持つものであってもよいし、メモリ素子、論理回路素子またはアナログ回路素子であってもよい。これらの素子の単層であってもよいし、積層されたものであってもよい。

【0087】

ここで、本発明に係る基板1は、ビア30を鋳型とする鋳込み成形体でなる柱状ヒートシンク3を有しており、柱状ヒートシンク3により、ビア30の側壁面に密着し、巣、空隙、空洞のない緻密な構造を持ち、熱伝導性及び放熱特性に優れた放熱路が形成される。このため、電子機器への適用において、電子部品又は電子デバイス6に発生した熱を、熱伝導性及び放熱特性に優れた柱状ヒートシンク3を通して、効率よく、確実に放熱し、電子部品又は電子デバイス6の異常発熱、熱暴走、誤動作を回避することができる。

【0088】

次に、図12を参照すると、貫通電極2と、柱状ヒートシンク3とを併せ持つ基板1が図示されている。この場合、貫通電極2と、柱状ヒートシンク3との間には、次のような組合せが存在し得る。

(a)貫通電極2が、カーボンナノチューブを含有し、基板1に設けられたビア20を鋳型とする鋳込み成形体でなり、柱状ヒートシンク3が、基板1に設けられたビア30を鋳型とする鋳込み成形体でなる構成。

(b)上記(a)において、貫通電極2及び柱状ヒートシンク3が、ナノコンポジット結晶構造の金属/合金成分を含む構成。

(c)上記(a)において、柱状ヒートシンク3が、熱伝導性の高い炭素原子構造体(ダイヤモンド、フラーレン又はカーボンナノチューブ等)を含有する構成。

(d)上記(a)において、柱状ヒートシンク3が、ナノコンポジット結晶構造の金属/合金成分と、熱伝導性の高い炭素原子構造体(ダイヤモンド、フラーレン又はカーボンナノチューブ等)を含有する複合材料でなる構成。

(e)貫通電極2が、基板1に設けられたビア20を鋳型とする鋳込み成形体でなり、柱状ヒートシンク3は、ナノコンポジット結晶構造の金属/合金成分を含み、基板1に設けられたビア30を鋳型とする鋳込み成形体でなる構成。貫通電極2がカーボンナノチューブを含有することは、必ずしも必要ではない。

(f)上記(e)において、柱状ヒートシンク3が、熱伝導性の高い炭素原子構造体(ダイヤモンド、フラーレン又はカーボンナノチューブ等)を含有する複合材料でなる構成。

(g)貫通電極2が、基板1に設けられたビア20を鋳型とする鋳込み成形体でなり、柱状ヒートシンク3が熱伝導性の高い炭素原子構造体(ダイヤモンド、フラーレン又はカーボンナノチューブ等)を含有する構成。貫通電極2がカーボンナノチューブを含有することは、必ずしも必要ではない。

【0089】

上述した基板1は、図13に図示するように、電子部品6と組み合わされて電子機器を構成する。電子部品6は、電極が貫通電極2に接合された状態で、基板1に取り付けられる。これにより、電子部品6に対して、電気抵抗の低い貫通電極2による電気回路を構成するとともに、電子部品6の動作によって発生した熱を、柱状ヒートシンク3によって効率よく放熱し、電子部品6の発熱による特性変動、誤動作、更には、熱暴走等を回避することができる。

【0090】

本発明において、電子部品には、能動素子、受動部品またはそれらを組み合わせた複合素子を含むことができる。能動素子の代表例として、発光ダイオード、各種メモリ、各種論理ICまたはアナログ回路素子等を例示することができる。受動部品には、キャパシタ、インダクタもしくは抵抗またはそれらを組み合わせた複合素子が含まれる。

【0091】

本発明において、電子機器には、電子工学の技術を応用した電気製品のほとんど全てが含まれる。具体例としては、パーソナル・コンピュータ、携帯電話機、デジタル家電、発光ダイオードを用いた発光装置、照明装置、交通信号灯、画像処理装置、イメージ・センサまたは車載電子機器等が含まれる。更には、TSV技術を適用して、3次元積層構造としたもの、又は、インターポーザと各種素子と組み合わせて3次元積層構造としたものも含まれる。次に、電子部品及び電子機器の具体的な実施例について説明する。例示する全ての実施例において、貫通電極及び柱状ヒートシンクは、既に述べた特徴を有し、作用効果を奏するので、それらの重複説明は省略する。

【0092】

実施例1:発光ダイオード及び発光デバイス

図14〜図16に図示された発光デバイスは、基板1と、発光素子6とを含む。発光素子6は蛍光層7によって覆われている。基板1は、いわゆるパッケージとなるものであって、2つの貫通電極2、2と、複数の柱状ヒートシンク3とを含み、一面に凹部11を有している。基板1の好ましい例は、Siを主成分とするものである。これとは異なって、基板1は、絶縁樹脂基板又は絶縁性セラミック基板で構成してもよい。基板1は、図示では、4角形状の外形を有するが、その形状は任意である。基板1の凹部11は、貫通電極2、2を、間隔をおいて囲むように形成されていて、その内側面のほぼ全周に、例えば、Al膜、Ag膜又はCr膜等でなる反射膜8がスパッタ等によって形成されている。反射膜8の下側には酸化膜等の絶縁膜を設けられることがある。

【0093】

貫通電極2、2のそれぞれは、凹部11を形成した領域内において、基板1を厚み方向に貫通し、一端が凹部11の内面に露出し、他端が基板1の他面に露出する。貫通電極2、2は、中身の詰まった中実柱状体であって、角形状、円形状等、任意の断面形状をとることができる。貫通電極2、2は、基板1を貫通する部分と、基板1の一面にあって、発光素子6と接合される部分との間で、その平面形状を異ならせてもよい。例えば、基板1を貫通する部分の断面形状を、角形状又は円形状等の形状とし、発光素子6と接合される部分を平面積の拡大されたパターンとするなどである。また、貫通電極2、2は、その端面形状を、接続される発光素子6の電極形状と対応させることが好ましい。このような観点から、実施例では、貫通電極2、2の一方の端面形状を、円形状とし、他方の端面形状を四角形状としてある。

【0094】

柱状ヒートシンク3は、その両端が基板1の厚み方向に貫通し、互いに微小間隔を隔てて、マトリクス状に多数配置されている。柱状ヒートシンク3は、基板1の裏面(他面)に設けられた放熱層31によって共通に接続されている。貫通電極2、2は、放熱層31から独立させてある。放熱層31の形態は、図示の膜状に限らず、拡大された放熱面積を有する3次元的構造であってもよい。

【0095】

発光素子6は、発光ダイオードであって、図17、図18に例示するものは、透明結晶層62の光出射面60とは反対側の他面に、P型半導体層611及びN型半導体層613を積層した半導体積層構造61を含んでいる。P型半導体層611及びN型半導体層613の間には活性層612が設けられる。

【0096】

P型半導体層611及びN型半導体層613のうち、透明結晶層62の側に位置するN型半導体層613は、P型半導体層611と重ならない部分614を有しており、N側電極63が、その重ならない部分614の表面に設けられている。P側電極64は、重なる部分において、P型半導体層611の表面に設けられている。N側電極63は、円形状に限らず、角形状であってもよい。

【0097】

実施例において、重ならない部分614に設けられたN側電極63の平面積は、重なる部分に設けられたP側電極64の平面積よりも小さい。より詳しくは、N側電極63及びP側電極64の配置方向で見た電極幅について、N側電極63の電極幅がP側電極64の電極幅よりも小さい。このような電極配置によれば、重ならない部分614の幅を小さくし、反射的に、発光領域となる重なる部分の幅及び面積を拡大できるから、発光量を増大することができる。

【0098】

もっとも、図17、図18は、本発明において適用可能な発光素子6の一例を示すものであって、これに限定されるものではない。例えば、透明結晶層62と半導体積層構造61との上下関係が逆転した構造であってもよい。また、電極面積は電流拡散を考慮して定められる。

【0099】

発光素子6は、図14に示したように、基板1の凹部11内に配置され、P型半導体層611のP側電極64が、貫通電極2の一端に接続され、N型半導体層613のN側電極63が、貫通電極2の一端に接続されている。発光素子6は、凹部11の内部に配置されたとき、その上面が凹部11の周りの基板1の表面よりも、低くなるように配置される。そして、その段差を埋めるように、蛍光層7を充填してある。

【0100】

P側電極64及びN側電極63は、間隔を隔てて互いに対向している。P側電極64と貫通電極2との接合、及び、N側電極63と貫通電極2との接合にあたっては、両者の接合界面に接合膜を介在させる。接合膜は、Sn、In、Bi、Ga又はSbの群から選択された少なくても1種の低融点金属成分と、Cr、Ag、Cu、Au、Pt、Pd、Ni、Ni−P合金、Ni−B合金の群から選択された少なくとも1種を含む高融点金属材料からなる。低融点金属は、P側電極64及び貫通電極2、N側電極63及び貫通電極2と反応して、金属間化合物を形成して消費され、接合後は融点が大幅に上昇する。

【0101】

透明結晶層62は、代表的にはサファイアであり、その一面が光出射面60となる。透明結晶層62の一面上には、バッファ層(図示しない)があり、半導体積層構造61は、バッファ層を介して、透明結晶層62の上に成長させてある。

【0102】

半導体積層構造61は、発光素子6において周知である。PN接合を持ち、代表的にはIII−V族化合物半導体が用いられる。もっとも、公知技術に限らず、これから提案されることのある化合物半導体を含むことができる。

【0103】

本発明において、発光素子6は、赤色発光素子、緑色発光素子、青色発光素子、橙色発光素子の何れであってもよいし、白色発光素子であってもよい。それらの発光素子において、半導体積層構造61を構成する半導体材料及びその製造方法は既に知られている。

【0104】

図示の発光デバイスでは、基板1は、2つの貫通電極2、2を含み、一面に凹部11を有している。貫通電極2、2のそれぞれは、基板1を厚み方向に貫通し、一端が凹部11の内面に露出している。この基板1の凹部11内に発光素子6が配置されている。発光素子6は、実施例では、透明結晶層62の光出射面となる一面60とは反対側の他面に、P型半導体層611及びN型半導体層613を積層した構造である。そして、凹部11の内部で、P型半導体層611のP側電極64が貫通電極2の一端に接続され、N型半導体層613のN側電極63が、貫通電極2、2の他方の一端に接続されている。したがって、実施例によれば、発光素子6に対しては、透明結晶層62のある側とは反対側から、電流が注入されることになり、発光素子6のための電極が、光出射面60に現れない構造が実現されることになる。よって、発生した光を、効率よく外部に放射させ得る。

【0105】

基板1は、複数の柱状ヒートシンク3を含んでいる。柱状ヒートシンク3は、基板1の厚み方向に設けられている。したがって、発光素子6の発光動作によって生じた熱を、柱状ヒートシンク3によって、基板1の外部に放熱し、発光素子6の電極63、64と貫通電極2、2とを接続する接合部分の接合強度を保存し、電気的接続の信頼性を維持することができる。また、発熱による発光素子6の発光特性の変動を回避することができる。

【0106】

柱状ヒートシンク3は、その一端が、基板1の他面側に導出され、基板1の他面に設けられた放熱層31に接続されている。この構造によれば、放熱特性が更に向上する。

【0107】

実施例では、凹部11の内面と発光素子6の側面との間に、反射膜8が設けられている。これにより、半導体層61で生じた光を、透明結晶層62における光散乱・吸収作用を抑えながら、透明結晶層62の光出射面60に導くことができる。

【0108】

反射膜8は、凹部11の内面に付着されていてもよいし、発光素子6の側面に付着されていてもよい。図14〜図16の実施例では、発光素子6は、凹部11に対して、微小なクリアランスを有して、嵌めこまれている。この構造によれば、基板1に対する発光素子6の位置決め・配置を、容易、かつ、確実に実行することができる。

【0109】

図示はされていないが、光出射面60に、微細凹凸形状を有する透明光学部品を配置することができる。これにより、光出射面60で、光を拡散又は分散させ、均一な面発光を実現することができる。透明光学部品を設ける代わりに、光出射面60に、微細凹凸形状が形成されていてもよい。さらに、図示は省略するけれども、微細凹凸とともに、あるいは、微細凹凸を設けることなく、光出射面60に蛍光体を設けてもよい。

【0110】

さらに、図19を参照すると、図14〜図16の実施の形態との対比において、凹部11の平面積を拡大した発光デバイスが図示されている。この凹部11は、発光素子6の平面積よりもかなり大きく、発光素子6の外周と、凹部11の内周面との間に蛍光層7等が充填されている。また、凹部11の内壁面に反射膜8が付着されている。柱状ヒートシンク3は、一端(上端)が凹部11の底面位置と略同じ位置で止まっていて、他端が基板1の裏面に導かれ、放熱層31に接続されている。

【0111】

図20を参照すると、図19と略同じような構造において、凹部11の中央部分に、突出部12を設け、この突出部12に発光素子6を搭載した発光デバイスが図示されている。

図19及び図20の実施の形態も、図14〜図17を参照して説明した作用効果を奏する。

【0112】

本発明に係る発光デバイスは、単一の発光素子である発光ダイオード、複数の発光素子を、例えばマトリクス状に配置した面発光装置、照明装置、液晶ディスプレイ用バックライト、信号灯等、広範な用途を持っている。以下に、その内の例を示す。

【0113】

図21は、発光ダイオードを用いた照明装置の平面図である。図示の照明装置は、矩形状の基板1と、この基板1にマトリックス状に配列された複数の発光デバイスQR、QG、QBとを含む。

【0114】

各発光デバイスQR、QG、QBは、所定の色相の光を発する発光素子6と、発光素子6を電気的に接続するための2個の貫通電極2、2と、発光素子6の周囲に配置された複数の柱状ヒートシンク3とを有する。各発光素子6は、基板1の板面に形成された凹部11内に配置されている。基板1の形状、発光デバイスQR、QG、QBの数、及び、配置形態、並びに柱状ヒートシンク3の数、及び配置形態は、図21に示された形態に限られず、適宜に決定すべきものである。

【0115】

図22〜図24には上記の発光デバイスQR、QG、QBが詳細に示されている。基板1は、いわゆるパッケージとなるものであって、複数の貫通電極2、2と、複数の柱状ヒートシンク3とを含み、板面に凹部11を有している。基板1は、Siを主成分とするものを採用すると好適であるが、これに限られず、絶縁樹脂基板、又は絶縁性セラミック基板を採用してもよい。更には、金属基板等の導電性基板であってもよい。本実施形態では、基板1がSi基板で構成されている場合を例にとって説明する。

【0116】

基板1の凹部11の形状は、図21に示されるような直方体形状に限られることはなく、他の形状であってもよい。この凹部11は、基板1を平面視したときに、貫通電極2、2を、間隔をおいて囲むように形成されていて、その内側面のほぼ全周に、反射膜8がスパッタ等によって形成されている。反射膜8は、上述した形態に限定されず、例えば発光素子6の側面に付着されてもよく、また、反射膜8の下側に酸化膜等の絶縁膜を設けてもよい。

【0117】

発光素子6は、凹部11に、微小なクリアランスをもって嵌めこまれている。この構造によれば、基板1に対する発光素子6の位置決め・配置を、容易、かつ、確実に実行することができる。また、発光素子6は、凹部11内において、上面を蛍光層7により覆われている。これにより、発光素子6の発する光の輝度を向上することができる。蛍光層7に用いられる蛍光物質としては、例えばリン酸カルシウムがある。また、蛍光層7の色相は、用途に応じて適宜に決定すべきものである。

【0118】

貫通電極2、2のそれぞれは、凹部11の底面内において、基板1を厚み方向に貫通し、一端が凹部11の内面に露出し、他端が基板1の他面に露出する。貫通電極2、2の端面形状を、接続される発光素子6の電極形状と対応させてもよく、この場合、貫通電極2、2の端面形状は、それぞれ円形状と四角形状になる。

【0119】

本実施形態における基板1は、導電性を有するSi基板でなるので、貫通電極2、2は基板1から電気絶縁されている。電気絶縁の手段として、貫通電極2、2の外周面と、貫通電極2、2が配置されたビアの内周面との間に、電気絶縁層9が設けられている。電気絶縁層9は、Si基板でなる基板1のビア内壁面を酸化または窒化して得られた酸化膜または窒化膜であってもよいし、ビア内に充填された有機絶縁物またはガラス等の無機絶縁物から構成された層であってもよい。

【0120】

柱状ヒートシンク3は、基板1の厚み方向に貫通し、互いに微小間隔を隔てて、マトリクス状に多数配置され、基板1の裏面(他面)に設けられた放熱層31に接続されている。これにより、柱状ヒートシンク3は、基板1から効果的に熱を逃がすことができる。

【0121】

放熱層31は、例えばアルミニウムなどの比較的に熱伝導率の高い物質からなり、基板1の裏面に、複数個に分けて設けてもよいし、あるいは、全てのヒートシンク3に対して共通に接続される単一の部材として設けてもよい。また、放熱層31の形態は、図示の膜状に限らず、拡大された放熱面積を有する3次元的構造であってもよい。

【0122】

図24には、発光デバイスQR、QG、QBの他の形態が示されている。本形態の発光デバイスと、先に述べた実施形態の相違点は、基板1が3つの層101〜103から構成されている点、及び、凹部11の平面積が拡張されている点である。

【0123】

本実施形態において、基板1は、SOI基板であり、第1基板層を構成する第1シリコン層101、絶縁層を構成する酸化層102、及び、第2基板層を構成する第2シリコン層103を、この順序で積層した構造となっている。

【0124】

凹部11は、第2シリコン層103の表面を切り抜いて形成されており、その内側面は、開口端に向かうに従って開口面積の拡大する傾斜面となっている。この凹部11は、発光素子6の平面積よりかなり大きい平面積を有しており、発光素子6の外周と、凹部11の内周面との間に蛍光層7が充填されている。また、凹部11の内壁面には、先の実施形態と同様に、反射膜8が付着されている。

【0125】

貫通電極2、2は、電気絶縁層9によって電気絶縁された状態で、第1シリコン層101を貫通しており、その凹部11側の端部は、酸化層102を貫通する接続部41、42とそれぞれ接続されている。接続部41、42は、発光素子6の両端子601、602と接続される。接続部41、42の形状は、円柱状に限られず、四角柱などの他の形状も採り得る。

【0126】

柱状ヒートシンク3は、貫通電極2、2と同様に、基板1の厚み方向において、第1シリコン層101を貫通するように設けられて、放熱層31に接続されている。すなわち、柱状ヒートシンク3は、基板1の裏面から第1シリコン層101と酸化層102との境界まで延在するように設けられている。この構成によると、柱状ヒートシンク3の形成にあたって、酸化層102をエッチング阻止層として機能させることができる。このため、柱状ヒートシンク3の深さ寸法が、第1シリコン層101の層厚により画定されるので、エッチングの工程管理が極めて容易になるという利点が得られる。

【0127】

上述した照明装置は、基板1を含んでおり、この基板1は、複数の柱状ヒートシンク3を含んでいる。柱状ヒートシンク3は、基板1の厚み方向に設けられているため、発光素子6の発光動作によって生じた熱を、柱状ヒートシンク3によって、基板1の外部に放熱し、発光素子6の端子601、602と貫通電極2、2とを接続する接合部分の接合強度を保存し、電気的接続の信頼性を維持することができ、また、発熱による発光素子6の発光特性の変動を回避することもできる。

【0128】

柱状ヒートシンク3は、その一端が基板1の他面側に導出され、基板1の他面に設けられた放熱層31に接続されているため、基板1の放熱特性は更に向上し得る。

【0129】

発光素子6は、図17及び図18に示したものである。したがって、発光素子6は、積層方向における透明結晶層32の反対側から電流が注入され、発光素子6の端子601、602が光出射面に現れない構造を有するから、出射した光を効率よく外部に放射させ得る。さらに、半導体層31で生じた光は、反射膜8によって透明結晶層62における光散乱・吸収作用が抑制され、透明結晶層32の光出射面に効果的に導かれる。

【0130】

次に、本発明に係る液晶ディスプレイを、図26を参照して説明する。液晶ディスプレイは、液晶パネル120と、バックライト130とを含む。この液晶ディスプレイは、概念上、一般的なコンピュータ用の表示装置や汎用電化製品の液晶表示部に限られず、液晶テレビ、あるいは携帯電話機、携帯ゲーム機、携帯情報端末といった携帯型電子機器にも適用され得る。

【0131】

液晶パネル120は、偏向フィルタ、ガラス基板、及び液晶層などから構成された液晶モジュールであって、画像信号に基づき、駆動回路(図示せず)からの電気信号によって駆動される。バックライト130は、図21〜図25に示された照明装置であり、複数の発光デバイスQR、QG、QBにより液晶パネル120をその背面側から照明する。もっとも、バックライト130の形態は、これに限定されず、例えば図14〜図20に示された照明装置でもよく、本発明に係る照明装置の何れの形態も取り得ることは言うまでもない。

【0132】

バックライト130において、貫通電極2、2はバンプ電極や配線基板を介して電源部と接続され、これにより電力を供給された発光素子6が液晶パネル120に対して光を照射する。また、柱状ヒートシンク3は、放熱層31と接続されて、基板1内部の熱を液晶ディスプレイの背面側へと排出する。

【0133】

本発明に係る液晶ディスプレイは、上述した照明装置を含むから、既に述べた作用効果を奏する。

【0134】

次に、本発明に係る発光ダイオードディスプレイを、図27及び図28を参照して説明する。発光ダイオードディスプレイは、発光素子自体を画素として用いることから、バックライトを必要とせず、消費電力を低減し得るという利点を有する。

【0135】

図27には、発光ダイオードディスプレイの画素Qが平面視で示されており、一方、図11には、この画素Qを基板1にマトリックス状に配置した発光ダイオードディスプレイが示されている。

【0136】

1個の画素Qは、3個の発光デバイスQR、QG、QBを有しており、これらの発光デバイスQR、QG、QBは、赤色光を発する発光素子6R、緑色光を発する発光素子6G、及び青色光を発する発光素子6Bをそれぞれ有している。本実施形態の発光ダイオードディスプレイは、フルカラー表示を前提としているため、このように3色の発光素子6R、6G、6Bを有するが、これに限定されるものではない。例えば、1色のみの表示を前提とする場合、画素Qは、3色の発光素子6R、6G、6Bのいずれか1個で構成すればよい。すなわち、画素Qは、表示機能に応じた発光素子を有する発光デバイスQR、QG、QBを、適宜に選択して構成される。

【0137】

また、本実施形態の画素Qは、図示されるように、3個の発光デバイスQR、QG、QBが三角形の各頂点の位置に配置されているが、これに限定されず、3色の発光素子6R、6G、6Bの特性に応じて適宜な配置態様を採り得る。

【0138】

本発明に係る発光ダイオードディスプレイは、各発光素子6R、6G、6Bの貫通電極2、2が薄膜トランジスタ(TFT)などと接続され、これにより、各画素Qは、画像信号に基づき、駆動回路によって発光制御される。また、柱状ヒートシンク3は、図22〜図27に示された構成と同様に、放熱層31と接続されて、基板1内部の熱をディスプレイの背面側へと放出する。

【0139】

本発明に係る発光ダイオードディスプレイは、上述した照明装置と同じ構成を含むから、既に述べた作用効果を奏する。

【0140】

また、本発明に係る信号灯は、例えば鉄道信号機や交通信号機に適用されるものであり、上述した発光ダイオードディスプレイのように、複数の発光デバイスQR、QG、QB0が配列されて構成され、例えば複数色の発光素子6R、6G、6Bを備える。

【0141】

本発明に係る信号灯は、上述した照明装置と同様の構成を含むから、既に述べた作用効果を奏する。

【0142】

図29に図示された基板1は、貫通電極2と、柱状ヒートシンク3と、凹部11とを含む。実施例に示す基板1はSOI基板であり、第1基板層を構成する第1シリコン層101、絶縁層を構成する酸化層102、及び、第2基板層を構成する第2シリコン層103を、この順序で積層した構造となっている。

【0143】

SOI基板としては、その製造法により、SIMOX(Separation by IMplantation of OXygen)方式のものと、張り合わせ方式の2種類のものが知られている。何れの方式のSOI基板を用いてもよい。 SIMOX方式のSOI基板として、酸素分子をイオン注入によりシリコン結晶表面から埋め込み、それを高熱で酸化させることにより、シリコン結晶中に酸化シリコンの絶縁層を形成する手法が知られている。このような絶縁層は、埋め込み酸化(BOX;Buried Oxide)層と称される。

【0144】

凹部11は、電子素子を取り付ける部分であって、第2シリコン層103の表面の面内に設けられている。図示の凹部11は、第2シリコン層103の中央部を切り抜いて4角形状に形成されていて、その内側面は、開口端に向かうに従って開口面積の拡大する傾斜面となっている。第2シリコン層103及び凹部11の内面は、絶縁膜132によって覆われている。この絶縁膜132は、シリコン酸化膜またはシリコン窒化膜で構成することができる。

【0145】

貫通電極2は、第1シリコン層101及び酸化層102を貫通し、端部が凹部11の底面から若干突出して露出している。貫通電極2は、具体的には、外部との接続部となる端子部(バンプ)21、第1シリコン層101を貫通する貫通部22、及び、電子素子の端子電極と接続される素子接続部23を含んでいる。端子部21は、貫通部22の一端面に付着されており、例えば、Ti―Au等の無電解メッキ膜でなる。

【0146】

基板1として、SOI基板を用いた実施例では、第1シリコン層101と貫通電極2との間、及び、第1シリコン層101の表面に、絶縁膜111を設けることになる。この絶縁膜111は、シリコン酸化膜またはシリコン窒化膜で構成することができる。

【0147】

素子接続部23は、一端が貫通部22の端部に付着され、他端が、絶縁膜111、酸化層102、及び、凹部11の底面に付着されている絶縁膜132を貫通して、凹部11の内部に突出して露出している。素子接続部23も、端子部21と同様に、Ti―Au等の無電解メッキ膜でなる。

【0148】

次に、柱状ヒートシンク3のそれぞれは、第1シリコン層101の厚み方向に設けたビア113の内部に充填されている。柱状ヒートシンク3は、その主要部をなす柱状部301と、その端面に付着された端子部302とからなる。端子部302は、端子部21と同様に、Ti―Au等の無電解メッキ膜でなる。柱状部301のあるビア113は、第1シリコン層101を貫通して、第1シリコン層101と酸化層102との境界で止まるように設けられ、基板1を平面視して、所定の面積占有率をもって、凹部11の周りに分布している。

【0149】

柱状ヒートシンク3と第1シリコン層101との間には、シリコン酸化膜またはシリコン窒化膜でなる絶縁膜111が設けられている。

【0150】

図30を参照すると、図29に示した基板1を用いた発光デバイスが図示されている。この発光デバイスでは、回路基板の凹部11に、電子素子たる発光素子(LED)6が取り付けられている。発光素子6の電極は、貫通電極2を構成する素子接続部23に接合5されている。図示はしないけれども、凹部11内の絶縁膜132に光反射膜を設けることが好ましい。

【0151】

ここで、基板1は、凹部11と、貫通電極2とを含んでおり、凹部11は、第2シリコン層103の表面の面内に設けられ、貫通電極2は、第1シリコン層101及び酸化層102を貫通し、端部が凹部11の底面に露出している。したがって、回路基板の凹部11内に電子素子たる発光素子6を配置し、凹部11の内部で、発光素子6の一面に設けられた電極を、貫通電極2の一端を構成する素子接続部23に接合5することができる。これによって、発光素子6は、フリップ・チップ・ボンディング方式によって、貫通電極2に接続されることになる。

【0152】

また、本発明に係る回路基板は、柱状ヒートシンク3を含んでおり、柱状ヒートシンク3は、ビア113内に充填されている。このビア113は、第1シリコン層101を貫通している。したがって、発光素子6の動作によって生じた熱を、柱状ヒートシンク3によって、基板1の外部に放熱し、発光素子6と貫通電極2とを接合5する部分の接合強度を保存し、電気的接続の信頼性を維持することができる。更に、発熱による発光素子6の電気的特性の変動を回避することができる。

【0153】

ビア113は、第1シリコン層101を貫通して、第1シリコン層101と酸化層102との境界で止まるように設けられている。このような構成であれば、ビア113を形成する場合に、酸化層102を、エッチング阻止層として機能させることができる。このため、ビア113の深さが、第1シリコン層101から酸化層102までの深さ、即ち、第1シリコン層101の層厚によって定まる画一的な値になるので、ビア113の深さの工程管理が極めて容易になる。

【0154】

ビア113は、基板1を平面視して、所定の面積占有率をもって凹部11の周りに分布している。したがって、凹部11の内部に収納された電子素子、即ち、発光素子6を、その全周から、柱状ヒートシンク3によって取り囲む放熱領域が形成されることになるから、発光素子6に発生した熱を集熱し、効率よく放熱することができる。

【0155】

また、柱状ヒートシンク3を構成する材料の熱抵抗、及び、柱状ヒートシンク3の占有率を適切に選ぶことにより、発光素子6の動作によって生じた熱を、柱状ヒートシンク3によって、基板1の外部に効率よく放熱しえる。

【0156】

実施例2:電子デバイス又は電子機器

電子素子としては、上述した発光素子6に限らず、能動素子、受動部品またはそれらを組み合わせた複合素子を含むことができる。更には、TSV技術を適用して、上述した各種素子自体を3次元積層構造としたもの、又は、インターポーザと各種素子と組み合わせて3次元積層構造としたものも含まれる。

【0157】

図31を参照すると、そのような電子素子を搭載するのに適した回路基板が図示されている。図において、先に示した図面に現れた構成部分と同一または類似の構成部分には、同一の参照符号を付してある。図31において、貫通電極2は、凹部11の内部に搭載される電子素子の有する端子電極に合わせて、その個数を増加させてある。また、凹部11は、内側面が略垂直に立ち上がる面となっている。

【0158】

図32は、図31に示した回路基板に電子素子6を組み込んだ電子デバイスの例を示している。電子素子6は、TSV技術を適用した3次元積層構造であって、例えば、LSI等の論理素子6Aと、DRAM等のメモリ素子6Cとを、インターポーザ6Bを介して積層し、接合した構造となっている。このような電子デバイスは、情報処理システムの基本要素として用いられる。より具体的には、例えば、モバイル、携帯電話機、デジタル家電、サーバ等における画像処理システムの構成要素として用いることができる。その他にも、イメージ・センサ・モジュールとしての適用例も考えられる。

【0159】

論理素子6Aは、所謂ロジックICであって、一面に設けた電極を、基板1に設けられた貫通電極2の素子接続部23に接合してある。論理素子6Aは、チップ状であって、その内部にLSIなどの半導体論理回路を有している。論理素子6Aは、内蔵された半導体論理回路を、TSV技術の適用によって、電極に導く3次元積層構造を採用することができる。

【0160】

インターポーザ6Bは、複数の貫通電極を有しており、貫通電極の一端を、論理素子6Aの電極に接続し、貫通電極2他端をメモリ素子6Cの電極に接続してある。インターポーザ6Bは、Si基板、樹脂基板又はセラミック基板に、回路基板の貫通電極と同様の組成、製造方法を適用し、貫通電極を形成することによって得られる。

【0161】

メモリ素子6Cは、内蔵されたメモリセルが電極に接続されている。メモリ素子6Cにおいても、論理素子6Aと同様に、TSV技術の適用によって、メモリセルを電極に導く3次元配置を採用することができる。

【0162】

もっとも、電子素子6を構成する素子6A〜6Cの積層数、種類、その電極配置等は、適用される電子素子6によって、さまざまに変化するもので、図32は、3次元積層構造の一例を概念的に示すものに過ぎない。

【0163】

図32に示す電子デバイスの場合も、基本的には、図30に示した電子デバイスと同様の作用効果を奏する。ただ、図32の電子デバイスでは、3次元積層構造を採ることにより、高密度化、高性能化、高速化、小型化、薄型化、軽量化が図られているから、動作によって発生する熱を、いかにして放熱するかが、更に重要な課題となる。

【0164】