電子素子のマウント方法

【課題】一括処理してもデバイスの完成体の特性にバラツキを生じない電子素子のマウント方法を提供する。

【解決手段】電子素子15のマウント方法は、電気回路11に接続する為の端子部を有する電子素子形成工程と、電子素子を配列する為の複数ザグリ部13を有するトレイ14の準備工程と、複数ザグリ部に電子素子を各々配置する工程と、複数ザグリ部に配置された各電子素子に相対する様に複数の電気回路を形成した平板状基板10の準備工程と、電気回路が有するマウント部111に電子素子を固着する為の接続部材12の一括形成工程と、電気回路のマウント部に形成した接続部材に対し、電子素子端子部を相対させて、トレイに配列した複数電子素子と基板とを一括で固着する工程を有する。

【解決手段】電子素子15のマウント方法は、電気回路11に接続する為の端子部を有する電子素子形成工程と、電子素子を配列する為の複数ザグリ部13を有するトレイ14の準備工程と、複数ザグリ部に電子素子を各々配置する工程と、複数ザグリ部に配置された各電子素子に相対する様に複数の電気回路を形成した平板状基板10の準備工程と、電気回路が有するマウント部111に電子素子を固着する為の接続部材12の一括形成工程と、電気回路のマウント部に形成した接続部材に対し、電子素子端子部を相対させて、トレイに配列した複数電子素子と基板とを一括で固着する工程を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子デバイスに用いられる電気回路が配列された集合基板を利用した圧電振動子などの電子デバイスの作製方法に係るものであり、特に、電子素子を電子デバイスの所定の位置にマウントする方法に関するものである。

【背景技術】

【0002】

近年、電子機器の小型化にともない、それに用いられる電子デバイスに対する小型化への要求が強くなってきている。

【0003】

このような電子デバイスの小型化にともない、デバイスの組立工程、特に素子の実装工程などにおいて、デバイス単個での取り扱いが困難となってきており、デバイスを縦横に配列した集合基板を取り扱うことが行われるようになってきた。

【0004】

例えば、特許文献1には、水晶振動子の製造方法として、基板に予め形成された複数のキャビティに水晶片を一括して搭載し、陽極接合を用いて基板及び蓋を接合した後に個片化する、いわゆるウエーハ状態での一括処理による製造方法が提案されている。

【0005】

図3(A)〜(B)は、従来における水晶振動子の製造方法である。まず図3(A)に示すように、1層目として、平板状のベースと呼ばれる基板を用意する。この基板は、例えば、所定の基準温度より低い900℃程度以下の低温で焼成することが可能な低温同時焼成セラミック(LTCC)からなる。この低温同時焼成セラミックは、イオン伝導性を有するガラスを含む。

【0006】

次いで、この基板上に、2層目として、低温同時焼成セラミックからなり、格子状に形成された枠200Aを積層して、凹型形状のキャビティ210を形成することにより、複数のキャビティ210を有する基板200を形成する。なお、このキャビティ210は、水晶片230を搭載する搭載領域としての収容部に対応する。

【0007】

このように、基板200として低温同時焼成セラミックを使用すれば、従来のセラミックを使用する場合と比較して、キャビティ210を有する多層構造を容易に形成することができ、また厚さを薄くすることができる。

【0008】

そして、複数のキャビティ210が形成された基板200を低温で焼成する。この場合、基板200として低温同時焼成セラミックを使用していることから、従来のセラミックのように、例えば、所定の基準温度を1500℃程度として、この温度で焼成する場合と比較して、基板200が収縮する度合いを低減することができる。従って、キャビティ210の寸法にばらつきが生じることがなく、ウエーハ状態での一括処理が可能となる。

【0009】

その後、各キャビティ210の内底面上に、搭載パッド220を一括して形成する。そして、図3(B)に示すように、各キャビティ210に形成された搭載パッド220に、導電性接着剤(図示せず)を介して水晶片230を接着することにより、ウエーハ状態で複数の水晶片230を一括して搭載する。

【0010】

しかしながら、各キャビティ210に形成された搭載パッド220に、導電性接着剤(図示せず)を塗布する場合、各キャビティ210ごとに導電性接着剤を塗布する必要がある。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2010−57095号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

このため、塗布のはじめと最後とで時間差が大きくなり、その結果、導電性接着剤の乾き状態などに差が生じてしまう。水晶振動子は水晶片の搭載状態が特性に大きく影響するため、水晶振動子の特性がばらついてしまうという課題を有していた。

【0013】

そこで本発明は、一括処理してもデバイスの完成体の特性にバラツキを生じない電子素子のマウント方法を提供することを目的とするものである。

【課題を解決するための手段】

【0014】

上記目的を達成するため、本発明の電子素子のマウント方法は、電気回路に接続するための端子部を有する電子素子を形成する工程と、前記電子素子を配列するための複数のザグリ部を有するトレイを準備する工程と、前記複数のザグリ部に前記電子素子を各々配置する工程と、前記複数のザグリ部に各々配置された前記電子素子に相対するように複数の電気回路を形成した平板状の基板を準備する工程と、前記電気回路が有するマウント部に前記電子素子を固着するための接続部材を一括で形成する工程と、前記電気回路の前記マウント部に形成した前記接続部材に対して、前記電子素子の前記端子部を相対させて、前記トレイに配列した複数の前記電子素子と前記基板とを一括で固着する工程を有する。

【0015】

本発明の電子素子のマウント方法は、電気回路に接続するための端子部を有する電子素子を形成する工程と、前記電子素子を配列するための複数のザグリ部を有するトレイを準備する工程と、前記複数のザグリ部に電子素子を各々配置する工程と、前記複数のザグリ部に各々配置された電子素子に相対するように複数の電気回路を形成した平板状の基板を準備する工程と、前記ザグリ部に配置された各々の前記電子素子の前記端子部に一括で接続部材を形成する工程と、前記電気回路が有するマウント部に対して、前記電子素子の前記端子部に形成した前記接続部材を相対させて、前記トレイに配列した複数の前記電子素子と前記基板とを一括で固着する工程を有する。

【0016】

本発明の電子素子のマウント方法において、前記接続部材の材料は、シリコーン系導電性接着剤、エポキシ系導電性接着剤、あるいは金属微粒子を含むペースト材料とする。

【0017】

本発明の電子素子のマウント方法において、前記接続部材を、ヒーターやレーザーなどによる加熱、あるいは紫外線などの光により固化させることで、前記トレイに配列した複数の前記電子素子と前記基板とを固着させる。

【0018】

本発明の電子素子のマウント方法は、前記接続部材を、スクリーン印刷、インクジェットあるいは転写法により形成する。

【0019】

本発明の電子素子のマウント方法において、各々の電子素子の前記端子、および各々の電気回路の前記マウント部は、それぞれ少なくとも2ヶ所設ける。

【0020】

本発明の電子素子のマウント方法において、前記電子素子は圧電振動子とする。

【0021】

本発明の電子素子のマウント方法において、電気回路が形成される平板状の基板は、アルミナ、窒化アルミなどのセラミックス、ガラス、あるいはシリコン(Si)などの少なくとも1種類の材料で構成する。

【発明の効果】

【0022】

本発明によれば、基板に予め形成された複数の電気回路に電子素子を一括して搭載する製造方法において、電子素子を支持固定するための接続部材も一括して形成できるため、複数の電気回路全てに、接続部材を接続部材の状態のばらつきを生じることなく形成することが可能となるので、一括処理してもデバイス特性のばらつかないデバイスを提供することが可能となる。

【図面の簡単な説明】

【0023】

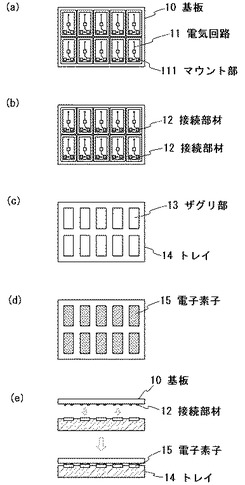

【図1】本発明における実施例の工程を示す図である。

【図2】本発明における他の実施例の工程を示す図である。

【図3】従来例における工程を示す図である。

【発明を実施するための形態】

【0024】

本発明の最良の実施形態について図1および図2を用いて説明する。

【実施例1】

【0025】

図1(a)〜(e)は本発明の一実施例における電子素子のマウント方法を示す工程図である。

【0026】

図1(a)は、縦横に配列された複数の電気回路11が形成されている平板状のアルミナ製の基板10の上面図を示しており、電気回路11の一部には電子素子を支持固定するためのマウント部111を設ける。

【0027】

図1(b)は、このマウント部111の位置にあわせて作製した印刷マスク(図示せず)を用いて、スクリーン印刷などの手法により接続部材12をそれぞれのマウント部111上に一括して形成した状態を示している。

【0028】

また、図1(c)は、基板10に形成された各々の電気回路11の位置と相対するようにザグリ部13を設けたトレイ14を示しており、図1(d)に示すように、これらザグリ部13各々には、基板10に設けられたマウント部111に支持固定する例えば圧電振動子などの電子素子15を配置する。

【0029】

次に図1(e)で示すように、図1(d)に示す電子素子15を配置したトレイ14と、図1(b)に示すマウント部111に接続部材12を形成した平板状の基板10とを相対させて、トレイ14に配置した電子素子15を平板状の基板10のマウント部111に接続部材12を介して一括で固着させる。

【0030】

接続部材12がシリコーン系導電性接着剤、エポキシ系導電性接着剤、あるいは金属微粒子を含むペースト材料などの材料である場合、電子素子15をマウント部111に接続部材12を介して接触させた後、接続部材12をヒーターやレーザーなどにより加熱、あるいは、紫外線などの光を照射することで固化させ、電子素子15を基板10に形成した電気回路11の一部であるマウント部111に固着する。

【実施例2】

【0031】

実施例1では、接続部材を基板に形成する場合を示したが、図2(a)に示すように、接続部材22は、トレイ24に配置した電子素子25へ、スクリーン印刷(図示せず)などの手法により一括で形成しても良い。

【0032】

接続部材22を電子素子25に形成した後は、図2(b)に示すように、実施例1と同様、トレイ24に配置された電子素子25を縦横に複数配列された電気回路が形成された平板状の基板20に設けられるマウント部211と相対させて、一括して固着する。

【0033】

実施例では、接続部材を形成する方法としてスクリーン印刷を説明したが、インクジェットや転写法などを用いてもよい。

【0034】

また、基板は、実施例で示したアルミナの他、窒化アルミニウム、ガラス、あるいはシリコンなどの少なくとも一種類の材料で構成することが可能である。

【0035】

なお、電子素子がトレイのザグリ部にある状態で、接続部材を加熱などにより固化し、電子素子と基板のマウント部とを接続部材を介して固着すれば、ザグリ部にある電子素子が接続部材の固化時に動くこともなく、基板に形成された電気回路に対して電子素子の位置がずれることがなくなり、特性の揃ったデバイスを作製することが可能となる。

【産業上の利用可能性】

【0036】

本発明は、電子素子を基板やパッケージに固着する圧電振動子などの電子デバイスのマウント方法として活用することが可能である。

【符号の説明】

【0037】

10、20、200 基板

11 電気回路

12、22 接続部材

13 ザグリ部

14、24 トレイ

15、25 電子素子

111、211 マウント部

210 キャビティ

220 搭載パッド

【技術分野】

【0001】

本発明は、電子デバイスに用いられる電気回路が配列された集合基板を利用した圧電振動子などの電子デバイスの作製方法に係るものであり、特に、電子素子を電子デバイスの所定の位置にマウントする方法に関するものである。

【背景技術】

【0002】

近年、電子機器の小型化にともない、それに用いられる電子デバイスに対する小型化への要求が強くなってきている。

【0003】

このような電子デバイスの小型化にともない、デバイスの組立工程、特に素子の実装工程などにおいて、デバイス単個での取り扱いが困難となってきており、デバイスを縦横に配列した集合基板を取り扱うことが行われるようになってきた。

【0004】

例えば、特許文献1には、水晶振動子の製造方法として、基板に予め形成された複数のキャビティに水晶片を一括して搭載し、陽極接合を用いて基板及び蓋を接合した後に個片化する、いわゆるウエーハ状態での一括処理による製造方法が提案されている。

【0005】

図3(A)〜(B)は、従来における水晶振動子の製造方法である。まず図3(A)に示すように、1層目として、平板状のベースと呼ばれる基板を用意する。この基板は、例えば、所定の基準温度より低い900℃程度以下の低温で焼成することが可能な低温同時焼成セラミック(LTCC)からなる。この低温同時焼成セラミックは、イオン伝導性を有するガラスを含む。

【0006】

次いで、この基板上に、2層目として、低温同時焼成セラミックからなり、格子状に形成された枠200Aを積層して、凹型形状のキャビティ210を形成することにより、複数のキャビティ210を有する基板200を形成する。なお、このキャビティ210は、水晶片230を搭載する搭載領域としての収容部に対応する。

【0007】

このように、基板200として低温同時焼成セラミックを使用すれば、従来のセラミックを使用する場合と比較して、キャビティ210を有する多層構造を容易に形成することができ、また厚さを薄くすることができる。

【0008】

そして、複数のキャビティ210が形成された基板200を低温で焼成する。この場合、基板200として低温同時焼成セラミックを使用していることから、従来のセラミックのように、例えば、所定の基準温度を1500℃程度として、この温度で焼成する場合と比較して、基板200が収縮する度合いを低減することができる。従って、キャビティ210の寸法にばらつきが生じることがなく、ウエーハ状態での一括処理が可能となる。

【0009】

その後、各キャビティ210の内底面上に、搭載パッド220を一括して形成する。そして、図3(B)に示すように、各キャビティ210に形成された搭載パッド220に、導電性接着剤(図示せず)を介して水晶片230を接着することにより、ウエーハ状態で複数の水晶片230を一括して搭載する。

【0010】

しかしながら、各キャビティ210に形成された搭載パッド220に、導電性接着剤(図示せず)を塗布する場合、各キャビティ210ごとに導電性接着剤を塗布する必要がある。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2010−57095号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

このため、塗布のはじめと最後とで時間差が大きくなり、その結果、導電性接着剤の乾き状態などに差が生じてしまう。水晶振動子は水晶片の搭載状態が特性に大きく影響するため、水晶振動子の特性がばらついてしまうという課題を有していた。

【0013】

そこで本発明は、一括処理してもデバイスの完成体の特性にバラツキを生じない電子素子のマウント方法を提供することを目的とするものである。

【課題を解決するための手段】

【0014】

上記目的を達成するため、本発明の電子素子のマウント方法は、電気回路に接続するための端子部を有する電子素子を形成する工程と、前記電子素子を配列するための複数のザグリ部を有するトレイを準備する工程と、前記複数のザグリ部に前記電子素子を各々配置する工程と、前記複数のザグリ部に各々配置された前記電子素子に相対するように複数の電気回路を形成した平板状の基板を準備する工程と、前記電気回路が有するマウント部に前記電子素子を固着するための接続部材を一括で形成する工程と、前記電気回路の前記マウント部に形成した前記接続部材に対して、前記電子素子の前記端子部を相対させて、前記トレイに配列した複数の前記電子素子と前記基板とを一括で固着する工程を有する。

【0015】

本発明の電子素子のマウント方法は、電気回路に接続するための端子部を有する電子素子を形成する工程と、前記電子素子を配列するための複数のザグリ部を有するトレイを準備する工程と、前記複数のザグリ部に電子素子を各々配置する工程と、前記複数のザグリ部に各々配置された電子素子に相対するように複数の電気回路を形成した平板状の基板を準備する工程と、前記ザグリ部に配置された各々の前記電子素子の前記端子部に一括で接続部材を形成する工程と、前記電気回路が有するマウント部に対して、前記電子素子の前記端子部に形成した前記接続部材を相対させて、前記トレイに配列した複数の前記電子素子と前記基板とを一括で固着する工程を有する。

【0016】

本発明の電子素子のマウント方法において、前記接続部材の材料は、シリコーン系導電性接着剤、エポキシ系導電性接着剤、あるいは金属微粒子を含むペースト材料とする。

【0017】

本発明の電子素子のマウント方法において、前記接続部材を、ヒーターやレーザーなどによる加熱、あるいは紫外線などの光により固化させることで、前記トレイに配列した複数の前記電子素子と前記基板とを固着させる。

【0018】

本発明の電子素子のマウント方法は、前記接続部材を、スクリーン印刷、インクジェットあるいは転写法により形成する。

【0019】

本発明の電子素子のマウント方法において、各々の電子素子の前記端子、および各々の電気回路の前記マウント部は、それぞれ少なくとも2ヶ所設ける。

【0020】

本発明の電子素子のマウント方法において、前記電子素子は圧電振動子とする。

【0021】

本発明の電子素子のマウント方法において、電気回路が形成される平板状の基板は、アルミナ、窒化アルミなどのセラミックス、ガラス、あるいはシリコン(Si)などの少なくとも1種類の材料で構成する。

【発明の効果】

【0022】

本発明によれば、基板に予め形成された複数の電気回路に電子素子を一括して搭載する製造方法において、電子素子を支持固定するための接続部材も一括して形成できるため、複数の電気回路全てに、接続部材を接続部材の状態のばらつきを生じることなく形成することが可能となるので、一括処理してもデバイス特性のばらつかないデバイスを提供することが可能となる。

【図面の簡単な説明】

【0023】

【図1】本発明における実施例の工程を示す図である。

【図2】本発明における他の実施例の工程を示す図である。

【図3】従来例における工程を示す図である。

【発明を実施するための形態】

【0024】

本発明の最良の実施形態について図1および図2を用いて説明する。

【実施例1】

【0025】

図1(a)〜(e)は本発明の一実施例における電子素子のマウント方法を示す工程図である。

【0026】

図1(a)は、縦横に配列された複数の電気回路11が形成されている平板状のアルミナ製の基板10の上面図を示しており、電気回路11の一部には電子素子を支持固定するためのマウント部111を設ける。

【0027】

図1(b)は、このマウント部111の位置にあわせて作製した印刷マスク(図示せず)を用いて、スクリーン印刷などの手法により接続部材12をそれぞれのマウント部111上に一括して形成した状態を示している。

【0028】

また、図1(c)は、基板10に形成された各々の電気回路11の位置と相対するようにザグリ部13を設けたトレイ14を示しており、図1(d)に示すように、これらザグリ部13各々には、基板10に設けられたマウント部111に支持固定する例えば圧電振動子などの電子素子15を配置する。

【0029】

次に図1(e)で示すように、図1(d)に示す電子素子15を配置したトレイ14と、図1(b)に示すマウント部111に接続部材12を形成した平板状の基板10とを相対させて、トレイ14に配置した電子素子15を平板状の基板10のマウント部111に接続部材12を介して一括で固着させる。

【0030】

接続部材12がシリコーン系導電性接着剤、エポキシ系導電性接着剤、あるいは金属微粒子を含むペースト材料などの材料である場合、電子素子15をマウント部111に接続部材12を介して接触させた後、接続部材12をヒーターやレーザーなどにより加熱、あるいは、紫外線などの光を照射することで固化させ、電子素子15を基板10に形成した電気回路11の一部であるマウント部111に固着する。

【実施例2】

【0031】

実施例1では、接続部材を基板に形成する場合を示したが、図2(a)に示すように、接続部材22は、トレイ24に配置した電子素子25へ、スクリーン印刷(図示せず)などの手法により一括で形成しても良い。

【0032】

接続部材22を電子素子25に形成した後は、図2(b)に示すように、実施例1と同様、トレイ24に配置された電子素子25を縦横に複数配列された電気回路が形成された平板状の基板20に設けられるマウント部211と相対させて、一括して固着する。

【0033】

実施例では、接続部材を形成する方法としてスクリーン印刷を説明したが、インクジェットや転写法などを用いてもよい。

【0034】

また、基板は、実施例で示したアルミナの他、窒化アルミニウム、ガラス、あるいはシリコンなどの少なくとも一種類の材料で構成することが可能である。

【0035】

なお、電子素子がトレイのザグリ部にある状態で、接続部材を加熱などにより固化し、電子素子と基板のマウント部とを接続部材を介して固着すれば、ザグリ部にある電子素子が接続部材の固化時に動くこともなく、基板に形成された電気回路に対して電子素子の位置がずれることがなくなり、特性の揃ったデバイスを作製することが可能となる。

【産業上の利用可能性】

【0036】

本発明は、電子素子を基板やパッケージに固着する圧電振動子などの電子デバイスのマウント方法として活用することが可能である。

【符号の説明】

【0037】

10、20、200 基板

11 電気回路

12、22 接続部材

13 ザグリ部

14、24 トレイ

15、25 電子素子

111、211 マウント部

210 キャビティ

220 搭載パッド

【特許請求の範囲】

【請求項1】

電気回路に接続するための端子部を有する電子素子を形成する工程と、

前記電子素子を配列するための複数のザグリ部を有するトレイを準備する工程と、

前記複数のザグリ部に前記電子素子を各々配置する工程と、

前記複数のザグリ部に各々配置された前記電子素子に相対するように複数の電気回路を形成した平板状の基板を準備する工程と、

前記電気回路が有するマウント部に前記電子素子を固着するための接続部材を一括で形成する工程と、

前記電気回路の前記マウント部に形成した前記接続部材に対して、前記電子素子の前記端子部を相対させて、前記トレイに配列した複数の前記電子素子と前記基板とを一括で固着する工程を有することを特徴とする電子素子のマウント方法。

【請求項2】

電気回路に接続するための端子部を有する電子素子を形成する工程と、

前記電子素子を配列するための複数のザグリ部を有するトレイを準備する工程と、

前記複数のザグリ部に電子素子を各々配置する工程と、

前記複数のザグリ部に各々配置された電子素子に相対するように複数の電気回路を形成した平板状の基板を準備する工程と、

前記ザグリ部に配置された各々の前記電子素子の前記端子部に一括で接続部材を形成する工程と、

前記電気回路が有するマウント部に対して、前記電子素子の前記端子部に形成した前記接続部材を相対させて、前記トレイに配列した複数の前記電子素子と前記基板とを一括で固着する工程を有することを特徴とする電子素子のマウント方法。

【請求項3】

前記接続部材の材料は、シリコーン系導電性接着剤、エポキシ系導電性接着剤、あるいは金属微粒子を含むペースト材料であることを特徴とする請求項1または2に記載の電子素子のマウント方法。

【請求項4】

前記接続部材を、ヒーターやレーザーなどによる加熱、あるいは紫外線などの光により固化させることで、前記トレイに配列した複数の前記電子素子と前記基板とを固着させることを特徴とする請求項1または2に記載の電子素子のマウント方法。

【請求項5】

前記接続部材を、スクリーン印刷、インクジェットあるいは転写法により形成することを特徴とする請求項1または2に記載の電子素子のマウント方法。

【請求項6】

各々の電子素子の前記端子、および各々の電気回路の前記マウント部は、

それぞれ少なくとも2ヶ所あることを特徴とする請求項1または2に記載の電子素子のマウント方法。

【請求項7】

前記電子素子が圧電振動子であることを特徴とする請求項1から6のいずれか一つに記載の電子素子のマウント方法。

【請求項8】

電気回路が形成される平板状の基板は、

アルミナ、窒化アルミなどのセラミックス、ガラス、あるいはシリコン(Si)などの少なくとも1種類の材料から成ることを特徴とする請求項1から6のいずれか一つに記載の電子素子のマウント方法。

【請求項1】

電気回路に接続するための端子部を有する電子素子を形成する工程と、

前記電子素子を配列するための複数のザグリ部を有するトレイを準備する工程と、

前記複数のザグリ部に前記電子素子を各々配置する工程と、

前記複数のザグリ部に各々配置された前記電子素子に相対するように複数の電気回路を形成した平板状の基板を準備する工程と、

前記電気回路が有するマウント部に前記電子素子を固着するための接続部材を一括で形成する工程と、

前記電気回路の前記マウント部に形成した前記接続部材に対して、前記電子素子の前記端子部を相対させて、前記トレイに配列した複数の前記電子素子と前記基板とを一括で固着する工程を有することを特徴とする電子素子のマウント方法。

【請求項2】

電気回路に接続するための端子部を有する電子素子を形成する工程と、

前記電子素子を配列するための複数のザグリ部を有するトレイを準備する工程と、

前記複数のザグリ部に電子素子を各々配置する工程と、

前記複数のザグリ部に各々配置された電子素子に相対するように複数の電気回路を形成した平板状の基板を準備する工程と、

前記ザグリ部に配置された各々の前記電子素子の前記端子部に一括で接続部材を形成する工程と、

前記電気回路が有するマウント部に対して、前記電子素子の前記端子部に形成した前記接続部材を相対させて、前記トレイに配列した複数の前記電子素子と前記基板とを一括で固着する工程を有することを特徴とする電子素子のマウント方法。

【請求項3】

前記接続部材の材料は、シリコーン系導電性接着剤、エポキシ系導電性接着剤、あるいは金属微粒子を含むペースト材料であることを特徴とする請求項1または2に記載の電子素子のマウント方法。

【請求項4】

前記接続部材を、ヒーターやレーザーなどによる加熱、あるいは紫外線などの光により固化させることで、前記トレイに配列した複数の前記電子素子と前記基板とを固着させることを特徴とする請求項1または2に記載の電子素子のマウント方法。

【請求項5】

前記接続部材を、スクリーン印刷、インクジェットあるいは転写法により形成することを特徴とする請求項1または2に記載の電子素子のマウント方法。

【請求項6】

各々の電子素子の前記端子、および各々の電気回路の前記マウント部は、

それぞれ少なくとも2ヶ所あることを特徴とする請求項1または2に記載の電子素子のマウント方法。

【請求項7】

前記電子素子が圧電振動子であることを特徴とする請求項1から6のいずれか一つに記載の電子素子のマウント方法。

【請求項8】

電気回路が形成される平板状の基板は、

アルミナ、窒化アルミなどのセラミックス、ガラス、あるいはシリコン(Si)などの少なくとも1種類の材料から成ることを特徴とする請求項1から6のいずれか一つに記載の電子素子のマウント方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2012−222368(P2012−222368A)

【公開日】平成24年11月12日(2012.11.12)

【国際特許分類】

【出願番号】特願2011−82358(P2011−82358)

【出願日】平成23年4月4日(2011.4.4)

【出願人】(000166948)シチズンファインテックミヨタ株式会社 (438)

【出願人】(000001960)シチズンホールディングス株式会社 (1,939)

【Fターム(参考)】

【公開日】平成24年11月12日(2012.11.12)

【国際特許分類】

【出願日】平成23年4月4日(2011.4.4)

【出願人】(000166948)シチズンファインテックミヨタ株式会社 (438)

【出願人】(000001960)シチズンホールディングス株式会社 (1,939)

【Fターム(参考)】

[ Back to top ]