電子素子及びその製造方法

【課題】素子性能の低下が抑制される電子素子を提供する。

【解決手段】基板12と、前記基板上の動作領域に配置された第1導電層14Gと、前記第1導電層上に該第1導電層と接して配置された絶縁層16と、前記基板上の非動作領域で前記絶縁層下に該絶縁層と接して配置され、前記絶縁層の亀裂30の発生を誘導する亀裂誘導部であって、前記第1導電層上の前記絶縁層よりも該亀裂誘導部上の前記絶縁層に亀裂を優先的に発生させる亀裂誘導部22と、を有する電子素子10。

【解決手段】基板12と、前記基板上の動作領域に配置された第1導電層14Gと、前記第1導電層上に該第1導電層と接して配置された絶縁層16と、前記基板上の非動作領域で前記絶縁層下に該絶縁層と接して配置され、前記絶縁層の亀裂30の発生を誘導する亀裂誘導部であって、前記第1導電層上の前記絶縁層よりも該亀裂誘導部上の前記絶縁層に亀裂を優先的に発生させる亀裂誘導部22と、を有する電子素子10。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子素子及びその製造方法に関するものである。

【背景技術】

【0002】

従来、シリコンに代表される無機材料が広くデバイスに応用されてきたが、有機材料を用いた薄膜トランジスタ等を含む電子素子はフレキシブルディスプレイや電子ペーパー等への応用から注目され、盛んに研究がされている。

【0003】

特許文献1には、半導体基板の表面にアイソレーション溝を形成する第1工程と、スピンコーティング法により過水素化シラザン重合体溶液を前記半導体基板の表面に直接または他の膜を介して塗布し、前記アイソレーション溝の内部を埋設する過水素化シラザン重合体溶液の塗膜を形成する第2工程と、前記過水素化シラザン重合体の塗膜を化学反応させて酸化シリコン膜を形成する第3工程と、前記酸化シリコン膜を選択的に除去してその酸化シリコン膜の前記アイソレーション溝の内部に埋設された部分を残す第4工程とを備え、前記酸化シリコン膜の前記アイソレーション溝の内部に埋設された部分が、トレンチ・アイソレーション構造のアイソレーション用絶縁物として機能するようにしたことを特徴とするトレンチ・アイソレーション構造の形成方法が開示されている。

【0004】

非特許文献1には、ペンタセンを半導体層とし、ポリシラザン膜をゲート絶縁層として用いた薄膜トランジスタが開示されている。

非特許文献2には、薄膜トランジスタ(TFT)のゲート絶縁層に用いる酸化シリコン膜として、シラザンを含む溶液をスピンコーティング法によって塗布した後、シラザン薄膜とオゾンを反応させることにより100℃以下で酸化シリコン膜を得る技術が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平11−307626号公報

【非特許文献】

【0006】

【非特許文献1】M.Kawasakiら、SID 06 DIGEST 第200頁〜第203頁

【非特許文献2】産業技術総合研究所 プレスリリース 「高品質SiO2絶縁膜を塗布法により100℃以下で作製する技術を開発」 2004年8月30日発表、インターネット<http://www.aist.go.jp/aist_j/press_release/pr2004/pr20040830/pr20040830.html>

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明は、素子性能の低下が抑制される電子素子を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記課題は、以下の手段により解決される。

請求項1に係る発明は、

基板と、

前記基板上の動作領域に配置された第1導電層と、

前記第1導電層上に該第1導電層と接して配置された絶縁層と、

前記基板上の非動作領域で前記絶縁層下に該絶縁層と接して配置され、前記絶縁層の亀裂の発生を誘導する亀裂誘導部であって、前記第1導電層上の前記絶縁層よりも該亀裂誘導部上の前記絶縁層に亀裂を優先的に発生させる亀裂誘導部と、

を有する電子素子である。

請求項2に係る発明は、

前記第1導電層が配置された動作領域の前記絶縁層上に該絶縁層と接して配置された第2導電層を有する請求項1に記載の電子素子である。

請求項3に係る発明は、

前記基板上に、ゲート電極と、ゲート絶縁層と、ソース電極と、ドレイン電極と、半導体層と、を備え、前記第1導電層及び前記第2導電層の一方が前記ゲート電極であり、他方が前記ソース電極及び前記ドレイン電極であり、前記絶縁層が前記ゲート絶縁層である請求項2に記載の電子素子である。

請求項4に係る発明は、

前記亀裂誘導部が、下記(1)〜(4)の少なくとも1つを満たす請求項1〜請求項3のいずれか一項に記載の電子素子である。

(1)前記亀裂誘導部の面積が、前記第1導電層の面積よりも大きい。

(2)前記亀裂誘導部の表面が、前記第1導電層の表面よりも疎水性である。

(3)前記亀裂誘導部の表面粗さが、前記第1導電層の表面粗さよりも大きい。

(4)前記亀裂誘導部の厚みが、前記第1導電層の厚みよりも大きい。

請求項5に係る発明は、

前記絶縁層がポリシラザンから形成されたものである請求項1〜請求項4のいずれか一項に記載の電子素子である。

請求項6に係る発明は、

基板上の動作領域に第1導電層を形成する第1導電層形成工程と、

前記基板上の非動作領域に配置される亀裂誘導部であって、該亀裂誘導部と前記第1導電層上に絶縁層を形成したときに、該亀裂誘導部上の前記絶縁層に前記第1導電層上の前記絶縁層よりも優先的に亀裂を生じさせる亀裂誘導部を形成する亀裂誘導部形成工程と、

前記第1導電層と前記亀裂誘導部上に前記絶縁層を形成するための塗布液を付与して塗膜を形成した後、該塗膜を乾燥させて前記絶縁層を形成する絶縁層形成工程と、

を有する電子素子の製造方法である。

請求項7に係る発明は、

前記絶縁層形成工程は、前記塗布液としてポリシラザンを含む溶液を用いる請求項6に記載の電子素子の製造方法である。

請求項8に係る発明は、

前記絶縁層形成工程の後に、前記絶縁層を緻密化する処理を施す緻密化処理工程を有する請求項6又は請求項7に記載の電子素子の製造方法である。

【発明の効果】

【0009】

請求項1〜5に係る発明によれば、本構成を有さない場合に比べ、素子性能の低下が抑制される電子素子が提供される。

請求項6〜8に係る発明によれば、本構成を有さない場合に比べ、素子性能の低下が抑制される電子素子の製造方法が提供される。

【図面の簡単な説明】

【0010】

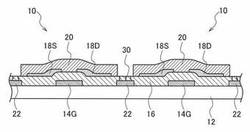

【図1】本実施形態に係る電子素子の一例(薄膜トランジスタ)を模式的に示す概略図である。

【図2】本実施形態に係る電子素子の他の例(薄膜トランジスタ)を模式的に示す概略図である。

【図3】実施例で形成した第1導電層と亀裂誘導部の配置と導電層に生じた亀裂の方向を概略的に示す図である。

【図4】実施例で亀裂誘導部の表面を観察した顕微鏡写真である。

【図5】実施例で第1導電層の表面を観察した顕微鏡写真である。

【図6】従来の薄膜トランジスタのゲート絶縁層に生じる亀裂を模式的に示す概略図である。

【発明を実施するための形態】

【0011】

本実施形態について図面を参照しつつ詳細に説明する。なお、同一の機能を有する部材には、全図面を通して同じ符号を付与し、重複する説明は省略する場合がある。

【0012】

本実施形態に係る電子素子は、基板と、前記基板上の動作領域に配置された第1導電層と、前記第1導電層上に該第1導電層と接して配置された絶縁層と、前記基板上の非動作領域で前記絶縁層下に該絶縁層と接して配置され、前記絶縁層の亀裂の発生を誘導する亀裂誘導部であって、前記第1導電層上の前記絶縁層よりも該亀裂誘導部上の前記絶縁層に亀裂を優先的に発生させる亀裂誘導部と、を有する。

【0013】

図1は、本実施形態の電子素子の一例として、薄膜トランジスタ(TFT)を概略的に示している。本実施形態に係るTFT10は、いわゆるボトムゲート型であり、基板12上の動作領域には、第1導電層としてゲート電極14G、絶縁層としてゲート絶縁層16、第2導電層としてソース電極18S及びドレイン電極18D、及び半導体層20がこの順に設けられている。

【0014】

一方、TFT10の非動作領域には、絶縁層16に亀裂(「クラック」とも呼ばれる場合がある)を発生させる亀裂誘導部22が配置されている。亀裂誘導部22は、TFT10と接触せずに、ゲート電極14Gとともに基板12上に形成されている。ゲート絶縁層16はゲート電極14Gと亀裂誘導部22に接し、ゲート電極14Gと亀裂誘導部22を覆い、さらにこれらの層14G,22が形成されていない領域では基板12と接するように一体的に形成されている。

【0015】

なお、本実施形態において、「動作領域」とは、基板上の領域のうち、TFT10のほか、キャパシタ、ゲートラインなど、装置の駆動に寄与する素子が基板上に形成されている領域を意味し、「非動作領域」とは、動作領域以外の領域を意味する。

【0016】

上記のような亀裂誘導部22が存在しない場合、図6に示すように、ゲート絶縁層16にランダムに亀裂30が生じ易く、ゲート電極14G表面と基板12表面との濡れ性の違いからゲート電極14G上の絶縁層16に亀裂30が生じ易い場合もある。ゲート電極14G上のゲート絶縁層16に亀裂30が生じると、ゲート電極14Gとソース電極18S及びドレイン電極18Dとの間で絶縁性が低下し、リーク電流が発生するなど素子性能が低下してしまう。また、ゲート絶縁層16にランダムに亀裂30が生じるため、TFT間の素子性能のばらつきも大きくなりやすい。

【0017】

一方、本実施形態に係るTFT10では、非動作領域でゲート絶縁層16下に亀裂誘導部22がゲート絶縁層16と接して配置されていることで、ゲート絶縁層16におけるランダムな亀裂30の発生が抑制され、亀裂誘導部22上のゲート絶縁層16に優先的に亀裂が生じる。これにより、ゲート絶縁層全体としての歪みが解消されるため、ゲート電極14G上のゲート絶縁層16に亀裂30が生じることが抑制され、結果的に素子性能の低下が抑制されると考えられる。

【0018】

以下、本実施形態に係る電子素子の各構成について、製造方法とともに説明する。

本実施形態に係る電子素子を製造する方法は限定されないが、有機トランジスタを作製する場合は、例えば、第1導電層から絶縁層までは、以下の工程、すなわち、

基板上の動作領域に第1導電層を形成する第1導電層形成工程と、

前記基板上の非動作領域に配置される亀裂誘導部であって、該亀裂誘導部と前記第1導電層上に絶縁層を形成したときに、該亀裂誘導部上の前記絶縁層に前記第1導電層上の前記絶縁層よりも優先的に亀裂を生じさせる亀裂誘導部を形成する亀裂誘導部形成工程と、

前記第1導電層と前記亀裂誘導部上に前記絶縁層を形成するための塗布液を付与して塗膜を形成した後、該塗膜を乾燥させて前記絶縁層を形成する絶縁層形成工程と、によって好適に形成される。

また、絶縁層形成工程の後に、前記絶縁層を緻密化する処理を施す緻密化処理工程を行ってもよい。

【0019】

<第1導電層形成工程>

まず、基板12上の動作領域に第1導電層を形成する。本実施形態では第1導電層としてゲート電極14Gを形成する。

【0020】

‐基板‐

基板12としては、シリコン単結晶基板(例えばリン等を高濃度にドープしたシリコン単結晶基板等)、ガラス基板、プラスチック基板(例えばポリカーボネート樹脂、ポリエステル樹脂、メタクリル樹脂、アクリル樹脂、ポリ塩化ビニル樹脂、セルロース樹脂、ウレタン樹脂、エポキシ樹脂、ポリススチレン樹脂、ポリビニルアセテート樹脂、スチレンブタジエン共重合体、塩化ビニルデン−アクリロニトリル共重合体、塩化ビニル−酢酸ビニル−無水マレイン酸共重合体、又はシリコン樹脂等)等が挙げられるが、これに限定されるものではない。

【0021】

‐ゲート電極‐

ゲート電極14Gを構成する材料としては、金(Au)等の金属、金属酸化物、導電性高分子等が挙げられる。ゲート電極14Gの形成方法としては、真空蒸着法やスパッタリング法に例示される物理的気相成長法(PVD)法;有機金属化合物化学気相成長法(MOCVD)法を含む各種の化学気相成長法(CVD)法;リフトオフ法;シャドウマスク法;電解メッキ法や無電解メッキ法若しくはこれらの組み合わせとったメッキ法;又は塗布液(液体材料)を塗布する方法として、スピンコーティング法、インクジェット法、スプレー法、エレクトロスプレー法などのうちいずれかと、必要に応じたパターニング技術との組み合わせが挙げられる。

【0022】

<亀裂誘導部形成工程>

電子素子の非動作領域に該当する基板12上に、第1導電層(ゲート電極14G)とは別に亀裂誘導部22を形成する。

【0023】

‐亀裂誘導部‐

亀裂誘導部22は、電子素子の非動作領域で、後工程で形成するゲート絶縁層16下にゲート絶縁層16と接して形成され、ゲート電極14G上のゲート絶縁層16よりも亀裂誘導部22上のゲート絶縁層16に優先的に亀裂を生じさせるように形成する。すなわち、亀裂誘導部22は、後工程でゲート絶縁層16を形成したときに、ゲート電極14G上の絶縁層16よりも亀裂誘導部22上の絶縁層16に亀裂30を生じさせ易い構成とすればよい。なおこのような構成である限り、亀裂誘導部22の配置形態は特に限定されず、ゲート電極14Gと接触して設けられていても、離間して設けられていてもよい。

【0024】

亀裂誘導部22は、例えば、下記(1)〜(4)の少なくとも1つを満たすように構成される。なお、ゲート電極14Gと同じ材料で同時に形成してもよいし、ゲート電極14Gを形成する前又は後に、ゲート電極14Gと同じ材料又は異なる材料で形成してもよい。

(1)亀裂誘導部22の面積が、第1導電層(例えば、ゲート電極14G)の面積よりも大きい。

(2)亀裂誘導部22の表面が、第1導電層(例えば、ゲート電極14G)の表面よりも疎水性である。

(3)亀裂誘導部22の表面粗さが、第1導電層(例えば、ゲート電極14G)の表面粗さよりも大きい。

(4)亀裂誘導部22の厚みが、第1導電層(例えば、ゲート電極14G)の厚みよりも大きい。

【0025】

亀裂誘導部22として使用される材料としては、金属、金属酸化物、導電性高分子、無機絶縁物、有機絶縁物、無機半導体、有機半導体等が挙げられる。

亀裂誘導部22の形成方法としては、真空蒸着法やスパッタリング法に例示される物理的気相成長法(PVD)法、有機金属化合物化学気相成長法(MOCVD)法を含む各種の化学気相成長法(CVD)法、リフトオフ法、シャドウマスク法、電解メッキ法や無電解メッキ法若しくはこれらを組み合わせたメッキ法、又は塗布液(液体材料)を塗布する方法として、スピンコーティング法、インクジェット法、スプレー法、エレクトロスプレー法などのうちいずれかと、必要に応じたパターニング技術との組み合わせが挙げられる。

【0026】

上記(1)の方法では、亀裂誘導部22の面積がゲート電極14Gよりも面積が大きければ良い。望ましくは亀裂誘導部の面積がゲート電極14Gの3倍以上の面積があることが良い。

上記(2)の方法では、ゲート電極14Gよりも亀裂誘導部22が疎水性となるように形成する。方法としては、材料の違いや表面処理による疎水性の違いを利用する。

上記(3)の方法では、ゲート電極14Gよりも亀裂誘導部22の表面粗さが粗くなるようにする。方法としては、作製方法の違いや表面処理による表面粗さの違いを利用する。

上記(4)の方法では、ゲート電極14Gよりも亀裂誘導部22が厚くなるように形成する。

実際の有効性を考慮すると、最も有効な方法から順に(3)、(2)、(1)、(4)の順となる。

【0027】

亀裂誘導部22の配置は、動作領域のゲート絶縁層16に亀裂が入らないように配置すれば、どのような配置でも構わない。例えば、動作領域を囲むような形であっても良い。

亀裂誘導部22の形状はいかなる形状でも良い。

亀裂誘導部22の厚みは特に限定されないが、例えば、10nm以上1μm以下が望ましい。

【0028】

<絶縁層形成工程>

第1導電層(ゲート電極14G)と亀裂誘導部22上に絶縁層16を形成するための塗布液を付与して塗膜を形成した後、該塗膜を乾燥させて絶縁層16を形成する。

【0029】

‐ゲート絶縁層‐

ゲート絶縁層16としては、酸化シリコン膜や、窒化シリコン膜や、ポリイミドのような有機系絶縁膜等が挙げられるが、これに限定されるものではない。

ゲート絶縁層16を形成する方法としては、スピンコーティング法、インクジェット法、スプレー法、エレクトロスプレー法等が挙げられるが、これらに限定されない。

【0030】

半導体素子などの電子素子を作製する際、基板のガラス転移温度以下で行う必要があるが、プラスチック基板のような低ガラス転移温度基板を用いるには、CVD法など基板が高温に曝される方法で酸化シリコン膜等の絶縁膜を作製することが困難であり、低温で形成される酸化シリコン膜が必要とされる。

【0031】

酸化シリコン膜を、溶液法で且つ低温で形成する方法として、ポリシラザンを含む溶液を基板上に塗布し、硬化させる方法があり、さらに絶縁膜としての機能を向上させる手段として、UVオゾン処理を施す方法がある。しかし、ポリシラザンから酸化シリコンに構造が変化する際に、密度変化が大きく、結果的に亀裂が発生してしまう。この亀裂が薄膜トランジスタ(TFT)のチャネル直下にあるときゲートリーク電流の原因となり素子性能を低下させる。

【0032】

しかし、本実施形態では、亀裂誘導部22を設けてあるため、亀裂誘導部22上の絶縁層16に優先的に亀裂30が生じ、絶縁層16にランダムに亀裂30が生じることが抑制され、それによりゲート電極14G上の絶縁層16に亀裂30が生じることが抑制される。本実施形態に係るTFT10では、亀裂誘導部22上の絶縁層16よりもゲート電極14G上の絶縁層16に生じる単位面積あたりの亀裂30の数(本/mm2)が少なく、亀裂誘導部22を形成しない場合に比べ、ゲート電極14G上の絶縁層16における亀裂30の密度が少なく抑えられ、ゲートリーク電流の発生が抑制される。

【0033】

なお、ゲート絶縁層16としての酸化シリコン膜は、CVD法などの気相法によって成膜する方法もあるが、上記のようにポリシラザンを含む溶液を用いて絶縁層を形成した場合は、絶縁層に含まれる未反応のポリシラザン又は残留溶媒を分析することで、気相法によって成膜した酸化シリコン膜から区別される。

【0034】

<緻密化処理工程>

本実施形態では、絶縁層形成工程の後に、前記絶縁層を緻密化する処理を施す緻密化処理工程を有していてもよい。

緻密化処理としては、UVオゾン処理、加熱処理等が挙げられる。緻密化処理を行うことで、ゲート絶縁層16全体が緻密化される。その影響で、一般的にはゲート絶縁層16には亀裂が発生しやすい状態となる。本実施形態では、より亀裂の入りやすい状態となる緻密化処理を行っても、動作領域のゲート絶縁層16に亀裂が入ることが抑制される。

【0035】

<第2導電層形成工程>

ゲート絶縁層16を形成した後、第2導電層として、ソース電極18S及びドレイン電極18D(ソース・ドレイン電極18S,18D)を形成する。

【0036】

‐ソース電極及びドレイン電極‐

ソース電極18S及びドレイン電極18Dを構成する材料としては、上述したゲート電極14Gを構成する材料が挙げられる。また、このソース電極18S及びドレイン電極18Dの形成方法についても上述したゲート電極14Gの形成方法として挙げた方法が用いられる。

【0037】

<半導体層形成工程>

次いで、ソース・ドレイン電極18S,18D上のチャネル領域に半導体層20を形成する。

【0038】

‐半導体層‐

半導体層20の構成材料としては、公知の半導体材料が挙げられる。具体的には、トリエチルシリルエチニルアントラジチオフェン(TES ADT)、ペンタセン、テトラセン、アントラセン、ナフタレン、α−6−チオフェン、ペリレン及びその誘導体、ルブレン及びその誘導体、コロネン及びその誘導体、ペリレンテトラカルボン酸ジイミド及びその誘導体、ペリレンテトラカルボン酸二無水物及びその誘導体、ポリチオフェン及びその誘導体、ポリパラフェニレンビニレン及びその誘導体、ポリパラフェニレン及びその誘導体、ポリフロレン及びその誘導体、ポリフロレン−オリゴチオフェンの共重合体及びその誘導体、ポリチオフェンビニレン及びその誘導体、ポリチオフェン−複素環芳香族共重合体及びその誘導体、ナフタレンのオリゴアセン及びその誘導体、α−5−チオフェンのオリゴチオフェン及びその誘導体、含金属または非含金属のフタロシアニン及びその誘導体、ピロメリト酸二無水物及びその誘導体、ピロメリト酸ジイミド及びその誘導体、ペリレンテトラカルボン酸二無水物及びその誘導体、ペリレンテトラカルボン酸ジイミド及びその誘導体、ナフタレンテトラカルボン酸ジイミド及びその誘導体、ならびにナフタレンテトラカルボン酸二無水物及びその誘導体等が挙げられる。

これらの中でも、結晶性の理由から、TES−ADTを用いることが好ましい。

【0039】

半導体材料を含む塗布液を用いて半導体層20を形成する場合には、この塗布液としては、半導体層20の構成材料として選択した半導体材料と、該半導体材料を溶解する溶媒と、を含む塗布液を用いればよい。

この塗布液に含まれる溶媒としては、半導体材料を溶解する液体を用いればよく、半導体層20の構成材料として選択した半導体材料に応じて選択すればよいが、例えば、トルエン、無機溶媒(硝酸、硫酸、アンモニア、過酸化水素、二硫化炭素、四塩化炭素、又はエチレンカーボネート等)、ケトン系溶媒(メチルエチルケトン、アセトン、ジエチルケトン、メチルイソブチルケトン、メチルイソプロピルケトン、又はジクロヘキサノン等)、アルコール系溶媒(メタノール、エタノール、イソプロパノール、エチレングリコール、ジエチレングリコール、又はグリセリン等)、エーテル系溶媒(ジエチルエーテル、ジイソプロピルエーテル、テトラヒドロフラン、ジオキサン、アニソール、ジエチレングリコールジメチルエーテル、又はジエチレングリコールエチルエーテル等)、セロソルブ系溶媒(メリルセロソブル、エチルセロソルブ、又はフェニルセロソルブ等)、脂肪族炭化水素系溶媒(ヘキサン、ヘプタン、ペンタン、ヘプタン、又はシクロヘキサン等)、芳香族炭化水素系溶媒(トルエン、キシレン、又はベンゼン等)、アミド系溶媒(ピリジン、ピラジン、フラン、ピロール、又はアミド等)、ハロゲン化合物系溶媒(モノクロロベンゼン、ジクロロメタン、クロロホルム、又は1,2−ジクロロエタン等)、エステル系溶媒(酢酸エチル、酢酸メチル、又はギ酸エチル等)、硫黄化合物系溶媒(ジメチルスルホキシド、又はスルホラン等)、ニトリル系溶媒(アセトニトリル、プロピオニトリル、又はアクリロニトリル等)、有機酸系溶媒(ギ酸、酢酸、トリクロロ酢酸、又はトリフルオロ酢酸等)の如く各種有機溶媒、又は、これらを含む混合溶媒などが挙げられるが、これに限るものではない。

【0040】

そして、半導体材料を含む塗布液を塗布することによって、半導体層20を形成する。この塗布法としては、例えば、スピンコーティング法、インクジェット法、スプレー法、エレクトロスプレー法などが挙げられる。

半導体層20を形成することで、TFT10が完成する。

【0041】

例えば、図1に示す例では、ソース電極18S及びドレイン電極18Dが、ソース電極18S及びドレイン電極18Dの基板12とは反対側の面で半導体層20に接する構成である場合を説明したが、本実施形態では、ソース電極18S及びドレイン電極18Dが、ソース電極18S及びドレイン電極18Dの基板12側の面で半導体層20に接する構成であってもよい。

この場合には、基板12上に、ゲート電極14Gと、ゲート絶縁層16と、半導体層20と、ソース電極18S及びドレイン電極18Dと、がこの順に設けられた構成とすればよい。

【0042】

また、図1に示す例では、ゲート電極14Gがソース電極18S及びドレイン電極18Dより基板12側に設けられた構成、所謂、ボトムゲート構造のTFTについて説明したが、ソース電極18S及びドレイン電極18Dがゲート電極14Gより基板12側に設けられた構成(所謂、トップゲート構造)であってもよい。

例えば、図2に示すように、基板12上に、半導体層20と、ソース電極18S及びドレイン電極18Dと、ゲート絶縁層16と、ゲート電極14Gと、をこの順に設けた構成のTFT11とした場合、ソース電極18S及びドレイン電極18Dが第1導電層、ゲート電極14Gが第2導電層となる。そして、ソース・ドレイン電極18S,18Dとは別に基板12上の非動作領域に亀裂誘導部22を設けることで、ソース・ドレイン電極18S,18D上のゲート絶縁層16に亀裂30が発生することが抑制される。

なお、トップゲート構造の場合、ソース電極18S及びドレイン電極18Dが、ソース電極18S及びドレイン電極18Dの基板12側とは反対側の面で半導体層20に接する構成であってもよい。

【0043】

また、本実施形態のTFT10又はTFT11を用いて、何らかの電子装置を作製する場合には、さらに他の素子や回路等を組み合わせてもよい。

【0044】

また、上記実施形態では、電子素子としてTFTを形成する場合について説明したが、本実施形態の亀裂誘導部22は、キャパシタを形成する場合にも適用される。例えば、キャパシタの下部電極を形成する際、非動作領域に亀裂誘導部22を形成し、その後、絶縁層(誘電層)、上部電極を形成する。これにより、キャパシタの上下電極間の絶縁層に亀裂が生じることが抑制される。

【0045】

また、本実施形態における亀裂誘導部22は、層間絶縁膜を形成する場合にも適用される。例えば、図2に示す形態のTFT11を形成した後、ゲート絶縁層16上の動作領域にゲート電極14Gを、非動作領域に亀裂誘導部22を形成する。次いで、層間絶縁膜を形成した後、層間絶縁膜に設けたコンタクトホールを通じて画素電極とソース・ドレイン電極を配線により電気的に接続する。これにより、亀裂誘導部上の層間絶縁膜に優先的に亀裂を生じさせ、層間絶縁膜上に形成された配線(図示せず)下の層間絶縁膜に亀裂が発生することが抑制されることになる。

【実施例】

【0046】

以下実施例によって本発明を説明する。なお、本発明はこれらの実施例によってのみ限定されるものではない。

【0047】

以下に示す如く、有機トランジスタを作製した。

【0048】

(実施例1)

図1に示す構成の有機トランジスタを作製した。

‐ゲート電極及び亀裂誘導部の形成‐

まず、ガラス基板の片面上に、スパッタリング装置(昭和真空製イオンビームスパッタリング装置)を用いてAuの蒸着膜を形成し、フォトリソグラフィー法によって、図3に示す位置関係で、ゲート電極14G(厚さ:200nm)と、亀裂誘導部22(厚さ:500nm)をそれぞれ形成した。ゲート電極と亀裂誘導部との間の距離は500nmとした。

【0049】

‐ゲート絶縁層の形成‐

次いで、ガラス基板のゲート電極と亀裂誘導部を形成した側の面に、ポリシラザン溶液をスピンコート法により塗布した後、ホットプレートによって100℃、30分間のアニールを施した。これにより酸化シリコン膜16を形成した。

さらに酸化シリコン膜の緻密化のため、UVオゾン処理装置を用い、100℃でUVオゾン処理を行なった。

【0050】

‐ソース電極及びドレイン電極の形成‐

フォトリソグラフィー法により、酸化シリコン膜上にソース・ドレイン電極18S,18Dを形成した。具体的には、Auを電極材料として用い、膜厚は100nmとした。また、ソース電極及びドレイン電極の電極間の距離(チャネル幅)は1000μmとし、チャネル長は20μmとした。ソース・ドレイン電極の形成にはスパッタリング装置(昭和真空製イオンビームスパッタリング装置)により、メタルマスクを用いた。

【0051】

‐半導体層の形成‐

ソース・ドレイン電極を形成した後、半導体層を形成した。具体的には、ガラス基板のソース・ドレイン電極を形成した面上に、TES−DTAをトルエン溶媒中に2質量%の濃度で溶かした溶液を滴下し、スピンコート塗布することによって、有機半導体膜(厚み0.1μm)を形成した。

以上の工程を経て、ボトムゲート型の有機薄膜トランジスタを製造した。

【0052】

上記工程において、ゲート絶縁層を形成し、緻密化した後のゲート電極上の酸化シリコン膜と亀裂誘導部上の酸化シリコン膜をそれぞれ光学顕微鏡で観察した。

図4に示すように、亀裂誘導部上の酸化シリコン膜には複数の亀裂が確認された。一方、図5に示すように、ゲート電極上の酸化シリコン膜には亀裂は確認されなかった。

【0053】

(実施例2)

実施例1においてゲート電極を形成した後、亀裂誘導部を形成したこと以外は実施例1と同様にしてTFTを形成した。

上記工程において、ゲート絶縁層を形成し、緻密化した後のゲート電極上の酸化シリコン膜と亀裂誘導部上の酸化シリコン膜をそれぞれ電子顕微鏡で観察したところ、亀裂誘導部上の絶縁層には複数の亀裂が確認されたが、ゲート電極上の絶縁層には亀裂は確認されなかった。

【0054】

(比較例1)

実施例1において亀裂誘導部を形成しなかったこと以外は実施例1と同様にしてTFTを形成した。

上記工程において、ゲート絶縁層を形成し、緻密化した後のゲート電極上の酸化シリコン膜を電子顕微鏡で観察したところ、ゲート電極上の絶縁層に複数の亀裂が確認された。

【符号の説明】

【0055】

10、11 薄膜トランジスタ,12 基板,14G ゲート電極,18S ソース電極,18D ドレイン電極,20 半導体層,22 亀裂誘導部

【技術分野】

【0001】

本発明は、電子素子及びその製造方法に関するものである。

【背景技術】

【0002】

従来、シリコンに代表される無機材料が広くデバイスに応用されてきたが、有機材料を用いた薄膜トランジスタ等を含む電子素子はフレキシブルディスプレイや電子ペーパー等への応用から注目され、盛んに研究がされている。

【0003】

特許文献1には、半導体基板の表面にアイソレーション溝を形成する第1工程と、スピンコーティング法により過水素化シラザン重合体溶液を前記半導体基板の表面に直接または他の膜を介して塗布し、前記アイソレーション溝の内部を埋設する過水素化シラザン重合体溶液の塗膜を形成する第2工程と、前記過水素化シラザン重合体の塗膜を化学反応させて酸化シリコン膜を形成する第3工程と、前記酸化シリコン膜を選択的に除去してその酸化シリコン膜の前記アイソレーション溝の内部に埋設された部分を残す第4工程とを備え、前記酸化シリコン膜の前記アイソレーション溝の内部に埋設された部分が、トレンチ・アイソレーション構造のアイソレーション用絶縁物として機能するようにしたことを特徴とするトレンチ・アイソレーション構造の形成方法が開示されている。

【0004】

非特許文献1には、ペンタセンを半導体層とし、ポリシラザン膜をゲート絶縁層として用いた薄膜トランジスタが開示されている。

非特許文献2には、薄膜トランジスタ(TFT)のゲート絶縁層に用いる酸化シリコン膜として、シラザンを含む溶液をスピンコーティング法によって塗布した後、シラザン薄膜とオゾンを反応させることにより100℃以下で酸化シリコン膜を得る技術が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平11−307626号公報

【非特許文献】

【0006】

【非特許文献1】M.Kawasakiら、SID 06 DIGEST 第200頁〜第203頁

【非特許文献2】産業技術総合研究所 プレスリリース 「高品質SiO2絶縁膜を塗布法により100℃以下で作製する技術を開発」 2004年8月30日発表、インターネット<http://www.aist.go.jp/aist_j/press_release/pr2004/pr20040830/pr20040830.html>

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明は、素子性能の低下が抑制される電子素子を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記課題は、以下の手段により解決される。

請求項1に係る発明は、

基板と、

前記基板上の動作領域に配置された第1導電層と、

前記第1導電層上に該第1導電層と接して配置された絶縁層と、

前記基板上の非動作領域で前記絶縁層下に該絶縁層と接して配置され、前記絶縁層の亀裂の発生を誘導する亀裂誘導部であって、前記第1導電層上の前記絶縁層よりも該亀裂誘導部上の前記絶縁層に亀裂を優先的に発生させる亀裂誘導部と、

を有する電子素子である。

請求項2に係る発明は、

前記第1導電層が配置された動作領域の前記絶縁層上に該絶縁層と接して配置された第2導電層を有する請求項1に記載の電子素子である。

請求項3に係る発明は、

前記基板上に、ゲート電極と、ゲート絶縁層と、ソース電極と、ドレイン電極と、半導体層と、を備え、前記第1導電層及び前記第2導電層の一方が前記ゲート電極であり、他方が前記ソース電極及び前記ドレイン電極であり、前記絶縁層が前記ゲート絶縁層である請求項2に記載の電子素子である。

請求項4に係る発明は、

前記亀裂誘導部が、下記(1)〜(4)の少なくとも1つを満たす請求項1〜請求項3のいずれか一項に記載の電子素子である。

(1)前記亀裂誘導部の面積が、前記第1導電層の面積よりも大きい。

(2)前記亀裂誘導部の表面が、前記第1導電層の表面よりも疎水性である。

(3)前記亀裂誘導部の表面粗さが、前記第1導電層の表面粗さよりも大きい。

(4)前記亀裂誘導部の厚みが、前記第1導電層の厚みよりも大きい。

請求項5に係る発明は、

前記絶縁層がポリシラザンから形成されたものである請求項1〜請求項4のいずれか一項に記載の電子素子である。

請求項6に係る発明は、

基板上の動作領域に第1導電層を形成する第1導電層形成工程と、

前記基板上の非動作領域に配置される亀裂誘導部であって、該亀裂誘導部と前記第1導電層上に絶縁層を形成したときに、該亀裂誘導部上の前記絶縁層に前記第1導電層上の前記絶縁層よりも優先的に亀裂を生じさせる亀裂誘導部を形成する亀裂誘導部形成工程と、

前記第1導電層と前記亀裂誘導部上に前記絶縁層を形成するための塗布液を付与して塗膜を形成した後、該塗膜を乾燥させて前記絶縁層を形成する絶縁層形成工程と、

を有する電子素子の製造方法である。

請求項7に係る発明は、

前記絶縁層形成工程は、前記塗布液としてポリシラザンを含む溶液を用いる請求項6に記載の電子素子の製造方法である。

請求項8に係る発明は、

前記絶縁層形成工程の後に、前記絶縁層を緻密化する処理を施す緻密化処理工程を有する請求項6又は請求項7に記載の電子素子の製造方法である。

【発明の効果】

【0009】

請求項1〜5に係る発明によれば、本構成を有さない場合に比べ、素子性能の低下が抑制される電子素子が提供される。

請求項6〜8に係る発明によれば、本構成を有さない場合に比べ、素子性能の低下が抑制される電子素子の製造方法が提供される。

【図面の簡単な説明】

【0010】

【図1】本実施形態に係る電子素子の一例(薄膜トランジスタ)を模式的に示す概略図である。

【図2】本実施形態に係る電子素子の他の例(薄膜トランジスタ)を模式的に示す概略図である。

【図3】実施例で形成した第1導電層と亀裂誘導部の配置と導電層に生じた亀裂の方向を概略的に示す図である。

【図4】実施例で亀裂誘導部の表面を観察した顕微鏡写真である。

【図5】実施例で第1導電層の表面を観察した顕微鏡写真である。

【図6】従来の薄膜トランジスタのゲート絶縁層に生じる亀裂を模式的に示す概略図である。

【発明を実施するための形態】

【0011】

本実施形態について図面を参照しつつ詳細に説明する。なお、同一の機能を有する部材には、全図面を通して同じ符号を付与し、重複する説明は省略する場合がある。

【0012】

本実施形態に係る電子素子は、基板と、前記基板上の動作領域に配置された第1導電層と、前記第1導電層上に該第1導電層と接して配置された絶縁層と、前記基板上の非動作領域で前記絶縁層下に該絶縁層と接して配置され、前記絶縁層の亀裂の発生を誘導する亀裂誘導部であって、前記第1導電層上の前記絶縁層よりも該亀裂誘導部上の前記絶縁層に亀裂を優先的に発生させる亀裂誘導部と、を有する。

【0013】

図1は、本実施形態の電子素子の一例として、薄膜トランジスタ(TFT)を概略的に示している。本実施形態に係るTFT10は、いわゆるボトムゲート型であり、基板12上の動作領域には、第1導電層としてゲート電極14G、絶縁層としてゲート絶縁層16、第2導電層としてソース電極18S及びドレイン電極18D、及び半導体層20がこの順に設けられている。

【0014】

一方、TFT10の非動作領域には、絶縁層16に亀裂(「クラック」とも呼ばれる場合がある)を発生させる亀裂誘導部22が配置されている。亀裂誘導部22は、TFT10と接触せずに、ゲート電極14Gとともに基板12上に形成されている。ゲート絶縁層16はゲート電極14Gと亀裂誘導部22に接し、ゲート電極14Gと亀裂誘導部22を覆い、さらにこれらの層14G,22が形成されていない領域では基板12と接するように一体的に形成されている。

【0015】

なお、本実施形態において、「動作領域」とは、基板上の領域のうち、TFT10のほか、キャパシタ、ゲートラインなど、装置の駆動に寄与する素子が基板上に形成されている領域を意味し、「非動作領域」とは、動作領域以外の領域を意味する。

【0016】

上記のような亀裂誘導部22が存在しない場合、図6に示すように、ゲート絶縁層16にランダムに亀裂30が生じ易く、ゲート電極14G表面と基板12表面との濡れ性の違いからゲート電極14G上の絶縁層16に亀裂30が生じ易い場合もある。ゲート電極14G上のゲート絶縁層16に亀裂30が生じると、ゲート電極14Gとソース電極18S及びドレイン電極18Dとの間で絶縁性が低下し、リーク電流が発生するなど素子性能が低下してしまう。また、ゲート絶縁層16にランダムに亀裂30が生じるため、TFT間の素子性能のばらつきも大きくなりやすい。

【0017】

一方、本実施形態に係るTFT10では、非動作領域でゲート絶縁層16下に亀裂誘導部22がゲート絶縁層16と接して配置されていることで、ゲート絶縁層16におけるランダムな亀裂30の発生が抑制され、亀裂誘導部22上のゲート絶縁層16に優先的に亀裂が生じる。これにより、ゲート絶縁層全体としての歪みが解消されるため、ゲート電極14G上のゲート絶縁層16に亀裂30が生じることが抑制され、結果的に素子性能の低下が抑制されると考えられる。

【0018】

以下、本実施形態に係る電子素子の各構成について、製造方法とともに説明する。

本実施形態に係る電子素子を製造する方法は限定されないが、有機トランジスタを作製する場合は、例えば、第1導電層から絶縁層までは、以下の工程、すなわち、

基板上の動作領域に第1導電層を形成する第1導電層形成工程と、

前記基板上の非動作領域に配置される亀裂誘導部であって、該亀裂誘導部と前記第1導電層上に絶縁層を形成したときに、該亀裂誘導部上の前記絶縁層に前記第1導電層上の前記絶縁層よりも優先的に亀裂を生じさせる亀裂誘導部を形成する亀裂誘導部形成工程と、

前記第1導電層と前記亀裂誘導部上に前記絶縁層を形成するための塗布液を付与して塗膜を形成した後、該塗膜を乾燥させて前記絶縁層を形成する絶縁層形成工程と、によって好適に形成される。

また、絶縁層形成工程の後に、前記絶縁層を緻密化する処理を施す緻密化処理工程を行ってもよい。

【0019】

<第1導電層形成工程>

まず、基板12上の動作領域に第1導電層を形成する。本実施形態では第1導電層としてゲート電極14Gを形成する。

【0020】

‐基板‐

基板12としては、シリコン単結晶基板(例えばリン等を高濃度にドープしたシリコン単結晶基板等)、ガラス基板、プラスチック基板(例えばポリカーボネート樹脂、ポリエステル樹脂、メタクリル樹脂、アクリル樹脂、ポリ塩化ビニル樹脂、セルロース樹脂、ウレタン樹脂、エポキシ樹脂、ポリススチレン樹脂、ポリビニルアセテート樹脂、スチレンブタジエン共重合体、塩化ビニルデン−アクリロニトリル共重合体、塩化ビニル−酢酸ビニル−無水マレイン酸共重合体、又はシリコン樹脂等)等が挙げられるが、これに限定されるものではない。

【0021】

‐ゲート電極‐

ゲート電極14Gを構成する材料としては、金(Au)等の金属、金属酸化物、導電性高分子等が挙げられる。ゲート電極14Gの形成方法としては、真空蒸着法やスパッタリング法に例示される物理的気相成長法(PVD)法;有機金属化合物化学気相成長法(MOCVD)法を含む各種の化学気相成長法(CVD)法;リフトオフ法;シャドウマスク法;電解メッキ法や無電解メッキ法若しくはこれらの組み合わせとったメッキ法;又は塗布液(液体材料)を塗布する方法として、スピンコーティング法、インクジェット法、スプレー法、エレクトロスプレー法などのうちいずれかと、必要に応じたパターニング技術との組み合わせが挙げられる。

【0022】

<亀裂誘導部形成工程>

電子素子の非動作領域に該当する基板12上に、第1導電層(ゲート電極14G)とは別に亀裂誘導部22を形成する。

【0023】

‐亀裂誘導部‐

亀裂誘導部22は、電子素子の非動作領域で、後工程で形成するゲート絶縁層16下にゲート絶縁層16と接して形成され、ゲート電極14G上のゲート絶縁層16よりも亀裂誘導部22上のゲート絶縁層16に優先的に亀裂を生じさせるように形成する。すなわち、亀裂誘導部22は、後工程でゲート絶縁層16を形成したときに、ゲート電極14G上の絶縁層16よりも亀裂誘導部22上の絶縁層16に亀裂30を生じさせ易い構成とすればよい。なおこのような構成である限り、亀裂誘導部22の配置形態は特に限定されず、ゲート電極14Gと接触して設けられていても、離間して設けられていてもよい。

【0024】

亀裂誘導部22は、例えば、下記(1)〜(4)の少なくとも1つを満たすように構成される。なお、ゲート電極14Gと同じ材料で同時に形成してもよいし、ゲート電極14Gを形成する前又は後に、ゲート電極14Gと同じ材料又は異なる材料で形成してもよい。

(1)亀裂誘導部22の面積が、第1導電層(例えば、ゲート電極14G)の面積よりも大きい。

(2)亀裂誘導部22の表面が、第1導電層(例えば、ゲート電極14G)の表面よりも疎水性である。

(3)亀裂誘導部22の表面粗さが、第1導電層(例えば、ゲート電極14G)の表面粗さよりも大きい。

(4)亀裂誘導部22の厚みが、第1導電層(例えば、ゲート電極14G)の厚みよりも大きい。

【0025】

亀裂誘導部22として使用される材料としては、金属、金属酸化物、導電性高分子、無機絶縁物、有機絶縁物、無機半導体、有機半導体等が挙げられる。

亀裂誘導部22の形成方法としては、真空蒸着法やスパッタリング法に例示される物理的気相成長法(PVD)法、有機金属化合物化学気相成長法(MOCVD)法を含む各種の化学気相成長法(CVD)法、リフトオフ法、シャドウマスク法、電解メッキ法や無電解メッキ法若しくはこれらを組み合わせたメッキ法、又は塗布液(液体材料)を塗布する方法として、スピンコーティング法、インクジェット法、スプレー法、エレクトロスプレー法などのうちいずれかと、必要に応じたパターニング技術との組み合わせが挙げられる。

【0026】

上記(1)の方法では、亀裂誘導部22の面積がゲート電極14Gよりも面積が大きければ良い。望ましくは亀裂誘導部の面積がゲート電極14Gの3倍以上の面積があることが良い。

上記(2)の方法では、ゲート電極14Gよりも亀裂誘導部22が疎水性となるように形成する。方法としては、材料の違いや表面処理による疎水性の違いを利用する。

上記(3)の方法では、ゲート電極14Gよりも亀裂誘導部22の表面粗さが粗くなるようにする。方法としては、作製方法の違いや表面処理による表面粗さの違いを利用する。

上記(4)の方法では、ゲート電極14Gよりも亀裂誘導部22が厚くなるように形成する。

実際の有効性を考慮すると、最も有効な方法から順に(3)、(2)、(1)、(4)の順となる。

【0027】

亀裂誘導部22の配置は、動作領域のゲート絶縁層16に亀裂が入らないように配置すれば、どのような配置でも構わない。例えば、動作領域を囲むような形であっても良い。

亀裂誘導部22の形状はいかなる形状でも良い。

亀裂誘導部22の厚みは特に限定されないが、例えば、10nm以上1μm以下が望ましい。

【0028】

<絶縁層形成工程>

第1導電層(ゲート電極14G)と亀裂誘導部22上に絶縁層16を形成するための塗布液を付与して塗膜を形成した後、該塗膜を乾燥させて絶縁層16を形成する。

【0029】

‐ゲート絶縁層‐

ゲート絶縁層16としては、酸化シリコン膜や、窒化シリコン膜や、ポリイミドのような有機系絶縁膜等が挙げられるが、これに限定されるものではない。

ゲート絶縁層16を形成する方法としては、スピンコーティング法、インクジェット法、スプレー法、エレクトロスプレー法等が挙げられるが、これらに限定されない。

【0030】

半導体素子などの電子素子を作製する際、基板のガラス転移温度以下で行う必要があるが、プラスチック基板のような低ガラス転移温度基板を用いるには、CVD法など基板が高温に曝される方法で酸化シリコン膜等の絶縁膜を作製することが困難であり、低温で形成される酸化シリコン膜が必要とされる。

【0031】

酸化シリコン膜を、溶液法で且つ低温で形成する方法として、ポリシラザンを含む溶液を基板上に塗布し、硬化させる方法があり、さらに絶縁膜としての機能を向上させる手段として、UVオゾン処理を施す方法がある。しかし、ポリシラザンから酸化シリコンに構造が変化する際に、密度変化が大きく、結果的に亀裂が発生してしまう。この亀裂が薄膜トランジスタ(TFT)のチャネル直下にあるときゲートリーク電流の原因となり素子性能を低下させる。

【0032】

しかし、本実施形態では、亀裂誘導部22を設けてあるため、亀裂誘導部22上の絶縁層16に優先的に亀裂30が生じ、絶縁層16にランダムに亀裂30が生じることが抑制され、それによりゲート電極14G上の絶縁層16に亀裂30が生じることが抑制される。本実施形態に係るTFT10では、亀裂誘導部22上の絶縁層16よりもゲート電極14G上の絶縁層16に生じる単位面積あたりの亀裂30の数(本/mm2)が少なく、亀裂誘導部22を形成しない場合に比べ、ゲート電極14G上の絶縁層16における亀裂30の密度が少なく抑えられ、ゲートリーク電流の発生が抑制される。

【0033】

なお、ゲート絶縁層16としての酸化シリコン膜は、CVD法などの気相法によって成膜する方法もあるが、上記のようにポリシラザンを含む溶液を用いて絶縁層を形成した場合は、絶縁層に含まれる未反応のポリシラザン又は残留溶媒を分析することで、気相法によって成膜した酸化シリコン膜から区別される。

【0034】

<緻密化処理工程>

本実施形態では、絶縁層形成工程の後に、前記絶縁層を緻密化する処理を施す緻密化処理工程を有していてもよい。

緻密化処理としては、UVオゾン処理、加熱処理等が挙げられる。緻密化処理を行うことで、ゲート絶縁層16全体が緻密化される。その影響で、一般的にはゲート絶縁層16には亀裂が発生しやすい状態となる。本実施形態では、より亀裂の入りやすい状態となる緻密化処理を行っても、動作領域のゲート絶縁層16に亀裂が入ることが抑制される。

【0035】

<第2導電層形成工程>

ゲート絶縁層16を形成した後、第2導電層として、ソース電極18S及びドレイン電極18D(ソース・ドレイン電極18S,18D)を形成する。

【0036】

‐ソース電極及びドレイン電極‐

ソース電極18S及びドレイン電極18Dを構成する材料としては、上述したゲート電極14Gを構成する材料が挙げられる。また、このソース電極18S及びドレイン電極18Dの形成方法についても上述したゲート電極14Gの形成方法として挙げた方法が用いられる。

【0037】

<半導体層形成工程>

次いで、ソース・ドレイン電極18S,18D上のチャネル領域に半導体層20を形成する。

【0038】

‐半導体層‐

半導体層20の構成材料としては、公知の半導体材料が挙げられる。具体的には、トリエチルシリルエチニルアントラジチオフェン(TES ADT)、ペンタセン、テトラセン、アントラセン、ナフタレン、α−6−チオフェン、ペリレン及びその誘導体、ルブレン及びその誘導体、コロネン及びその誘導体、ペリレンテトラカルボン酸ジイミド及びその誘導体、ペリレンテトラカルボン酸二無水物及びその誘導体、ポリチオフェン及びその誘導体、ポリパラフェニレンビニレン及びその誘導体、ポリパラフェニレン及びその誘導体、ポリフロレン及びその誘導体、ポリフロレン−オリゴチオフェンの共重合体及びその誘導体、ポリチオフェンビニレン及びその誘導体、ポリチオフェン−複素環芳香族共重合体及びその誘導体、ナフタレンのオリゴアセン及びその誘導体、α−5−チオフェンのオリゴチオフェン及びその誘導体、含金属または非含金属のフタロシアニン及びその誘導体、ピロメリト酸二無水物及びその誘導体、ピロメリト酸ジイミド及びその誘導体、ペリレンテトラカルボン酸二無水物及びその誘導体、ペリレンテトラカルボン酸ジイミド及びその誘導体、ナフタレンテトラカルボン酸ジイミド及びその誘導体、ならびにナフタレンテトラカルボン酸二無水物及びその誘導体等が挙げられる。

これらの中でも、結晶性の理由から、TES−ADTを用いることが好ましい。

【0039】

半導体材料を含む塗布液を用いて半導体層20を形成する場合には、この塗布液としては、半導体層20の構成材料として選択した半導体材料と、該半導体材料を溶解する溶媒と、を含む塗布液を用いればよい。

この塗布液に含まれる溶媒としては、半導体材料を溶解する液体を用いればよく、半導体層20の構成材料として選択した半導体材料に応じて選択すればよいが、例えば、トルエン、無機溶媒(硝酸、硫酸、アンモニア、過酸化水素、二硫化炭素、四塩化炭素、又はエチレンカーボネート等)、ケトン系溶媒(メチルエチルケトン、アセトン、ジエチルケトン、メチルイソブチルケトン、メチルイソプロピルケトン、又はジクロヘキサノン等)、アルコール系溶媒(メタノール、エタノール、イソプロパノール、エチレングリコール、ジエチレングリコール、又はグリセリン等)、エーテル系溶媒(ジエチルエーテル、ジイソプロピルエーテル、テトラヒドロフラン、ジオキサン、アニソール、ジエチレングリコールジメチルエーテル、又はジエチレングリコールエチルエーテル等)、セロソルブ系溶媒(メリルセロソブル、エチルセロソルブ、又はフェニルセロソルブ等)、脂肪族炭化水素系溶媒(ヘキサン、ヘプタン、ペンタン、ヘプタン、又はシクロヘキサン等)、芳香族炭化水素系溶媒(トルエン、キシレン、又はベンゼン等)、アミド系溶媒(ピリジン、ピラジン、フラン、ピロール、又はアミド等)、ハロゲン化合物系溶媒(モノクロロベンゼン、ジクロロメタン、クロロホルム、又は1,2−ジクロロエタン等)、エステル系溶媒(酢酸エチル、酢酸メチル、又はギ酸エチル等)、硫黄化合物系溶媒(ジメチルスルホキシド、又はスルホラン等)、ニトリル系溶媒(アセトニトリル、プロピオニトリル、又はアクリロニトリル等)、有機酸系溶媒(ギ酸、酢酸、トリクロロ酢酸、又はトリフルオロ酢酸等)の如く各種有機溶媒、又は、これらを含む混合溶媒などが挙げられるが、これに限るものではない。

【0040】

そして、半導体材料を含む塗布液を塗布することによって、半導体層20を形成する。この塗布法としては、例えば、スピンコーティング法、インクジェット法、スプレー法、エレクトロスプレー法などが挙げられる。

半導体層20を形成することで、TFT10が完成する。

【0041】

例えば、図1に示す例では、ソース電極18S及びドレイン電極18Dが、ソース電極18S及びドレイン電極18Dの基板12とは反対側の面で半導体層20に接する構成である場合を説明したが、本実施形態では、ソース電極18S及びドレイン電極18Dが、ソース電極18S及びドレイン電極18Dの基板12側の面で半導体層20に接する構成であってもよい。

この場合には、基板12上に、ゲート電極14Gと、ゲート絶縁層16と、半導体層20と、ソース電極18S及びドレイン電極18Dと、がこの順に設けられた構成とすればよい。

【0042】

また、図1に示す例では、ゲート電極14Gがソース電極18S及びドレイン電極18Dより基板12側に設けられた構成、所謂、ボトムゲート構造のTFTについて説明したが、ソース電極18S及びドレイン電極18Dがゲート電極14Gより基板12側に設けられた構成(所謂、トップゲート構造)であってもよい。

例えば、図2に示すように、基板12上に、半導体層20と、ソース電極18S及びドレイン電極18Dと、ゲート絶縁層16と、ゲート電極14Gと、をこの順に設けた構成のTFT11とした場合、ソース電極18S及びドレイン電極18Dが第1導電層、ゲート電極14Gが第2導電層となる。そして、ソース・ドレイン電極18S,18Dとは別に基板12上の非動作領域に亀裂誘導部22を設けることで、ソース・ドレイン電極18S,18D上のゲート絶縁層16に亀裂30が発生することが抑制される。

なお、トップゲート構造の場合、ソース電極18S及びドレイン電極18Dが、ソース電極18S及びドレイン電極18Dの基板12側とは反対側の面で半導体層20に接する構成であってもよい。

【0043】

また、本実施形態のTFT10又はTFT11を用いて、何らかの電子装置を作製する場合には、さらに他の素子や回路等を組み合わせてもよい。

【0044】

また、上記実施形態では、電子素子としてTFTを形成する場合について説明したが、本実施形態の亀裂誘導部22は、キャパシタを形成する場合にも適用される。例えば、キャパシタの下部電極を形成する際、非動作領域に亀裂誘導部22を形成し、その後、絶縁層(誘電層)、上部電極を形成する。これにより、キャパシタの上下電極間の絶縁層に亀裂が生じることが抑制される。

【0045】

また、本実施形態における亀裂誘導部22は、層間絶縁膜を形成する場合にも適用される。例えば、図2に示す形態のTFT11を形成した後、ゲート絶縁層16上の動作領域にゲート電極14Gを、非動作領域に亀裂誘導部22を形成する。次いで、層間絶縁膜を形成した後、層間絶縁膜に設けたコンタクトホールを通じて画素電極とソース・ドレイン電極を配線により電気的に接続する。これにより、亀裂誘導部上の層間絶縁膜に優先的に亀裂を生じさせ、層間絶縁膜上に形成された配線(図示せず)下の層間絶縁膜に亀裂が発生することが抑制されることになる。

【実施例】

【0046】

以下実施例によって本発明を説明する。なお、本発明はこれらの実施例によってのみ限定されるものではない。

【0047】

以下に示す如く、有機トランジスタを作製した。

【0048】

(実施例1)

図1に示す構成の有機トランジスタを作製した。

‐ゲート電極及び亀裂誘導部の形成‐

まず、ガラス基板の片面上に、スパッタリング装置(昭和真空製イオンビームスパッタリング装置)を用いてAuの蒸着膜を形成し、フォトリソグラフィー法によって、図3に示す位置関係で、ゲート電極14G(厚さ:200nm)と、亀裂誘導部22(厚さ:500nm)をそれぞれ形成した。ゲート電極と亀裂誘導部との間の距離は500nmとした。

【0049】

‐ゲート絶縁層の形成‐

次いで、ガラス基板のゲート電極と亀裂誘導部を形成した側の面に、ポリシラザン溶液をスピンコート法により塗布した後、ホットプレートによって100℃、30分間のアニールを施した。これにより酸化シリコン膜16を形成した。

さらに酸化シリコン膜の緻密化のため、UVオゾン処理装置を用い、100℃でUVオゾン処理を行なった。

【0050】

‐ソース電極及びドレイン電極の形成‐

フォトリソグラフィー法により、酸化シリコン膜上にソース・ドレイン電極18S,18Dを形成した。具体的には、Auを電極材料として用い、膜厚は100nmとした。また、ソース電極及びドレイン電極の電極間の距離(チャネル幅)は1000μmとし、チャネル長は20μmとした。ソース・ドレイン電極の形成にはスパッタリング装置(昭和真空製イオンビームスパッタリング装置)により、メタルマスクを用いた。

【0051】

‐半導体層の形成‐

ソース・ドレイン電極を形成した後、半導体層を形成した。具体的には、ガラス基板のソース・ドレイン電極を形成した面上に、TES−DTAをトルエン溶媒中に2質量%の濃度で溶かした溶液を滴下し、スピンコート塗布することによって、有機半導体膜(厚み0.1μm)を形成した。

以上の工程を経て、ボトムゲート型の有機薄膜トランジスタを製造した。

【0052】

上記工程において、ゲート絶縁層を形成し、緻密化した後のゲート電極上の酸化シリコン膜と亀裂誘導部上の酸化シリコン膜をそれぞれ光学顕微鏡で観察した。

図4に示すように、亀裂誘導部上の酸化シリコン膜には複数の亀裂が確認された。一方、図5に示すように、ゲート電極上の酸化シリコン膜には亀裂は確認されなかった。

【0053】

(実施例2)

実施例1においてゲート電極を形成した後、亀裂誘導部を形成したこと以外は実施例1と同様にしてTFTを形成した。

上記工程において、ゲート絶縁層を形成し、緻密化した後のゲート電極上の酸化シリコン膜と亀裂誘導部上の酸化シリコン膜をそれぞれ電子顕微鏡で観察したところ、亀裂誘導部上の絶縁層には複数の亀裂が確認されたが、ゲート電極上の絶縁層には亀裂は確認されなかった。

【0054】

(比較例1)

実施例1において亀裂誘導部を形成しなかったこと以外は実施例1と同様にしてTFTを形成した。

上記工程において、ゲート絶縁層を形成し、緻密化した後のゲート電極上の酸化シリコン膜を電子顕微鏡で観察したところ、ゲート電極上の絶縁層に複数の亀裂が確認された。

【符号の説明】

【0055】

10、11 薄膜トランジスタ,12 基板,14G ゲート電極,18S ソース電極,18D ドレイン電極,20 半導体層,22 亀裂誘導部

【特許請求の範囲】

【請求項1】

基板と、

前記基板上の動作領域に配置された第1導電層と、

前記第1導電層上に該第1導電層と接して配置された絶縁層と、

前記基板上の非動作領域で前記絶縁層下に該絶縁層と接して配置され、前記絶縁層の亀裂の発生を誘導する亀裂誘導部であって、前記第1導電層上の前記絶縁層よりも該亀裂誘導部上の前記絶縁層に亀裂を優先的に発生させる亀裂誘導部と、

を有する電子素子。

【請求項2】

前記第1導電層が配置された動作領域の前記絶縁層上に該絶縁層と接して配置された第2導電層を有する請求項1に記載の電子素子。

【請求項3】

前記基板上に、ゲート電極と、ゲート絶縁層と、ソース電極と、ドレイン電極と、半導体層と、を備え、前記第1導電層及び前記第2導電層の一方が前記ゲート電極であり、他方が前記ソース電極及び前記ドレイン電極であり、前記絶縁層が前記ゲート絶縁層である請求項2に記載の電子素子。

【請求項4】

前記亀裂誘導部が、下記(1)〜(4)の少なくとも1つを満たす請求項1〜請求項3のいずれか一項に記載の電子素子。

(1)前記亀裂誘導部の面積が、前記第1導電層の面積よりも大きい。

(2)前記亀裂誘導部の表面が、前記第1導電層の表面よりも疎水性である。

(3)前記亀裂誘導部の表面粗さが、前記第1導電層の表面粗さよりも大きい。

(4)前記亀裂誘導部の厚みが、前記第1導電層の厚みよりも大きい。

【請求項5】

前記絶縁層がポリシラザンから形成されたものである請求項1〜請求項4のいずれか一項に記載の電子素子。

【請求項6】

基板上の動作領域に第1導電層を形成する第1導電層形成工程と、

前記基板上の非動作領域に配置される亀裂誘導部であって、該亀裂誘導部と前記第1導電層上に絶縁層を形成したときに、該亀裂誘導部上の前記絶縁層に前記第1導電層上の前記絶縁層よりも優先的に亀裂を生じさせる亀裂誘導部を形成する亀裂誘導部形成工程と、

前記第1導電層と前記亀裂誘導部上に前記絶縁層を形成するための塗布液を付与して塗膜を形成した後、該塗膜を乾燥させて前記絶縁層を形成する絶縁層形成工程と、

を有する電子素子の製造方法。

【請求項7】

前記絶縁層形成工程は、前記塗布液としてポリシラザンを含む溶液を用いる請求項6に記載の電子素子の製造方法。

【請求項8】

前記絶縁層形成工程の後に、前記絶縁層を緻密化する処理を施す緻密化処理工程を有する請求項6又は請求項7に記載の電子素子の製造方法。

【請求項1】

基板と、

前記基板上の動作領域に配置された第1導電層と、

前記第1導電層上に該第1導電層と接して配置された絶縁層と、

前記基板上の非動作領域で前記絶縁層下に該絶縁層と接して配置され、前記絶縁層の亀裂の発生を誘導する亀裂誘導部であって、前記第1導電層上の前記絶縁層よりも該亀裂誘導部上の前記絶縁層に亀裂を優先的に発生させる亀裂誘導部と、

を有する電子素子。

【請求項2】

前記第1導電層が配置された動作領域の前記絶縁層上に該絶縁層と接して配置された第2導電層を有する請求項1に記載の電子素子。

【請求項3】

前記基板上に、ゲート電極と、ゲート絶縁層と、ソース電極と、ドレイン電極と、半導体層と、を備え、前記第1導電層及び前記第2導電層の一方が前記ゲート電極であり、他方が前記ソース電極及び前記ドレイン電極であり、前記絶縁層が前記ゲート絶縁層である請求項2に記載の電子素子。

【請求項4】

前記亀裂誘導部が、下記(1)〜(4)の少なくとも1つを満たす請求項1〜請求項3のいずれか一項に記載の電子素子。

(1)前記亀裂誘導部の面積が、前記第1導電層の面積よりも大きい。

(2)前記亀裂誘導部の表面が、前記第1導電層の表面よりも疎水性である。

(3)前記亀裂誘導部の表面粗さが、前記第1導電層の表面粗さよりも大きい。

(4)前記亀裂誘導部の厚みが、前記第1導電層の厚みよりも大きい。

【請求項5】

前記絶縁層がポリシラザンから形成されたものである請求項1〜請求項4のいずれか一項に記載の電子素子。

【請求項6】

基板上の動作領域に第1導電層を形成する第1導電層形成工程と、

前記基板上の非動作領域に配置される亀裂誘導部であって、該亀裂誘導部と前記第1導電層上に絶縁層を形成したときに、該亀裂誘導部上の前記絶縁層に前記第1導電層上の前記絶縁層よりも優先的に亀裂を生じさせる亀裂誘導部を形成する亀裂誘導部形成工程と、

前記第1導電層と前記亀裂誘導部上に前記絶縁層を形成するための塗布液を付与して塗膜を形成した後、該塗膜を乾燥させて前記絶縁層を形成する絶縁層形成工程と、

を有する電子素子の製造方法。

【請求項7】

前記絶縁層形成工程は、前記塗布液としてポリシラザンを含む溶液を用いる請求項6に記載の電子素子の製造方法。

【請求項8】

前記絶縁層形成工程の後に、前記絶縁層を緻密化する処理を施す緻密化処理工程を有する請求項6又は請求項7に記載の電子素子の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−169502(P2012−169502A)

【公開日】平成24年9月6日(2012.9.6)

【国際特許分類】

【出願番号】特願2011−30237(P2011−30237)

【出願日】平成23年2月15日(2011.2.15)

【出願人】(000005496)富士ゼロックス株式会社 (21,908)

【Fターム(参考)】

【公開日】平成24年9月6日(2012.9.6)

【国際特許分類】

【出願日】平成23年2月15日(2011.2.15)

【出願人】(000005496)富士ゼロックス株式会社 (21,908)

【Fターム(参考)】

[ Back to top ]