電子装置、配線基板、及び、電子装置の製造方法

【課題】フリップチップ接続されて構成される半導体装置などのように、はんだを用いた電極どうしの電気的接続が行われる電子装置においても、チップなどの電子部品の回路、又は、配線基板の回路を変更する以外の手法で、電子部品の電極の接続先を切り替える。

【解決手段】電子装置(例えば、半導体装置100)は、複数の第1電極210を一方の面上に有する配線基板200と、複数の第1電極210とそれぞれ対応して配置された複数の第2電極310を一方の面上に有する電子部品(例えば、チップ300)を有する。第1電極210のうちの少なくとも1つ以上は、複数の分割部分221、222に分割された特定電極220であり、分割部分221、222が、各々異なる配線251、252に接続されている。分割部分221、222のうちの何れか1つ以上が、対応する第2電極310とはんだ110を介して接続されている。

【解決手段】電子装置(例えば、半導体装置100)は、複数の第1電極210を一方の面上に有する配線基板200と、複数の第1電極210とそれぞれ対応して配置された複数の第2電極310を一方の面上に有する電子部品(例えば、チップ300)を有する。第1電極210のうちの少なくとも1つ以上は、複数の分割部分221、222に分割された特定電極220であり、分割部分221、222が、各々異なる配線251、252に接続されている。分割部分221、222のうちの何れか1つ以上が、対応する第2電極310とはんだ110を介して接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子装置、配線基板、及び、電子装置の製造方法に関する。

【背景技術】

【0002】

ボンディングワイヤーを使用する半導体装置の場合、ボンディングオプションにてボンディングワイヤーの接続先を切り替えることによって、半導体チップ(以下、単にチップ)の一部の機能を用途に応じて変更することが可能である。これにより、複数の用途間で、チップの共用、或いは、チップが搭載される配線基板を共用が可能となる。一般的なボンディングオプションは、チップと配線基板をワイヤーボンディングする際に、接続先をボンディングプログラムによって切り替えることにより実現する。

【0003】

一方、このようなボンディングプログラムによる接続先の切り換え以外の方法でボンディングオプションを実現する方法としては、特許文献1乃至3に記載のものがある。

【0004】

特許文献1の方法では、チップの電極に複数本の配線を接続しておき、それら配線のうち所望の特性を得るために必要な配線以外の配線を切断することでチップの回路を変更することによって、ボンディングオプションを実現する。

【0005】

特許文献2の方法では、パターンが形成されたTABテープにチップを搭載する際に、チップを搭載する位置を変更することにより、チップの電極のデータ端子の接続先を切り替える。

【0006】

特許文献3の方法では、信号線に接続している第1電極と、スリットを介して第1電極の外側に設けられ、他の信号線に接続している第2電極と、を有するボンディングパッドを用いる。そして、ボンディングワイヤーの接続先を第1電極のみにするか、又は、第1及び第2電極にするかを切り替えることによって、ボンディングオプションを実現する。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平11−40563号公報

【特許文献2】特開平11−177040号公報

【特許文献3】特開2000−323519号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、フリップチップ接続される半導体装置の場合、チップと配線基板とをはんだで接続する為、このはんだの直接的な接続先を簡単には変えることができない。そのため、フリップチップ接続される半導体装置の場合、用途毎にチップを変更したり、或いは、用途毎に配線基板上の配線パターンを変更することによって、回路を切り替えることが一般的である。しかし、その場合、回路の種類ごとにチップと配線基板との組み合わせを用意する必要があり、非効率である。

【0009】

その為、フリップチップ接続されて構成される半導体装置などのように、はんだを用いた電極どうしの電気的接続が行われる電子装置においても、チップなどの電子部品の回路、又は、配線基板の回路を変更する以外の手法で、電子部品の電極の接続先を切り替える方法が望まれている。

【課題を解決するための手段】

【0010】

本発明は、複数の第1電極を一方の面上に有する配線基板と、

前記複数の第1電極とそれぞれ対応して配置された複数の第2電極を一方の面上に有する電子部品と、

を有し、

前記第1電極のうちの少なくとも1つ以上は、複数の分割部分に分割された特定電極であり、

前記分割部分が、各々異なる配線に接続され、

前記分割部分のうちの何れか1つ以上が、対応する前記第2電極とはんだを介して接続されていることを特徴とする電子装置を提供する。

【0011】

この発明によれば、特定電極の複数の分割部分のうちの何れか1つ以上が、対応する第2電極とはんだを介して接続されることによって、第2電極の接続先が選択された構造の電子装置を提供することができる。つまり、フリップチップ接続されて構成される半導体装置などのように、はんだを用いた電極どうしの電気的接続が行われる電子装置においても、チップなどの電子部品の回路、又は、配線基板の回路を変更する以外の手法で、電子部品の電極の接続先を切り替えることができる。

【0012】

また、本発明は、基板本体と、

前記基板本体の一方の面上に形成された複数の第1電極と、

を有し、

前記第1電極のうちの少なくとも1つ以上は、複数の分割部分に分割された特定電極であり、

前記分割部分が、各々異なる配線に接続され、

前記第1電極のうちの他の少なくとも1つ以上は、複数分割されずにその全体が一体的に構成されている通常電極であり、

前記通常電極の径が、前記分割部分どうしの間隔よりも大きいことを特徴とする配線基板を提供する。

【0013】

また、本発明は、複数の第1電極を一方の面上に有する配線基板上に、

前記複数の第1電極とそれぞれ対応して配置された複数の第2電極を一方の面上に有し、前記第1電極のうちの少なくとも1つ以上は複数の分割部分に分割された特定電極であり、前記分割部分が各々異なる配線に接続され、前記第2電極の各々にはんだボールが形成されている電子部品、を搭載する工程と、

前記はんだボールをリフローさせて、前記第2電極の各々を前記第1電極とはんだを介して接続する工程と、

を有し、

前記接続する工程では、前記分割部分のうちの何れか1つ以上を、対応する前記第2電極とはんだを介して接続することを特徴とする電子装置の製造方法を提供する。

【発明の効果】

【0014】

本発明によれば、フリップチップ接続されて構成される半導体装置などのように、はんだを用いた電極どうしの電気的接続が行われる電子装置においても、チップなどの電子部品の回路、又は、配線基板の回路を変更する以外の手法で、電子部品の電極の接続先を切り替えることができる。

【図面の簡単な説明】

【0015】

【図1】第1の実施形態に係る半導体装置を示す断面図である。

【図2】第1の実施形態に係る半導体装置の配線基板の特定電極を示す平面図である。

【図3】第1の実施形態に係る半導体装置を示す図である。

【図4】第1の実施形態に係る半導体装置の配線基板の一部分を示す平面図である。

【図5】第1の実施形態に係る半導体装置の半導体チップの第2電極と配線基板の第1電極との配置関係及び寸法の関係を示す図である。

【図6】第1の実施形態に係る半導体装置の配線基板の第1電極の平面的な配置の例を示す平面図である。

【図7】第1の実施形態に係る半導体装置の配線基板の特定電極と通常電極との寸法の関係を示す図である。

【図8】第1の実施形態に係る半導体装置の寸法規定の例を説明するための断面図である。

【図9】第1の実施形態に係る半導体装置の製造方法の一例を説明するための図である。

【図10】第1の実施形態に係る半導体装置の製造方法の他の一例を説明するための図である。

【図11】第1の実施形態に係る半導体装置の製造方法におけるはんだのリフローの仕方を説明するための図である。

【図12】第2の実施形態に係る半導体装置を示す図であり、このうち(a)は側断面図、(b)は拡大断面図である。

【図13】第3の実施形態に係る半導体装置の模式的な断面図である。

【図14】第3の実施形態に係る半導体装置の半導体チップと配線基板とを対向させた状態を示す側断面図である。

【図15】第3の実施形態に係る半導体装置の製造方法の一例を説明するための図である。

【図16】第3の実施形態に係る半導体装置の製造方法の他の一例を説明するための図である。

【図17】特定電極の形状のバリエーションを説明するための平面図である。

【図18】第5の実施形態に係る半導体装置の製造方法を説明するための平面図である。

【図19】第5の実施形態に係る半導体装置の製造方法でのはんだのリフローの仕方を説明するための図である。

【図20】複数の特定電極を配置する場合の配置の一例を示す平面図である。

【図21】複数の特定電極を配置する場合の配置の他の一例を示す平面図である。

【図22】図21の配置の場合におけるボンディングオプションのバリエーションを説明するための図である。

【図23】第6の実施形態に係る半導体装置を示す断面図である。

【図24】第7の実施形態に係る半導体装置を示す断面図である。

【図25】変形例に係る半導体装置を示す図である。

【発明を実施するための形態】

【0016】

以下、本発明の実施形態について、図面を用いて説明する。なお、すべての図面において、同様の構成要素には同一の符号を付し、適宜に説明を省略する。

【0017】

〔第1の実施形態〕

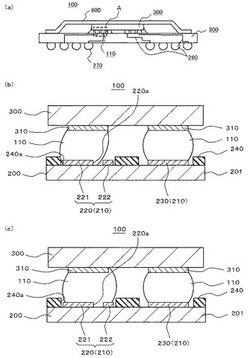

図1(a)は第1の実施形態に係る半導体装置100の模式的な断面図であり、図1(b)及び(c)は、図1(a)の破線で囲まれた領域Aを拡大した模式的な断面図である。このうち(b)は特定電極220の分割部分221が半導体チップ300(以下、チップ300)の第2電極310と接続されている例を示し、(c)は特定電極220の分割部分221及び222がチップ300の第2電極310と接続されている例を示す。図2は第1の実施形態に係る半導体装置100の配線基板200の特定電極220を示す平面図である。図3は半導体装置100の模式図であり、このうち(a)は側断面図、(b)は半導体装置100の一部分を示す平面図である。

【0018】

本実施形態に係る電子装置(例えば、半導体装置100)は、複数の第1電極210を一方の面上に有する配線基板200と、複数の第1電極210とそれぞれ対応して配置された複数の第2電極310を一方の面上に有する電子部品(例えば、チップ300)と、を有し、第1電極210のうちの少なくとも1つ以上は、複数の分割部分(例えば、2つの分割部分221、222)に分割された特定電極220であり、分割部分221、222が、各々異なる配線251、252に接続され、分割部分221、222のうちの何れか1つ以上が、対応する第2電極310とはんだ110を介して接続されている。本実施形態に係る半導体装置100は、例えば、半導体パッケージである。

また、本実施形態に係る配線基板200は、基板本体201と、基板本体201の一方の面上に形成された複数の第1電極210と、を有し、第1電極210のうちの少なくとも1つ以上は、複数の分割部分(例えば、2つの分割部分221、222)に分割された特定電極220であり、分割部分221、222が、各々異なる配線251、252に接続され、第1電極210のうちの他の少なくとも1つ以上は、複数分割されずにその全体が一体的に構成されている通常電極230であり、通常電極230の径が、分割部分221、222どうしの間隔よりも大きい。

以下、詳細に説明する。

【0019】

図1及び図3に示すように、半導体装置100は、配線基板200と、チップ300と、を有している。配線基板200の一方の面上には、複数の第1電極210が規則的に(例えばマトリクス状に)配置されている(図4参照)。チップ300の一方の面上には、複数の第2電極310が、それぞれ第1電極210と対向する配置で形成されている。配線基板200の各第1電極210とチップ300の各第2電極310とは、はんだ110を介して接続されている。すなわち、チップ300は、配線基板200上にフリップチップ接続されている。

【0020】

図1(a)に示すように、配線基板200の内部には、配線260が引き回されている。配線基板200の他方の面には電極(不図示)が形成されており、これら電極上(図1(a)では下)には、はんだボール270が設けられている。はんだボール270は、配線基板200の他方の面の電極と、マザーボードなど他の電子部品の電極(不図示)とを接続するためのものである。

配線260は、一部の配線250とはんだボール270とを相互に接続している。

チップ300は、その上面または周囲に、CuやAlなどを含む金属などからなる保護部材(リッド)600を有していても良い。

【0021】

図4は配線基板200の一部分(図2(b)の領域A内の部分)を示す平面図であり、このうち(a)では各第1電極210(特定電極220及び通常電極230)に接続された配線250も示しているが、(b)では第1電極210の形状を分かりやすくするため配線250の図示を省略している。

【0022】

図4に示すように、配線基板200の一方の面上にはソルダーレジスト240が形成されている。ソルダーレジスト240は、ソルダーレジスト240の一部が除去されることによって形成され、配線基板200のチップ側に向けて開口した複数の開口240aを一定間隔で有している。第1電極210は、それぞれ対応する開口240a内に配置されている。

【0023】

複数の第1電極210には、特定電極220と通常電極230とが含まれている。通常電極230は、複数分割されずにその全体が一体的に構成されている。特定電極220は、複数の分割部分(例えば、2つの分割部分221、222)に分割されている。

特定電極220の複数の分割部分221、222は、共通の開口240a内に配置されている。

通常電極230の径は、分割部分221、222どうしの間隔(つまり、後述するスリット220aの幅)よりも大きい。

【0024】

また、本実施形態において、複数の開口240aは互いに同じ半径の円形である。本実施形態の半導体装置100における配線基板200は、内部に特定電極220を有する第1の開口240aと、当該特定電極220と配線250を介して接続された通常電極230を内部に有し第1の開口240aに隣接する第2の開口240aとを備えている。第1の開口240aの中心と、第2の開口240aの中心とを通る直線に対して、分割部分221、222はいずれも線対称である。

また、第2の開口240aに隣接し前記第1の開口240aと第2の開口240aとの中心を通る直線上に開口中心が配置された第3の開口240aを更に備えており、第1の開口240aの中心と第2の開口240aの中心との間の距離は、第2の開口240aの中心と第3の開口240aの中心との間の距離と等しい。

また、分割部分221を起点として配線251が延伸する方向と、分割部分222を起点として配線252が延伸する方向とは、互いに反対方向である。

【0025】

図4(a)に示すように、各第1電極210は、それぞれ配線250に接続されている。これらの配線250には、所定の信号が伝達される配線(信号線)251や、グランド端子(図示略)に接続されている配線(グランド線)252が含まれる。

【0026】

ここで、特定電極220の分割部分221、222の各々は、互いに異なる配線250に接続されている。本実施形態の場合、例えば、分割部分221は信号線251に接続され、分割部分222はグランド線252に接続されている。

【0027】

図2に示すように、特定電極220の複数の分割部分221、222には、相対的に寸法が大きい大寸法部である分割部分221と、相対的に寸法が小さい小寸法部である分割部分222と、が含まれる。

このうち、大寸法部である分割部分221が特定電極220の中央部に配置されている。すなわち、分割部分221は、当該分割部分221を含む特定電極220と対応する開口240aの中央部に配置される。

本実施形態の場合、例えば、分割部分221、222は、1つの円を、これら分割部分221、222の並び方向と直交する直線状のスリット220aにより分断することにより得られる形状となっている。

【0028】

ここで、大寸法部である分割部分221の平面積は、例えば、通常電極230の平面積の75%以上150%以下であることが挙げられる。

【0029】

図5は半導体装置100の半導体チップ300(以下、チップ300)の第2電極310と配線基板200の特定電極220及び通常電極230との配置関係及び寸法の関係を示す図である。

このうち図5(a)は、各通常電極230の中心と、それら通常電極230と対応する第2電極310の中心と、が対向するように、配線基板200とチップ300とを対向させた状態の側断面図である。

図5(b)は配線基板200の特定電極220及び通常電極230を実線で示し、チップ300の第2電極310を一点鎖線で示し、それらを重ねて示した平面図である。

【0030】

図5(a)に示すように配線基板200とチップ300とを対向させた状態で、図5(a)及び図5(b)に示すように、特定電極220の各分割部分221、222の各々が、対応する第2電極310と対向するように、各分割部分221、222の寸法及び配置が設定されている。

【0031】

なお、図1に示すように、チップ300を配線基板200上に接続した状態でも、特定電極220の各分割部分221、222の各々が、対応する第2電極310と対向している。すなわち、第2電極310を配線基板200上に投影した場合に、その投影されたエリア内に、各分割部分221、222の少なくとも一部分ずつが存在している。

ただし、小寸法部である分割部分222の一部分は、その投影されたエリアの外側に位置していることが好ましい。

【0032】

図6は配線基板200の第1電極210(特定電極220及び通常電極230)の平面的な配置の例を示す平面図である。

【0033】

図6に示すように、配線基板200には、例えば、非常に多くの数の第1電極210が形成されている。このうち、最外周から10列以内の第1電極210のみが、特定電極220となっていることが好ましい。また、これら第1電極210のうち、多くても10%以下(例えば、5%以下)の第1電極210のみが、特定電極220となっていることが好ましい。

【0034】

図7は配線基板200の特定電極220と通常電極230との寸法の関係を示す平面図である。

図7に示すように、特定電極220と通常電極230の中心を合わせたときに、各分割部分221、222の少なくとも一部分ずつが、通常電極230と重なる。

【0035】

図8は半導体装置100の特定電極220、はんだ110、第2電極310等の寸法規定の例を説明するための断面図である。

【0036】

特定電極220の分割部分221、222とは、下記式で規定される間隔(MIN Gap)以上の距離を開けて隣り合って配置されている。これにより、分割部分221に対して選択的にはんだ110を接合したい場合に、はんだ110が分割部分222に接触してしまうことを抑制することができる。

【0037】

MIN Gap=S+(K・M/2S)−(L+J/2)

ここで、式中のSは、下記式で表される。

S=(R2−(K/2)2)1/2

また、式中のJ、R、K、L、Mは、それぞれ、以下の値である。

J:第2電極310の中心位置と分割部分221の中心位置との平面的なずれ量

R:はんだ110の半径

K:はんだの高さ

L:第2電極310の中心位置と、分割部分221における分割部分222側の端部との水平距離

M:分割部分222の厚み

【0038】

次に、本実施形態に係る半導体装置の製造方法を説明する。

図9はこの製造方法の一例を説明するための図である。このうち図9(a)乃至(c)は一連の工程を示す断面図、図9(d)は図9(a)の段階での第2電極310と特定電極220との平面的な位置関係を示す図である。

同様に、図10はこの製造方法の他の一例を説明するための図である。このうち図10(a)乃至(c)は一連の工程を示す断面図、図10(d)は図10(a)の段階での第2電極310と特定電極220との平面的な位置関係を示す図である。

【0039】

この製造方法は、上述の配線基板200上に、上述のチップ300(電子部品)を搭載する工程と、はんだボール111をリフローさせて、第2電極310の各々を第1電極210とはんだ110を介して接続する工程と、を有し、前記接続する工程では、分割部分221、222のうちの何れか1つ以上を、対応する第2電極310とはんだ110を介して接続する。この製造方法は、例えば、いわゆるC4(Controlled Collapse Chip Connection)法により実現することができる。以下、詳細に説明する。

【0040】

先ず、図9を参照して、特定電極220の分割部分221、222のうち、分割部分221のみが対応する第2電極310と接続されるように、チップ300を配線基板200上にフリップチップ接続する例を説明する。

【0041】

チップ300の各第2電極310上(図9(a)では第2電極310の下)には、予め、はんだボール111が固定されている。なお、各はんだボール111の寸法は、互いに等しい。次に、各はんだボール111の頂部(図9(a)では下部)に、フラックス(図示略)を付着させる。

【0042】

次に、図9(a)及び図9(d)に示すように、各第2電極310の中心c(図9(d))を各第1電極210の中心からオフセットさせて、チップ300を配線基板200上に搭載する。ここで、オフセットの方向は、特定電極220の複数の分割部分221、222の並び方向であり、且つ、分割部分222から分割部分221に向かう方向である。

これにより、例えば、図9(a)に示すように、特定電極220上のはんだボール111が分割部分221上に配置され、且つ、分割部分222上には配置されない。なお、通常電極230上にもはんだボール111が配置された状態となる。ただし、はんだボール111は、通常電極230の中心から、上記の方向(図9(a)の左側)へオフセットされて配置されている。

【0043】

次に、図9(b)に示すように、はんだボール111を加熱することによってリフローさせる。図9(b)は、はんだボール111が溶融した直後の状態を示している。この状態では、溶融したはんだ112の上にチップ300が浮いている。なお、この加熱の段階から、フラックスは徐々に揮発する。

【0044】

図9(b)に示す状態の後は、溶融した各はんだ112の表面張力により、チップ300が配線基板200に対して相対的に移動する。具体的には、それら表面張力の水平方向成分の合算値がゼロに近づく方向(図9(b)の矢印B方向)へと、チップ300が配線基板200に対して相対的に移動する。換言すれば、上述したオフセットの方向の反対方向へと、チップ300が配線基板200に対して相対的に移動する。

【0045】

その結果、図9(c)に示すように、各通常電極230の中心がそれぞれ対応する第2電極310の中心と対向する位置でバランスが取れて、チップ300と配線基板200との相対位置が安定する。そして、その位置で溶融したはんだ112が固化し、固化したはんだ110を介してチップ300と配線基板200とが接続される。

【0046】

ここで、上記のように、溶融したはんだ112の表面張力により、配線基板200に対するチップ300の位置が自動的に補正される動作を、セルフアライメントという。

このようなセルフアライメントが生じる理由は、上述のように、多数の第1電極210のうち僅かな(例えば数%以下の)第1電極210のみが特定電極220である一方で、残りの大多数の第1電極210は通常電極230であり、これら通常電極230上で溶融したはんだ112の表面張力が、配線基板200に対するチップ300のセルフアライメントに際して支配的となるためである。

【0047】

なお、このようなセルフアライメントにより、特定電極220上のはんだ110(112)は、図9(c)に示すように、チップ300及び配線基板200の法線に対して傾斜する方向に引き伸ばされる。

ここで、はんだボール111は、図9(a)の段階でフラックスが付着された部位にのみ濡れ広がる(図9(b))。すなわち、特定電極220上のはんだボール111は、分割部分221、222のうち、分割部分221上にのみ濡れ広がる。そして、はんだボール111と、このように濡れ広がった箇所と、の接続が維持されたまま、セルフアライメントされる(図9(c))。また、他方の分割部分222には、たとえ溶融したはんだ112が該分割部分222に触れたとしても、はんだ110が接合されない。

このため、はんだ110は、分割部分221に対して選択的に接続され、分割部分222とは導通しない。

【0048】

次に、図10を参照して、特定電極220の分割部分221、222の双方が第2電極310と接続されるように、チップ300を配線基板200上にフリップチップ接続する例を説明する。

【0049】

この場合も、先ず、チップ300の各第2電極310上に固定されたはんだボール111の頂部(図10(a)では下部)に、フラックス(図示略)を付着させる。

【0050】

次に、図10(a)及び図10(d)に示すように、各第2電極310の中心c(図10(d))を各第1電極210の中心からオフセットさせて、チップ300を配線基板200上に搭載する。ここで、オフセットの方向は、特定電極220の複数の分割部分221、222の並び方向であり、且つ、分割部分221から分割部分222に向かう方向である。

これにより、例えば、図10(a)に示すように、特定電極220上のはんだボール111が分割部分222上に配置され、且つ、分割部分221上には配置されない。なお、通常電極230上にもはんだボール111が配置された状態となる。ただし、はんだボール111は、通常電極230の中心から、上記の方向(図10(a)の右側)へオフセットされて配置されている。そのオフセット量は、図10(a)に示すようにはんだボール111が特定電極220の分割部分222とのみ接するようなオフセット量でも良いし、はんだボール111が特定電極の分割部分221、222の双方に接触するようなオフセット量でも良い。

【0051】

次に、図10(b)に示すように、はんだボール111を加熱することによってリフローさせる。図10(b)は、はんだボール111が溶融した直後の状態を示している。この状態では、溶融したはんだ112の上にチップ300が浮いている。

【0052】

図10(b)に示す状態の後は、溶融した各はんだ112の表面張力により、図9のケースと反対方向(図10(b)の矢印D方向)に、チップ300が配線基板200に対してセルフアライメントされる。

【0053】

その結果、図10(c)に示すように、各通常電極230の中心がそれぞれ対応する第2電極310の中心と対向する位置でバランスが取れて、チップ300と配線基板200との相対位置が安定する。そして、その位置で溶融したはんだ112が固化し、固化したはんだ110を介してチップ300と配線基板200とが接続される。

【0054】

ここで、はんだボール111は、図10(a)の段階でフラックスが付着された部位にのみ濡れ広がろうとするが、この場合、分割部分221よりも分割部分222の電極面積が小さいため、フラックスが全て揮発するよりも前に、はんだボール111が分割部分221にも接触する。その結果、はんだボール111は、セルフアライメントの過程で、特定電極220の中央に位置する分割部分221上にも濡れ広がる。

このため、はんだ110は、分割部分221及び222の双方に対して接続される。

【0055】

なお、図9の方法により、はんだ110を分割部分221に対して選択的に接続することによって、チップ300の対応する第2電極310から供給される信号を、所望の供給先に供給することができる。

一方、図10の方法により、はんだ110を分割部分221及び分割部分222に対して接続することによって、チップ300の対応する第2電極310から供給される信号は、分割部分222を介してグランドに伝達されるため、この信号を使わない状態とすることができる。

【0056】

図11は第1の実施形態に係る半導体装置の製造方法におけるはんだのリフローの仕方を説明するための図である。

【0057】

先ず、予めはんだボール111が設けられたチップ300を配線基板200上に搭載する(図11(a))。この状態は、図9(a)又は図10(a)の状態に相当する。

【0058】

次に、配線基板200及びチップ300をリフロー装置400内に投入し、加熱する(図11(b))。これにより、はんだボール111を溶融させて、上述のセルフアライメントを行う。この状態は、図9(b)又は図10(b)の状態に相当する。

【0059】

次に、配線基板200及びチップ300をリフロー装置400から搬出し、冷却する。これにより、溶融したはんだ112を硬化させ、チップ300と配線基板200とがはんだ110を介して相互に接続された状態とする。こうして、半導体装置100が得られる(図11(c))。この状態は、図9(c)又は図10(c)の状態に相当する。

【0060】

以上のような第1の実施形態によれば、特定電極220の複数の分割部分221、222のうちの何れか1つ以上を、対応する第2電極310とはんだ110を介して接続することによって、第2電極310の接続先を切り替えることができる。

【0061】

上記のように、はんだボール111を溶融させて、セルフアライメントにより配線基板200に対するチップ300の相対位置を調節する場合、チップ300を配線基板200上に搭載する位置を変更するだけで、第2電極310の接続先を切り替えることができる。つまり、チップ300を自動搭載するマウンタの制御を変更するだけで、第2電極310の接続先を切り替えることができる。

なお、セルフアライメントにより配線基板200に対するチップ300の相対位置を調節する場合、最終的なチップ300と配線基板200との相対位置関係は、通常の製品と同様であり、従って、最終的に得られる半導体装置100の形状も、通常の製品と同様であるため、半導体装置100に生じる反り等の影響も、通常の製品と同様である。

【0062】

本実施形態においては、特定電極220を、相対的に寸法が大きい大寸法部である分割部分221と、相対的に寸法が小さい小寸法部である分割部分222と、が含まれるように分割している。これにより、大寸法部(分割部分221)のみにはんだ110を接合した場合と、大寸法部と小寸法部(分割部分222)の双方にはんだ110を接合した場合と、のいずれの接続形態を選んだ場合であっても、高い接合歩留まりを得ることができる。

以下、その理由を具体的に説明する。

はんだボール111を特定電極220の一方の分割部分に対してのみ選択的に接合したい時、接合対象の分割部分の面積が通常電極230と比べて極端に小さい場合、接合対象の特定電極220よりはみだしたはんだが同じ特定電極200内の他方の分割部分に接触し、意図せずはんだ110が双方の分割部分に対して接続されてしまうことがある。

これに対して、特定電極220を、互いに表面積が異なる大寸法部と小寸法部とに分割することによって、はんだ110を大寸法部に対してのみ接合したり、または、大寸法部及び小寸法部の双方に対して接合することができる。一方の分割部分に対してはんだ110を選択的に接続する必要がある場合であっても、相対的に寸法の大きな大寸法部である分割部部分221に対してはんだ110を接続することにより、一定以上のはんだ接合面積を確保することができる。

【0063】

また、本実施形態において、特定電極220は、その側面がソルダーレジスト240から離間して形成される所謂NSMD(Non-Solder Mask Defined)構造となっている。NSMD構造では電極の側面もはんだ接合が可能であるため、平面視において充分な面積の分割部分221を確保できない場合であっても、電極の側面をはんだ接合部とすることにより、電極面積の低下の影響を緩和することができる。

【0064】

さらに、特定電極220の大寸法部である分割部分221をNSMD構造とし、小寸法部である分割部分222をSMD(Solde Mask Defined)構造としても良い。例えば小寸法部である分割部分222の導体パターンのうち、配線250よりも幅が広い導体部の一部をソルダーレジスト240で覆う形とする。電極側面の一部をソルダーレジスト240で覆うことで、その部分がはんだ接合しない領域となり、大寸法部に対してのみ接続する場合と、大寸法部及び小寸法部の双方に接続する場合と、のそれぞれの場合における特定電極220とはんだ110との接合面積の差をさらに小さくでき、接合歩留まりを高くすることができる。

【0065】

さらに、特定電極220の大寸法部である分割部分221と、小寸法部である分割部分222との双方をSMD構造としても良い。SMD構造でははんだ接合面積の確保が難しくなるが、特定電極200が互いに面積が異なる分割部分を有するため、はんだ110を大寸法部に対してのみ接合したり、または、大寸法部及び小寸法部の双方に対して接合することにより、一定以上のはんだ接合面積を確保することができる。

【0066】

〔第2の実施形態〕

図12は第2の実施形態に係る半導体装置100を示す図であり、このうち(a)は側断面図、(b)は拡大断面図である。

【0067】

本実施形態に係る半導体装置100は、チップ300と配線基板200との間隔にアンダーフィル樹脂(樹脂)120が充填されている点でのみ、上記の第1の実施形態に係る半導体装置100と相違し、その他の点は第1の実施形態に係る半導体装置100と同様に構成されている。

【0068】

ここで、図12(b)に示す例では、図1(a)と同様に、特定電極220の複数の分割部分221、222のうち、分割部分221に対してのみ、はんだ110が接続され、分割部分222にははんだ110が接続されていない。

【0069】

この場合、アンダーフィル樹脂120は、分割部分221と分割部分222との間隔にも充填されている。すなわち、アンダーフィル樹脂120は、特定電極220の複数の分割部分221、222のうち、はんだ110を介して相互に接続されていない部分どうしの間にも充填されている。

【0070】

以上のような第2の実施形態によれば、チップ300と配線基板200との間隔にアンダーフィル樹脂120が充填されているので、このアンダーフィル樹脂120によって、予期しない短絡の発生を抑制することができる。

特に、特定電極220の複数の分割部分221、222に、はんだ110を介して相互に接続されていない部分が存在する場合に、それらの間隔にもアンダーフィル樹脂120が充填されているので、それらの短絡の発生を抑制することができる。

本実施形態に係る半導体装置100は、特にはんだボール270を備える場合に有効である。すなわち半導体装置100は、該半導体装置100をマザーボードなど他の電子部品の電極とはんだボール270を介して接続する際に、はんだボール270の融点以上に加熱されることがあるが、この加熱時にはんだ110が再溶融しても、アンダーフィル樹脂120によって分割部分221、222との接続状態が変化することを防止することができる。

特にはんだ110が純スズ(Sn)、もしくはスズ(Sn)を主成分とし、銀(Ag),銅(Cu),ビスマス(Bi),亜鉛(Zn)の何れか一つ以上を含む合金からなる、いわゆるPbフリーはんだの場合は、はんだ110とはんだボール270との融点差が小さくなるため、本実施形態に係る半導体装置100は顕著な効果を得ることができる。

【0071】

〔第3の実施形態〕

図13は第3の実施形態に係る半導体装置100の模式的な断面図であり、このうち(a)は特定電極220の分割部分221がチップ300の第2電極310と接続されている例を示し、(b)は特定電極220の分割部分221及び222がチップ300の第2電極310と接続されている例を示す。また、図14は、第2電極310にはんだボール111が設けられたチップ300と配線基板200とを対向させた状態を示す断面図である。

【0072】

上記の第1の実施形態では、チップ300の第2電極310がパッド状であり半導体装置100をC4法により製造する例を説明したが、第3の実施形態では、チップ300の第2電極310がポスト状である例を説明する。

【0073】

図13に示すように、本実施形態の場合、チップ300の第2電極310は、はんだ110よりも高融点の金属からなる柱状の導体であり、例えば、Cuポストである。そして、図14に示すように、第2電極310上に、はんだボール111が設けられている。

【0074】

次に、本実施形態の場合の半導体装置の製造方法を説明する。

図15はこの製造方法の一例を説明するための図である。このうち図15(a)乃至(c)は一連の工程を示す断面図、図15(d)は図15(a)の段階での第2電極310と特定電極220との平面的な位置関係を示す図である。

同様に、図16はこの製造方法の他の一例を説明するための図である。このうち図16(a)乃至(c)は一連の工程を示す断面図、図16(d)は図16(a)の段階での第2電極310と特定電極220との平面的な位置関係を示す図である。

【0075】

先ず、図15を参照して、特定電極220の分割部分221、222のうち、分割部分221のみが対応する第2電極310と接続されるように、チップ300を配線基板200上にフリップチップ接続する例を説明する。

【0076】

先ず、各はんだボール111に、フラックス(図示略)を付着させる。

【0077】

次に、図15(a)及び図15(d)に示すように、各第2電極310の中心c(図15(d))を各第1電極210の中心からオフセットさせて、チップ300を配線基板200上に搭載する。オフセットの方向は、図9(a)の場合と同様である。

【0078】

次に、図15(b)に示すように、はんだボール111を加熱することによってリフローさせる。図15(b)は、はんだボール111が溶融した直後の状態を示している。この状態では、溶融したはんだ112の上にチップ300が浮いている。

【0079】

その後、図9(b)の場合と同様に、はんだ112の表面張力によって、矢印B方向にセルフアライメントがなされる。

【0080】

その結果、図15(c)に示すように、各通常電極230の中心がそれぞれ対応する第2電極310の中心と対向する位置でバランスが取れて、チップ300と配線基板200との相対位置が安定する。そして、その位置で溶融したはんだ112が固化し、固化したはんだ110を介してチップ300と配線基板200とが接続される。

【0081】

ここで、はんだボール111は、図15(a)の段階でフラックスが付着された部位にのみ濡れ広がる。すなわち、特定電極220上のはんだボール111は、分割部分221、222のうち、分割部分221上にのみ濡れ広がる。

このため、はんだ110は、分割部分221に対して選択的に接続され、分割部分222とは導通しない。

【0082】

次に、図16を参照して、特定電極220の分割部分221、222のうち、分割部分222のみが対応する第2電極310と接続されるように、チップ300を配線基板200上にフリップチップ接続する例を説明する。

【0083】

この場合も、先ず、チップ300の各第2電極310上に固定されたはんだボール111に、フラックス(図示略)を付着させる。

【0084】

次に、図16(a)及び図16(d)に示すように、各第2電極310の中心c(図16(d))を各第1電極210の中心からオフセットさせて、チップ300を配線基板200上に搭載する。オフセットの方向は、図10(a)の場合と同様である。

【0085】

次に、図16(b)に示すように、はんだボール111を加熱することによってリフローさせる。図16(b)は、はんだボール111が溶融した直後の状態を示している。この状態では、溶融したはんだ112の上にチップ300が浮いている。

【0086】

その後、図10(b)の場合と同様に、はんだ112の表面張力によって、矢印D方向にセルフアライメントがなされる。

【0087】

その結果、図16(c)に示すように、各通常電極230の中心がそれぞれ対応する第2電極310の中心と対向する位置でバランスが取れて、チップ300と配線基板200との相対位置が安定する。そして、その位置で溶融したはんだ112が固化し、固化したはんだ110を介してチップ300と配線基板200とが接続される。

【0088】

ここで、はんだボール111は、図16(a)の段階でフラックスが付着された部位にのみ濡れ広がろうとするが、この場合、セルフアライメントの過程で、特定電極220の中央に位置する分割部分221上にも濡れ広がる。

このため、はんだ110は、分割部分221及び222の双方に対して接続される。

【0089】

以上のような第3の実施形態によれば、上記の第1の実施形態と同様の効果が得られる。

さらに、本実施形態によれば、半導体装置100は、はんだ110よりも高融点の金属からなる柱状導体を備えるため、チップ300と配線基板200の接合リフロー前のはんだボール111の基板水平方向の位置バラツキを、該柱状導体を備えない場合と比べて小さくできる。これにより高い歩留まりで特定電極220に対する所望の接続を得ることができる。

なお、第3の実施形態においても、第2の実施形態と同様に、チップ300と配線基板200との間隔にアンダーフィル樹脂120を充填しても良い。

特に、チップ300と配線基板200との接合リフロー前に、硬化前のアンダーフィル樹脂120を予め形成する場合であっても、はんだボール111は柱状導体に支持されているため、予め形成されたアンダーフィル樹脂120中にはんだボール111を挿入する際のはんだボール111の変形を小さくすることができる。

【0090】

〔第4の実施形態〕

本実施形態では、図17の平面図を参照して、特定電極220の形状のバリエーションを説明する。

【0091】

図17(a)の例では、特定電極220は、3つの分割部分221、222、223を有している。このうち大寸法部である分割部分221は、8角形に形成されている。この分割部分221の両側に、それぞれ半円形の小寸法部である分割部分222、223が配置されている。分割部分221と分割部分222、223との間には、それぞれ直線状のスリット220aが形成されている。図示は省略するが、各分割部分221〜223には、それぞれ異なる配線250が接続されている。

この例では、はんだバンプ(はんだ110)は、分割部分221に対してのみ接続される場合と、分割部分221及び222に対してのみ接続される場合と、分割部分221及び223に対してのみ接続される場合と、分割部分221、222、223のすべてに対して接続される場合とがある。これらの何れの場合にも、特定電極220に対するはんだ110の接続端の形状が、なるべく丸まった形状となることができるように、各分割部分221〜223の形状及び配置が設定されている。

【0092】

図17(b)の例でも、特定電極220は、3つの分割部分221、222、223を有し、大寸法部である分割部分221は8角形に形成され、この分割部分221の両側に、それぞれ小寸法部である分割部分222、223が配置されている。ただし、図17(b)の例では、分割部分222、223は、それぞれ直線状(細長い矩形状)に形成されている。図示は省略するが、各分割部分221〜223には、それぞれ異なる配線250が接続されている。

これら分割部分222、223は、例えば、配線250(図示略)の延長線上に、配線250と同じ幅(図17(b)の左右幅)で形成されている。こうすることにより、分割部分222、223及び配線250の一括形成がより容易となる。

なお、図17(b)の例でも、特定電極220とはんだ110との接続のバリエーションは、図17(a)の例と同様である。

【0093】

図17(c)の例では、特定電極220は、5つの分割部分221、222、223、224、225を有している。このうち小寸法部である分割部分222〜225は、それぞれ楕円形に形成されている。分割部分222〜225は、大寸法部である分割部分221の四方に90度間隔でそれぞれ配置されている。各分割部分222〜225と分割部分221との間には、分割部分222〜225の各々の長軸に沿った弧状の外周に沿う弧状のスリット220aが形成されている。このため、分割部分221の外周には、分割部分222〜225の各々の長軸に沿った弧状の外周に沿う形状の凹みが形成されている。図示は省略するが、各分割部分221〜225には、それぞれ異なる配線250が接続されている。図17(c)の例では、図17(a)、図17(b)の場合と比べて、分割部分221〜225の数が多いため、特定電極220とはんだ110との接続のバリエーションを増やすことができる。

【0094】

図17(d)の例でも、特定電極220は、5つの分割部分221、222、223、224、225を有している。この例では、大寸法部である分割部分221は、円形とされている。また、小寸法部である分割部分222〜225は、それぞれ矩形状に形成されている。分割部分222〜225は、分割部分221の四方に90度間隔でそれぞれ配置されている。図示は省略するが、各分割部分221〜225には、それぞれ異なる配線250が接続されている。

分割部分222〜225は、例えば、配線250(図示略)の延長線上に、配線250と同じ幅で形成されている。こうすることにより、分割部分222〜225及び配線250の一括形成がより容易となる。

図17(d)の例の特定電極220とはんだ110との接続のバリエーションは、図17(c)の例と同様である。

【0095】

図17(e)の例では、特定電極220は、3つの分割部分221、222、223を有し、大寸法部である分割部分221は楕円形又は円形に形成され、この分割部分221の両側に、それぞれ三日月型の小寸法部である分割部分222、223がそれぞれの弦を分割部分221側にして配置されている。図示は省略するが、各分割部分221〜223には、それぞれ異なる配線250が接続されている。

図17(e)の例の特定電極220とはんだ110との接続のバリエーションは、図17(a)の例と同様である。この何れのバリエーションの場合にも、特定電極220に対するはんだ110の接続端の形状が、なるべく丸まった形状となることができるように、各分割部分221〜223の形状及び配置が設定されている。

【0096】

このように、図17(a)〜(e)の何れの場合においても、大寸法部(分割部分221)の周囲に複数の小寸法部(分割部分222〜225)が配置されている。

【0097】

なお、図17(a)〜(e)の何れの場合においても、小寸法部である各分割部分221〜225は、例えば、互いに同一形状、且つ、同一寸法に形成されている。ただし、小寸法部である各分割部分221〜225のうち少なくとも2つ以上の形状又は寸法が互いに異なっていても良い。

【0098】

〔第5の実施形態〕

第5の実施形態では、ローカルリフロー装置を用いてはんだを特定電極の所望の分割部分上に濡れ広がらせる例を説明する。

図18は第5の実施形態に係る半導体装置の製造方法を説明するための平面図、図19はこの製造方法でのはんだのリフローの仕方を説明するための図である。

【0099】

本実施形態の場合、チップ300の構造は、上記の第3の実施形態と同様であり、第2電極310は、例えば、Cuポストである(図14参照)。

また、配線基板200は、特定電極220の構造以外については、第3の実施形態と同様である。本実施形態の場合、特定電極220は、図18(a)に示す構造となっている。この構造は、上記の第4の実施形態で説明した図17(d)の構造である。

【0100】

以下、本実施形態に係る半導体装置の製造方法を説明する。

【0101】

先ず、予めはんだボール111が設けられたチップ300をローカルリフロー装置(全体図示略)の吸着ヘッド500により吸着保持する。そして、吸着ヘッド500によりチップ300を吸着保持したままで、チップ300を配線基板200上に搭載する(図19(a))。ここで、図18(b)に示すように、特定電極220の所望の小寸法部及び大寸法部の上にはんだボール111が位置するように、チップ300を配線基板200上に配置する。例えば、はんだボール111は、分割部分225上及び分割部分221上に位置している。ここで、図18(b)の段階でのはんだボール111の径は、Cuポストである第2電極310の径と略等しい。

【0102】

次に、吸着ヘッド500を加熱することによって、はんだボール111を溶融させる(図18(b)、図19(b))。これにより、溶融したはんだ112は、先ず、分割部分225上及び分割部分221上に濡れ広がる。

【0103】

吸着ヘッド500によりチップ300を吸着保持したままで、吸着ヘッド500とともにチップ300を図18(c)の矢印D方向に配線基板200に対して相対的に移動させる。これにより、図18(c)に示すように、溶融したはんだ112は、分割部分225上、分割部分221上及び分割部分224上に亘って濡れ広がる。つまり、複数の分割部分のうち、所望の分割部分上に、溶融したはんだ112を濡れ広がらせることができる。

【0104】

次に、溶解したはんだ112を冷却し固化させる。これにより、チップ300と配線基板200とがはんだ110を介して相互に接続された状態とする。具体的には、例えば、特定電極220の分割部分221、224及び225が、はんだ110を介して第2電極310と接続された状態となる。

【0105】

以上のような第5の実施形態によれば、以下の効果が得られる。すなわち、チップ300の電極がCuポストなどである場合においては、電極上のはんだの量が比較的少ないため、配線基板200の電極上に濡れ広がりにくい。このような事情に対し、本実施形態では、はんだを溶融させた状態で、チップ300を保持して配線基板200に対して相対的に移動させることにより、はんだを所望の分割部分上に濡れ広がらせることができる。つまり、例えば、Cuポストである第2電極310の径よりも広い範囲にまで、はんだを濡れ広がらせることができる。

また、例えば、選別後の検査で、半導体装置の動作不良が見つかった場合に、はんだ110を再溶融させて、回路の繋ぎ替えを行うこともでき、歩留まりを向上させることもできる。

【0106】

〔第6の実施形態〕

図23を用いて第6の実施形態を説明する。本実施形態における半導体装置においてはチップ300の搭載前に特定電極220の分割部分222が絶縁膜700で覆われている点が他の実施形態と異なる。絶縁膜700は例えばエポキシ基を含む熱硬化樹脂からなる。絶縁膜700は、分割部分222の側面及び上面をすべて覆っていることが好ましい。絶縁膜700は、分割部分222上における厚さが、ソルダーレジスト240の厚さよりも薄くなるように形成されることが好ましい。絶縁膜700を形成するには、配線基板200に例えばインクジェット法により任意の分割部分222を覆うように硬化前の絶縁性樹脂を印刷し、熱処理、UV処理などで硬化させる。その後チップ300を搭載することにより、本実施形態に係る半導体装置を得ることができる。

本実施形態においては、分割部分222が絶縁膜700で覆われているので、特定電極220の分割部分222とはんだ110との意図せぬ短絡を確実に抑制できる。よって、はんだ110を特定電極220の分割部分221に対して選択的に接合することができる。

また、例えばチップ300の搭載時のオフセット量を小さくすることが可能となる。

さらにアンダーフィル樹脂120を形成することで特定電極220の分割部分222とはんだ110との間に2重の絶縁膜が形成されることとなり、絶縁膜700またはアンダーフィル樹脂120の一方がボイドなどを含んでいる場合でも確実な絶縁が可能となる。

【0107】

〔第7の実施形態〕

図24を用いて第7の実施形態を説明する。本実施形態において、ソルダーレジスト240の開口240aがソルダーレジスト240の底面(基板本体201に近い側)から上面(チップ300に近い側)にかけて拡径するテーパ形状を備えている点が他の実施形態と異なる。ソルダーレジスト240の底面と、側壁(開口240aの内周壁)とのなす角度を75度よりも小さくすることが好適である。

ソルダーレジスト240のこのようなテーパ形状は、例えばソルダーレジスト240の開口を形成する露光工程での回折を増す、あるいは現像工程でのエッチング量を増加させる、あるいはソルダーレジストを異なる開口径の2層で形成するなどにより実現できる。

ソルダーレジスト240をこのようなテーパ形状とすることで、チップ300のオフセット搭載時にはんだボール111がソルダーレジストに乗り上げることによって発生する未着不良を軽減できるとともに、溶融したはんだ112が拡がることが可能な空間を大きくできるため特定電極220の分割部分221をはんだ110と接続しつつ、分割部分222とはんだ110との意図せぬ短絡を防止することができる。

尚、第1電極210の断面形状を底面(基板本体201に近い側)から上面(チップ300に近い側)にかけて径が小さくなる台形状としても同様の効果を得ることができる。すなわち、溶融したはんだ112が拡がることが可能な空間を大きくできるため、特定電極220の分割部分221をはんだ110と接続しつつ、分割部分222とはんだ110との意図せぬ短絡を防止することができる。

第1電極210のパターニング後にウェットエッチングを行うことにより、第1電極210の断面形状をこのような台形状とすることができる。そのウェットエッチング後、第1電極210の表面に例えばNi層やAuめっき層を形成しても台形状は維持される。

【0108】

上記の各実施形態では、チップ300を配線基板200上にフリップチップ接続する例を説明したが、本発明は、この例に限らず、BGA(Ball Grid Array)パッケージ(半導体装置)をマザーボード(配線基板)に実装する場合にも同様に適用することができる。

【0109】

また、上記の各実施形態では、電子部品がチップ300であり、電子装置が半導体装置100である例を説明したが、電子部品はチップ以外の電子部品であっても良く、電子装置は半導体装置以外の電子装置であっても良い。

【0110】

また、複数の第1電極210のうちの少なくとも1つ以上の第1電極210は、第2電極310と接続されていなくても良い。

【0111】

また、特定電極220の分割部分のうちの少なくとも何れか1つは、電源線に接続されていても良いし、或いは、他の第1電極210に接続されていても良い。

【0112】

また、配線基板200上に複数の特定電極220を形成する場合、それら特定電極220の向きは、図20に示すように互いに同一であっても良いし、或いは、図21に示すように、互いに異なる向きの特定電極220が含まれていても良い。

すなわち、図20に示される2つの特定電極220は、複数の分割部分221、222の並び方向が互いに同一(図20の左右方向)である。

これに対し、図21に示される2つの特定電極220のうち、一方(上側)の特定電極220における複数の分割部分221、222の並び方向(図21の上下方向)と、他方(下側)の特定電極220における複数の分割部分221、222の並び方向(図21の左右方向)とは、互いに直交している。

【0113】

ここで、図22を参照して、複数の特定電極220が図21に示すような向きで配置されている場合に、セルフアライメントによりチップ300を配線基板200上に接続する場合の、ボンディングオプションのバリエーションを説明する。

チップ300を配線基板200に対して相対的に、図22(a)に示される矢印E方向(左下方向)にオフセットして、チップ300を配線基板200に搭載し、上述したようなセルフアライメントを行うことにより、上側の特定電極220では、双方の分割部分221、222に対してはんだ110を接続し、下側の特定電極220では、分割部分221に対してのみ選択的にはんだ110を接続することができる。

また、チップ300を配線基板200に対して相対的に、図22(b)に示される矢印F方向(右下方向)にオフセットして、チップ300を配線基板200に搭載し、上述したようなセルフアライメントを行うことにより、上側の特定電極220では、双方の分割部分221、222に対してはんだ110を接続し、下側の特定電極220でも、双方の分割部分221、222に対してはんだ110を接続することができる。

また、チップ300を配線基板200に対して相対的に、図22(c)に示される矢印G方向(右上方向)にオフセットして、チップ300を配線基板200に搭載し、上述したようなセルフアライメントを行うことにより、上側の特定電極220では、分割部分221に対してのみ選択的にはんだ110を接続し、下側の特定電極220では、双方の分割部分221、222に対してはんだ110を接続することができる。

また、チップ300を配線基板200に対して相対的に、図22(d)に示される矢印H方向(左上方向)にオフセットして、チップ300を配線基板200に搭載し、上述したようなセルフアライメントを行うことにより、上側の特定電極220では、分割部分221に対してのみ選択的にはんだ110を接続し、下側の特定電極220でも、分割部分221に対してのみ選択的にはんだ110を接続することができる。

このように、配線基板200上に、互いに異なる向きの複数の特定電極220を形成することにより、ボンディングオプションのバリエーションを増やすことができる。

【0114】

また、上記の各実施形態では、ソルダーレジスト240の別個の開口240a内に第1電極210の特定電極220と通常電極230とが配置されている例を説明したが、ソルダーレジスト240の同一の開口240a内に特定電極220と通常電極230とが配置されていても良い。例えば配線基板200の第1の辺に沿って延伸する開口240a内に配線基板200の第1の辺に対して垂直な方向に延伸する線状の第1電極210を形成しても良い。

図25を用いて説明する。図25は変形例に係る半導体装置を示す図であり、このうち(a)は平面図、(b)は図25(a)のB−B線に沿った断面図、(c)は図25(a)のC−C線に沿った断面図である。

図25(a)における左の実線は配線基板200の第1の辺202を示しており、配線基板200は第1の辺202に対して垂直な方向に延伸する線(リード)状の第1の電極210を有する。第1の電極210には特定電極220と通常電極230とが含まれる。配線基板200は表面にソルダーレジスト240を有しており、ソルダーレジスト240は開口240aを有し、同一の開口240a内に特定電極220と通常電極230とを有する。特定電極220は分割部分221、222を有する。分割部分221は、分割部分222よりも面積が大きく、例えば信号線に接続される。分割部分222は、例えばグランドなどの固定電位に接続される。

図25(a)には、配線基板200に搭載されるチップ300の第2電極310上に形成されるはんだ110の領域を1点鎖線および2点鎖線で示す。なお、図25(b)、図25(c)には、はんだ110が2点鎖線の領域に位置する場合の断面を示している。本変形例においても、チップ300を第1の辺202側(図の左側)、一点鎖線上にはんだボール111が位置するように搭載しリフローすることにより、はんだ110を分割部分221に対して選択的に接続することができる。一方で、チップ300を図の右側、つまり図の2点鎖線にはんだボール111が位置するように搭載してリフローすることにより、はんだ110が分割部分221と分割部分222との双方に接続された接続状態を得ることができる。図25(a)の例では、図の上下方向に並ぶ複数の第1電極210が同一の開口240a内に配置されており、それらがソルダーレジスト240によって互いに区画されていない。このため、特に、図25(b)及び図25(c)に示すように、チップ300の第2電極310をポスト状とすることにより、隣接する第1電極210間での意図せぬ短絡を防止することができる。すなわち、図25の例の第2電極310は、例えば、はんだ110よりも高融点の金属からなる柱状の導体であり、例えば、Cuポストである。

また、基板200が、第1の辺202に対して隣接し且つ直交する第2の辺203(不図示)に沿って形成された第2の開口240a(不図示)と、第2の開口240a内に形成された電極210(不図示)とを備える場合、該電極210の幅(該電極210が延伸する方向に対して直交する方向における電極210の長さ)は、第1の開口240aにおける分割部分221と分割部分222との間の距離よりも大きいことが好ましい。これにより、チップ300搭載時の第1の辺202に対する垂直方向でのチップ300のオフセットに関わらず、第2の開口240a内の電極210とチップ300との接続状態を同一とすることができる。

なお、チップ300の第2電極310が千鳥配置の場合であっても、該第2電極310の配置にあわせて、特定電極220の分割部分をずらして配置することにより、同様の効果が得られる。

【符号の説明】

【0115】

100 半導体装置

110 はんだ

111 はんだボール

112 溶融したはんだ

120 アンダーフィル樹脂

200 配線基板

201 基板本体

202 第1の辺

210 第1電極

220 特定電極

220a スリット

221 分割部分(大寸法部)

222、223、224、225 分割部分(小寸法部)

230 通常電極

240 ソルダーレジスト

240a 開口

250 配線

251 配線

252 配線

260 配線

270 はんだボール

300 半導体チップ

310 第2電極

400 リフロー装置

500 吸着ヘッド

600 保護部材

700 絶縁膜

【技術分野】

【0001】

本発明は、電子装置、配線基板、及び、電子装置の製造方法に関する。

【背景技術】

【0002】

ボンディングワイヤーを使用する半導体装置の場合、ボンディングオプションにてボンディングワイヤーの接続先を切り替えることによって、半導体チップ(以下、単にチップ)の一部の機能を用途に応じて変更することが可能である。これにより、複数の用途間で、チップの共用、或いは、チップが搭載される配線基板を共用が可能となる。一般的なボンディングオプションは、チップと配線基板をワイヤーボンディングする際に、接続先をボンディングプログラムによって切り替えることにより実現する。

【0003】

一方、このようなボンディングプログラムによる接続先の切り換え以外の方法でボンディングオプションを実現する方法としては、特許文献1乃至3に記載のものがある。

【0004】

特許文献1の方法では、チップの電極に複数本の配線を接続しておき、それら配線のうち所望の特性を得るために必要な配線以外の配線を切断することでチップの回路を変更することによって、ボンディングオプションを実現する。

【0005】

特許文献2の方法では、パターンが形成されたTABテープにチップを搭載する際に、チップを搭載する位置を変更することにより、チップの電極のデータ端子の接続先を切り替える。

【0006】

特許文献3の方法では、信号線に接続している第1電極と、スリットを介して第1電極の外側に設けられ、他の信号線に接続している第2電極と、を有するボンディングパッドを用いる。そして、ボンディングワイヤーの接続先を第1電極のみにするか、又は、第1及び第2電極にするかを切り替えることによって、ボンディングオプションを実現する。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平11−40563号公報

【特許文献2】特開平11−177040号公報

【特許文献3】特開2000−323519号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、フリップチップ接続される半導体装置の場合、チップと配線基板とをはんだで接続する為、このはんだの直接的な接続先を簡単には変えることができない。そのため、フリップチップ接続される半導体装置の場合、用途毎にチップを変更したり、或いは、用途毎に配線基板上の配線パターンを変更することによって、回路を切り替えることが一般的である。しかし、その場合、回路の種類ごとにチップと配線基板との組み合わせを用意する必要があり、非効率である。

【0009】

その為、フリップチップ接続されて構成される半導体装置などのように、はんだを用いた電極どうしの電気的接続が行われる電子装置においても、チップなどの電子部品の回路、又は、配線基板の回路を変更する以外の手法で、電子部品の電極の接続先を切り替える方法が望まれている。

【課題を解決するための手段】

【0010】

本発明は、複数の第1電極を一方の面上に有する配線基板と、

前記複数の第1電極とそれぞれ対応して配置された複数の第2電極を一方の面上に有する電子部品と、

を有し、

前記第1電極のうちの少なくとも1つ以上は、複数の分割部分に分割された特定電極であり、

前記分割部分が、各々異なる配線に接続され、

前記分割部分のうちの何れか1つ以上が、対応する前記第2電極とはんだを介して接続されていることを特徴とする電子装置を提供する。

【0011】

この発明によれば、特定電極の複数の分割部分のうちの何れか1つ以上が、対応する第2電極とはんだを介して接続されることによって、第2電極の接続先が選択された構造の電子装置を提供することができる。つまり、フリップチップ接続されて構成される半導体装置などのように、はんだを用いた電極どうしの電気的接続が行われる電子装置においても、チップなどの電子部品の回路、又は、配線基板の回路を変更する以外の手法で、電子部品の電極の接続先を切り替えることができる。

【0012】

また、本発明は、基板本体と、

前記基板本体の一方の面上に形成された複数の第1電極と、

を有し、

前記第1電極のうちの少なくとも1つ以上は、複数の分割部分に分割された特定電極であり、

前記分割部分が、各々異なる配線に接続され、

前記第1電極のうちの他の少なくとも1つ以上は、複数分割されずにその全体が一体的に構成されている通常電極であり、

前記通常電極の径が、前記分割部分どうしの間隔よりも大きいことを特徴とする配線基板を提供する。

【0013】

また、本発明は、複数の第1電極を一方の面上に有する配線基板上に、

前記複数の第1電極とそれぞれ対応して配置された複数の第2電極を一方の面上に有し、前記第1電極のうちの少なくとも1つ以上は複数の分割部分に分割された特定電極であり、前記分割部分が各々異なる配線に接続され、前記第2電極の各々にはんだボールが形成されている電子部品、を搭載する工程と、

前記はんだボールをリフローさせて、前記第2電極の各々を前記第1電極とはんだを介して接続する工程と、

を有し、

前記接続する工程では、前記分割部分のうちの何れか1つ以上を、対応する前記第2電極とはんだを介して接続することを特徴とする電子装置の製造方法を提供する。

【発明の効果】

【0014】

本発明によれば、フリップチップ接続されて構成される半導体装置などのように、はんだを用いた電極どうしの電気的接続が行われる電子装置においても、チップなどの電子部品の回路、又は、配線基板の回路を変更する以外の手法で、電子部品の電極の接続先を切り替えることができる。

【図面の簡単な説明】

【0015】

【図1】第1の実施形態に係る半導体装置を示す断面図である。

【図2】第1の実施形態に係る半導体装置の配線基板の特定電極を示す平面図である。

【図3】第1の実施形態に係る半導体装置を示す図である。

【図4】第1の実施形態に係る半導体装置の配線基板の一部分を示す平面図である。

【図5】第1の実施形態に係る半導体装置の半導体チップの第2電極と配線基板の第1電極との配置関係及び寸法の関係を示す図である。

【図6】第1の実施形態に係る半導体装置の配線基板の第1電極の平面的な配置の例を示す平面図である。

【図7】第1の実施形態に係る半導体装置の配線基板の特定電極と通常電極との寸法の関係を示す図である。

【図8】第1の実施形態に係る半導体装置の寸法規定の例を説明するための断面図である。

【図9】第1の実施形態に係る半導体装置の製造方法の一例を説明するための図である。

【図10】第1の実施形態に係る半導体装置の製造方法の他の一例を説明するための図である。

【図11】第1の実施形態に係る半導体装置の製造方法におけるはんだのリフローの仕方を説明するための図である。

【図12】第2の実施形態に係る半導体装置を示す図であり、このうち(a)は側断面図、(b)は拡大断面図である。

【図13】第3の実施形態に係る半導体装置の模式的な断面図である。

【図14】第3の実施形態に係る半導体装置の半導体チップと配線基板とを対向させた状態を示す側断面図である。

【図15】第3の実施形態に係る半導体装置の製造方法の一例を説明するための図である。

【図16】第3の実施形態に係る半導体装置の製造方法の他の一例を説明するための図である。

【図17】特定電極の形状のバリエーションを説明するための平面図である。

【図18】第5の実施形態に係る半導体装置の製造方法を説明するための平面図である。

【図19】第5の実施形態に係る半導体装置の製造方法でのはんだのリフローの仕方を説明するための図である。

【図20】複数の特定電極を配置する場合の配置の一例を示す平面図である。

【図21】複数の特定電極を配置する場合の配置の他の一例を示す平面図である。

【図22】図21の配置の場合におけるボンディングオプションのバリエーションを説明するための図である。

【図23】第6の実施形態に係る半導体装置を示す断面図である。

【図24】第7の実施形態に係る半導体装置を示す断面図である。

【図25】変形例に係る半導体装置を示す図である。

【発明を実施するための形態】

【0016】

以下、本発明の実施形態について、図面を用いて説明する。なお、すべての図面において、同様の構成要素には同一の符号を付し、適宜に説明を省略する。

【0017】

〔第1の実施形態〕

図1(a)は第1の実施形態に係る半導体装置100の模式的な断面図であり、図1(b)及び(c)は、図1(a)の破線で囲まれた領域Aを拡大した模式的な断面図である。このうち(b)は特定電極220の分割部分221が半導体チップ300(以下、チップ300)の第2電極310と接続されている例を示し、(c)は特定電極220の分割部分221及び222がチップ300の第2電極310と接続されている例を示す。図2は第1の実施形態に係る半導体装置100の配線基板200の特定電極220を示す平面図である。図3は半導体装置100の模式図であり、このうち(a)は側断面図、(b)は半導体装置100の一部分を示す平面図である。

【0018】

本実施形態に係る電子装置(例えば、半導体装置100)は、複数の第1電極210を一方の面上に有する配線基板200と、複数の第1電極210とそれぞれ対応して配置された複数の第2電極310を一方の面上に有する電子部品(例えば、チップ300)と、を有し、第1電極210のうちの少なくとも1つ以上は、複数の分割部分(例えば、2つの分割部分221、222)に分割された特定電極220であり、分割部分221、222が、各々異なる配線251、252に接続され、分割部分221、222のうちの何れか1つ以上が、対応する第2電極310とはんだ110を介して接続されている。本実施形態に係る半導体装置100は、例えば、半導体パッケージである。

また、本実施形態に係る配線基板200は、基板本体201と、基板本体201の一方の面上に形成された複数の第1電極210と、を有し、第1電極210のうちの少なくとも1つ以上は、複数の分割部分(例えば、2つの分割部分221、222)に分割された特定電極220であり、分割部分221、222が、各々異なる配線251、252に接続され、第1電極210のうちの他の少なくとも1つ以上は、複数分割されずにその全体が一体的に構成されている通常電極230であり、通常電極230の径が、分割部分221、222どうしの間隔よりも大きい。

以下、詳細に説明する。

【0019】

図1及び図3に示すように、半導体装置100は、配線基板200と、チップ300と、を有している。配線基板200の一方の面上には、複数の第1電極210が規則的に(例えばマトリクス状に)配置されている(図4参照)。チップ300の一方の面上には、複数の第2電極310が、それぞれ第1電極210と対向する配置で形成されている。配線基板200の各第1電極210とチップ300の各第2電極310とは、はんだ110を介して接続されている。すなわち、チップ300は、配線基板200上にフリップチップ接続されている。

【0020】

図1(a)に示すように、配線基板200の内部には、配線260が引き回されている。配線基板200の他方の面には電極(不図示)が形成されており、これら電極上(図1(a)では下)には、はんだボール270が設けられている。はんだボール270は、配線基板200の他方の面の電極と、マザーボードなど他の電子部品の電極(不図示)とを接続するためのものである。

配線260は、一部の配線250とはんだボール270とを相互に接続している。

チップ300は、その上面または周囲に、CuやAlなどを含む金属などからなる保護部材(リッド)600を有していても良い。

【0021】

図4は配線基板200の一部分(図2(b)の領域A内の部分)を示す平面図であり、このうち(a)では各第1電極210(特定電極220及び通常電極230)に接続された配線250も示しているが、(b)では第1電極210の形状を分かりやすくするため配線250の図示を省略している。

【0022】

図4に示すように、配線基板200の一方の面上にはソルダーレジスト240が形成されている。ソルダーレジスト240は、ソルダーレジスト240の一部が除去されることによって形成され、配線基板200のチップ側に向けて開口した複数の開口240aを一定間隔で有している。第1電極210は、それぞれ対応する開口240a内に配置されている。

【0023】

複数の第1電極210には、特定電極220と通常電極230とが含まれている。通常電極230は、複数分割されずにその全体が一体的に構成されている。特定電極220は、複数の分割部分(例えば、2つの分割部分221、222)に分割されている。

特定電極220の複数の分割部分221、222は、共通の開口240a内に配置されている。

通常電極230の径は、分割部分221、222どうしの間隔(つまり、後述するスリット220aの幅)よりも大きい。

【0024】

また、本実施形態において、複数の開口240aは互いに同じ半径の円形である。本実施形態の半導体装置100における配線基板200は、内部に特定電極220を有する第1の開口240aと、当該特定電極220と配線250を介して接続された通常電極230を内部に有し第1の開口240aに隣接する第2の開口240aとを備えている。第1の開口240aの中心と、第2の開口240aの中心とを通る直線に対して、分割部分221、222はいずれも線対称である。

また、第2の開口240aに隣接し前記第1の開口240aと第2の開口240aとの中心を通る直線上に開口中心が配置された第3の開口240aを更に備えており、第1の開口240aの中心と第2の開口240aの中心との間の距離は、第2の開口240aの中心と第3の開口240aの中心との間の距離と等しい。

また、分割部分221を起点として配線251が延伸する方向と、分割部分222を起点として配線252が延伸する方向とは、互いに反対方向である。

【0025】

図4(a)に示すように、各第1電極210は、それぞれ配線250に接続されている。これらの配線250には、所定の信号が伝達される配線(信号線)251や、グランド端子(図示略)に接続されている配線(グランド線)252が含まれる。

【0026】

ここで、特定電極220の分割部分221、222の各々は、互いに異なる配線250に接続されている。本実施形態の場合、例えば、分割部分221は信号線251に接続され、分割部分222はグランド線252に接続されている。

【0027】

図2に示すように、特定電極220の複数の分割部分221、222には、相対的に寸法が大きい大寸法部である分割部分221と、相対的に寸法が小さい小寸法部である分割部分222と、が含まれる。

このうち、大寸法部である分割部分221が特定電極220の中央部に配置されている。すなわち、分割部分221は、当該分割部分221を含む特定電極220と対応する開口240aの中央部に配置される。

本実施形態の場合、例えば、分割部分221、222は、1つの円を、これら分割部分221、222の並び方向と直交する直線状のスリット220aにより分断することにより得られる形状となっている。

【0028】

ここで、大寸法部である分割部分221の平面積は、例えば、通常電極230の平面積の75%以上150%以下であることが挙げられる。

【0029】

図5は半導体装置100の半導体チップ300(以下、チップ300)の第2電極310と配線基板200の特定電極220及び通常電極230との配置関係及び寸法の関係を示す図である。

このうち図5(a)は、各通常電極230の中心と、それら通常電極230と対応する第2電極310の中心と、が対向するように、配線基板200とチップ300とを対向させた状態の側断面図である。

図5(b)は配線基板200の特定電極220及び通常電極230を実線で示し、チップ300の第2電極310を一点鎖線で示し、それらを重ねて示した平面図である。

【0030】

図5(a)に示すように配線基板200とチップ300とを対向させた状態で、図5(a)及び図5(b)に示すように、特定電極220の各分割部分221、222の各々が、対応する第2電極310と対向するように、各分割部分221、222の寸法及び配置が設定されている。

【0031】

なお、図1に示すように、チップ300を配線基板200上に接続した状態でも、特定電極220の各分割部分221、222の各々が、対応する第2電極310と対向している。すなわち、第2電極310を配線基板200上に投影した場合に、その投影されたエリア内に、各分割部分221、222の少なくとも一部分ずつが存在している。

ただし、小寸法部である分割部分222の一部分は、その投影されたエリアの外側に位置していることが好ましい。

【0032】

図6は配線基板200の第1電極210(特定電極220及び通常電極230)の平面的な配置の例を示す平面図である。

【0033】

図6に示すように、配線基板200には、例えば、非常に多くの数の第1電極210が形成されている。このうち、最外周から10列以内の第1電極210のみが、特定電極220となっていることが好ましい。また、これら第1電極210のうち、多くても10%以下(例えば、5%以下)の第1電極210のみが、特定電極220となっていることが好ましい。

【0034】

図7は配線基板200の特定電極220と通常電極230との寸法の関係を示す平面図である。

図7に示すように、特定電極220と通常電極230の中心を合わせたときに、各分割部分221、222の少なくとも一部分ずつが、通常電極230と重なる。

【0035】

図8は半導体装置100の特定電極220、はんだ110、第2電極310等の寸法規定の例を説明するための断面図である。

【0036】

特定電極220の分割部分221、222とは、下記式で規定される間隔(MIN Gap)以上の距離を開けて隣り合って配置されている。これにより、分割部分221に対して選択的にはんだ110を接合したい場合に、はんだ110が分割部分222に接触してしまうことを抑制することができる。

【0037】

MIN Gap=S+(K・M/2S)−(L+J/2)

ここで、式中のSは、下記式で表される。

S=(R2−(K/2)2)1/2

また、式中のJ、R、K、L、Mは、それぞれ、以下の値である。

J:第2電極310の中心位置と分割部分221の中心位置との平面的なずれ量

R:はんだ110の半径

K:はんだの高さ

L:第2電極310の中心位置と、分割部分221における分割部分222側の端部との水平距離

M:分割部分222の厚み

【0038】

次に、本実施形態に係る半導体装置の製造方法を説明する。

図9はこの製造方法の一例を説明するための図である。このうち図9(a)乃至(c)は一連の工程を示す断面図、図9(d)は図9(a)の段階での第2電極310と特定電極220との平面的な位置関係を示す図である。

同様に、図10はこの製造方法の他の一例を説明するための図である。このうち図10(a)乃至(c)は一連の工程を示す断面図、図10(d)は図10(a)の段階での第2電極310と特定電極220との平面的な位置関係を示す図である。

【0039】

この製造方法は、上述の配線基板200上に、上述のチップ300(電子部品)を搭載する工程と、はんだボール111をリフローさせて、第2電極310の各々を第1電極210とはんだ110を介して接続する工程と、を有し、前記接続する工程では、分割部分221、222のうちの何れか1つ以上を、対応する第2電極310とはんだ110を介して接続する。この製造方法は、例えば、いわゆるC4(Controlled Collapse Chip Connection)法により実現することができる。以下、詳細に説明する。

【0040】

先ず、図9を参照して、特定電極220の分割部分221、222のうち、分割部分221のみが対応する第2電極310と接続されるように、チップ300を配線基板200上にフリップチップ接続する例を説明する。

【0041】

チップ300の各第2電極310上(図9(a)では第2電極310の下)には、予め、はんだボール111が固定されている。なお、各はんだボール111の寸法は、互いに等しい。次に、各はんだボール111の頂部(図9(a)では下部)に、フラックス(図示略)を付着させる。

【0042】

次に、図9(a)及び図9(d)に示すように、各第2電極310の中心c(図9(d))を各第1電極210の中心からオフセットさせて、チップ300を配線基板200上に搭載する。ここで、オフセットの方向は、特定電極220の複数の分割部分221、222の並び方向であり、且つ、分割部分222から分割部分221に向かう方向である。

これにより、例えば、図9(a)に示すように、特定電極220上のはんだボール111が分割部分221上に配置され、且つ、分割部分222上には配置されない。なお、通常電極230上にもはんだボール111が配置された状態となる。ただし、はんだボール111は、通常電極230の中心から、上記の方向(図9(a)の左側)へオフセットされて配置されている。

【0043】

次に、図9(b)に示すように、はんだボール111を加熱することによってリフローさせる。図9(b)は、はんだボール111が溶融した直後の状態を示している。この状態では、溶融したはんだ112の上にチップ300が浮いている。なお、この加熱の段階から、フラックスは徐々に揮発する。

【0044】

図9(b)に示す状態の後は、溶融した各はんだ112の表面張力により、チップ300が配線基板200に対して相対的に移動する。具体的には、それら表面張力の水平方向成分の合算値がゼロに近づく方向(図9(b)の矢印B方向)へと、チップ300が配線基板200に対して相対的に移動する。換言すれば、上述したオフセットの方向の反対方向へと、チップ300が配線基板200に対して相対的に移動する。

【0045】

その結果、図9(c)に示すように、各通常電極230の中心がそれぞれ対応する第2電極310の中心と対向する位置でバランスが取れて、チップ300と配線基板200との相対位置が安定する。そして、その位置で溶融したはんだ112が固化し、固化したはんだ110を介してチップ300と配線基板200とが接続される。

【0046】

ここで、上記のように、溶融したはんだ112の表面張力により、配線基板200に対するチップ300の位置が自動的に補正される動作を、セルフアライメントという。

このようなセルフアライメントが生じる理由は、上述のように、多数の第1電極210のうち僅かな(例えば数%以下の)第1電極210のみが特定電極220である一方で、残りの大多数の第1電極210は通常電極230であり、これら通常電極230上で溶融したはんだ112の表面張力が、配線基板200に対するチップ300のセルフアライメントに際して支配的となるためである。

【0047】

なお、このようなセルフアライメントにより、特定電極220上のはんだ110(112)は、図9(c)に示すように、チップ300及び配線基板200の法線に対して傾斜する方向に引き伸ばされる。

ここで、はんだボール111は、図9(a)の段階でフラックスが付着された部位にのみ濡れ広がる(図9(b))。すなわち、特定電極220上のはんだボール111は、分割部分221、222のうち、分割部分221上にのみ濡れ広がる。そして、はんだボール111と、このように濡れ広がった箇所と、の接続が維持されたまま、セルフアライメントされる(図9(c))。また、他方の分割部分222には、たとえ溶融したはんだ112が該分割部分222に触れたとしても、はんだ110が接合されない。

このため、はんだ110は、分割部分221に対して選択的に接続され、分割部分222とは導通しない。

【0048】

次に、図10を参照して、特定電極220の分割部分221、222の双方が第2電極310と接続されるように、チップ300を配線基板200上にフリップチップ接続する例を説明する。

【0049】

この場合も、先ず、チップ300の各第2電極310上に固定されたはんだボール111の頂部(図10(a)では下部)に、フラックス(図示略)を付着させる。

【0050】

次に、図10(a)及び図10(d)に示すように、各第2電極310の中心c(図10(d))を各第1電極210の中心からオフセットさせて、チップ300を配線基板200上に搭載する。ここで、オフセットの方向は、特定電極220の複数の分割部分221、222の並び方向であり、且つ、分割部分221から分割部分222に向かう方向である。

これにより、例えば、図10(a)に示すように、特定電極220上のはんだボール111が分割部分222上に配置され、且つ、分割部分221上には配置されない。なお、通常電極230上にもはんだボール111が配置された状態となる。ただし、はんだボール111は、通常電極230の中心から、上記の方向(図10(a)の右側)へオフセットされて配置されている。そのオフセット量は、図10(a)に示すようにはんだボール111が特定電極220の分割部分222とのみ接するようなオフセット量でも良いし、はんだボール111が特定電極の分割部分221、222の双方に接触するようなオフセット量でも良い。

【0051】

次に、図10(b)に示すように、はんだボール111を加熱することによってリフローさせる。図10(b)は、はんだボール111が溶融した直後の状態を示している。この状態では、溶融したはんだ112の上にチップ300が浮いている。

【0052】

図10(b)に示す状態の後は、溶融した各はんだ112の表面張力により、図9のケースと反対方向(図10(b)の矢印D方向)に、チップ300が配線基板200に対してセルフアライメントされる。

【0053】

その結果、図10(c)に示すように、各通常電極230の中心がそれぞれ対応する第2電極310の中心と対向する位置でバランスが取れて、チップ300と配線基板200との相対位置が安定する。そして、その位置で溶融したはんだ112が固化し、固化したはんだ110を介してチップ300と配線基板200とが接続される。

【0054】

ここで、はんだボール111は、図10(a)の段階でフラックスが付着された部位にのみ濡れ広がろうとするが、この場合、分割部分221よりも分割部分222の電極面積が小さいため、フラックスが全て揮発するよりも前に、はんだボール111が分割部分221にも接触する。その結果、はんだボール111は、セルフアライメントの過程で、特定電極220の中央に位置する分割部分221上にも濡れ広がる。

このため、はんだ110は、分割部分221及び222の双方に対して接続される。

【0055】

なお、図9の方法により、はんだ110を分割部分221に対して選択的に接続することによって、チップ300の対応する第2電極310から供給される信号を、所望の供給先に供給することができる。

一方、図10の方法により、はんだ110を分割部分221及び分割部分222に対して接続することによって、チップ300の対応する第2電極310から供給される信号は、分割部分222を介してグランドに伝達されるため、この信号を使わない状態とすることができる。

【0056】

図11は第1の実施形態に係る半導体装置の製造方法におけるはんだのリフローの仕方を説明するための図である。

【0057】

先ず、予めはんだボール111が設けられたチップ300を配線基板200上に搭載する(図11(a))。この状態は、図9(a)又は図10(a)の状態に相当する。

【0058】

次に、配線基板200及びチップ300をリフロー装置400内に投入し、加熱する(図11(b))。これにより、はんだボール111を溶融させて、上述のセルフアライメントを行う。この状態は、図9(b)又は図10(b)の状態に相当する。

【0059】

次に、配線基板200及びチップ300をリフロー装置400から搬出し、冷却する。これにより、溶融したはんだ112を硬化させ、チップ300と配線基板200とがはんだ110を介して相互に接続された状態とする。こうして、半導体装置100が得られる(図11(c))。この状態は、図9(c)又は図10(c)の状態に相当する。

【0060】

以上のような第1の実施形態によれば、特定電極220の複数の分割部分221、222のうちの何れか1つ以上を、対応する第2電極310とはんだ110を介して接続することによって、第2電極310の接続先を切り替えることができる。

【0061】

上記のように、はんだボール111を溶融させて、セルフアライメントにより配線基板200に対するチップ300の相対位置を調節する場合、チップ300を配線基板200上に搭載する位置を変更するだけで、第2電極310の接続先を切り替えることができる。つまり、チップ300を自動搭載するマウンタの制御を変更するだけで、第2電極310の接続先を切り替えることができる。

なお、セルフアライメントにより配線基板200に対するチップ300の相対位置を調節する場合、最終的なチップ300と配線基板200との相対位置関係は、通常の製品と同様であり、従って、最終的に得られる半導体装置100の形状も、通常の製品と同様であるため、半導体装置100に生じる反り等の影響も、通常の製品と同様である。

【0062】

本実施形態においては、特定電極220を、相対的に寸法が大きい大寸法部である分割部分221と、相対的に寸法が小さい小寸法部である分割部分222と、が含まれるように分割している。これにより、大寸法部(分割部分221)のみにはんだ110を接合した場合と、大寸法部と小寸法部(分割部分222)の双方にはんだ110を接合した場合と、のいずれの接続形態を選んだ場合であっても、高い接合歩留まりを得ることができる。

以下、その理由を具体的に説明する。

はんだボール111を特定電極220の一方の分割部分に対してのみ選択的に接合したい時、接合対象の分割部分の面積が通常電極230と比べて極端に小さい場合、接合対象の特定電極220よりはみだしたはんだが同じ特定電極200内の他方の分割部分に接触し、意図せずはんだ110が双方の分割部分に対して接続されてしまうことがある。

これに対して、特定電極220を、互いに表面積が異なる大寸法部と小寸法部とに分割することによって、はんだ110を大寸法部に対してのみ接合したり、または、大寸法部及び小寸法部の双方に対して接合することができる。一方の分割部分に対してはんだ110を選択的に接続する必要がある場合であっても、相対的に寸法の大きな大寸法部である分割部部分221に対してはんだ110を接続することにより、一定以上のはんだ接合面積を確保することができる。

【0063】

また、本実施形態において、特定電極220は、その側面がソルダーレジスト240から離間して形成される所謂NSMD(Non-Solder Mask Defined)構造となっている。NSMD構造では電極の側面もはんだ接合が可能であるため、平面視において充分な面積の分割部分221を確保できない場合であっても、電極の側面をはんだ接合部とすることにより、電極面積の低下の影響を緩和することができる。

【0064】

さらに、特定電極220の大寸法部である分割部分221をNSMD構造とし、小寸法部である分割部分222をSMD(Solde Mask Defined)構造としても良い。例えば小寸法部である分割部分222の導体パターンのうち、配線250よりも幅が広い導体部の一部をソルダーレジスト240で覆う形とする。電極側面の一部をソルダーレジスト240で覆うことで、その部分がはんだ接合しない領域となり、大寸法部に対してのみ接続する場合と、大寸法部及び小寸法部の双方に接続する場合と、のそれぞれの場合における特定電極220とはんだ110との接合面積の差をさらに小さくでき、接合歩留まりを高くすることができる。

【0065】

さらに、特定電極220の大寸法部である分割部分221と、小寸法部である分割部分222との双方をSMD構造としても良い。SMD構造でははんだ接合面積の確保が難しくなるが、特定電極200が互いに面積が異なる分割部分を有するため、はんだ110を大寸法部に対してのみ接合したり、または、大寸法部及び小寸法部の双方に対して接合することにより、一定以上のはんだ接合面積を確保することができる。

【0066】

〔第2の実施形態〕

図12は第2の実施形態に係る半導体装置100を示す図であり、このうち(a)は側断面図、(b)は拡大断面図である。

【0067】

本実施形態に係る半導体装置100は、チップ300と配線基板200との間隔にアンダーフィル樹脂(樹脂)120が充填されている点でのみ、上記の第1の実施形態に係る半導体装置100と相違し、その他の点は第1の実施形態に係る半導体装置100と同様に構成されている。

【0068】

ここで、図12(b)に示す例では、図1(a)と同様に、特定電極220の複数の分割部分221、222のうち、分割部分221に対してのみ、はんだ110が接続され、分割部分222にははんだ110が接続されていない。

【0069】

この場合、アンダーフィル樹脂120は、分割部分221と分割部分222との間隔にも充填されている。すなわち、アンダーフィル樹脂120は、特定電極220の複数の分割部分221、222のうち、はんだ110を介して相互に接続されていない部分どうしの間にも充填されている。

【0070】

以上のような第2の実施形態によれば、チップ300と配線基板200との間隔にアンダーフィル樹脂120が充填されているので、このアンダーフィル樹脂120によって、予期しない短絡の発生を抑制することができる。

特に、特定電極220の複数の分割部分221、222に、はんだ110を介して相互に接続されていない部分が存在する場合に、それらの間隔にもアンダーフィル樹脂120が充填されているので、それらの短絡の発生を抑制することができる。

本実施形態に係る半導体装置100は、特にはんだボール270を備える場合に有効である。すなわち半導体装置100は、該半導体装置100をマザーボードなど他の電子部品の電極とはんだボール270を介して接続する際に、はんだボール270の融点以上に加熱されることがあるが、この加熱時にはんだ110が再溶融しても、アンダーフィル樹脂120によって分割部分221、222との接続状態が変化することを防止することができる。

特にはんだ110が純スズ(Sn)、もしくはスズ(Sn)を主成分とし、銀(Ag),銅(Cu),ビスマス(Bi),亜鉛(Zn)の何れか一つ以上を含む合金からなる、いわゆるPbフリーはんだの場合は、はんだ110とはんだボール270との融点差が小さくなるため、本実施形態に係る半導体装置100は顕著な効果を得ることができる。

【0071】

〔第3の実施形態〕

図13は第3の実施形態に係る半導体装置100の模式的な断面図であり、このうち(a)は特定電極220の分割部分221がチップ300の第2電極310と接続されている例を示し、(b)は特定電極220の分割部分221及び222がチップ300の第2電極310と接続されている例を示す。また、図14は、第2電極310にはんだボール111が設けられたチップ300と配線基板200とを対向させた状態を示す断面図である。

【0072】

上記の第1の実施形態では、チップ300の第2電極310がパッド状であり半導体装置100をC4法により製造する例を説明したが、第3の実施形態では、チップ300の第2電極310がポスト状である例を説明する。

【0073】

図13に示すように、本実施形態の場合、チップ300の第2電極310は、はんだ110よりも高融点の金属からなる柱状の導体であり、例えば、Cuポストである。そして、図14に示すように、第2電極310上に、はんだボール111が設けられている。

【0074】

次に、本実施形態の場合の半導体装置の製造方法を説明する。

図15はこの製造方法の一例を説明するための図である。このうち図15(a)乃至(c)は一連の工程を示す断面図、図15(d)は図15(a)の段階での第2電極310と特定電極220との平面的な位置関係を示す図である。

同様に、図16はこの製造方法の他の一例を説明するための図である。このうち図16(a)乃至(c)は一連の工程を示す断面図、図16(d)は図16(a)の段階での第2電極310と特定電極220との平面的な位置関係を示す図である。

【0075】

先ず、図15を参照して、特定電極220の分割部分221、222のうち、分割部分221のみが対応する第2電極310と接続されるように、チップ300を配線基板200上にフリップチップ接続する例を説明する。

【0076】

先ず、各はんだボール111に、フラックス(図示略)を付着させる。

【0077】

次に、図15(a)及び図15(d)に示すように、各第2電極310の中心c(図15(d))を各第1電極210の中心からオフセットさせて、チップ300を配線基板200上に搭載する。オフセットの方向は、図9(a)の場合と同様である。

【0078】

次に、図15(b)に示すように、はんだボール111を加熱することによってリフローさせる。図15(b)は、はんだボール111が溶融した直後の状態を示している。この状態では、溶融したはんだ112の上にチップ300が浮いている。

【0079】

その後、図9(b)の場合と同様に、はんだ112の表面張力によって、矢印B方向にセルフアライメントがなされる。

【0080】

その結果、図15(c)に示すように、各通常電極230の中心がそれぞれ対応する第2電極310の中心と対向する位置でバランスが取れて、チップ300と配線基板200との相対位置が安定する。そして、その位置で溶融したはんだ112が固化し、固化したはんだ110を介してチップ300と配線基板200とが接続される。

【0081】

ここで、はんだボール111は、図15(a)の段階でフラックスが付着された部位にのみ濡れ広がる。すなわち、特定電極220上のはんだボール111は、分割部分221、222のうち、分割部分221上にのみ濡れ広がる。

このため、はんだ110は、分割部分221に対して選択的に接続され、分割部分222とは導通しない。

【0082】

次に、図16を参照して、特定電極220の分割部分221、222のうち、分割部分222のみが対応する第2電極310と接続されるように、チップ300を配線基板200上にフリップチップ接続する例を説明する。

【0083】

この場合も、先ず、チップ300の各第2電極310上に固定されたはんだボール111に、フラックス(図示略)を付着させる。

【0084】

次に、図16(a)及び図16(d)に示すように、各第2電極310の中心c(図16(d))を各第1電極210の中心からオフセットさせて、チップ300を配線基板200上に搭載する。オフセットの方向は、図10(a)の場合と同様である。

【0085】

次に、図16(b)に示すように、はんだボール111を加熱することによってリフローさせる。図16(b)は、はんだボール111が溶融した直後の状態を示している。この状態では、溶融したはんだ112の上にチップ300が浮いている。

【0086】

その後、図10(b)の場合と同様に、はんだ112の表面張力によって、矢印D方向にセルフアライメントがなされる。

【0087】

その結果、図16(c)に示すように、各通常電極230の中心がそれぞれ対応する第2電極310の中心と対向する位置でバランスが取れて、チップ300と配線基板200との相対位置が安定する。そして、その位置で溶融したはんだ112が固化し、固化したはんだ110を介してチップ300と配線基板200とが接続される。

【0088】

ここで、はんだボール111は、図16(a)の段階でフラックスが付着された部位にのみ濡れ広がろうとするが、この場合、セルフアライメントの過程で、特定電極220の中央に位置する分割部分221上にも濡れ広がる。

このため、はんだ110は、分割部分221及び222の双方に対して接続される。

【0089】

以上のような第3の実施形態によれば、上記の第1の実施形態と同様の効果が得られる。

さらに、本実施形態によれば、半導体装置100は、はんだ110よりも高融点の金属からなる柱状導体を備えるため、チップ300と配線基板200の接合リフロー前のはんだボール111の基板水平方向の位置バラツキを、該柱状導体を備えない場合と比べて小さくできる。これにより高い歩留まりで特定電極220に対する所望の接続を得ることができる。

なお、第3の実施形態においても、第2の実施形態と同様に、チップ300と配線基板200との間隔にアンダーフィル樹脂120を充填しても良い。

特に、チップ300と配線基板200との接合リフロー前に、硬化前のアンダーフィル樹脂120を予め形成する場合であっても、はんだボール111は柱状導体に支持されているため、予め形成されたアンダーフィル樹脂120中にはんだボール111を挿入する際のはんだボール111の変形を小さくすることができる。

【0090】

〔第4の実施形態〕

本実施形態では、図17の平面図を参照して、特定電極220の形状のバリエーションを説明する。

【0091】

図17(a)の例では、特定電極220は、3つの分割部分221、222、223を有している。このうち大寸法部である分割部分221は、8角形に形成されている。この分割部分221の両側に、それぞれ半円形の小寸法部である分割部分222、223が配置されている。分割部分221と分割部分222、223との間には、それぞれ直線状のスリット220aが形成されている。図示は省略するが、各分割部分221〜223には、それぞれ異なる配線250が接続されている。

この例では、はんだバンプ(はんだ110)は、分割部分221に対してのみ接続される場合と、分割部分221及び222に対してのみ接続される場合と、分割部分221及び223に対してのみ接続される場合と、分割部分221、222、223のすべてに対して接続される場合とがある。これらの何れの場合にも、特定電極220に対するはんだ110の接続端の形状が、なるべく丸まった形状となることができるように、各分割部分221〜223の形状及び配置が設定されている。

【0092】

図17(b)の例でも、特定電極220は、3つの分割部分221、222、223を有し、大寸法部である分割部分221は8角形に形成され、この分割部分221の両側に、それぞれ小寸法部である分割部分222、223が配置されている。ただし、図17(b)の例では、分割部分222、223は、それぞれ直線状(細長い矩形状)に形成されている。図示は省略するが、各分割部分221〜223には、それぞれ異なる配線250が接続されている。

これら分割部分222、223は、例えば、配線250(図示略)の延長線上に、配線250と同じ幅(図17(b)の左右幅)で形成されている。こうすることにより、分割部分222、223及び配線250の一括形成がより容易となる。

なお、図17(b)の例でも、特定電極220とはんだ110との接続のバリエーションは、図17(a)の例と同様である。

【0093】

図17(c)の例では、特定電極220は、5つの分割部分221、222、223、224、225を有している。このうち小寸法部である分割部分222〜225は、それぞれ楕円形に形成されている。分割部分222〜225は、大寸法部である分割部分221の四方に90度間隔でそれぞれ配置されている。各分割部分222〜225と分割部分221との間には、分割部分222〜225の各々の長軸に沿った弧状の外周に沿う弧状のスリット220aが形成されている。このため、分割部分221の外周には、分割部分222〜225の各々の長軸に沿った弧状の外周に沿う形状の凹みが形成されている。図示は省略するが、各分割部分221〜225には、それぞれ異なる配線250が接続されている。図17(c)の例では、図17(a)、図17(b)の場合と比べて、分割部分221〜225の数が多いため、特定電極220とはんだ110との接続のバリエーションを増やすことができる。

【0094】

図17(d)の例でも、特定電極220は、5つの分割部分221、222、223、224、225を有している。この例では、大寸法部である分割部分221は、円形とされている。また、小寸法部である分割部分222〜225は、それぞれ矩形状に形成されている。分割部分222〜225は、分割部分221の四方に90度間隔でそれぞれ配置されている。図示は省略するが、各分割部分221〜225には、それぞれ異なる配線250が接続されている。

分割部分222〜225は、例えば、配線250(図示略)の延長線上に、配線250と同じ幅で形成されている。こうすることにより、分割部分222〜225及び配線250の一括形成がより容易となる。

図17(d)の例の特定電極220とはんだ110との接続のバリエーションは、図17(c)の例と同様である。

【0095】

図17(e)の例では、特定電極220は、3つの分割部分221、222、223を有し、大寸法部である分割部分221は楕円形又は円形に形成され、この分割部分221の両側に、それぞれ三日月型の小寸法部である分割部分222、223がそれぞれの弦を分割部分221側にして配置されている。図示は省略するが、各分割部分221〜223には、それぞれ異なる配線250が接続されている。

図17(e)の例の特定電極220とはんだ110との接続のバリエーションは、図17(a)の例と同様である。この何れのバリエーションの場合にも、特定電極220に対するはんだ110の接続端の形状が、なるべく丸まった形状となることができるように、各分割部分221〜223の形状及び配置が設定されている。

【0096】

このように、図17(a)〜(e)の何れの場合においても、大寸法部(分割部分221)の周囲に複数の小寸法部(分割部分222〜225)が配置されている。

【0097】

なお、図17(a)〜(e)の何れの場合においても、小寸法部である各分割部分221〜225は、例えば、互いに同一形状、且つ、同一寸法に形成されている。ただし、小寸法部である各分割部分221〜225のうち少なくとも2つ以上の形状又は寸法が互いに異なっていても良い。

【0098】

〔第5の実施形態〕

第5の実施形態では、ローカルリフロー装置を用いてはんだを特定電極の所望の分割部分上に濡れ広がらせる例を説明する。

図18は第5の実施形態に係る半導体装置の製造方法を説明するための平面図、図19はこの製造方法でのはんだのリフローの仕方を説明するための図である。

【0099】

本実施形態の場合、チップ300の構造は、上記の第3の実施形態と同様であり、第2電極310は、例えば、Cuポストである(図14参照)。

また、配線基板200は、特定電極220の構造以外については、第3の実施形態と同様である。本実施形態の場合、特定電極220は、図18(a)に示す構造となっている。この構造は、上記の第4の実施形態で説明した図17(d)の構造である。

【0100】

以下、本実施形態に係る半導体装置の製造方法を説明する。

【0101】

先ず、予めはんだボール111が設けられたチップ300をローカルリフロー装置(全体図示略)の吸着ヘッド500により吸着保持する。そして、吸着ヘッド500によりチップ300を吸着保持したままで、チップ300を配線基板200上に搭載する(図19(a))。ここで、図18(b)に示すように、特定電極220の所望の小寸法部及び大寸法部の上にはんだボール111が位置するように、チップ300を配線基板200上に配置する。例えば、はんだボール111は、分割部分225上及び分割部分221上に位置している。ここで、図18(b)の段階でのはんだボール111の径は、Cuポストである第2電極310の径と略等しい。

【0102】

次に、吸着ヘッド500を加熱することによって、はんだボール111を溶融させる(図18(b)、図19(b))。これにより、溶融したはんだ112は、先ず、分割部分225上及び分割部分221上に濡れ広がる。

【0103】

吸着ヘッド500によりチップ300を吸着保持したままで、吸着ヘッド500とともにチップ300を図18(c)の矢印D方向に配線基板200に対して相対的に移動させる。これにより、図18(c)に示すように、溶融したはんだ112は、分割部分225上、分割部分221上及び分割部分224上に亘って濡れ広がる。つまり、複数の分割部分のうち、所望の分割部分上に、溶融したはんだ112を濡れ広がらせることができる。

【0104】

次に、溶解したはんだ112を冷却し固化させる。これにより、チップ300と配線基板200とがはんだ110を介して相互に接続された状態とする。具体的には、例えば、特定電極220の分割部分221、224及び225が、はんだ110を介して第2電極310と接続された状態となる。

【0105】

以上のような第5の実施形態によれば、以下の効果が得られる。すなわち、チップ300の電極がCuポストなどである場合においては、電極上のはんだの量が比較的少ないため、配線基板200の電極上に濡れ広がりにくい。このような事情に対し、本実施形態では、はんだを溶融させた状態で、チップ300を保持して配線基板200に対して相対的に移動させることにより、はんだを所望の分割部分上に濡れ広がらせることができる。つまり、例えば、Cuポストである第2電極310の径よりも広い範囲にまで、はんだを濡れ広がらせることができる。

また、例えば、選別後の検査で、半導体装置の動作不良が見つかった場合に、はんだ110を再溶融させて、回路の繋ぎ替えを行うこともでき、歩留まりを向上させることもできる。

【0106】

〔第6の実施形態〕

図23を用いて第6の実施形態を説明する。本実施形態における半導体装置においてはチップ300の搭載前に特定電極220の分割部分222が絶縁膜700で覆われている点が他の実施形態と異なる。絶縁膜700は例えばエポキシ基を含む熱硬化樹脂からなる。絶縁膜700は、分割部分222の側面及び上面をすべて覆っていることが好ましい。絶縁膜700は、分割部分222上における厚さが、ソルダーレジスト240の厚さよりも薄くなるように形成されることが好ましい。絶縁膜700を形成するには、配線基板200に例えばインクジェット法により任意の分割部分222を覆うように硬化前の絶縁性樹脂を印刷し、熱処理、UV処理などで硬化させる。その後チップ300を搭載することにより、本実施形態に係る半導体装置を得ることができる。

本実施形態においては、分割部分222が絶縁膜700で覆われているので、特定電極220の分割部分222とはんだ110との意図せぬ短絡を確実に抑制できる。よって、はんだ110を特定電極220の分割部分221に対して選択的に接合することができる。

また、例えばチップ300の搭載時のオフセット量を小さくすることが可能となる。

さらにアンダーフィル樹脂120を形成することで特定電極220の分割部分222とはんだ110との間に2重の絶縁膜が形成されることとなり、絶縁膜700またはアンダーフィル樹脂120の一方がボイドなどを含んでいる場合でも確実な絶縁が可能となる。

【0107】

〔第7の実施形態〕

図24を用いて第7の実施形態を説明する。本実施形態において、ソルダーレジスト240の開口240aがソルダーレジスト240の底面(基板本体201に近い側)から上面(チップ300に近い側)にかけて拡径するテーパ形状を備えている点が他の実施形態と異なる。ソルダーレジスト240の底面と、側壁(開口240aの内周壁)とのなす角度を75度よりも小さくすることが好適である。

ソルダーレジスト240のこのようなテーパ形状は、例えばソルダーレジスト240の開口を形成する露光工程での回折を増す、あるいは現像工程でのエッチング量を増加させる、あるいはソルダーレジストを異なる開口径の2層で形成するなどにより実現できる。

ソルダーレジスト240をこのようなテーパ形状とすることで、チップ300のオフセット搭載時にはんだボール111がソルダーレジストに乗り上げることによって発生する未着不良を軽減できるとともに、溶融したはんだ112が拡がることが可能な空間を大きくできるため特定電極220の分割部分221をはんだ110と接続しつつ、分割部分222とはんだ110との意図せぬ短絡を防止することができる。

尚、第1電極210の断面形状を底面(基板本体201に近い側)から上面(チップ300に近い側)にかけて径が小さくなる台形状としても同様の効果を得ることができる。すなわち、溶融したはんだ112が拡がることが可能な空間を大きくできるため、特定電極220の分割部分221をはんだ110と接続しつつ、分割部分222とはんだ110との意図せぬ短絡を防止することができる。

第1電極210のパターニング後にウェットエッチングを行うことにより、第1電極210の断面形状をこのような台形状とすることができる。そのウェットエッチング後、第1電極210の表面に例えばNi層やAuめっき層を形成しても台形状は維持される。

【0108】

上記の各実施形態では、チップ300を配線基板200上にフリップチップ接続する例を説明したが、本発明は、この例に限らず、BGA(Ball Grid Array)パッケージ(半導体装置)をマザーボード(配線基板)に実装する場合にも同様に適用することができる。

【0109】

また、上記の各実施形態では、電子部品がチップ300であり、電子装置が半導体装置100である例を説明したが、電子部品はチップ以外の電子部品であっても良く、電子装置は半導体装置以外の電子装置であっても良い。

【0110】

また、複数の第1電極210のうちの少なくとも1つ以上の第1電極210は、第2電極310と接続されていなくても良い。

【0111】

また、特定電極220の分割部分のうちの少なくとも何れか1つは、電源線に接続されていても良いし、或いは、他の第1電極210に接続されていても良い。

【0112】

また、配線基板200上に複数の特定電極220を形成する場合、それら特定電極220の向きは、図20に示すように互いに同一であっても良いし、或いは、図21に示すように、互いに異なる向きの特定電極220が含まれていても良い。

すなわち、図20に示される2つの特定電極220は、複数の分割部分221、222の並び方向が互いに同一(図20の左右方向)である。

これに対し、図21に示される2つの特定電極220のうち、一方(上側)の特定電極220における複数の分割部分221、222の並び方向(図21の上下方向)と、他方(下側)の特定電極220における複数の分割部分221、222の並び方向(図21の左右方向)とは、互いに直交している。

【0113】

ここで、図22を参照して、複数の特定電極220が図21に示すような向きで配置されている場合に、セルフアライメントによりチップ300を配線基板200上に接続する場合の、ボンディングオプションのバリエーションを説明する。

チップ300を配線基板200に対して相対的に、図22(a)に示される矢印E方向(左下方向)にオフセットして、チップ300を配線基板200に搭載し、上述したようなセルフアライメントを行うことにより、上側の特定電極220では、双方の分割部分221、222に対してはんだ110を接続し、下側の特定電極220では、分割部分221に対してのみ選択的にはんだ110を接続することができる。

また、チップ300を配線基板200に対して相対的に、図22(b)に示される矢印F方向(右下方向)にオフセットして、チップ300を配線基板200に搭載し、上述したようなセルフアライメントを行うことにより、上側の特定電極220では、双方の分割部分221、222に対してはんだ110を接続し、下側の特定電極220でも、双方の分割部分221、222に対してはんだ110を接続することができる。

また、チップ300を配線基板200に対して相対的に、図22(c)に示される矢印G方向(右上方向)にオフセットして、チップ300を配線基板200に搭載し、上述したようなセルフアライメントを行うことにより、上側の特定電極220では、分割部分221に対してのみ選択的にはんだ110を接続し、下側の特定電極220では、双方の分割部分221、222に対してはんだ110を接続することができる。

また、チップ300を配線基板200に対して相対的に、図22(d)に示される矢印H方向(左上方向)にオフセットして、チップ300を配線基板200に搭載し、上述したようなセルフアライメントを行うことにより、上側の特定電極220では、分割部分221に対してのみ選択的にはんだ110を接続し、下側の特定電極220でも、分割部分221に対してのみ選択的にはんだ110を接続することができる。

このように、配線基板200上に、互いに異なる向きの複数の特定電極220を形成することにより、ボンディングオプションのバリエーションを増やすことができる。

【0114】

また、上記の各実施形態では、ソルダーレジスト240の別個の開口240a内に第1電極210の特定電極220と通常電極230とが配置されている例を説明したが、ソルダーレジスト240の同一の開口240a内に特定電極220と通常電極230とが配置されていても良い。例えば配線基板200の第1の辺に沿って延伸する開口240a内に配線基板200の第1の辺に対して垂直な方向に延伸する線状の第1電極210を形成しても良い。

図25を用いて説明する。図25は変形例に係る半導体装置を示す図であり、このうち(a)は平面図、(b)は図25(a)のB−B線に沿った断面図、(c)は図25(a)のC−C線に沿った断面図である。

図25(a)における左の実線は配線基板200の第1の辺202を示しており、配線基板200は第1の辺202に対して垂直な方向に延伸する線(リード)状の第1の電極210を有する。第1の電極210には特定電極220と通常電極230とが含まれる。配線基板200は表面にソルダーレジスト240を有しており、ソルダーレジスト240は開口240aを有し、同一の開口240a内に特定電極220と通常電極230とを有する。特定電極220は分割部分221、222を有する。分割部分221は、分割部分222よりも面積が大きく、例えば信号線に接続される。分割部分222は、例えばグランドなどの固定電位に接続される。

図25(a)には、配線基板200に搭載されるチップ300の第2電極310上に形成されるはんだ110の領域を1点鎖線および2点鎖線で示す。なお、図25(b)、図25(c)には、はんだ110が2点鎖線の領域に位置する場合の断面を示している。本変形例においても、チップ300を第1の辺202側(図の左側)、一点鎖線上にはんだボール111が位置するように搭載しリフローすることにより、はんだ110を分割部分221に対して選択的に接続することができる。一方で、チップ300を図の右側、つまり図の2点鎖線にはんだボール111が位置するように搭載してリフローすることにより、はんだ110が分割部分221と分割部分222との双方に接続された接続状態を得ることができる。図25(a)の例では、図の上下方向に並ぶ複数の第1電極210が同一の開口240a内に配置されており、それらがソルダーレジスト240によって互いに区画されていない。このため、特に、図25(b)及び図25(c)に示すように、チップ300の第2電極310をポスト状とすることにより、隣接する第1電極210間での意図せぬ短絡を防止することができる。すなわち、図25の例の第2電極310は、例えば、はんだ110よりも高融点の金属からなる柱状の導体であり、例えば、Cuポストである。

また、基板200が、第1の辺202に対して隣接し且つ直交する第2の辺203(不図示)に沿って形成された第2の開口240a(不図示)と、第2の開口240a内に形成された電極210(不図示)とを備える場合、該電極210の幅(該電極210が延伸する方向に対して直交する方向における電極210の長さ)は、第1の開口240aにおける分割部分221と分割部分222との間の距離よりも大きいことが好ましい。これにより、チップ300搭載時の第1の辺202に対する垂直方向でのチップ300のオフセットに関わらず、第2の開口240a内の電極210とチップ300との接続状態を同一とすることができる。

なお、チップ300の第2電極310が千鳥配置の場合であっても、該第2電極310の配置にあわせて、特定電極220の分割部分をずらして配置することにより、同様の効果が得られる。

【符号の説明】

【0115】

100 半導体装置

110 はんだ

111 はんだボール

112 溶融したはんだ

120 アンダーフィル樹脂

200 配線基板

201 基板本体

202 第1の辺

210 第1電極

220 特定電極

220a スリット

221 分割部分(大寸法部)

222、223、224、225 分割部分(小寸法部)

230 通常電極

240 ソルダーレジスト

240a 開口

250 配線

251 配線

252 配線

260 配線

270 はんだボール

300 半導体チップ

310 第2電極

400 リフロー装置

500 吸着ヘッド

600 保護部材

700 絶縁膜

【特許請求の範囲】

【請求項1】

複数の第1電極を一方の面上に有する配線基板と、

前記複数の第1電極とそれぞれ対応して配置された複数の第2電極を一方の面上に有する電子部品と、

を有し、

前記第1電極のうちの少なくとも1つ以上は、複数の分割部分に分割された特定電極であり、

前記分割部分が、各々異なる配線に接続され、

前記分割部分のうちの何れか1つ以上が、対応する前記第2電極とはんだを介して接続されていることを特徴とする電子装置。

【請求項2】

前記第1電極のうちの少なくとも1つ以上は、複数分割されずにその全体が一体的に構成されている通常電極であり、

前記通常電極が、対応する前記第2電極とはんだを介して接続されていることを特徴とする請求項1に記載の電子装置。

【請求項3】

前記複数の分割部分には、

相対的に寸法が大きい大寸法部と、

相対的に寸法が小さい小寸法部と、

が含まれることを特徴とする請求項1又は2に記載の電子装置。

【請求項4】

前記分割部分の各々が対応する前記第2電極と対向していることを特徴とする請求項1乃至3の何れか一項に記載の電子装置。

【請求項5】

前記配線基板の前記一方の面上にはソルダーレジストが形成され、

前記ソルダーレジストには、複数の開口が一定間隔で形成され、

前記第1電極は、それぞれ対応する前記開口内に配置されていることを特徴とする請求項1乃至4の何れか一項に記載の電子装置。

【請求項6】

前記通常電極の径が、前記分割部分どうしの間隔よりも大きいことを特徴とする請求項2に記載の電子装置。

【請求項7】

前記大寸法部が前記特定電極の中央部に配置されていることを特徴とする請求項3に記載の電子装置。

【請求項8】

前記大寸法部の周囲に複数の前記小寸法部が配置されていることを特徴とする請求項7に記載の電子装置。

【請求項9】

前記電子部品と前記配線基板との間隔に樹脂が充填されていることを特徴とする請求項1乃至8の何れか一項に記載の電子装置。

【請求項10】

前記電子部品は半導体チップであることを特徴とする請求項1乃至9の何れか一項に記載の電子装置。

【請求項11】

前記電子部品は半導体パッケージであることを特徴とする請求項1乃至9の何れか一項に記載の電子装置。

【請求項12】

基板本体と、

前記基板本体の一方の面上に形成された複数の第1電極と、

を有し、

前記第1電極のうちの少なくとも1つ以上は、複数の分割部分に分割された特定電極であり、

前記分割部分が、各々異なる配線に接続され、

前記第1電極のうちの他の少なくとも1つ以上は、複数分割されずにその全体が一体的に構成されている通常電極であり、

前記通常電極の径が、前記分割部分どうしの間隔よりも大きいことを特徴とする配線基板。

【請求項13】

当該配線基板を、複数の第2電極が規則的に配置された電子部品と対向させたときに、

前記通常電極がそれぞれ対応する前記第2電極と対向し、

前記特定電極の前記分割部分の各々が対応する前記第2電極と対向することを特徴とする請求項12に記載の配線基板。

【請求項14】

フリップチップ接続用であることを特徴とする請求項12又は13に記載の配線基板。

【請求項15】

複数の第1電極を一方の面上に有する配線基板上に、

前記複数の第1電極とそれぞれ対応して配置された複数の第2電極を一方の面上に有し、前記第1電極のうちの少なくとも1つ以上は複数の分割部分に分割された特定電極であり、前記分割部分が各々異なる配線に接続され、前記第2電極の各々にはんだボールが形成されている電子部品、を搭載する工程と、

前記はんだボールをリフローさせて、前記第2電極の各々を前記第1電極とはんだを介して接続する工程と、

を有し、

前記接続する工程では、前記分割部分のうちの何れか1つ以上を、対応する前記第2電極とはんだを介して接続することを特徴とする電子装置の製造方法。

【請求項16】

前記複数の分割部分には、

相対的に寸法が大きい大寸法部と、

相対的に寸法が小さい小寸法部と、

が含まれ、

前記大寸法部が前記第1電極の中央部に配置され、

前記複数の分割部分の並び方向において、前記第1電極の中心に対して前記第2電極を前記小寸法部側へオフセットさせて前記配線基板上に前記電子部品を搭載した状態で、前記はんだボールを前記リフローさせることにより、前記大寸法部と前記小寸法部とを前記第1電極と接続することを特徴とする請求項15に記載の電子装置の製造方法。

【請求項17】

前記接続する工程では、前記はんだボールをリフローさせた状態で、前記チップを保持して前記配線基板に対して相対的に移動させることにより、前記特定電極の複数の前記分割部分のうち、所望の分割部分上にはんだを濡れ広がらせることを特徴とする請求項15に記載の電子装置の製造方法。

【請求項1】

複数の第1電極を一方の面上に有する配線基板と、

前記複数の第1電極とそれぞれ対応して配置された複数の第2電極を一方の面上に有する電子部品と、

を有し、

前記第1電極のうちの少なくとも1つ以上は、複数の分割部分に分割された特定電極であり、

前記分割部分が、各々異なる配線に接続され、

前記分割部分のうちの何れか1つ以上が、対応する前記第2電極とはんだを介して接続されていることを特徴とする電子装置。

【請求項2】

前記第1電極のうちの少なくとも1つ以上は、複数分割されずにその全体が一体的に構成されている通常電極であり、

前記通常電極が、対応する前記第2電極とはんだを介して接続されていることを特徴とする請求項1に記載の電子装置。

【請求項3】

前記複数の分割部分には、

相対的に寸法が大きい大寸法部と、

相対的に寸法が小さい小寸法部と、

が含まれることを特徴とする請求項1又は2に記載の電子装置。

【請求項4】

前記分割部分の各々が対応する前記第2電極と対向していることを特徴とする請求項1乃至3の何れか一項に記載の電子装置。

【請求項5】

前記配線基板の前記一方の面上にはソルダーレジストが形成され、

前記ソルダーレジストには、複数の開口が一定間隔で形成され、

前記第1電極は、それぞれ対応する前記開口内に配置されていることを特徴とする請求項1乃至4の何れか一項に記載の電子装置。

【請求項6】

前記通常電極の径が、前記分割部分どうしの間隔よりも大きいことを特徴とする請求項2に記載の電子装置。

【請求項7】

前記大寸法部が前記特定電極の中央部に配置されていることを特徴とする請求項3に記載の電子装置。

【請求項8】

前記大寸法部の周囲に複数の前記小寸法部が配置されていることを特徴とする請求項7に記載の電子装置。

【請求項9】

前記電子部品と前記配線基板との間隔に樹脂が充填されていることを特徴とする請求項1乃至8の何れか一項に記載の電子装置。

【請求項10】

前記電子部品は半導体チップであることを特徴とする請求項1乃至9の何れか一項に記載の電子装置。

【請求項11】

前記電子部品は半導体パッケージであることを特徴とする請求項1乃至9の何れか一項に記載の電子装置。

【請求項12】

基板本体と、

前記基板本体の一方の面上に形成された複数の第1電極と、

を有し、

前記第1電極のうちの少なくとも1つ以上は、複数の分割部分に分割された特定電極であり、

前記分割部分が、各々異なる配線に接続され、

前記第1電極のうちの他の少なくとも1つ以上は、複数分割されずにその全体が一体的に構成されている通常電極であり、

前記通常電極の径が、前記分割部分どうしの間隔よりも大きいことを特徴とする配線基板。

【請求項13】

当該配線基板を、複数の第2電極が規則的に配置された電子部品と対向させたときに、

前記通常電極がそれぞれ対応する前記第2電極と対向し、

前記特定電極の前記分割部分の各々が対応する前記第2電極と対向することを特徴とする請求項12に記載の配線基板。

【請求項14】

フリップチップ接続用であることを特徴とする請求項12又は13に記載の配線基板。

【請求項15】

複数の第1電極を一方の面上に有する配線基板上に、

前記複数の第1電極とそれぞれ対応して配置された複数の第2電極を一方の面上に有し、前記第1電極のうちの少なくとも1つ以上は複数の分割部分に分割された特定電極であり、前記分割部分が各々異なる配線に接続され、前記第2電極の各々にはんだボールが形成されている電子部品、を搭載する工程と、

前記はんだボールをリフローさせて、前記第2電極の各々を前記第1電極とはんだを介して接続する工程と、

を有し、

前記接続する工程では、前記分割部分のうちの何れか1つ以上を、対応する前記第2電極とはんだを介して接続することを特徴とする電子装置の製造方法。

【請求項16】

前記複数の分割部分には、

相対的に寸法が大きい大寸法部と、

相対的に寸法が小さい小寸法部と、

が含まれ、

前記大寸法部が前記第1電極の中央部に配置され、

前記複数の分割部分の並び方向において、前記第1電極の中心に対して前記第2電極を前記小寸法部側へオフセットさせて前記配線基板上に前記電子部品を搭載した状態で、前記はんだボールを前記リフローさせることにより、前記大寸法部と前記小寸法部とを前記第1電極と接続することを特徴とする請求項15に記載の電子装置の製造方法。

【請求項17】

前記接続する工程では、前記はんだボールをリフローさせた状態で、前記チップを保持して前記配線基板に対して相対的に移動させることにより、前記特定電極の複数の前記分割部分のうち、所望の分割部分上にはんだを濡れ広がらせることを特徴とする請求項15に記載の電子装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【公開番号】特開2013−74054(P2013−74054A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−211399(P2011−211399)

【出願日】平成23年9月27日(2011.9.27)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月27日(2011.9.27)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]