電子装置およびその製造方法

【課題】グラフェンを活性領域に使った電子装置において、グラフェンにバンドギャップをもたせ、オンオフを可能とする。

【解決手段】電子装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたグラフェンシートと、前記グラフェンシートの一端に形成されたソース電極と、前記グラフェンシートの他端に形成されたドレイン電極と、前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極の間において、前記ソース電極からドレイン電極へのキャリアの流れを横切って形成された、複数の開口部よりなる開口部列と、を備え、前記各々の開口部は少なくとも一つのジグザグ端により画成されており、前記少なくとも一つのジグザグ端は、前記ソース電極とドレイン電極を結んだ方向に対し、いずれも30°の角度をなす。

【解決手段】電子装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたグラフェンシートと、前記グラフェンシートの一端に形成されたソース電極と、前記グラフェンシートの他端に形成されたドレイン電極と、前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極の間において、前記ソース電極からドレイン電極へのキャリアの流れを横切って形成された、複数の開口部よりなる開口部列と、を備え、前記各々の開口部は少なくとも一つのジグザグ端により画成されており、前記少なくとも一つのジグザグ端は、前記ソース電極とドレイン電極を結んだ方向に対し、いずれも30°の角度をなす。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はグラフェンシートを使った電子装置に関する。

【背景技術】

【0002】

グラフェンは例えば黒鉛結晶中において炭素の六角形格子を構成するsp2結合をした炭素原子よりなる原子層であるが、散乱の効果を抑制できれば室温でも200000cm2V-1cm-1を超える非常に大きな電子移動度を達成可能であることから、グラフェンのシートを使って超高速電子装置を作製する研究がなされている。

【0003】

しかしながら黒鉛結晶と同様にグラフェンシートも半金属であり、価電子帯と伝導帯が重なっていてバンドギャップが存在しないため、そのままでは電流のスイッチングに使えない。

【0004】

このため、特許文献1におけるようにグラフェンシートにより幅が10nm以下のリボン状構造を形成し、量子閉じ込め効果によって、バンドギャップを発生させる技術が提案されている。

【0005】

またグラフェンシートに半径が10nm前後の孔をメッシュ状に形成し、形成された孔の周期配列の効果によりバンドギャップを発生させる技術も提案されている(非特許文献1〜3)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−94190号公報

【非特許文献】

【0007】

【非特許文献1】J. Bai et al., Nature Nanotech. 5, 190 (2010)

【非特許文献2】M. Kim et al., Nano. Lett. 10, 1125 (2010)

【非特許文献3】X. Liang et al., Nano Lett. 10, 2454 (2010)

【非特許文献4】K. S. Noveselov, et al., Science 306, 666 (2004)

【非特許文献5】C. Berger, et al., J. Phys. Chem. B 108, 19912 (2004)

【非特許文献6】A. Reina et.al., Nano. Lett. 9, 30 (2009)

【発明の概要】

【発明が解決しようとする課題】

【0008】

図1は、グラフェンシート1の例を示す平面図である。

【0009】

図1を参照するに、グラフェンシート1は先にも述べた通りsp2結合をした炭素原子の六角格子よりなる原子層であるが、このようなグラフェンシート1を構成する六角形格子は、互いに平行で互い違いに配置されたC−C結合1aおよびC−C結合1bを含み全体としては前記C−C結合1aおよび1bの方向に延在する第1のエッジ1Aと、ジグザグに繰り返すC−C(炭素−炭素)結合1cおよび1dを含み、全体としては前記エッジ1Aに直交する方向に延在する第2のエッジ1Bで画成されている。

【0010】

前記第1のエッジ1Aでは、C−C結合1aは次のC−C結合1bに斜めのC−C結合1eで連続し、また前記C−C結合1bが次のC−C結合1aに、斜めのC−C結合1fにより連続し、アームチェア端とよばれる縁部形状をなす。これに対し前記第2のエッジ1Bは前記C−C結合1cとC−C結合1dが繰り返されることからジグザグ端とよばれる形状をなす。

【0011】

このようなアームチェア端をなすエッジ1Aあるいはジグザグ端をなすエッジ1Bでは電子の量子閉じ込め効果が生じ、このため、前記特許文献1ではこのようなアームチェア端あるいはジグザグ端により、グラフェンシートのバンド構造中にバンドギャップを発生させ、電子装置のオン/オフ動作を可能としていた。

【0012】

しかし特許文献1に記載の方法では、チャネルが実効的に前記アームチェア端あるいはジグザグ端に対応して形成されるためチャネル幅が10nm以下と狭くなり、大きな電流を得ようとすると、アームチェア端あるいはジグザグ端を有する多数のリボン状構造をグラフェンシートにより作製し、これらのリボン状構造をソース領域とドレイン領域の間に並列に、かつ高密度に配置する必要がある。このためかかる従来技術では、電子装置の製造工程が複雑になる問題が生じる。

【0013】

また非特許文献1〜3に記載の方法では、孔の二次元周期配列によりバンドギャップを発生させていることから、グラフェンシート中に半径が10nm程度の孔を二次元的に配列させる必要があり、チャネル長が数十ナノメートル程度の微細化された電子装置には使うことができない。さらにこのような10nmオーダーの周期性により形成されたバンドギャップはせいぜい0.1eV程度と小さく、通常の電子装置で使われるような動作電圧で確実にオンオフ動作をさせるのは容易ではない。

【0014】

さらに2層になったグラフェンシートの面に垂直に電場を印加することによりバンドギャップを発生させる技術も提案されているが、かかる構成で得られるバンドギャップの大きさは最大でも0.3eV程度にしかならず、電子装置への適用は困難である。

【課題を解決するための手段】

【0015】

一の側面によれば電子装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたグラフェンシートと、前記グラフェンシートの一端に形成されたソース電極と、前記グラフェンシートの他端に形成されたドレイン電極と、前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極の間において、前記ソース電極とドレイン電極を結ぶ方向を横切って形成された、複数の開口部よりなる開口部列と、を備え、前記各々の開口部は少なくとも一つのジグザグ端により画成されており、前記少なくとも一つのジグザグ端は、前記ソース電極とドレイン電極を結んだ方向に対し、いずれも30°の角度をなす。

【0016】

他の側面によれば電子装置は、基板と、前記基板上に形成されたグラフェンシートと、前記グラフェンシートの一端に形成されたソース電極と、前記グラフェンシートの他端に形成されたドレイン電極と、前記グラフェンシートを前記ソース電極とドレイン電極の間において覆うゲート絶縁膜と、前記ソース電極とドレイン電極の間において前記グラフェンシート上に、前記ゲート絶縁膜を介して形成され、前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、前記ソース電極とドレイン電極の間において、前記グラフェンシートに前記ソース電極とドレイン電極を結ぶ方向を横切って形成された複数の開口部よりなる開口部列と、を備え、前記各々の開口部は少なくとも一つのジグザグ端により画成されており、前記少なくとも一つのジグザグ端は、前記ソース電極とドレイン電極を結んだ方向に対し、いずれも30°の角度をなす。

【0017】

他の側面によれば電子装置の製造方法は、基板上にグラフェンシートを形成する工程と、前記グラフェンシート上に絶縁膜を形成する工程と、前記絶縁膜中にマスク開口部を、形成する工程と、前記グラフェンシートを、前記絶縁膜をマスクにパターニングし、前記グラフェンシート中に前記マスク開口部に対応した開口部を形成する工程と、前記グラフェンシートを非酸化性雰囲気中で熱処理し、前記グラフェンシート中の開口部の形状を安定な形状に変化させる工程と、前記グラフェンシート上に、前記開口部を挟んで一方の側にソース電極を、他方の側にドレイン電極を形成する工程と、を含み、前記マスク開口部を形成する工程は、前記マスク開口部が、前記ソース電極とドレイン電極を結ぶ直線に対し、いずれも時計回り方向あるいは反時計回り方向に30°の角度をなす一または複数の縁部により画成されるように形成される。

【発明の効果】

【0018】

本発明によれば、グラフェンシート中に、キャリアの移動方向に対して30°の角度をなすジグザグ端が形成でき、かかるジグザグ端の効果により、前記グラフェンシートのバンド構造中に、大きな伝導ギャップを形成することが可能となる。

【図面の簡単な説明】

【0019】

【図1】グラフェンの六角形格子を示す平面図である。

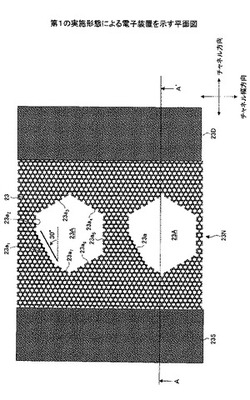

【図2】第1の実施形態による電子装置を示す平面図である。

【図3】図2中、線A−A'に沿った断面図である。

【図4】図2の電子装置においてグラフェンシートに生じるバンドギャップを示すグラフである。

【図5】グラフェンシートに形成される他の開口部の例を示す平面図である。

【図6】グラフェンシートに形成されるさらに他の開口部の例を示す平面図である。

【図7】図2の電子装置において生じる電子透過率とエネルギの関係を示すグラフである。

【図8】図2の電子装置において生じるスイッチング特性を比較対照例のものと比較して示すグラフである。

【図9】第2の実施形態による電子装置を示す平面図である。

【図10】図9の電子装置においてグラフェンシートに生じるバンドギャップを示すグラフである。

【図11】図9の電子装置において生じる電子透過率とエネルギの関係を示すグラフである。

【図12】図9の電子装置において生じるスイッチング特性を、比較対照例および図2の電子装置のものと比較して示すグラフである。

【図13】図2および図9の電子装置の製造方法を説明するフローチャートである。

【図14A】図2および図9の電子装置の製造方法を説明する工程断面図(その1)である。

【図14B】図2および図9の電子装置の製造方法を説明する工程断面図(その2)である。

【図14C】図2および図9の電子装置の製造方法を説明する工程断面図(その3)である。

【図14D】図2および図9の電子装置の製造方法を説明する工程断面図(その4)である。

【図14E】図2および図9の電子装置の製造方法を説明する工程断面図(その5)である。

【図14F】図2および図9の電子装置の製造方法を説明する工程断面図(その6)である。

【図14G】図2および図9の電子装置の製造方法を説明する工程断面図(その7)である。

【図14H】図2および図9の電子装置の製造方法を説明する工程断面図(その8)である。

【図14I】図2および図9の電子装置の製造方法を説明する工程断面図(その9)である。

【図14J】図2および図9の電子装置の製造方法を説明する工程断面図(その10)である。

【図15】グラフェンシートへの開口部のパターニングに使われるマスクの例を示す平面図である。

【図16】第2の実施形態の一変形例によるグラフェンシートを示す平面図である。

【図17】第3の実施形態による電子装置を示す断面図である。

【図18】図17の電子装置の製造方法を説明するフローチャートである。

【図19A】図17の電子装置の製造方法を説明する工程断面図(その1)である。

【図19B】図17の電子装置の製造方法を説明する工程断面図(その2)である。

【図19C】図17の電子装置の製造方法を説明する工程断面図(その3)である。

【図19D】図17の電子装置の製造方法を説明する工程断面図(その4)である。

【図19E】図17の電子装置の製造方法を説明する工程断面図(その5)である。

【図19F】図17の電子装置の製造方法を説明する工程断面図(その6)である。

【図19G】図17の電子装置の製造方法を説明する工程断面図(その7)である。

【図19H】図17の電子装置の製造方法を説明する工程断面図(その8)である。

【図19I】図17の電子装置の製造方法を説明する工程断面図(その9)である。

【図19J】図17の電子装置の製造方法を説明する工程断面図(その10)である。

【図19K】図17の電子装置の製造方法を説明する工程断面図(その11)である。

【発明を実施するための形態】

【0020】

[第1の実施形態]

図2は、第1の実施形態による電子装置20の平面図、図3は、図2中、線A−A'に沿った断面図を示す。

【0021】

最初に図3の断面図を参照するに、例えばp+型にドープされゲート電極を兼用するシリコン基板21上には、ゲート絶縁膜となるシリコン酸化膜22が形成されており、前記シリコン酸化膜22上には前記図1のグラフェンシート1と同様なグラフェンシート23が形成されている。

【0022】

さらに前記シリコン基板21上、前記グラフェンシート23の一方の端にはソース電極23Sが、また他方の端にはドレイン電極23Dが形成されている。

【0023】

前記グラフェンシート23には、図2の平面図に示すように複数の開口部23Aが、前記ソース電極23Sとドレイン電極23Dを結んだ方向(以下、「チャネル方向」と表記する)を横切って、前記チャネル方向に直交するチャネル幅方向に延在する開口部列23Nの形で形成されている。図示の例では各々の開口部23Aは縁部23a1〜23a7により画成されて歪んだ七角形をなしており、前記縁部23a1にはジグザグ端が、また前記縁部23a2〜23a7にはアームチェア端が形成されている。ここで前記「チャネル方向」は、前記ソース電極23Sから前記グラフェンシート23に放出された電子が前記グラフェンシート23中をドレイン電極23Dに向かって走行する方向でもあり、図2における直線A−A'に平行な方向である。

【0024】

図2の構成では前記ソース電極23Sとドレイン電極23Dとは平行に対向しており、前記直線A−A'は前記ソース電極23Sおよびドレイン電極23Dに直交している。

【0025】

図2の構成の電子装置20では、前記グラフェンシート23が前記シリコン基板21上において、グラフェンシート23を構成する炭素原子の六角形格子のうちの平行に対向する一対の縁部が、前記チャネル方向に直交するような向きに配置されており、その結果、前記ジグザグ端23aは、前記チャネル方向に対して反時計回り方向に30°傾いた角度をなしている。

【0026】

図4は、このような構成の電子装置20において、グラフェンシート23に生じるバンドギャップEgの大きさを、(a)前記グラフェンシート23中に形成される開口部23Aの代わりに、図5に示す、正六角形状を有しアームチェア端のみで画成された開口部23Bを形成した場合、および(b)図6に示すように歪んだ七角形状で、一つのジグザグ端23c1と六つのアームチェア端23c2〜23c7を有する開口部23Cを形成した場合と比較して示すグラフである。図4において(c)で示したデータが、図2および図3の電子装置20のものである。図4の計算は、炭素原子一個あたり一つのpz軌道を基底とし、最近接原子間の相互作用のみを考慮した強束縛近似計算により行っている。

【0027】

また図4の計算において、図5および図6でのグラフェンシート23の向きは、図2におけるグラフェンシート23の向きと同じにしており、その結果、図5の構成では前記開口部23Bの正六角形を画成する六つのアームチェア端23b1〜23b6は、前記チャネル方向に対して反時計回り方向に60°または時計回り方向に60°の角度を、あるいは0°の角度をなす。また図6の構成では、前記開口部23Cを画成するジグザグ端23c1は、前記チャネル方向に直交する、すなわちチャネル幅方向の向きを有する一方、前記アームチェア端23c2〜23c7は、前記チャネル方向に対して反時計回り方向あるいは時計回り方向に60°の角度、もしくは0°の角度をなす。

【0028】

図4中、縦軸はこのようにして求められたバンドギャップEgの半値(Eg/2)をエレクトロンボルトの単位で、横軸は、前記キャリアの流れを横切るように配列された開口部列23N中における開口部23A(あるいは開口部23B,23C)の繰り返し周期を、前記六角形状格子をなす炭素六員環一つの大きさを単位として表したものである。また図4中、(c)のデータは図2および3に示す本実施形態の電子装置20についてのものである。

【0029】

なお図2の、グラフェンシート23中に前記開口部23Aにより開口部列23Nを形成した構成の場合、一つの開口部23Aのチャネル幅方向のサイズが、炭素原子六員環15個分の大きさになっているため、図4中で周期が「17」の値の場合には、二つの開口部23Aが前記チャネル幅方向に、炭素原子六員環1ないし2個分の距離を隔てて隣接していることになり、周期の値が事実上の最小値になっている。なおここで「チャネル幅方向」は、前記グラフェンシート23の面内において前記「チャネル方向」に直交する方向を意味する。

【0030】

図4を参照するに、(c)で示す図2および図3の電子装置20の場合には、前記開口部列23N中の開口部23Aの繰り返し周期が17〜19の範囲においてバンドギャップEgが1.2eV以上で1.6eVに近い値(半値Eg/2にして0.6eV以上で0.8eVに近い値)をとるのに対し、図2および図3の電子装置20において、図5の形状の開口部23Bを形成したグラフェンシートを使った場合には、特定の繰り返し周期でしか、高いバンドギャップを得られないことがわかる。

【0031】

ただし図4の結果は、前記グラフェンシート23中に、図5のアームチェア端をなす開口部23Bを形成する場合や、図6の、キャリアの移動方向に直交する向きにジグザグ端を有する開口部23Cを形成する場合でも、開口部列中における開口部の繰り返し周期を最適化すれば、従来の0.3eV程度の値を大きく超えるバンドギャップを実現することが可能であることも示している。

【0032】

図7は、図2のグラフェンシート23において、前記開口部23Aを、炭素六員環17個を1周期として繰り返し配列して開口部列23Nを形成した場合の電子透過率とエネルギの関係を示すグラフである。図中EFはフェルミ準位を表す。

【0033】

図7を参照するに、通常のグラフェンシートではバンドギャップが存在しないのに対し、本実施形態のグラフェンシート23では約1.5eVのバンドギャップエネルギEgが出現しているのがわかる。

【0034】

図8中、曲線Aは、前記図2のグラフェンシート23において、前記開口部23Aを、炭素六員環17個を1周期として繰り返し配列して開口部列23Nを形成し、さらに前記開口部列に直角方向に電流を流した場合の、グラフェンシート23に印加するバイアス電圧と電流密度との関係を、強束縛近似計算の結果から見積もったグラフである。図8中、横軸はバイアス電圧を、縦軸は電流密度を表す。図8において横軸のバイアス電圧はゲート電極として作用するp+型シリコン基板21により前記グラフェンシート23に、ゲート絶縁膜として作用するシリコン酸化膜22を介して印加され、縦軸の電流密度は、前記ソース電極23Sからドレイン電極23Dへ流れる電流の密度である。

【0035】

図8を参照するに、電子装置20においては、導通/非導通のしきい値となる電流密度を0.2μA/nmとした場合、グラフェンシート23を導通させるには1.5Vのバイアス電圧がしきい値電圧(伝導ギャップ)として必要となり、明瞭なしきい値特性が得られているのがわかる。なお図8中、曲線「REF」は、前記グラフェンシート23の代わりに、開口部を形成していないグラフェンを使った場合を示している。

【0036】

また前記図8中、曲線Bは前記開口部23Aの代わりに図5の開口部23Bを形成した場合、また曲線Cは図6の開口部23Cを形成した場合の特性を示しているが、このような場合であっても、開口部列23N中における繰り返し周期を、例えば炭素六員環の径(1.7nm)で18個分、あるいは21個分に最適化すれば、図2の開口部23Aを形成した場合と同等のバンドギャップEgを発生させることが可能であるのがわかる。

【0037】

なおグラフェンシートに前記開口部23A,23B,23Cを含む一般的な開口部を形成した場合の熱力学的に安定な形状は、グラフェンシートを図2あるいは図5,図6に示すように六角形格子の互いに平行な一対の縁部を前記チャネル方向に直交する向きに配置した場合、前記開口部が前記チャネル方向に対し0°,あるいは反時計回りあるいは時計回り方向に30°,あるいは反時計回りあるいは時計回り方向に60°、あるいは90°のいずれかの角度をなす縁部により画成された形状に限定され、このうち0°方向および反時計回りあるいは時計回り方向に60°の角度をなす縁部はアームチェア端となり、反時計回りあるいは時計回り方向に30°の角度をなす縁部、および90°の角度をなす縁部はジグザグ端となる。

【0038】

前記電子装置20の製造工程については、次の実施形態に関連して説明する。

【0039】

[第2の実施形態]

図9は第2の実施形態による電子装置40の構成を示す平面図である。図中、先に説明した部分には対応する参照符号を付し、説明を省略する。また9の断面図は、先に図3で説明したものと同じであり、図示を省略する。

【0040】

図9を参照するに、電子装置40ではグラフェンシート23中に、図2の開口部23Aに代えて図示の例では八角形状の開口部23Eが形成され、前記開口部23Eを前記チャネル幅方向に周期配列させることで前記開口部列23Nを形成しており、各々の開口部23Eは、前記チャネル方向に対して反時計回りに30°傾いた第1のジグザグ端23e1と、時計回り方向に30°傾いた第2のジグザグ端23e2と、さらにアームチェア端23e3〜23e8とよりなる縁部により画成されている。その際、前記開口部23Fにおいて前記アームチェア端23e3と23e6とは前記チャネル方向に延在しており、アームチェア端23e7と23e8とは、前記チャネル方向に対してそれぞれ反時計回り方向および時計回り方向に60°傾いている。またアームチェア端23e4と23e5とは前記チャネル方向に対してそれぞれ反時計回り方向および時計回り方向に60°および60°傾いている。

【0041】

図10は、前記図4の結果に、さらに図9の電子装置40においてグラフェンシート23に生じるバンドギャップEgの大きさを、前記開口部23Eのチャネル幅方向への繰り返し周期の関数として求めた結果を示すグラフである。図4の場合と同様に、バンドギャップEgの計算は、炭素原子一個あたり一つのpz軌道を基底とし、最近接原子間の相互作用のみを考慮した強束縛近似計算により行っている。

【0042】

図10を参照するに、曲線(a)および曲線(c)は図4の曲線(a)および曲線(c)にそれぞれ対応し、前記グラフェンシート23に図5の開口部23Bあるいは図2の開口部23Aを形成することにより前記開口部列23Nを形成した場合のバンドギャップEgと開口部の繰り返し周期の関係を示している。これに対し、曲線(d)は前記図9の実施形態に対応しており、グラフェンシート23中に開口部23Eにより前記開口部列23Nを形成した場合におけるバンドギャップEgと繰り返し周期との関係を示している。

【0043】

図10を参照するに、前記開口部23Eにはチャネル方向に対して反時計回り方向に傾斜したジグザグ端23e1に加えて、時計回り方向にジグザグ端23e2が追加して形成されていることに対応して、グラフェンシート23のバンド構造には、曲線(d)の二倍近い大きなバンドギャップEgが生じること、また開口部23Eの繰り返し周期が最小値である17から増大しても、バンドギャップEgの値の減少は、曲線(a)あるいは(c)の場合よりもゆるやかであることがわかる。

【0044】

図11は、前記図7に対応した、電子装置40中のグラフェンシート23において、前記開口部23Eを、炭素六員環17個を1周期として繰り返し配列して開口部列23Nを形成した場合の電子透過率とエネルギの関係を示すグラフである。図中、比較のため図7に示した電子装置20における電子透過率とエネルギの関係を示している。

【0045】

図11を参照するに、前記電子装置40では、図10の関係に対応して、2.7eVに達する大きなバンドギャップが生じているのがわかる。

【0046】

図12は、前記図8に対応した、グラフェンシート23印加するバイアス電圧と電流密度の関係を、強束縛近似計算の結果から見積もったグラフである。図12中、曲線Aは先の実施形態による電子装置20に対応し、本実施形態による電子装置40の特性は曲線Bにより示されている。なお図8と同様、比較のためグラフェンシート23中に開口部を形成しなかった場合の特性を曲線「Ref」で示している。

【0047】

図12を参照するに、電子装置40ではバンドギャップEgが増大した結果、さらに高い、約2.7Vのしきい値電圧を実現できることがわかる。

【0048】

なお上記の各実施形態において、「グラフェンシート」は、必ずしも、炭素の六角形格子を構成するsp2結合をした炭素原子よりなる厳密に単一の原子層である必要はなく、かかる原子層を複数含んでいてもよい。

【0049】

次に、図13のフローチャートおよび図14A〜図14Lの工程断面図を参照しながら、図9の電子装置40の製造工程について説明する。なお図2および図3で説明した第1の実施形態による電子装置20も同様な製造工程により製造することができる。

【0050】

図13のフローチャートを参照するに、ステップ1において図14Aに示すように、例えばp+型にドープされたシリコン基板21上に、ゲート絶縁膜として作用する厚さが例えば300nmのシリコン酸化膜22を介してグラフェンシート23を形成する。ここで前記シリコン酸化膜22は、前記シリコン基板21の熱酸化などにより形成することができる。なお前記基板21としては、p+型にドープされたシリコン基板以外にも、n+型にドープされたシリコン基板や金属基板など、他の導電性基板を使うことができる。この場合には前記シリコン酸化膜22は例えばスパッタ法などにより形成することができる。

【0051】

次に図13のステップ2において、図14Bに示すように、前記シリコン酸化膜22上にグラフェンシート23を形成する。前記グラフェンシート23は、例えば高配向熱分解グラファイト(Highly Oriented Pyrolytic Graphite;HOPG)や天然グラファイト、キッシュグラファイトなどのバルクグラファイト結晶表面からグラファイト層をスコッチテープ(登録商標)やセロテープ(登録商標)などの粘着テープや粘着シートなどの粘着媒体により機械的に剥離ないしへき開させ、さらにこれを例えば非特許文献4などに記載されているように、別の粘着テープで繰り返しへき開させることにより薄片化するプロセスにより得ることができる。このようにして得られたグラフェンシート23は、さらに粘着媒体ごと、前記シリコン酸化膜22の表面にこすりつけて転写され、図14Bの構造が得られる。

【0052】

あるいは非特許文献5などに記載されているように六方晶系の6H−SiC基板を用意し、これを真空中またはArなど非酸化性雰囲気中、1200℃以上に加熱することで基板表面からSi原子を脱離させることにより、SiC基板表面にSiCの六方晶系の原子配列に依存してグラフェンシートをエピタキシャルに得ることも可能である。この場合にも、得られたグラフェンシートを粘着媒体などに転写し、これを前記シリコン酸化膜22の表面に転写することによって、前記図14Bの構造を得ることができる。

【0053】

また非特許文献6などに記載されているようにグラフェンシートをCVD法で形成することも可能である。この場合には、Fe,Ni,Cuなどの金属触媒をシリコン基板上のシリコン酸化膜表面に堆積し、アセチレンを原料とした熱CVDプロセスを650〜1000℃程度の温度で実行することにより、前記金属触媒上にグラフェンを合成することができる。この場合も、得られたグラフェンを粘着媒体に転写し、さらにこれを前記シリコン酸化膜22の表面に転写することにより、図14Bの構造を得ることができる。

【0054】

次にステップ3において図14Cに示すように、前記グラフェンシート23を覆って、ハードマスクとなるシリコン酸化膜HM1を、例えばCVD法あるいはスパッタ法により、形成し、さらにステップ4において、レジストパターンR1のマスク方位を合わせた上で、前記シリコン酸化膜HM1を図14Dに示すように、前記レジストパターンR1をマスクにパターニングし、前記グラフェンシート23のうち、前記ソース電極23Sが形成されるソース領域23sと前記ドレイン電極23Dが形成されるドレイン領域23dとを、前記ソース領域23sとドレイン領域23dとを結んだ線が、前記グラフェンシート23を構成する炭素の六角形格子のうち、平行に対向して延在する二辺に直交するように、露出させる。

【0055】

さらにステップ5において前記図14Dの構造上にソース電極パターン23S,ドレイン電極パターン23Dとなる金属膜23Mを、図14Eに示すように前記シリコン酸化膜HM1上においてレジストパターンR1をも覆うように例えばスパッタ法あるいは電子ビーム蒸着法などにより堆積し、さらにステップ7において図14Fに示すように前記レジストパターンR1を、その上に堆積した金属膜23M共々リフトオフする。これにより、前記グラフェンシート23のソース領域23sに前記ソース電極パターン23Sが、またドレイン領域23dに前記ドレイン電極パターン23Dが、それぞれ形成される。前記金属膜23Mは、例えば厚さが5nmのTi密着膜(図示せず)と厚さが例えば30nmのAu膜(図示せず)とを順次積層した構造を有してもよい。

【0056】

次にステップ8において前記シリコン酸化膜HM1上にレジスト膜R2が形成され、前記レジスト膜R2中に図15のマスクパターンMを使って図14Gに示すようにレジスト開口部R2Aが、前記マスクパターンM中のマスク開口部23Mに対応して形成される。前記マスク開口部23Mは、前記グラフェンシート23中に形成される開口部列23Eに対応した形状を有しており、前記開口部23Eのジグザグ端23e1および23e2がそれぞれマスク開口部23Mのエッジ23m1および23m2に対応し、また開口部23Eのアームチェア端23e3〜23e8がそれぞれエッジ23m3〜23m8に対応している。

【0057】

ステップ8ではその際、前記マスク開口部23Mの向きが、前記グラフェンシート23中に形成したい開口部23Aの向きに一致するように、前記グラフェンシート23に対して方位を設定される。このようなマスク方位合わせの結果、前記エッジ23m1は前記チャネル方向から反時計回り方向に30°傾いており、一方前記エッジ23m2は、前記チャネル方向から時計回り方向に30°傾いている。

【0058】

前記ステップ8では、さらにこのようにして形成されたレジスト開口部R2Aにより前記シリコン酸化膜HM1が図14Hに示すようにパターニングされ、前記シリコン酸化膜HM1中には前記マスク開口部23Mに対応したマスク開口部HMAが形成される。

【0059】

次にステップ9の工程において前記グラフェンシート23に対し、図14Iに示すように前記シリコン酸化膜HM1をマスクに、例えば10mTorrの圧力下、90Wのプラズマパワーで25sccmの流量で酸素ガスを供給しながら反応性イオンエッチング(RIE)を行い、前記グラフェンシート23に、前記マスク開口部HMAに対応して開口部23Aを、前記グラフェンシート23の方位に対して所定の関係になるように、すなわち開口部23Aのジグザグ端23e1および23e2が、前記チャネル方向に対してそれぞれ反時計回り方向および時計回り方向に30°傾くように、形成する。前記マスクMにおいて前記マスク開口部23Mは図15に示すように開口部列方向に周期的に形成されており、これにより前記グラフェンシート23にはかかる開口部23Aにより開口部列23Nが、前記チャネル幅方向に形成される。

【0060】

さらにステップ10において図14Jに示すように前記シリコン酸化膜HM1を、HFを使ったウェットエッチングにより選択的に除去し、その後、水素雰囲気などの還元雰囲気中、例えば1000°の温度で熱処理することにより、前記開口部23Aの端部における炭素原子の配列を安定化させる。かかる安定化の結果、仮に図14Hの工程でマスクMの方位が僅かにずれていたとしても、前記開口部23Aの縁部において炭素原子は再配列し、前記チャネル方向に反時計回り方向あるいは時計回り方向に30°の角度のジグザグ端が安定に得られる。

【0061】

先の第1の実施形態の電子装置20においても上記の製造方法を適用することができる。

【0062】

なお本実施形態において、図9の開口部23Eの代わりに、図16に示すように、チャネル幅方向に互いに対向し、チャネル方向に対してそれぞれ反時計回り方向および時計回り方向に30°傾いたジグザグ端23f1および23f2と、チャネル幅方向に互いに対向し、チャネル方向に対してそれぞれ時計回り方向および反時計回り方向に30°傾いたジグザグ端23f3および23f4とを含む縁部で画成された開口部23Fを形成することも可能である。図16の構成では、チャネル方向に対して30°傾いたジグザグ端の数が増加するため、バンドギャップEgをさらに増大させることができる。

【0063】

図16の構成でも、開口部23Fはチャネル幅方向に繰り返し形成されている。

【0064】

[第3の実施形態]

図17は、第3の実施形態による電子装置60の構成を示す断面図である。図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0065】

図17を参照するに、電子装置60は6H−SiC基板61の(0001)面上に形成されており、前記(0001)面上に直接に形成され、前記図2あるいは図9、あるいは図16の平面図に示した開口部23A,23Eあるいは23Fにより開口部列23Nを形成されたグラフェンシート23と、前記グラフェンシート23上に、前記グラフェンシート23を構成する炭素原子の六角形格子のうち、平行に対向する二辺に対して直交する向きにおいて相互に対向するように形成されたソース電極23Sおよびドレイン電極23Dを含む。

【0066】

さらに前記グラフェンシート23は、前記開口部列23Nごと、たとえは厚さが10nmの酸化ハフニウム(HfO2)よりなるゲート絶縁膜62により覆われ、前記ゲート絶縁膜62上には、厚さが例えば5nmのチタン(Ti)膜と厚さが例えば30nmの金(Au)膜とを順次積層した構成のゲート電極63が形成されている。

【0067】

なお図示の構成ではソース電極23Sおよびドレイン電極23Dも前記酸化ハフニウム膜62により覆われており、前記酸化ハフニウム膜62には前記ソース電極23Sおよび23Dに対応して図示しないビアホールが形成される。

【0068】

かかる構成の電子装置でも、前記ソース電極23Sとドレイン電極23Dとが、前記ソース電極23Sとドレイン電極23Dとを結んだ直線が、前記グラフェンシート23Sを構成する炭素の六角形格子のうち相対向する二辺に対して直交するような向きに形成されているため、先の図2あるいは図9あるいは図16の実施形態と同様に、前記グラフェンシート23中には、前記チャネル方向に対して時計回り方向あるいは反時計回り方向に30°傾いたジグザグ端が形成されており、その結果、前記グラフェンシート23は、図4あるいは図10よりわかるように、1.6eV以上、あるいは2.8eV以上の大きなバンドギャップEgを示す。このため図17の電子装置17においても、前記ソース電極23Sからドレイン電極62Dへの電子の流れを、前記ゲート電極63に印加したゲート電圧により確実に制御することが可能となる。

【0069】

以下、図17の電子装置60の製造方法を、図18のフローチャートおよび図19A〜図19Kの工程断面図を参照しながら説明する。図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0070】

図18を参照するに、ステップ21において図19Aに示すように(0001)面を主面とする6H−SiC基板61を準備し、ステップ22において前記6H−SiC基板を真空中、あるいは1200°以上のアルゴン(Ar)など非酸化雰囲気中において熱処理し、前記基板21の主面を画成する(0001)面からSi元素を脱離させる。その結果、(0001)面よりなる前記6H−SiC基板21の主面には、図19Bに示すように六方晶系配列した炭素原子よりなる炭素原子層が残り、所望のグラフェンシート23がエピタキシャルに形成される。

【0071】

次に図18のステップ23において図19Cに示すようにシリコン酸化膜よりなるハードマスク膜HM1を、例えばスパッタ法やCVD法により形成し、ステップ24において前記ハードマスク膜HM1を、レジストパターンR1をマスクにパターニングして、図19Dに示すように前記グラフェンシート23のうち、ソース領域23sとドレイン領域23dとを露出する。

【0072】

さらに図18のステップ25において前記図19Dの構造上に、厚さが5nmのチタン膜と厚さが30nmの金膜とを、電子ビーム蒸着法あるいはスパッタ法により順次堆積して図19Eに示す金属膜23Mを形成し、さらに図18のステップ26において図19Fに示すように前記レジストパターンR1をその上の金属膜23M共々リフトオフし、前記グラフェンシート23のソース領域23sにソース電極23Sを、またドレイン領域23dにドレイン電極23Dを、それぞれ形成する。

【0073】

さらに図18のステップ27において前記ハードマスク膜HM1を、例えば図15で説明したマスクMを使ってパターニングして、図19Gに示すように前記グラフェンシート23を露出する開口部HMAを形成し、ステップ28において前記グラフェンシート23を、前記ハードマスク膜HM1をマスクにパターニングし、図19Hに示すように前記グラフェンシート23中に、例えば開口部23Aよりなる開口部列23Nを形成する。前記ステップ28において、前記開口部23Aの代わりに開口部23Eあるいは23Fを形成することも可能である。

【0074】

さらに図18のステップ29において、前記グラフェンシート23を水素雰囲気など還元雰囲気中、例えば1000°の温度で熱処理し、先に形成された開口部23Aなどの縁部における炭素原子の配列を安定化させる。さらにステップ30において図19Iに示すようにハードマスク膜HM1をたとえはHFによるウェット処理により除去し、さらにステップ31において図19Jに示すように、ゲート絶縁膜62を前記グラフェンシート23上に形成する。図示の例では、前記ゲート絶縁膜62として酸化ハフニウム(HfO2)膜を使っているが、酸化ジルコニウム(ZrO2)膜やハフニウムシリケート(HfSiO4)膜やハフニウムジルコネート(ZrSiO4)膜などを使うことも可能である。

【0075】

さらにステップ32において前記ゲート絶縁膜62上に前記ソース電極パターン23Sあるいはドレイン電極パターン23Dと同様な、Ti膜と金膜の積層構造のゲート電極63を形成することにより、図19Kに示すようにトップゲート構造の電子装置を得ることができる。

【0076】

以上、本発明を好ましい実施形態について説明したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

【符号の説明】

【0077】

1,23 グラフェンシート

1A アームチェア端

1B ジグザグ端

1a,1b,1c,1d,1e C−C結合

20,40,60 電子装置

21 シリコン基板

23A,23B,23C,23E,23F 開口部

23a1〜23a7,23b1〜23b6,23c1〜23c7,23e1〜23e8,23f1〜23f4 縁部

23N 開口部列

23M マスク開口部

23m1〜23m8 エッジ

23S ソース電極パターン

23D ドレイン電極パターン

61 SiC基板

62 ゲート絶縁膜

63 ゲート電極

【技術分野】

【0001】

本発明はグラフェンシートを使った電子装置に関する。

【背景技術】

【0002】

グラフェンは例えば黒鉛結晶中において炭素の六角形格子を構成するsp2結合をした炭素原子よりなる原子層であるが、散乱の効果を抑制できれば室温でも200000cm2V-1cm-1を超える非常に大きな電子移動度を達成可能であることから、グラフェンのシートを使って超高速電子装置を作製する研究がなされている。

【0003】

しかしながら黒鉛結晶と同様にグラフェンシートも半金属であり、価電子帯と伝導帯が重なっていてバンドギャップが存在しないため、そのままでは電流のスイッチングに使えない。

【0004】

このため、特許文献1におけるようにグラフェンシートにより幅が10nm以下のリボン状構造を形成し、量子閉じ込め効果によって、バンドギャップを発生させる技術が提案されている。

【0005】

またグラフェンシートに半径が10nm前後の孔をメッシュ状に形成し、形成された孔の周期配列の効果によりバンドギャップを発生させる技術も提案されている(非特許文献1〜3)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−94190号公報

【非特許文献】

【0007】

【非特許文献1】J. Bai et al., Nature Nanotech. 5, 190 (2010)

【非特許文献2】M. Kim et al., Nano. Lett. 10, 1125 (2010)

【非特許文献3】X. Liang et al., Nano Lett. 10, 2454 (2010)

【非特許文献4】K. S. Noveselov, et al., Science 306, 666 (2004)

【非特許文献5】C. Berger, et al., J. Phys. Chem. B 108, 19912 (2004)

【非特許文献6】A. Reina et.al., Nano. Lett. 9, 30 (2009)

【発明の概要】

【発明が解決しようとする課題】

【0008】

図1は、グラフェンシート1の例を示す平面図である。

【0009】

図1を参照するに、グラフェンシート1は先にも述べた通りsp2結合をした炭素原子の六角格子よりなる原子層であるが、このようなグラフェンシート1を構成する六角形格子は、互いに平行で互い違いに配置されたC−C結合1aおよびC−C結合1bを含み全体としては前記C−C結合1aおよび1bの方向に延在する第1のエッジ1Aと、ジグザグに繰り返すC−C(炭素−炭素)結合1cおよび1dを含み、全体としては前記エッジ1Aに直交する方向に延在する第2のエッジ1Bで画成されている。

【0010】

前記第1のエッジ1Aでは、C−C結合1aは次のC−C結合1bに斜めのC−C結合1eで連続し、また前記C−C結合1bが次のC−C結合1aに、斜めのC−C結合1fにより連続し、アームチェア端とよばれる縁部形状をなす。これに対し前記第2のエッジ1Bは前記C−C結合1cとC−C結合1dが繰り返されることからジグザグ端とよばれる形状をなす。

【0011】

このようなアームチェア端をなすエッジ1Aあるいはジグザグ端をなすエッジ1Bでは電子の量子閉じ込め効果が生じ、このため、前記特許文献1ではこのようなアームチェア端あるいはジグザグ端により、グラフェンシートのバンド構造中にバンドギャップを発生させ、電子装置のオン/オフ動作を可能としていた。

【0012】

しかし特許文献1に記載の方法では、チャネルが実効的に前記アームチェア端あるいはジグザグ端に対応して形成されるためチャネル幅が10nm以下と狭くなり、大きな電流を得ようとすると、アームチェア端あるいはジグザグ端を有する多数のリボン状構造をグラフェンシートにより作製し、これらのリボン状構造をソース領域とドレイン領域の間に並列に、かつ高密度に配置する必要がある。このためかかる従来技術では、電子装置の製造工程が複雑になる問題が生じる。

【0013】

また非特許文献1〜3に記載の方法では、孔の二次元周期配列によりバンドギャップを発生させていることから、グラフェンシート中に半径が10nm程度の孔を二次元的に配列させる必要があり、チャネル長が数十ナノメートル程度の微細化された電子装置には使うことができない。さらにこのような10nmオーダーの周期性により形成されたバンドギャップはせいぜい0.1eV程度と小さく、通常の電子装置で使われるような動作電圧で確実にオンオフ動作をさせるのは容易ではない。

【0014】

さらに2層になったグラフェンシートの面に垂直に電場を印加することによりバンドギャップを発生させる技術も提案されているが、かかる構成で得られるバンドギャップの大きさは最大でも0.3eV程度にしかならず、電子装置への適用は困難である。

【課題を解決するための手段】

【0015】

一の側面によれば電子装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたグラフェンシートと、前記グラフェンシートの一端に形成されたソース電極と、前記グラフェンシートの他端に形成されたドレイン電極と、前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極の間において、前記ソース電極とドレイン電極を結ぶ方向を横切って形成された、複数の開口部よりなる開口部列と、を備え、前記各々の開口部は少なくとも一つのジグザグ端により画成されており、前記少なくとも一つのジグザグ端は、前記ソース電極とドレイン電極を結んだ方向に対し、いずれも30°の角度をなす。

【0016】

他の側面によれば電子装置は、基板と、前記基板上に形成されたグラフェンシートと、前記グラフェンシートの一端に形成されたソース電極と、前記グラフェンシートの他端に形成されたドレイン電極と、前記グラフェンシートを前記ソース電極とドレイン電極の間において覆うゲート絶縁膜と、前記ソース電極とドレイン電極の間において前記グラフェンシート上に、前記ゲート絶縁膜を介して形成され、前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、前記ソース電極とドレイン電極の間において、前記グラフェンシートに前記ソース電極とドレイン電極を結ぶ方向を横切って形成された複数の開口部よりなる開口部列と、を備え、前記各々の開口部は少なくとも一つのジグザグ端により画成されており、前記少なくとも一つのジグザグ端は、前記ソース電極とドレイン電極を結んだ方向に対し、いずれも30°の角度をなす。

【0017】

他の側面によれば電子装置の製造方法は、基板上にグラフェンシートを形成する工程と、前記グラフェンシート上に絶縁膜を形成する工程と、前記絶縁膜中にマスク開口部を、形成する工程と、前記グラフェンシートを、前記絶縁膜をマスクにパターニングし、前記グラフェンシート中に前記マスク開口部に対応した開口部を形成する工程と、前記グラフェンシートを非酸化性雰囲気中で熱処理し、前記グラフェンシート中の開口部の形状を安定な形状に変化させる工程と、前記グラフェンシート上に、前記開口部を挟んで一方の側にソース電極を、他方の側にドレイン電極を形成する工程と、を含み、前記マスク開口部を形成する工程は、前記マスク開口部が、前記ソース電極とドレイン電極を結ぶ直線に対し、いずれも時計回り方向あるいは反時計回り方向に30°の角度をなす一または複数の縁部により画成されるように形成される。

【発明の効果】

【0018】

本発明によれば、グラフェンシート中に、キャリアの移動方向に対して30°の角度をなすジグザグ端が形成でき、かかるジグザグ端の効果により、前記グラフェンシートのバンド構造中に、大きな伝導ギャップを形成することが可能となる。

【図面の簡単な説明】

【0019】

【図1】グラフェンの六角形格子を示す平面図である。

【図2】第1の実施形態による電子装置を示す平面図である。

【図3】図2中、線A−A'に沿った断面図である。

【図4】図2の電子装置においてグラフェンシートに生じるバンドギャップを示すグラフである。

【図5】グラフェンシートに形成される他の開口部の例を示す平面図である。

【図6】グラフェンシートに形成されるさらに他の開口部の例を示す平面図である。

【図7】図2の電子装置において生じる電子透過率とエネルギの関係を示すグラフである。

【図8】図2の電子装置において生じるスイッチング特性を比較対照例のものと比較して示すグラフである。

【図9】第2の実施形態による電子装置を示す平面図である。

【図10】図9の電子装置においてグラフェンシートに生じるバンドギャップを示すグラフである。

【図11】図9の電子装置において生じる電子透過率とエネルギの関係を示すグラフである。

【図12】図9の電子装置において生じるスイッチング特性を、比較対照例および図2の電子装置のものと比較して示すグラフである。

【図13】図2および図9の電子装置の製造方法を説明するフローチャートである。

【図14A】図2および図9の電子装置の製造方法を説明する工程断面図(その1)である。

【図14B】図2および図9の電子装置の製造方法を説明する工程断面図(その2)である。

【図14C】図2および図9の電子装置の製造方法を説明する工程断面図(その3)である。

【図14D】図2および図9の電子装置の製造方法を説明する工程断面図(その4)である。

【図14E】図2および図9の電子装置の製造方法を説明する工程断面図(その5)である。

【図14F】図2および図9の電子装置の製造方法を説明する工程断面図(その6)である。

【図14G】図2および図9の電子装置の製造方法を説明する工程断面図(その7)である。

【図14H】図2および図9の電子装置の製造方法を説明する工程断面図(その8)である。

【図14I】図2および図9の電子装置の製造方法を説明する工程断面図(その9)である。

【図14J】図2および図9の電子装置の製造方法を説明する工程断面図(その10)である。

【図15】グラフェンシートへの開口部のパターニングに使われるマスクの例を示す平面図である。

【図16】第2の実施形態の一変形例によるグラフェンシートを示す平面図である。

【図17】第3の実施形態による電子装置を示す断面図である。

【図18】図17の電子装置の製造方法を説明するフローチャートである。

【図19A】図17の電子装置の製造方法を説明する工程断面図(その1)である。

【図19B】図17の電子装置の製造方法を説明する工程断面図(その2)である。

【図19C】図17の電子装置の製造方法を説明する工程断面図(その3)である。

【図19D】図17の電子装置の製造方法を説明する工程断面図(その4)である。

【図19E】図17の電子装置の製造方法を説明する工程断面図(その5)である。

【図19F】図17の電子装置の製造方法を説明する工程断面図(その6)である。

【図19G】図17の電子装置の製造方法を説明する工程断面図(その7)である。

【図19H】図17の電子装置の製造方法を説明する工程断面図(その8)である。

【図19I】図17の電子装置の製造方法を説明する工程断面図(その9)である。

【図19J】図17の電子装置の製造方法を説明する工程断面図(その10)である。

【図19K】図17の電子装置の製造方法を説明する工程断面図(その11)である。

【発明を実施するための形態】

【0020】

[第1の実施形態]

図2は、第1の実施形態による電子装置20の平面図、図3は、図2中、線A−A'に沿った断面図を示す。

【0021】

最初に図3の断面図を参照するに、例えばp+型にドープされゲート電極を兼用するシリコン基板21上には、ゲート絶縁膜となるシリコン酸化膜22が形成されており、前記シリコン酸化膜22上には前記図1のグラフェンシート1と同様なグラフェンシート23が形成されている。

【0022】

さらに前記シリコン基板21上、前記グラフェンシート23の一方の端にはソース電極23Sが、また他方の端にはドレイン電極23Dが形成されている。

【0023】

前記グラフェンシート23には、図2の平面図に示すように複数の開口部23Aが、前記ソース電極23Sとドレイン電極23Dを結んだ方向(以下、「チャネル方向」と表記する)を横切って、前記チャネル方向に直交するチャネル幅方向に延在する開口部列23Nの形で形成されている。図示の例では各々の開口部23Aは縁部23a1〜23a7により画成されて歪んだ七角形をなしており、前記縁部23a1にはジグザグ端が、また前記縁部23a2〜23a7にはアームチェア端が形成されている。ここで前記「チャネル方向」は、前記ソース電極23Sから前記グラフェンシート23に放出された電子が前記グラフェンシート23中をドレイン電極23Dに向かって走行する方向でもあり、図2における直線A−A'に平行な方向である。

【0024】

図2の構成では前記ソース電極23Sとドレイン電極23Dとは平行に対向しており、前記直線A−A'は前記ソース電極23Sおよびドレイン電極23Dに直交している。

【0025】

図2の構成の電子装置20では、前記グラフェンシート23が前記シリコン基板21上において、グラフェンシート23を構成する炭素原子の六角形格子のうちの平行に対向する一対の縁部が、前記チャネル方向に直交するような向きに配置されており、その結果、前記ジグザグ端23aは、前記チャネル方向に対して反時計回り方向に30°傾いた角度をなしている。

【0026】

図4は、このような構成の電子装置20において、グラフェンシート23に生じるバンドギャップEgの大きさを、(a)前記グラフェンシート23中に形成される開口部23Aの代わりに、図5に示す、正六角形状を有しアームチェア端のみで画成された開口部23Bを形成した場合、および(b)図6に示すように歪んだ七角形状で、一つのジグザグ端23c1と六つのアームチェア端23c2〜23c7を有する開口部23Cを形成した場合と比較して示すグラフである。図4において(c)で示したデータが、図2および図3の電子装置20のものである。図4の計算は、炭素原子一個あたり一つのpz軌道を基底とし、最近接原子間の相互作用のみを考慮した強束縛近似計算により行っている。

【0027】

また図4の計算において、図5および図6でのグラフェンシート23の向きは、図2におけるグラフェンシート23の向きと同じにしており、その結果、図5の構成では前記開口部23Bの正六角形を画成する六つのアームチェア端23b1〜23b6は、前記チャネル方向に対して反時計回り方向に60°または時計回り方向に60°の角度を、あるいは0°の角度をなす。また図6の構成では、前記開口部23Cを画成するジグザグ端23c1は、前記チャネル方向に直交する、すなわちチャネル幅方向の向きを有する一方、前記アームチェア端23c2〜23c7は、前記チャネル方向に対して反時計回り方向あるいは時計回り方向に60°の角度、もしくは0°の角度をなす。

【0028】

図4中、縦軸はこのようにして求められたバンドギャップEgの半値(Eg/2)をエレクトロンボルトの単位で、横軸は、前記キャリアの流れを横切るように配列された開口部列23N中における開口部23A(あるいは開口部23B,23C)の繰り返し周期を、前記六角形状格子をなす炭素六員環一つの大きさを単位として表したものである。また図4中、(c)のデータは図2および3に示す本実施形態の電子装置20についてのものである。

【0029】

なお図2の、グラフェンシート23中に前記開口部23Aにより開口部列23Nを形成した構成の場合、一つの開口部23Aのチャネル幅方向のサイズが、炭素原子六員環15個分の大きさになっているため、図4中で周期が「17」の値の場合には、二つの開口部23Aが前記チャネル幅方向に、炭素原子六員環1ないし2個分の距離を隔てて隣接していることになり、周期の値が事実上の最小値になっている。なおここで「チャネル幅方向」は、前記グラフェンシート23の面内において前記「チャネル方向」に直交する方向を意味する。

【0030】

図4を参照するに、(c)で示す図2および図3の電子装置20の場合には、前記開口部列23N中の開口部23Aの繰り返し周期が17〜19の範囲においてバンドギャップEgが1.2eV以上で1.6eVに近い値(半値Eg/2にして0.6eV以上で0.8eVに近い値)をとるのに対し、図2および図3の電子装置20において、図5の形状の開口部23Bを形成したグラフェンシートを使った場合には、特定の繰り返し周期でしか、高いバンドギャップを得られないことがわかる。

【0031】

ただし図4の結果は、前記グラフェンシート23中に、図5のアームチェア端をなす開口部23Bを形成する場合や、図6の、キャリアの移動方向に直交する向きにジグザグ端を有する開口部23Cを形成する場合でも、開口部列中における開口部の繰り返し周期を最適化すれば、従来の0.3eV程度の値を大きく超えるバンドギャップを実現することが可能であることも示している。

【0032】

図7は、図2のグラフェンシート23において、前記開口部23Aを、炭素六員環17個を1周期として繰り返し配列して開口部列23Nを形成した場合の電子透過率とエネルギの関係を示すグラフである。図中EFはフェルミ準位を表す。

【0033】

図7を参照するに、通常のグラフェンシートではバンドギャップが存在しないのに対し、本実施形態のグラフェンシート23では約1.5eVのバンドギャップエネルギEgが出現しているのがわかる。

【0034】

図8中、曲線Aは、前記図2のグラフェンシート23において、前記開口部23Aを、炭素六員環17個を1周期として繰り返し配列して開口部列23Nを形成し、さらに前記開口部列に直角方向に電流を流した場合の、グラフェンシート23に印加するバイアス電圧と電流密度との関係を、強束縛近似計算の結果から見積もったグラフである。図8中、横軸はバイアス電圧を、縦軸は電流密度を表す。図8において横軸のバイアス電圧はゲート電極として作用するp+型シリコン基板21により前記グラフェンシート23に、ゲート絶縁膜として作用するシリコン酸化膜22を介して印加され、縦軸の電流密度は、前記ソース電極23Sからドレイン電極23Dへ流れる電流の密度である。

【0035】

図8を参照するに、電子装置20においては、導通/非導通のしきい値となる電流密度を0.2μA/nmとした場合、グラフェンシート23を導通させるには1.5Vのバイアス電圧がしきい値電圧(伝導ギャップ)として必要となり、明瞭なしきい値特性が得られているのがわかる。なお図8中、曲線「REF」は、前記グラフェンシート23の代わりに、開口部を形成していないグラフェンを使った場合を示している。

【0036】

また前記図8中、曲線Bは前記開口部23Aの代わりに図5の開口部23Bを形成した場合、また曲線Cは図6の開口部23Cを形成した場合の特性を示しているが、このような場合であっても、開口部列23N中における繰り返し周期を、例えば炭素六員環の径(1.7nm)で18個分、あるいは21個分に最適化すれば、図2の開口部23Aを形成した場合と同等のバンドギャップEgを発生させることが可能であるのがわかる。

【0037】

なおグラフェンシートに前記開口部23A,23B,23Cを含む一般的な開口部を形成した場合の熱力学的に安定な形状は、グラフェンシートを図2あるいは図5,図6に示すように六角形格子の互いに平行な一対の縁部を前記チャネル方向に直交する向きに配置した場合、前記開口部が前記チャネル方向に対し0°,あるいは反時計回りあるいは時計回り方向に30°,あるいは反時計回りあるいは時計回り方向に60°、あるいは90°のいずれかの角度をなす縁部により画成された形状に限定され、このうち0°方向および反時計回りあるいは時計回り方向に60°の角度をなす縁部はアームチェア端となり、反時計回りあるいは時計回り方向に30°の角度をなす縁部、および90°の角度をなす縁部はジグザグ端となる。

【0038】

前記電子装置20の製造工程については、次の実施形態に関連して説明する。

【0039】

[第2の実施形態]

図9は第2の実施形態による電子装置40の構成を示す平面図である。図中、先に説明した部分には対応する参照符号を付し、説明を省略する。また9の断面図は、先に図3で説明したものと同じであり、図示を省略する。

【0040】

図9を参照するに、電子装置40ではグラフェンシート23中に、図2の開口部23Aに代えて図示の例では八角形状の開口部23Eが形成され、前記開口部23Eを前記チャネル幅方向に周期配列させることで前記開口部列23Nを形成しており、各々の開口部23Eは、前記チャネル方向に対して反時計回りに30°傾いた第1のジグザグ端23e1と、時計回り方向に30°傾いた第2のジグザグ端23e2と、さらにアームチェア端23e3〜23e8とよりなる縁部により画成されている。その際、前記開口部23Fにおいて前記アームチェア端23e3と23e6とは前記チャネル方向に延在しており、アームチェア端23e7と23e8とは、前記チャネル方向に対してそれぞれ反時計回り方向および時計回り方向に60°傾いている。またアームチェア端23e4と23e5とは前記チャネル方向に対してそれぞれ反時計回り方向および時計回り方向に60°および60°傾いている。

【0041】

図10は、前記図4の結果に、さらに図9の電子装置40においてグラフェンシート23に生じるバンドギャップEgの大きさを、前記開口部23Eのチャネル幅方向への繰り返し周期の関数として求めた結果を示すグラフである。図4の場合と同様に、バンドギャップEgの計算は、炭素原子一個あたり一つのpz軌道を基底とし、最近接原子間の相互作用のみを考慮した強束縛近似計算により行っている。

【0042】

図10を参照するに、曲線(a)および曲線(c)は図4の曲線(a)および曲線(c)にそれぞれ対応し、前記グラフェンシート23に図5の開口部23Bあるいは図2の開口部23Aを形成することにより前記開口部列23Nを形成した場合のバンドギャップEgと開口部の繰り返し周期の関係を示している。これに対し、曲線(d)は前記図9の実施形態に対応しており、グラフェンシート23中に開口部23Eにより前記開口部列23Nを形成した場合におけるバンドギャップEgと繰り返し周期との関係を示している。

【0043】

図10を参照するに、前記開口部23Eにはチャネル方向に対して反時計回り方向に傾斜したジグザグ端23e1に加えて、時計回り方向にジグザグ端23e2が追加して形成されていることに対応して、グラフェンシート23のバンド構造には、曲線(d)の二倍近い大きなバンドギャップEgが生じること、また開口部23Eの繰り返し周期が最小値である17から増大しても、バンドギャップEgの値の減少は、曲線(a)あるいは(c)の場合よりもゆるやかであることがわかる。

【0044】

図11は、前記図7に対応した、電子装置40中のグラフェンシート23において、前記開口部23Eを、炭素六員環17個を1周期として繰り返し配列して開口部列23Nを形成した場合の電子透過率とエネルギの関係を示すグラフである。図中、比較のため図7に示した電子装置20における電子透過率とエネルギの関係を示している。

【0045】

図11を参照するに、前記電子装置40では、図10の関係に対応して、2.7eVに達する大きなバンドギャップが生じているのがわかる。

【0046】

図12は、前記図8に対応した、グラフェンシート23印加するバイアス電圧と電流密度の関係を、強束縛近似計算の結果から見積もったグラフである。図12中、曲線Aは先の実施形態による電子装置20に対応し、本実施形態による電子装置40の特性は曲線Bにより示されている。なお図8と同様、比較のためグラフェンシート23中に開口部を形成しなかった場合の特性を曲線「Ref」で示している。

【0047】

図12を参照するに、電子装置40ではバンドギャップEgが増大した結果、さらに高い、約2.7Vのしきい値電圧を実現できることがわかる。

【0048】

なお上記の各実施形態において、「グラフェンシート」は、必ずしも、炭素の六角形格子を構成するsp2結合をした炭素原子よりなる厳密に単一の原子層である必要はなく、かかる原子層を複数含んでいてもよい。

【0049】

次に、図13のフローチャートおよび図14A〜図14Lの工程断面図を参照しながら、図9の電子装置40の製造工程について説明する。なお図2および図3で説明した第1の実施形態による電子装置20も同様な製造工程により製造することができる。

【0050】

図13のフローチャートを参照するに、ステップ1において図14Aに示すように、例えばp+型にドープされたシリコン基板21上に、ゲート絶縁膜として作用する厚さが例えば300nmのシリコン酸化膜22を介してグラフェンシート23を形成する。ここで前記シリコン酸化膜22は、前記シリコン基板21の熱酸化などにより形成することができる。なお前記基板21としては、p+型にドープされたシリコン基板以外にも、n+型にドープされたシリコン基板や金属基板など、他の導電性基板を使うことができる。この場合には前記シリコン酸化膜22は例えばスパッタ法などにより形成することができる。

【0051】

次に図13のステップ2において、図14Bに示すように、前記シリコン酸化膜22上にグラフェンシート23を形成する。前記グラフェンシート23は、例えば高配向熱分解グラファイト(Highly Oriented Pyrolytic Graphite;HOPG)や天然グラファイト、キッシュグラファイトなどのバルクグラファイト結晶表面からグラファイト層をスコッチテープ(登録商標)やセロテープ(登録商標)などの粘着テープや粘着シートなどの粘着媒体により機械的に剥離ないしへき開させ、さらにこれを例えば非特許文献4などに記載されているように、別の粘着テープで繰り返しへき開させることにより薄片化するプロセスにより得ることができる。このようにして得られたグラフェンシート23は、さらに粘着媒体ごと、前記シリコン酸化膜22の表面にこすりつけて転写され、図14Bの構造が得られる。

【0052】

あるいは非特許文献5などに記載されているように六方晶系の6H−SiC基板を用意し、これを真空中またはArなど非酸化性雰囲気中、1200℃以上に加熱することで基板表面からSi原子を脱離させることにより、SiC基板表面にSiCの六方晶系の原子配列に依存してグラフェンシートをエピタキシャルに得ることも可能である。この場合にも、得られたグラフェンシートを粘着媒体などに転写し、これを前記シリコン酸化膜22の表面に転写することによって、前記図14Bの構造を得ることができる。

【0053】

また非特許文献6などに記載されているようにグラフェンシートをCVD法で形成することも可能である。この場合には、Fe,Ni,Cuなどの金属触媒をシリコン基板上のシリコン酸化膜表面に堆積し、アセチレンを原料とした熱CVDプロセスを650〜1000℃程度の温度で実行することにより、前記金属触媒上にグラフェンを合成することができる。この場合も、得られたグラフェンを粘着媒体に転写し、さらにこれを前記シリコン酸化膜22の表面に転写することにより、図14Bの構造を得ることができる。

【0054】

次にステップ3において図14Cに示すように、前記グラフェンシート23を覆って、ハードマスクとなるシリコン酸化膜HM1を、例えばCVD法あるいはスパッタ法により、形成し、さらにステップ4において、レジストパターンR1のマスク方位を合わせた上で、前記シリコン酸化膜HM1を図14Dに示すように、前記レジストパターンR1をマスクにパターニングし、前記グラフェンシート23のうち、前記ソース電極23Sが形成されるソース領域23sと前記ドレイン電極23Dが形成されるドレイン領域23dとを、前記ソース領域23sとドレイン領域23dとを結んだ線が、前記グラフェンシート23を構成する炭素の六角形格子のうち、平行に対向して延在する二辺に直交するように、露出させる。

【0055】

さらにステップ5において前記図14Dの構造上にソース電極パターン23S,ドレイン電極パターン23Dとなる金属膜23Mを、図14Eに示すように前記シリコン酸化膜HM1上においてレジストパターンR1をも覆うように例えばスパッタ法あるいは電子ビーム蒸着法などにより堆積し、さらにステップ7において図14Fに示すように前記レジストパターンR1を、その上に堆積した金属膜23M共々リフトオフする。これにより、前記グラフェンシート23のソース領域23sに前記ソース電極パターン23Sが、またドレイン領域23dに前記ドレイン電極パターン23Dが、それぞれ形成される。前記金属膜23Mは、例えば厚さが5nmのTi密着膜(図示せず)と厚さが例えば30nmのAu膜(図示せず)とを順次積層した構造を有してもよい。

【0056】

次にステップ8において前記シリコン酸化膜HM1上にレジスト膜R2が形成され、前記レジスト膜R2中に図15のマスクパターンMを使って図14Gに示すようにレジスト開口部R2Aが、前記マスクパターンM中のマスク開口部23Mに対応して形成される。前記マスク開口部23Mは、前記グラフェンシート23中に形成される開口部列23Eに対応した形状を有しており、前記開口部23Eのジグザグ端23e1および23e2がそれぞれマスク開口部23Mのエッジ23m1および23m2に対応し、また開口部23Eのアームチェア端23e3〜23e8がそれぞれエッジ23m3〜23m8に対応している。

【0057】

ステップ8ではその際、前記マスク開口部23Mの向きが、前記グラフェンシート23中に形成したい開口部23Aの向きに一致するように、前記グラフェンシート23に対して方位を設定される。このようなマスク方位合わせの結果、前記エッジ23m1は前記チャネル方向から反時計回り方向に30°傾いており、一方前記エッジ23m2は、前記チャネル方向から時計回り方向に30°傾いている。

【0058】

前記ステップ8では、さらにこのようにして形成されたレジスト開口部R2Aにより前記シリコン酸化膜HM1が図14Hに示すようにパターニングされ、前記シリコン酸化膜HM1中には前記マスク開口部23Mに対応したマスク開口部HMAが形成される。

【0059】

次にステップ9の工程において前記グラフェンシート23に対し、図14Iに示すように前記シリコン酸化膜HM1をマスクに、例えば10mTorrの圧力下、90Wのプラズマパワーで25sccmの流量で酸素ガスを供給しながら反応性イオンエッチング(RIE)を行い、前記グラフェンシート23に、前記マスク開口部HMAに対応して開口部23Aを、前記グラフェンシート23の方位に対して所定の関係になるように、すなわち開口部23Aのジグザグ端23e1および23e2が、前記チャネル方向に対してそれぞれ反時計回り方向および時計回り方向に30°傾くように、形成する。前記マスクMにおいて前記マスク開口部23Mは図15に示すように開口部列方向に周期的に形成されており、これにより前記グラフェンシート23にはかかる開口部23Aにより開口部列23Nが、前記チャネル幅方向に形成される。

【0060】

さらにステップ10において図14Jに示すように前記シリコン酸化膜HM1を、HFを使ったウェットエッチングにより選択的に除去し、その後、水素雰囲気などの還元雰囲気中、例えば1000°の温度で熱処理することにより、前記開口部23Aの端部における炭素原子の配列を安定化させる。かかる安定化の結果、仮に図14Hの工程でマスクMの方位が僅かにずれていたとしても、前記開口部23Aの縁部において炭素原子は再配列し、前記チャネル方向に反時計回り方向あるいは時計回り方向に30°の角度のジグザグ端が安定に得られる。

【0061】

先の第1の実施形態の電子装置20においても上記の製造方法を適用することができる。

【0062】

なお本実施形態において、図9の開口部23Eの代わりに、図16に示すように、チャネル幅方向に互いに対向し、チャネル方向に対してそれぞれ反時計回り方向および時計回り方向に30°傾いたジグザグ端23f1および23f2と、チャネル幅方向に互いに対向し、チャネル方向に対してそれぞれ時計回り方向および反時計回り方向に30°傾いたジグザグ端23f3および23f4とを含む縁部で画成された開口部23Fを形成することも可能である。図16の構成では、チャネル方向に対して30°傾いたジグザグ端の数が増加するため、バンドギャップEgをさらに増大させることができる。

【0063】

図16の構成でも、開口部23Fはチャネル幅方向に繰り返し形成されている。

【0064】

[第3の実施形態]

図17は、第3の実施形態による電子装置60の構成を示す断面図である。図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0065】

図17を参照するに、電子装置60は6H−SiC基板61の(0001)面上に形成されており、前記(0001)面上に直接に形成され、前記図2あるいは図9、あるいは図16の平面図に示した開口部23A,23Eあるいは23Fにより開口部列23Nを形成されたグラフェンシート23と、前記グラフェンシート23上に、前記グラフェンシート23を構成する炭素原子の六角形格子のうち、平行に対向する二辺に対して直交する向きにおいて相互に対向するように形成されたソース電極23Sおよびドレイン電極23Dを含む。

【0066】

さらに前記グラフェンシート23は、前記開口部列23Nごと、たとえは厚さが10nmの酸化ハフニウム(HfO2)よりなるゲート絶縁膜62により覆われ、前記ゲート絶縁膜62上には、厚さが例えば5nmのチタン(Ti)膜と厚さが例えば30nmの金(Au)膜とを順次積層した構成のゲート電極63が形成されている。

【0067】

なお図示の構成ではソース電極23Sおよびドレイン電極23Dも前記酸化ハフニウム膜62により覆われており、前記酸化ハフニウム膜62には前記ソース電極23Sおよび23Dに対応して図示しないビアホールが形成される。

【0068】

かかる構成の電子装置でも、前記ソース電極23Sとドレイン電極23Dとが、前記ソース電極23Sとドレイン電極23Dとを結んだ直線が、前記グラフェンシート23Sを構成する炭素の六角形格子のうち相対向する二辺に対して直交するような向きに形成されているため、先の図2あるいは図9あるいは図16の実施形態と同様に、前記グラフェンシート23中には、前記チャネル方向に対して時計回り方向あるいは反時計回り方向に30°傾いたジグザグ端が形成されており、その結果、前記グラフェンシート23は、図4あるいは図10よりわかるように、1.6eV以上、あるいは2.8eV以上の大きなバンドギャップEgを示す。このため図17の電子装置17においても、前記ソース電極23Sからドレイン電極62Dへの電子の流れを、前記ゲート電極63に印加したゲート電圧により確実に制御することが可能となる。

【0069】

以下、図17の電子装置60の製造方法を、図18のフローチャートおよび図19A〜図19Kの工程断面図を参照しながら説明する。図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0070】

図18を参照するに、ステップ21において図19Aに示すように(0001)面を主面とする6H−SiC基板61を準備し、ステップ22において前記6H−SiC基板を真空中、あるいは1200°以上のアルゴン(Ar)など非酸化雰囲気中において熱処理し、前記基板21の主面を画成する(0001)面からSi元素を脱離させる。その結果、(0001)面よりなる前記6H−SiC基板21の主面には、図19Bに示すように六方晶系配列した炭素原子よりなる炭素原子層が残り、所望のグラフェンシート23がエピタキシャルに形成される。

【0071】

次に図18のステップ23において図19Cに示すようにシリコン酸化膜よりなるハードマスク膜HM1を、例えばスパッタ法やCVD法により形成し、ステップ24において前記ハードマスク膜HM1を、レジストパターンR1をマスクにパターニングして、図19Dに示すように前記グラフェンシート23のうち、ソース領域23sとドレイン領域23dとを露出する。

【0072】

さらに図18のステップ25において前記図19Dの構造上に、厚さが5nmのチタン膜と厚さが30nmの金膜とを、電子ビーム蒸着法あるいはスパッタ法により順次堆積して図19Eに示す金属膜23Mを形成し、さらに図18のステップ26において図19Fに示すように前記レジストパターンR1をその上の金属膜23M共々リフトオフし、前記グラフェンシート23のソース領域23sにソース電極23Sを、またドレイン領域23dにドレイン電極23Dを、それぞれ形成する。

【0073】

さらに図18のステップ27において前記ハードマスク膜HM1を、例えば図15で説明したマスクMを使ってパターニングして、図19Gに示すように前記グラフェンシート23を露出する開口部HMAを形成し、ステップ28において前記グラフェンシート23を、前記ハードマスク膜HM1をマスクにパターニングし、図19Hに示すように前記グラフェンシート23中に、例えば開口部23Aよりなる開口部列23Nを形成する。前記ステップ28において、前記開口部23Aの代わりに開口部23Eあるいは23Fを形成することも可能である。

【0074】

さらに図18のステップ29において、前記グラフェンシート23を水素雰囲気など還元雰囲気中、例えば1000°の温度で熱処理し、先に形成された開口部23Aなどの縁部における炭素原子の配列を安定化させる。さらにステップ30において図19Iに示すようにハードマスク膜HM1をたとえはHFによるウェット処理により除去し、さらにステップ31において図19Jに示すように、ゲート絶縁膜62を前記グラフェンシート23上に形成する。図示の例では、前記ゲート絶縁膜62として酸化ハフニウム(HfO2)膜を使っているが、酸化ジルコニウム(ZrO2)膜やハフニウムシリケート(HfSiO4)膜やハフニウムジルコネート(ZrSiO4)膜などを使うことも可能である。

【0075】

さらにステップ32において前記ゲート絶縁膜62上に前記ソース電極パターン23Sあるいはドレイン電極パターン23Dと同様な、Ti膜と金膜の積層構造のゲート電極63を形成することにより、図19Kに示すようにトップゲート構造の電子装置を得ることができる。

【0076】

以上、本発明を好ましい実施形態について説明したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

【符号の説明】

【0077】

1,23 グラフェンシート

1A アームチェア端

1B ジグザグ端

1a,1b,1c,1d,1e C−C結合

20,40,60 電子装置

21 シリコン基板

23A,23B,23C,23E,23F 開口部

23a1〜23a7,23b1〜23b6,23c1〜23c7,23e1〜23e8,23f1〜23f4 縁部

23N 開口部列

23M マスク開口部

23m1〜23m8 エッジ

23S ソース電極パターン

23D ドレイン電極パターン

61 SiC基板

62 ゲート絶縁膜

63 ゲート電極

【特許請求の範囲】

【請求項1】

基板と、

前記基板上にゲート絶縁膜を介して形成されたグラフェンシートと、

前記グラフェンシートの一端に形成されたソース電極と、

前記グラフェンシートの他端に形成されたドレイン電極と、

前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、

前記グラフェンシートに前記ソース電極とドレイン電極の間において、前記ソース電極とドレイン電極を結ぶ方向を横切って形成された、複数の開口部よりなる開口部列と、

を備え、

前記各々の開口部は少なくとも一つのジグザグ端により画成されており、前記少なくとも一つのジグザグ端は、前記ソース電極とドレイン電極を結んだ方向に対し、いずれも30°の角度をなすことを特徴とする電子装置。

【請求項2】

基板と、

前記基板上に形成されたグラフェンシートと、

前記グラフェンシートの一端に形成されたソース電極と、

前記グラフェンシートの他端に形成されたドレイン電極と、

前記グラフェンシートを前記ソース電極とドレイン電極の間において覆うゲート絶縁膜と、

前記ソース電極とドレイン電極の間において前記グラフェンシート上に、前記ゲート絶縁膜を介して形成され、前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、

前記ソース電極とドレイン電極の間において、前記グラフェンシートに前記ソース電極とドレイン電極を結ぶ方向を横切って形成された複数の開口部よりなる開口部列と、

を備え、

前記各々の開口部は少なくとも一つのジグザグ端により画成されており、前記少なくとも一つのジグザグ端は、前記ソース電極とドレイン電極を結んだ方向に対し、いずれも30°の角度をなすことを特徴とする電子装置。

【請求項3】

前記少なくとも一つのジグザグ端の一つは、前記グラフェンシートの面に対して垂直方向から見た場合に、前記ソース電極とドレイン電極を結んだ方向に対し、時計回りに30°の角度をなすことを特徴とする請求項1または2記載の電子装置。

【請求項4】

前記少なくとも一つのジグザグ端の一つは、前記グラフェンシートの面に対して垂直方向から見た場合に、前記ソース電極とドレイン電極を結んだ方向に対し、反時計回りに30°の角度をなすことを特徴とする請求項1または2記載の電子装置。

【請求項5】

前記少なくとも一つのジグザグ端は、前記ソース電極から前記ドレイン電極に向かって相互間隔を増大させる第1および第2のジグザグ端と、前記ソース電極から前記ドレイン電極に向かって相互間隔を減少させる第3および第4のジグザグ端と、を含み、前記第1および第3のジグザグ端は、前記ソース電極とドレイン電極を結んだ方向に対し、それぞれ反時計回りおよび時計回りに30°の角度をなし、前記第2および第4のジグザグ端は、前記ソース電極とドレイン電極を結んだ方向に対し、それぞれ時計回りおよび反時計回りに30°の角度をなすことを特徴とする請求項1または2記載の電子装置。

【請求項6】

前記ジグザグ形状の端部は、他の炭素原子に結合していない結合手を有する炭素原子を二個以上含む5個以上の炭素原子から構成されていることを特徴とする請求項1〜5のうち、いずれか一項記載の電子装置。

【請求項7】

前記開口部列は、前記ソース電極とドレイン電極の間で、前記キャリアの流れを横切って複数列にわたり形成されていることを特徴とする請求項1〜6のうち、いずれか一項記載の電子装置。

【請求項8】

基板上にグラフェンシートを形成する工程と、

前記グラフェンシート上に絶縁膜を形成する工程と、

前記絶縁膜中にマスク開口部を、形成する工程と、

前記グラフェンシートを、前記絶縁膜をマスクにパターニングし、前記グラフェンシート中に前記マスク開口部に対応した開口部を形成する工程と、

前記グラフェンシートを非酸化性雰囲気中で熱処理し、前記グラフェンシート中の開口部の形状を安定な形状に変化させる工程と、

前記グラフェンシート上に、前記開口部を挟んで一方の側にソース電極を、他方の側にドレイン電極を形成する工程と、

を含み、

前記マスク開口部を形成する工程は、前記マスク開口部が、前記ソース電極とドレイン電極を結ぶ直線に対し、いずれも時計回り方向あるいは反時計回り方向に30°の角度をなす一または複数の縁部により画成されるように形成されることを特徴とする電子装置の製造方法。

【請求項9】

前記ソース電極とドレイン電極とを形成する工程は、前記ソース電極とドレイン電極とを結んだ直線が、前記グラフェンシートを構成する炭素原子の六角形格子の相対向する2辺に平行あるいは直交するように、位置合わせする工程を含むことを特徴とする電子装置の製造方法。

【請求項1】

基板と、

前記基板上にゲート絶縁膜を介して形成されたグラフェンシートと、

前記グラフェンシートの一端に形成されたソース電極と、

前記グラフェンシートの他端に形成されたドレイン電極と、

前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、

前記グラフェンシートに前記ソース電極とドレイン電極の間において、前記ソース電極とドレイン電極を結ぶ方向を横切って形成された、複数の開口部よりなる開口部列と、

を備え、

前記各々の開口部は少なくとも一つのジグザグ端により画成されており、前記少なくとも一つのジグザグ端は、前記ソース電極とドレイン電極を結んだ方向に対し、いずれも30°の角度をなすことを特徴とする電子装置。

【請求項2】

基板と、

前記基板上に形成されたグラフェンシートと、

前記グラフェンシートの一端に形成されたソース電極と、

前記グラフェンシートの他端に形成されたドレイン電極と、

前記グラフェンシートを前記ソース電極とドレイン電極の間において覆うゲート絶縁膜と、

前記ソース電極とドレイン電極の間において前記グラフェンシート上に、前記ゲート絶縁膜を介して形成され、前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、

前記ソース電極とドレイン電極の間において、前記グラフェンシートに前記ソース電極とドレイン電極を結ぶ方向を横切って形成された複数の開口部よりなる開口部列と、

を備え、

前記各々の開口部は少なくとも一つのジグザグ端により画成されており、前記少なくとも一つのジグザグ端は、前記ソース電極とドレイン電極を結んだ方向に対し、いずれも30°の角度をなすことを特徴とする電子装置。

【請求項3】

前記少なくとも一つのジグザグ端の一つは、前記グラフェンシートの面に対して垂直方向から見た場合に、前記ソース電極とドレイン電極を結んだ方向に対し、時計回りに30°の角度をなすことを特徴とする請求項1または2記載の電子装置。

【請求項4】

前記少なくとも一つのジグザグ端の一つは、前記グラフェンシートの面に対して垂直方向から見た場合に、前記ソース電極とドレイン電極を結んだ方向に対し、反時計回りに30°の角度をなすことを特徴とする請求項1または2記載の電子装置。

【請求項5】

前記少なくとも一つのジグザグ端は、前記ソース電極から前記ドレイン電極に向かって相互間隔を増大させる第1および第2のジグザグ端と、前記ソース電極から前記ドレイン電極に向かって相互間隔を減少させる第3および第4のジグザグ端と、を含み、前記第1および第3のジグザグ端は、前記ソース電極とドレイン電極を結んだ方向に対し、それぞれ反時計回りおよび時計回りに30°の角度をなし、前記第2および第4のジグザグ端は、前記ソース電極とドレイン電極を結んだ方向に対し、それぞれ時計回りおよび反時計回りに30°の角度をなすことを特徴とする請求項1または2記載の電子装置。

【請求項6】

前記ジグザグ形状の端部は、他の炭素原子に結合していない結合手を有する炭素原子を二個以上含む5個以上の炭素原子から構成されていることを特徴とする請求項1〜5のうち、いずれか一項記載の電子装置。

【請求項7】

前記開口部列は、前記ソース電極とドレイン電極の間で、前記キャリアの流れを横切って複数列にわたり形成されていることを特徴とする請求項1〜6のうち、いずれか一項記載の電子装置。

【請求項8】

基板上にグラフェンシートを形成する工程と、

前記グラフェンシート上に絶縁膜を形成する工程と、

前記絶縁膜中にマスク開口部を、形成する工程と、

前記グラフェンシートを、前記絶縁膜をマスクにパターニングし、前記グラフェンシート中に前記マスク開口部に対応した開口部を形成する工程と、

前記グラフェンシートを非酸化性雰囲気中で熱処理し、前記グラフェンシート中の開口部の形状を安定な形状に変化させる工程と、

前記グラフェンシート上に、前記開口部を挟んで一方の側にソース電極を、他方の側にドレイン電極を形成する工程と、

を含み、

前記マスク開口部を形成する工程は、前記マスク開口部が、前記ソース電極とドレイン電極を結ぶ直線に対し、いずれも時計回り方向あるいは反時計回り方向に30°の角度をなす一または複数の縁部により画成されるように形成されることを特徴とする電子装置の製造方法。

【請求項9】

前記ソース電極とドレイン電極とを形成する工程は、前記ソース電極とドレイン電極とを結んだ直線が、前記グラフェンシートを構成する炭素原子の六角形格子の相対向する2辺に平行あるいは直交するように、位置合わせする工程を含むことを特徴とする電子装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14A】

【図14B】

【図14C】

【図14D】

【図14E】

【図14F】

【図14G】

【図14H】

【図14I】

【図14J】

【図16】

【図17】

【図18】

【図19A】

【図19B】

【図19C】

【図19D】

【図19E】

【図19F】

【図19G】

【図19H】

【図19I】

【図19J】

【図19K】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14A】

【図14B】

【図14C】

【図14D】

【図14E】

【図14F】

【図14G】

【図14H】

【図14I】

【図14J】

【図16】

【図17】

【図18】

【図19A】

【図19B】

【図19C】

【図19D】

【図19E】

【図19F】

【図19G】

【図19H】

【図19I】

【図19J】

【図19K】

【図15】

【公開番号】特開2013−16641(P2013−16641A)

【公開日】平成25年1月24日(2013.1.24)

【国際特許分類】

【出願番号】特願2011−148434(P2011−148434)

【出願日】平成23年7月4日(2011.7.4)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成25年1月24日(2013.1.24)

【国際特許分類】

【出願日】平成23年7月4日(2011.7.4)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]