電子装置及びその電子装置の製造方法

【課題】高密度に集積化して高機能な電子装置を製造するにあたり、ICチップやパッケージ設計上の制約が少なく生産性を向上し、汎用化が容易な電子装置の製造方法を提供する。

【解決手段】金属バンプ電極すなわちAuスタッドバンプ1を有する第1の電子装置すなわち親チップ2に搭載されると共に親チップ2のAuスタッドバンプ1に接続される電極を備える第2の電子装置すなわち子チップ3の前記電極形成面のほぼ全面を被覆する様に子チップ3に接着材層5を形成する工程と、親チップ2に子チップ3を搭載する工程とより成り、親チップ2に子チップ3を搭載する工程で親チップ2のAuスタッドバンプ1が接着材層5を貫通して子チップ3上の電極と電気的に接続すると共に親チップ2と子チップ3間が接着材層5により封止される。

【解決手段】金属バンプ電極すなわちAuスタッドバンプ1を有する第1の電子装置すなわち親チップ2に搭載されると共に親チップ2のAuスタッドバンプ1に接続される電極を備える第2の電子装置すなわち子チップ3の前記電極形成面のほぼ全面を被覆する様に子チップ3に接着材層5を形成する工程と、親チップ2に子チップ3を搭載する工程とより成り、親チップ2に子チップ3を搭載する工程で親チップ2のAuスタッドバンプ1が接着材層5を貫通して子チップ3上の電極と電気的に接続すると共に親チップ2と子チップ3間が接着材層5により封止される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、チップ・オン・チップ構造の電子装置の製造方法及びその電子装置並びに半導体装置の製造方法に関するものである。

【背景技術】

【0002】

ICチップ間をバンプ電極等により直接接続するチップ・オン・チップ型半導体装置は、高い実装密度とチップ間の高速なデータ転送を実現することができる。しかしながら、このチップ・オン・チップ型半導体装置の製造方法では、設計上の制約が大きく、生産性が低いといった問題があった。

ここで、チップ・オン・チップ構造とは、親チップと呼ばれるICチップ上にこれより小さい子チップと呼ばれるICチップをバンプと呼ばれる金属突起電極を介して接続したものである。親チップは一般的にワイヤボンディングやTAB技術、あるいはフリップチップ接続技術等を用いて配線基板に電気的に接続され、チップ全体やワイヤボンディング接続部が樹脂により封止されることにより半導体パッケージが構成される。チップ・オン・チップの接続部はチップ間が電気信号伝達のために金属バンプにより接続されていると同時に、バンプ接続部分を除くチップ間が絶縁樹脂等により保護されることが信頼性上必要である。

【0003】

このチップ・オン・チップ構造の半導体パッケージの製造方法について例を用いて説明する。まず、配線基板やリードフレームといったパッケージ基板上に、Agペーストやフィルム状の接着剤などにより親チップを接着する。親チップ上には子チップと接続するためにアルミパッドあるいはAuバンプ等の電極が形成されている。また、子チップ側にも親チップと接続される電極としてAuバンプやアルミパッドが形成されている。これらの接続電極の構造はその電極の密度や配置に応じて様々なものが考えられ、上記の他にはんだバンプを用いたものも用いられる。チップ・オン・チップ接合プロセスに関しては、チップ間への絶縁樹脂の充填方法によって2つの方法に分けられる。第1の方法は、子チップと親チップをバンプにより接続した後に、毛細管現象を利用して液状の熱硬化樹脂をチップ間に注入、加熱して硬化させる方法である。子チップと親チップの電極間の接合工法としては、双方の電極がAuである場合は熱圧着工法あるいは超音波接合法、それぞれAuとAlである場合は超音波接合法などの金属間の固層拡散を用いた接合法、はんだ電極である場合は接合部をはんだの融点以上の温度に加熱、液相拡散により金属接合を得る方法が用いられる。第2の方法は液状またはフィルム状の樹脂をあらかじめ親チップ上の、子チップが接続される領域に供給しておき、この上に子チップを搭載、バンプ接続と樹脂封止を同時に行う方法である。この方法ではバンプの狭ピッチ化によりチップ間の間隙が縮小しても樹脂を充填しやすいという特徴がある。

【0004】

このようにして親チップ、子チップ間のバンプ接合と樹脂封止を行った後、ワイヤボンディング法により親チップ上に形成された電極とパッケージ基板の配線を接続する。この時、当然ながら、親チップ上のパッケージ基板に接続される電極は、子チップが搭載されていない領域に形成されていなければならない。最後にチップやワイヤボンディング部をトランスファーモールド法などにより樹脂封止することにより、チップ・オン・チップ構造を含む半導体パッケージが形成される。

【0005】

図5は、以上に説明したチップ・オン・チップの接合プロセスの一例を示す。親チップ20上の子チップ30が接続される領域に液状の接着樹脂40をポッティング法などにより供給する。この後、Auスタッドバンプ電極10を形成した子チップ30を、親チップ20の対応する電極に位置合わせして接合することにより、電極同士の接合と樹脂封止が行われる。しかしながらこの方法では樹脂40の量のコントロールを正確に行うことが困難であるため、子チップ接合領域からはみ出した樹脂40が親チップ20上の配線基板とワイヤボンディング等を用いて接続するための電極を汚染したり、子チップ30を搭載するためのボンディングツールを汚染するという問題が発生していた。

【0006】

ここで、特許文献1には例えばポッティング法によって熱可塑性樹脂を基板のはんだボールを設けた側に設け、半導体素子の電極以外の部分に接着剤が形成された構造を採用して、ボード実装時に熱可塑性樹脂の溶融により実装強度を向上させるという半導体装置の製造方法が開示されている。

【0007】

また特許文献2にはウェハのチップ領域のパッド上に金線を用いて突起付電極を形成し、突起付電極を完全に覆うように樹脂層を形成し、樹脂層を研磨して金バンプ露出面を有する金バンプと樹脂層とを形成し、ウェハを分割して半導体チップを完成させるプロセスが開示された。

【0008】

【特許文献1】特開平11−297750

【特許文献2】特開平11−274241

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかし、前記のチップ・オン・チップ接合プロセスでは、特に樹脂の充填プロセスにおける問題により設計上の制約が大きかった。

すなわち前述の第1の方法では、チップ間に液状の熱硬化性樹脂を注入する際に、親チップ上に樹脂を供給するスペースを設ける必要があり、また、液状樹脂が親チップ上のパッケージ基板に接続される電極を汚染するという問題があるため、親チップのサイズが子チップのサイズに比較して十分大きくなくてはならないという設計上の制約があった。また、樹脂の供給はチップ単位で行わなければならないため、生産性が低いという問題があった。

また第2の方法では、液状樹脂を用いた場合は樹脂の供給量、接着剤フィルムの場合はフィルムの貼付位置精度により第1の方法と同様の親チップ、子チップのサイズに関する制約が発生し、さらに、子チップを親チップ上にフリップチップボンダにて搭載する際に、子チップを吸着保持するツールを汚染することを防ぐために、子チップの厚さが十分厚くなければならないという理由からパッケージの薄型化が困難であった。

【0010】

また特許文献1に記載された技術では、半導体素子の電極を露出させたまま、電極以外の部分に選択的に接着層を形成することは、特殊なプロセスが必要になり、製造コストが上昇する。具体的には、特許文献1に示されるように、柔軟性のあるシートで電極上を覆い、金型内に保持し、シートと半導体ウェハの間に樹脂を注入するプロセスが必要となり、特殊な製造プロセス、製造設備を必要とする。

【0011】

さらに、特許文献2に記載された技術では突起電極を完全に覆うように樹脂で埋め込んだ後、樹脂を研削することにより電極を露出させるという固有のプロセスが存在し特殊な製造プロセス、製造設備を必要とする。

【0012】

本発明は、以上の問題に鑑みてなされたものであり、複数のICチップを、安価な方法で相互に接続し、高密度に集積化して高機能な電子装置を製造するにあたり、ICチップやパッケージ設計上の制約が少なく生産性を向上し、汎用化が容易な電子装置の製造方法及びその電子装置並びに半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明者は、親チップ上に搭載される子チップの電極形成面全面に、ウェハ状態にて樹脂フィルムをラミネートしてダイシングすることにより接着剤層を形成し、汎用ワイヤボンダによりAuスタッドバンプを形成した親チップ上に超音波フリップチップ工法を用いて搭載することにより、接着剤層を貫通したAuスタッドバンプと子チップ電極の接合とチップ間の樹脂封止を同時に行うことができるという着想に基づき本発明に想到した。

【0014】

すなわち本発明の電子装置の製造方法は、金属バンプ電極を有する第1の電子装置に搭載されると共に第1の電子装置の前記金属バンプに接続される電極を備える第2の電子装置の前記電極形成面のほぼ全面を被覆する様に第2の電子装置に接着剤層を形成する工程と、第1の電子装置に第2の電子装置を搭載する工程とより成り、第1の電子装置に第2の電子装置を搭載する工程で前記第1の電子装置上のバンプ電極が前記接着剤層を貫通して第2の電子装置上の電極と電気的に接続すると共に第1の電子装置と第2の電子装置間が前記接着剤層により封止されることを特徴とする。

【0015】

また本発明の電子装置は金属バンプ電極を有する第1の電子装置に第2の電子装置を搭載して成り、前記第1の電子装置上のバンプ電極が接着剤層を貫通して第2の電子装置上の電極と電気的に接続されると共に第1の電子装置と第2の電子装置間が前記接着剤層により封止され、前記接着剤層構成成分を第1の電子装置のバンプ電極と第2の電子装置の電極間に含んでなることを特徴とする。

【0016】

金属バンプ電極を有する第1の電子装置に搭載されると共に第1の電子装置の前記金属バンプに接続される電極を備える第2の電子装置の前記電極形成面のほぼ全面を被覆する様に第2の電子装置に接着剤層を形成する工程と、第1の電子装置に第2の電子装置を搭載する工程とより成り、第1の電子装置に第2の電子装置を搭載する工程で前記第1の電子装置上のバンプ電極が前記接着剤層を貫通して第2の電子装置上の電極と電気的に接続すると共に第1の電子装置と第2の電子装置間が前記接着剤層により封止され、接着剤層構成成分を第1の電子装置のバンプ電極と第2の電子装置の電極間に含んでなることを特徴とする。

【0017】

さらに本発明の半導体装置の製造方法は、ICが複数形成されたウェハの電極面と相対する面を支持体上に貼り付ける工程と、前記ウェハの電極形成面に接着剤フィルムを貼り付ける工程と、前記接着剤フィルムの貼り付けられたウェハを支持体上で複数のICチップに切断分離する工程とを含み、ICチップの電極形成面上に接着剤層を形成することを特徴とする。

【0018】

さらに本発明の半導体装置の製造方法は、ICが複数形成されたウェハの電極面と相対する面を支持体上に貼り付ける工程と、前記ウェハの電極形成面にスピンコート法により接着剤層をコーティングする工程と、前記接着材層の形成されたウェハを支持体上で複数のICチップに切断分離する工程を含み、ICチップの電極形成面上に接着剤層を形成することを特徴とする。

【0019】

さらに本発明の半導体装置の製造方法は、支持体上に形成された接着剤層上に前記ICが複数形成されたウェハの電極形成面を貼り付け、前記ウェハと接着剤層を支持体上で切断分離する工程を含み、ICチップの電極形成面上に接着剤層を形成することを特徴とする。

本発明の半導体装置は、半導体基板と、前記半導体基板の上面に形成された複数の電極と、前記複数の電極を完全に覆う封止樹脂層とから成ることを特徴とする。

また、本発明の半導体装置の製造方法は、半導体ウェハの上面に複数の電極を形成する工程と、前記複数の電極を完全に覆う封止樹脂層を形成する工程と、前記複数の電極が形成され且つ前記複数の電極を完全に覆う封止樹脂層が形成された半導体ウェハを複数の半導体装置に切り分ける工程とから成ることを特徴とする。

さらに、本発明の半導体装置の製造方法は、複数のバンプ電極を有する第一の半導体装置を準備する工程と、複数の電極と当該複数の電極を完全に覆う封止樹脂層とを有する第二の半導体装置を準備する工程と、前記第二の半導体装置を前記第一の半導体装置にマウントして前記バンプ電極が前記封止樹脂層を貫通するようにし前記バンプ電極と前記第二の半導体装置の電極とを接合する工程とから成ることを特徴とする。

【0020】

本発明の電子装置の製造方法によれば、子チップのウェハに対し、ダイシングシート上にマウントされた状態で接着剤フィルムを貼付して、ダイシングすることにより、樹脂量の最適化が可能になる。一般に子チップを親チップ上に搭載し接合したときの親チップ上での封止樹脂のはみ出しは、チップ間の間隙を埋める体積以上の樹脂が供給された場合や、供給位置が的確でない場合に発生する。例えば、接合プロセス直前に液状樹脂を親チップ上に供給するポッティング法では、正確に樹脂の量をチップ間の間隙を埋める体積とするのは困難である。また、接着剤フィルムを親チップ上に貼り付ける方法でも、子チップの搭載位置に正確に貼り付けるのは困難で、現実的には500ミクロン程度の貼付位置誤差が出る。これに対し、本発明の電子装置の製造方法によれば、子チップの面積と供給する樹脂フィルムの厚さにより樹脂量は決まり、また子チップのウェハに対し、ダイシングシート上にマウントされた状態で接着剤フィルムを貼付るので樹脂の供給位置も正確に子チップ直下となる。このことにより樹脂はみだしは極めて少なくなり、また樹脂の子チップ上への這い上がりの危険も少ないことから子チップの厚さも極めて薄くすることができる。

【発明の効果】

【0021】

本発明の効果として、本発明の電子装置の製造方法によれば、薄く研削された子チップのウェハに対し、ダイシングシート上にマウントされた状態で接着剤フィルムを貼付、ダイシングすることにより、樹脂量の最適化と子チップの薄チップ化が可能になり、親チップ、子チップのサイズ、厚さに関する制約が大幅に緩和され生産性が大幅に向上する。そのため設計自由度、生産性の高いチップ・オン・チップ型電子装置が得られる。

また本発明の電子装置によれば、接着剤層構成成分を第1の電子装置のバンプ電極と第2の電子装置の電極間に含んでなることにより接合圧力が局所的に集中し、例えばはんだ表面の自然酸化膜がやぶれることにより接合プロセスが安定する。この場合に第1の電子装置のバンプ電極と第2の電子装置の電極間はんだ界面に残留する接着剤層構成成分それ自体は直接的には接合には寄与することなく、接合圧力を局所的に集中させて接合プロセスを安定させるという間接的機能が認められる。

【発明を実施するための最良の形態】

【0022】

図1に示すように金属バンプ電極すなわちAuスタッドバンプ1を有する第1の電子装置すなわち親チップ2に搭載されると共に親チップ2のAuスタッドバンプ1に接続される電極を備える第2の電子装置すなわち子チップ3の子チップウェハ4の電極形成面のほぼ全面を被覆する様に子チップ3に接着剤層5を形成する工程と、親チップ2に子チップ3を搭載する工程とより成り、親チップ2に子チップ3を搭載する工程で親チップ2のAuスタッドバンプ1が接着剤層5を貫通して子チップ3上の電極と電気的に接続すると共に親チップ2と子チップ3間が接着剤層5により封止される。

以上のチップ・オン・チップ接合プロセスにおいて子チップ3と親チップ2とは表面に電子回路の形成された平板形状にされ、かつ、親チップ2は子チップ3より大きな回路面積を有する。また親チップ2は子チップ3と接続されない電極を有し、その電極が親チップ2に子チップ3を搭載した後に子チップ3との接続領域外の表面に露出している。これによって、親チップ2は他のICチップ若しくは配線基板との接続が可能となる。また親チップ2または子チップ3は少なくとも一方がICチップとされる。また親チップ2または子チップ3は少なくとも一方が配線基板であってもよい。

(実施例1)

【0023】

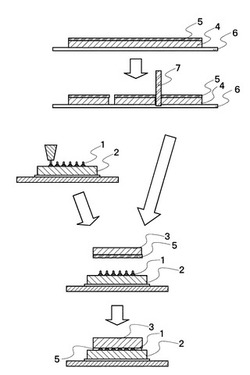

図1に本発明の電子装置の製造方法におけるチップ・オン・チップ接合プロセスの実施例1を示す。図1に示されるように、この実施例では、まず裏面研削により薄型化したダイシング前の子チップウェハ4をダイシングシート6上にマウントし、この状態で接着剤フィルムのウェハ4に対する貼り付けを行う。さらにそのように接着剤フィルムを貼り付け接着剤層5を形成した状態でダイシングブレード7によって子チップウェハ4のダイシングを行うことにより子チップ3の個片化を行う。この方法により、電極を含む素子形成面の全面に接着剤層5が形成された非常に薄い子チップ3が得られる。

【0024】

なお、ウェハ4上への接着剤層5の形成方法としては、液状樹脂をスピンコート法により塗布する方法を用いても良い。また、減圧雰囲気中でこれを行うことにより、気泡等を巻き込む事無く貼り付けることが可能となる。子チップ3の電極としてはAlやAuなどが望ましく、形状としては平面状のパッドであっても、メッキ法などで形成されたバンプ形状であっても良い。また子チップ3上のほぼ全面に形成され、Alパッド電極部分に開口部を有する保護膜表面すなわちポリイミドカバー膜表面から窪んだ位置に形成されたAlパッドとすることもできる。なお、保護膜材質としてはポリイミドなどの有機膜の他に、SiNなどの無機膜だけにすることもできる。

【0025】

一方、配線基板上に接着剤やAgペースト等を用いて搭載された親チップ2のAlパッド電極上にワイヤボンダを用いてAuスタッドバンプ1の形成を行う。

次に、チップ・オン・チップの接合プロセスでは、周知の超音波フリップチップボンダにより親チップ2上に子チップ3を搭載し、親チップ2上に形成されたバンプ電極が子チップ3の電極上の樹脂を貫通し、子チップ3の電極と接続し、同時に子チップ3上に形成された接着剤層5により、子チップ3及び親チップ2間が樹脂封止された状態が形成できる。この工法を用いることにより、チップ間を封止する樹脂の量はウェハ状態で貼り付ける樹脂フィルムの厚さとチップサイズによりほぼ正確に決定され、子チップ3の搭載される部分に正確に樹脂が供給されることになる。このことは、子チップ3の搭載領域から樹脂が大きくはみだすことで親チップ2上に形成されたパッケージ基板に接続するための電極を汚染することや、樹脂が子チップ3上に乗り上げることを防止することが可能となり、結果として子チップ3と親チップ2のチップサイズに関する制限が小さくなり、さらに、子チップ3を薄型化できるということを意味する。

【0026】

上記のプロセスにおいては、子チップ3上の樹脂層は、親チップ2への接合時にチップ間に樹脂が十分に充填されるために電極表面を完全に被覆していることが必要であり、また、フリップチップボンダにより搭載する際にカメラによる子チップ3表面のパターン認識が可能であることを考慮し、35ミクロン程度以下であることが望ましい。またフィルム樹脂の特性としては、ダイシングシート6上のウェハに貼り付けることを考慮し、100℃以下の低温で接着可能な樹脂であることが望ましい。また上記プロセスでは、親チップ2のバンプ電極が樹脂を貫通、子チップ3の電極に押圧する過程において、子チップ3に対して超音波振動を印加することにより、両電極間に存在する殆どの樹脂が排除され、電極間に金属的、電気的接続を得ることが可能である。この場合フィルム樹脂の構成成分が両電極間に残存する場合もある。この際、超音波の振動エネルギーが電極間に効率的に供給されて良好な電極間の接合を得るために、接合温度において樹脂の粘度が約1000Pa・s以下に下がるような樹脂を選択することが望ましい。このような適切な樹脂や接合プロセス条件を選定することにより、電極間の接合部に含まれる接着剤層5構成成分は微量となり、或いは無くなり、高い信頼性の確保が可能となる。

【0027】

以上のプロセスによりチップ・オン・チップ構造を形成した後は、一般の製造方法と同様に、ワイヤボンディングを用いて親チップ2上の電極と配線基板を接続、最後にチップやワイヤボンディング部をトランスファーモールド法などにより樹脂封止することにより、チップ・オン・チップ構造を含む半導体パッケージを形成する。

(実施例2)

【0028】

図2に本発明の実施例2を示す。実施例1では、親チップ2が配線基板上に搭載された状態で実施されているが、これに限らず、親チップ2をダイシングにより個片化する前の親チップウェハ8状態で子チップ3を接合しても構わない。このようにウェハ8状態で接合することにより、親チップ2、子チップ3間の高い平行度が得られ、狭ピッチの接続にも対応可能である。また、図では親チップ2上のバンプ電極として、メッキ法を用いて形成されたAuメッキバンプ1aを用いた場合を示している。親チップ2のバンプ電極としては、この他にもはんだバンプ電極を始め、各種の材料により構成されたバンプを用いることが可能である。さらに、親チップ2、子チップ3、いずれかの電極をはんだ材料により構成することで、はんだ溶融による液層拡散を用いた接合プロセスを用いることもできる。

【0029】

この実施例ではバンプ電極が狭ピッチ化することによりチップ間の間隙が小さくなった場合でも、親チップ2が厚さの均一性に優れたウェハ状態でチップ・オン・チップ接合プロセスを行うことにより、親チップ2と子チップ3の平行度を保つことが容易になる。またメッキ法により狭ピッチのバンプを形成できる。さらに、はんだを用いた溶融接合法を用いることにより接合部の下部に形成された配線や素子にダメージを与える危険の小さな接合プロセスが実現できる。

(実施例3)

【0030】

図3に子チップ3表面への接着剤層5の形成プロセスに関する前記各実施例とは異なる実施例を示す。この実施例ではダイシングを行う際の支持体であるダイシングシート6上にはあらかじめ接着剤フィルムを貼り付けて接着剤層5が形成されており、子チップ3ウェハ4の電極形成面をこの接着材層5に貼り付けた状態でダイシングブレード7により子チップ3と接着剤層5とを共に切断することにより表面に接着剤層5の形成された子チップ3を得ることが可能である。

(実施例4)

【0031】

図4に本発明の実施例4を示す。実施例4では親チップ2上のバンプ電極として、メッキ法を用いて形成されたAuメッキバンプ1aを用い、子チップ3の電極部9表面に低融点材料であるはんだ12を設けた。また接着剤層5は導電性フィラー11を分散して含有する。その結果、図4(b)に示されるように、親チップ2上のAuメッキバンプ1aと子チップ3のはんだ12が接合された状態では、接合部分に導電性フィラー11が介在する。その結果、導電性フィラー11が備える性能により、接合プロセスの安定化と、接合部分の特性改善が可能となる。具体的には、導電性フィラー11が介在することにより接合圧力が局所的に集中し、はんだ表面の自然酸化膜がやぶれることにより接合プロセスが安定する。また係る介在物は導電性フィラー11に限られず、例えば絶縁性介在物を介在させることによってAuメッキバンプ1aと子チップ3のはんだ12の接合強度を向上する等、目的に応じて介在物を選択し、Auメッキバンプ1aと子チップ3のはんだ12の接合部に所要の特性を付与することが可能となる。

なお、導電性フィラー11としては、図4(b)示される導体球の他に、樹脂コアを持つものなども用いることができる。

【0032】

なお以上の本発明の電子装置の製造方法の実施に際し、親チップ2上に子チップ3を搭載するに当たり、子チップ3を温度管理する機構を備える電子装置製造装置を用いて子チップ3を所定に温度管理して親チップ2上に子チップ3を搭載する製造工程を実施することによって、円滑に電子装置の製造工程を進めることができる。

【0033】

以上、本発明の好適な実施例について種々述べてきたが、本発明は前記実施例に限定されるものでなく、発明の精神を逸脱しない範囲でさらに多くの改変を施しえるのはもちろんのことである。

【0034】

例えば、ダイシングシート6はシート状のものに限定するものでなく、ウェハをダイシングする際にウェハを支持するもの(ここでは支持体と呼ぶ)であれば良い。また、ダイシングシート6上にあらかじめ接着剤層5を形成しておき、半導体ウェハの回路形成面を接着材層5に接着、ダイシングを行うという方法を用いても良い。また、子チップ3ウェハ4上への樹脂の供給方法としては、ダイシングシート6上でのフィルム樹脂の貼付によるものだけでなく、液状樹脂をスピンコート法によりウェハ上に供給する方法を用いても良い。いずれにしても、ダイシングを行う際のウェハを支持する構造体(支持体)の上でウェハに接着剤層5が形成され、この状態でダイシングを行うことにより、薄いチップに対して接着剤層を形成することが可能になる。

【0035】

バンプ接続工法に関しても、超音波併用熱圧着工法、熱圧着工法、はんだによる溶融接合法など電極構成素材に応じて最適なものを選ぶことができる。

また、ここまでは2つのICチップをチップ・オン・チップ接合する構成に関して述べてきたが、親チップ2すなわち第1の電子装置及び子チップ3すなわち第2の電子装置はそれぞれICに限定されず、いずれかが配線基板等の電子回路の形成された平板状の電子装置であっても良い。

【図面の簡単な説明】

【0036】

【図1】本発明に係る電子装置の接続方法の一実施例を示す図である。

【図2】本発明に係る電子装置の接続方法の他の一実施例を示す図である。

【図3】本発明に係る電子装置の接続方法の別の実施例を示す図である。

【図4】本発明に係る電子装置の接続方法のさらに他の実施例を示す図である。

【図5】従来における電子装置の接続方法を示す図である。

【符号の説明】

【0037】

1 Auスタッドバンプ

1a Auメッキバンプ

2 親チップ

3 子チップ

4 子チップウェハ

5 接着剤層

6 ダイシングシート

7 ダイシングブレード

8 親チップウェハ

10 Auスタッドバンプ電極

11 導電性フィラー

12 はんだ

20 親チップ

30 子チップ

40 接着樹脂

【技術分野】

【0001】

本発明は、チップ・オン・チップ構造の電子装置の製造方法及びその電子装置並びに半導体装置の製造方法に関するものである。

【背景技術】

【0002】

ICチップ間をバンプ電極等により直接接続するチップ・オン・チップ型半導体装置は、高い実装密度とチップ間の高速なデータ転送を実現することができる。しかしながら、このチップ・オン・チップ型半導体装置の製造方法では、設計上の制約が大きく、生産性が低いといった問題があった。

ここで、チップ・オン・チップ構造とは、親チップと呼ばれるICチップ上にこれより小さい子チップと呼ばれるICチップをバンプと呼ばれる金属突起電極を介して接続したものである。親チップは一般的にワイヤボンディングやTAB技術、あるいはフリップチップ接続技術等を用いて配線基板に電気的に接続され、チップ全体やワイヤボンディング接続部が樹脂により封止されることにより半導体パッケージが構成される。チップ・オン・チップの接続部はチップ間が電気信号伝達のために金属バンプにより接続されていると同時に、バンプ接続部分を除くチップ間が絶縁樹脂等により保護されることが信頼性上必要である。

【0003】

このチップ・オン・チップ構造の半導体パッケージの製造方法について例を用いて説明する。まず、配線基板やリードフレームといったパッケージ基板上に、Agペーストやフィルム状の接着剤などにより親チップを接着する。親チップ上には子チップと接続するためにアルミパッドあるいはAuバンプ等の電極が形成されている。また、子チップ側にも親チップと接続される電極としてAuバンプやアルミパッドが形成されている。これらの接続電極の構造はその電極の密度や配置に応じて様々なものが考えられ、上記の他にはんだバンプを用いたものも用いられる。チップ・オン・チップ接合プロセスに関しては、チップ間への絶縁樹脂の充填方法によって2つの方法に分けられる。第1の方法は、子チップと親チップをバンプにより接続した後に、毛細管現象を利用して液状の熱硬化樹脂をチップ間に注入、加熱して硬化させる方法である。子チップと親チップの電極間の接合工法としては、双方の電極がAuである場合は熱圧着工法あるいは超音波接合法、それぞれAuとAlである場合は超音波接合法などの金属間の固層拡散を用いた接合法、はんだ電極である場合は接合部をはんだの融点以上の温度に加熱、液相拡散により金属接合を得る方法が用いられる。第2の方法は液状またはフィルム状の樹脂をあらかじめ親チップ上の、子チップが接続される領域に供給しておき、この上に子チップを搭載、バンプ接続と樹脂封止を同時に行う方法である。この方法ではバンプの狭ピッチ化によりチップ間の間隙が縮小しても樹脂を充填しやすいという特徴がある。

【0004】

このようにして親チップ、子チップ間のバンプ接合と樹脂封止を行った後、ワイヤボンディング法により親チップ上に形成された電極とパッケージ基板の配線を接続する。この時、当然ながら、親チップ上のパッケージ基板に接続される電極は、子チップが搭載されていない領域に形成されていなければならない。最後にチップやワイヤボンディング部をトランスファーモールド法などにより樹脂封止することにより、チップ・オン・チップ構造を含む半導体パッケージが形成される。

【0005】

図5は、以上に説明したチップ・オン・チップの接合プロセスの一例を示す。親チップ20上の子チップ30が接続される領域に液状の接着樹脂40をポッティング法などにより供給する。この後、Auスタッドバンプ電極10を形成した子チップ30を、親チップ20の対応する電極に位置合わせして接合することにより、電極同士の接合と樹脂封止が行われる。しかしながらこの方法では樹脂40の量のコントロールを正確に行うことが困難であるため、子チップ接合領域からはみ出した樹脂40が親チップ20上の配線基板とワイヤボンディング等を用いて接続するための電極を汚染したり、子チップ30を搭載するためのボンディングツールを汚染するという問題が発生していた。

【0006】

ここで、特許文献1には例えばポッティング法によって熱可塑性樹脂を基板のはんだボールを設けた側に設け、半導体素子の電極以外の部分に接着剤が形成された構造を採用して、ボード実装時に熱可塑性樹脂の溶融により実装強度を向上させるという半導体装置の製造方法が開示されている。

【0007】

また特許文献2にはウェハのチップ領域のパッド上に金線を用いて突起付電極を形成し、突起付電極を完全に覆うように樹脂層を形成し、樹脂層を研磨して金バンプ露出面を有する金バンプと樹脂層とを形成し、ウェハを分割して半導体チップを完成させるプロセスが開示された。

【0008】

【特許文献1】特開平11−297750

【特許文献2】特開平11−274241

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかし、前記のチップ・オン・チップ接合プロセスでは、特に樹脂の充填プロセスにおける問題により設計上の制約が大きかった。

すなわち前述の第1の方法では、チップ間に液状の熱硬化性樹脂を注入する際に、親チップ上に樹脂を供給するスペースを設ける必要があり、また、液状樹脂が親チップ上のパッケージ基板に接続される電極を汚染するという問題があるため、親チップのサイズが子チップのサイズに比較して十分大きくなくてはならないという設計上の制約があった。また、樹脂の供給はチップ単位で行わなければならないため、生産性が低いという問題があった。

また第2の方法では、液状樹脂を用いた場合は樹脂の供給量、接着剤フィルムの場合はフィルムの貼付位置精度により第1の方法と同様の親チップ、子チップのサイズに関する制約が発生し、さらに、子チップを親チップ上にフリップチップボンダにて搭載する際に、子チップを吸着保持するツールを汚染することを防ぐために、子チップの厚さが十分厚くなければならないという理由からパッケージの薄型化が困難であった。

【0010】

また特許文献1に記載された技術では、半導体素子の電極を露出させたまま、電極以外の部分に選択的に接着層を形成することは、特殊なプロセスが必要になり、製造コストが上昇する。具体的には、特許文献1に示されるように、柔軟性のあるシートで電極上を覆い、金型内に保持し、シートと半導体ウェハの間に樹脂を注入するプロセスが必要となり、特殊な製造プロセス、製造設備を必要とする。

【0011】

さらに、特許文献2に記載された技術では突起電極を完全に覆うように樹脂で埋め込んだ後、樹脂を研削することにより電極を露出させるという固有のプロセスが存在し特殊な製造プロセス、製造設備を必要とする。

【0012】

本発明は、以上の問題に鑑みてなされたものであり、複数のICチップを、安価な方法で相互に接続し、高密度に集積化して高機能な電子装置を製造するにあたり、ICチップやパッケージ設計上の制約が少なく生産性を向上し、汎用化が容易な電子装置の製造方法及びその電子装置並びに半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明者は、親チップ上に搭載される子チップの電極形成面全面に、ウェハ状態にて樹脂フィルムをラミネートしてダイシングすることにより接着剤層を形成し、汎用ワイヤボンダによりAuスタッドバンプを形成した親チップ上に超音波フリップチップ工法を用いて搭載することにより、接着剤層を貫通したAuスタッドバンプと子チップ電極の接合とチップ間の樹脂封止を同時に行うことができるという着想に基づき本発明に想到した。

【0014】

すなわち本発明の電子装置の製造方法は、金属バンプ電極を有する第1の電子装置に搭載されると共に第1の電子装置の前記金属バンプに接続される電極を備える第2の電子装置の前記電極形成面のほぼ全面を被覆する様に第2の電子装置に接着剤層を形成する工程と、第1の電子装置に第2の電子装置を搭載する工程とより成り、第1の電子装置に第2の電子装置を搭載する工程で前記第1の電子装置上のバンプ電極が前記接着剤層を貫通して第2の電子装置上の電極と電気的に接続すると共に第1の電子装置と第2の電子装置間が前記接着剤層により封止されることを特徴とする。

【0015】

また本発明の電子装置は金属バンプ電極を有する第1の電子装置に第2の電子装置を搭載して成り、前記第1の電子装置上のバンプ電極が接着剤層を貫通して第2の電子装置上の電極と電気的に接続されると共に第1の電子装置と第2の電子装置間が前記接着剤層により封止され、前記接着剤層構成成分を第1の電子装置のバンプ電極と第2の電子装置の電極間に含んでなることを特徴とする。

【0016】

金属バンプ電極を有する第1の電子装置に搭載されると共に第1の電子装置の前記金属バンプに接続される電極を備える第2の電子装置の前記電極形成面のほぼ全面を被覆する様に第2の電子装置に接着剤層を形成する工程と、第1の電子装置に第2の電子装置を搭載する工程とより成り、第1の電子装置に第2の電子装置を搭載する工程で前記第1の電子装置上のバンプ電極が前記接着剤層を貫通して第2の電子装置上の電極と電気的に接続すると共に第1の電子装置と第2の電子装置間が前記接着剤層により封止され、接着剤層構成成分を第1の電子装置のバンプ電極と第2の電子装置の電極間に含んでなることを特徴とする。

【0017】

さらに本発明の半導体装置の製造方法は、ICが複数形成されたウェハの電極面と相対する面を支持体上に貼り付ける工程と、前記ウェハの電極形成面に接着剤フィルムを貼り付ける工程と、前記接着剤フィルムの貼り付けられたウェハを支持体上で複数のICチップに切断分離する工程とを含み、ICチップの電極形成面上に接着剤層を形成することを特徴とする。

【0018】

さらに本発明の半導体装置の製造方法は、ICが複数形成されたウェハの電極面と相対する面を支持体上に貼り付ける工程と、前記ウェハの電極形成面にスピンコート法により接着剤層をコーティングする工程と、前記接着材層の形成されたウェハを支持体上で複数のICチップに切断分離する工程を含み、ICチップの電極形成面上に接着剤層を形成することを特徴とする。

【0019】

さらに本発明の半導体装置の製造方法は、支持体上に形成された接着剤層上に前記ICが複数形成されたウェハの電極形成面を貼り付け、前記ウェハと接着剤層を支持体上で切断分離する工程を含み、ICチップの電極形成面上に接着剤層を形成することを特徴とする。

本発明の半導体装置は、半導体基板と、前記半導体基板の上面に形成された複数の電極と、前記複数の電極を完全に覆う封止樹脂層とから成ることを特徴とする。

また、本発明の半導体装置の製造方法は、半導体ウェハの上面に複数の電極を形成する工程と、前記複数の電極を完全に覆う封止樹脂層を形成する工程と、前記複数の電極が形成され且つ前記複数の電極を完全に覆う封止樹脂層が形成された半導体ウェハを複数の半導体装置に切り分ける工程とから成ることを特徴とする。

さらに、本発明の半導体装置の製造方法は、複数のバンプ電極を有する第一の半導体装置を準備する工程と、複数の電極と当該複数の電極を完全に覆う封止樹脂層とを有する第二の半導体装置を準備する工程と、前記第二の半導体装置を前記第一の半導体装置にマウントして前記バンプ電極が前記封止樹脂層を貫通するようにし前記バンプ電極と前記第二の半導体装置の電極とを接合する工程とから成ることを特徴とする。

【0020】

本発明の電子装置の製造方法によれば、子チップのウェハに対し、ダイシングシート上にマウントされた状態で接着剤フィルムを貼付して、ダイシングすることにより、樹脂量の最適化が可能になる。一般に子チップを親チップ上に搭載し接合したときの親チップ上での封止樹脂のはみ出しは、チップ間の間隙を埋める体積以上の樹脂が供給された場合や、供給位置が的確でない場合に発生する。例えば、接合プロセス直前に液状樹脂を親チップ上に供給するポッティング法では、正確に樹脂の量をチップ間の間隙を埋める体積とするのは困難である。また、接着剤フィルムを親チップ上に貼り付ける方法でも、子チップの搭載位置に正確に貼り付けるのは困難で、現実的には500ミクロン程度の貼付位置誤差が出る。これに対し、本発明の電子装置の製造方法によれば、子チップの面積と供給する樹脂フィルムの厚さにより樹脂量は決まり、また子チップのウェハに対し、ダイシングシート上にマウントされた状態で接着剤フィルムを貼付るので樹脂の供給位置も正確に子チップ直下となる。このことにより樹脂はみだしは極めて少なくなり、また樹脂の子チップ上への這い上がりの危険も少ないことから子チップの厚さも極めて薄くすることができる。

【発明の効果】

【0021】

本発明の効果として、本発明の電子装置の製造方法によれば、薄く研削された子チップのウェハに対し、ダイシングシート上にマウントされた状態で接着剤フィルムを貼付、ダイシングすることにより、樹脂量の最適化と子チップの薄チップ化が可能になり、親チップ、子チップのサイズ、厚さに関する制約が大幅に緩和され生産性が大幅に向上する。そのため設計自由度、生産性の高いチップ・オン・チップ型電子装置が得られる。

また本発明の電子装置によれば、接着剤層構成成分を第1の電子装置のバンプ電極と第2の電子装置の電極間に含んでなることにより接合圧力が局所的に集中し、例えばはんだ表面の自然酸化膜がやぶれることにより接合プロセスが安定する。この場合に第1の電子装置のバンプ電極と第2の電子装置の電極間はんだ界面に残留する接着剤層構成成分それ自体は直接的には接合には寄与することなく、接合圧力を局所的に集中させて接合プロセスを安定させるという間接的機能が認められる。

【発明を実施するための最良の形態】

【0022】

図1に示すように金属バンプ電極すなわちAuスタッドバンプ1を有する第1の電子装置すなわち親チップ2に搭載されると共に親チップ2のAuスタッドバンプ1に接続される電極を備える第2の電子装置すなわち子チップ3の子チップウェハ4の電極形成面のほぼ全面を被覆する様に子チップ3に接着剤層5を形成する工程と、親チップ2に子チップ3を搭載する工程とより成り、親チップ2に子チップ3を搭載する工程で親チップ2のAuスタッドバンプ1が接着剤層5を貫通して子チップ3上の電極と電気的に接続すると共に親チップ2と子チップ3間が接着剤層5により封止される。

以上のチップ・オン・チップ接合プロセスにおいて子チップ3と親チップ2とは表面に電子回路の形成された平板形状にされ、かつ、親チップ2は子チップ3より大きな回路面積を有する。また親チップ2は子チップ3と接続されない電極を有し、その電極が親チップ2に子チップ3を搭載した後に子チップ3との接続領域外の表面に露出している。これによって、親チップ2は他のICチップ若しくは配線基板との接続が可能となる。また親チップ2または子チップ3は少なくとも一方がICチップとされる。また親チップ2または子チップ3は少なくとも一方が配線基板であってもよい。

(実施例1)

【0023】

図1に本発明の電子装置の製造方法におけるチップ・オン・チップ接合プロセスの実施例1を示す。図1に示されるように、この実施例では、まず裏面研削により薄型化したダイシング前の子チップウェハ4をダイシングシート6上にマウントし、この状態で接着剤フィルムのウェハ4に対する貼り付けを行う。さらにそのように接着剤フィルムを貼り付け接着剤層5を形成した状態でダイシングブレード7によって子チップウェハ4のダイシングを行うことにより子チップ3の個片化を行う。この方法により、電極を含む素子形成面の全面に接着剤層5が形成された非常に薄い子チップ3が得られる。

【0024】

なお、ウェハ4上への接着剤層5の形成方法としては、液状樹脂をスピンコート法により塗布する方法を用いても良い。また、減圧雰囲気中でこれを行うことにより、気泡等を巻き込む事無く貼り付けることが可能となる。子チップ3の電極としてはAlやAuなどが望ましく、形状としては平面状のパッドであっても、メッキ法などで形成されたバンプ形状であっても良い。また子チップ3上のほぼ全面に形成され、Alパッド電極部分に開口部を有する保護膜表面すなわちポリイミドカバー膜表面から窪んだ位置に形成されたAlパッドとすることもできる。なお、保護膜材質としてはポリイミドなどの有機膜の他に、SiNなどの無機膜だけにすることもできる。

【0025】

一方、配線基板上に接着剤やAgペースト等を用いて搭載された親チップ2のAlパッド電極上にワイヤボンダを用いてAuスタッドバンプ1の形成を行う。

次に、チップ・オン・チップの接合プロセスでは、周知の超音波フリップチップボンダにより親チップ2上に子チップ3を搭載し、親チップ2上に形成されたバンプ電極が子チップ3の電極上の樹脂を貫通し、子チップ3の電極と接続し、同時に子チップ3上に形成された接着剤層5により、子チップ3及び親チップ2間が樹脂封止された状態が形成できる。この工法を用いることにより、チップ間を封止する樹脂の量はウェハ状態で貼り付ける樹脂フィルムの厚さとチップサイズによりほぼ正確に決定され、子チップ3の搭載される部分に正確に樹脂が供給されることになる。このことは、子チップ3の搭載領域から樹脂が大きくはみだすことで親チップ2上に形成されたパッケージ基板に接続するための電極を汚染することや、樹脂が子チップ3上に乗り上げることを防止することが可能となり、結果として子チップ3と親チップ2のチップサイズに関する制限が小さくなり、さらに、子チップ3を薄型化できるということを意味する。

【0026】

上記のプロセスにおいては、子チップ3上の樹脂層は、親チップ2への接合時にチップ間に樹脂が十分に充填されるために電極表面を完全に被覆していることが必要であり、また、フリップチップボンダにより搭載する際にカメラによる子チップ3表面のパターン認識が可能であることを考慮し、35ミクロン程度以下であることが望ましい。またフィルム樹脂の特性としては、ダイシングシート6上のウェハに貼り付けることを考慮し、100℃以下の低温で接着可能な樹脂であることが望ましい。また上記プロセスでは、親チップ2のバンプ電極が樹脂を貫通、子チップ3の電極に押圧する過程において、子チップ3に対して超音波振動を印加することにより、両電極間に存在する殆どの樹脂が排除され、電極間に金属的、電気的接続を得ることが可能である。この場合フィルム樹脂の構成成分が両電極間に残存する場合もある。この際、超音波の振動エネルギーが電極間に効率的に供給されて良好な電極間の接合を得るために、接合温度において樹脂の粘度が約1000Pa・s以下に下がるような樹脂を選択することが望ましい。このような適切な樹脂や接合プロセス条件を選定することにより、電極間の接合部に含まれる接着剤層5構成成分は微量となり、或いは無くなり、高い信頼性の確保が可能となる。

【0027】

以上のプロセスによりチップ・オン・チップ構造を形成した後は、一般の製造方法と同様に、ワイヤボンディングを用いて親チップ2上の電極と配線基板を接続、最後にチップやワイヤボンディング部をトランスファーモールド法などにより樹脂封止することにより、チップ・オン・チップ構造を含む半導体パッケージを形成する。

(実施例2)

【0028】

図2に本発明の実施例2を示す。実施例1では、親チップ2が配線基板上に搭載された状態で実施されているが、これに限らず、親チップ2をダイシングにより個片化する前の親チップウェハ8状態で子チップ3を接合しても構わない。このようにウェハ8状態で接合することにより、親チップ2、子チップ3間の高い平行度が得られ、狭ピッチの接続にも対応可能である。また、図では親チップ2上のバンプ電極として、メッキ法を用いて形成されたAuメッキバンプ1aを用いた場合を示している。親チップ2のバンプ電極としては、この他にもはんだバンプ電極を始め、各種の材料により構成されたバンプを用いることが可能である。さらに、親チップ2、子チップ3、いずれかの電極をはんだ材料により構成することで、はんだ溶融による液層拡散を用いた接合プロセスを用いることもできる。

【0029】

この実施例ではバンプ電極が狭ピッチ化することによりチップ間の間隙が小さくなった場合でも、親チップ2が厚さの均一性に優れたウェハ状態でチップ・オン・チップ接合プロセスを行うことにより、親チップ2と子チップ3の平行度を保つことが容易になる。またメッキ法により狭ピッチのバンプを形成できる。さらに、はんだを用いた溶融接合法を用いることにより接合部の下部に形成された配線や素子にダメージを与える危険の小さな接合プロセスが実現できる。

(実施例3)

【0030】

図3に子チップ3表面への接着剤層5の形成プロセスに関する前記各実施例とは異なる実施例を示す。この実施例ではダイシングを行う際の支持体であるダイシングシート6上にはあらかじめ接着剤フィルムを貼り付けて接着剤層5が形成されており、子チップ3ウェハ4の電極形成面をこの接着材層5に貼り付けた状態でダイシングブレード7により子チップ3と接着剤層5とを共に切断することにより表面に接着剤層5の形成された子チップ3を得ることが可能である。

(実施例4)

【0031】

図4に本発明の実施例4を示す。実施例4では親チップ2上のバンプ電極として、メッキ法を用いて形成されたAuメッキバンプ1aを用い、子チップ3の電極部9表面に低融点材料であるはんだ12を設けた。また接着剤層5は導電性フィラー11を分散して含有する。その結果、図4(b)に示されるように、親チップ2上のAuメッキバンプ1aと子チップ3のはんだ12が接合された状態では、接合部分に導電性フィラー11が介在する。その結果、導電性フィラー11が備える性能により、接合プロセスの安定化と、接合部分の特性改善が可能となる。具体的には、導電性フィラー11が介在することにより接合圧力が局所的に集中し、はんだ表面の自然酸化膜がやぶれることにより接合プロセスが安定する。また係る介在物は導電性フィラー11に限られず、例えば絶縁性介在物を介在させることによってAuメッキバンプ1aと子チップ3のはんだ12の接合強度を向上する等、目的に応じて介在物を選択し、Auメッキバンプ1aと子チップ3のはんだ12の接合部に所要の特性を付与することが可能となる。

なお、導電性フィラー11としては、図4(b)示される導体球の他に、樹脂コアを持つものなども用いることができる。

【0032】

なお以上の本発明の電子装置の製造方法の実施に際し、親チップ2上に子チップ3を搭載するに当たり、子チップ3を温度管理する機構を備える電子装置製造装置を用いて子チップ3を所定に温度管理して親チップ2上に子チップ3を搭載する製造工程を実施することによって、円滑に電子装置の製造工程を進めることができる。

【0033】

以上、本発明の好適な実施例について種々述べてきたが、本発明は前記実施例に限定されるものでなく、発明の精神を逸脱しない範囲でさらに多くの改変を施しえるのはもちろんのことである。

【0034】

例えば、ダイシングシート6はシート状のものに限定するものでなく、ウェハをダイシングする際にウェハを支持するもの(ここでは支持体と呼ぶ)であれば良い。また、ダイシングシート6上にあらかじめ接着剤層5を形成しておき、半導体ウェハの回路形成面を接着材層5に接着、ダイシングを行うという方法を用いても良い。また、子チップ3ウェハ4上への樹脂の供給方法としては、ダイシングシート6上でのフィルム樹脂の貼付によるものだけでなく、液状樹脂をスピンコート法によりウェハ上に供給する方法を用いても良い。いずれにしても、ダイシングを行う際のウェハを支持する構造体(支持体)の上でウェハに接着剤層5が形成され、この状態でダイシングを行うことにより、薄いチップに対して接着剤層を形成することが可能になる。

【0035】

バンプ接続工法に関しても、超音波併用熱圧着工法、熱圧着工法、はんだによる溶融接合法など電極構成素材に応じて最適なものを選ぶことができる。

また、ここまでは2つのICチップをチップ・オン・チップ接合する構成に関して述べてきたが、親チップ2すなわち第1の電子装置及び子チップ3すなわち第2の電子装置はそれぞれICに限定されず、いずれかが配線基板等の電子回路の形成された平板状の電子装置であっても良い。

【図面の簡単な説明】

【0036】

【図1】本発明に係る電子装置の接続方法の一実施例を示す図である。

【図2】本発明に係る電子装置の接続方法の他の一実施例を示す図である。

【図3】本発明に係る電子装置の接続方法の別の実施例を示す図である。

【図4】本発明に係る電子装置の接続方法のさらに他の実施例を示す図である。

【図5】従来における電子装置の接続方法を示す図である。

【符号の説明】

【0037】

1 Auスタッドバンプ

1a Auメッキバンプ

2 親チップ

3 子チップ

4 子チップウェハ

5 接着剤層

6 ダイシングシート

7 ダイシングブレード

8 親チップウェハ

10 Auスタッドバンプ電極

11 導電性フィラー

12 はんだ

20 親チップ

30 子チップ

40 接着樹脂

【特許請求の範囲】

【請求項1】

金属バンプ電極を有する第1の電子装置に搭載されると共に第1の電子装置の前記金属バンプに接続される電極を備える第2の電子装置の前記電極形成面のほぼ全面を被覆する様に第2の電子装置に接着剤層を形成する工程と、第1の電子装置に第2の電子装置を搭載する工程とより成り、第1の電子装置に第2の電子装置を搭載する工程で前記第1の電子装置上のバンプ電極が前記接着剤層を貫通して第2の電子装置上の電極と電気的に接続すると共に第1の電子装置と第2の電子装置間が前記接着剤層により封止されることを特徴とする電子装置の製造方法。

【請求項2】

第1の電子装置および第2の電子装置のそれぞれの表面に電子回路が形成され、第1の電子装置が第2の電子装置よりも大なる面積の領域に電子回路を有する請求項1に記載の電子装置の製造方法。

【請求項3】

第1の電子装置が、第2の電子装置の電極と接続されない電極を有し、第1の電子装置に第2の電子装置を搭載して第2の電子装置の電極と第1の電子装置の電極とを接続した後に第2の電子装置の電極と接続されない第1の電子装置の電極が表面に露出している請求項1に記載の電子装置の製造方法。

【請求項4】

第1の電子装置または第2の電子装置がICチップである請求項1に記載の電子装置の製造方法。

【請求項5】

第1の電子装置または第2の電子装置が配線基板である請求項1に記載の電子装置の製造方法。

【請求項6】

第1の電子装置上のバンプ電極の表面または第2の電子装置上の電極の表面が、AuまたはCuを主成分とする金属により形成されている請求項1に記載の電子装置の製造方法。

【請求項7】

第1の電子装置上のバンプ電極の表面または第2の電子装置上の電極の表面が電極材料よりも融点の低い低融点材料により形成されている請求項1に記載の電子装置の製造方法。

【請求項8】

第1の電子装置上のバンプ電極の表面がAuを主成分とする金属により形成されており、第2の電子装置上の電極の表面がAlを主成分とする金属により形成されている請求項1に記載の電子装置の製造方法。

【請求項9】

第1の電子装置が配線基板上に搭載されたICチップである請求項1に記載の電子装置の製造方法。

【請求項10】

複数のICが形成された半導体ウェハの各々のICを第1の電子装置として第1の電子装置に第2の電子装置を搭載する工程が行われる請求項1に記載の電子装置の製造方法。

【請求項11】

第2の電子装置がICチップである請求項1に記載の電子装置の製造方法。

【請求項12】

第1の電子装置上のバンプ電極がワイヤボンディング法を用いて形成されたAuスタッドバンプである請求項1に記載の電子装置の製造方法。

【請求項13】

第1の電子装置上のバンプ電極がメッキ法を用いて形成された金属バンプである請求項1に記載の電子装置の製造方法。

【請求項14】

第2の電子装置上の電極が、第2の電子装置上に形成され前記電極部分に開口部を有する保護膜表面から窪んだ位置に形成されたAlパッドである請求項1に記載の電子装置の製造方法。

【請求項15】

第2の電子装置上の電極が、AuメッキバンプまたはAuパッドである請求項1に記載の電子装置の製造方法。

【請求項16】

請求項1に記載の電子装置の製造方法において、第1の電子装置上に複数の第2の電子装置を搭載することを特徴とする電子装置の製造方法。

【請求項17】

請求項1に記載の電子装置の製造方法において、第1の電子装置に第2の電子装置を搭載し、第2の電子装置に対して、加熱及び加圧を行うことにより第1の電子装置上のバンプ電極と第2の電子装置上の電極とを接合すると共に接着剤層により第1の電子装置と第2の電子装置間を封止することを特徴とする電子装置の製造方法。

【請求項18】

請求項1に記載の電子装置の製造方法において、第1の電子装置上に第2の電子装置を搭載し、第2の電子装置に対して、加熱及び加圧を行うと共に超音波を印加することにより、第1の電子装置上のバンプ電極と第2の電子装置上の電極とを接合すると共に接着剤層により第1の電子装置と第2の電子装置間を封止することを特徴とする電子装置の製造方法。

【請求項19】

請求項1に記載の電子装置の製造方法において、第1の電子装置上に第2の電子装置を搭載し、第2の電子装置に対して、第1の工程で加熱及び加圧を行うと共に超音波を印加し、これに続く第2の工程で加圧力を上昇させることにより、第1の電子装置上のバンプ電極と第2の電子装置上の電極とを接合すると共に接着剤層により第1の電子装置と第2の電子装置間を封止することを特徴とする電子装置の製造方法。

【請求項20】

請求項1に記載の電子装置の製造方法において、第2の電子装置を所定に温度管理することを特徴とする電子装置の製造方法。

【請求項21】

金属バンプ電極を有する第1の電子装置に第2の電子装置を搭載して成り、前記第1の電子装置上のバンプ電極が接着剤層を貫通して第2の電子装置上の電極と電気的に接続されると共に第1の電子装置と第2の電子装置間が前記接着剤層により封止され、前記接着剤層構成成分を第1の電子装置のバンプ電極と第2の電子装置の電極間に含んでなることを特徴とする電子装置。

【請求項22】

金属バンプ電極を有する第1の電子装置に搭載されると共に第1の電子装置の前記金属バンプに接続される電極を備える第2の電子装置の前記電極形成面のほぼ全面を被覆する様に第2の電子装置に接着剤層を形成する工程と、第1の電子装置に第2の電子装置を搭載する工程とより成り、第1の電子装置に第2の電子装置を搭載する工程で前記第1の電子装置上のバンプ電極が前記接着剤層を貫通して第2の電子装置上の電極と電気的に接続すると共に第1の電子装置と第2の電子装置間が前記接着剤層により封止され、接着剤層構成成分を第1の電子装置のバンプ電極と第2の電子装置の電極間に含んでなることを特徴とする電子装置。

【請求項23】

ICが複数形成されたウェハの電極面と相対する面を支持体上に貼り付ける工程と、前記ウェハの電極形成面に接着剤フィルムを貼り付ける工程と、前記接着剤フィルムの貼り付けられたウェハを支持体上で複数のICチップに切断分離する工程とを含み、ICチップの電極形成面上に接着剤層を形成することを特徴とする半導体装置の製造方法。

【請求項24】

ICが複数形成されたウェハの電極面と相対する面を支持体上に貼り付ける工程と、前記ウェハの電極形成面にスピンコート法により接着剤層をコーティングする工程と、前記接着材層の形成されたウェハを支持体上で複数のICチップに切断分離する工程を含み、ICチップの電極形成面上に接着剤層を形成することを特徴とする半導体装置の製造方法。

【請求項25】

支持体上に形成された接着剤層上に前記ICが複数形成されたウェハの電極形成面を貼り付け、前記ウェハと接着剤層を支持体上で切断分離する工程を含み、ICチップの電極形成面上に接着剤層を形成することを特徴とする半導体装置の製造方法。

【請求項26】

請求項23又は24に記載の半導体装置の製造方法において、前記ウェハを支持体上に貼り付ける工程の前に、ウェハを薄化する工程を含むことを特徴とする半導体装置の製造方法。

【請求項27】

請求項25に記載の半導体装置の製造方法において、支持体上にウェハを貼り付ける工程の後に、ウェハの電極形成面と相対する面を研削し、ウェハを薄化する工程を含むことを特徴とする半導体装置の製造方法。

【請求項28】

半導体基板と、前記半導体基板の上面に形成された複数の電極と、前記複数の電極を完全に覆う封止樹脂層とから成ることを特徴とする半導体装置。

【請求項29】

請求項28に記載の半導体装置において、前記封止樹脂層を完全に覆う保護層が形成され、且つ前記保護層は前記複数の電極を露出するための穴が形成されていることを特徴とする半導体装置。

【請求項30】

請求項28に記載の半導体装置において、前記複数の電極は前記半導体基板の上面に形成されたパッド電極であることを特徴とする半導体装置。

【請求項31】

請求項28に記載の半導体装置において、前記複数の電極はそれぞれ、前記半導体基板の上面に形成されたパッド電極と当該パッド電極上に形成されたバンプとを有することを特徴とする半導体装置。

【請求項32】

請求項31に記載の半導体装置において、前記バンプはスタッド状の金属バンプであることを特徴とする半導体装置。

【請求項33】

請求項28に記載の半導体装置において、前記封止樹脂層は固体分子を含むフィラーを含有して成ることを特徴とする半導体装置。

【請求項34】

請求項33に記載の半導体装置において、前記固体分子は導電性を有することを特徴とする半導体装置。

【請求項35】

半導体ウェハの上面に複数の電極を形成する工程と、前記複数の電極を完全に覆う封止樹脂層を形成する工程と、前記複数の電極が形成され且つ前記複数の電極を完全に覆う封止樹脂層が形成された半導体ウェハを複数の半導体装置に切り分ける工程とから成ることを特徴とする半導体装置の製造方法。

【請求項36】

請求項35に記載の半導体装置の製造方法において、前記複数の電極はそれぞれ、前記半導体ウェハの上面に形成されたパッド電極と当該パッド電極上に形成されたバンプとを有し、前記バンプはプレーティングにより形成されることを特徴とする半導体装置の製造方法。

【請求項37】

請求項35に記載の半導体装置の製造方法において、前記封止樹脂の形成方法は、前記半導体ウェハの上面に前記封止樹脂の樹脂材料を置く工程と、前記樹脂材料が置かれた半導体ウェハを回転させて前記樹脂材料を前記半導体ウェハ上に薄く延ばして前記封止樹脂層を形成する工程とからなることを特徴とする半導体装置の製造方法。

【請求項38】

請求項35に記載の半導体装置の製造方法において、前記封止樹脂層の製造方法は、粘着性の樹脂シートを準備する工程と、前記粘着性の樹脂シートを前記半導体ウェハの上面に薄く延ばして前記封止樹脂層を形成する工程とからなることを特徴とする半導体装置の製造方法。

【請求項39】

請求項35に記載の半導体装置の製造方法において、基板の第一の表面に複数のバンプ電極を形成する工程と、前記半導体装置を前記基板にマウントして前記複数のバンプ電極が前記封止樹脂層を貫通するようにし前記半導体装置の電極と前記複数のバンプ電極とを接合する工程とを追加したことを特徴とする半導体装置の製造方法。

【請求項40】

請求項39に記載の半導体装置の製造方法において、前記基板は他の半導体装置であることを特徴とする半導体装置の製造方法。

【請求項41】

請求項39に記載の半導体装置の製造方法において、前記基板は介在物であることを特徴とする半導体装置の製造方法。

【請求項42】

請求項39に記載の半導体装置の製造方法において、前記基板はワイヤボードであることを特徴とする半導体装置の製造方法。

【請求項43】

請求項39に記載の半導体装置の製造方法において、前記封止樹脂層は固体分子を含むフィラーを含有し、前記バンプ電極と前記半導体装置の電極とが接合した後、前記固体分子の一部分が前記バンプ電極と前記半導体装置の電極との間に残留することを特徴とする半導体装置の製造方法。

【請求項44】

請求項43に記載の半導体装置の製造方法において、前記固体分子は導電性を有することを特徴とする半導体装置の製造方法。

【請求項45】

請求項38に記載の半導体装置の製造方法において、前記粘着性の樹脂シートはダイシングシート上で薄く延ばされ、前記粘着性の樹脂シートの上に前記半導体装置が下向きにしてあてがわれることを特徴とする半導体装置の製造方法。

【請求項46】

請求項39に記載の半導体装置の製造方法において、前記基板は第二の半導体ウェハであって、前記半導体装置を前記第二の半導体ウェハにマウントした後に前記第二の半導体ウェハを複数のチップ・オン・チップ構造の半導体装置に切断分離することを特徴とする半導体装置の製造方法。

【請求項47】

複数のバンプ電極を有する第一の半導体装置を準備する工程と、複数の電極と当該複数の電極を完全に覆う封止樹脂層とを有する第二の半導体装置を準備する工程と、前記第二の半導体装置を前記第一の半導体装置にマウントして前記バンプ電極が前記封止樹脂層を貫通するようにし前記バンプ電極と前記第二の半導体装置の電極とを接合する工程とから成ることを特徴とする半導体装置の製造方法。

【請求項1】

金属バンプ電極を有する第1の電子装置に搭載されると共に第1の電子装置の前記金属バンプに接続される電極を備える第2の電子装置の前記電極形成面のほぼ全面を被覆する様に第2の電子装置に接着剤層を形成する工程と、第1の電子装置に第2の電子装置を搭載する工程とより成り、第1の電子装置に第2の電子装置を搭載する工程で前記第1の電子装置上のバンプ電極が前記接着剤層を貫通して第2の電子装置上の電極と電気的に接続すると共に第1の電子装置と第2の電子装置間が前記接着剤層により封止されることを特徴とする電子装置の製造方法。

【請求項2】

第1の電子装置および第2の電子装置のそれぞれの表面に電子回路が形成され、第1の電子装置が第2の電子装置よりも大なる面積の領域に電子回路を有する請求項1に記載の電子装置の製造方法。

【請求項3】

第1の電子装置が、第2の電子装置の電極と接続されない電極を有し、第1の電子装置に第2の電子装置を搭載して第2の電子装置の電極と第1の電子装置の電極とを接続した後に第2の電子装置の電極と接続されない第1の電子装置の電極が表面に露出している請求項1に記載の電子装置の製造方法。

【請求項4】

第1の電子装置または第2の電子装置がICチップである請求項1に記載の電子装置の製造方法。

【請求項5】

第1の電子装置または第2の電子装置が配線基板である請求項1に記載の電子装置の製造方法。

【請求項6】

第1の電子装置上のバンプ電極の表面または第2の電子装置上の電極の表面が、AuまたはCuを主成分とする金属により形成されている請求項1に記載の電子装置の製造方法。

【請求項7】

第1の電子装置上のバンプ電極の表面または第2の電子装置上の電極の表面が電極材料よりも融点の低い低融点材料により形成されている請求項1に記載の電子装置の製造方法。

【請求項8】

第1の電子装置上のバンプ電極の表面がAuを主成分とする金属により形成されており、第2の電子装置上の電極の表面がAlを主成分とする金属により形成されている請求項1に記載の電子装置の製造方法。

【請求項9】

第1の電子装置が配線基板上に搭載されたICチップである請求項1に記載の電子装置の製造方法。

【請求項10】

複数のICが形成された半導体ウェハの各々のICを第1の電子装置として第1の電子装置に第2の電子装置を搭載する工程が行われる請求項1に記載の電子装置の製造方法。

【請求項11】

第2の電子装置がICチップである請求項1に記載の電子装置の製造方法。

【請求項12】

第1の電子装置上のバンプ電極がワイヤボンディング法を用いて形成されたAuスタッドバンプである請求項1に記載の電子装置の製造方法。

【請求項13】

第1の電子装置上のバンプ電極がメッキ法を用いて形成された金属バンプである請求項1に記載の電子装置の製造方法。

【請求項14】

第2の電子装置上の電極が、第2の電子装置上に形成され前記電極部分に開口部を有する保護膜表面から窪んだ位置に形成されたAlパッドである請求項1に記載の電子装置の製造方法。

【請求項15】

第2の電子装置上の電極が、AuメッキバンプまたはAuパッドである請求項1に記載の電子装置の製造方法。

【請求項16】

請求項1に記載の電子装置の製造方法において、第1の電子装置上に複数の第2の電子装置を搭載することを特徴とする電子装置の製造方法。

【請求項17】

請求項1に記載の電子装置の製造方法において、第1の電子装置に第2の電子装置を搭載し、第2の電子装置に対して、加熱及び加圧を行うことにより第1の電子装置上のバンプ電極と第2の電子装置上の電極とを接合すると共に接着剤層により第1の電子装置と第2の電子装置間を封止することを特徴とする電子装置の製造方法。

【請求項18】

請求項1に記載の電子装置の製造方法において、第1の電子装置上に第2の電子装置を搭載し、第2の電子装置に対して、加熱及び加圧を行うと共に超音波を印加することにより、第1の電子装置上のバンプ電極と第2の電子装置上の電極とを接合すると共に接着剤層により第1の電子装置と第2の電子装置間を封止することを特徴とする電子装置の製造方法。

【請求項19】

請求項1に記載の電子装置の製造方法において、第1の電子装置上に第2の電子装置を搭載し、第2の電子装置に対して、第1の工程で加熱及び加圧を行うと共に超音波を印加し、これに続く第2の工程で加圧力を上昇させることにより、第1の電子装置上のバンプ電極と第2の電子装置上の電極とを接合すると共に接着剤層により第1の電子装置と第2の電子装置間を封止することを特徴とする電子装置の製造方法。

【請求項20】

請求項1に記載の電子装置の製造方法において、第2の電子装置を所定に温度管理することを特徴とする電子装置の製造方法。

【請求項21】

金属バンプ電極を有する第1の電子装置に第2の電子装置を搭載して成り、前記第1の電子装置上のバンプ電極が接着剤層を貫通して第2の電子装置上の電極と電気的に接続されると共に第1の電子装置と第2の電子装置間が前記接着剤層により封止され、前記接着剤層構成成分を第1の電子装置のバンプ電極と第2の電子装置の電極間に含んでなることを特徴とする電子装置。

【請求項22】

金属バンプ電極を有する第1の電子装置に搭載されると共に第1の電子装置の前記金属バンプに接続される電極を備える第2の電子装置の前記電極形成面のほぼ全面を被覆する様に第2の電子装置に接着剤層を形成する工程と、第1の電子装置に第2の電子装置を搭載する工程とより成り、第1の電子装置に第2の電子装置を搭載する工程で前記第1の電子装置上のバンプ電極が前記接着剤層を貫通して第2の電子装置上の電極と電気的に接続すると共に第1の電子装置と第2の電子装置間が前記接着剤層により封止され、接着剤層構成成分を第1の電子装置のバンプ電極と第2の電子装置の電極間に含んでなることを特徴とする電子装置。

【請求項23】

ICが複数形成されたウェハの電極面と相対する面を支持体上に貼り付ける工程と、前記ウェハの電極形成面に接着剤フィルムを貼り付ける工程と、前記接着剤フィルムの貼り付けられたウェハを支持体上で複数のICチップに切断分離する工程とを含み、ICチップの電極形成面上に接着剤層を形成することを特徴とする半導体装置の製造方法。

【請求項24】

ICが複数形成されたウェハの電極面と相対する面を支持体上に貼り付ける工程と、前記ウェハの電極形成面にスピンコート法により接着剤層をコーティングする工程と、前記接着材層の形成されたウェハを支持体上で複数のICチップに切断分離する工程を含み、ICチップの電極形成面上に接着剤層を形成することを特徴とする半導体装置の製造方法。

【請求項25】

支持体上に形成された接着剤層上に前記ICが複数形成されたウェハの電極形成面を貼り付け、前記ウェハと接着剤層を支持体上で切断分離する工程を含み、ICチップの電極形成面上に接着剤層を形成することを特徴とする半導体装置の製造方法。

【請求項26】

請求項23又は24に記載の半導体装置の製造方法において、前記ウェハを支持体上に貼り付ける工程の前に、ウェハを薄化する工程を含むことを特徴とする半導体装置の製造方法。

【請求項27】

請求項25に記載の半導体装置の製造方法において、支持体上にウェハを貼り付ける工程の後に、ウェハの電極形成面と相対する面を研削し、ウェハを薄化する工程を含むことを特徴とする半導体装置の製造方法。

【請求項28】

半導体基板と、前記半導体基板の上面に形成された複数の電極と、前記複数の電極を完全に覆う封止樹脂層とから成ることを特徴とする半導体装置。

【請求項29】

請求項28に記載の半導体装置において、前記封止樹脂層を完全に覆う保護層が形成され、且つ前記保護層は前記複数の電極を露出するための穴が形成されていることを特徴とする半導体装置。

【請求項30】

請求項28に記載の半導体装置において、前記複数の電極は前記半導体基板の上面に形成されたパッド電極であることを特徴とする半導体装置。

【請求項31】

請求項28に記載の半導体装置において、前記複数の電極はそれぞれ、前記半導体基板の上面に形成されたパッド電極と当該パッド電極上に形成されたバンプとを有することを特徴とする半導体装置。

【請求項32】

請求項31に記載の半導体装置において、前記バンプはスタッド状の金属バンプであることを特徴とする半導体装置。

【請求項33】

請求項28に記載の半導体装置において、前記封止樹脂層は固体分子を含むフィラーを含有して成ることを特徴とする半導体装置。

【請求項34】

請求項33に記載の半導体装置において、前記固体分子は導電性を有することを特徴とする半導体装置。

【請求項35】

半導体ウェハの上面に複数の電極を形成する工程と、前記複数の電極を完全に覆う封止樹脂層を形成する工程と、前記複数の電極が形成され且つ前記複数の電極を完全に覆う封止樹脂層が形成された半導体ウェハを複数の半導体装置に切り分ける工程とから成ることを特徴とする半導体装置の製造方法。

【請求項36】

請求項35に記載の半導体装置の製造方法において、前記複数の電極はそれぞれ、前記半導体ウェハの上面に形成されたパッド電極と当該パッド電極上に形成されたバンプとを有し、前記バンプはプレーティングにより形成されることを特徴とする半導体装置の製造方法。

【請求項37】

請求項35に記載の半導体装置の製造方法において、前記封止樹脂の形成方法は、前記半導体ウェハの上面に前記封止樹脂の樹脂材料を置く工程と、前記樹脂材料が置かれた半導体ウェハを回転させて前記樹脂材料を前記半導体ウェハ上に薄く延ばして前記封止樹脂層を形成する工程とからなることを特徴とする半導体装置の製造方法。

【請求項38】

請求項35に記載の半導体装置の製造方法において、前記封止樹脂層の製造方法は、粘着性の樹脂シートを準備する工程と、前記粘着性の樹脂シートを前記半導体ウェハの上面に薄く延ばして前記封止樹脂層を形成する工程とからなることを特徴とする半導体装置の製造方法。

【請求項39】

請求項35に記載の半導体装置の製造方法において、基板の第一の表面に複数のバンプ電極を形成する工程と、前記半導体装置を前記基板にマウントして前記複数のバンプ電極が前記封止樹脂層を貫通するようにし前記半導体装置の電極と前記複数のバンプ電極とを接合する工程とを追加したことを特徴とする半導体装置の製造方法。

【請求項40】

請求項39に記載の半導体装置の製造方法において、前記基板は他の半導体装置であることを特徴とする半導体装置の製造方法。

【請求項41】

請求項39に記載の半導体装置の製造方法において、前記基板は介在物であることを特徴とする半導体装置の製造方法。

【請求項42】

請求項39に記載の半導体装置の製造方法において、前記基板はワイヤボードであることを特徴とする半導体装置の製造方法。

【請求項43】

請求項39に記載の半導体装置の製造方法において、前記封止樹脂層は固体分子を含むフィラーを含有し、前記バンプ電極と前記半導体装置の電極とが接合した後、前記固体分子の一部分が前記バンプ電極と前記半導体装置の電極との間に残留することを特徴とする半導体装置の製造方法。

【請求項44】

請求項43に記載の半導体装置の製造方法において、前記固体分子は導電性を有することを特徴とする半導体装置の製造方法。

【請求項45】

請求項38に記載の半導体装置の製造方法において、前記粘着性の樹脂シートはダイシングシート上で薄く延ばされ、前記粘着性の樹脂シートの上に前記半導体装置が下向きにしてあてがわれることを特徴とする半導体装置の製造方法。

【請求項46】

請求項39に記載の半導体装置の製造方法において、前記基板は第二の半導体ウェハであって、前記半導体装置を前記第二の半導体ウェハにマウントした後に前記第二の半導体ウェハを複数のチップ・オン・チップ構造の半導体装置に切断分離することを特徴とする半導体装置の製造方法。

【請求項47】

複数のバンプ電極を有する第一の半導体装置を準備する工程と、複数の電極と当該複数の電極を完全に覆う封止樹脂層とを有する第二の半導体装置を準備する工程と、前記第二の半導体装置を前記第一の半導体装置にマウントして前記バンプ電極が前記封止樹脂層を貫通するようにし前記バンプ電極と前記第二の半導体装置の電極とを接合する工程とから成ることを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2009−65183(P2009−65183A)

【公開日】平成21年3月26日(2009.3.26)

【国際特許分類】

【出願番号】特願2008−265799(P2008−265799)

【出願日】平成20年10月14日(2008.10.14)

【分割の表示】特願2003−295067(P2003−295067)の分割

【原出願日】平成15年8月19日(2003.8.19)

【出願人】(302062931)NECエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成21年3月26日(2009.3.26)

【国際特許分類】

【出願日】平成20年10月14日(2008.10.14)

【分割の表示】特願2003−295067(P2003−295067)の分割

【原出願日】平成15年8月19日(2003.8.19)

【出願人】(302062931)NECエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]