電子部品、半導体装置、及び半導体装置の製造方法

【課題】半導体基板の側面を基点としたクラックが半導体装置の多層配線層に伝播することを抑制する。

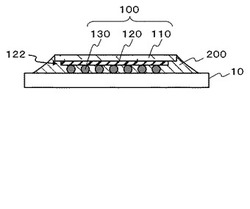

【解決手段】半導体装置100は実装基板10上に、バンプ130を用いてフリップチップ実装されている。アンダーフィル樹脂層200は、半導体装置100の能動面と実装基板10の間の空間を封止している。また半導体装置100の多層配線層120は半導体基板110の能動面側の面に形成されており、かつ半導体基板110の縁に位置する部分122が全周にわたって除去されている。多層配線層120のうち除去されている部分122の幅をwとして、半導体基板110の厚さをhとしたときに、w>hである。

【解決手段】半導体装置100は実装基板10上に、バンプ130を用いてフリップチップ実装されている。アンダーフィル樹脂層200は、半導体装置100の能動面と実装基板10の間の空間を封止している。また半導体装置100の多層配線層120は半導体基板110の能動面側の面に形成されており、かつ半導体基板110の縁に位置する部分122が全周にわたって除去されている。多層配線層120のうち除去されている部分122の幅をwとして、半導体基板110の厚さをhとしたときに、w>hである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、アンダーフィル樹脂を用いて実装基板上に半導体装置を実装した電子部品、半導体装置、及び半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置を実装基板に実装する方式の一つに、フリップチップ実装がある。フリップチップ実装は、半導体装置の能動面を実装基板に対向させ、バンプなどを介して実装基板の配線と半導体装置の外部接続端子とを接続するものである。フリップチップ実装において、半導体装置の能動面と実装基板の間の空間は、アンダーフィル樹脂により封止されている。

【0003】

半導体装置を実装基板に実装した半導体パッケージには、信頼性を確保するためにTC(熱サイクル)試験などが行われる。この熱サイクル試験の際には、膜が剥がれる可能性がある。この膜剥がれを抑制する技術として、例えば特許文献1及び2に記載の技術がある。特許文献1に記載の技術は、半導体チップの下面側のコーナー頂部に傾斜部を形成するものである。特許文献2に記載の技術は、半導体基板上に形成された積層膜の周縁部に、レーザ加工溝を形成するものである。

【0004】

また特許文献3には、半導体ウェハを複数の半導体チップに個片化する工程において、半導体チップのダイシングテープとの接着部分にクラックが生じることを抑制するために、半導体チップのエッジを階段状にすることが記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−294688号公報

【特許文献2】特開2008−78382号公報

【特許文献3】特開2001−127010号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、上記したTC試験において、本発明者は、図8に示すように、半導体装置の半導体基板の端部にクラックXが生じることがあることを見出した。これは、半導体装置400(特に半導体基板410)と実装基板430は、互いの熱膨張係数が異なり、また熱ストレスによって半導体装置400と実装基板430には互いに異なる方向の反りが生じるためと考えられる。このクラックXは、半導体基板410の断面において斜め45°の方向に進行することが多い。このため、上記した特許文献1〜3では、クラックXが半導体装置400の多層配線層420に伝播することを抑制することは難しかった

【課題を解決するための手段】

【0007】

本発明によれば、実装基板と、

前記実装基板上にフリップチップ実装された半導体装置と、

前記半導体装置の能動面と前記実装基板の間の空間を封止しているアンダーフィル樹脂層と、

を備え、

前記半導体装置は、

半導体基板と、

前記半導体基板の前記能動面に形成されていて前記半導体基板の縁に位置する部分が除去されている多層配線層と、

を有し、

前記多層配線層が除去されている領域の幅をwとして、前記半導体基板の厚さをhとしたときに、w>hである電子部品が提供される。

【0008】

本発明によれば、多層配線層は、半導体基板の縁に位置する部分が除去されている。そしてこの除去されている部分の幅wは、半導体基板の厚さhより大きい。一方、半導体基板に側面を基点としたクラックが発生し、このクラックが半導体基板の断面方向において斜め45°の方向に進行した場合、このクラックは、半導体基板の能動面のうち縁からh以上内側の部分には到達しない。従って、本発明によれば、クラックが半導体装置の多層配線層に伝播することを抑制できる。

【0009】

本発明によれば、半導体基板と、

前記半導体基板の能動面に形成されていて前記半導体基板の縁に位置する部分が除去されている多層配線層と、

を備え、

前記多層配線層が除去されている領域の幅をwとして、前記半導体基板の厚さをhとしたときに、w>hである半導体装置が提供される。

【0010】

本発明によれば、ウェハ上に多層配線層を形成する配線層形成工程と、

前記多層配線層のうちダイシングライン及びその周囲に位置する部分を除去する除去工程と、

前記ウェハを前記ダイシングラインに沿って切断することにより、複数の半導体装置を形成する装置形成工程と、

を備え、

前記複数の半導体装置は、前記多層配線層が除去されている領域の幅をwとして、前記ウェハの厚さをhとしたときに、w>hである半導体装置の製造方法が提供される。

【発明の効果】

【0011】

本発明によれば、半導体基板の側面を基点としたクラックが半導体装置の多層配線層に伝播することを抑制できる。

【図面の簡単な説明】

【0012】

【図1】第1の実施形態に係る半導体パッケージの構成を示す断面図である。

【図2】図1の要部を示す断面拡大図である。

【図3】第1の実施形態に係る半導体パッケージの製造方法を示す断面図である。

【図4】第2の実施形態に係る半導体パッケージの構造の要部を示す断面図である。

【図5】図4に示した半導体装置の製造方法を示す断面図である。

【図6】第3の実施形態に係る電子部品の構造の要部を示す断面図である。

【図7】図6に示した電子部品の製造方法を示す断面図である。

【図8】本発明の課題を説明するための断面図である。

【発明を実施するための形態】

【0013】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0014】

図1は、第1の実施形態に係る半導体パッケージの構成を示す断面図である。図2は、図1の要部を示す断面拡大図である。この半導体パッケージは、実装基板10、半導体装置100、及びアンダーフィル樹脂層200を備えている。半導体装置100は実装基板10上に、バンプ130を用いてフリップチップ実装されている。アンダーフィル樹脂層200は、半導体装置100の能動面と実装基板10の間の空間を封止している。また半導体装置100は、半導体基板110及び多層配線層120を有している。多層配線層120は半導体基板110の能動面側の面に形成されており、かつ半導体基板110の縁に位置する部分122が全周にわたって除去されている。多層配線層120のうち除去されている部分122の幅をwとして、半導体基板110の厚さをhとしたときに、w>hである。半導体基板110の厚さhは、例えば40μm超である。

【0015】

実装基板10は、例えばインターポーザ基板である。また半導体基板110は、例えばシリコンウェハであり、その表面の面方位は<110>である。半導体基板110の能動面には、トランジスタなどの素子(図示せず)が複数形成されている。これらの素子は、多層配線層120及びバンプ130を介して実装基板10の配線(図示せず)に接続している。なお上記した素子は、半導体基板110の能動面のうち多層配線層120が除去される領域には形成されていない。

【0016】

アンダーフィル樹脂層200は、例えばエポキシ樹脂を主成分としており、半導体基板110の側面の少なくとも一部も被覆している。

【0017】

図3の各図は、本実施形態に係る半導体パッケージの製造方法を示す断面図である。

まず図3(a)に示すように、ウェハ状態の半導体基板110にトランジスタを含む複数の素子(図示せず)を形成する。次いで、半導体基板110上に多層配線層120を形成する。多層配線層120の最上層の配線層には、電極パッド(図示せず)が形成されている。

【0018】

次いで第1のダイシングブレード300を用いて、多層配線層120のうちダイシングライン及びその周囲に位置する部分を除去する。ここでダイシングラインは、後述する第2のダイシングブレード310が通る領域として定義される。第1のダイシングブレード300の幅は、第2のダイシングブレード310の幅より広い。このため、第1のダイシングブレード300を用いることにより、多層配線層120のうちダイシングライン及びその周囲に位置する部分122を除去することができる。

【0019】

次いで図3(b)に示すように、第2のダイシングブレード310を用いてウェハ状態の半導体基板110を切断し、チップ状態の半導体装置100に個片化する。上記したように、多層配線層120は、第1のダイシングブレード300により、ダイシングラインの周囲に位置する部分が除去されている。このため、個片化された半導体装置100のそれぞれは、半導体基板110の縁に位置する部分122が除去された状態になる。

【0020】

そして図1に示すように、半導体装置100にバンプ130を形成し、バンプ130を用いて半導体装置100を実装基板10にフリップチップ実装する。次いで、半導体基板110の能動面と実装基板10の間の空間にアンダーフィル樹脂層200を形成する。このときアンダーフィル樹脂層200の周辺部は、半導体基板110の側面を這い上がり、フィレットを形成する。

【0021】

なお、実装基板10上にアンダーフィル樹脂層200を予め形成した後、アンダーフィル樹脂層200を硬化させる前に、バンプ130が形成された半導体装置100を実装基板10にフリップチップ実装してもよい。

【0022】

次に、本実施形態の作用及び効果について、図2を用いて説明する。フリップチップ実装構造を有している半導体パッケージにおいて、半導体基板110の端部にクラックXが進行することがある。クラックXは半導体基板110の側面のうち、例えばアンダーフィル樹脂層200の上端近傍を起点にしている。そしてクラックXの進行方向は、斜め下45°の方向である。このためクラックXは、半導体基板110の能動面のうち縁からh以上内側の部分には到達しない。

【0023】

一方、本実施形態では、多層配線層120は、半導体基板110の縁に位置する部分122が除去されている。そしてこの除去されている部分122の幅wは、半導体基板110の厚さhより大きい。このため、クラックXが多層配線層120に伝播し、配線のショートや層剥離に起因して半導体パッケージの信頼性が低下することを抑制できる。

【0024】

また図2に示すようにフィレットの上端近傍を基点としてクラックXが発生した場合であっても、クラックXは多層配線層120ではなくアンダーフィル樹脂層200に到達する。この状態において、半導体基板110のうちクラックXより外側に位置する部分はクラックXにより本体部分から分離された状態になる。アンダーフィル樹脂層200は半導体基板110より弾性を有しているため、半導体基板110の周縁部がクラックXより本体部分から分離されると、半導体基板110に生じる熱応力が緩和される。

【0025】

また、クラックXは多層配線層120ではなくアンダーフィル樹脂層200に到達するが、アンダーフィル樹脂層200ではクラックXが伝播しにくいため、クラックXの成長が抑制される。

【0026】

図4は、第2の実施形態に係る半導体パッケージの構造の要部を示す断面図であり、第1の実施形態における図2に相当している。本実施形態に係る半導体パッケージは、半導体基板110が能動面に凹部112を有している点を除いて、第1の実施形態に係る半導体装置と同様の構成である。

【0027】

凹部112は、半導体基板110の能動面のうち多層配線層が除去されている部分122に形成されている。本実施形態では、平面視において凹部112は多層配線層120が除去されている部分122の全面に形成されており、半導体基板110の全周にわたって形成されている。凹部112の深さをaとしたとき、0<a≦2h/3である。

【0028】

図5の各図は、図4に示した半導体装置の製造方法を示す断面図である。この半導体パッケージの製造方法は、図5(a)に示すように、第1のダイシングブレード300を用いて多層配線層120のうちダイシングライン及びその周囲に位置する部分122を除去するときに、第1のダイシングブレード300を用いて凹部112を形成する点を除いて、第1の実施形態に係る半導体パッケージの製造方法と同様である。

【0029】

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。また、半導体基板110に凹部112を形成しているため、クラックXが多層配線層120に伝播することをさらに抑制できる。また凹部の深さの上限を2h/3としたため、半導体基板110の周縁部の機械的強度を保つことができる。

【0030】

図6は、第3の実施形態に係る電子部品の構造の要部を示す断面図であり、第1の実施形態における図1に相当している。本実施形態に係る電子部品は、ウェハレベルCSP(Chip Size Package)構造を有している半導体装置102を、実装基板12にフリップチップ実装したものである。

【0031】

半導体装置102は、図1又は図4に示した半導体装置100に再配線層140を追加した構成である。なお図6では、図1に示した半導体装置100の場合を例示している。再配線層140は、多層配線層120上に位置しており、多層配線層120の電極パッド(図示せず)とバンプ132とを互いに接続している。そして再配線層140は、半導体基板110の縁に位置する部分が多層配線層120と共に除去されている。なお実装基板12、アンダーフィル樹脂層202、及びバンプ132は、図1における実装基板10、アンダーフィル樹脂層200、及びバンプ130に相当している。

【0032】

図7の各図は、図6に示した電子部品の製造方法を示す断面図である。この電子部品の製造方法は、以下の点を除いて、第1又は第2の半導体パッケージの製造方法と同様である。本図では、第1の半導体パッケージと同様の場合を示している。

【0033】

まず図7(a)に示すように、第1のダイシングブレード300を用いる前に、再配線層140を形成しておく。そして、第1のダイシングブレード300を用いて多層配線層120のうちダイシングライン及びその周囲に位置する部分122を除去するとき、再配線層140は、半導体基板110の縁に位置する部分が多層配線層120と共に除去される。

【0034】

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。

【0035】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。例えば第1のダイシングブレード300及び第2のダイシングブレード310を用いる代わりに、レーザダイシング法を用いてもよい。また多層配線層120や再配線層140を除去する方法は、上記した方法に限定されない。

【符号の説明】

【0036】

10 実装基板

12 実装基板

100 半導体装置

102 半導体装置

110 半導体基板

112 凹部

120 多層配線層

122 部分

130 バンプ

132 バンプ

140 再配線層

200 アンダーフィル樹脂層

202 アンダーフィル樹脂層

300 ダイシングブレード

310 ダイシングブレード

400 半導体装置

410 半導体基板

420 多層配線層

430 実装基板

【技術分野】

【0001】

本発明は、アンダーフィル樹脂を用いて実装基板上に半導体装置を実装した電子部品、半導体装置、及び半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置を実装基板に実装する方式の一つに、フリップチップ実装がある。フリップチップ実装は、半導体装置の能動面を実装基板に対向させ、バンプなどを介して実装基板の配線と半導体装置の外部接続端子とを接続するものである。フリップチップ実装において、半導体装置の能動面と実装基板の間の空間は、アンダーフィル樹脂により封止されている。

【0003】

半導体装置を実装基板に実装した半導体パッケージには、信頼性を確保するためにTC(熱サイクル)試験などが行われる。この熱サイクル試験の際には、膜が剥がれる可能性がある。この膜剥がれを抑制する技術として、例えば特許文献1及び2に記載の技術がある。特許文献1に記載の技術は、半導体チップの下面側のコーナー頂部に傾斜部を形成するものである。特許文献2に記載の技術は、半導体基板上に形成された積層膜の周縁部に、レーザ加工溝を形成するものである。

【0004】

また特許文献3には、半導体ウェハを複数の半導体チップに個片化する工程において、半導体チップのダイシングテープとの接着部分にクラックが生じることを抑制するために、半導体チップのエッジを階段状にすることが記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−294688号公報

【特許文献2】特開2008−78382号公報

【特許文献3】特開2001−127010号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、上記したTC試験において、本発明者は、図8に示すように、半導体装置の半導体基板の端部にクラックXが生じることがあることを見出した。これは、半導体装置400(特に半導体基板410)と実装基板430は、互いの熱膨張係数が異なり、また熱ストレスによって半導体装置400と実装基板430には互いに異なる方向の反りが生じるためと考えられる。このクラックXは、半導体基板410の断面において斜め45°の方向に進行することが多い。このため、上記した特許文献1〜3では、クラックXが半導体装置400の多層配線層420に伝播することを抑制することは難しかった

【課題を解決するための手段】

【0007】

本発明によれば、実装基板と、

前記実装基板上にフリップチップ実装された半導体装置と、

前記半導体装置の能動面と前記実装基板の間の空間を封止しているアンダーフィル樹脂層と、

を備え、

前記半導体装置は、

半導体基板と、

前記半導体基板の前記能動面に形成されていて前記半導体基板の縁に位置する部分が除去されている多層配線層と、

を有し、

前記多層配線層が除去されている領域の幅をwとして、前記半導体基板の厚さをhとしたときに、w>hである電子部品が提供される。

【0008】

本発明によれば、多層配線層は、半導体基板の縁に位置する部分が除去されている。そしてこの除去されている部分の幅wは、半導体基板の厚さhより大きい。一方、半導体基板に側面を基点としたクラックが発生し、このクラックが半導体基板の断面方向において斜め45°の方向に進行した場合、このクラックは、半導体基板の能動面のうち縁からh以上内側の部分には到達しない。従って、本発明によれば、クラックが半導体装置の多層配線層に伝播することを抑制できる。

【0009】

本発明によれば、半導体基板と、

前記半導体基板の能動面に形成されていて前記半導体基板の縁に位置する部分が除去されている多層配線層と、

を備え、

前記多層配線層が除去されている領域の幅をwとして、前記半導体基板の厚さをhとしたときに、w>hである半導体装置が提供される。

【0010】

本発明によれば、ウェハ上に多層配線層を形成する配線層形成工程と、

前記多層配線層のうちダイシングライン及びその周囲に位置する部分を除去する除去工程と、

前記ウェハを前記ダイシングラインに沿って切断することにより、複数の半導体装置を形成する装置形成工程と、

を備え、

前記複数の半導体装置は、前記多層配線層が除去されている領域の幅をwとして、前記ウェハの厚さをhとしたときに、w>hである半導体装置の製造方法が提供される。

【発明の効果】

【0011】

本発明によれば、半導体基板の側面を基点としたクラックが半導体装置の多層配線層に伝播することを抑制できる。

【図面の簡単な説明】

【0012】

【図1】第1の実施形態に係る半導体パッケージの構成を示す断面図である。

【図2】図1の要部を示す断面拡大図である。

【図3】第1の実施形態に係る半導体パッケージの製造方法を示す断面図である。

【図4】第2の実施形態に係る半導体パッケージの構造の要部を示す断面図である。

【図5】図4に示した半導体装置の製造方法を示す断面図である。

【図6】第3の実施形態に係る電子部品の構造の要部を示す断面図である。

【図7】図6に示した電子部品の製造方法を示す断面図である。

【図8】本発明の課題を説明するための断面図である。

【発明を実施するための形態】

【0013】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0014】

図1は、第1の実施形態に係る半導体パッケージの構成を示す断面図である。図2は、図1の要部を示す断面拡大図である。この半導体パッケージは、実装基板10、半導体装置100、及びアンダーフィル樹脂層200を備えている。半導体装置100は実装基板10上に、バンプ130を用いてフリップチップ実装されている。アンダーフィル樹脂層200は、半導体装置100の能動面と実装基板10の間の空間を封止している。また半導体装置100は、半導体基板110及び多層配線層120を有している。多層配線層120は半導体基板110の能動面側の面に形成されており、かつ半導体基板110の縁に位置する部分122が全周にわたって除去されている。多層配線層120のうち除去されている部分122の幅をwとして、半導体基板110の厚さをhとしたときに、w>hである。半導体基板110の厚さhは、例えば40μm超である。

【0015】

実装基板10は、例えばインターポーザ基板である。また半導体基板110は、例えばシリコンウェハであり、その表面の面方位は<110>である。半導体基板110の能動面には、トランジスタなどの素子(図示せず)が複数形成されている。これらの素子は、多層配線層120及びバンプ130を介して実装基板10の配線(図示せず)に接続している。なお上記した素子は、半導体基板110の能動面のうち多層配線層120が除去される領域には形成されていない。

【0016】

アンダーフィル樹脂層200は、例えばエポキシ樹脂を主成分としており、半導体基板110の側面の少なくとも一部も被覆している。

【0017】

図3の各図は、本実施形態に係る半導体パッケージの製造方法を示す断面図である。

まず図3(a)に示すように、ウェハ状態の半導体基板110にトランジスタを含む複数の素子(図示せず)を形成する。次いで、半導体基板110上に多層配線層120を形成する。多層配線層120の最上層の配線層には、電極パッド(図示せず)が形成されている。

【0018】

次いで第1のダイシングブレード300を用いて、多層配線層120のうちダイシングライン及びその周囲に位置する部分を除去する。ここでダイシングラインは、後述する第2のダイシングブレード310が通る領域として定義される。第1のダイシングブレード300の幅は、第2のダイシングブレード310の幅より広い。このため、第1のダイシングブレード300を用いることにより、多層配線層120のうちダイシングライン及びその周囲に位置する部分122を除去することができる。

【0019】

次いで図3(b)に示すように、第2のダイシングブレード310を用いてウェハ状態の半導体基板110を切断し、チップ状態の半導体装置100に個片化する。上記したように、多層配線層120は、第1のダイシングブレード300により、ダイシングラインの周囲に位置する部分が除去されている。このため、個片化された半導体装置100のそれぞれは、半導体基板110の縁に位置する部分122が除去された状態になる。

【0020】

そして図1に示すように、半導体装置100にバンプ130を形成し、バンプ130を用いて半導体装置100を実装基板10にフリップチップ実装する。次いで、半導体基板110の能動面と実装基板10の間の空間にアンダーフィル樹脂層200を形成する。このときアンダーフィル樹脂層200の周辺部は、半導体基板110の側面を這い上がり、フィレットを形成する。

【0021】

なお、実装基板10上にアンダーフィル樹脂層200を予め形成した後、アンダーフィル樹脂層200を硬化させる前に、バンプ130が形成された半導体装置100を実装基板10にフリップチップ実装してもよい。

【0022】

次に、本実施形態の作用及び効果について、図2を用いて説明する。フリップチップ実装構造を有している半導体パッケージにおいて、半導体基板110の端部にクラックXが進行することがある。クラックXは半導体基板110の側面のうち、例えばアンダーフィル樹脂層200の上端近傍を起点にしている。そしてクラックXの進行方向は、斜め下45°の方向である。このためクラックXは、半導体基板110の能動面のうち縁からh以上内側の部分には到達しない。

【0023】

一方、本実施形態では、多層配線層120は、半導体基板110の縁に位置する部分122が除去されている。そしてこの除去されている部分122の幅wは、半導体基板110の厚さhより大きい。このため、クラックXが多層配線層120に伝播し、配線のショートや層剥離に起因して半導体パッケージの信頼性が低下することを抑制できる。

【0024】

また図2に示すようにフィレットの上端近傍を基点としてクラックXが発生した場合であっても、クラックXは多層配線層120ではなくアンダーフィル樹脂層200に到達する。この状態において、半導体基板110のうちクラックXより外側に位置する部分はクラックXにより本体部分から分離された状態になる。アンダーフィル樹脂層200は半導体基板110より弾性を有しているため、半導体基板110の周縁部がクラックXより本体部分から分離されると、半導体基板110に生じる熱応力が緩和される。

【0025】

また、クラックXは多層配線層120ではなくアンダーフィル樹脂層200に到達するが、アンダーフィル樹脂層200ではクラックXが伝播しにくいため、クラックXの成長が抑制される。

【0026】

図4は、第2の実施形態に係る半導体パッケージの構造の要部を示す断面図であり、第1の実施形態における図2に相当している。本実施形態に係る半導体パッケージは、半導体基板110が能動面に凹部112を有している点を除いて、第1の実施形態に係る半導体装置と同様の構成である。

【0027】

凹部112は、半導体基板110の能動面のうち多層配線層が除去されている部分122に形成されている。本実施形態では、平面視において凹部112は多層配線層120が除去されている部分122の全面に形成されており、半導体基板110の全周にわたって形成されている。凹部112の深さをaとしたとき、0<a≦2h/3である。

【0028】

図5の各図は、図4に示した半導体装置の製造方法を示す断面図である。この半導体パッケージの製造方法は、図5(a)に示すように、第1のダイシングブレード300を用いて多層配線層120のうちダイシングライン及びその周囲に位置する部分122を除去するときに、第1のダイシングブレード300を用いて凹部112を形成する点を除いて、第1の実施形態に係る半導体パッケージの製造方法と同様である。

【0029】

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。また、半導体基板110に凹部112を形成しているため、クラックXが多層配線層120に伝播することをさらに抑制できる。また凹部の深さの上限を2h/3としたため、半導体基板110の周縁部の機械的強度を保つことができる。

【0030】

図6は、第3の実施形態に係る電子部品の構造の要部を示す断面図であり、第1の実施形態における図1に相当している。本実施形態に係る電子部品は、ウェハレベルCSP(Chip Size Package)構造を有している半導体装置102を、実装基板12にフリップチップ実装したものである。

【0031】

半導体装置102は、図1又は図4に示した半導体装置100に再配線層140を追加した構成である。なお図6では、図1に示した半導体装置100の場合を例示している。再配線層140は、多層配線層120上に位置しており、多層配線層120の電極パッド(図示せず)とバンプ132とを互いに接続している。そして再配線層140は、半導体基板110の縁に位置する部分が多層配線層120と共に除去されている。なお実装基板12、アンダーフィル樹脂層202、及びバンプ132は、図1における実装基板10、アンダーフィル樹脂層200、及びバンプ130に相当している。

【0032】

図7の各図は、図6に示した電子部品の製造方法を示す断面図である。この電子部品の製造方法は、以下の点を除いて、第1又は第2の半導体パッケージの製造方法と同様である。本図では、第1の半導体パッケージと同様の場合を示している。

【0033】

まず図7(a)に示すように、第1のダイシングブレード300を用いる前に、再配線層140を形成しておく。そして、第1のダイシングブレード300を用いて多層配線層120のうちダイシングライン及びその周囲に位置する部分122を除去するとき、再配線層140は、半導体基板110の縁に位置する部分が多層配線層120と共に除去される。

【0034】

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。

【0035】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。例えば第1のダイシングブレード300及び第2のダイシングブレード310を用いる代わりに、レーザダイシング法を用いてもよい。また多層配線層120や再配線層140を除去する方法は、上記した方法に限定されない。

【符号の説明】

【0036】

10 実装基板

12 実装基板

100 半導体装置

102 半導体装置

110 半導体基板

112 凹部

120 多層配線層

122 部分

130 バンプ

132 バンプ

140 再配線層

200 アンダーフィル樹脂層

202 アンダーフィル樹脂層

300 ダイシングブレード

310 ダイシングブレード

400 半導体装置

410 半導体基板

420 多層配線層

430 実装基板

【特許請求の範囲】

【請求項1】

実装基板と、

前記実装基板上にフリップチップ実装された半導体装置と、

前記半導体装置の能動面と前記実装基板の間の空間を封止しているアンダーフィル樹脂層と、

を備え、

前記半導体装置は、

半導体基板と、

前記半導体基板の前記能動面に形成されていて前記半導体基板の縁に位置する部分が除去されている多層配線層と、

を有し、

前記多層配線層が除去されている領域の幅をwとして、前記半導体基板の厚さをhとしたときに、w>hである電子部品。

【請求項2】

請求項1に記載の電子部品において、

前記半導体基板は、前記多層配線層が形成されている面のうち前記多層配線層が除去されている領域に凹部を有している電子部品。

【請求項3】

請求項2に記載の電子部品において、

前記凹部は前記多層配線層が除去されている領域の全面である電子部品。

【請求項4】

請求項2または3に記載の電子部品において、

前記凹部の深さをaとして、前記半導体基板の厚さをhとしたときに、0<a≦2h/3である電子部品。

【請求項5】

請求項1〜4のいずれか一つに記載の電子部品において、

前記半導体装置は、前記多層配線層上に形成された再配線層をさらに備え、

前記再配線層は、前記半導体基板の縁に位置する部分が前記多層配線層と共に除去されている電子部品。

【請求項6】

半導体基板と、

前記半導体基板の能動面に形成されていて前記半導体基板の縁に位置する部分が除去されている多層配線層と、

を備え、

前記多層配線層が除去されている領域の幅をwとして、前記半導体基板の厚さをhとしたときに、w>hである半導体装置。

【請求項7】

請求項6に記載の半導体装置において、

前記半導体基板は、前記多層配線層が形成されている面のうち前記多層配線層が除去されている領域に凹部を有している半導体装置。

【請求項8】

請求項7に記載の半導体装置において、

前記凹部は前記多層配線層が除去されている領域の全面である半導体装置。

【請求項9】

請求項7または8に記載の半導体装置において、

前記凹部の深さをaとして、前記半導体基板の厚さをhとしたときに、0<a≦2h/3である半導体装置。

【請求項10】

請求項6〜9のいずれか一つに記載の半導体装置において、

前記多層配線層上に形成された再配線層をさらに備え、

前記再配線層は、前記半導体基板の縁に位置する部分が前記多層配線層と共に除去されている半導体装置。

【請求項11】

ウェハ上に多層配線層を形成する配線層形成工程と、

前記多層配線層のうちダイシングライン及びその周囲に位置する部分を除去する除去工程と、

前記ウェハを前記ダイシングラインに沿って切断することにより、複数の半導体装置を形成する装置形成工程と、

を備え、

前記複数の半導体装置は、前記多層配線層が除去されている領域の幅をwとして、前記ウェハの厚さをhとしたときに、w>hである半導体装置の製造方法。

【請求項12】

請求項11に記載の半導体装置の製造方法において、

前記装置形成工程の後に、

前記半導体装置を実装基板上にフリップチップ実装する工程と、

前記半導体装置と前記実装基板の間の空間をアンダーフィル樹脂層で封止する工程と、

を備える半導体装置の製造方法。

【請求項13】

請求項11又は請求項12に記載の半導体装置の製造方法において、

前記配線層形成工程と、前記除去工程の間に、前記多層配線層上に再配線層を形成する工程を備え、

前記除去工程において、前記再配線層のうち前記ダイシングライン及びその周囲に位置する部分を前記多層配線層と共に除去する半導体装置の製造方法。

【請求項1】

実装基板と、

前記実装基板上にフリップチップ実装された半導体装置と、

前記半導体装置の能動面と前記実装基板の間の空間を封止しているアンダーフィル樹脂層と、

を備え、

前記半導体装置は、

半導体基板と、

前記半導体基板の前記能動面に形成されていて前記半導体基板の縁に位置する部分が除去されている多層配線層と、

を有し、

前記多層配線層が除去されている領域の幅をwとして、前記半導体基板の厚さをhとしたときに、w>hである電子部品。

【請求項2】

請求項1に記載の電子部品において、

前記半導体基板は、前記多層配線層が形成されている面のうち前記多層配線層が除去されている領域に凹部を有している電子部品。

【請求項3】

請求項2に記載の電子部品において、

前記凹部は前記多層配線層が除去されている領域の全面である電子部品。

【請求項4】

請求項2または3に記載の電子部品において、

前記凹部の深さをaとして、前記半導体基板の厚さをhとしたときに、0<a≦2h/3である電子部品。

【請求項5】

請求項1〜4のいずれか一つに記載の電子部品において、

前記半導体装置は、前記多層配線層上に形成された再配線層をさらに備え、

前記再配線層は、前記半導体基板の縁に位置する部分が前記多層配線層と共に除去されている電子部品。

【請求項6】

半導体基板と、

前記半導体基板の能動面に形成されていて前記半導体基板の縁に位置する部分が除去されている多層配線層と、

を備え、

前記多層配線層が除去されている領域の幅をwとして、前記半導体基板の厚さをhとしたときに、w>hである半導体装置。

【請求項7】

請求項6に記載の半導体装置において、

前記半導体基板は、前記多層配線層が形成されている面のうち前記多層配線層が除去されている領域に凹部を有している半導体装置。

【請求項8】

請求項7に記載の半導体装置において、

前記凹部は前記多層配線層が除去されている領域の全面である半導体装置。

【請求項9】

請求項7または8に記載の半導体装置において、

前記凹部の深さをaとして、前記半導体基板の厚さをhとしたときに、0<a≦2h/3である半導体装置。

【請求項10】

請求項6〜9のいずれか一つに記載の半導体装置において、

前記多層配線層上に形成された再配線層をさらに備え、

前記再配線層は、前記半導体基板の縁に位置する部分が前記多層配線層と共に除去されている半導体装置。

【請求項11】

ウェハ上に多層配線層を形成する配線層形成工程と、

前記多層配線層のうちダイシングライン及びその周囲に位置する部分を除去する除去工程と、

前記ウェハを前記ダイシングラインに沿って切断することにより、複数の半導体装置を形成する装置形成工程と、

を備え、

前記複数の半導体装置は、前記多層配線層が除去されている領域の幅をwとして、前記ウェハの厚さをhとしたときに、w>hである半導体装置の製造方法。

【請求項12】

請求項11に記載の半導体装置の製造方法において、

前記装置形成工程の後に、

前記半導体装置を実装基板上にフリップチップ実装する工程と、

前記半導体装置と前記実装基板の間の空間をアンダーフィル樹脂層で封止する工程と、

を備える半導体装置の製造方法。

【請求項13】

請求項11又は請求項12に記載の半導体装置の製造方法において、

前記配線層形成工程と、前記除去工程の間に、前記多層配線層上に再配線層を形成する工程を備え、

前記除去工程において、前記再配線層のうち前記ダイシングライン及びその周囲に位置する部分を前記多層配線層と共に除去する半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2011−146453(P2011−146453A)

【公開日】平成23年7月28日(2011.7.28)

【国際特許分類】

【出願番号】特願2010−4589(P2010−4589)

【出願日】平成22年1月13日(2010.1.13)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成23年7月28日(2011.7.28)

【国際特許分類】

【出願日】平成22年1月13日(2010.1.13)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]