電子部品の実装基板および実装方法

【課題】はんだ付け不良を低減する。

【解決手段】絶縁性基板1上に耐熱性及び電気絶縁性を有するフィルム4を、絶縁性基板1のパッド2を避けるように形成し、パッド2上にはんだバンプ3を形成して電子部品の実装基板を得る。実装基板上に電子部品を載せて、この電子部品の電極をはんだバンプ上に重ね合わせ、はんだバンプを溶融させてパッドと電子部品の電極とをはんだによって接合する。

【解決手段】絶縁性基板1上に耐熱性及び電気絶縁性を有するフィルム4を、絶縁性基板1のパッド2を避けるように形成し、パッド2上にはんだバンプ3を形成して電子部品の実装基板を得る。実装基板上に電子部品を載せて、この電子部品の電極をはんだバンプ上に重ね合わせ、はんだバンプを溶融させてパッドと電子部品の電極とをはんだによって接合する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体チップやBGA等の電子部品を実装する実装基板、および電子部品の実装方法に関するものである。

【背景技術】

【0002】

従来より、半導体チップ又はBGA(Ball Grid Array )を基板上に実装する場合、図4(A)のように基板100上のパッド101にはんだバンプ102を形成し、図4(B)のように基板100上にフラックス103を塗布し、図4(C)のように半導体チップ(又はBGA)104を基板100上にマウントし、図4(D)のようにリフローにより半導体チップ(又はBGA)104と基板100とをはんだ付けしていた。

【0003】

図5は特許文献1に開示された従来の他の実装方法を示す集積回路の断面図である。図5において、200は基板、201はパッド、202ははんだバンプ、203は半導体チップ、204は抑止部材(ダム)である。特許文献1に開示された実装方法では、リフローによりはんだ付けを行う際に、はんだバンプ202がパッド201の外側に過剰に流れることを防止するために、枠状の抑止部材204を設けるようにしている。

【0004】

図6は特許文献2に開示された従来の他の実装方法を示す集積回路の断面図である。図6において、300は基板、301はパッド、302は電子部品、303は電子部品302のリード、304はフィルム構体、305はクリームはんだである。特許文献2に開示された実装方法では、電気絶縁性・耐熱性を有するフィルムの開口内にクリームはんだ305を充填して接合用フィルム構体304を作製し、このフィルム構体304を基板300上に支給して、クリームはんだ305を基板300のパッド301上に重ね合わせる。そして、電子部品302をフィルム構体304上に支給し、電子部品302のリード303をクリームはんだ305上に重ね合わせ、基板300を加熱してクリームはんだ305を溶融させる。こうして、特許文献2に開示された実装方法では、フィルム構体304によってクリームはんだ305の広がりを阻止するようにしている。

【0005】

【特許文献1】特開昭57−210638号公報

【特許文献2】特開平7−015122号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

図4(A)〜図4(D)に示した従来の実装方法では、図4(D)の工程において、はんだショート105、はんだぬれ不良106等のはんだ付け不良が生じることがあるという問題点があった。

また、特許文献1に開示された実装方法では、はんだバンプがパッドの外側に流れることを防止できるが、図4(A)〜図4(D)の場合と同様に、はんだ付け不良の発生を防止することはできなかった。

また、特許文献2に開示された実装方法では、狭ピッチのベアチップなどを実装する場合に、フィルムから溢れ出たはんだペーストがショートして不良が発生する可能性があった。

【0007】

本発明は、上記課題を解決するためになされたもので、はんだ付け不良を低減することができる電子部品の実装基板および実装方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の電子部品の実装基板は、絶縁性基板と、この絶縁性基板上に形成されたパッドと、このパッド上に形成されたはんだバンプと、前記絶縁性基板上に、前記パッド及びはんだバンプを避けるように形成された耐熱性及び電気絶縁性を有するフィルムとを備えるものである。

また、本発明の電子部品の実装基板の1構成例において、前記フィルムは、可溶性フィルムであることを特徴とする。

【0009】

また、本発明の電子部品の実装方法は、絶縁性基板上に耐熱性及び電気絶縁性を有するフィルムを、前記絶縁性基板のパッドを避けるように形成し、前記パッド上にはんだバンプを形成して電子部品の実装基板を得る基板作製工程と、前記実装基板上に電子部品を載せて、この電子部品の電極を前記はんだバンプ上に重ね合わせる搭載工程と、前記はんだバンプを溶融させて前記パッドと前記電子部品の電極とをはんだによって接合するリフロー工程とを有するものである。

また、本発明の電子部品の実装方法は、絶縁性基板のパッド上にはんだバンプを形成し、前記絶縁性基板上に耐熱性及び電気絶縁性を有するフィルムを、前記パッド及びはんだバンプを避けるように形成して電子部品の実装基板を得る基板作製工程と、前記実装基板上に電子部品を載せて、この電子部品の電極を前記はんだバンプ上に重ね合わせる搭載工程と、前記はんだバンプを溶融させて前記パッドと前記電子部品の電極とをはんだによって接合するリフロー工程とを有するものである。

また、本発明の電子部品の実装方法の1構成例において、前記フィルムは、可溶性フィルムであり、前記リフロー工程の後に、前記フィルムを溶剤で除去する除去工程を有することを特徴とする。

【発明の効果】

【0010】

本発明によれば、パッド及びはんだバンプを避けるようにして絶縁性基板上にフィルムを形成した実装基板を用いることにより、電子部品の実装時のリフロー工程におけるフラックス不足を解消することができ、また電子部品と絶縁性基板との間のスタンドオフ高さを確保することができ、電子部品に荷重をかけながらリフローを行うことができるので、はんだぬれ不良を防止することができ、電子部品と基板との位置ずれを防止することができる。また、本発明では、フィルムによって隣接バンプ同士を完全に隔離することができるので、はんだショートを防止することができる。また、本発明では、リフロー後のスタンドオフ高さもフィルムの厚みによって制御することができる。

【0011】

また、本発明では、可溶性フィルムを用いることにより、電子部品の実装後に溶解によりフィルムを取り除くことができる。

【発明を実施するための最良の形態】

【0012】

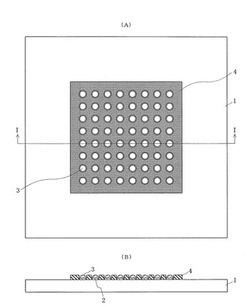

以下、本発明の実施の形態について図面を参照して説明する。図1(A)は本発明の実施の形態に係る実装基板の平面図、図1(B)は図1(A)の実装基板のI−I線断面図である。1は半導体チップ又はBGA等の電子部品(不図示)を実装する絶縁性基板、2は電子部品の電極と接続される導電層であるパッド、3はパッド2上に形成されたはんだバンプ、4は絶縁性基板1上に形成された、電気絶縁性及び耐熱性を有するフィルムである。

【0013】

本実施の形態の実装基板は、絶縁性基板1上に、はんだバンプ3を避けるような形でフィルム4が形成されていることを特徴とする。このフィルム4は、電子部品を実装する際のリフロー温度に対する耐熱性、及び電気絶縁性を有することが必要である。また、電子部品の実装後に、フィルム4の除去が必要な場合は、フィルム4の材料として例えば有機溶剤に可溶な可溶性ポリイミドフィルム等の材料を用いればよい。

【0014】

次に、本実施の形態の実装基板の作製方法と、実装基板への電子部品の実装方法について図2、図3を用いて説明する。図2(D)、図2(E)、図2(F)、図3(C)、図3(D)は、それぞれ図2(A)、図2(B)、図2(C)、図3(A)、図3(B)の点aの部分を拡大した断面図である。

【0015】

最初に、実装基板の作製方法について説明する。まず、図2(A)、図2(D)に示す絶縁性基板1上にパッド2を避けるような形でフィルム4を形成する(図2(B)、図2(E))。可溶性ポリイミドを用いてフィルム4を形成する場合には、例えば絶縁性基板1上にポリイミドを塗布して硬化させた後、エッチングによってパッド2の部分のポリイミドを除去するパターニング成形を行えばよい。

【0016】

続いて、図2(C)、図2(F)に示すように、パッド2上にはんだバンプ3を形成する。これで、図1(A)、図1(B)に示した実装基板が完成する。

なお、上記のプロセスとは逆に、まずパッド2上にはんだバンプ3を形成し、続いて絶縁性基板1上にパッド2及びはんだバンプ3を避けるような形でフィルム4を形成してもよい。

【0017】

次に、実装基板への電子部品の実装方法について説明する。まず、図3(A)、図3(C)に示すように、実装基板にフラックス5を塗布する。ただし、この工程は省略できる場合もある。

続いて、半導体チップ又はBGA等の電子部品6を実装基板上に載せて、電子部品6に重りを載せる等して荷重をかけ、リフローによりはんだバンプ3を溶融させてパッド2と電子部品6の電極とをはんだによって接合する(図3(B)、図3(D))。

【0018】

こうして、実装基板への電子部品の実装が完了するが、フィルム4の除去が必要な場合には、図3(B)、図3(D)の工程の後でフィルム4を有機溶剤等で除去する。

以上のように、本実施の形態では、電子部品と絶縁性基板との間にフィルムを挟むことにより、リフロー時のフラックス不足を解消することができ、また電子部品と絶縁性基板との間のスタンドオフ高さを確保することができ、電子部品に荷重をかけながらリフローを行うことができるので、はんだぬれ不良を防止することができ、電子部品と基板との位置ずれを防止することができる。また、本実施の形態では、フィルムによって隣接バンプ同士を完全に隔離することができるので、はんだショートを防止することができる。また、本実施の形態では、リフロー後のスタンドオフ高さもフィルムの厚みによって制御することができる。さらに、本実施の形態では、溶解性のフィルムを用いた場合には、電子部品の実装後に溶解によりフィルムを取り除くことができる。

【産業上の利用可能性】

【0019】

本発明は、半導体チップやBGA等の電子部品の実装に適用することができる。

【図面の簡単な説明】

【0020】

【図1】本発明の実施の形態に係る実装基板の平面図及び断面図である。

【図2】図1の実装基板の作製方法と実装基板への電子部品の実装方法を示す平面図及び断面図である。

【図3】図1の実装基板の作製方法と実装基板への電子部品の実装方法を示す平面図及び断面図である。

【図4】半導体チップ又はBGAを基板上に実装する従来の実装方法を示す断面図である。

【図5】従来の他の実装方法を示す集積回路の断面図である。

【図6】従来の他の実装方法を示す集積回路の断面図である。

【符号の説明】

【0021】

1…絶縁性基板、2…パッド、3…はんだバンプ、4…フィルム、5…フラックス、6…電子部品。

【技術分野】

【0001】

本発明は、半導体チップやBGA等の電子部品を実装する実装基板、および電子部品の実装方法に関するものである。

【背景技術】

【0002】

従来より、半導体チップ又はBGA(Ball Grid Array )を基板上に実装する場合、図4(A)のように基板100上のパッド101にはんだバンプ102を形成し、図4(B)のように基板100上にフラックス103を塗布し、図4(C)のように半導体チップ(又はBGA)104を基板100上にマウントし、図4(D)のようにリフローにより半導体チップ(又はBGA)104と基板100とをはんだ付けしていた。

【0003】

図5は特許文献1に開示された従来の他の実装方法を示す集積回路の断面図である。図5において、200は基板、201はパッド、202ははんだバンプ、203は半導体チップ、204は抑止部材(ダム)である。特許文献1に開示された実装方法では、リフローによりはんだ付けを行う際に、はんだバンプ202がパッド201の外側に過剰に流れることを防止するために、枠状の抑止部材204を設けるようにしている。

【0004】

図6は特許文献2に開示された従来の他の実装方法を示す集積回路の断面図である。図6において、300は基板、301はパッド、302は電子部品、303は電子部品302のリード、304はフィルム構体、305はクリームはんだである。特許文献2に開示された実装方法では、電気絶縁性・耐熱性を有するフィルムの開口内にクリームはんだ305を充填して接合用フィルム構体304を作製し、このフィルム構体304を基板300上に支給して、クリームはんだ305を基板300のパッド301上に重ね合わせる。そして、電子部品302をフィルム構体304上に支給し、電子部品302のリード303をクリームはんだ305上に重ね合わせ、基板300を加熱してクリームはんだ305を溶融させる。こうして、特許文献2に開示された実装方法では、フィルム構体304によってクリームはんだ305の広がりを阻止するようにしている。

【0005】

【特許文献1】特開昭57−210638号公報

【特許文献2】特開平7−015122号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

図4(A)〜図4(D)に示した従来の実装方法では、図4(D)の工程において、はんだショート105、はんだぬれ不良106等のはんだ付け不良が生じることがあるという問題点があった。

また、特許文献1に開示された実装方法では、はんだバンプがパッドの外側に流れることを防止できるが、図4(A)〜図4(D)の場合と同様に、はんだ付け不良の発生を防止することはできなかった。

また、特許文献2に開示された実装方法では、狭ピッチのベアチップなどを実装する場合に、フィルムから溢れ出たはんだペーストがショートして不良が発生する可能性があった。

【0007】

本発明は、上記課題を解決するためになされたもので、はんだ付け不良を低減することができる電子部品の実装基板および実装方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の電子部品の実装基板は、絶縁性基板と、この絶縁性基板上に形成されたパッドと、このパッド上に形成されたはんだバンプと、前記絶縁性基板上に、前記パッド及びはんだバンプを避けるように形成された耐熱性及び電気絶縁性を有するフィルムとを備えるものである。

また、本発明の電子部品の実装基板の1構成例において、前記フィルムは、可溶性フィルムであることを特徴とする。

【0009】

また、本発明の電子部品の実装方法は、絶縁性基板上に耐熱性及び電気絶縁性を有するフィルムを、前記絶縁性基板のパッドを避けるように形成し、前記パッド上にはんだバンプを形成して電子部品の実装基板を得る基板作製工程と、前記実装基板上に電子部品を載せて、この電子部品の電極を前記はんだバンプ上に重ね合わせる搭載工程と、前記はんだバンプを溶融させて前記パッドと前記電子部品の電極とをはんだによって接合するリフロー工程とを有するものである。

また、本発明の電子部品の実装方法は、絶縁性基板のパッド上にはんだバンプを形成し、前記絶縁性基板上に耐熱性及び電気絶縁性を有するフィルムを、前記パッド及びはんだバンプを避けるように形成して電子部品の実装基板を得る基板作製工程と、前記実装基板上に電子部品を載せて、この電子部品の電極を前記はんだバンプ上に重ね合わせる搭載工程と、前記はんだバンプを溶融させて前記パッドと前記電子部品の電極とをはんだによって接合するリフロー工程とを有するものである。

また、本発明の電子部品の実装方法の1構成例において、前記フィルムは、可溶性フィルムであり、前記リフロー工程の後に、前記フィルムを溶剤で除去する除去工程を有することを特徴とする。

【発明の効果】

【0010】

本発明によれば、パッド及びはんだバンプを避けるようにして絶縁性基板上にフィルムを形成した実装基板を用いることにより、電子部品の実装時のリフロー工程におけるフラックス不足を解消することができ、また電子部品と絶縁性基板との間のスタンドオフ高さを確保することができ、電子部品に荷重をかけながらリフローを行うことができるので、はんだぬれ不良を防止することができ、電子部品と基板との位置ずれを防止することができる。また、本発明では、フィルムによって隣接バンプ同士を完全に隔離することができるので、はんだショートを防止することができる。また、本発明では、リフロー後のスタンドオフ高さもフィルムの厚みによって制御することができる。

【0011】

また、本発明では、可溶性フィルムを用いることにより、電子部品の実装後に溶解によりフィルムを取り除くことができる。

【発明を実施するための最良の形態】

【0012】

以下、本発明の実施の形態について図面を参照して説明する。図1(A)は本発明の実施の形態に係る実装基板の平面図、図1(B)は図1(A)の実装基板のI−I線断面図である。1は半導体チップ又はBGA等の電子部品(不図示)を実装する絶縁性基板、2は電子部品の電極と接続される導電層であるパッド、3はパッド2上に形成されたはんだバンプ、4は絶縁性基板1上に形成された、電気絶縁性及び耐熱性を有するフィルムである。

【0013】

本実施の形態の実装基板は、絶縁性基板1上に、はんだバンプ3を避けるような形でフィルム4が形成されていることを特徴とする。このフィルム4は、電子部品を実装する際のリフロー温度に対する耐熱性、及び電気絶縁性を有することが必要である。また、電子部品の実装後に、フィルム4の除去が必要な場合は、フィルム4の材料として例えば有機溶剤に可溶な可溶性ポリイミドフィルム等の材料を用いればよい。

【0014】

次に、本実施の形態の実装基板の作製方法と、実装基板への電子部品の実装方法について図2、図3を用いて説明する。図2(D)、図2(E)、図2(F)、図3(C)、図3(D)は、それぞれ図2(A)、図2(B)、図2(C)、図3(A)、図3(B)の点aの部分を拡大した断面図である。

【0015】

最初に、実装基板の作製方法について説明する。まず、図2(A)、図2(D)に示す絶縁性基板1上にパッド2を避けるような形でフィルム4を形成する(図2(B)、図2(E))。可溶性ポリイミドを用いてフィルム4を形成する場合には、例えば絶縁性基板1上にポリイミドを塗布して硬化させた後、エッチングによってパッド2の部分のポリイミドを除去するパターニング成形を行えばよい。

【0016】

続いて、図2(C)、図2(F)に示すように、パッド2上にはんだバンプ3を形成する。これで、図1(A)、図1(B)に示した実装基板が完成する。

なお、上記のプロセスとは逆に、まずパッド2上にはんだバンプ3を形成し、続いて絶縁性基板1上にパッド2及びはんだバンプ3を避けるような形でフィルム4を形成してもよい。

【0017】

次に、実装基板への電子部品の実装方法について説明する。まず、図3(A)、図3(C)に示すように、実装基板にフラックス5を塗布する。ただし、この工程は省略できる場合もある。

続いて、半導体チップ又はBGA等の電子部品6を実装基板上に載せて、電子部品6に重りを載せる等して荷重をかけ、リフローによりはんだバンプ3を溶融させてパッド2と電子部品6の電極とをはんだによって接合する(図3(B)、図3(D))。

【0018】

こうして、実装基板への電子部品の実装が完了するが、フィルム4の除去が必要な場合には、図3(B)、図3(D)の工程の後でフィルム4を有機溶剤等で除去する。

以上のように、本実施の形態では、電子部品と絶縁性基板との間にフィルムを挟むことにより、リフロー時のフラックス不足を解消することができ、また電子部品と絶縁性基板との間のスタンドオフ高さを確保することができ、電子部品に荷重をかけながらリフローを行うことができるので、はんだぬれ不良を防止することができ、電子部品と基板との位置ずれを防止することができる。また、本実施の形態では、フィルムによって隣接バンプ同士を完全に隔離することができるので、はんだショートを防止することができる。また、本実施の形態では、リフロー後のスタンドオフ高さもフィルムの厚みによって制御することができる。さらに、本実施の形態では、溶解性のフィルムを用いた場合には、電子部品の実装後に溶解によりフィルムを取り除くことができる。

【産業上の利用可能性】

【0019】

本発明は、半導体チップやBGA等の電子部品の実装に適用することができる。

【図面の簡単な説明】

【0020】

【図1】本発明の実施の形態に係る実装基板の平面図及び断面図である。

【図2】図1の実装基板の作製方法と実装基板への電子部品の実装方法を示す平面図及び断面図である。

【図3】図1の実装基板の作製方法と実装基板への電子部品の実装方法を示す平面図及び断面図である。

【図4】半導体チップ又はBGAを基板上に実装する従来の実装方法を示す断面図である。

【図5】従来の他の実装方法を示す集積回路の断面図である。

【図6】従来の他の実装方法を示す集積回路の断面図である。

【符号の説明】

【0021】

1…絶縁性基板、2…パッド、3…はんだバンプ、4…フィルム、5…フラックス、6…電子部品。

【特許請求の範囲】

【請求項1】

絶縁性基板と、

この絶縁性基板上に形成されたパッドと、

このパッド上に形成されたはんだバンプと、

前記絶縁性基板上に、前記パッド及びはんだバンプを避けるように形成された耐熱性及び電気絶縁性を有するフィルムとを備えることを特徴とする電子部品の実装基板。

【請求項2】

請求項1記載の電子部品の実装基板において、

前記フィルムは、可溶性フィルムであることを特徴とする電子部品の実装基板。

【請求項3】

絶縁性基板上に耐熱性及び電気絶縁性を有するフィルムを、前記絶縁性基板のパッドを避けるように形成し、前記パッド上にはんだバンプを形成して電子部品の実装基板を得る基板作製工程と、

前記実装基板上に電子部品を載せて、この電子部品の電極を前記はんだバンプ上に重ね合わせる搭載工程と、

前記はんだバンプを溶融させて前記パッドと前記電子部品の電極とをはんだによって接合するリフロー工程とを有することを特徴とする電子部品の実装方法。

【請求項4】

絶縁性基板のパッド上にはんだバンプを形成し、前記絶縁性基板上に耐熱性及び電気絶縁性を有するフィルムを、前記パッド及びはんだバンプを避けるように形成して電子部品の実装基板を得る基板作製工程と、

前記実装基板上に電子部品を載せて、この電子部品の電極を前記はんだバンプ上に重ね合わせる搭載工程と、

前記はんだバンプを溶融させて前記パッドと前記電子部品の電極とをはんだによって接合するリフロー工程とを有することを特徴とする電子部品の実装方法。

【請求項5】

請求項3又は4記載の電子部品の実装方法において、

前記フィルムは、可溶性フィルムであり、

前記リフロー工程の後に、前記フィルムを溶剤で除去する除去工程を有することを特徴とする電子部品の実装方法。

【請求項1】

絶縁性基板と、

この絶縁性基板上に形成されたパッドと、

このパッド上に形成されたはんだバンプと、

前記絶縁性基板上に、前記パッド及びはんだバンプを避けるように形成された耐熱性及び電気絶縁性を有するフィルムとを備えることを特徴とする電子部品の実装基板。

【請求項2】

請求項1記載の電子部品の実装基板において、

前記フィルムは、可溶性フィルムであることを特徴とする電子部品の実装基板。

【請求項3】

絶縁性基板上に耐熱性及び電気絶縁性を有するフィルムを、前記絶縁性基板のパッドを避けるように形成し、前記パッド上にはんだバンプを形成して電子部品の実装基板を得る基板作製工程と、

前記実装基板上に電子部品を載せて、この電子部品の電極を前記はんだバンプ上に重ね合わせる搭載工程と、

前記はんだバンプを溶融させて前記パッドと前記電子部品の電極とをはんだによって接合するリフロー工程とを有することを特徴とする電子部品の実装方法。

【請求項4】

絶縁性基板のパッド上にはんだバンプを形成し、前記絶縁性基板上に耐熱性及び電気絶縁性を有するフィルムを、前記パッド及びはんだバンプを避けるように形成して電子部品の実装基板を得る基板作製工程と、

前記実装基板上に電子部品を載せて、この電子部品の電極を前記はんだバンプ上に重ね合わせる搭載工程と、

前記はんだバンプを溶融させて前記パッドと前記電子部品の電極とをはんだによって接合するリフロー工程とを有することを特徴とする電子部品の実装方法。

【請求項5】

請求項3又は4記載の電子部品の実装方法において、

前記フィルムは、可溶性フィルムであり、

前記リフロー工程の後に、前記フィルムを溶剤で除去する除去工程を有することを特徴とする電子部品の実装方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2008−218552(P2008−218552A)

【公開日】平成20年9月18日(2008.9.18)

【国際特許分類】

【出願番号】特願2007−51267(P2007−51267)

【出願日】平成19年3月1日(2007.3.1)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

【公開日】平成20年9月18日(2008.9.18)

【国際特許分類】

【出願日】平成19年3月1日(2007.3.1)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

[ Back to top ]