電子部品の製造方法

【課題】 マザー基板から各電子部品への切断工程を不要とし、生産性の向上をはかった電子部品の製造方法に関する。

【解決手段】 本発明の電子部品の製造方法は、焼成により消失する消失層2を準備する消失層準備工程と、消失層上に、電子部品を形成するための、未焼成チップ7を、間隔をあけて複数個形成する未焼成チップ形成工程と、消失層上に形成された複数個の未焼成チップ7を、消失層2とともに所定のプロファイルで焼成し、消失層2を消失させるとともに、複数個の分離した焼成済チップ8を得る焼成工程とを有するようにした。

【解決手段】 本発明の電子部品の製造方法は、焼成により消失する消失層2を準備する消失層準備工程と、消失層上に、電子部品を形成するための、未焼成チップ7を、間隔をあけて複数個形成する未焼成チップ形成工程と、消失層上に形成された複数個の未焼成チップ7を、消失層2とともに所定のプロファイルで焼成し、消失層2を消失させるとともに、複数個の分離した焼成済チップ8を得る焼成工程とを有するようにした。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は電子部品の製造方法に関し、さらに詳しくは、各電子部品への切断工程を不要とし、生産性の向上をはかった電子部品の製造方法に関する。

【背景技術】

【0002】

従来から、大量生産に適した電子部品の製造方法として、たとえば、次の方法が知られている。

【0003】

まず、多数個の電子部品を一括して製造するための、大きなセラミックのマザーグリーンシートを準備する。マザーグリーンシートには、表面に各電子部品の内部電極となる導電パターンが形成されたもの、厚み方向に貫通して表裏間の導通をとるための導電スルーホールが形成されたもの、導電パターンと導電スルーホールの両方が形成されたもの、導電パターンと導電スルーホールのいずれも形成されていないものなどを、必要に応じて、複数の種類、準備する。

【0004】

次に、マザーグリーンシートを、所定の順番に、所定の枚数積層し、加圧して密着させ、マザー未焼成基板を形成する。

【0005】

次に、マザー未焼成基板を、各電子部品用の未焼成チップに切断する。この切断工程には、回転ブレードや昇降ブレードなどの各種ブレードを用いる。なお、多い場合には、1枚のマザー未焼成基板から、数千個の未焼成チップをカットする場合もある。

【0006】

次に、切断された多数個の未焼成チップを一括して焼成し、焼成済チップを形成する。

【0007】

次に、複数の焼成済チップを一括してバレル装置に投入し、焼成済チップの表面をバレル研磨する。これは、切断工程の際に、チップに発生した角やバリを取るとともに、内部電極の所定の個所をチップの端面に露出させるためにおこなうものである。

【0008】

最後に、各焼成済チップに、導電ペーストを塗布し、焼付けるなどの方法により外部電極を形成し、積層セラミック型の電子部品を完成させる。

【0009】

この従来の電子部品の製造方法は、一度に多数個の電子部品を製造することができるため、大量生産に適したものである。しかしながら、マザー未焼成基板を各電子部品用の未焼成チップに切断する工程を必要とするため、次のような問題を有していた。すなわち、マザー未焼成基板を構成する各マザーグリーンシート、およびその表面に塗布される内部電極用の導電パターンを形成するための導電ペーストは、有機結合材などを含有しており粘りを有しているため、上記未焼成チップへの切断工程を高速でおこなうことができず、製造時間を短縮する妨げとなっていた。また、未焼成チップへの切断工程に起因して、焼成済チップをバレル研磨しなければならないことも、製造時間を短縮する妨げとなっていた。

【0010】

この問題の解決に取組んだものとして、特許文献1(特開2005‐123508号公報)に開示された電子部品の製造方法がある。以下、特許文献1に開示された電子部品の製造方法について、図12〜14を参照しながら、簡単に説明する。なお、図12〜14は、この電子部品の製造方法において適用される、各工程を示す斜視図である。

【0011】

まず、図12に示すように、複数種類のマザーグリーンシート101a、101bを準備し、所定の順番に、所定の枚数を積層する。

【0012】

準備される各マザーグリーンシート101a、101bは、各電子部品の領域を区画するように、焼成した際に消失する材料から構成された消失部102が、碁盤の目状に形成されている。なお、マザーグリーンシート101aの表面には、内部電極用の導電パターン103が形成されている。一方、マザーグリーンシート101bの表面には、導電パターンは形成されていない。なお、マザーグリーンシートの種類はこれらには限定されず、必要に応じて、種々のものが準備される。たとえば、表裏間の導通をとるための導電スルーホールが厚み方向に貫通して形成されたものや、表面に外部への引出し用の導電パターンが形成されたものなどである。

【0013】

次に、図13に示すように、積層されたマザーグリーンシート101a、101bを加圧して密着させ、マザー未焼成基板104を形成する。

【0014】

次に、マザー未焼成基板104を、所定のプロファイルで焼成する。この結果、各マザーグリーンシート101a、101bの碁盤の目状の消失部102が消失し、図14に示すように、各焼成済チップ105を分離した状態で得ることができる。

【0015】

最後に、各焼成済チップ105に外部電極を、導電ペーストの塗布、焼付けなどの方法により形成し、積層セラミック型の電子部品を完成させる。

【0016】

以上のように、特許文献1に記載された電子部品の製造方法では、各未焼成チップへの切断工程が不要になっている。

【先行技術文献】

【特許文献】

【0017】

【特許文献1】特開2005−123508号公報

【発明の概要】

【発明が解決しようとする課題】

【0018】

上述した、特許文献1に開示された電子部品の製造方法は、各電子部品への切断工程を不要にしたものであるが、各マザーグリーンシート101a、101bに、各電子部品の領域を区画するように、碁盤の目状に消失部102を形成しなければならず、かえって製造工程が複雑で、生産性の低いものになっていた。

【0019】

特許文献1には、たとえば、次の方法でマザーグリーンシートを形成する旨が記載されている。(特許文献1の[0020]〜[0021]欄を参照。)

まず、PETフィルムなどの基材層上に、誘電体などの粉体を含有するセラミックスラリーを塗布し(マザー)グリーンシートを形成する。次に、(マザー)グリーンシートに、レーザー加工法やブレードを用いて、(碁盤の目状の)溝部を設ける。次に、溝部に消失材料を充填して、消失部(消失層)を形成する。最後に、消失部の形成された(マザー)グリーンシートから、基材層を剥離除去する。

【0020】

このように、特許文献1に開示された電子部品の製造方法は、マザーグリーンシートの製造工程が極めて煩雑であり、かえって生産性の低いものになっていた。

【課題を解決するための手段】

【0021】

本発明は、上述した特許文献1に開示された従来技術の有する問題点を解決するためになされたものである。

【0022】

そして、本発明の電子部品の製造方法は、その手段として、焼成により消失する消失層を準備する消失層準備工程と、消失層上に、電子部品を形成するための、未焼成チップを、間隔をあけて複数個形成する未焼成チップ形成工程と、消失層上に形成された複数個の未焼成チップを、消失層とともに所定のプロファイルで焼成し、消失層を消失させるとともに、複数個の分離した焼成済チップを得る焼成工程とを有するようにしたことを特徴とする。

【発明の効果】

【0023】

本発明の電子部品の製造方法によれば、消失層上に形成された複数個の未焼成チップを、消失層とともに焼成し、消失層を消失させることにより、分離した複数個の焼成済チップを得ることができる。したがって、各電子部品への切断工程が不要であり、極めて高い生産性で、電子部品を製造することができる。

【図面の簡単な説明】

【0024】

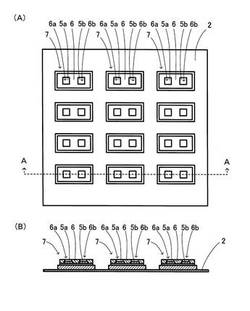

【図1】本発明の第1実施形態にかかる電子部品の製造方法において適用される一つの工程を示し、図1(A)は平面図、図1(B)は図1(A)の鎖線A−A部分の断面図である。

【図2】上記の第1実施形態にかかる電子部品の製造方法において適用される他の一つの工程を示し、図2(A)は平面図、図2(B)は図2(A)の鎖線A−A部分の断面図である。

【図3】上記の第1実施形態にかかる電子部品の製造方法において適用されるさらに他の一つの工程を示し、図3(A)は平面図、図3(B)は図3(A)の鎖線A−A部分の断面図である。

【図4】上記の第1実施形態にかかる電子部品の製造方法において適用されるさらに他の一つの工程を示し、図4(A)は平面図、図4(B)は図4(A)の鎖線A−A部分の断面図である。

【図5】上記の第1実施形態にかかる電子部品の製造方法において適用されるさらに他の一つの工程を示し、図5(A)は平面図、図5(B)は図5(A)の鎖線A−A部分の断面図である。

【図6】上記の第1実施形態にかかる電子部品の製造方法において適用されるさらに他の一つの工程を示し、図6(A)は平面図、図6(B)は図4(A)の鎖線A−A部分の断面図である。

【図7】上記の第1実施形態にかかる電子部品の製造方法において製造された電子部品(負特性サーミスタ)の等価回路図である。

【図8】本発明の第2実施形態にかかる電子部品の製造方法において適用される一つの工程を示す平面図である。

【図9】本発明の第3実施形態にかかる電子部品の製造方法において適用される一つの工程を示す平面図である。

【図10】本発明の第4実施形態にかかる電子部品の製造方法において適用される一つの工程を示す断面図である。

【図11】上記の第4実施形態にかかる電子部品の製造方法において適用される他の一つの工程を示す断面図である。

【図12】従来の電子部品の製造方法において適用される一つの工程を示す斜視図である。

【図13】図12に示した従来の電子部品の製造方法において適用される他の一つの工程を示す斜視図である。

【図14】図12、13に示した従来の電子部品の製造方法において適用されるさらに他の一つの工程を示す斜視図である。

【発明を実施するための形態】

【0025】

以下、図面を参照しながら、本発明を実施するための形態について説明する。

[第1実施形態]

本発明の第1実施形態にかかる電子部品の製造方法を図1〜6に示す。なお、図1〜6はこの電子部品の製造方法において適用される各工程を示し、各図はそれぞれ図(A)と図(B)の2つの図面からなり、図(A)は平面図、図(B)は図(A)の鎖線A−A部分の断面図である。

【0026】

第1実施形態においては、電子部品として、負特性サーミスタを製造する場合を説明する。

【0027】

まず、図1(A)、(B)示すように、PETフィルムなどからなる基材層1上の全面に、消失層2を形成する。本実施形態においては、基材層1の厚みを20μm、消失層2の厚みを20μmとした。消失層2の材料には、たとえば、ポリアクリル樹脂やポリ酢酸ビニル樹脂などのバインダー樹脂を用いることができる。なお、消失層2は、焼成により消失する材質であれば良く、バインダー樹脂に替えて、紙を用いることもできる。一方、基材層1は、消失層2を搬送したり、消失層2上に後で説明する未焼成チップを形成する際に、消失層2に形状強度を付与するためのものである。しかしながら、基材層1は、本発明の必須の構成要素ではなく、消失層2自体が適切な形状強度を有していれば省略することもできる。

【0028】

次に、同じく図1(A)、(B)に示すように、消失層2上に、各負特性サーミスタの下部電極となる下部電極パターン3を、導電ペーストを印刷することにより形成する。第1実施形態においては、縦0.6mm、横1.2mm、厚み30μmの下部電極パターン3を、16個形成した。導電ペーストとしては、たとえば、Ni、Cu、Ag、Pdなどの金属を主成分として含むものを用いることができる。導電ペーストの印刷方法としては、たとえば、スクリーン印刷やグラビア印刷を用いることができる。

【0029】

次に、図2(A)、(B)に示すように、各下部電極パターン3上に、セラミックパターン4を、セラミックペーストを印刷することによって形成する。第1実施形態においては、セラミックパターン4の厚みを10μmとした。セラミックペーストには、たとえば、Ni、Mn、Feなどを主成分として含み、焼成後に負の係数からなる半導体特性を示現し、負特性サーミスタとして使用できるものを用いる。セラミックペーストの印刷方法としては、たとえば、スクリーン印刷を用いることができる。

【0030】

次に、図3(A)、(B)に示すように、各セラミックパターン4上に、各負特性サーミスタの外部引出用の上部電極となる、1対の上部電極パターン5a、5bを、導電ペーストを印刷することにより形成する。第1実施形態においては、上部電極パターン5a、5bの厚みを10μmとした。導電ペーストとしては、たとえば、下部電極パターン3と同様に、Ni、Cu、Ag、Pdなどを主成分として含むものを用いることができる。また、印刷方法としては、スクリーン印刷を用いることができる。

【0031】

次に、図4(A)、(B)に示すように、上部電極パターン5a、5bの形成された各セラミックパターン4上に、保護層用のセラミックパターン6を、セラミックペーストを印刷することにより形成する。セラミックパターン6には、上部電極パターン5a、5bを露出するための開口6a、6bを設ける。ここでのセラミックペーストには、焼成後に、絶縁性を示現するものを用いる。セラミックペーストの印刷方法としては、たとえば、スクリーン印刷を用いることができる。以上により、消失層2上に、16個の未焼成チップ7が形成される。

【0032】

次に、図5(A)、(B)に示すように、消失層2の裏面から、基材層1を剥離除去する。

【0033】

次に、図6(A)、(B)に示すように、消失層2上に形成された16個の未焼成チップ7を、消失層2とともに所定のプロファイルで、脱脂し、焼成し、消失層2を消失させるとともに、16個の分離した焼成済チップ8を得る。焼成済チップ8は、縦0.5mm、横1.0mm、厚み50μmの寸法を有する。なお、焼成済チップ8は、サーミスタ層4’の下側に下部電極3’、上側に1対の上部電極5a’、5b’がそれぞれ形成され、さらにその上に、保護層6’が、開口6a’、6b’から上部電極5a’、5b’を露出させて形成された構造からなる。そして、必要に応じて、開口6a’、6b’から露出した上部電極5a’、5b’の表面にめっきを施すことにより、負特性サーミスタは完成する。図7に、完成した負特性サーミスタの等価回路を示す。完成した負特性サーミスタは、2つの負特性サーミスタ素子(NTH)が、直列に接続された等価回路を有する。

【0034】

以上のように、第1実施形態にかかる電子部品の製造方法によれば、各電子部品への切断工程が不要であるため、生産性が格段に向上している。また、従来必要であった、焼成後のバレル研磨工程も不要であるため、この点からも生産性の向上に寄与している。

【0035】

以上、本発明の第1実施形態にかかる電子部品の製造方法について説明したが、本発明が上記の内容に限定されることはなく、発明の主旨に沿って、種々の変形をなすことができる。たとえば、製造される電子部品は、負特性サーミスタには限定されず、コンデンサ、コイル、抵抗など、種々の電子部品を製造することができる。また、消失層2上に形成される未焼成チップ7の個数も任意であり、もっと多数個を一括して製造することができる。

[第2実施形態]

本発明の第2実施形態にかかる電子部品の製造方法を図8に示す。なお、図8は、この電子部品の製造方法において適用される一つの工程を示す平面図である。

【0036】

上記の第1実施形態においては、消失層2上に16個の未焼成チップ7を規則的に、すなわち未焼成チップ7どうしの間隔が碁盤の目状になるように配置したが、第2実施形態においては、消失層12上に16個の未焼成チップ17を不規則に配置した。

【0037】

本発明において、未焼成チップの配置は、1つの消失層上に形成する未焼成チップの個数、焼成工程における焼成度への影響などを考慮しながら、自由に設計することができる。

【0038】

第2実施形態においては、他の点は、基本的に第1実施形態と同様の製造方法によった。

[第3実施形態]

本発明の第3実施形態にかかる電子部品の製造方法を図9に示す。なお、図9は、この電子部品の製造方法において適用される一つの工程を示す平面図である。

【0039】

第3実施形態にかかる電子部品の製造方法においては、消失層22上に、不規則な形状の未焼成チップ27を形成した。すなわち、消失層22上に、L形状の未焼成チップ27を8個形成した。

【0040】

従来、平面視が四角形以外の電子部品は、マザー基板から各電子部品への切断が困難であり、実用に困難をともなっていたが、本発明の電子部品の製造方法によれば、切断工程が不要であるため、あらゆる形状の電子部品に対応することができる。

【0041】

第3実施形態においては、他の点は、基本的に第1実施形態と同様の製造方法によった。

[第4実施形態]

本発明の第4実施形態にかかる電子部品の製造方法を図10、11に示す。なお、図10、11はこの電子部品の製造方法において適用される各工程を示し、各図はそれぞれ断面図である。

【0042】

上記の第1〜3実施形態においては、未焼成チップを、セラミックペーストと、導電ペーストとを、所定の順番に、所定のパターン形状に印刷して形成したが、第4実施形態においては、複数のセラミックグリーンシートを、所定の順番に積層して形成する。なお、第4実施形態においては、電子部品として、積層コンデンサを製造する場合について説明する。

【0043】

図10に示すように、PETフィルムなどからなる基材層31上の全面に、消失層32を形成し、さらに消失層32上に、各積層コンデンサの一部となるセラミックパターン34を、セラミックペーストを印刷することによって形成する。セラミックペーストは、たとえば、チタン酸バリウムなどを主成分に含み、焼成後に誘電体として機能するものを用いることができる。なお、セラミックパターン34は必須ではなく、省略し、消失層32上に直接、次に説明するセラミックグリーンシートを積層するようにしても良い。

【0044】

次に、同じく図10に示すように、セラミックパターン34上に、セラミックグリーンシート35a、35b、35cを、所定の順番に積層する。なお、セラミックグリーンシート35aの下面には一端(図において左側)に引き出される内部電極パターン36aが形成され、セラミックグリーンシート35bの下面には他端(図において右側)に引き出される内部電極パターン36bが形成されている。セラミックグリーンシート35cの下面には、内部電極パターンは形成されていない。セラミックグリーンシート35a、35b、35cにも、たとえば、チタン酸バリウムなどを主成分に含み、焼成後に誘電体として機能するものを用いることができる。なお、セラミックグリーンシート35a、35b、35cの積層は、いわゆる圧着後剥離による転写積層の方法により積層することができる。

すなわち、PETフィルムなどの基材層(図示せず)上に形成され、所定の寸法にカットされたセラミックグリーンシート35a、35b、35cを、一枚ずつ、順番に、セラミックグリーンシート側を下にして積層し、基材層側から押圧したうえで、基材層を剥離除去し、その上に、次のセラミックグリーンシートを積層する工程を繰り返すことにより積層することができる。

【0045】

次に、図11に示すように、圧着されて一体となった複数の未焼成チップ37が形成された消失層32の裏面から、基材層31を剥離除去したうえで、消失層32上に形成された未焼成チップ37を、消失層32とともに所定のプロファイルで、脱脂し、焼成し、消失層32を消失させ、焼成済チップを得る。焼成済チップは、それぞれ分離した状態で得ることができる。

【0046】

そして、焼成済チップの両端に、慣用されている方法により外部電極を形成して、積層コンデンサが完成する。

【0047】

このように、本発明の電子部品の製造方法は、複数のセラミックグリーンシートを積層して、未焼成チップを形成することによっても実施することができる。

【符号の説明】

【0048】

1、31:基材層

2、12、22、32:消失層

3:下部電極パターン

4:セラミックパターン

5a、5b:上部電極パターン

6:保護層

6a、6b:開口

7、17、27、37:未焼成チップ

8:焼成済チップ

34:セラミックパターン

35a、35b、35c:セラミックグリーンシート

36a、36b:内部電極パターン

【技術分野】

【0001】

本発明は電子部品の製造方法に関し、さらに詳しくは、各電子部品への切断工程を不要とし、生産性の向上をはかった電子部品の製造方法に関する。

【背景技術】

【0002】

従来から、大量生産に適した電子部品の製造方法として、たとえば、次の方法が知られている。

【0003】

まず、多数個の電子部品を一括して製造するための、大きなセラミックのマザーグリーンシートを準備する。マザーグリーンシートには、表面に各電子部品の内部電極となる導電パターンが形成されたもの、厚み方向に貫通して表裏間の導通をとるための導電スルーホールが形成されたもの、導電パターンと導電スルーホールの両方が形成されたもの、導電パターンと導電スルーホールのいずれも形成されていないものなどを、必要に応じて、複数の種類、準備する。

【0004】

次に、マザーグリーンシートを、所定の順番に、所定の枚数積層し、加圧して密着させ、マザー未焼成基板を形成する。

【0005】

次に、マザー未焼成基板を、各電子部品用の未焼成チップに切断する。この切断工程には、回転ブレードや昇降ブレードなどの各種ブレードを用いる。なお、多い場合には、1枚のマザー未焼成基板から、数千個の未焼成チップをカットする場合もある。

【0006】

次に、切断された多数個の未焼成チップを一括して焼成し、焼成済チップを形成する。

【0007】

次に、複数の焼成済チップを一括してバレル装置に投入し、焼成済チップの表面をバレル研磨する。これは、切断工程の際に、チップに発生した角やバリを取るとともに、内部電極の所定の個所をチップの端面に露出させるためにおこなうものである。

【0008】

最後に、各焼成済チップに、導電ペーストを塗布し、焼付けるなどの方法により外部電極を形成し、積層セラミック型の電子部品を完成させる。

【0009】

この従来の電子部品の製造方法は、一度に多数個の電子部品を製造することができるため、大量生産に適したものである。しかしながら、マザー未焼成基板を各電子部品用の未焼成チップに切断する工程を必要とするため、次のような問題を有していた。すなわち、マザー未焼成基板を構成する各マザーグリーンシート、およびその表面に塗布される内部電極用の導電パターンを形成するための導電ペーストは、有機結合材などを含有しており粘りを有しているため、上記未焼成チップへの切断工程を高速でおこなうことができず、製造時間を短縮する妨げとなっていた。また、未焼成チップへの切断工程に起因して、焼成済チップをバレル研磨しなければならないことも、製造時間を短縮する妨げとなっていた。

【0010】

この問題の解決に取組んだものとして、特許文献1(特開2005‐123508号公報)に開示された電子部品の製造方法がある。以下、特許文献1に開示された電子部品の製造方法について、図12〜14を参照しながら、簡単に説明する。なお、図12〜14は、この電子部品の製造方法において適用される、各工程を示す斜視図である。

【0011】

まず、図12に示すように、複数種類のマザーグリーンシート101a、101bを準備し、所定の順番に、所定の枚数を積層する。

【0012】

準備される各マザーグリーンシート101a、101bは、各電子部品の領域を区画するように、焼成した際に消失する材料から構成された消失部102が、碁盤の目状に形成されている。なお、マザーグリーンシート101aの表面には、内部電極用の導電パターン103が形成されている。一方、マザーグリーンシート101bの表面には、導電パターンは形成されていない。なお、マザーグリーンシートの種類はこれらには限定されず、必要に応じて、種々のものが準備される。たとえば、表裏間の導通をとるための導電スルーホールが厚み方向に貫通して形成されたものや、表面に外部への引出し用の導電パターンが形成されたものなどである。

【0013】

次に、図13に示すように、積層されたマザーグリーンシート101a、101bを加圧して密着させ、マザー未焼成基板104を形成する。

【0014】

次に、マザー未焼成基板104を、所定のプロファイルで焼成する。この結果、各マザーグリーンシート101a、101bの碁盤の目状の消失部102が消失し、図14に示すように、各焼成済チップ105を分離した状態で得ることができる。

【0015】

最後に、各焼成済チップ105に外部電極を、導電ペーストの塗布、焼付けなどの方法により形成し、積層セラミック型の電子部品を完成させる。

【0016】

以上のように、特許文献1に記載された電子部品の製造方法では、各未焼成チップへの切断工程が不要になっている。

【先行技術文献】

【特許文献】

【0017】

【特許文献1】特開2005−123508号公報

【発明の概要】

【発明が解決しようとする課題】

【0018】

上述した、特許文献1に開示された電子部品の製造方法は、各電子部品への切断工程を不要にしたものであるが、各マザーグリーンシート101a、101bに、各電子部品の領域を区画するように、碁盤の目状に消失部102を形成しなければならず、かえって製造工程が複雑で、生産性の低いものになっていた。

【0019】

特許文献1には、たとえば、次の方法でマザーグリーンシートを形成する旨が記載されている。(特許文献1の[0020]〜[0021]欄を参照。)

まず、PETフィルムなどの基材層上に、誘電体などの粉体を含有するセラミックスラリーを塗布し(マザー)グリーンシートを形成する。次に、(マザー)グリーンシートに、レーザー加工法やブレードを用いて、(碁盤の目状の)溝部を設ける。次に、溝部に消失材料を充填して、消失部(消失層)を形成する。最後に、消失部の形成された(マザー)グリーンシートから、基材層を剥離除去する。

【0020】

このように、特許文献1に開示された電子部品の製造方法は、マザーグリーンシートの製造工程が極めて煩雑であり、かえって生産性の低いものになっていた。

【課題を解決するための手段】

【0021】

本発明は、上述した特許文献1に開示された従来技術の有する問題点を解決するためになされたものである。

【0022】

そして、本発明の電子部品の製造方法は、その手段として、焼成により消失する消失層を準備する消失層準備工程と、消失層上に、電子部品を形成するための、未焼成チップを、間隔をあけて複数個形成する未焼成チップ形成工程と、消失層上に形成された複数個の未焼成チップを、消失層とともに所定のプロファイルで焼成し、消失層を消失させるとともに、複数個の分離した焼成済チップを得る焼成工程とを有するようにしたことを特徴とする。

【発明の効果】

【0023】

本発明の電子部品の製造方法によれば、消失層上に形成された複数個の未焼成チップを、消失層とともに焼成し、消失層を消失させることにより、分離した複数個の焼成済チップを得ることができる。したがって、各電子部品への切断工程が不要であり、極めて高い生産性で、電子部品を製造することができる。

【図面の簡単な説明】

【0024】

【図1】本発明の第1実施形態にかかる電子部品の製造方法において適用される一つの工程を示し、図1(A)は平面図、図1(B)は図1(A)の鎖線A−A部分の断面図である。

【図2】上記の第1実施形態にかかる電子部品の製造方法において適用される他の一つの工程を示し、図2(A)は平面図、図2(B)は図2(A)の鎖線A−A部分の断面図である。

【図3】上記の第1実施形態にかかる電子部品の製造方法において適用されるさらに他の一つの工程を示し、図3(A)は平面図、図3(B)は図3(A)の鎖線A−A部分の断面図である。

【図4】上記の第1実施形態にかかる電子部品の製造方法において適用されるさらに他の一つの工程を示し、図4(A)は平面図、図4(B)は図4(A)の鎖線A−A部分の断面図である。

【図5】上記の第1実施形態にかかる電子部品の製造方法において適用されるさらに他の一つの工程を示し、図5(A)は平面図、図5(B)は図5(A)の鎖線A−A部分の断面図である。

【図6】上記の第1実施形態にかかる電子部品の製造方法において適用されるさらに他の一つの工程を示し、図6(A)は平面図、図6(B)は図4(A)の鎖線A−A部分の断面図である。

【図7】上記の第1実施形態にかかる電子部品の製造方法において製造された電子部品(負特性サーミスタ)の等価回路図である。

【図8】本発明の第2実施形態にかかる電子部品の製造方法において適用される一つの工程を示す平面図である。

【図9】本発明の第3実施形態にかかる電子部品の製造方法において適用される一つの工程を示す平面図である。

【図10】本発明の第4実施形態にかかる電子部品の製造方法において適用される一つの工程を示す断面図である。

【図11】上記の第4実施形態にかかる電子部品の製造方法において適用される他の一つの工程を示す断面図である。

【図12】従来の電子部品の製造方法において適用される一つの工程を示す斜視図である。

【図13】図12に示した従来の電子部品の製造方法において適用される他の一つの工程を示す斜視図である。

【図14】図12、13に示した従来の電子部品の製造方法において適用されるさらに他の一つの工程を示す斜視図である。

【発明を実施するための形態】

【0025】

以下、図面を参照しながら、本発明を実施するための形態について説明する。

[第1実施形態]

本発明の第1実施形態にかかる電子部品の製造方法を図1〜6に示す。なお、図1〜6はこの電子部品の製造方法において適用される各工程を示し、各図はそれぞれ図(A)と図(B)の2つの図面からなり、図(A)は平面図、図(B)は図(A)の鎖線A−A部分の断面図である。

【0026】

第1実施形態においては、電子部品として、負特性サーミスタを製造する場合を説明する。

【0027】

まず、図1(A)、(B)示すように、PETフィルムなどからなる基材層1上の全面に、消失層2を形成する。本実施形態においては、基材層1の厚みを20μm、消失層2の厚みを20μmとした。消失層2の材料には、たとえば、ポリアクリル樹脂やポリ酢酸ビニル樹脂などのバインダー樹脂を用いることができる。なお、消失層2は、焼成により消失する材質であれば良く、バインダー樹脂に替えて、紙を用いることもできる。一方、基材層1は、消失層2を搬送したり、消失層2上に後で説明する未焼成チップを形成する際に、消失層2に形状強度を付与するためのものである。しかしながら、基材層1は、本発明の必須の構成要素ではなく、消失層2自体が適切な形状強度を有していれば省略することもできる。

【0028】

次に、同じく図1(A)、(B)に示すように、消失層2上に、各負特性サーミスタの下部電極となる下部電極パターン3を、導電ペーストを印刷することにより形成する。第1実施形態においては、縦0.6mm、横1.2mm、厚み30μmの下部電極パターン3を、16個形成した。導電ペーストとしては、たとえば、Ni、Cu、Ag、Pdなどの金属を主成分として含むものを用いることができる。導電ペーストの印刷方法としては、たとえば、スクリーン印刷やグラビア印刷を用いることができる。

【0029】

次に、図2(A)、(B)に示すように、各下部電極パターン3上に、セラミックパターン4を、セラミックペーストを印刷することによって形成する。第1実施形態においては、セラミックパターン4の厚みを10μmとした。セラミックペーストには、たとえば、Ni、Mn、Feなどを主成分として含み、焼成後に負の係数からなる半導体特性を示現し、負特性サーミスタとして使用できるものを用いる。セラミックペーストの印刷方法としては、たとえば、スクリーン印刷を用いることができる。

【0030】

次に、図3(A)、(B)に示すように、各セラミックパターン4上に、各負特性サーミスタの外部引出用の上部電極となる、1対の上部電極パターン5a、5bを、導電ペーストを印刷することにより形成する。第1実施形態においては、上部電極パターン5a、5bの厚みを10μmとした。導電ペーストとしては、たとえば、下部電極パターン3と同様に、Ni、Cu、Ag、Pdなどを主成分として含むものを用いることができる。また、印刷方法としては、スクリーン印刷を用いることができる。

【0031】

次に、図4(A)、(B)に示すように、上部電極パターン5a、5bの形成された各セラミックパターン4上に、保護層用のセラミックパターン6を、セラミックペーストを印刷することにより形成する。セラミックパターン6には、上部電極パターン5a、5bを露出するための開口6a、6bを設ける。ここでのセラミックペーストには、焼成後に、絶縁性を示現するものを用いる。セラミックペーストの印刷方法としては、たとえば、スクリーン印刷を用いることができる。以上により、消失層2上に、16個の未焼成チップ7が形成される。

【0032】

次に、図5(A)、(B)に示すように、消失層2の裏面から、基材層1を剥離除去する。

【0033】

次に、図6(A)、(B)に示すように、消失層2上に形成された16個の未焼成チップ7を、消失層2とともに所定のプロファイルで、脱脂し、焼成し、消失層2を消失させるとともに、16個の分離した焼成済チップ8を得る。焼成済チップ8は、縦0.5mm、横1.0mm、厚み50μmの寸法を有する。なお、焼成済チップ8は、サーミスタ層4’の下側に下部電極3’、上側に1対の上部電極5a’、5b’がそれぞれ形成され、さらにその上に、保護層6’が、開口6a’、6b’から上部電極5a’、5b’を露出させて形成された構造からなる。そして、必要に応じて、開口6a’、6b’から露出した上部電極5a’、5b’の表面にめっきを施すことにより、負特性サーミスタは完成する。図7に、完成した負特性サーミスタの等価回路を示す。完成した負特性サーミスタは、2つの負特性サーミスタ素子(NTH)が、直列に接続された等価回路を有する。

【0034】

以上のように、第1実施形態にかかる電子部品の製造方法によれば、各電子部品への切断工程が不要であるため、生産性が格段に向上している。また、従来必要であった、焼成後のバレル研磨工程も不要であるため、この点からも生産性の向上に寄与している。

【0035】

以上、本発明の第1実施形態にかかる電子部品の製造方法について説明したが、本発明が上記の内容に限定されることはなく、発明の主旨に沿って、種々の変形をなすことができる。たとえば、製造される電子部品は、負特性サーミスタには限定されず、コンデンサ、コイル、抵抗など、種々の電子部品を製造することができる。また、消失層2上に形成される未焼成チップ7の個数も任意であり、もっと多数個を一括して製造することができる。

[第2実施形態]

本発明の第2実施形態にかかる電子部品の製造方法を図8に示す。なお、図8は、この電子部品の製造方法において適用される一つの工程を示す平面図である。

【0036】

上記の第1実施形態においては、消失層2上に16個の未焼成チップ7を規則的に、すなわち未焼成チップ7どうしの間隔が碁盤の目状になるように配置したが、第2実施形態においては、消失層12上に16個の未焼成チップ17を不規則に配置した。

【0037】

本発明において、未焼成チップの配置は、1つの消失層上に形成する未焼成チップの個数、焼成工程における焼成度への影響などを考慮しながら、自由に設計することができる。

【0038】

第2実施形態においては、他の点は、基本的に第1実施形態と同様の製造方法によった。

[第3実施形態]

本発明の第3実施形態にかかる電子部品の製造方法を図9に示す。なお、図9は、この電子部品の製造方法において適用される一つの工程を示す平面図である。

【0039】

第3実施形態にかかる電子部品の製造方法においては、消失層22上に、不規則な形状の未焼成チップ27を形成した。すなわち、消失層22上に、L形状の未焼成チップ27を8個形成した。

【0040】

従来、平面視が四角形以外の電子部品は、マザー基板から各電子部品への切断が困難であり、実用に困難をともなっていたが、本発明の電子部品の製造方法によれば、切断工程が不要であるため、あらゆる形状の電子部品に対応することができる。

【0041】

第3実施形態においては、他の点は、基本的に第1実施形態と同様の製造方法によった。

[第4実施形態]

本発明の第4実施形態にかかる電子部品の製造方法を図10、11に示す。なお、図10、11はこの電子部品の製造方法において適用される各工程を示し、各図はそれぞれ断面図である。

【0042】

上記の第1〜3実施形態においては、未焼成チップを、セラミックペーストと、導電ペーストとを、所定の順番に、所定のパターン形状に印刷して形成したが、第4実施形態においては、複数のセラミックグリーンシートを、所定の順番に積層して形成する。なお、第4実施形態においては、電子部品として、積層コンデンサを製造する場合について説明する。

【0043】

図10に示すように、PETフィルムなどからなる基材層31上の全面に、消失層32を形成し、さらに消失層32上に、各積層コンデンサの一部となるセラミックパターン34を、セラミックペーストを印刷することによって形成する。セラミックペーストは、たとえば、チタン酸バリウムなどを主成分に含み、焼成後に誘電体として機能するものを用いることができる。なお、セラミックパターン34は必須ではなく、省略し、消失層32上に直接、次に説明するセラミックグリーンシートを積層するようにしても良い。

【0044】

次に、同じく図10に示すように、セラミックパターン34上に、セラミックグリーンシート35a、35b、35cを、所定の順番に積層する。なお、セラミックグリーンシート35aの下面には一端(図において左側)に引き出される内部電極パターン36aが形成され、セラミックグリーンシート35bの下面には他端(図において右側)に引き出される内部電極パターン36bが形成されている。セラミックグリーンシート35cの下面には、内部電極パターンは形成されていない。セラミックグリーンシート35a、35b、35cにも、たとえば、チタン酸バリウムなどを主成分に含み、焼成後に誘電体として機能するものを用いることができる。なお、セラミックグリーンシート35a、35b、35cの積層は、いわゆる圧着後剥離による転写積層の方法により積層することができる。

すなわち、PETフィルムなどの基材層(図示せず)上に形成され、所定の寸法にカットされたセラミックグリーンシート35a、35b、35cを、一枚ずつ、順番に、セラミックグリーンシート側を下にして積層し、基材層側から押圧したうえで、基材層を剥離除去し、その上に、次のセラミックグリーンシートを積層する工程を繰り返すことにより積層することができる。

【0045】

次に、図11に示すように、圧着されて一体となった複数の未焼成チップ37が形成された消失層32の裏面から、基材層31を剥離除去したうえで、消失層32上に形成された未焼成チップ37を、消失層32とともに所定のプロファイルで、脱脂し、焼成し、消失層32を消失させ、焼成済チップを得る。焼成済チップは、それぞれ分離した状態で得ることができる。

【0046】

そして、焼成済チップの両端に、慣用されている方法により外部電極を形成して、積層コンデンサが完成する。

【0047】

このように、本発明の電子部品の製造方法は、複数のセラミックグリーンシートを積層して、未焼成チップを形成することによっても実施することができる。

【符号の説明】

【0048】

1、31:基材層

2、12、22、32:消失層

3:下部電極パターン

4:セラミックパターン

5a、5b:上部電極パターン

6:保護層

6a、6b:開口

7、17、27、37:未焼成チップ

8:焼成済チップ

34:セラミックパターン

35a、35b、35c:セラミックグリーンシート

36a、36b:内部電極パターン

【特許請求の範囲】

【請求項1】

焼成により消失する消失層を準備する消失層準備工程と、

前記消失層上に、電子部品を形成するための、未焼成チップを、間隔をあけて複数個形成する未焼成チップ形成工程と、

前記消失層上に形成された複数個の未焼成チップを、前記消失層とともに所定のプロファイルで焼成し、前記消失層を消失させるとともに、複数個の分離した焼成済チップを得る焼成工程と、を有することを特徴とする電子部品の製造方法。

【請求項2】

前記消失層準備工程において、前記消失層は基材層上に形成され、当該基材層は、前記焼成工程の前に前記消失層から剥離除去されることを特徴とする、請求項1に記載された電子部品の製造方法。

【請求項3】

前記未焼成チップ形成工程が、セラミックペーストと、導電ペーストとを、所定の順番に、所定のパターン形状に印刷する工程を含むことを特徴とする、請求項1または2に記載された電子部品の製造方法。

【請求項4】

前記未焼成チップ形成工程が、複数のセラミックグリーンシートを、所定の順番に積層する工程を含むことを特徴とする、請求項1または2に記載された電子部品の製造方法。

【請求項5】

前記複数のセラミックグリーンシートが、表面に導電パターンが形成されたものと、表面に導電パターンが形成されていないものとからなることを特徴とする、請求項4に記載された電子部品の製造方法。

【請求項6】

前記焼成済チップに外部電極を形成する外部電極形成工程をさらに有することを特徴とする、請求項1ないし5のいずれか1項に記載された電子部品の製造方法。

【請求項1】

焼成により消失する消失層を準備する消失層準備工程と、

前記消失層上に、電子部品を形成するための、未焼成チップを、間隔をあけて複数個形成する未焼成チップ形成工程と、

前記消失層上に形成された複数個の未焼成チップを、前記消失層とともに所定のプロファイルで焼成し、前記消失層を消失させるとともに、複数個の分離した焼成済チップを得る焼成工程と、を有することを特徴とする電子部品の製造方法。

【請求項2】

前記消失層準備工程において、前記消失層は基材層上に形成され、当該基材層は、前記焼成工程の前に前記消失層から剥離除去されることを特徴とする、請求項1に記載された電子部品の製造方法。

【請求項3】

前記未焼成チップ形成工程が、セラミックペーストと、導電ペーストとを、所定の順番に、所定のパターン形状に印刷する工程を含むことを特徴とする、請求項1または2に記載された電子部品の製造方法。

【請求項4】

前記未焼成チップ形成工程が、複数のセラミックグリーンシートを、所定の順番に積層する工程を含むことを特徴とする、請求項1または2に記載された電子部品の製造方法。

【請求項5】

前記複数のセラミックグリーンシートが、表面に導電パターンが形成されたものと、表面に導電パターンが形成されていないものとからなることを特徴とする、請求項4に記載された電子部品の製造方法。

【請求項6】

前記焼成済チップに外部電極を形成する外部電極形成工程をさらに有することを特徴とする、請求項1ないし5のいずれか1項に記載された電子部品の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2011−151281(P2011−151281A)

【公開日】平成23年8月4日(2011.8.4)

【国際特許分類】

【出願番号】特願2010−12771(P2010−12771)

【出願日】平成22年1月25日(2010.1.25)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成23年8月4日(2011.8.4)

【国際特許分類】

【出願日】平成22年1月25日(2010.1.25)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]