電子部品及びその製造方法、並びに電子機器

【課題】機能素子と基板との間を容易に真空封止が可能で、機能素子に加わる応力を低減させる。

【解決手段】一方の基板40と他方の基板10との間に封止部材30で囲まれた封止空間60が形成され、封止空間60内に少なくとも機能素子50の一部が配置される。封止部材30に封止空間60と連通して設けられた開口部30Aと、封止空間内の環境を維持し、且つ開口部30Aを閉塞する封止薄膜2aとを備える。

【解決手段】一方の基板40と他方の基板10との間に封止部材30で囲まれた封止空間60が形成され、封止空間60内に少なくとも機能素子50の一部が配置される。封止部材30に封止空間60と連通して設けられた開口部30Aと、封止空間内の環境を維持し、且つ開口部30Aを閉塞する封止薄膜2aとを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子部品及びその製造方法、並びに電子機器に関するものである。

【背景技術】

【0002】

近年、半導体素子等の機能素子を、当該機能素子の能動面を基板側に向けて実装した電子部品が種々の用途に用いられている。このような電子部品は、機能素子そのものを封止空間を形成するための基板として用い、当該機能素子の能動面が基板側に向けて配置されることによって、基板と機能素子との間に形成された封止空間内に能動面が位置するようにされている。ところで、このような電子部品においては、電子部品の正常な動作を確保するために、封止空間内の環境を維持するための対策がとられている。

例えば、特許文献1〜特許文献4には、機能素子と基板との間を樹脂や半田によって封止、この樹脂によって封止空間内の環境の維持を試みている。

【特許文献1】特開平11−87406号公報

【特許文献2】特開平11−97584号公報

【特許文献3】特開2000−77458号公報

【特許文献4】特開2003−92382号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、上述したような従来技術には、以下のような問題が存在する。

樹脂や半田によって機能素子と基板との間を封止した場合には、樹脂や半田の熱膨張係数と基板の熱膨張係数との差に起因して、機能素子に応力が加わる場合がある。樹脂や半田を基板に配置する場合には、熱を加えるため、このような製造工程において、機能素子に対して特に応力が加わることとなる。このように機能素子に応力が加わった場合には、能動面にも応力が加わることとなり、機能素子の特性が変化し、電子部品が正常に動作しない恐れが生じる。

近年は、弾性表面波素子を備える機能素子を用いた電子部品が使用されており、このような弾性表面波素子を備える機能素子を用いた電子部品においては、特に、機能素子に加わる応力によって誤動作を生じる虞がある。

【0004】

また、上記の技術では、封止空間を真空封止する場合、ろう材等を使用する必要があり、大きな熱が加わる虞があることに加えて、煩雑な構造、プロセスが必要になるという問題が生じる。

【0005】

本発明は、以上のような点を考慮してなされたもので、機能素子と基板との間を容易に真空封止が可能で、機能素子に加わる応力を低減させる電子部品及びその製造方法、並びにこの電子部品を備える電子機器を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記の目的を達成するために本発明は、以下の構成を採用している。

本発明の電子部品は、一方の基板と他方の基板との間に封止部材で囲まれた封止空間が形成され、該封止空間内に少なくとも機能素子の一部が配置された電子部品であって、前記封止部材に前記封止空間と連通して設けられた開口部と、前記封止空間内の環境を維持し、且つ前記開口部を閉塞する封止薄膜とを備えることを特徴とするものである。

前記封止薄膜としては、略真空下で成膜される構成を好適に採用できる。

【0007】

従って、本発明の電子部品では、封止薄膜が非常に薄い部材であるため、封止薄膜の熱膨張係数と基板の膨張係数とに差がある場合であっても、封止薄膜の熱膨張係数と基板の熱膨張係数との差に起因して機能素子に加わる応力を極力低減させることが可能となる。また、薄膜は、低温プロセスによって形成する技術が確立されているため、製造工程において各部材に熱が加わることを抑止でき、封止薄膜の熱膨張係数と基板の熱膨張係数との差に起因して機能素子に加わる応力をより低減させることが可能となる。

また、本発明の電子部品では、封止薄膜を略真空下で成膜することにより、開口部を介して封止空間を脱気して真空状態としつつ封止することが可能になり、容易に真空封止を実現できる。

【0008】

また、本発明の電子部品においては、前記封止薄膜が、前記一方の基板あるいは前記他方の基板を覆って形成されているという構成を採用することができる。

このような構成を採用することによって、封止薄膜を形成する際に、細かな位置決めを行う必要がなくなるため、容易に封止薄膜を形成することが可能となる。

【0009】

また、本発明では、前記封止薄膜の少なくとも前記開口部を閉塞する領域に積層して成膜された第2薄膜を有することが好ましい。

これにより、本発明では、少なくとも開口部を閉塞する領域を厚膜の封止膜で覆うことができ、機械的な強度を向上させて信頼性を上げることが可能になる。

【0010】

また、本発明の電子部品においては、上記封止薄膜が、金属薄膜であるという構成を採用することができる。

具体的には、クロム、チタン、銅、アルミニウム及びチタンタングステンのいずれかの材料からなる金属薄膜を用いることができる。

【0011】

また、本発明の電子部品においては、上記封止薄膜が、無機薄膜であるという構成を採用することもできる。

具体的には、酸化シリコン、窒化シリコン、アルミナ及びポリシラザンのいずれかの材料からなる無機薄膜を用いることができる。

【0012】

また、樹脂は、その性質上、内部に水分を取り込んでしまう。このため、外部の水蒸気(ガス)が一旦樹脂に吸収され、その後、外気温の上昇等によって、樹脂の内部に取り込まれた水分が蒸発して封止空間内の環境を壊す恐れがある。すなわち、樹脂は、結果として水蒸気を透過する可能性がある。この点、封止薄膜として金属薄膜や無機薄膜を用いた場合には、内部に水分が取り込まれる可能性が低いため、電子部品の誤動作をより抑止することが可能となる。

【0013】

しかしながら、本発明は、封止薄膜が樹脂によって形成されていることを除くものではなく、樹脂によって封止薄膜を形成した場合であっても、機能素子に加わる応力を低減させることは可能である。

なお、封止薄膜を樹脂によって形成する場合には、他の部材の少なくとも転移温度以下で形成可能な樹脂を用いることが好ましい。これによって、他の部材の特性を変化させることなく、封止薄膜を形成することが可能となる。

具体的には、高密度ポリエチレン、塩化ビニリデン、ポリビニルアルコール、ナイロン及びエチレンビニルアルコールのいずれかの材料からなる樹脂を用いることができる。

【0014】

さらに、本発明の電子部品においては、前記封止薄膜が、有機薄膜と無機薄膜の積層体であるという構成を採用することもできる。

【0015】

そして、本発明の電子機器は、本発明の電子部品を備えることを特徴とする。

本発明の電子部品によれば、機能素子に加わる応力を低減させることが可能となるため、このような本発明の電子部品を備える本発明の電子機器は、信頼性に優れたものとなる。

【0016】

次に、本発明の電子部品の製造方法は、一方の基板と他方の基板との間に封止部材で囲まれた封止空間が形成され、該封止空間内に少なくとも機能素子の一部が配置された電子部品の製造方法であって、前記封止空間と連通する開口部を有する前記封止部材を設ける工程と、前記封止空間内の環境を維持し、且つ前記開口部を閉塞する封止薄膜を成膜する工程とを有することを特徴とする。

【0017】

従って、本発明では、封止薄膜が非常に薄い部材であるため、封止薄膜の熱膨張係数と基板の膨張係数とに差がある場合であっても、封止薄膜の熱膨張係数と基板の熱膨張係数との差に起因して機能素子に加わる応力を極力低減させることが可能となる。また、薄膜は、低温プロセスによって形成する技術が確立されているため、製造工程において各部材に熱が加わることを抑止でき、封止薄膜の熱膨張係数と基板の熱膨張係数との差に起因して機能素子に加わる応力をより低減させることが可能となる。

また、本発明では、封止薄膜を略真空下で成膜することにより、開口部を介して封止空間を脱気して真空状態としつつ封止することが可能になり、容易に真空封止を実現できる。

【0018】

また、本発明の電子部品の製造方法は、前記封止薄膜の少なくとも前記開口部を閉塞する領域に第2薄膜を積層して成膜する工程を有することを特徴とする。

これにより、本発明では、少なくとも開口部を閉塞する領域を厚膜の封止膜で覆うことができ、機械的な強度を向上させて信頼性を上げることが可能になる。

【発明を実施するための最良の形態】

【0019】

以下、図面を参照して、本発明に係る電子部品及びその製造方法、並びに電子機器の一実施形態について説明する。なお、ここでは、1枚のウエハ上に複数の電子部品を形成した後に、各電子部品に個片化する場合の例を用いて説明する。

また、以下の図面において、各部材を認識可能な大きさとするために、各部材の縮尺を適宜変更している。

【0020】

(第1実施形態)

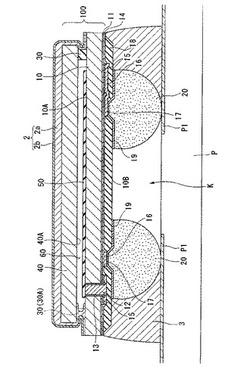

図1は、本第1実施形態の電子部品100の概略構成を示した模式図である。この図に示すように、本実施形態の電子部品100は、基板P上にバンプ20を介して接続されている。

【0021】

図2は、本実施形態の電子部品100をより詳細に表した断面図である。

この図に示すように、電子部品100は、シリコン基板からなる半導体基板10と、半導体基板10の第1面10A側に設けられた弾性表面波素子(機能素子、以下SAW(Surface Acoustic Wave)素子と称する)50と、第1面10Aとその第1面10Aとは反対側の第2面10Bとを貫通する貫通電極12とを備え、封止薄膜2により覆われている。SAW素子50は、圧電薄膜とその圧電薄膜に接する櫛歯電極とを含んで構成されており、半導体基板10の第1面10Aに形成されている。また、不図示ではあるが、半導体基板10の第2面10B上には、例えばトランジスタ、メモリ素子、その他の電子素子を含む集積回路が形成されている。そして、貫通電極12の一端部が、第1面10Aに設けられたSAW素子50と電気的に接続されているとともに、貫通電極12の他端部が、第2面10Bに設けられた上記集積回路と電極15を介して電気的に接続されている。したがって、半導体基板10の第1面10A上に設けられたSAW素子50と、半導体基板10の第2面10B上に設けられた集積回路とが貫通電極12を介して電気的に接続されている。また、貫通電極12と半導体基板10との間には絶縁膜13が設けられており、貫通電極12と半導体基板10とは電気的に絶縁されている。

【0022】

また、本実施形態の電子部品100は、第1面10A上との間でSAW素子50を封止する封止部材40を備えている。封止部材40はガラス基板によって形成されている。なお、封止部材40はシリコン基板であってもよい。封止部材40のうち半導体基板10の第1面10Aと対向する第3面40Aは、第1面10Aとは離間した位置に設けられている。半導体基板10の第1面10Aの周縁部と封止部材40の第3面40Aの周縁部とは、接着剤層(封止部材)30により接着されている。接着剤層30は、例えばポリイミド樹脂等の合成樹脂で形成されている。そして、半導体基板10の第1面10Aと、封止部材40の第3面40Aと、接着剤層30(接着層)とで囲まれた厚さ数μm程度の内部空間60(封止空間)にSAW素子50が配置された構成となっている。

【0023】

図3は、封止部材40が装着されない状態の半導体基板10の平面図である。

この図に示すように、接着剤層30は、半導体基板の周囲に、側縁から所定の隙間をもった矩形枠状に配置されており、短辺の1辺の中央部において開口部30Aが形成されたC字状を有している。

【0024】

半導体基板10の第2面10B上には下地層11が設けられている。下地層11は例えば酸化シリコン(SiO2)等の絶縁性材料によって形成されている。また、下地層11上の複数の所定領域のそれぞれには電極15が設けられ、その電極15が設けられた領域以外の領域には第1絶縁層14が設けられている。また、第1絶縁層14上には複数の第1配線16が設けられており、複数の第1配線16のうち特定の第1配線16は、複数の電極15のうちの一部の電極15と電気的に接続されている。また、複数の電極15のうち特定の電極15は貫通電極12の他端部と電気的に接続されている。また、第1絶縁層14上には、貫通電極12や第1配線16の一部を覆うように第2絶縁層18が設けられている。また、その第2絶縁層18の一部からは第1配線16の一部が露出してランド部17を形成している。ランド部17上には第2配線19が設けられており、そのランド部17(第1配線16)と第2配線19とは電気的に接続されている。

【0025】

封止薄膜2は、内部空間60内の環境を維持するためのものであり、上述のようにSAW素子50が配置された半導体基板10上に封止部材40及び接着剤層30を覆って形成された封止薄膜2aと、さらに封止薄膜2aを覆う封止薄膜2bとから構成されている。

なお、後に詳説するが、この封止薄膜2a、2bは、複数の半導体基板10が形成された第1基板に封止部材40を複数貼り合わせた状態において形成される。このような封止薄膜2a、2bを備えることによって、半導体基板10と封止部材40との間の内部空間60内の環境をより確実に維持することができる。

【0026】

そして、このような封止薄膜2a、2bは、非常に薄い膜であるため、封止薄膜2a、2bの熱膨張係数と半導体基板10の膨張係数とに差がある場合であっても、封止薄膜2a、2bの熱膨張係数と半導体基板10の熱膨張係数との差に起因してSAW素子50に加わる応力を極力低減させることが可能となる。

したがって、本実施形態の電子部品100によれば、半導体基板10と封止部材40との間の内部空間60内の環境をより確実に維持することができるとともに、SAW素子50に加わる応力を低減させることができ、電子部品100の正常な動作をより確保することが可能となる。

【0027】

なお、封止薄膜2a、2bとしては、金属薄膜や無機薄膜を用いることができる。具体的には、金属薄膜としては、クロム(Cr)、チタン(Ti)、銅(Cu)、アルミニウム(Al)及びチタンタングステン(TiW)のいずれかの材料からなる金属薄膜を用いることができる。また、無機薄膜としては、酸化シリコン(SiO2)、窒化シリコン(SiN)、アルミナ(Al3O2)及びポリシラザンのいずれかの材料からなる無機薄膜を用いることができる。

また、封止薄膜2a、2bとして、有機薄膜と無機薄膜との積層体を用いることも可能である。

【0028】

また、SAW素子50に加わる応力を低減させるためのみであれば、封止薄膜2a、2bとして、樹脂からなる薄膜を用いることもできるが、樹脂は、上述のように、結果として水蒸気を透過する可能性があるため、封止薄膜2a、2bとして金属薄膜あるいは無機薄膜を用いることが好ましい。しかしながら、封止薄膜2a、2bとして樹脂からなる薄膜を用いる場合には、他の部材の転移温度以下で形成可能な樹脂を用いることが好ましい。これによって、他の部材の特性を変化させることなく封止薄膜2a、2bの形成が可能となる。具体的には、高密度ポリエチレン、塩化ビニリデン、ポリビニルアルコール(PVA)、ナイロン及びエチレンビニルアルコールのいずれかの材料からなる樹脂を用いて封止薄膜2a、2bを形成することができる。

【0029】

すなわち、本実施形態の電子部品100においては、本発明の一方の基板が封止部材40によって構成され、本発明の他方の基板が半導体基板10によって構成され、本発明の機能素子がSAW素子50によって構成されている。そして、封止部材40と半導体基板10との間に形成された封止空間である内部空間60にSAW素子50が配置されている。

【0030】

そして、第2配線19上には、外部機器との接続端子であるバンプ20が設けられている。バンプ20は半導体基板10の第2面10B上に設けられ、電子部品100は、バンプ20を介して、基板Pに電気的に接続される。

なお、バンプ20の形成材料としては、導電性部材であれば用いることができるが、一般的には、鉛フリー半田や金等を用いる。

また、基板Pは、配線パターンP1を備えている。そして、この配線パターンP1と電子部品100とがバンプ20を介して電気的に接続されている。なお、基板Pとしては、樹脂に配線パターンが形成されたプリント配線基板、配線パターンが形成されたシリコン基板あるいは配線パターンが形成されたガラス基板等を用いることができる。

【0031】

封止樹脂3は、電子部品100と基板Pとの間の空間Kを囲うようにバンプ20の外側に配置形成されている。この封止樹脂3によって、空間Kに外部からのガスが侵入することを簡易的に防止することができる。

なお、封止樹脂3としては、周知の封止用の樹脂を用いることができ、例えば、エポキシ系樹脂やポリイミド系樹脂等を用いることができる。

【0032】

次に、上述のように構成された本実施形態の電子部品100の製造方法について説明する。なお、以下に説明するように、電子部品100は、同一のシリコン基板110(図4参照)に複数形成されるが、説明の便宜上、以下の図面においては、単一の電子部品100を製造しているように図示する場合がある。

【0033】

まず、図4に示すような複数の半導体基板10を備えるシリコン基板110を用意する。そして、図5に示すように各半導体基板10の第2面10B上に下地層11が形成され、その下地層11上に電極15が形成される。ここで、半導体基板10の第2面10B上には、例えばトランジスタ、メモリ素子、その他の電子素子を含む集積回路(不図示)が形成されている。下地層11は絶縁層であって、シリコン(Si)の酸化膜(SiO2)によって形成されている。電極15は、上記集積回路と電気的に接続されており、チタン(Ti)、窒化チタン(TiN)、アルミニウム(Al)、銅(Cu)等によって形成されている。そして、下地層11及び電極15を覆うように、第1絶縁層14が設けられる。

第1絶縁層14は、ポリイミド樹脂、シリコン変性ポリイミド樹脂、エポキシ樹脂、シリコン変性エポキシ樹脂、アクリル樹脂、フェノール樹脂、ベンゾシクロブテン(BCB)、ポリベンゾオキサゾール(PBO)等で形成することができる。あるいは、第1絶縁層14は、酸化シリコン(SiO2)、窒化シリコン(SiN)等、絶縁性があれば他のもので形成されてもよい。

【0034】

次に、スピンコート法等によりフォトレジスト(不図示)が第1絶縁層14上の全面に塗布される。そして、所定のパターンが形成されたマスクを用いて露光処理が行われた後、現像処理が行われる。これによって、フォトレジストは所定形状にパターニングされる。

そして、エッチング処理が行われ、図中、右側の電極15を覆う第1絶縁層14の一部が除去されて開口部が形成される。次に、上記開口部を形成した第1絶縁層14上のフォトレジストをマスクとして、ドライエッチングにより、複数の電極15のうち、図中、右側の電極15の一部が開口される。更に、その開口に対応する下地層11、及び半導体基板10を一部がエッチングにより除去される。これによって、図6に示すように、半導体基板10の第2面10B側の一部に孔部12Hが形成される。

【0035】

次に、第1絶縁層14上及び孔部12Hの内壁及び底面に絶縁膜13が形成される。絶縁膜13は、電流リークの発生、酸素及び水分等による半導体基板10の浸食等を防止するために設けられ、PECVD(Plasma Enhanced Chemical Vapor Deposition)を用いて形成した正珪酸四エチル(Tetra Ethyl Ortho Silicate:Si(OC2H5)4:以下、TEOSという)、すなわちPE−TEOS、及び、オゾンCVDを用いて形成したTEOS、すなわちO3−TEOS、又はCVDを用いて形成した酸化シリコン(SiO2)を用いることができる。なお、絶縁膜13は、絶縁性があれば、他の物でも良く、樹脂でもよい。なお、簡単のため、第1絶縁層14上に設けられた絶縁膜13はその図示が省略されている。そして、電極15上に設けられた絶縁膜13及び第1絶縁層14をエッチングにより除去することで、図7に示すような形態となる。

【0036】

次に、電気化学プレーティング(ECP)法を用いて、孔部12Hの内側及び電極15上にめっき処理が施され、その孔部12Hの内側に貫通電極12を形成するための導電性材料が配置される。貫通電極12を形成するための導電性材料としては、例えば銅(Cu)を用いることができ、孔部12Hには銅(Cu)が埋め込まれる。これによって、電極15上に突出した形状の貫通電極12が形成され、図8に示すような形態となる。本実施形態における貫通電極12を形成する工程には、TiN、Cuをスパッタ法で形成(積層)する工程と、Cuをめっき法で形成する工程とが含まれる。なお、TiW、Cuをスパッタ法で形成(積層)する工程と、Cuをめっき法で形成する工程とが含まれたものであってもよい。なお、貫通電極12の形成方法としては、上述した方法に限らず、導電ペースト、溶融金属、金属ワイヤ等を埋め込んでもよい。

【0037】

次に、図9に示すように、第1絶縁層14上に複数の第1配線16が形成される。複数の第1配線16のうち、一部の第1配線16は、図中、左側の電極15に電気的に接続されるように形成される。第1配線16は、銅(Cu)、クロム(Cr)、チタン(Ti)、ニッケル(Ni)、チタンタングステン(TiW)、金(Au)、銀(Ag)、アルミニウム(Al)、ニッケルバナジウム(NiV)、タングステン(W)、窒化チタン(TiN)、Pb(鉛)のうち少なくとも1つを含む材料で形成される。また、これらの材料のうち少なくとも2つの材料を積層することで第1配線を形成してもよい。本実施形態における第1配線16を形成する工程には、TiW、Cu、TiWの順にスパッタ法により形成する工程が含まれる。なお、TiW、Cuの順にスパッタ法により形成する工程と、Cuをめっき法で形成する工程とが含まれたものであってもよい。

【0038】

次に、図10に示すように、貫通電極12、第1配線16、及び第1絶縁層14を覆うように、第2絶縁層18が設けられる。第2絶縁層18は、ポリイミド樹脂、シリコン変性ポリイミド樹脂、エポキシ樹脂、シリコン変性エポキシ樹脂、アクリル樹脂、フェノール樹脂、ベンゾシクロブテン(BCB)、ポリベンゾオキサゾール(PBO)等で形成することができる。あるいは、第2絶縁層18は、酸化シリコン(SiO2)、窒化シリコン(SiN)等で形成されてもよい。なお、第2絶縁層18は、絶縁性があれば他の物でもよい。

【0039】

次に、第2絶縁層18のうち、ランド部17に対応する領域が除去され、第1配線16の一部が露出されてランド部17が形成される。なお、第2絶縁層18のうちランド部17に対応する領域を除去するときには、露光処理及び現像処理を含むフォトリソグラフィ法を用いることができる。そして、ランド部17に接続するように、第2絶縁層18上に第2配線19が形成され、図11に示すような形態が得られる。

【0040】

次いで、紫外光(UV光)の照射により剥離可能な接着剤で、半導体基板10の第2面10B側に不図示のガラス板が貼り付けられる。このガラス板はWSS(Wafer SupportSystem)と呼ばれるものの一部であって、半導体基板10はガラス板に支持される。そして、このガラス板を貼り付けた状態で、半導体基板10の第1面10Aに対して研磨処理、ドライエッチング処理、あるいはウエットエッチング処理等の所定の処理が施される。

これによって、図12に示すように、半導体基板10が薄くされるとともに、貫通電極12の一端部が、第1面10Aより露出する。

【0041】

次に、図13に示すように、半導体基板10の第1面10A側にSAW素子50が形成される。SAW素子50を形成する工程には、圧電薄膜を形成する工程と、圧電薄膜に接するように櫛歯電極を形成する工程と、保護膜を形成する工程とが含まれる。更には、SAW素子50を形成する工程には、プラズマ等をSAW素子50に照射して周波数調整を行う工程が含まれる。圧電薄膜の形成材料としては、は酸化亜鉛(ZnO)、窒化アルミニウム(AlN)、ニオブ酸リチウム(LiNbO3)、タンタル酸リチウム(LiTaO3)、ニオブ酸カリウム(KNbO3)等が挙げられる。櫛歯電極の形成材料としては、アルミニウムを含む金属が挙げられる。保護膜の形成材料としては、酸化シリコン(SiO2)、窒化シリコン(Si3N4)、窒化チタン(TiN)等が挙げられる。そして、形成されるSAW素子50は、第1面10A側に露出した貫通電極12の一端部と電気的に接続される。

【0042】

次に、半導体基板10の第1面10A及び封止部材40の第3面40Aのうち少なくとも一方に、図2に示した接着剤層30を形成するための接着剤が設けられる。接着剤層30としては、例えば感光性のポリイミド接着剤等を使用することができる。この際、接着剤層30には、図3に示した開口部30Aが形成されるが、開口部30Aを除いた位置に接着剤を配設してもよいし、開口部30Aを含めた全周に接着剤を配置した後に、開口部30Aを形成する位置の接着剤を部分的に除去してもよい。

【0043】

そして、その接着剤層30を介して、半導体基板10の第1面10Aと封止部材40の第3面40Aとが対向するように、それら半導体基板10と封止部材40とが接合される。なお、ここでは、図14に示すように、複数の封止部材40を備える封止基板120を用意する。そして、複数の半導体基板10を備えるシリコン基板110と複数の封止部材40を備える封止基板120とを貼り合わせることによって、図15に示すように、半導体基板10と封止部材40とが接合される。

【0044】

次に、封止基板120のみがダイシングされることによって、封止基板120が複数の封止部材40に個片化することによって内部空間60が形成される。そして、図16に示すように、薄膜2a、2bからなる封止薄膜2を封止部材40が配置されたシリコン基板110上に封止部材40を覆って形成する。具体的には、封止薄膜2aを金属薄膜として形成する場合には、蒸着法、スパッタ法、CVD(chemical vapor deposition)法あるいはメッキ法等によって形成することができる。また、封止薄膜2aを無機薄膜として形成する場合には、蒸着法、スパッタ法、CVD法あるいはウェット法(例えば、スピンコート法、ディップ法、スプレー法等)等によって形成することができる。

【0045】

この封止薄膜2aを形成する際には、真空引きによって接着剤層30の開口部30Aから内部空間60を脱気しつつ成膜する。そして、封止薄膜2aの成膜が進行すると、内部空間60が略真空状態になるとともに、シリコン基板110上で封止部材40を覆う封止薄膜2aにより開口部30Aが閉塞される。

【0046】

続いて、封止薄膜2aを覆う封止薄膜2bを積層して成膜する。封止薄膜2aとしては、上記封止薄膜2bと同様の材料・工程で成膜することができる。本実施形態では、メッキにより銅薄膜を厚膜で成膜する。このように、メッキにより銅の封止薄膜を形成する場合には、封止薄膜2aをTiやCrで成膜することが厚膜化を容易に行えるため好ましい。封止薄膜2bを封止薄膜2aに積層して成膜することにより、開口部30Aを閉塞する薄膜の膜厚が増し、機械的な強度が向上する。

【0047】

このような封止薄膜2a、2bを形成する工程は、封止部材40を覆うように封止用の樹脂部材を形成する工程と比較して低温で行うことができる。例えば、封止薄膜2aの材料を溶媒に溶かし、この液体を塗布後、溶媒を蒸発させることによって、室温で封止薄膜2aを形成することができる。このため、封止薄膜2a、2bを形成する工程において、SAW素子50に熱的なダメージが与えられることを防止することができる。また、封止薄膜2a、2bの形成工程において各部材に熱が加わることを抑止でき、封止薄膜2a、2bの熱膨張係数と基板Pの熱膨張係数との差に起因してSAW素子50に加わる応力をより低減させることが可能となる。これよって、例えば、SAW素子50の周波数変動等の特性変化が生じることを防止することが可能となる。

【0048】

次に、再びシリコン基板110がダイシングされることによって、シリコン基板110が半導体基板10に個片化される。そして、以上の工程によって、電子部品100が製造される。

【0049】

続いて、図17に示すように電子部品100を基板Pの配線P1にバンプ20を介して接続する。なお、図17以降の図においては、便宜上、封止薄膜2a、2bを一層の封止薄膜2として図示する。

【0050】

配線P1には、予め電子部品100を設置する領域が形成されており、電子部品100は、配線P1の所定領域にバンプ20を介して接続される。具体的には、上記WSSを構成するガラス板を半導体基板10より剥離した後、半導体基板10の第2面10B側に設けられた第2配線19上あるいは配線P1の所定領域上に、例えば鉛フリー半田からなるバンプ20が搭載され、当該バンプ20を介して電子部品100と配線P1とが接続される。なお、バンプ20を設ける際には、半田ボールを第2配線19上あるいは配線P1の所定領域上に搭載する形態でもよいし、半田ペーストを第2配線19上あるいは配線P1の所定領域上に印刷する形態でもよい。

【0051】

次に、電子部品100と基板Pとの間の空間Kを囲うようにバンプ20の外側に封止樹脂3を形成する。具体的には、ディスペンサー等によって、電子部品100と基板Pとの間の空間Kを囲うようにバンプ20の外側に樹脂を塗布する。ここで、ディスペンサー等から塗布する樹脂の粘性及びチクソ性は、電子部品100と基板Pとの間の空間Kに樹脂が流れ込まないように適切に調整されている。なお、樹脂の粘性及びチクソ性は、樹脂に対する無機材料の含有量や、樹脂の組成比率等を調整することによって調整することができる。そして、ディスペンサー等によって塗布した樹脂が熱硬化性の樹脂である場合には、塗布した樹脂に対して熱量を加えることによって封止樹脂3が形成される。また、ディスペンサー等によって塗布した樹脂が光硬化性の樹脂である場合には、塗布した樹脂に対して光を照射することによって封止樹脂3が形成される。

そして、以上の工程によって、図1及び図2に示すように本実施形態の電子部品100が基板P上に搭載される。

【0052】

以上説明したように、本実施形態の電子部品の製造方法によれば、SAW素子50が配された内部空間6を容易に真空封止することができる。また、本実施形態では、封止用の樹脂部材を形成する工程と比較して低温で封止薄膜2a、2bを形成できるため、上述のように、封止薄膜2の熱膨張係数と基板Pの熱膨張係数との差に起因して機能素子であるSAW素子50に加わる応力をより低減させることが可能となる。したがって、本実施形態の電子部品100の製造方法によれば、より信頼性に優れた電子部品を製造することが可能となる。

また、本実施の形態では、封止薄膜2aの上に封止薄膜2bを積層して成膜しているので、封止膜として機械的な強度を向上させることが可能になり、真空封止に対する信頼性を上げることが可能になる。

【0053】

なお、本実施形態においては、封止部材40を複数備える封止基板120をシリコン基板110に貼り合わせた後にダイシングすることによって、複数の封止部材40に個片化した。しかしながら、本発明は、これに限定されるものではなく、予め封止基板120をダイシングすることによって複数の封止部材40に個片化し、その後、各封止部材40をシリコン基板110に貼り合わせても良い。

【0054】

(第2実施形態)

次に、本発明の第2実施形態について説明する。なお、本第2実施形態の説明において、上記第1実施形態と同様の部分については、その説明を省略あるいは簡略化する。

【0055】

図18は、本第2実施形態の電子部品200の断面図である。この図に示すように、本第2実施形態の電子部品200は、SAW素子50が、半導体基板10の第1面10A上に形成されておらず、その第1面10Aと対向する封止部材40の第3面40A上に、第1面10Aとは離れて設けられている。本実施形態においては、半導体基板10とは別の部材にSAWを設けることにより、半導体基板10に掛かる熱応力、膜応力の影響を受けにくいため、良好な特性を得ることができる。この場合、封止部材40は、シリコン基板、水晶基板、シリコン及びダイヤを含む基板によって構成されている。そして、封止部材40の第3面40A上に予めSAW素子50を形成しておき、その後、半導体基板10の第1面10Aより突出するようにして設けられた貫通電極12の一端部と、封止部材40の第3面40A上に形成されたSAW素子50の端子51とが電気的に接続されるように、半導体基板10と封止部材40とが接着剤層30を介して接合される。貫通電極12の一端部及び端子51は、金属接続しやすいように、金などの表面処理、あるいはロウ材を表面に設けることが好ましい。あるいは、貫通電極12の一端部と端子51とは、接着剤層30の収縮による圧接でもよい。

この構成の電子部品200においても、封止薄膜2(2a、2b)は略真空下で成膜されるため、内部空間60を容易に真空封止することが可能になり、またSAW素子50に加わる応力をより低減させることが可能となる。

【0056】

(第3実施形態)

次に、本発明の第3実施形態について説明する。なお、本第3実施形態の説明においても、上記第1実施形態と同様の部分については、その説明を省略あるいは簡略化する。

【0057】

図19は、本第3実施形態の電子部品300の断面図である。この図に示すように、本第3実施形態の電子部品300においては、半導体基板10の第1面10Aと封止部材40との間に設けられた第2基板80に、SAW素子50が設けられている。本実施形態においても、半導体基板10とは別の部材にSAWを設けることにより、上記第2実施形態と同様に、半導体基板10に掛かる熱応力、膜応力の影響を受けにくいため、良好な特性を得ることができる。SAW素子50は、第2基板80のうち、半導体基板10の第1面10Aに対向する面80Aに設けられる。第2基板80は、シリコン基板、水晶基板、及びシリコンとダイヤとを含む基板によって構成されている。

【0058】

そして、半導体基板10の第1面10Aより突出するようにして設けられた貫通電極12の一端部と、第2基板80の面80A上に形成されたSAW素子50の端子51とが電気的に接続される。本実施形態においても、貫通電極12の一端部及び端子51は、金属接続しやすいように、金などの表面処理、あるいはロウ材を表面に設けることが好ましい。あるいは、貫通電極12の一端部と端子51とは、接着剤層30の収縮による圧接でもよい。その後、半導体基板10と封止部材40とが接着剤層30を介して接合され、半導体基板10と封止部材40と接着剤層30とで囲まれた内部空間60に、SAW素子50を有する第2基板80が配置される。

本実施形態においても、封止薄膜2(2a、2b)は略真空下で成膜されるため、内部空間60を容易に真空封止することが可能になり、またSAW素子50に加わる応力をより低減させることが可能となる。

【0059】

(第4実施形態)

次に、本発明の第4実施形態として、上記第1〜第3いずれかの実施形態の電子部品100〜300を備える電子機器について説明する。

図20は、本実施形態の電子機器の一例を示す図であって、携帯電話500を示す図である。そして、本実施形態の電子機器である携帯電話500は、上記第1〜第4いずれかの実施形態の電子部品100〜300を備えるものであるため、信頼性に優れたものとなる。

【0060】

以上、添付図面を参照しながら本発明に係る好適な実施形態について説明したが、本発明は係る例に限定されないことは言うまでもない。上述した例において示した各構成部材の諸形状や組み合わせ等は一例であって、本発明の主旨から逸脱しない範囲において設計要求等に基づき種々変更可能である。

【0061】

例えば、上記実施形態では、封止薄膜2aの上に封止薄膜2bを積層する構成としたが、これに限定されるものではなく、真空封止を維持できる厚さ、強度で封止薄膜2aを成膜した場合には封止薄膜2bは必ずしも必要ではない。

また、上記実施形態では、封止薄膜2bを封止基板2aと同様に、半導体基板10上に封止部材40及び接着剤層30を覆って形する構成としたが、これに限られず、例えば開口部30Aを閉塞する領域のみに成膜する構成としてもよい。

【0062】

さらに、機能素子としてSAW素子が用いられる構成を例示したが、これに限定されるものではなく、水晶振動子や、ジャイロセンサ等、他の機能素子が用いられる構成であってもよい。

【図面の簡単な説明】

【0063】

【図1】本発明の第1実施形態である電子部品の概略構成を示した模式図である。

【図2】本発明の第1実施形態である電子部品の断面図である。

【図3】封止部材が装着されない状態の半導体基板の平面図である。

【図4】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図5】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図6】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図7】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図8】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図9】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図10】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図11】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図12】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図13】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図14】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図15】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図16】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図17】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図18】本発明の第2実施形態である電子部品の断面図である。

【図19】本発明の第3実施形態である電子部品の断面図である。

【図20】本発明の第4実施形態である電子機器を示す図である。

【符号の説明】

【0064】

P…基板、 2a…封止薄膜、 2b…封止薄膜(第2薄膜)、 10…半導体基板(他方の基板)、 30…接着剤層(封止部材)、 40…封止部材(一方の基板)、 50…弾性表面波素子(機能素子)、 60…内部空間(封止空間)、 100、200、300…電子部品、 500…携帯電話(電子機器)

【技術分野】

【0001】

本発明は、電子部品及びその製造方法、並びに電子機器に関するものである。

【背景技術】

【0002】

近年、半導体素子等の機能素子を、当該機能素子の能動面を基板側に向けて実装した電子部品が種々の用途に用いられている。このような電子部品は、機能素子そのものを封止空間を形成するための基板として用い、当該機能素子の能動面が基板側に向けて配置されることによって、基板と機能素子との間に形成された封止空間内に能動面が位置するようにされている。ところで、このような電子部品においては、電子部品の正常な動作を確保するために、封止空間内の環境を維持するための対策がとられている。

例えば、特許文献1〜特許文献4には、機能素子と基板との間を樹脂や半田によって封止、この樹脂によって封止空間内の環境の維持を試みている。

【特許文献1】特開平11−87406号公報

【特許文献2】特開平11−97584号公報

【特許文献3】特開2000−77458号公報

【特許文献4】特開2003−92382号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、上述したような従来技術には、以下のような問題が存在する。

樹脂や半田によって機能素子と基板との間を封止した場合には、樹脂や半田の熱膨張係数と基板の熱膨張係数との差に起因して、機能素子に応力が加わる場合がある。樹脂や半田を基板に配置する場合には、熱を加えるため、このような製造工程において、機能素子に対して特に応力が加わることとなる。このように機能素子に応力が加わった場合には、能動面にも応力が加わることとなり、機能素子の特性が変化し、電子部品が正常に動作しない恐れが生じる。

近年は、弾性表面波素子を備える機能素子を用いた電子部品が使用されており、このような弾性表面波素子を備える機能素子を用いた電子部品においては、特に、機能素子に加わる応力によって誤動作を生じる虞がある。

【0004】

また、上記の技術では、封止空間を真空封止する場合、ろう材等を使用する必要があり、大きな熱が加わる虞があることに加えて、煩雑な構造、プロセスが必要になるという問題が生じる。

【0005】

本発明は、以上のような点を考慮してなされたもので、機能素子と基板との間を容易に真空封止が可能で、機能素子に加わる応力を低減させる電子部品及びその製造方法、並びにこの電子部品を備える電子機器を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記の目的を達成するために本発明は、以下の構成を採用している。

本発明の電子部品は、一方の基板と他方の基板との間に封止部材で囲まれた封止空間が形成され、該封止空間内に少なくとも機能素子の一部が配置された電子部品であって、前記封止部材に前記封止空間と連通して設けられた開口部と、前記封止空間内の環境を維持し、且つ前記開口部を閉塞する封止薄膜とを備えることを特徴とするものである。

前記封止薄膜としては、略真空下で成膜される構成を好適に採用できる。

【0007】

従って、本発明の電子部品では、封止薄膜が非常に薄い部材であるため、封止薄膜の熱膨張係数と基板の膨張係数とに差がある場合であっても、封止薄膜の熱膨張係数と基板の熱膨張係数との差に起因して機能素子に加わる応力を極力低減させることが可能となる。また、薄膜は、低温プロセスによって形成する技術が確立されているため、製造工程において各部材に熱が加わることを抑止でき、封止薄膜の熱膨張係数と基板の熱膨張係数との差に起因して機能素子に加わる応力をより低減させることが可能となる。

また、本発明の電子部品では、封止薄膜を略真空下で成膜することにより、開口部を介して封止空間を脱気して真空状態としつつ封止することが可能になり、容易に真空封止を実現できる。

【0008】

また、本発明の電子部品においては、前記封止薄膜が、前記一方の基板あるいは前記他方の基板を覆って形成されているという構成を採用することができる。

このような構成を採用することによって、封止薄膜を形成する際に、細かな位置決めを行う必要がなくなるため、容易に封止薄膜を形成することが可能となる。

【0009】

また、本発明では、前記封止薄膜の少なくとも前記開口部を閉塞する領域に積層して成膜された第2薄膜を有することが好ましい。

これにより、本発明では、少なくとも開口部を閉塞する領域を厚膜の封止膜で覆うことができ、機械的な強度を向上させて信頼性を上げることが可能になる。

【0010】

また、本発明の電子部品においては、上記封止薄膜が、金属薄膜であるという構成を採用することができる。

具体的には、クロム、チタン、銅、アルミニウム及びチタンタングステンのいずれかの材料からなる金属薄膜を用いることができる。

【0011】

また、本発明の電子部品においては、上記封止薄膜が、無機薄膜であるという構成を採用することもできる。

具体的には、酸化シリコン、窒化シリコン、アルミナ及びポリシラザンのいずれかの材料からなる無機薄膜を用いることができる。

【0012】

また、樹脂は、その性質上、内部に水分を取り込んでしまう。このため、外部の水蒸気(ガス)が一旦樹脂に吸収され、その後、外気温の上昇等によって、樹脂の内部に取り込まれた水分が蒸発して封止空間内の環境を壊す恐れがある。すなわち、樹脂は、結果として水蒸気を透過する可能性がある。この点、封止薄膜として金属薄膜や無機薄膜を用いた場合には、内部に水分が取り込まれる可能性が低いため、電子部品の誤動作をより抑止することが可能となる。

【0013】

しかしながら、本発明は、封止薄膜が樹脂によって形成されていることを除くものではなく、樹脂によって封止薄膜を形成した場合であっても、機能素子に加わる応力を低減させることは可能である。

なお、封止薄膜を樹脂によって形成する場合には、他の部材の少なくとも転移温度以下で形成可能な樹脂を用いることが好ましい。これによって、他の部材の特性を変化させることなく、封止薄膜を形成することが可能となる。

具体的には、高密度ポリエチレン、塩化ビニリデン、ポリビニルアルコール、ナイロン及びエチレンビニルアルコールのいずれかの材料からなる樹脂を用いることができる。

【0014】

さらに、本発明の電子部品においては、前記封止薄膜が、有機薄膜と無機薄膜の積層体であるという構成を採用することもできる。

【0015】

そして、本発明の電子機器は、本発明の電子部品を備えることを特徴とする。

本発明の電子部品によれば、機能素子に加わる応力を低減させることが可能となるため、このような本発明の電子部品を備える本発明の電子機器は、信頼性に優れたものとなる。

【0016】

次に、本発明の電子部品の製造方法は、一方の基板と他方の基板との間に封止部材で囲まれた封止空間が形成され、該封止空間内に少なくとも機能素子の一部が配置された電子部品の製造方法であって、前記封止空間と連通する開口部を有する前記封止部材を設ける工程と、前記封止空間内の環境を維持し、且つ前記開口部を閉塞する封止薄膜を成膜する工程とを有することを特徴とする。

【0017】

従って、本発明では、封止薄膜が非常に薄い部材であるため、封止薄膜の熱膨張係数と基板の膨張係数とに差がある場合であっても、封止薄膜の熱膨張係数と基板の熱膨張係数との差に起因して機能素子に加わる応力を極力低減させることが可能となる。また、薄膜は、低温プロセスによって形成する技術が確立されているため、製造工程において各部材に熱が加わることを抑止でき、封止薄膜の熱膨張係数と基板の熱膨張係数との差に起因して機能素子に加わる応力をより低減させることが可能となる。

また、本発明では、封止薄膜を略真空下で成膜することにより、開口部を介して封止空間を脱気して真空状態としつつ封止することが可能になり、容易に真空封止を実現できる。

【0018】

また、本発明の電子部品の製造方法は、前記封止薄膜の少なくとも前記開口部を閉塞する領域に第2薄膜を積層して成膜する工程を有することを特徴とする。

これにより、本発明では、少なくとも開口部を閉塞する領域を厚膜の封止膜で覆うことができ、機械的な強度を向上させて信頼性を上げることが可能になる。

【発明を実施するための最良の形態】

【0019】

以下、図面を参照して、本発明に係る電子部品及びその製造方法、並びに電子機器の一実施形態について説明する。なお、ここでは、1枚のウエハ上に複数の電子部品を形成した後に、各電子部品に個片化する場合の例を用いて説明する。

また、以下の図面において、各部材を認識可能な大きさとするために、各部材の縮尺を適宜変更している。

【0020】

(第1実施形態)

図1は、本第1実施形態の電子部品100の概略構成を示した模式図である。この図に示すように、本実施形態の電子部品100は、基板P上にバンプ20を介して接続されている。

【0021】

図2は、本実施形態の電子部品100をより詳細に表した断面図である。

この図に示すように、電子部品100は、シリコン基板からなる半導体基板10と、半導体基板10の第1面10A側に設けられた弾性表面波素子(機能素子、以下SAW(Surface Acoustic Wave)素子と称する)50と、第1面10Aとその第1面10Aとは反対側の第2面10Bとを貫通する貫通電極12とを備え、封止薄膜2により覆われている。SAW素子50は、圧電薄膜とその圧電薄膜に接する櫛歯電極とを含んで構成されており、半導体基板10の第1面10Aに形成されている。また、不図示ではあるが、半導体基板10の第2面10B上には、例えばトランジスタ、メモリ素子、その他の電子素子を含む集積回路が形成されている。そして、貫通電極12の一端部が、第1面10Aに設けられたSAW素子50と電気的に接続されているとともに、貫通電極12の他端部が、第2面10Bに設けられた上記集積回路と電極15を介して電気的に接続されている。したがって、半導体基板10の第1面10A上に設けられたSAW素子50と、半導体基板10の第2面10B上に設けられた集積回路とが貫通電極12を介して電気的に接続されている。また、貫通電極12と半導体基板10との間には絶縁膜13が設けられており、貫通電極12と半導体基板10とは電気的に絶縁されている。

【0022】

また、本実施形態の電子部品100は、第1面10A上との間でSAW素子50を封止する封止部材40を備えている。封止部材40はガラス基板によって形成されている。なお、封止部材40はシリコン基板であってもよい。封止部材40のうち半導体基板10の第1面10Aと対向する第3面40Aは、第1面10Aとは離間した位置に設けられている。半導体基板10の第1面10Aの周縁部と封止部材40の第3面40Aの周縁部とは、接着剤層(封止部材)30により接着されている。接着剤層30は、例えばポリイミド樹脂等の合成樹脂で形成されている。そして、半導体基板10の第1面10Aと、封止部材40の第3面40Aと、接着剤層30(接着層)とで囲まれた厚さ数μm程度の内部空間60(封止空間)にSAW素子50が配置された構成となっている。

【0023】

図3は、封止部材40が装着されない状態の半導体基板10の平面図である。

この図に示すように、接着剤層30は、半導体基板の周囲に、側縁から所定の隙間をもった矩形枠状に配置されており、短辺の1辺の中央部において開口部30Aが形成されたC字状を有している。

【0024】

半導体基板10の第2面10B上には下地層11が設けられている。下地層11は例えば酸化シリコン(SiO2)等の絶縁性材料によって形成されている。また、下地層11上の複数の所定領域のそれぞれには電極15が設けられ、その電極15が設けられた領域以外の領域には第1絶縁層14が設けられている。また、第1絶縁層14上には複数の第1配線16が設けられており、複数の第1配線16のうち特定の第1配線16は、複数の電極15のうちの一部の電極15と電気的に接続されている。また、複数の電極15のうち特定の電極15は貫通電極12の他端部と電気的に接続されている。また、第1絶縁層14上には、貫通電極12や第1配線16の一部を覆うように第2絶縁層18が設けられている。また、その第2絶縁層18の一部からは第1配線16の一部が露出してランド部17を形成している。ランド部17上には第2配線19が設けられており、そのランド部17(第1配線16)と第2配線19とは電気的に接続されている。

【0025】

封止薄膜2は、内部空間60内の環境を維持するためのものであり、上述のようにSAW素子50が配置された半導体基板10上に封止部材40及び接着剤層30を覆って形成された封止薄膜2aと、さらに封止薄膜2aを覆う封止薄膜2bとから構成されている。

なお、後に詳説するが、この封止薄膜2a、2bは、複数の半導体基板10が形成された第1基板に封止部材40を複数貼り合わせた状態において形成される。このような封止薄膜2a、2bを備えることによって、半導体基板10と封止部材40との間の内部空間60内の環境をより確実に維持することができる。

【0026】

そして、このような封止薄膜2a、2bは、非常に薄い膜であるため、封止薄膜2a、2bの熱膨張係数と半導体基板10の膨張係数とに差がある場合であっても、封止薄膜2a、2bの熱膨張係数と半導体基板10の熱膨張係数との差に起因してSAW素子50に加わる応力を極力低減させることが可能となる。

したがって、本実施形態の電子部品100によれば、半導体基板10と封止部材40との間の内部空間60内の環境をより確実に維持することができるとともに、SAW素子50に加わる応力を低減させることができ、電子部品100の正常な動作をより確保することが可能となる。

【0027】

なお、封止薄膜2a、2bとしては、金属薄膜や無機薄膜を用いることができる。具体的には、金属薄膜としては、クロム(Cr)、チタン(Ti)、銅(Cu)、アルミニウム(Al)及びチタンタングステン(TiW)のいずれかの材料からなる金属薄膜を用いることができる。また、無機薄膜としては、酸化シリコン(SiO2)、窒化シリコン(SiN)、アルミナ(Al3O2)及びポリシラザンのいずれかの材料からなる無機薄膜を用いることができる。

また、封止薄膜2a、2bとして、有機薄膜と無機薄膜との積層体を用いることも可能である。

【0028】

また、SAW素子50に加わる応力を低減させるためのみであれば、封止薄膜2a、2bとして、樹脂からなる薄膜を用いることもできるが、樹脂は、上述のように、結果として水蒸気を透過する可能性があるため、封止薄膜2a、2bとして金属薄膜あるいは無機薄膜を用いることが好ましい。しかしながら、封止薄膜2a、2bとして樹脂からなる薄膜を用いる場合には、他の部材の転移温度以下で形成可能な樹脂を用いることが好ましい。これによって、他の部材の特性を変化させることなく封止薄膜2a、2bの形成が可能となる。具体的には、高密度ポリエチレン、塩化ビニリデン、ポリビニルアルコール(PVA)、ナイロン及びエチレンビニルアルコールのいずれかの材料からなる樹脂を用いて封止薄膜2a、2bを形成することができる。

【0029】

すなわち、本実施形態の電子部品100においては、本発明の一方の基板が封止部材40によって構成され、本発明の他方の基板が半導体基板10によって構成され、本発明の機能素子がSAW素子50によって構成されている。そして、封止部材40と半導体基板10との間に形成された封止空間である内部空間60にSAW素子50が配置されている。

【0030】

そして、第2配線19上には、外部機器との接続端子であるバンプ20が設けられている。バンプ20は半導体基板10の第2面10B上に設けられ、電子部品100は、バンプ20を介して、基板Pに電気的に接続される。

なお、バンプ20の形成材料としては、導電性部材であれば用いることができるが、一般的には、鉛フリー半田や金等を用いる。

また、基板Pは、配線パターンP1を備えている。そして、この配線パターンP1と電子部品100とがバンプ20を介して電気的に接続されている。なお、基板Pとしては、樹脂に配線パターンが形成されたプリント配線基板、配線パターンが形成されたシリコン基板あるいは配線パターンが形成されたガラス基板等を用いることができる。

【0031】

封止樹脂3は、電子部品100と基板Pとの間の空間Kを囲うようにバンプ20の外側に配置形成されている。この封止樹脂3によって、空間Kに外部からのガスが侵入することを簡易的に防止することができる。

なお、封止樹脂3としては、周知の封止用の樹脂を用いることができ、例えば、エポキシ系樹脂やポリイミド系樹脂等を用いることができる。

【0032】

次に、上述のように構成された本実施形態の電子部品100の製造方法について説明する。なお、以下に説明するように、電子部品100は、同一のシリコン基板110(図4参照)に複数形成されるが、説明の便宜上、以下の図面においては、単一の電子部品100を製造しているように図示する場合がある。

【0033】

まず、図4に示すような複数の半導体基板10を備えるシリコン基板110を用意する。そして、図5に示すように各半導体基板10の第2面10B上に下地層11が形成され、その下地層11上に電極15が形成される。ここで、半導体基板10の第2面10B上には、例えばトランジスタ、メモリ素子、その他の電子素子を含む集積回路(不図示)が形成されている。下地層11は絶縁層であって、シリコン(Si)の酸化膜(SiO2)によって形成されている。電極15は、上記集積回路と電気的に接続されており、チタン(Ti)、窒化チタン(TiN)、アルミニウム(Al)、銅(Cu)等によって形成されている。そして、下地層11及び電極15を覆うように、第1絶縁層14が設けられる。

第1絶縁層14は、ポリイミド樹脂、シリコン変性ポリイミド樹脂、エポキシ樹脂、シリコン変性エポキシ樹脂、アクリル樹脂、フェノール樹脂、ベンゾシクロブテン(BCB)、ポリベンゾオキサゾール(PBO)等で形成することができる。あるいは、第1絶縁層14は、酸化シリコン(SiO2)、窒化シリコン(SiN)等、絶縁性があれば他のもので形成されてもよい。

【0034】

次に、スピンコート法等によりフォトレジスト(不図示)が第1絶縁層14上の全面に塗布される。そして、所定のパターンが形成されたマスクを用いて露光処理が行われた後、現像処理が行われる。これによって、フォトレジストは所定形状にパターニングされる。

そして、エッチング処理が行われ、図中、右側の電極15を覆う第1絶縁層14の一部が除去されて開口部が形成される。次に、上記開口部を形成した第1絶縁層14上のフォトレジストをマスクとして、ドライエッチングにより、複数の電極15のうち、図中、右側の電極15の一部が開口される。更に、その開口に対応する下地層11、及び半導体基板10を一部がエッチングにより除去される。これによって、図6に示すように、半導体基板10の第2面10B側の一部に孔部12Hが形成される。

【0035】

次に、第1絶縁層14上及び孔部12Hの内壁及び底面に絶縁膜13が形成される。絶縁膜13は、電流リークの発生、酸素及び水分等による半導体基板10の浸食等を防止するために設けられ、PECVD(Plasma Enhanced Chemical Vapor Deposition)を用いて形成した正珪酸四エチル(Tetra Ethyl Ortho Silicate:Si(OC2H5)4:以下、TEOSという)、すなわちPE−TEOS、及び、オゾンCVDを用いて形成したTEOS、すなわちO3−TEOS、又はCVDを用いて形成した酸化シリコン(SiO2)を用いることができる。なお、絶縁膜13は、絶縁性があれば、他の物でも良く、樹脂でもよい。なお、簡単のため、第1絶縁層14上に設けられた絶縁膜13はその図示が省略されている。そして、電極15上に設けられた絶縁膜13及び第1絶縁層14をエッチングにより除去することで、図7に示すような形態となる。

【0036】

次に、電気化学プレーティング(ECP)法を用いて、孔部12Hの内側及び電極15上にめっき処理が施され、その孔部12Hの内側に貫通電極12を形成するための導電性材料が配置される。貫通電極12を形成するための導電性材料としては、例えば銅(Cu)を用いることができ、孔部12Hには銅(Cu)が埋め込まれる。これによって、電極15上に突出した形状の貫通電極12が形成され、図8に示すような形態となる。本実施形態における貫通電極12を形成する工程には、TiN、Cuをスパッタ法で形成(積層)する工程と、Cuをめっき法で形成する工程とが含まれる。なお、TiW、Cuをスパッタ法で形成(積層)する工程と、Cuをめっき法で形成する工程とが含まれたものであってもよい。なお、貫通電極12の形成方法としては、上述した方法に限らず、導電ペースト、溶融金属、金属ワイヤ等を埋め込んでもよい。

【0037】

次に、図9に示すように、第1絶縁層14上に複数の第1配線16が形成される。複数の第1配線16のうち、一部の第1配線16は、図中、左側の電極15に電気的に接続されるように形成される。第1配線16は、銅(Cu)、クロム(Cr)、チタン(Ti)、ニッケル(Ni)、チタンタングステン(TiW)、金(Au)、銀(Ag)、アルミニウム(Al)、ニッケルバナジウム(NiV)、タングステン(W)、窒化チタン(TiN)、Pb(鉛)のうち少なくとも1つを含む材料で形成される。また、これらの材料のうち少なくとも2つの材料を積層することで第1配線を形成してもよい。本実施形態における第1配線16を形成する工程には、TiW、Cu、TiWの順にスパッタ法により形成する工程が含まれる。なお、TiW、Cuの順にスパッタ法により形成する工程と、Cuをめっき法で形成する工程とが含まれたものであってもよい。

【0038】

次に、図10に示すように、貫通電極12、第1配線16、及び第1絶縁層14を覆うように、第2絶縁層18が設けられる。第2絶縁層18は、ポリイミド樹脂、シリコン変性ポリイミド樹脂、エポキシ樹脂、シリコン変性エポキシ樹脂、アクリル樹脂、フェノール樹脂、ベンゾシクロブテン(BCB)、ポリベンゾオキサゾール(PBO)等で形成することができる。あるいは、第2絶縁層18は、酸化シリコン(SiO2)、窒化シリコン(SiN)等で形成されてもよい。なお、第2絶縁層18は、絶縁性があれば他の物でもよい。

【0039】

次に、第2絶縁層18のうち、ランド部17に対応する領域が除去され、第1配線16の一部が露出されてランド部17が形成される。なお、第2絶縁層18のうちランド部17に対応する領域を除去するときには、露光処理及び現像処理を含むフォトリソグラフィ法を用いることができる。そして、ランド部17に接続するように、第2絶縁層18上に第2配線19が形成され、図11に示すような形態が得られる。

【0040】

次いで、紫外光(UV光)の照射により剥離可能な接着剤で、半導体基板10の第2面10B側に不図示のガラス板が貼り付けられる。このガラス板はWSS(Wafer SupportSystem)と呼ばれるものの一部であって、半導体基板10はガラス板に支持される。そして、このガラス板を貼り付けた状態で、半導体基板10の第1面10Aに対して研磨処理、ドライエッチング処理、あるいはウエットエッチング処理等の所定の処理が施される。

これによって、図12に示すように、半導体基板10が薄くされるとともに、貫通電極12の一端部が、第1面10Aより露出する。

【0041】

次に、図13に示すように、半導体基板10の第1面10A側にSAW素子50が形成される。SAW素子50を形成する工程には、圧電薄膜を形成する工程と、圧電薄膜に接するように櫛歯電極を形成する工程と、保護膜を形成する工程とが含まれる。更には、SAW素子50を形成する工程には、プラズマ等をSAW素子50に照射して周波数調整を行う工程が含まれる。圧電薄膜の形成材料としては、は酸化亜鉛(ZnO)、窒化アルミニウム(AlN)、ニオブ酸リチウム(LiNbO3)、タンタル酸リチウム(LiTaO3)、ニオブ酸カリウム(KNbO3)等が挙げられる。櫛歯電極の形成材料としては、アルミニウムを含む金属が挙げられる。保護膜の形成材料としては、酸化シリコン(SiO2)、窒化シリコン(Si3N4)、窒化チタン(TiN)等が挙げられる。そして、形成されるSAW素子50は、第1面10A側に露出した貫通電極12の一端部と電気的に接続される。

【0042】

次に、半導体基板10の第1面10A及び封止部材40の第3面40Aのうち少なくとも一方に、図2に示した接着剤層30を形成するための接着剤が設けられる。接着剤層30としては、例えば感光性のポリイミド接着剤等を使用することができる。この際、接着剤層30には、図3に示した開口部30Aが形成されるが、開口部30Aを除いた位置に接着剤を配設してもよいし、開口部30Aを含めた全周に接着剤を配置した後に、開口部30Aを形成する位置の接着剤を部分的に除去してもよい。

【0043】

そして、その接着剤層30を介して、半導体基板10の第1面10Aと封止部材40の第3面40Aとが対向するように、それら半導体基板10と封止部材40とが接合される。なお、ここでは、図14に示すように、複数の封止部材40を備える封止基板120を用意する。そして、複数の半導体基板10を備えるシリコン基板110と複数の封止部材40を備える封止基板120とを貼り合わせることによって、図15に示すように、半導体基板10と封止部材40とが接合される。

【0044】

次に、封止基板120のみがダイシングされることによって、封止基板120が複数の封止部材40に個片化することによって内部空間60が形成される。そして、図16に示すように、薄膜2a、2bからなる封止薄膜2を封止部材40が配置されたシリコン基板110上に封止部材40を覆って形成する。具体的には、封止薄膜2aを金属薄膜として形成する場合には、蒸着法、スパッタ法、CVD(chemical vapor deposition)法あるいはメッキ法等によって形成することができる。また、封止薄膜2aを無機薄膜として形成する場合には、蒸着法、スパッタ法、CVD法あるいはウェット法(例えば、スピンコート法、ディップ法、スプレー法等)等によって形成することができる。

【0045】

この封止薄膜2aを形成する際には、真空引きによって接着剤層30の開口部30Aから内部空間60を脱気しつつ成膜する。そして、封止薄膜2aの成膜が進行すると、内部空間60が略真空状態になるとともに、シリコン基板110上で封止部材40を覆う封止薄膜2aにより開口部30Aが閉塞される。

【0046】

続いて、封止薄膜2aを覆う封止薄膜2bを積層して成膜する。封止薄膜2aとしては、上記封止薄膜2bと同様の材料・工程で成膜することができる。本実施形態では、メッキにより銅薄膜を厚膜で成膜する。このように、メッキにより銅の封止薄膜を形成する場合には、封止薄膜2aをTiやCrで成膜することが厚膜化を容易に行えるため好ましい。封止薄膜2bを封止薄膜2aに積層して成膜することにより、開口部30Aを閉塞する薄膜の膜厚が増し、機械的な強度が向上する。

【0047】

このような封止薄膜2a、2bを形成する工程は、封止部材40を覆うように封止用の樹脂部材を形成する工程と比較して低温で行うことができる。例えば、封止薄膜2aの材料を溶媒に溶かし、この液体を塗布後、溶媒を蒸発させることによって、室温で封止薄膜2aを形成することができる。このため、封止薄膜2a、2bを形成する工程において、SAW素子50に熱的なダメージが与えられることを防止することができる。また、封止薄膜2a、2bの形成工程において各部材に熱が加わることを抑止でき、封止薄膜2a、2bの熱膨張係数と基板Pの熱膨張係数との差に起因してSAW素子50に加わる応力をより低減させることが可能となる。これよって、例えば、SAW素子50の周波数変動等の特性変化が生じることを防止することが可能となる。

【0048】

次に、再びシリコン基板110がダイシングされることによって、シリコン基板110が半導体基板10に個片化される。そして、以上の工程によって、電子部品100が製造される。

【0049】

続いて、図17に示すように電子部品100を基板Pの配線P1にバンプ20を介して接続する。なお、図17以降の図においては、便宜上、封止薄膜2a、2bを一層の封止薄膜2として図示する。

【0050】

配線P1には、予め電子部品100を設置する領域が形成されており、電子部品100は、配線P1の所定領域にバンプ20を介して接続される。具体的には、上記WSSを構成するガラス板を半導体基板10より剥離した後、半導体基板10の第2面10B側に設けられた第2配線19上あるいは配線P1の所定領域上に、例えば鉛フリー半田からなるバンプ20が搭載され、当該バンプ20を介して電子部品100と配線P1とが接続される。なお、バンプ20を設ける際には、半田ボールを第2配線19上あるいは配線P1の所定領域上に搭載する形態でもよいし、半田ペーストを第2配線19上あるいは配線P1の所定領域上に印刷する形態でもよい。

【0051】

次に、電子部品100と基板Pとの間の空間Kを囲うようにバンプ20の外側に封止樹脂3を形成する。具体的には、ディスペンサー等によって、電子部品100と基板Pとの間の空間Kを囲うようにバンプ20の外側に樹脂を塗布する。ここで、ディスペンサー等から塗布する樹脂の粘性及びチクソ性は、電子部品100と基板Pとの間の空間Kに樹脂が流れ込まないように適切に調整されている。なお、樹脂の粘性及びチクソ性は、樹脂に対する無機材料の含有量や、樹脂の組成比率等を調整することによって調整することができる。そして、ディスペンサー等によって塗布した樹脂が熱硬化性の樹脂である場合には、塗布した樹脂に対して熱量を加えることによって封止樹脂3が形成される。また、ディスペンサー等によって塗布した樹脂が光硬化性の樹脂である場合には、塗布した樹脂に対して光を照射することによって封止樹脂3が形成される。

そして、以上の工程によって、図1及び図2に示すように本実施形態の電子部品100が基板P上に搭載される。

【0052】

以上説明したように、本実施形態の電子部品の製造方法によれば、SAW素子50が配された内部空間6を容易に真空封止することができる。また、本実施形態では、封止用の樹脂部材を形成する工程と比較して低温で封止薄膜2a、2bを形成できるため、上述のように、封止薄膜2の熱膨張係数と基板Pの熱膨張係数との差に起因して機能素子であるSAW素子50に加わる応力をより低減させることが可能となる。したがって、本実施形態の電子部品100の製造方法によれば、より信頼性に優れた電子部品を製造することが可能となる。

また、本実施の形態では、封止薄膜2aの上に封止薄膜2bを積層して成膜しているので、封止膜として機械的な強度を向上させることが可能になり、真空封止に対する信頼性を上げることが可能になる。

【0053】

なお、本実施形態においては、封止部材40を複数備える封止基板120をシリコン基板110に貼り合わせた後にダイシングすることによって、複数の封止部材40に個片化した。しかしながら、本発明は、これに限定されるものではなく、予め封止基板120をダイシングすることによって複数の封止部材40に個片化し、その後、各封止部材40をシリコン基板110に貼り合わせても良い。

【0054】

(第2実施形態)

次に、本発明の第2実施形態について説明する。なお、本第2実施形態の説明において、上記第1実施形態と同様の部分については、その説明を省略あるいは簡略化する。

【0055】

図18は、本第2実施形態の電子部品200の断面図である。この図に示すように、本第2実施形態の電子部品200は、SAW素子50が、半導体基板10の第1面10A上に形成されておらず、その第1面10Aと対向する封止部材40の第3面40A上に、第1面10Aとは離れて設けられている。本実施形態においては、半導体基板10とは別の部材にSAWを設けることにより、半導体基板10に掛かる熱応力、膜応力の影響を受けにくいため、良好な特性を得ることができる。この場合、封止部材40は、シリコン基板、水晶基板、シリコン及びダイヤを含む基板によって構成されている。そして、封止部材40の第3面40A上に予めSAW素子50を形成しておき、その後、半導体基板10の第1面10Aより突出するようにして設けられた貫通電極12の一端部と、封止部材40の第3面40A上に形成されたSAW素子50の端子51とが電気的に接続されるように、半導体基板10と封止部材40とが接着剤層30を介して接合される。貫通電極12の一端部及び端子51は、金属接続しやすいように、金などの表面処理、あるいはロウ材を表面に設けることが好ましい。あるいは、貫通電極12の一端部と端子51とは、接着剤層30の収縮による圧接でもよい。

この構成の電子部品200においても、封止薄膜2(2a、2b)は略真空下で成膜されるため、内部空間60を容易に真空封止することが可能になり、またSAW素子50に加わる応力をより低減させることが可能となる。

【0056】

(第3実施形態)

次に、本発明の第3実施形態について説明する。なお、本第3実施形態の説明においても、上記第1実施形態と同様の部分については、その説明を省略あるいは簡略化する。

【0057】

図19は、本第3実施形態の電子部品300の断面図である。この図に示すように、本第3実施形態の電子部品300においては、半導体基板10の第1面10Aと封止部材40との間に設けられた第2基板80に、SAW素子50が設けられている。本実施形態においても、半導体基板10とは別の部材にSAWを設けることにより、上記第2実施形態と同様に、半導体基板10に掛かる熱応力、膜応力の影響を受けにくいため、良好な特性を得ることができる。SAW素子50は、第2基板80のうち、半導体基板10の第1面10Aに対向する面80Aに設けられる。第2基板80は、シリコン基板、水晶基板、及びシリコンとダイヤとを含む基板によって構成されている。

【0058】

そして、半導体基板10の第1面10Aより突出するようにして設けられた貫通電極12の一端部と、第2基板80の面80A上に形成されたSAW素子50の端子51とが電気的に接続される。本実施形態においても、貫通電極12の一端部及び端子51は、金属接続しやすいように、金などの表面処理、あるいはロウ材を表面に設けることが好ましい。あるいは、貫通電極12の一端部と端子51とは、接着剤層30の収縮による圧接でもよい。その後、半導体基板10と封止部材40とが接着剤層30を介して接合され、半導体基板10と封止部材40と接着剤層30とで囲まれた内部空間60に、SAW素子50を有する第2基板80が配置される。

本実施形態においても、封止薄膜2(2a、2b)は略真空下で成膜されるため、内部空間60を容易に真空封止することが可能になり、またSAW素子50に加わる応力をより低減させることが可能となる。

【0059】

(第4実施形態)

次に、本発明の第4実施形態として、上記第1〜第3いずれかの実施形態の電子部品100〜300を備える電子機器について説明する。

図20は、本実施形態の電子機器の一例を示す図であって、携帯電話500を示す図である。そして、本実施形態の電子機器である携帯電話500は、上記第1〜第4いずれかの実施形態の電子部品100〜300を備えるものであるため、信頼性に優れたものとなる。

【0060】

以上、添付図面を参照しながら本発明に係る好適な実施形態について説明したが、本発明は係る例に限定されないことは言うまでもない。上述した例において示した各構成部材の諸形状や組み合わせ等は一例であって、本発明の主旨から逸脱しない範囲において設計要求等に基づき種々変更可能である。

【0061】

例えば、上記実施形態では、封止薄膜2aの上に封止薄膜2bを積層する構成としたが、これに限定されるものではなく、真空封止を維持できる厚さ、強度で封止薄膜2aを成膜した場合には封止薄膜2bは必ずしも必要ではない。

また、上記実施形態では、封止薄膜2bを封止基板2aと同様に、半導体基板10上に封止部材40及び接着剤層30を覆って形する構成としたが、これに限られず、例えば開口部30Aを閉塞する領域のみに成膜する構成としてもよい。

【0062】

さらに、機能素子としてSAW素子が用いられる構成を例示したが、これに限定されるものではなく、水晶振動子や、ジャイロセンサ等、他の機能素子が用いられる構成であってもよい。

【図面の簡単な説明】

【0063】

【図1】本発明の第1実施形態である電子部品の概略構成を示した模式図である。

【図2】本発明の第1実施形態である電子部品の断面図である。

【図3】封止部材が装着されない状態の半導体基板の平面図である。

【図4】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図5】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図6】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図7】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図8】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図9】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図10】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図11】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図12】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図13】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図14】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図15】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図16】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図17】本発明の第1実施形態である電子部品の製造方法を説明するための説明図である。

【図18】本発明の第2実施形態である電子部品の断面図である。

【図19】本発明の第3実施形態である電子部品の断面図である。

【図20】本発明の第4実施形態である電子機器を示す図である。

【符号の説明】

【0064】

P…基板、 2a…封止薄膜、 2b…封止薄膜(第2薄膜)、 10…半導体基板(他方の基板)、 30…接着剤層(封止部材)、 40…封止部材(一方の基板)、 50…弾性表面波素子(機能素子)、 60…内部空間(封止空間)、 100、200、300…電子部品、 500…携帯電話(電子機器)

【特許請求の範囲】

【請求項1】

一方の基板と他方の基板との間に封止部材で囲まれた封止空間が形成され、該封止空間内に少なくとも機能素子の一部が配置された電子部品であって、

前記封止部材に前記封止空間と連通して設けられた開口部と、

前記封止空間内の環境を維持し、且つ前記開口部を閉塞する封止薄膜とを備えることを特徴とする電子部品。

【請求項2】

請求項1記載の電子部品において、

前記封止薄膜は、略真空下で成膜されることを特徴とする電子部品。

【請求項3】

請求項1または2記載の電子部品において、

前記封止薄膜は、前記一方の基板と前記他方の基板との少なくとも一方を覆って形成されていることを特徴とする電子部品。

【請求項4】

請求項1から3のいずれかに記載の電子部品において、

前記封止薄膜の少なくとも前記開口部を閉塞する領域に積層して成膜された第2薄膜を有することを特徴とする電子部品。

【請求項5】

請求項1から4のいずれかに記載の電子部品において、

前記封止薄膜は、金属薄膜であることを特徴とする電子部品。

【請求項6】

請求項5記載の電子部品において、

前記金属薄膜は、クロム、チタン、銅、アルミニウム及びチタンタングステンの少なくとも一つの材料からなることを特徴とする電子部品。

【請求項7】

請求項1から4のいずれかに記載の電子部品において、

前記封止薄膜は、無機薄膜であることを特徴とする電子部品。

【請求項8】

請求項7記載の電子部品において、

前記無機薄膜は、酸化シリコン、窒化シリコン、アルミナ及びポリシラザンの少なくとも一つの材料からなることを特徴とする電子部品。

【請求項9】

請求項1から4のいずれかに記載の電子部品において、

前記封止薄膜は、他の部材の少なくとも転移温度以下で形成可能な樹脂であることを特徴とする電子部品。

【請求項10】

請求項9記載の電子部品において、

前記樹脂は、高密度ポリエチレン、塩化ビニリデン、ポリビニルアルコール、ナイロン及びエチレンビニルアルコールの少なくとも一つの材料からなることを特徴とする電子部品。

【請求項11】

請求項1から4のいずれかに記載の電子部品において、

前記封止薄膜は、有機薄膜と無機薄膜との積層体であることを特徴とする電子部品。

【請求項12】

請求項1から11のいずれかに記載の電子部品を備えることを特徴とする電子機器。

【請求項13】

一方の基板と他方の基板との間に封止部材で囲まれた封止空間が形成され、該封止空間内に少なくとも機能素子の一部が配置された電子部品の製造方法であって、

前記封止空間と連通する開口部を有する前記封止部材を設ける工程と、

前記封止空間内の環境を維持し、且つ前記開口部を閉塞する封止薄膜を成膜する工程とを有することを特徴とする電子部品の製造方法。

【請求項14】

請求項13記載の電子部品の製造方法において、

前記封止薄膜を略真空下で成膜することを特徴とする電子部品の製造方法。

【請求項15】

請求項13または14記載の電子部品の製造方法において、

前記封止薄膜の少なくとも前記開口部を閉塞する領域に第2薄膜を積層して成膜する工程を有することを特徴とする電子部品の製造方法。

【請求項1】

一方の基板と他方の基板との間に封止部材で囲まれた封止空間が形成され、該封止空間内に少なくとも機能素子の一部が配置された電子部品であって、

前記封止部材に前記封止空間と連通して設けられた開口部と、

前記封止空間内の環境を維持し、且つ前記開口部を閉塞する封止薄膜とを備えることを特徴とする電子部品。

【請求項2】

請求項1記載の電子部品において、

前記封止薄膜は、略真空下で成膜されることを特徴とする電子部品。

【請求項3】

請求項1または2記載の電子部品において、

前記封止薄膜は、前記一方の基板と前記他方の基板との少なくとも一方を覆って形成されていることを特徴とする電子部品。

【請求項4】

請求項1から3のいずれかに記載の電子部品において、

前記封止薄膜の少なくとも前記開口部を閉塞する領域に積層して成膜された第2薄膜を有することを特徴とする電子部品。

【請求項5】

請求項1から4のいずれかに記載の電子部品において、

前記封止薄膜は、金属薄膜であることを特徴とする電子部品。

【請求項6】

請求項5記載の電子部品において、

前記金属薄膜は、クロム、チタン、銅、アルミニウム及びチタンタングステンの少なくとも一つの材料からなることを特徴とする電子部品。

【請求項7】

請求項1から4のいずれかに記載の電子部品において、

前記封止薄膜は、無機薄膜であることを特徴とする電子部品。

【請求項8】

請求項7記載の電子部品において、

前記無機薄膜は、酸化シリコン、窒化シリコン、アルミナ及びポリシラザンの少なくとも一つの材料からなることを特徴とする電子部品。

【請求項9】

請求項1から4のいずれかに記載の電子部品において、

前記封止薄膜は、他の部材の少なくとも転移温度以下で形成可能な樹脂であることを特徴とする電子部品。

【請求項10】

請求項9記載の電子部品において、

前記樹脂は、高密度ポリエチレン、塩化ビニリデン、ポリビニルアルコール、ナイロン及びエチレンビニルアルコールの少なくとも一つの材料からなることを特徴とする電子部品。

【請求項11】

請求項1から4のいずれかに記載の電子部品において、

前記封止薄膜は、有機薄膜と無機薄膜との積層体であることを特徴とする電子部品。

【請求項12】

請求項1から11のいずれかに記載の電子部品を備えることを特徴とする電子機器。

【請求項13】

一方の基板と他方の基板との間に封止部材で囲まれた封止空間が形成され、該封止空間内に少なくとも機能素子の一部が配置された電子部品の製造方法であって、

前記封止空間と連通する開口部を有する前記封止部材を設ける工程と、

前記封止空間内の環境を維持し、且つ前記開口部を閉塞する封止薄膜を成膜する工程とを有することを特徴とする電子部品の製造方法。

【請求項14】

請求項13記載の電子部品の製造方法において、

前記封止薄膜を略真空下で成膜することを特徴とする電子部品の製造方法。

【請求項15】

請求項13または14記載の電子部品の製造方法において、

前記封止薄膜の少なくとも前記開口部を閉塞する領域に第2薄膜を積層して成膜する工程を有することを特徴とする電子部品の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2007−149816(P2007−149816A)

【公開日】平成19年6月14日(2007.6.14)

【国際特許分類】

【出願番号】特願2005−339972(P2005−339972)

【出願日】平成17年11月25日(2005.11.25)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成19年6月14日(2007.6.14)

【国際特許分類】

【出願日】平成17年11月25日(2005.11.25)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]