電子部品及び基板モジュール

【課題】低ESL化を図ることができると共に、回路基板への実装の際にショートが発生することを抑制できる電子部品及び基板モジュールを提供することである。

【解決手段】積層体11は、コンデンサを形成している第1の容量導体及び第2の容量導体を内蔵している。外部電極12a,12bはそれぞれ、第1の容量導体及び第2の容量導体に引き出し導体を介して接続されている。外部電極13,14は、引き出し導体を介して第1の容量導体に接続されている。外部電極15,16は、引き出し導体を介して第2の容量導体に接続されている。側面S5において、端面S3と外部電極13との間には、外部電極13の電位と異なる電位に保たれる外部電極が設けられていない。側面S5において、端面S4と外部電極15との間には、外部電極15の電位と異なる電位に保たれる外部電極が設けられていない。

【解決手段】積層体11は、コンデンサを形成している第1の容量導体及び第2の容量導体を内蔵している。外部電極12a,12bはそれぞれ、第1の容量導体及び第2の容量導体に引き出し導体を介して接続されている。外部電極13,14は、引き出し導体を介して第1の容量導体に接続されている。外部電極15,16は、引き出し導体を介して第2の容量導体に接続されている。側面S5において、端面S3と外部電極13との間には、外部電極13の電位と異なる電位に保たれる外部電極が設けられていない。側面S5において、端面S4と外部電極15との間には、外部電極15の電位と異なる電位に保たれる外部電極が設けられていない。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子部品及び基板モジュールに関し、より特定的には、コンデンサを内蔵している電子部品及び基板モジュールに関する。

【背景技術】

【0002】

従来の電子部品としては、例えば、特許文献1に記載の積層コンデンサが知られている。図18は、特許文献1に記載の積層コンデンサ500の正面図である。

【0003】

積層コンデンサ500は、積層体502、内部導体504,506、引出電極508,510及び外部電極512,514を備えている。積層体502は、複数の誘電体層が積層されることにより構成されている。図18において、積層体502の下側の面が実装面である。内部導体504,506は、誘電体層と共に積層されており、誘電体層を挟んで互いに対向することにより静電容量を形成している。引出電極508,510はそれぞれ、内部導体504,506に接続されていると共に、実装面に引き出されている。外部電極512,514はそれぞれ、引出電極508,510に接続されている。以上のような積層コンデンサ500では、引出電極508,510間の距離と内部導体504,506から実装面までの距離とを所定の関係に保つことにより、等価直列インダクタンスの低減を図っている。

【0004】

しかしながら、特許文献1に記載の積層コンデンサ500では、外部電極512,514が近接しているので、回路基板への実装時に、外部電極512と外部電極514とがはんだによって接続されてしまうおそれがある。すなわち、積層コンデンサ500では、ショートが発生するおそれがある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2004−140183号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

そこで、本発明の目的は、低ESL化を図ることができると共に、回路基板への実装の際にショートが発生することを抑制できる電子部品及び基板モジュールを提供することである。

【課題を解決するための手段】

【0007】

本発明の一形態に係る電子部品は、複数の誘電体層が積層されてなる直方体状の積層体と、前記誘電体層上に設けられている第1の容量導体と、前記第1の容量導体に接続され、かつ、前記積層体の第1の端面に引き出されている第1の引き出し導体と、前記第1の容量導体に接続され、かつ、前記積層体の第1の側面に引き出されている第3の引き出し導体と、前記誘電体層上に設けられ、かつ、前記第1の容量導体と前記誘電体層を介して対向している第2の容量導体と、前記第2の容量導体に接続され、かつ、前記積層体の第2の端面に引き出されている第2の引き出し導体と、前記第2の容量導体に接続され、かつ、前記第1の側面に引き出されている第4の引き出し導体と、前記第1の端面及び前記第2の端面のそれぞれと前記積層体の底面とに跨って設けられ、かつ、前記第1の引き出し導体及び前記第2の引き出し導体のそれぞれに接続されている第1の外部電極及び第2の外部電極と、前記第1の側面に設けられ、かつ、前記第3の引き出し導体に接続されている第3の外部電極と、前記第1の側面に設けられ、かつ、前記第4の引き出し導体に接続されている第4の外部電極と、を備えており、前記第1の側面において、前記第1の端面と前記第3の外部電極との間には、該第3の外部電極の電位と異なる電位に保たれる外部電極が設けられておらず、前記第1の側面において、前記第2の端面と前記第4の外部電極との間には、該第4の外部電極の電位と異なる電位に保たれる外部電極が設けられていないこと、を特徴とする。

【0008】

本発明の一形態に係る基板モジュールは、第1のランド及び第2のランドを含んでいる回路基板と、前記回路基板に実装される前記電子部品と、を備えており、前記第1の外部電極は、前記第1のランドに接続され、前記第2の外部電極は、前記第2のランドに接続されていること、を特徴とする。

【発明の効果】

【0009】

本発明によれば、低ESL化を図ることができると共に、回路基板への実装の際にショートが発生することを抑制できる。

【図面の簡単な説明】

【0010】

【図1】第1の実施形態に係る電子部品の外観斜視図である。

【図2】図1の電子部品の積層体の分解斜視図である。

【図3】図1の電子部品の内部平面図である。

【図4】図4(a)は、基板モジュールの断面構造図であり、図4(b)は、基板モジュールをz軸方向の正方向側から平面視した図である。

【図5】図4の基板モジュールの等価回路図である。

【図6】比較例に係る電子部品の外観斜視図である。

【図7】比較例に係る電子部品の積層体の分解斜視図である。

【図8】第1のサンプル及び第2のサンプルの伝送特性(S21)を示したグラフである。

【図9】基板モジュールの断面構造図である。

【図10】基板モジュールの断面構造図である。

【図11】第1のサンプルないし第4のサンプルの伝送特性(S21)を示したグラフである。

【図12】第2の実施形態に係る電子部品の積層体の分解斜視図である。

【図13】図12の電子部品の内部平面図である。

【図14】第3の実施形態に係る電子部品の内部平面図である。

【図15】第4の実施形態に係る電子部品の内部平面図である。

【図16】第5の実施形態に係る電子部品の外観斜視図である。

【図17】第6の実施形態に係る電子部品の外観斜視図である。

【図18】特許文献1に記載の積層コンデンサの正面図である。

【発明を実施するための形態】

【0011】

以下に、本発明の実施形態に係る電子部品及び基板モジュールについて図面を参照しながら説明する。

【0012】

(第1の実施形態)

(電子部品の構成)

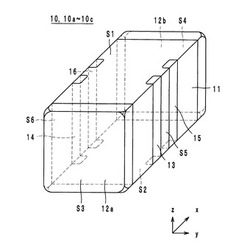

まず、第1の実施形態に係る電子部品の構成について図面を参照しながら説明する。図1は、第1の実施形態に係る電子部品10の外観斜視図である。図2は、図1の電子部品10の積層体11の分解斜視図である。図3は、図1の電子部品の内部平面図である。以下では、積層体11の積層方向をz軸方向と定義する。積層体11をz軸方向から平面視したときに、積層体11の長辺が延在している方向をx軸方向と定義する。積層体11をz軸方向から平面視したときに、積層体11の短辺が延在している方向をy軸方向と定義する。

【0013】

電子部品10は、例えば、カップリングコンデンサとして用いられるチップコンデンサであり、図1ないし図3に示すように、積層体11、外部電極12(12a,12b),13〜16及び内部導体30(30a〜30c),31(31a〜31c)(図1には図示せず)を備えている。

【0014】

積層体11は、直方体状をなしている。ただし、積層体11は、面取りが施されることにより角及び稜線において丸みを帯びた形状をなしている。以下では、積層体11において、z軸方向の正方向側の面を上面S1とし、z軸方向の負方向側の面を下面S2とする。また、x軸方向の負方向側の面を端面S3とし、x軸方向の正方向側の面を端面S4とする。また、y軸方向の正方向側の面を側面S5とし、y軸方向の負方向側の面を側面S6とする。

【0015】

積層体11は、図2に示すように、複数のセラミック層17(17a〜17h)がz軸方向の正方向側から負方向側へとこの順に並ぶように積層されることにより構成されている。セラミック層17は、長方形状をなしており、誘電体セラミックにより作製されている。以下では、セラミック層17のz軸方向の正方向側の主面を表面と称し、セラミック層17のz軸方向の負方向側の主面を裏面と称す。

【0016】

積層体11の上面S1は、z軸方向の最も正方向側に設けられているセラミック層17aの表面により構成されている。積層体11の下面S2は、z軸方向の最も負方向側に設けられているセラミック層17hの裏面により構成されている。また、端面S3は、セラミック層17a〜17hのx軸方向の負方向側の短辺が連なることによって構成されている。端面S4は、セラミック層17a〜17hのx軸方向の正方向側の短辺が連なることによって構成されている。側面S5は、セラミック層17a〜17hのy軸方向の正方向側の長辺が連なることによって構成されている。側面S6は、セラミック層17a〜17hのy軸方向の負方向側の長辺が連なることによって構成されている。

【0017】

内部導体30a〜30cはそれぞれ、図2及び図3に示すように、セラミック層17b,17d,17fの表面上に設けられており、積層体11に内蔵されている。内部導体31a〜31cはそれぞれ、セラミック層17c,17e,17gの表面上に設けられており、積層体11に内蔵されている。すなわち、内部導体30と内部導体31とは、z軸方向において交互に積層されている。

【0018】

内部導体30(30a〜30c)は、容量導体18(18a〜18c)及び引き出し導体20(20a〜20c),22(22a〜22c),23(23a〜23c)を有している。容量導体18は、長方形状をなしており、セラミック層17の外縁に接しないように、セラミック層17の表面上に設けられている。

【0019】

引き出し導体20は、容量導体18に接続され、かつ、積層体11の端面S3に引き出されることにより端面S3から露出している。より詳細には、引き出し導体20は、容量導体18のx軸方向の負方向側の短辺から、x軸方向の負方向側に向かって引き出されている。これにより、引き出し導体20は、セラミック層17のx軸方向の負方向側の短辺に引き出されている。

【0020】

引き出し導体22は、容量導体18に接続され、かつ、積層体11の側面S5に引き出されることにより側面S5から露出している。より詳細には、引き出し導体22は、容量導体18のy軸方向の正方向側の長辺の中点よりx軸方向の負方向側の位置から、y軸方向の正方向側に向かって延在している。これにより、引き出し導体22は、セラミック層17のy軸方向の正方向側の長辺の中点よりx軸方向の負方向側の位置に引き出されている。

【0021】

引き出し導体23は、容量導体18に接続され、かつ、積層体11の側面S6に引き出されることにより側面S6から露出している。より詳細には、引き出し導体23は、容量導体18のy軸方向の負方向側の長辺の中点よりx軸方向の負方向側の位置から、y軸方向の負方向側に向かって延在している。これにより、引き出し導体23は、セラミック層17のy軸方向の負方向側の長辺の中点よりx軸方向の負方向側の位置に引き出されている。

【0022】

内部導体31(31a〜31c)は、容量導体19(19a〜19c)及び引き出し導体21(21a〜21c),24(24a〜24c),25(25a〜25c)を有している。容量導体19は、長方形状をなしており、セラミック層17の外縁に接しないように、セラミック層17の表面上に設けられている。そして、容量導体19は、容量導体18とセラミック層17を介して対向している。これにより、容量導体18,19間には静電容量(すなわち、コンデンサ)が形成されている。

【0023】

引き出し導体21は、容量導体19に接続され、かつ、積層体11の端面S4に引き出されることにより端面S4から露出している。より詳細には、引き出し導体21は、容量導体19のx軸方向の正方向側の短辺から、x軸方向の正方向側に向かって引き出されている。これにより、引き出し導体21は、セラミック層17のx軸方向の正方向側の短辺に引き出されている。

【0024】

引き出し導体24は、容量導体19に接続され、かつ、積層体11の側面S5に引き出されることにより側面S5から露出している。より詳細には、引き出し導体24は、容量導体19のy軸方向の正方向側の長辺の中点よりx軸方向の正方向側の位置から、y軸方向の正方向側に向かって延在している。これにより、引き出し導体24は、セラミック層17のy軸方向の正方向側の長辺の中点よりx軸方向の正方向側の位置に引き出されている。すなわち、引き出し導体24は、z軸方向から平面視したときに、引き出し導体22よりもx軸方向の正方向側に位置している。

【0025】

引き出し導体25は、容量導体19に接続され、かつ、積層体11の側面S6に引き出されることにより側面S6から露出している。より詳細には、引き出し導体25は、容量導体19のy軸方向の負方向側の長辺の中点よりx軸方向の正方向側の位置から、y軸方向の負方向側に向かって延在している。これにより、引き出し導体25は、セラミック層17のy軸方向の負方向側の長辺の中点よりx軸方向の正方向側の位置に引き出されている。すなわち、引き出し導体25は、z軸方向から平面視したときに、引き出し導体23よりもx軸方向の正方向側に位置している。

【0026】

外部電極12a,12bはそれぞれ、端面S3,S4のそれぞれと積層体11の上面S1、下面S2及び側面S5,S6とに跨って設けられ、かつ、引き出し導体20a〜20c,21a〜21cのそれぞれに接続されている。より詳細には、外部電極12aは、引き出し導体20a〜20cが端面S3から露出している部分を覆うように、積層体11の端面S3の全面を覆っている。更に、外部電極12aは、端面S3から上面S1、下面S2及び側面S5,S6に折り返されている。外部電極12bは、引き出し導体21a〜21cが端面S4から露出している部分を覆うように、積層体11の端面S4の全面を覆っている。更に、外部電極12bは、端面S4から上面S1、下面S2及び側面S5,S6に折り返されている。

【0027】

外部電極13,14はそれぞれ、側面S5,S6に設けられ、かつ、引き出し導体22a〜22c,23a〜23cに接続されている。より詳細には、外部電極13は、引き出し導体22a〜22cが側面S5から露出している部分を覆うように、積層体11の側面S5においてz軸方向に延在する帯状に形成されている。更に、外部電極13は、側面S5から上面S1及び下面S2に折り返されている。外部電極14は、引き出し導体23a〜23cが側面S6から露出している部分を覆うように、積層体11の側面S6においてz軸方向に延在する帯状に形成されている。このとき、外部電極14は、外部電極13と対向している。更に、外部電極14は、側面S6から上面S1及び下面S2に折り返されている。

【0028】

外部電極15,16はそれぞれ、側面S5,S6に設けられ、かつ、引き出し導体24a〜24c,25a〜25cに接続されている。より詳細には、外部電極15は、引き出し導体24a〜24cが側面S5から露出している部分を覆うように、積層体11の側面S5においてz軸方向に延在する帯状に形成されている。更に、外部電極15は、側面S5から上面S1及び下面S2に折り返されている。また、外部電極15は、引き出し導体24が引き出し導体22よりもx軸方向の正方向側に位置しているので、外部電極13よりもx軸方向の正方向側に位置している。外部電極16は、引き出し導体25a〜25cが側面S6から露出している部分を覆うように、積層体11の側面S6においてz軸方向に延在する帯状に形成されている。このとき、外部電極16は、外部電極15と対向している。更に、外部電極16は、側面S6から上面S1及び下面S2に折り返されている。また、外部電極16は、引き出し導体25が引き出し導体23よりもx軸方向の正方向側に位置しているので、外部電極14よりもx軸方向の正方向側に位置している。

【0029】

また、電子部品10では、図1に示すように、側面S5,S6において、端面S3と外部電極13,14との間にはそれぞれ、外部電極13,14と異なる電位に保たれる外部電極が設けられていない。なお、図1に示すように、側面S5,S6には、外部電極12aが端面S3から折り返されている。そのため、端面S3と外部電極13,14との間にはそれぞれ、外部電極12aが設けられている。ただし、外部電極12aはそれぞれ、外部電極13,14と内部導体30を介して電気的に接続されている。そのため、外部電極12aの電位は、外部電極13,14の電位と等しい。

【0030】

また、電子部品10では、図1に示すように、側面S5,S6において、端面S4と外部電極15,16との間にはそれぞれ、外部電極15,16と異なる電位に保たれる外部電極が設けられていない。なお、図1に示すように、側面S5,S6には、外部電極12bが端面S4から折り返されている。そのため、端面S4と外部電極15,16との間にはそれぞれ、外部電極12bが設けられている。ただし、外部電極12bはそれぞれ、外部電極15,16と内部導体31を介して電気的に接続されている。そのため、外部電極12bの電位は、外部電極15,16の電位と等しい。

【0031】

更に、側面S5において、外部電極13と外部電極15との間には、外部電極13,15の電位と異なる電位に保たれる外部電極が設けられていない。同様に、側面S6において、外部電極14と外部電極16との間には、外部電極14,16の電位と異なる電位に保たれる外部電極が設けられていない。すなわち、外部電極13,15間及び外部電極14,16間には、外部電極が設けられていない。これにより、外部電極13,15が隣り合うと共に、外部電極14,16が隣り合うようになる。

【0032】

(電子部品の製造方法)

次に、電子部品10の製造方法について説明する。なお、図面は、図1ないし図3を援用する。

【0033】

まず、主成分であるBaTiO3、CaTiO3、SrTiO3又はCaZrO3と、副成分であるMn化合物、Fe化合物、Cr化合物、Co化合物、Ni化合物または希土類化合物とを所定の比率で秤量してボールミルに投入し、湿式調合を行う。得られた混合物を乾燥してから粉砕し、得られた粉末を仮焼する。得られた仮焼粉末をボールミルにて湿式粉砕した後、乾燥してから解砕して、誘電体セラミック粉末を得る。

【0034】

この誘電体セラミック粉末に対して、有機バインダ及び有機溶剤を加えてボールミルで混合を行う。得られたセラミックスラリーをドクターブレード法により、キャリアシート上にシート状に形成して乾燥させ、セラミック層17となるべきセラミックグリーンシートを作製する。セラミック層17となるべきセラミックグリーンシートの厚さは、0.5μm以上10μm以下であることが好ましい。

【0035】

次に、セラミック層17となるべきセラミックグリーンシート上に、導電性材料からなるペーストをスクリーン印刷法やフォトリソグラフィ法などの方法で塗布することにより、内部導体30,31を形成する。導電性材料からなるペーストは、例えば、金属粉末に、有機バインダ及び有機溶剤が加えられたものである。金属粉末は、例えば、Ni、Cu、Ag、Pd、Ag−Pd合金、Au等である。内部導体30,31の厚さは、0.3μm以上2.0μm以下であることが好ましい。

【0036】

次に、セラミック層17となるべきセラミックグリーンシートを積層して未焼成のマザー積層体を得る。この後、未焼成のマザー積層体に対して、静水圧プレスにて圧着を施す。

【0037】

次に、未焼成のマザー積層体を所定寸法にカットして、複数の未焼成の積層体11を得る。この後、積層体11の表面に、バレル研磨加工等の研磨加工を施す。

【0038】

次に、未焼成の積層体11を焼成する。焼成温度は、例えば、900℃以上1300℃以下であることが好ましい。以上の工程により、積層体11の準備が完了する。

【0039】

次に、積層体11に外部電極12〜16を形成する。具体的には、公知のディップ法やスリット工法等により、積層体11の表面に導電性ペーストを塗布する。そして、導電性ペーストを700℃以上900℃以下の温度で焼付けを行うことにより、外部電極12〜16の下地電極を形成する。導電性ペーストの材料としては、例えば、Cu,Ni,Ag,Pd,Ag−Pd合金,Au等が挙げられる。下地電極の厚さは、10μm以上50μm以下であることが好ましい。次に、下地電極上にめっきを施して外部電極12〜16を完成させる。めっき層の材料としては、例えば、Cu,Ni,Ag,Pd,Ag−Pd合金,Au等が挙げられる。また、複数回のめっきを行って、複数層のめっき層を下地電極上に形成してもよい。以上の工程により、電子部品10が完成する。

【0040】

(基板モジュールの構成)

次に、電子部品10を備えている基板モジュール40aについて図面を参照しながら説明する。図4(a)は、基板モジュール40aの断面構造図であり、図4(b)は、基板モジュール40aをz軸方向の正方向側から平面視した図である。図5は、図4の基板モジュール40aの等価回路図である。

【0041】

基板モジュール40aは、図4(a)に示すように、電子部品10及び回路基板51を備えている。回路基板51は、基板本体52、信号導体54、グランド電極55、ビアホール導体56及びグランド導体Gを含んでいる。

【0042】

基板本体52は、複数のセラミック層及び導体層が積層されてなる積層基板であり、その主面及び内部において電気回路を有している。信号導体54は、基板本体52のz軸方向の正方向側の主面上に設けられており、図4(b)に示すようにy軸方向に延在している。信号導体54のy軸方向の正方向側の端部には、図示しない入力ポートP1が設けられており、信号導体54のy軸方向の負方向側の端部には、図示しない出力ポートP2が設けられている。グランド電極55は、回路基板51のz軸方向の正方向側の主面上に設けられており、図4(b)に示すように、長方形状をなしている。

【0043】

グランド導体Gは、基板本体52内に設けられており、接地電位に保たれる。グランド導体Gは、図示しないグランドポートP3に接続されている。ビアホール導体56は、基板本体52内に設けられており、グランド電極55とグランド導体Gとを接続している。これにより、グランド電極55も接地電位に保たれる。

【0044】

電子部品10は、回路基板51に実装されている。より詳細には、外部電極12aは、はんだ60aにより、信号導体54に接続されている。また、外部電極12bは、はんだ60bにより、グランド電極55に接続されている。これにより、基板モジュール40aは、図5に示す回路構成を有するようになる。すなわち、信号導体54は、入力ポートP1と出力ポートP2とを接続している。そして、電子部品10は、信号導体54とグランドポートP3との間に設けられている。図5において、コンデンサC、抵抗R及びコイルLは、電子部品10が有している静電容量、電気抵抗及びインダクタを示している。基板モジュール40aが図5に示す構成を有することにより、高周波信号は、入力ポートP1から入力し、出力ポートP2から出力される。更に、入力ポートP1から入力した高周波信号の内、電子部品10の共振周波数の高周波信号は、出力ポートP2から出力せずに、グランドポートP3から出力する。なお、基板モジュール40aの回路構成は、図5に限らない。よって、基板モジュール40aにおいて、電子部品10が入力ポートP1と出力ポートP2との間に設けられていてもよい。

【0045】

(効果)

以上の電子部品10及び基板モジュール40aによれば、以下に説明するように、低ESL化を図ることができる。図6は、比較例に係る電子部品110の外観斜視図である。図7は、比較例に係る電子部品110の積層体111の分解斜視図である。比較例に係る電子部品110は、電子部品10において引き出し導体22〜25及び外部電極13〜16を取り除いたものである。そこで、電子部品110において電子部品10と同じ構成については、電子部品10の構成の参照符号に100を足した参照符号を付した。

【0046】

比較例に係る電子部品110が実装された基板モジュールでは、高周波信号は、信号導体から外部電極112aを介して電子部品110内に入力し、外部電極112bを介してグランド電極へと出力する。この際、高周波信号は、信号導体、外部電極112a、引き出し導体120、容量導体118、容量導体119、引き出し導体121、外部電極112b、グランド電極の順に流れる。すなわち、比較例に係る電子部品110が実装された基板モジュールでは、高周波信号は、1本の経路のみを流れる。

【0047】

一方、基板モジュール40aの電子部品10では、高周波信号は、信号導体54から外部電極12aを介して電子部品10内に入力し、外部電極12bを介してグランド電極55へと出力する。この際、高周波信号は、以下に説明する第1の経路及び第2の経路を流れる。

【0048】

第1の経路は、信号導体54、外部電極12a、引き出し導体20、容量導体18、容量導体19、引き出し導体21、外部電極12b、グランド電極55の順に高周波信号が流れる経路である。第2の経路は、信号導体54、外部電極12a、引き出し導体20、容量導体18、引き出し導体22,23、外部電極13,14、外部電極15,16、引き出し導体24,25、容量導体19、引き出し導体21、外部電極12b、グランド電極55の順に高周波信号が流れる経路である。ここで、第2の経路において、高周波信号は、外部電極13,14から外部電極15,16へと流れる場合には、外部電極13,14と外部電極15,16との間の誘電体内部を通過することにより、外部電極13,14から外部電極15,16へと通過する。

【0049】

以上のように、電子部品10が実装された基板モジュール40aでは、高周波信号は、並列に接続された第1の経路及び第2の経路を流れる。ここで、電子部品10の第1の経路は、電子部品110の経路と同じである。よって、電子部品10は、電子部品110に対して第2の経路が追加された構造を有している。そして、第1の経路のインダクタンス値L1と第2の経路のインダクタンス値L2との合成インダクタンス値LTは、以下の式(1)に示される。

【0050】

LT=L1・L2/(L1+L2)・・・(1)

【0051】

電子部品110の経路のインダクタンス値はL1である。よって、電子部品10の第1の経路及び第2の経路の合成インダクタンス値LTは、電子部品110の経路のインダクタンス値L1よりも小さくなる。すなわち、電子部品10は、電子部品110に比べて低ESL化が図られている。

【0052】

また、電子部品10において、低ESL化が図られることにより、共振周波数が高くなる。その結果、電子部品10の高周波特性が向上する。

【0053】

なお、高周波信号が外部電極13,14から外部電極15,16に流れるためには、側面S5において、外部電極13と外部電極15との間には、外部電極13,15の電位と異なる電位に保たれる外部電極が設けられていないことが好ましい。同様に、側面S6において、外部電極14と外部電極16との間には、外部電極14,16の電位と異なる電位に保たれる外部電極が設けられていないことが好ましい。

【0054】

また、高周波信号が外部電極13,14から外部電極15,16に流れるためには、外部電極13,14の間隔及び外部電極15,16の間隔は、できるだけ小さいことが好ましく、例えば、50μm以上200μmであることが好ましい。

【0055】

また、電子部品10では、回路基板51への実装の際にショートが発生することを抑制できる。より詳細には、特許文献1に記載の積層コンデンサ500では、外部電極512,514間が近接しているので、回路基板への実装時に、外部電極512と外部電極514との間がはんだによって接続されてしまうおそれがある。すなわち、積層コンデンサ500では、ショートが発生するおそれがある。

【0056】

一方、電子部品10では、外部電極12a,12bは、特許文献1に記載の積層コンデンサ500の外部電極512,514に比べて近接していない。その代わり、外部電極13と外部電極15とは近接している。同様に、外部電極14と外部電極16とは近接している。しかしながら、外部電極13〜16は、回路基板51に対してはんだ実装されない。そのため、外部電極13と外部電極15との間、及び、外部電極14と外部電極16との間がはんだにより接続される可能性が低い。よって、電子部品10では、回路基板51への実装の際にショートが発生することを抑制できる。

【0057】

また、電子部品10では、電子部品10を流れる高周波信号に損失が発生しにくい。より詳細には、電子部品10において、高周波信号は、x軸方向の正方向側に向かって流れる必要がある。ここで、電子部品10において、側面S5,S6において、端面S3と外部電極13,14との間に、外部電極13,14と異なる電位に保たれる外部電極が設けられていると、外部電極13,14から該外部電極に向かって(すなわち、x軸方向の負方向側に向かって)高周波信号が流れる。すなわち、高周波信号が流れるべき方向の反対方向に高周波信号が流れるようになり、損失が発生してしまう。そこで、電子部品10では、図1に示すように、側面S5,S6において、端面S3と外部電極13,14との間にはそれぞれ、外部電極13,14と異なる電位に保たれる外部電極が設けられていない。これにより、前記損失の発生が抑制される。なお、同じ理由により、側面S5,S6において、端面S4と外部電極15,16との間にはそれぞれ、外部電極15,16と異なる電位に保たれる外部電極が設けられていない。

【0058】

電子部品10では、デラミネーションの発生を抑制できる。より詳細には、電子部品において、積層体の角ではデラミネーションが発生しやすい。角に引き出し電極とセラミック層とが積層されていると、引き出し電極とセラミック層との間においてデラミネーションが特に発生しやすい。そこで、電子部品10では、引き出し導体20,21は、積層体10の角に引き出されていない。これにより、電子部品10では、デラミネーションの発生が抑制される。更に、電子部品10では、積層体11の角において、引き出し電極20,21が露出しないので、電子部品10の耐湿性が向上する。

【0059】

(第1の実験)

本願発明者は、電子部品10及び基板モジュール40aが奏する効果をより明確にするために、以下に説明する第1の実験を行った。具体的には、図4に示す基板モジュール40aのサンプル(以下、第1のサンプル)及び図6及び図7に示す電子部品110が図4の回路基板51に実装されてなる基板モジュールのサンプル(第2のサンプル)を作製した。そして、ネットワークアナライザ(アジレント社製8722D)を用いて、第1のサンプル及び第2のサンプルのESL、伝送特性(S21)を測定した。まず、第1のサンプル及び第2のサンプルの条件について説明する。

【0060】

寸法:2.096mm×1.290mm×0.793mm

静電容量:14pF

内部導体及び外部電極の材料:Cu

セラミック層の比誘電率(ε):27

内部導体の枚数:6

素子厚(内部導体30,31の間隔):122μm

外層厚み(内部導体30a,31cから積層体11の上面S1又は下面S2までの距離):88μm

【0061】

以上の条件の第1のサンプル及び第2のサンプルでは、ESLは以下の通りとなった。なお、ESLは0.5〜20GHzの周波数帯域で測定した。

【0062】

第1のサンプルのESL:465pH

第2のサンプルのESL:500pH

【0063】

よって、本実験により、電子部品10を備えた基板モジュール40aでは、電子部品110を備えた回路モジュールよりも、低ESL化が図られていることが分かる。

【0064】

図8は、第1のサンプル及び第2のサンプルの伝送特性(S21)を示したグラフである。縦軸は減衰量を示し、横軸は周波数を示している。

【0065】

図8によれば、第1のサンプルの自己共振周波数f1が、第2のサンプルの自己共振周波数f2よりも高くなっていることが分かる。具体的には、自己共振周波数f1は、1.975GHzであり、自己共振周波数f2は、1.905GHzである。よって、図8の実験結果によれば、基板モジュール40aの高周波特性は、電子部品110を備えた回路モジュールの高周波特性よりも優れていることが分かる。

【0066】

(第1の変形例)

次に、第1の変形例に係る基板モジュールについて図面を参照しながら説明する。図9は、基板モジュール40bの断面構造図である。

【0067】

基板モジュール40bは、外部電極15,16がグランド電極55にはんだ60cにより接続されている点において基板モジュール40aと相違する。その他の相違点は存在しないので、基板モジュール40bの構成のこれ以上の説明を省略する。

【0068】

基板モジュール40aでは、高周波信号は、第1の経路及び第2の経路を流れていた。一方、基板モジュール40bでは、高周波信号は、第1の経路及び第2の経路に加えて、以下に説明する第3の経路及び第4の経路を流れる。

【0069】

第3の経路は、信号導体54、外部電極12a、引き出し導体20、容量導体18、容量導体19、引き出し導体24,25、外部電極15,16、グランド電極55の順に高周波信号が流れる経路である。第4の経路は、信号導体54、外部電極12a、引き出し導体20、容量導体18、引き出し導体22,23、外部電極13,14、外部電極15,16、グランド電極55の順に高周波信号が流れる経路である。

【0070】

以上のように、基板モジュール40bでは、高周波信号は、第1の経路及び第2の経路に加えて、第3の経路及び第4の経路も流れるようになる。その結果、基板モジュール40bでは、基板モジュール40aよりも更に低ESL化が図られると共に、高周波特性が向上する。

【0071】

また、基板モジュール40bでは、外部電極13,14に近接している外部電極15,16がはんだ60cによりグランド電極55に接続されている。ただし、電子部品10の回路基板51への固定は、主に、外部電極12aと信号導体54との接続、及び、外部電極12bとグランド電極55との接続によって行われている。そのため、外部電極15,16は、グランド電極55に電気的に接続されていればよく、グランド電極55に強固に固定されている必要はない。したがって、はんだ60cの量は少なくてもよい。よって、はんだ60cにより、外部電極13,14と外部電極15,16とが接続される可能性は低い。すなわち、基板モジュール40bにおいても、電子部品10の回路基板51への実装の際にショートが発生することを抑制できる。

【0072】

(第2の変形例)

次に、第2の変形例に係る基板モジュールについて図面を参照しながら説明する。図10は、基板モジュール40cの断面構造図である。

【0073】

基板モジュール40cは、外部電極13,14が信号導体54にはんだ60dにより接続されている点において基板モジュール40bと相違する。その他の相違点は存在しないので、基板モジュール40cの構成のこれ以上の説明を省略する。

【0074】

基板モジュール40bでは、高周波信号は、第1の経路ないし第4の経路を流れていた。一方、基板モジュール40bでは、高周波信号は、第1の経路ないし第4の経路に加えて、以下に説明する第5の経路ないし第7の経路を流れる。

【0075】

第5の経路は、信号導体54、外部電極13,14、引き出し導体22,23、容量導体18、容量導体19、引き出し導体21、外部電極12b、グランド電極55の順に高周波信号が流れる経路である。第6の経路は、信号導体54、外部電極13,14、引き出し導体22,23、容量導体18、容量導体19、引き出し導体24,25、外部電極15,16、グランド電極55の順に高周波信号が流れる経路である。第7の経路は、信号導体54、外部電極13,14、外部電極15,16、グランド電極55の順に高周波信号が流れる経路である。

【0076】

以上のように、基板モジュール40cでは、高周波信号は、第1の経路ないし第4の経路に加えて、第5の経路ないし第7の経路も流れるようになる。その結果、基板モジュール40cでは、基板モジュール40cよりも更に低ESL化が図られると共に、高周波特性が向上する。

【0077】

また、基板モジュール40cでは、外部電極13,14がはんだ60dにより信号導体54に接続され、かつ、外部電極15,16がはんだ60cによりグランド電極55に接続されている。ただし、電子部品10の回路基板51への固定は、主に、外部電極12aと信号導体54との接続、及び、外部電極12bとグランド電極55との接続によって行われている。そのため、外部電極13,14は、信号導体54に接続されていればよく、信号導体54に強固に固定されている必要はない。同様に、外部電極15,16は、グランド電極55に電気的に接続されていればよく、グランド電極55に強固に固定されている必要はない。したがって、はんだ60c,60dの量は少なくてもよい。よって、はんだ60c,60dにより、外部電極13,14と外部電極15,16とが接続される可能性は低い。すなわち、基板モジュール40cにおいても、電子部品10の回路基板51への実装の際にショートが発生することを抑制できる。

【0078】

(第2の実験)

本願発明者は、電子部品10及び基板モジュール40b,40cが奏する効果をより明確にするために、以下に説明する第2の実験を行った。具体的には、図9に示す基板モジュール40bのサンプル(以下、第3のサンプル)及び図10に示す基板モジュール40cのサンプル(以下、第4のサンプル)を作製した。そして、第3のサンプル及び第4のサンプルのESL、伝送特性(S21)を測定した。第3のサンプル及び第4のサンプルの条件は、第1のサンプル及び第2のサンプルの条件と同じであるので、説明を省略する。

【0079】

第3のサンプル及び第4のサンプルでは、ESLは以下の通りとなった。

【0080】

第3のサンプルのESL:405pH

第4のサンプルのESL:355pH

【0081】

よって、本実験により、基板モジュール40b,40cでは、基板モジュール40aよりも更に低ESL化が図られていることが分かる。

【0082】

図11は、第1のサンプルないし第4のサンプルの伝送特性(S21)を示したグラフである。縦軸は減衰量を示し、横軸は周波数を示している。

【0083】

図11によれば、第3のサンプルの自己共振周波数f3が、第1のサンプルの自己共振周波数f1よりも高くなっていることが分かる。また、第4のサンプルの自己共振周波数f4が、第3のサンプルの自己共振周波数f3よりも高くなっていることが分かる。具体的には、自己共振周波数f4は、2.25GHzであり、自己共振周波数f3は、2.115GHzであり、自己共振周波数f1は、1.975GHzである。よって、図11の実験結果によれば、基板モジュール40b,40cの高周波特性は、基板モジュール40aの高周波特性よりも更に優れていることが分かる。

【0084】

(第2の実施形態)

以下に、第2の実施形態に係る電子部品10aの構成について図面を参照しながら説明する。図12は、第2の実施形態に係る電子部品10aの積層体11aの分解斜視図である。図13は、図12の電子部品10aの内部平面図である。なお、電子部品10aの外観斜視図は、電子部品10の外観斜視図と同じであるので、図1を援用する。

【0085】

積層体11aは、図12に示すように、セラミック層17i及び内部導体41,42を更に備えている。

【0086】

セラミック層17iは、図12に示すように、セラミック層17aとセラミック層17bとの間に設けられている。内部導体41,42は、セラミック層17iの表面上に設けられており、隙間を空けた状態でx軸方向の負方向側から正方向側へとこの順に並んでいる。

【0087】

内部導体41は、図12及び図13に示すように、容量導体43、引き出し導体44,47,48を備えている。容量導体43は、長方形状をなしており、セラミック層17iのx軸方向の負方向側の半分の領域内に設けられている。

【0088】

引き出し導体44は、図12及び図13に示すように、容量導体43に接続され、かつ、積層体11の端面S3に引き出されることにより端面S3から露出している。より詳細には、引き出し導体44は、容量導体43のx軸方向の負方向側の辺から、x軸方向の負方向側に向かって延在している。これにより、引き出し導体44は、セラミック層17iのx軸方向の負方向側の短辺に引き出され、外部電極12aに接続されている。

【0089】

引き出し導体47は、図12及び図13に示すように、容量導体43に接続され、かつ、積層体11の側面S5に引き出されることにより側面S5から露出している。より詳細には、引き出し導体47は、容量導体43のy軸方向の正方向側の辺から、y軸方向の正方向側に向かって引き出されている。これにより、引き出し導体47は、セラミック層17iのy軸方向の正方向側の長辺の中点よりx軸方向の負方向側の位置に引き出され、外部電極13に接続されている。

【0090】

引き出し導体48は、図12及び図13に示すように、容量導体43に接続され、かつ、積層体11の側面S6に引き出されることにより側面S6から露出している。より詳細には、引き出し導体48は、容量導体43のy軸方向の負方向側の辺から、y軸方向の負方向側に向かって引き出されている。これにより、引き出し導体48は、セラミック層17iのy軸方向の負方向側の長辺の中点よりx軸方向の負方向側の位置に引き出され、外部電極14と接続されている。

【0091】

内部導体42は、図12及び図13に示すように、容量導体45、引き出し導体46,49,50を備えている。容量導体45は、長方形状をなしており、セラミック層17iのx軸方向の正方向側の半分の領域内に設けられている。

【0092】

引き出し導体46は、図12及び図13に示すように、容量導体45に接続され、かつ、積層体11の端面S4に引き出されることにより端面S4から露出している。より詳細には、引き出し導体46は、容量導体45のx軸方向の正方向側の辺から、x軸方向の正方向側に向かって引き出されている。これにより、引き出し導体46は、セラミック層17iのx軸方向の正方向側の短辺に引き出され、外部電極12bに接続されている。

【0093】

引き出し導体49は、図12及び図13に示すように、容量導体45に接続され、かつ、積層体11の側面S5に引き出されることにより側面S5から露出している。より詳細には、引き出し導体49は、容量導体45のy軸方向の正方向側の辺から、y軸方向の正方向側に向かって延在している。これにより、引き出し導体49は、セラミック層17iのy軸方向の正方向側の長辺の中点よりx軸方向の正方向側の位置に引き出され、外部電極15に接続されている。

【0094】

引き出し導体50は、図12及び図13に示すように、容量導体45に接続され、かつ、積層体11の側面S6に引き出されることにより側面S6から露出している。より詳細には、引き出し導体50は、容量導体45のy軸方向の負方向側の辺から、y軸方向の負方向側に向かって引き出されている。これにより、引き出し導体50は、セラミック層17iのy軸方向の負方向側の長辺の中点よりx軸方向の正方向側の位置に引き出され、外部電極16と接続されている。

【0095】

以上のような積層体11aを備えた電子部品10では、第2の経路を流れる高周波信号の強度が強くなる。より詳細には、高周波信号は、信号導体54、外部電極12a、引き出し導体44、容量導体43、引き出し導体47,48、外部電極13,14、外部電極15,16、引き出し導体49,50、容量導体45、引き出し導体46、外部電極12b、グランド電極55の順に流れる。すなわち、高周波信号は、第2の経路と等価な経路を流れる。その結果、積層体11aを備えた電子部品10では、高周波特性が向上する。

【0096】

(第3の実施形態)

以下に、第3の実施形態に係る電子部品10bの構成について図面を参照しながら説明する。図14は、第3の実施形態に係る電子部品10bの内部平面図である。なお、電子部品10bの外観斜視図は、電子部品10の外観斜視図と同じであるので、図1を援用する。

【0097】

電子部品10bでは、図14に示すように、引き出し導体23,25が設けられていない点において電子部品10と相違する。この場合には、電子部品10bは、側面S5が回路基板51に対向するように実装される。電子部品10の上面S1及び下面S2には外部電極13〜16が設けられていないので、電子部品10のz軸方向における幅を小さくできる。その結果、電子部品10同士を近づけて配置することが可能となる。

【0098】

(第4の実施形態)

以下に、第4の実施形態に係る電子部品10cの構成について図面を参照しながら説明する。図15は、第4の実施形態に係る電子部品10cの内部平面図である。なお、電子部品10cの外観斜視図は、電子部品10の外観斜視図と同じであるので、図1を援用する。

【0099】

電子部品10cは、引き出し導体72(72a〜72c),73(73a〜73c),74(74a〜74c),75(75a〜75c)を備えている点において、電子部品10と相違する。

【0100】

引き出し導体72は、接続導体20に接続され、かつ、積層体11cの側面S5に引き出されることにより側面S5から露出している。より詳細には、引き出し導体72は、接続導体20のy軸方向の正方向側の辺の中点から、y軸方向の正方向側に向かって延在している。これにより、引き出し導体72は、セラミック層17のy軸方向の正方向側の長辺において引き出し導体22よりx軸方向の負方向側の位置に引き出され、外部電極12aに接続されている。

【0101】

引き出し導体73は、接続導体20に接続され、かつ、積層体11cの側面S6に引き出されることにより側面S6から露出している。より詳細には、引き出し導体73は、接続導体20のy軸方向の負方向側の辺の中点から、y軸方向の負方向側に向かって延在している。これにより、引き出し導体73は、セラミック層17のy軸方向の負方向側の長辺において引き出し導体23よりx軸方向の負方向側の位置に引き出され、外部電極12aに接続されている。

【0102】

引き出し導体74は、接続導体21に接続され、かつ、積層体11cの側面S5に引き出されることにより側面S5から露出している。より詳細には、引き出し導体74は、接続導体21のy軸方向の正方向側の辺の中点から、y軸方向の正方向側に向かって延在している。これにより、引き出し導体74は、セラミック層17のy軸方向の正方向側の長辺において引き出し導体24よりx軸方向の負方向側の位置に引き出され、外部電極12bに接続されている。

【0103】

引き出し導体75は、接続導体21に接続され、かつ、積層体11cの側面S6に引き出されることにより側面S6から露出している。より詳細には、引き出し導体75は、接続導体21のy軸方向の負方向側の辺の中点から、y軸方向の負方向側に向かって延在している。これにより、引き出し導体75は、セラミック層17のy軸方向の負方向側の長辺において引き出し導体25よりx軸方向の正方向側の位置に引き出され、外部電極12bに接続されている。

【0104】

電子部品10cでは、引き出し導体72〜75が設けられているので、電子部品10c内における電流経路が電子部品10内における電流経路よりも多くなる。その結果、電子部品10cでは、より効果的に低ESL化を図ることができる。

【0105】

なお、電子部品10cにおいて、引き出し導体72〜75は、セラミック層17の角には設けられていないことが好ましい。

【0106】

(第5の実施形態)

以下に、第5の実施形態に係る電子部品10dについて図面を参照しながら説明する。図16は、第5の実施形態に係る電子部品10dの外観斜視図である。

【0107】

図16に示すように、外部電極13と外部電極14とは、上面S1及び下面S2に設けられている外部電極によってつながっていてもよい。同様に、外部電極15と外部電極16とは、上面S1及び下面S2に設けられている外部電極によってつながっていてもよい。なお、電子部品10dの内部構造は、電子部品10,10a〜10cの内部構造のいずれであってもよい。

【0108】

(第6の実施形態)

以下に、第6の実施形態に係る電子部品10eについて図面を参照しながら説明する。図17は、第6の実施形態に係る電子部品10eの外観斜視図である。

【0109】

図17に示すように、外部電極13,15はそれぞれ、側面S5にのみ設けられ、上面S1及び下面S2に折り返されていなくてもよい。同様に、外部電極14,16はそれぞれ、側面S6にのみ設けられ、上面S1及び下面S2に折り返されていなくてもよい。

【0110】

外部電極13,15の間隔、及び、外部電極14,16の間隔を小さくする場合には、例えば、外部電極13〜16を直接めっきで形成することが考えられる。直接めっきでは、引き出し導体22〜25が露出した部分を覆うように外部電極13〜15が形成される。よって、この場合には、外部電極13〜15は、上面S1及び下面S2には形成されないことが多い。

【0111】

(その他の実施形態)

本発明に係る電子部品10,10a〜10e及び基板モジュール40a〜40cは、前記実施形態に示したものに限らず、その要旨の範囲内において変更可能である。

【0112】

なお、セラミック層17の代わりに、エポキシ樹脂、ポリプロピレン等の樹脂材料が用いられてもよい。

【産業上の利用可能性】

【0113】

以上のように、本発明は、電子部品及び基板モジュールに有用であり、特に、低ESL化を図ることができると共に、回路基板への実装の際にショートが発生することを抑制できる点において優れている。

【符号の説明】

【0114】

S1 上面

S2 下面

S3,S4 端面

S5,S6 側面

10,10a〜10e 電子部品

11,11a〜11e 積層体

12a,12b,13〜16 外部電極

17a〜17i セラミック層

18a〜18c,19a〜19c,43,45 容量導体

20a〜20c,21a〜21c,22a〜22c,23a〜23c,24a〜24c,25a〜25c,44,46〜50,72a〜72c,73a〜73c,74a〜74c,75a〜75c 引き出し導体

30a〜30c,31a〜31c,41,42 内部導体

40a〜40c 基板モジュール

51 回路基板

52 基板本体

54 信号導体

55 グランド電極

56 ビアホール導体

60a〜60d はんだ

【技術分野】

【0001】

本発明は、電子部品及び基板モジュールに関し、より特定的には、コンデンサを内蔵している電子部品及び基板モジュールに関する。

【背景技術】

【0002】

従来の電子部品としては、例えば、特許文献1に記載の積層コンデンサが知られている。図18は、特許文献1に記載の積層コンデンサ500の正面図である。

【0003】

積層コンデンサ500は、積層体502、内部導体504,506、引出電極508,510及び外部電極512,514を備えている。積層体502は、複数の誘電体層が積層されることにより構成されている。図18において、積層体502の下側の面が実装面である。内部導体504,506は、誘電体層と共に積層されており、誘電体層を挟んで互いに対向することにより静電容量を形成している。引出電極508,510はそれぞれ、内部導体504,506に接続されていると共に、実装面に引き出されている。外部電極512,514はそれぞれ、引出電極508,510に接続されている。以上のような積層コンデンサ500では、引出電極508,510間の距離と内部導体504,506から実装面までの距離とを所定の関係に保つことにより、等価直列インダクタンスの低減を図っている。

【0004】

しかしながら、特許文献1に記載の積層コンデンサ500では、外部電極512,514が近接しているので、回路基板への実装時に、外部電極512と外部電極514とがはんだによって接続されてしまうおそれがある。すなわち、積層コンデンサ500では、ショートが発生するおそれがある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2004−140183号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

そこで、本発明の目的は、低ESL化を図ることができると共に、回路基板への実装の際にショートが発生することを抑制できる電子部品及び基板モジュールを提供することである。

【課題を解決するための手段】

【0007】

本発明の一形態に係る電子部品は、複数の誘電体層が積層されてなる直方体状の積層体と、前記誘電体層上に設けられている第1の容量導体と、前記第1の容量導体に接続され、かつ、前記積層体の第1の端面に引き出されている第1の引き出し導体と、前記第1の容量導体に接続され、かつ、前記積層体の第1の側面に引き出されている第3の引き出し導体と、前記誘電体層上に設けられ、かつ、前記第1の容量導体と前記誘電体層を介して対向している第2の容量導体と、前記第2の容量導体に接続され、かつ、前記積層体の第2の端面に引き出されている第2の引き出し導体と、前記第2の容量導体に接続され、かつ、前記第1の側面に引き出されている第4の引き出し導体と、前記第1の端面及び前記第2の端面のそれぞれと前記積層体の底面とに跨って設けられ、かつ、前記第1の引き出し導体及び前記第2の引き出し導体のそれぞれに接続されている第1の外部電極及び第2の外部電極と、前記第1の側面に設けられ、かつ、前記第3の引き出し導体に接続されている第3の外部電極と、前記第1の側面に設けられ、かつ、前記第4の引き出し導体に接続されている第4の外部電極と、を備えており、前記第1の側面において、前記第1の端面と前記第3の外部電極との間には、該第3の外部電極の電位と異なる電位に保たれる外部電極が設けられておらず、前記第1の側面において、前記第2の端面と前記第4の外部電極との間には、該第4の外部電極の電位と異なる電位に保たれる外部電極が設けられていないこと、を特徴とする。

【0008】

本発明の一形態に係る基板モジュールは、第1のランド及び第2のランドを含んでいる回路基板と、前記回路基板に実装される前記電子部品と、を備えており、前記第1の外部電極は、前記第1のランドに接続され、前記第2の外部電極は、前記第2のランドに接続されていること、を特徴とする。

【発明の効果】

【0009】

本発明によれば、低ESL化を図ることができると共に、回路基板への実装の際にショートが発生することを抑制できる。

【図面の簡単な説明】

【0010】

【図1】第1の実施形態に係る電子部品の外観斜視図である。

【図2】図1の電子部品の積層体の分解斜視図である。

【図3】図1の電子部品の内部平面図である。

【図4】図4(a)は、基板モジュールの断面構造図であり、図4(b)は、基板モジュールをz軸方向の正方向側から平面視した図である。

【図5】図4の基板モジュールの等価回路図である。

【図6】比較例に係る電子部品の外観斜視図である。

【図7】比較例に係る電子部品の積層体の分解斜視図である。

【図8】第1のサンプル及び第2のサンプルの伝送特性(S21)を示したグラフである。

【図9】基板モジュールの断面構造図である。

【図10】基板モジュールの断面構造図である。

【図11】第1のサンプルないし第4のサンプルの伝送特性(S21)を示したグラフである。

【図12】第2の実施形態に係る電子部品の積層体の分解斜視図である。

【図13】図12の電子部品の内部平面図である。

【図14】第3の実施形態に係る電子部品の内部平面図である。

【図15】第4の実施形態に係る電子部品の内部平面図である。

【図16】第5の実施形態に係る電子部品の外観斜視図である。

【図17】第6の実施形態に係る電子部品の外観斜視図である。

【図18】特許文献1に記載の積層コンデンサの正面図である。

【発明を実施するための形態】

【0011】

以下に、本発明の実施形態に係る電子部品及び基板モジュールについて図面を参照しながら説明する。

【0012】

(第1の実施形態)

(電子部品の構成)

まず、第1の実施形態に係る電子部品の構成について図面を参照しながら説明する。図1は、第1の実施形態に係る電子部品10の外観斜視図である。図2は、図1の電子部品10の積層体11の分解斜視図である。図3は、図1の電子部品の内部平面図である。以下では、積層体11の積層方向をz軸方向と定義する。積層体11をz軸方向から平面視したときに、積層体11の長辺が延在している方向をx軸方向と定義する。積層体11をz軸方向から平面視したときに、積層体11の短辺が延在している方向をy軸方向と定義する。

【0013】

電子部品10は、例えば、カップリングコンデンサとして用いられるチップコンデンサであり、図1ないし図3に示すように、積層体11、外部電極12(12a,12b),13〜16及び内部導体30(30a〜30c),31(31a〜31c)(図1には図示せず)を備えている。

【0014】

積層体11は、直方体状をなしている。ただし、積層体11は、面取りが施されることにより角及び稜線において丸みを帯びた形状をなしている。以下では、積層体11において、z軸方向の正方向側の面を上面S1とし、z軸方向の負方向側の面を下面S2とする。また、x軸方向の負方向側の面を端面S3とし、x軸方向の正方向側の面を端面S4とする。また、y軸方向の正方向側の面を側面S5とし、y軸方向の負方向側の面を側面S6とする。

【0015】

積層体11は、図2に示すように、複数のセラミック層17(17a〜17h)がz軸方向の正方向側から負方向側へとこの順に並ぶように積層されることにより構成されている。セラミック層17は、長方形状をなしており、誘電体セラミックにより作製されている。以下では、セラミック層17のz軸方向の正方向側の主面を表面と称し、セラミック層17のz軸方向の負方向側の主面を裏面と称す。

【0016】

積層体11の上面S1は、z軸方向の最も正方向側に設けられているセラミック層17aの表面により構成されている。積層体11の下面S2は、z軸方向の最も負方向側に設けられているセラミック層17hの裏面により構成されている。また、端面S3は、セラミック層17a〜17hのx軸方向の負方向側の短辺が連なることによって構成されている。端面S4は、セラミック層17a〜17hのx軸方向の正方向側の短辺が連なることによって構成されている。側面S5は、セラミック層17a〜17hのy軸方向の正方向側の長辺が連なることによって構成されている。側面S6は、セラミック層17a〜17hのy軸方向の負方向側の長辺が連なることによって構成されている。

【0017】

内部導体30a〜30cはそれぞれ、図2及び図3に示すように、セラミック層17b,17d,17fの表面上に設けられており、積層体11に内蔵されている。内部導体31a〜31cはそれぞれ、セラミック層17c,17e,17gの表面上に設けられており、積層体11に内蔵されている。すなわち、内部導体30と内部導体31とは、z軸方向において交互に積層されている。

【0018】

内部導体30(30a〜30c)は、容量導体18(18a〜18c)及び引き出し導体20(20a〜20c),22(22a〜22c),23(23a〜23c)を有している。容量導体18は、長方形状をなしており、セラミック層17の外縁に接しないように、セラミック層17の表面上に設けられている。

【0019】

引き出し導体20は、容量導体18に接続され、かつ、積層体11の端面S3に引き出されることにより端面S3から露出している。より詳細には、引き出し導体20は、容量導体18のx軸方向の負方向側の短辺から、x軸方向の負方向側に向かって引き出されている。これにより、引き出し導体20は、セラミック層17のx軸方向の負方向側の短辺に引き出されている。

【0020】

引き出し導体22は、容量導体18に接続され、かつ、積層体11の側面S5に引き出されることにより側面S5から露出している。より詳細には、引き出し導体22は、容量導体18のy軸方向の正方向側の長辺の中点よりx軸方向の負方向側の位置から、y軸方向の正方向側に向かって延在している。これにより、引き出し導体22は、セラミック層17のy軸方向の正方向側の長辺の中点よりx軸方向の負方向側の位置に引き出されている。

【0021】

引き出し導体23は、容量導体18に接続され、かつ、積層体11の側面S6に引き出されることにより側面S6から露出している。より詳細には、引き出し導体23は、容量導体18のy軸方向の負方向側の長辺の中点よりx軸方向の負方向側の位置から、y軸方向の負方向側に向かって延在している。これにより、引き出し導体23は、セラミック層17のy軸方向の負方向側の長辺の中点よりx軸方向の負方向側の位置に引き出されている。

【0022】

内部導体31(31a〜31c)は、容量導体19(19a〜19c)及び引き出し導体21(21a〜21c),24(24a〜24c),25(25a〜25c)を有している。容量導体19は、長方形状をなしており、セラミック層17の外縁に接しないように、セラミック層17の表面上に設けられている。そして、容量導体19は、容量導体18とセラミック層17を介して対向している。これにより、容量導体18,19間には静電容量(すなわち、コンデンサ)が形成されている。

【0023】

引き出し導体21は、容量導体19に接続され、かつ、積層体11の端面S4に引き出されることにより端面S4から露出している。より詳細には、引き出し導体21は、容量導体19のx軸方向の正方向側の短辺から、x軸方向の正方向側に向かって引き出されている。これにより、引き出し導体21は、セラミック層17のx軸方向の正方向側の短辺に引き出されている。

【0024】

引き出し導体24は、容量導体19に接続され、かつ、積層体11の側面S5に引き出されることにより側面S5から露出している。より詳細には、引き出し導体24は、容量導体19のy軸方向の正方向側の長辺の中点よりx軸方向の正方向側の位置から、y軸方向の正方向側に向かって延在している。これにより、引き出し導体24は、セラミック層17のy軸方向の正方向側の長辺の中点よりx軸方向の正方向側の位置に引き出されている。すなわち、引き出し導体24は、z軸方向から平面視したときに、引き出し導体22よりもx軸方向の正方向側に位置している。

【0025】

引き出し導体25は、容量導体19に接続され、かつ、積層体11の側面S6に引き出されることにより側面S6から露出している。より詳細には、引き出し導体25は、容量導体19のy軸方向の負方向側の長辺の中点よりx軸方向の正方向側の位置から、y軸方向の負方向側に向かって延在している。これにより、引き出し導体25は、セラミック層17のy軸方向の負方向側の長辺の中点よりx軸方向の正方向側の位置に引き出されている。すなわち、引き出し導体25は、z軸方向から平面視したときに、引き出し導体23よりもx軸方向の正方向側に位置している。

【0026】

外部電極12a,12bはそれぞれ、端面S3,S4のそれぞれと積層体11の上面S1、下面S2及び側面S5,S6とに跨って設けられ、かつ、引き出し導体20a〜20c,21a〜21cのそれぞれに接続されている。より詳細には、外部電極12aは、引き出し導体20a〜20cが端面S3から露出している部分を覆うように、積層体11の端面S3の全面を覆っている。更に、外部電極12aは、端面S3から上面S1、下面S2及び側面S5,S6に折り返されている。外部電極12bは、引き出し導体21a〜21cが端面S4から露出している部分を覆うように、積層体11の端面S4の全面を覆っている。更に、外部電極12bは、端面S4から上面S1、下面S2及び側面S5,S6に折り返されている。

【0027】

外部電極13,14はそれぞれ、側面S5,S6に設けられ、かつ、引き出し導体22a〜22c,23a〜23cに接続されている。より詳細には、外部電極13は、引き出し導体22a〜22cが側面S5から露出している部分を覆うように、積層体11の側面S5においてz軸方向に延在する帯状に形成されている。更に、外部電極13は、側面S5から上面S1及び下面S2に折り返されている。外部電極14は、引き出し導体23a〜23cが側面S6から露出している部分を覆うように、積層体11の側面S6においてz軸方向に延在する帯状に形成されている。このとき、外部電極14は、外部電極13と対向している。更に、外部電極14は、側面S6から上面S1及び下面S2に折り返されている。

【0028】

外部電極15,16はそれぞれ、側面S5,S6に設けられ、かつ、引き出し導体24a〜24c,25a〜25cに接続されている。より詳細には、外部電極15は、引き出し導体24a〜24cが側面S5から露出している部分を覆うように、積層体11の側面S5においてz軸方向に延在する帯状に形成されている。更に、外部電極15は、側面S5から上面S1及び下面S2に折り返されている。また、外部電極15は、引き出し導体24が引き出し導体22よりもx軸方向の正方向側に位置しているので、外部電極13よりもx軸方向の正方向側に位置している。外部電極16は、引き出し導体25a〜25cが側面S6から露出している部分を覆うように、積層体11の側面S6においてz軸方向に延在する帯状に形成されている。このとき、外部電極16は、外部電極15と対向している。更に、外部電極16は、側面S6から上面S1及び下面S2に折り返されている。また、外部電極16は、引き出し導体25が引き出し導体23よりもx軸方向の正方向側に位置しているので、外部電極14よりもx軸方向の正方向側に位置している。

【0029】

また、電子部品10では、図1に示すように、側面S5,S6において、端面S3と外部電極13,14との間にはそれぞれ、外部電極13,14と異なる電位に保たれる外部電極が設けられていない。なお、図1に示すように、側面S5,S6には、外部電極12aが端面S3から折り返されている。そのため、端面S3と外部電極13,14との間にはそれぞれ、外部電極12aが設けられている。ただし、外部電極12aはそれぞれ、外部電極13,14と内部導体30を介して電気的に接続されている。そのため、外部電極12aの電位は、外部電極13,14の電位と等しい。

【0030】

また、電子部品10では、図1に示すように、側面S5,S6において、端面S4と外部電極15,16との間にはそれぞれ、外部電極15,16と異なる電位に保たれる外部電極が設けられていない。なお、図1に示すように、側面S5,S6には、外部電極12bが端面S4から折り返されている。そのため、端面S4と外部電極15,16との間にはそれぞれ、外部電極12bが設けられている。ただし、外部電極12bはそれぞれ、外部電極15,16と内部導体31を介して電気的に接続されている。そのため、外部電極12bの電位は、外部電極15,16の電位と等しい。

【0031】

更に、側面S5において、外部電極13と外部電極15との間には、外部電極13,15の電位と異なる電位に保たれる外部電極が設けられていない。同様に、側面S6において、外部電極14と外部電極16との間には、外部電極14,16の電位と異なる電位に保たれる外部電極が設けられていない。すなわち、外部電極13,15間及び外部電極14,16間には、外部電極が設けられていない。これにより、外部電極13,15が隣り合うと共に、外部電極14,16が隣り合うようになる。

【0032】

(電子部品の製造方法)

次に、電子部品10の製造方法について説明する。なお、図面は、図1ないし図3を援用する。

【0033】

まず、主成分であるBaTiO3、CaTiO3、SrTiO3又はCaZrO3と、副成分であるMn化合物、Fe化合物、Cr化合物、Co化合物、Ni化合物または希土類化合物とを所定の比率で秤量してボールミルに投入し、湿式調合を行う。得られた混合物を乾燥してから粉砕し、得られた粉末を仮焼する。得られた仮焼粉末をボールミルにて湿式粉砕した後、乾燥してから解砕して、誘電体セラミック粉末を得る。

【0034】

この誘電体セラミック粉末に対して、有機バインダ及び有機溶剤を加えてボールミルで混合を行う。得られたセラミックスラリーをドクターブレード法により、キャリアシート上にシート状に形成して乾燥させ、セラミック層17となるべきセラミックグリーンシートを作製する。セラミック層17となるべきセラミックグリーンシートの厚さは、0.5μm以上10μm以下であることが好ましい。

【0035】

次に、セラミック層17となるべきセラミックグリーンシート上に、導電性材料からなるペーストをスクリーン印刷法やフォトリソグラフィ法などの方法で塗布することにより、内部導体30,31を形成する。導電性材料からなるペーストは、例えば、金属粉末に、有機バインダ及び有機溶剤が加えられたものである。金属粉末は、例えば、Ni、Cu、Ag、Pd、Ag−Pd合金、Au等である。内部導体30,31の厚さは、0.3μm以上2.0μm以下であることが好ましい。

【0036】

次に、セラミック層17となるべきセラミックグリーンシートを積層して未焼成のマザー積層体を得る。この後、未焼成のマザー積層体に対して、静水圧プレスにて圧着を施す。

【0037】

次に、未焼成のマザー積層体を所定寸法にカットして、複数の未焼成の積層体11を得る。この後、積層体11の表面に、バレル研磨加工等の研磨加工を施す。

【0038】

次に、未焼成の積層体11を焼成する。焼成温度は、例えば、900℃以上1300℃以下であることが好ましい。以上の工程により、積層体11の準備が完了する。

【0039】

次に、積層体11に外部電極12〜16を形成する。具体的には、公知のディップ法やスリット工法等により、積層体11の表面に導電性ペーストを塗布する。そして、導電性ペーストを700℃以上900℃以下の温度で焼付けを行うことにより、外部電極12〜16の下地電極を形成する。導電性ペーストの材料としては、例えば、Cu,Ni,Ag,Pd,Ag−Pd合金,Au等が挙げられる。下地電極の厚さは、10μm以上50μm以下であることが好ましい。次に、下地電極上にめっきを施して外部電極12〜16を完成させる。めっき層の材料としては、例えば、Cu,Ni,Ag,Pd,Ag−Pd合金,Au等が挙げられる。また、複数回のめっきを行って、複数層のめっき層を下地電極上に形成してもよい。以上の工程により、電子部品10が完成する。

【0040】

(基板モジュールの構成)

次に、電子部品10を備えている基板モジュール40aについて図面を参照しながら説明する。図4(a)は、基板モジュール40aの断面構造図であり、図4(b)は、基板モジュール40aをz軸方向の正方向側から平面視した図である。図5は、図4の基板モジュール40aの等価回路図である。

【0041】

基板モジュール40aは、図4(a)に示すように、電子部品10及び回路基板51を備えている。回路基板51は、基板本体52、信号導体54、グランド電極55、ビアホール導体56及びグランド導体Gを含んでいる。

【0042】

基板本体52は、複数のセラミック層及び導体層が積層されてなる積層基板であり、その主面及び内部において電気回路を有している。信号導体54は、基板本体52のz軸方向の正方向側の主面上に設けられており、図4(b)に示すようにy軸方向に延在している。信号導体54のy軸方向の正方向側の端部には、図示しない入力ポートP1が設けられており、信号導体54のy軸方向の負方向側の端部には、図示しない出力ポートP2が設けられている。グランド電極55は、回路基板51のz軸方向の正方向側の主面上に設けられており、図4(b)に示すように、長方形状をなしている。

【0043】

グランド導体Gは、基板本体52内に設けられており、接地電位に保たれる。グランド導体Gは、図示しないグランドポートP3に接続されている。ビアホール導体56は、基板本体52内に設けられており、グランド電極55とグランド導体Gとを接続している。これにより、グランド電極55も接地電位に保たれる。

【0044】

電子部品10は、回路基板51に実装されている。より詳細には、外部電極12aは、はんだ60aにより、信号導体54に接続されている。また、外部電極12bは、はんだ60bにより、グランド電極55に接続されている。これにより、基板モジュール40aは、図5に示す回路構成を有するようになる。すなわち、信号導体54は、入力ポートP1と出力ポートP2とを接続している。そして、電子部品10は、信号導体54とグランドポートP3との間に設けられている。図5において、コンデンサC、抵抗R及びコイルLは、電子部品10が有している静電容量、電気抵抗及びインダクタを示している。基板モジュール40aが図5に示す構成を有することにより、高周波信号は、入力ポートP1から入力し、出力ポートP2から出力される。更に、入力ポートP1から入力した高周波信号の内、電子部品10の共振周波数の高周波信号は、出力ポートP2から出力せずに、グランドポートP3から出力する。なお、基板モジュール40aの回路構成は、図5に限らない。よって、基板モジュール40aにおいて、電子部品10が入力ポートP1と出力ポートP2との間に設けられていてもよい。

【0045】

(効果)

以上の電子部品10及び基板モジュール40aによれば、以下に説明するように、低ESL化を図ることができる。図6は、比較例に係る電子部品110の外観斜視図である。図7は、比較例に係る電子部品110の積層体111の分解斜視図である。比較例に係る電子部品110は、電子部品10において引き出し導体22〜25及び外部電極13〜16を取り除いたものである。そこで、電子部品110において電子部品10と同じ構成については、電子部品10の構成の参照符号に100を足した参照符号を付した。

【0046】

比較例に係る電子部品110が実装された基板モジュールでは、高周波信号は、信号導体から外部電極112aを介して電子部品110内に入力し、外部電極112bを介してグランド電極へと出力する。この際、高周波信号は、信号導体、外部電極112a、引き出し導体120、容量導体118、容量導体119、引き出し導体121、外部電極112b、グランド電極の順に流れる。すなわち、比較例に係る電子部品110が実装された基板モジュールでは、高周波信号は、1本の経路のみを流れる。

【0047】

一方、基板モジュール40aの電子部品10では、高周波信号は、信号導体54から外部電極12aを介して電子部品10内に入力し、外部電極12bを介してグランド電極55へと出力する。この際、高周波信号は、以下に説明する第1の経路及び第2の経路を流れる。

【0048】

第1の経路は、信号導体54、外部電極12a、引き出し導体20、容量導体18、容量導体19、引き出し導体21、外部電極12b、グランド電極55の順に高周波信号が流れる経路である。第2の経路は、信号導体54、外部電極12a、引き出し導体20、容量導体18、引き出し導体22,23、外部電極13,14、外部電極15,16、引き出し導体24,25、容量導体19、引き出し導体21、外部電極12b、グランド電極55の順に高周波信号が流れる経路である。ここで、第2の経路において、高周波信号は、外部電極13,14から外部電極15,16へと流れる場合には、外部電極13,14と外部電極15,16との間の誘電体内部を通過することにより、外部電極13,14から外部電極15,16へと通過する。

【0049】

以上のように、電子部品10が実装された基板モジュール40aでは、高周波信号は、並列に接続された第1の経路及び第2の経路を流れる。ここで、電子部品10の第1の経路は、電子部品110の経路と同じである。よって、電子部品10は、電子部品110に対して第2の経路が追加された構造を有している。そして、第1の経路のインダクタンス値L1と第2の経路のインダクタンス値L2との合成インダクタンス値LTは、以下の式(1)に示される。

【0050】

LT=L1・L2/(L1+L2)・・・(1)

【0051】

電子部品110の経路のインダクタンス値はL1である。よって、電子部品10の第1の経路及び第2の経路の合成インダクタンス値LTは、電子部品110の経路のインダクタンス値L1よりも小さくなる。すなわち、電子部品10は、電子部品110に比べて低ESL化が図られている。

【0052】

また、電子部品10において、低ESL化が図られることにより、共振周波数が高くなる。その結果、電子部品10の高周波特性が向上する。

【0053】

なお、高周波信号が外部電極13,14から外部電極15,16に流れるためには、側面S5において、外部電極13と外部電極15との間には、外部電極13,15の電位と異なる電位に保たれる外部電極が設けられていないことが好ましい。同様に、側面S6において、外部電極14と外部電極16との間には、外部電極14,16の電位と異なる電位に保たれる外部電極が設けられていないことが好ましい。

【0054】

また、高周波信号が外部電極13,14から外部電極15,16に流れるためには、外部電極13,14の間隔及び外部電極15,16の間隔は、できるだけ小さいことが好ましく、例えば、50μm以上200μmであることが好ましい。

【0055】

また、電子部品10では、回路基板51への実装の際にショートが発生することを抑制できる。より詳細には、特許文献1に記載の積層コンデンサ500では、外部電極512,514間が近接しているので、回路基板への実装時に、外部電極512と外部電極514との間がはんだによって接続されてしまうおそれがある。すなわち、積層コンデンサ500では、ショートが発生するおそれがある。

【0056】

一方、電子部品10では、外部電極12a,12bは、特許文献1に記載の積層コンデンサ500の外部電極512,514に比べて近接していない。その代わり、外部電極13と外部電極15とは近接している。同様に、外部電極14と外部電極16とは近接している。しかしながら、外部電極13〜16は、回路基板51に対してはんだ実装されない。そのため、外部電極13と外部電極15との間、及び、外部電極14と外部電極16との間がはんだにより接続される可能性が低い。よって、電子部品10では、回路基板51への実装の際にショートが発生することを抑制できる。

【0057】

また、電子部品10では、電子部品10を流れる高周波信号に損失が発生しにくい。より詳細には、電子部品10において、高周波信号は、x軸方向の正方向側に向かって流れる必要がある。ここで、電子部品10において、側面S5,S6において、端面S3と外部電極13,14との間に、外部電極13,14と異なる電位に保たれる外部電極が設けられていると、外部電極13,14から該外部電極に向かって(すなわち、x軸方向の負方向側に向かって)高周波信号が流れる。すなわち、高周波信号が流れるべき方向の反対方向に高周波信号が流れるようになり、損失が発生してしまう。そこで、電子部品10では、図1に示すように、側面S5,S6において、端面S3と外部電極13,14との間にはそれぞれ、外部電極13,14と異なる電位に保たれる外部電極が設けられていない。これにより、前記損失の発生が抑制される。なお、同じ理由により、側面S5,S6において、端面S4と外部電極15,16との間にはそれぞれ、外部電極15,16と異なる電位に保たれる外部電極が設けられていない。

【0058】

電子部品10では、デラミネーションの発生を抑制できる。より詳細には、電子部品において、積層体の角ではデラミネーションが発生しやすい。角に引き出し電極とセラミック層とが積層されていると、引き出し電極とセラミック層との間においてデラミネーションが特に発生しやすい。そこで、電子部品10では、引き出し導体20,21は、積層体10の角に引き出されていない。これにより、電子部品10では、デラミネーションの発生が抑制される。更に、電子部品10では、積層体11の角において、引き出し電極20,21が露出しないので、電子部品10の耐湿性が向上する。

【0059】

(第1の実験)

本願発明者は、電子部品10及び基板モジュール40aが奏する効果をより明確にするために、以下に説明する第1の実験を行った。具体的には、図4に示す基板モジュール40aのサンプル(以下、第1のサンプル)及び図6及び図7に示す電子部品110が図4の回路基板51に実装されてなる基板モジュールのサンプル(第2のサンプル)を作製した。そして、ネットワークアナライザ(アジレント社製8722D)を用いて、第1のサンプル及び第2のサンプルのESL、伝送特性(S21)を測定した。まず、第1のサンプル及び第2のサンプルの条件について説明する。

【0060】

寸法:2.096mm×1.290mm×0.793mm

静電容量:14pF

内部導体及び外部電極の材料:Cu

セラミック層の比誘電率(ε):27

内部導体の枚数:6

素子厚(内部導体30,31の間隔):122μm

外層厚み(内部導体30a,31cから積層体11の上面S1又は下面S2までの距離):88μm

【0061】

以上の条件の第1のサンプル及び第2のサンプルでは、ESLは以下の通りとなった。なお、ESLは0.5〜20GHzの周波数帯域で測定した。

【0062】

第1のサンプルのESL:465pH

第2のサンプルのESL:500pH

【0063】

よって、本実験により、電子部品10を備えた基板モジュール40aでは、電子部品110を備えた回路モジュールよりも、低ESL化が図られていることが分かる。

【0064】

図8は、第1のサンプル及び第2のサンプルの伝送特性(S21)を示したグラフである。縦軸は減衰量を示し、横軸は周波数を示している。

【0065】

図8によれば、第1のサンプルの自己共振周波数f1が、第2のサンプルの自己共振周波数f2よりも高くなっていることが分かる。具体的には、自己共振周波数f1は、1.975GHzであり、自己共振周波数f2は、1.905GHzである。よって、図8の実験結果によれば、基板モジュール40aの高周波特性は、電子部品110を備えた回路モジュールの高周波特性よりも優れていることが分かる。

【0066】

(第1の変形例)

次に、第1の変形例に係る基板モジュールについて図面を参照しながら説明する。図9は、基板モジュール40bの断面構造図である。

【0067】

基板モジュール40bは、外部電極15,16がグランド電極55にはんだ60cにより接続されている点において基板モジュール40aと相違する。その他の相違点は存在しないので、基板モジュール40bの構成のこれ以上の説明を省略する。

【0068】

基板モジュール40aでは、高周波信号は、第1の経路及び第2の経路を流れていた。一方、基板モジュール40bでは、高周波信号は、第1の経路及び第2の経路に加えて、以下に説明する第3の経路及び第4の経路を流れる。

【0069】

第3の経路は、信号導体54、外部電極12a、引き出し導体20、容量導体18、容量導体19、引き出し導体24,25、外部電極15,16、グランド電極55の順に高周波信号が流れる経路である。第4の経路は、信号導体54、外部電極12a、引き出し導体20、容量導体18、引き出し導体22,23、外部電極13,14、外部電極15,16、グランド電極55の順に高周波信号が流れる経路である。

【0070】

以上のように、基板モジュール40bでは、高周波信号は、第1の経路及び第2の経路に加えて、第3の経路及び第4の経路も流れるようになる。その結果、基板モジュール40bでは、基板モジュール40aよりも更に低ESL化が図られると共に、高周波特性が向上する。

【0071】

また、基板モジュール40bでは、外部電極13,14に近接している外部電極15,16がはんだ60cによりグランド電極55に接続されている。ただし、電子部品10の回路基板51への固定は、主に、外部電極12aと信号導体54との接続、及び、外部電極12bとグランド電極55との接続によって行われている。そのため、外部電極15,16は、グランド電極55に電気的に接続されていればよく、グランド電極55に強固に固定されている必要はない。したがって、はんだ60cの量は少なくてもよい。よって、はんだ60cにより、外部電極13,14と外部電極15,16とが接続される可能性は低い。すなわち、基板モジュール40bにおいても、電子部品10の回路基板51への実装の際にショートが発生することを抑制できる。

【0072】

(第2の変形例)

次に、第2の変形例に係る基板モジュールについて図面を参照しながら説明する。図10は、基板モジュール40cの断面構造図である。

【0073】

基板モジュール40cは、外部電極13,14が信号導体54にはんだ60dにより接続されている点において基板モジュール40bと相違する。その他の相違点は存在しないので、基板モジュール40cの構成のこれ以上の説明を省略する。

【0074】

基板モジュール40bでは、高周波信号は、第1の経路ないし第4の経路を流れていた。一方、基板モジュール40bでは、高周波信号は、第1の経路ないし第4の経路に加えて、以下に説明する第5の経路ないし第7の経路を流れる。

【0075】

第5の経路は、信号導体54、外部電極13,14、引き出し導体22,23、容量導体18、容量導体19、引き出し導体21、外部電極12b、グランド電極55の順に高周波信号が流れる経路である。第6の経路は、信号導体54、外部電極13,14、引き出し導体22,23、容量導体18、容量導体19、引き出し導体24,25、外部電極15,16、グランド電極55の順に高周波信号が流れる経路である。第7の経路は、信号導体54、外部電極13,14、外部電極15,16、グランド電極55の順に高周波信号が流れる経路である。

【0076】

以上のように、基板モジュール40cでは、高周波信号は、第1の経路ないし第4の経路に加えて、第5の経路ないし第7の経路も流れるようになる。その結果、基板モジュール40cでは、基板モジュール40cよりも更に低ESL化が図られると共に、高周波特性が向上する。

【0077】

また、基板モジュール40cでは、外部電極13,14がはんだ60dにより信号導体54に接続され、かつ、外部電極15,16がはんだ60cによりグランド電極55に接続されている。ただし、電子部品10の回路基板51への固定は、主に、外部電極12aと信号導体54との接続、及び、外部電極12bとグランド電極55との接続によって行われている。そのため、外部電極13,14は、信号導体54に接続されていればよく、信号導体54に強固に固定されている必要はない。同様に、外部電極15,16は、グランド電極55に電気的に接続されていればよく、グランド電極55に強固に固定されている必要はない。したがって、はんだ60c,60dの量は少なくてもよい。よって、はんだ60c,60dにより、外部電極13,14と外部電極15,16とが接続される可能性は低い。すなわち、基板モジュール40cにおいても、電子部品10の回路基板51への実装の際にショートが発生することを抑制できる。

【0078】

(第2の実験)

本願発明者は、電子部品10及び基板モジュール40b,40cが奏する効果をより明確にするために、以下に説明する第2の実験を行った。具体的には、図9に示す基板モジュール40bのサンプル(以下、第3のサンプル)及び図10に示す基板モジュール40cのサンプル(以下、第4のサンプル)を作製した。そして、第3のサンプル及び第4のサンプルのESL、伝送特性(S21)を測定した。第3のサンプル及び第4のサンプルの条件は、第1のサンプル及び第2のサンプルの条件と同じであるので、説明を省略する。

【0079】

第3のサンプル及び第4のサンプルでは、ESLは以下の通りとなった。

【0080】

第3のサンプルのESL:405pH

第4のサンプルのESL:355pH

【0081】

よって、本実験により、基板モジュール40b,40cでは、基板モジュール40aよりも更に低ESL化が図られていることが分かる。

【0082】

図11は、第1のサンプルないし第4のサンプルの伝送特性(S21)を示したグラフである。縦軸は減衰量を示し、横軸は周波数を示している。

【0083】

図11によれば、第3のサンプルの自己共振周波数f3が、第1のサンプルの自己共振周波数f1よりも高くなっていることが分かる。また、第4のサンプルの自己共振周波数f4が、第3のサンプルの自己共振周波数f3よりも高くなっていることが分かる。具体的には、自己共振周波数f4は、2.25GHzであり、自己共振周波数f3は、2.115GHzであり、自己共振周波数f1は、1.975GHzである。よって、図11の実験結果によれば、基板モジュール40b,40cの高周波特性は、基板モジュール40aの高周波特性よりも更に優れていることが分かる。

【0084】

(第2の実施形態)

以下に、第2の実施形態に係る電子部品10aの構成について図面を参照しながら説明する。図12は、第2の実施形態に係る電子部品10aの積層体11aの分解斜視図である。図13は、図12の電子部品10aの内部平面図である。なお、電子部品10aの外観斜視図は、電子部品10の外観斜視図と同じであるので、図1を援用する。

【0085】

積層体11aは、図12に示すように、セラミック層17i及び内部導体41,42を更に備えている。

【0086】

セラミック層17iは、図12に示すように、セラミック層17aとセラミック層17bとの間に設けられている。内部導体41,42は、セラミック層17iの表面上に設けられており、隙間を空けた状態でx軸方向の負方向側から正方向側へとこの順に並んでいる。

【0087】

内部導体41は、図12及び図13に示すように、容量導体43、引き出し導体44,47,48を備えている。容量導体43は、長方形状をなしており、セラミック層17iのx軸方向の負方向側の半分の領域内に設けられている。

【0088】

引き出し導体44は、図12及び図13に示すように、容量導体43に接続され、かつ、積層体11の端面S3に引き出されることにより端面S3から露出している。より詳細には、引き出し導体44は、容量導体43のx軸方向の負方向側の辺から、x軸方向の負方向側に向かって延在している。これにより、引き出し導体44は、セラミック層17iのx軸方向の負方向側の短辺に引き出され、外部電極12aに接続されている。

【0089】

引き出し導体47は、図12及び図13に示すように、容量導体43に接続され、かつ、積層体11の側面S5に引き出されることにより側面S5から露出している。より詳細には、引き出し導体47は、容量導体43のy軸方向の正方向側の辺から、y軸方向の正方向側に向かって引き出されている。これにより、引き出し導体47は、セラミック層17iのy軸方向の正方向側の長辺の中点よりx軸方向の負方向側の位置に引き出され、外部電極13に接続されている。

【0090】

引き出し導体48は、図12及び図13に示すように、容量導体43に接続され、かつ、積層体11の側面S6に引き出されることにより側面S6から露出している。より詳細には、引き出し導体48は、容量導体43のy軸方向の負方向側の辺から、y軸方向の負方向側に向かって引き出されている。これにより、引き出し導体48は、セラミック層17iのy軸方向の負方向側の長辺の中点よりx軸方向の負方向側の位置に引き出され、外部電極14と接続されている。

【0091】

内部導体42は、図12及び図13に示すように、容量導体45、引き出し導体46,49,50を備えている。容量導体45は、長方形状をなしており、セラミック層17iのx軸方向の正方向側の半分の領域内に設けられている。

【0092】

引き出し導体46は、図12及び図13に示すように、容量導体45に接続され、かつ、積層体11の端面S4に引き出されることにより端面S4から露出している。より詳細には、引き出し導体46は、容量導体45のx軸方向の正方向側の辺から、x軸方向の正方向側に向かって引き出されている。これにより、引き出し導体46は、セラミック層17iのx軸方向の正方向側の短辺に引き出され、外部電極12bに接続されている。

【0093】

引き出し導体49は、図12及び図13に示すように、容量導体45に接続され、かつ、積層体11の側面S5に引き出されることにより側面S5から露出している。より詳細には、引き出し導体49は、容量導体45のy軸方向の正方向側の辺から、y軸方向の正方向側に向かって延在している。これにより、引き出し導体49は、セラミック層17iのy軸方向の正方向側の長辺の中点よりx軸方向の正方向側の位置に引き出され、外部電極15に接続されている。

【0094】

引き出し導体50は、図12及び図13に示すように、容量導体45に接続され、かつ、積層体11の側面S6に引き出されることにより側面S6から露出している。より詳細には、引き出し導体50は、容量導体45のy軸方向の負方向側の辺から、y軸方向の負方向側に向かって引き出されている。これにより、引き出し導体50は、セラミック層17iのy軸方向の負方向側の長辺の中点よりx軸方向の正方向側の位置に引き出され、外部電極16と接続されている。

【0095】

以上のような積層体11aを備えた電子部品10では、第2の経路を流れる高周波信号の強度が強くなる。より詳細には、高周波信号は、信号導体54、外部電極12a、引き出し導体44、容量導体43、引き出し導体47,48、外部電極13,14、外部電極15,16、引き出し導体49,50、容量導体45、引き出し導体46、外部電極12b、グランド電極55の順に流れる。すなわち、高周波信号は、第2の経路と等価な経路を流れる。その結果、積層体11aを備えた電子部品10では、高周波特性が向上する。

【0096】

(第3の実施形態)

以下に、第3の実施形態に係る電子部品10bの構成について図面を参照しながら説明する。図14は、第3の実施形態に係る電子部品10bの内部平面図である。なお、電子部品10bの外観斜視図は、電子部品10の外観斜視図と同じであるので、図1を援用する。

【0097】

電子部品10bでは、図14に示すように、引き出し導体23,25が設けられていない点において電子部品10と相違する。この場合には、電子部品10bは、側面S5が回路基板51に対向するように実装される。電子部品10の上面S1及び下面S2には外部電極13〜16が設けられていないので、電子部品10のz軸方向における幅を小さくできる。その結果、電子部品10同士を近づけて配置することが可能となる。

【0098】

(第4の実施形態)

以下に、第4の実施形態に係る電子部品10cの構成について図面を参照しながら説明する。図15は、第4の実施形態に係る電子部品10cの内部平面図である。なお、電子部品10cの外観斜視図は、電子部品10の外観斜視図と同じであるので、図1を援用する。

【0099】

電子部品10cは、引き出し導体72(72a〜72c),73(73a〜73c),74(74a〜74c),75(75a〜75c)を備えている点において、電子部品10と相違する。

【0100】

引き出し導体72は、接続導体20に接続され、かつ、積層体11cの側面S5に引き出されることにより側面S5から露出している。より詳細には、引き出し導体72は、接続導体20のy軸方向の正方向側の辺の中点から、y軸方向の正方向側に向かって延在している。これにより、引き出し導体72は、セラミック層17のy軸方向の正方向側の長辺において引き出し導体22よりx軸方向の負方向側の位置に引き出され、外部電極12aに接続されている。

【0101】

引き出し導体73は、接続導体20に接続され、かつ、積層体11cの側面S6に引き出されることにより側面S6から露出している。より詳細には、引き出し導体73は、接続導体20のy軸方向の負方向側の辺の中点から、y軸方向の負方向側に向かって延在している。これにより、引き出し導体73は、セラミック層17のy軸方向の負方向側の長辺において引き出し導体23よりx軸方向の負方向側の位置に引き出され、外部電極12aに接続されている。

【0102】

引き出し導体74は、接続導体21に接続され、かつ、積層体11cの側面S5に引き出されることにより側面S5から露出している。より詳細には、引き出し導体74は、接続導体21のy軸方向の正方向側の辺の中点から、y軸方向の正方向側に向かって延在している。これにより、引き出し導体74は、セラミック層17のy軸方向の正方向側の長辺において引き出し導体24よりx軸方向の負方向側の位置に引き出され、外部電極12bに接続されている。

【0103】

引き出し導体75は、接続導体21に接続され、かつ、積層体11cの側面S6に引き出されることにより側面S6から露出している。より詳細には、引き出し導体75は、接続導体21のy軸方向の負方向側の辺の中点から、y軸方向の負方向側に向かって延在している。これにより、引き出し導体75は、セラミック層17のy軸方向の負方向側の長辺において引き出し導体25よりx軸方向の正方向側の位置に引き出され、外部電極12bに接続されている。

【0104】

電子部品10cでは、引き出し導体72〜75が設けられているので、電子部品10c内における電流経路が電子部品10内における電流経路よりも多くなる。その結果、電子部品10cでは、より効果的に低ESL化を図ることができる。

【0105】

なお、電子部品10cにおいて、引き出し導体72〜75は、セラミック層17の角には設けられていないことが好ましい。

【0106】

(第5の実施形態)

以下に、第5の実施形態に係る電子部品10dについて図面を参照しながら説明する。図16は、第5の実施形態に係る電子部品10dの外観斜視図である。

【0107】

図16に示すように、外部電極13と外部電極14とは、上面S1及び下面S2に設けられている外部電極によってつながっていてもよい。同様に、外部電極15と外部電極16とは、上面S1及び下面S2に設けられている外部電極によってつながっていてもよい。なお、電子部品10dの内部構造は、電子部品10,10a〜10cの内部構造のいずれであってもよい。

【0108】

(第6の実施形態)

以下に、第6の実施形態に係る電子部品10eについて図面を参照しながら説明する。図17は、第6の実施形態に係る電子部品10eの外観斜視図である。

【0109】

図17に示すように、外部電極13,15はそれぞれ、側面S5にのみ設けられ、上面S1及び下面S2に折り返されていなくてもよい。同様に、外部電極14,16はそれぞれ、側面S6にのみ設けられ、上面S1及び下面S2に折り返されていなくてもよい。

【0110】

外部電極13,15の間隔、及び、外部電極14,16の間隔を小さくする場合には、例えば、外部電極13〜16を直接めっきで形成することが考えられる。直接めっきでは、引き出し導体22〜25が露出した部分を覆うように外部電極13〜15が形成される。よって、この場合には、外部電極13〜15は、上面S1及び下面S2には形成されないことが多い。

【0111】

(その他の実施形態)

本発明に係る電子部品10,10a〜10e及び基板モジュール40a〜40cは、前記実施形態に示したものに限らず、その要旨の範囲内において変更可能である。

【0112】

なお、セラミック層17の代わりに、エポキシ樹脂、ポリプロピレン等の樹脂材料が用いられてもよい。

【産業上の利用可能性】

【0113】

以上のように、本発明は、電子部品及び基板モジュールに有用であり、特に、低ESL化を図ることができると共に、回路基板への実装の際にショートが発生することを抑制できる点において優れている。

【符号の説明】

【0114】

S1 上面

S2 下面

S3,S4 端面

S5,S6 側面

10,10a〜10e 電子部品

11,11a〜11e 積層体

12a,12b,13〜16 外部電極

17a〜17i セラミック層

18a〜18c,19a〜19c,43,45 容量導体

20a〜20c,21a〜21c,22a〜22c,23a〜23c,24a〜24c,25a〜25c,44,46〜50,72a〜72c,73a〜73c,74a〜74c,75a〜75c 引き出し導体

30a〜30c,31a〜31c,41,42 内部導体

40a〜40c 基板モジュール

51 回路基板

52 基板本体

54 信号導体

55 グランド電極

56 ビアホール導体

60a〜60d はんだ

【特許請求の範囲】

【請求項1】

複数の誘電体層が積層されてなる直方体状の積層体と、

前記誘電体層上に設けられている第1の容量導体と、

前記第1の容量導体に接続され、かつ、前記積層体の第1の端面に引き出されている第1の引き出し導体と、

前記第1の容量導体に接続され、かつ、前記積層体の第1の側面に引き出されている第3の引き出し導体と、

前記誘電体層上に設けられ、かつ、前記第1の容量導体と前記誘電体層を介して対向している第2の容量導体と、

前記第2の容量導体に接続され、かつ、前記積層体の第2の端面に引き出されている第2の引き出し導体と、

前記第2の容量導体に接続され、かつ、前記第1の側面に引き出されている第4の引き出し導体と、

前記第1の端面及び前記第2の端面のそれぞれと前記積層体の底面とに跨って設けられ、かつ、前記第1の引き出し導体及び前記第2の引き出し導体のそれぞれに接続されている第1の外部電極及び第2の外部電極と、

前記第1の側面に設けられ、かつ、前記第3の引き出し導体に接続されている第3の外部電極と、

前記第1の側面に設けられ、かつ、前記第4の引き出し導体に接続されている第4の外部電極と、

を備えており、

前記第1の側面において、前記第1の端面と前記第3の外部電極との間には、該第3の外部電極の電位と異なる電位に保たれる外部電極が設けられておらず、

前記第1の側面において、前記第2の端面と前記第4の外部電極との間には、該第4の外部電極の電位と異なる電位に保たれる外部電極が設けられていないこと、

を特徴とする電子部品。

【請求項2】

前記第1の側面において、前記第3の外部電極と前記第4の外部電極との間には、該第3の外部電極の電位及び該第4の外部電極の電位と異なる電位に保たれる外部電極が設けられていないこと、

を特徴とする請求項1に記載の電子部品。

【請求項3】

前記第1の容量導体に接続され、かつ、前記積層体の第2の側面に引き出されている第5の引き出し導体と、

前記第2の容量導体に接続され、かつ、前記第2の側面に引き出されている第6の引き出し導体と、

前記第2の側面に設けられ、かつ、前記第5の引き出し導体に接続されている第5の外部電極と、

前記第2の側面に設けられ、かつ、前記第6の引き出し導体に接続されている第6の外部電極と、

を更に備えており、

前記第2の側面において、前記第1の端面と前記第5の外部電極との間には、該第5の外部電極の電位と異なる電位に保たれる外部電極が設けられておらず、

前記第2の側面において、前記第2の端面と前記第6の外部電極との間には、該第6の外部電極の電位と異なる電位に保たれる外部電極が設けられていないこと、

を特徴とする請求項1又は請求項2のいずれかに記載の電子部品。

【請求項4】

第1のランド及び第2のランドを含んでいる回路基板と、

前記回路基板に実装される請求項1ないし請求項3のいずれかに記載の電子部品と、

を備えており、

前記第1の外部電極は、前記第1のランドに接続され、

前記第2の外部電極は、前記第2のランドに接続されていること、

を特徴とする基板モジュール。

【請求項5】

前記第4の外部電極は、前記第2のランドに接続されていること、

を特徴とする請求項4に記載の基板モジュール。

【請求項6】

前記第3の外部電極は、前記第1のランドに接続されていること、

を特徴とする請求項5に記載の基板モジュール。

【請求項1】

複数の誘電体層が積層されてなる直方体状の積層体と、

前記誘電体層上に設けられている第1の容量導体と、

前記第1の容量導体に接続され、かつ、前記積層体の第1の端面に引き出されている第1の引き出し導体と、

前記第1の容量導体に接続され、かつ、前記積層体の第1の側面に引き出されている第3の引き出し導体と、

前記誘電体層上に設けられ、かつ、前記第1の容量導体と前記誘電体層を介して対向している第2の容量導体と、

前記第2の容量導体に接続され、かつ、前記積層体の第2の端面に引き出されている第2の引き出し導体と、

前記第2の容量導体に接続され、かつ、前記第1の側面に引き出されている第4の引き出し導体と、

前記第1の端面及び前記第2の端面のそれぞれと前記積層体の底面とに跨って設けられ、かつ、前記第1の引き出し導体及び前記第2の引き出し導体のそれぞれに接続されている第1の外部電極及び第2の外部電極と、

前記第1の側面に設けられ、かつ、前記第3の引き出し導体に接続されている第3の外部電極と、

前記第1の側面に設けられ、かつ、前記第4の引き出し導体に接続されている第4の外部電極と、

を備えており、

前記第1の側面において、前記第1の端面と前記第3の外部電極との間には、該第3の外部電極の電位と異なる電位に保たれる外部電極が設けられておらず、

前記第1の側面において、前記第2の端面と前記第4の外部電極との間には、該第4の外部電極の電位と異なる電位に保たれる外部電極が設けられていないこと、

を特徴とする電子部品。

【請求項2】

前記第1の側面において、前記第3の外部電極と前記第4の外部電極との間には、該第3の外部電極の電位及び該第4の外部電極の電位と異なる電位に保たれる外部電極が設けられていないこと、

を特徴とする請求項1に記載の電子部品。

【請求項3】

前記第1の容量導体に接続され、かつ、前記積層体の第2の側面に引き出されている第5の引き出し導体と、

前記第2の容量導体に接続され、かつ、前記第2の側面に引き出されている第6の引き出し導体と、

前記第2の側面に設けられ、かつ、前記第5の引き出し導体に接続されている第5の外部電極と、

前記第2の側面に設けられ、かつ、前記第6の引き出し導体に接続されている第6の外部電極と、

を更に備えており、

前記第2の側面において、前記第1の端面と前記第5の外部電極との間には、該第5の外部電極の電位と異なる電位に保たれる外部電極が設けられておらず、

前記第2の側面において、前記第2の端面と前記第6の外部電極との間には、該第6の外部電極の電位と異なる電位に保たれる外部電極が設けられていないこと、

を特徴とする請求項1又は請求項2のいずれかに記載の電子部品。

【請求項4】

第1のランド及び第2のランドを含んでいる回路基板と、

前記回路基板に実装される請求項1ないし請求項3のいずれかに記載の電子部品と、

を備えており、

前記第1の外部電極は、前記第1のランドに接続され、

前記第2の外部電極は、前記第2のランドに接続されていること、

を特徴とする基板モジュール。

【請求項5】

前記第4の外部電極は、前記第2のランドに接続されていること、

を特徴とする請求項4に記載の基板モジュール。

【請求項6】

前記第3の外部電極は、前記第1のランドに接続されていること、

を特徴とする請求項5に記載の基板モジュール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2012−119663(P2012−119663A)

【公開日】平成24年6月21日(2012.6.21)

【国際特許分類】

【出願番号】特願2011−220587(P2011−220587)

【出願日】平成23年10月5日(2011.10.5)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成24年6月21日(2012.6.21)

【国際特許分類】

【出願日】平成23年10月5日(2011.10.5)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]