電子部品

【課題】積層体に大きなクラックが発生することを抑制できる電子部品を提供することである。

【解決手段】積層体11は、複数のセラミック層が積層されてなり、上面S1及び底面S2、並びに、互いに対向している2つの端面S3,S4を有している。コンデンサ導体層30,31は、セラミック層上に設けられており、コンデンサを構成している。外部電極12a,12bは、端面S3,S4を覆っていると共に、上面S1及び底面S2に折り返されている。ダミー導体層40,41は、コンデンサ導体30,31が設けられているセラミック層よりも底面S2の近くに位置しているセラミック層上に設けられており、z軸方向から平面視したときに、外部電極12a,12bにおける底面S2に折り返されている部分の先端Tb,Tdと重なっている。ダミー導体層40,41の厚みは、コンデンサ導体層30,31の厚みよりも大きい。

【解決手段】積層体11は、複数のセラミック層が積層されてなり、上面S1及び底面S2、並びに、互いに対向している2つの端面S3,S4を有している。コンデンサ導体層30,31は、セラミック層上に設けられており、コンデンサを構成している。外部電極12a,12bは、端面S3,S4を覆っていると共に、上面S1及び底面S2に折り返されている。ダミー導体層40,41は、コンデンサ導体30,31が設けられているセラミック層よりも底面S2の近くに位置しているセラミック層上に設けられており、z軸方向から平面視したときに、外部電極12a,12bにおける底面S2に折り返されている部分の先端Tb,Tdと重なっている。ダミー導体層40,41の厚みは、コンデンサ導体層30,31の厚みよりも大きい。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子部品に関し、より特定的には、コンデンサを内蔵している電子部品に関する。

【背景技術】

【0002】

従来の電子部品としては、例えば、特許文献1に記載のチップ型電子部品が知られている。図22は、特許文献1に記載のチップ型電子部品500の断面構造図である。

【0003】

チップ型電子部品500は、図22に示すように、積層体502、外部電極504a,504b、補強層506及びコンデンサCを備えている。積層体502は、複数のセラミック層が積層されて構成されており、直方体状をなしている。外部電極504a,504bはそれぞれ、積層体502の互いに対向する端面を覆うように設けられており、上面、下面及び側面に折り返されている。

【0004】

コンデンサCは、積層体502内に内蔵されており、複数のコンデンサ導体層がセラミック層と交互に積層されて構成されている。補強層506は、積層体502に内蔵されており、コンデンサCよりも積層方向の上側及び下側に設けられている。補強層506は、積層方向から平面視したときに、外部電極504a,504bの端部と重なっている。

【0005】

以上のように構成されたチップ型電子部品500では、曲げや引っ張り等の機械的応力に対する耐久性が高い。より詳細には、回路基板に実装後、回路基板を分割する場合があるが、その際、チップ型電子部品に曲げ応力が加わって、外部電極504aと504b近傍にクラックが形成される。しかし、チップ型電子部品500では、補強層506が設けられているため、外部電極504a,504b近傍にクラックが形成されたとしても、補強層506でクラックの伸展を抑制している。すなわち、チップ型電子部品500では、曲げや引っ張り等の機械的応力に対する耐久性が高い。

【0006】

しかしながら、チップ型電子部品500では、依然として、積層体502にクラックが形成され、クラックがコンデンサ導体層に到達する場合がある。なぜなら、チップ型電子部品500では、コンデンサ電極に加えて補強層506を持つため、電極枚数が増加し構造欠陥が発生し易くなるため、補強層506及びコンデンサ導体層の厚みを薄く形成する必要がある。このように補強層506及びコンデンサ導体層を薄く形成すると、補強層506及びコンデンサ導体層には、空孔が多く形成されることになるため、補強層506を避けて空孔を通過するようにクラックがコンデンサ導体層近くまで伸展する。その結果、クラックを通して水分がコンデンサ導体層に侵入し、コンデンサとしての信頼性を低下させてしまうことになる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2002−75780号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

そこで、本発明の目的は、ダミー導体層を超えてコンデンサ導体近くにまでクラックが到達することを抑制できる電子部品を提供することである。

【課題を解決するための手段】

【0009】

本発明の一形態に係る電子部品によれば、複数の誘電体層が積層されてなる積層体であって、積層方向の両端に位置し互いに対向している上面及び底面、互いに対向している2つの側面、並びに、互いに対向している2つの端面を有している直方体状の積層体と、前記誘電体層上に設けられているコンデンサ導体層であって、コンデンサを構成しているコンデンサ導体層と、前記端面を覆っていると共に、前記上面及び前記底面に折り返されている外部電極と、前記複数のコンデンサ導体が設けられている前記誘電体層よりも前記底面の近くに位置している前記誘電体層上に設けられているダミー導体層であって、積層方向から平面視したときに、前記外部電極における該底面に折り返されている部分の先端と重なっているダミー導体層と、を備えており、前記ダミー導体層の厚みは、前記コンデンサ導体層の厚みよりも大きいこと、を特徴とする。

【発明の効果】

【0010】

本発明によれば、ダミー導体層を超えてコンデンサ導体近くにまでクラックが到達することを抑制できる。

【図面の簡単な説明】

【0011】

【図1】一実施形態に係る電子部品の外観斜視図である。

【図2】図1の電子部品の積層体の分解斜視図である。

【図3】図1の電子部品の断面構造図である。

【図4】比較例に用いた電子部品の断面構造図である。

【図5】解析結果を示したグラフである。

【図6】第1の変形例に係る電子部品の断面構造図である。

【図7】第2の変形例に係る電子部品の断面構造図である。

【図8】第3の変形例に係る電子部品の断面構造図である。

【図9】第4の変形例に係る電子部品の断面構造図である。

【図10】第5の変形例に係る電子部品の内部平面図である。

【図11】第6の変形例に係る電子部品の内部平面図である。

【図12】第7の変形例に係る電子部品の内部平面図である。

【図13】第8の変形例に係る電子部品の内部平面図である。

【図14】第9の変形例に係る電子部品の断面構造図である。

【図15】第9の変形例に係る電子部品の内部平面図である。

【図16】第10の変形例に係る電子部品の断面構造図である。

【図17】第11の変形例に係る電子部品の断面構造図である。

【図18】第12の変形例に係る電子部品の内部平面図である。

【図19】第13の変形例に係る電子部品の内部平面図である。

【図20】第14の変形例に係る電子部品の内部平面図である。

【図21】第15の変形例に係る電子部品の内部平面図である。

【図22】特許文献1に記載のチップ型電子部品の断面構造図である。

【発明を実施するための形態】

【0012】

以下に、本発明の実施形態に係る電子部品について図面を参照しながら説明する。

【0013】

(電子部品の構成)

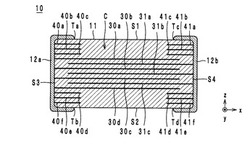

まず、一実施形態に係る電子部品の構成について図面を参照しながら説明する。図1は、一実施形態に係る電子部品10の外観斜視図である。図2は、図1の電子部品10の積層体11の分解斜視図である。図2では、セラミック層17g〜17iについては省略してある。図3は、図1の電子部品の断面構造図である。以下では、積層体11の積層方向をz軸方向と定義する。積層体11をz軸方向から平面視したときに、積層体11の長辺が延在している方向をx軸方向と定義する。積層体11をz軸方向から平面視したときに、積層体11の短辺が延在している方向をy軸方向と定義する。

【0014】

電子部品10は、チップコンデンサであり、図1ないし図3に示すように、積層体11、外部電極12(12a,12b)、コンデンサ導体層30(30a〜30d),31(31a〜31c)(図1には図示せず)及びダミー導体層40(40a〜40f),41(41a〜41f)(図1には図示せず)を備えている。

【0015】

積層体11は、z軸方向の両端に位置している上面S1及び底面S2、互いに対向している端面S3,S4、並びに、互いに対向している側面S5,S6を有する直方体状をなしている。ただし、積層体11は、面取りが施されることにより角及び稜線において丸みを帯びた形状をなしている。以下では、積層体11において、z軸方向の正方向側の面を上面S1とし、z軸方向の負方向側の面を底面S2とする。また、x軸方向の負方向側の面を端面S3とし、x軸方向の正方向側の面を端面S4とする。また、y軸方向の正方向側の面を側面S5とし、y軸方向の負方向側の面を側面S6とする。底面S2は、電子部品10が回路基板に実装される際に、該回路基板の主面と対向する実装面である。

【0016】

積層体11は、図2に示すように、複数のセラミック層(誘電体層)17(17a〜17o)がz軸方向の正方向側から負方向側へとこの順に並ぶように積層されることにより構成されている。セラミック層17は、長方形状をなしており、BaTiO3を主成分としBi2O3を含む誘電体セラミックにより作製されている。以下では、セラミック層17のz軸方向の正方向側の主面を表面と称し、セラミック層17のz軸方向の負方向側の主面を裏面と称す。

【0017】

積層体11の上面S1は、z軸方向の最も正方向側に設けられているセラミック層17aの表面により構成されている。積層体11の底面S2は、z軸方向の最も負方向側に設けられているセラミック層17oの裏面により構成されている。また、端面S3は、セラミック層17a〜17oのx軸方向の負方向側の短辺が連なることによって構成されている。端面S4は、セラミック層17a〜17oのx軸方向の正方向側の短辺が連なることによって構成されている。側面S5は、セラミック層17a〜17oのy軸方向の正方向側の長辺が連なることによって構成されている。側面S6は、セラミック層17a〜17oのy軸方向の負方向側の長辺が連なることによって構成されている。

【0018】

コンデンサ導体層30a〜30d,31a〜31cは、Al、Ni,Cuなどを主成分とする材料により作製されている導体層であり、セラミック層17を介して互いに対向することによってコンデンサを構成している。

【0019】

コンデンサ導体層30a〜30dはそれぞれ、図2及び図3に示すように、セラミック層17e,17g,17i,17kの表面上に設けられており、積層体11に内蔵されている。コンデンサ導体層30a〜30dは、長方形状をなしており、セラミック層17e,17g,17i,17kのx軸方向の負方向側の短辺に引き出されている。

【0020】

コンデンサ導体層31a〜31cはそれぞれ、図2及び図3に示すように、セラミック層17f,17h,17jの表面上に設けられており、積層体11に内蔵されている。コンデンサ導体層31a〜31cは、長方形状をなしており、セラミック層17f,17h,17jのx軸方向の正方向側の短辺に引き出されている。コンデンサ導体層30a〜30dとコンデンサ導体層31a〜31cとは、z軸方向から平面視したときに、重なりあっている。これにより、コンデンサ導体層30,31間にはコンデンサCが形成されている。

【0021】

外部電極12a,12bは、Ag、Cu、Niペーストが塗布されて形成される電極である。外部電極12aは、端面S3を覆っていると共に、上面S1、底面S2及び側面S5,S6とに折り返されている。また、外部電極12aは、コンデンサ導体層30a〜30dに接続されている。より詳細には、外部電極12aは、コンデンサ導体層30a〜30dが端面S3から露出している部分を覆うように、積層体11の端面S3の全面を覆っている。

【0022】

外部電極12bは、端面S4を覆っていると共に、上面S1、底面S2及び側面S5,S6とに折り返されている。また、外部電極12bは、コンデンサ導体層31a〜31cに接続されている。より詳細には、外部電極12bは、コンデンサ導体層31a〜31cが端面S4から露出している部分を覆うように、積層体11の端面S4の全面を覆っている。

【0023】

ダミー導体層40a〜40f,41a〜41fは、Al、Ni、Cuを主成分とする材料により作製されている導体層である。ダミー導体層40a〜40c,41a〜41cはそれぞれ、コンデンサ導体層30a〜30d,31a〜31cが設けられているセラミック層17e〜17kよりも上面S1の近くに位置しているセラミック層17b〜17dの表面上に設けられている。ダミー導体層40d〜40f,41d〜41fはそれぞれ、コンデンサ導体層30a〜30d,31a〜31cが設けられているセラミック層17e〜17kよりも底面S2の近くに位置しているセラミック層17l〜17nの表面上に設けられている。

【0024】

ダミー導体層40a〜40fは、長方形状をなしており、セラミック層17b〜17d,17l〜17nのx軸方向の負方向側の短辺に引き出されている。これにより、ダミー導体層40a〜40fは、外部電極12aに接続されている。また、ダミー導体層40a〜40cは、z軸方向から平面視したときに、図3に示すように、外部電極12aにおける上面S1に折り返されている部分の先端Taと重なっている。ダミー導体層40d〜40fは、z軸方向から平面視したときに、図3に示すように、外部電極12aにおける底面S2に折り返されている部分の先端Tbと重なっている。

【0025】

ダミー導体層41a〜41fは、長方形状をなしており、セラミック層17b〜17d,17l〜17nのx軸方向の正方向側の短辺に引き出されている。これにより、ダミー導体層41a〜41fは、外部電極12bに接続されている。また、ダミー導体層41a〜41cは、z軸方向から平面視したときに、図3に示すように、外部電極12bにおける上面S1に折り返されている部分の先端Tcと重なっている。ダミー導体層41d〜41fは、z軸方向から平面視したときに、図3に示すように、外部電極12bにおける底面S2に折り返されている部分の先端Tdと重なっている。

【0026】

ところで、電子部品10では、クラックがコンデンサ導体層へ到達することを抑制するため、ダミー導体層40,41の空孔量を減らし、カバレッジを増加させている。ダミー導体層40,41のカバレッジは、70%以上100%以下であることが好ましい。複数枚のダミー導体層を有する場合は、すべて上記範囲内であることが好ましい。また、積層体11の構造欠陥を防止するため、コンデンサ導体層30,31は薄く、カバレッジは60%以上70%未満であることが好ましい。

【0027】

カバレッジは、コンデンサ導体層30,31及びダミー導体層40,41をz軸方向から平面視したときに、コンデンサ導体層30,31及びダミー導体層40,41の面積に対するコンデンサ導体層30,31及びダミー導体層40,41に形成されている空孔の面積の割合を100%から減算した値である。ダミー導体層が複数枚ある場合は、各層の平均値とする。カバレッジの測定は、以下の手順により行われる。

【0028】

まず、電子部品10のセラミック層17を剥離して、コンデンサ導体層30,31及びダミー導体層40,41を露出させて、SEMにより撮影を行う。SEMにより得られた画像に2値化処理を施して、コンデンサ導体層30,31及びダミー導体層40,41の隙間(空孔)から見えるセラミック層17の面積を求める。そして、コンデンサ導体層30,31及びダミー導体層40,41の隙間(空孔)から見えるセラミック層17の面積をコンデンサ導体層30,31及びダミー導体層40,41の面積で割って100を掛けた値を100%から減算する。これにより、カバレッジが算出される。

【0029】

(電子部品の製造方法)

次に、電子部品10の製造方法について説明する。なお、図面は、図1ないし図3を援用する。

【0030】

まず、BaTiO3、Bi2O3、BaCO3の原料粉末に対して、ポリビニルブチラール系バインダ及びエタノール等の有機溶剤を加えてボールミルに投入し、湿式調合を行って、セラミックスラリーを得る。原料粉末は、BaTiO3が100モル部、Bi2O3が3モル部、BaCO3が2モル部の割合で混合されて構成されている。得られたセラミックスラリーをドクターブレード法により、キャリアシート上にシート状に形成して乾燥させ、セラミック層17となるべきセラミックグリーンシートを作製する。セラミック層17となるべきセラミックグリーンシートの厚さは、例えば、6μmである。

【0031】

次に、セラミック層17となるべきセラミックグリーンシート上に、導電性材料からなるペーストをスクリーン印刷法で塗布することにより、コンデンサ導体層30,31及びダミー導体層40,41を形成する。導電性材料からなるペーストは、金属粉末に、有機バインダ及び有機溶剤が加えられたものである。金属粉末は、Al、Cu、Niである。コンデンサ導体層30,31の厚さは、0.1μm以上2.0μm以下である。ダミー導体層40,41の厚さは、0.1μm以上10.0μm以下である。

【0032】

次に、セラミック層17となるべきセラミックグリーンシートを積層して未焼成のマザー積層体を得る。この後、未焼成のマザー積層体に対して、静水圧プレスにて圧着を施す。

【0033】

次に、未焼成のマザー積層体を所定寸法にカットして、複数の未焼成の積層体11を得る。この後、積層体11の表面に、バレル研磨加工等の研磨加工を施す。

【0034】

次に、未焼成の積層体11を大気中で270℃に加熱して、未焼成の積層体11中のバインダを燃焼させる。更に、未焼成の積層体11を焼成する。焼成温度は、例えば、650℃である。

【0035】

次に、積層体11に外部電極12を形成する。具体的には、公知のディップ法やスリット工法等により、積層体11の表面にBi2O3−SiO2−BaO系ガラスフリットを含有するAgペーストを塗布する。そして、大気中でAg、Cu、Niペーストを600〜900℃で焼付けを行うことにより、外部電極12を形成する。以上の工程により、電子部品10が完成する。

【0036】

(効果)

以上の電子部品10によれば、以下に説明するように、カバレッジが高く空孔が少なくカバレッジが高いため、積層体11にクラックが形成されても、ダミー導体層によってコンデンサ導体層付近にまでクラックが到達することが抑制され、水分が侵入せずにコンデンサとして信頼性を高めることが可能になる。

【0037】

電子部品10では、ダミー導体層40d〜40f,41d〜41fはそれぞれ、コンデンサ導体層30a〜30d,31a〜31cが設けられているセラミック層17e〜17kよりも底面S2の近くに位置しているセラミック層17l〜17nの表面上に設けられている。更に、ダミー導体層40d〜40fは、z軸方向から平面視したときに、図3に示すように、外部電極12aにおける底面S2に折り返されている部分の先端Tbと重なっている。ダミー導体層41d〜41fは、z軸方向から平面視したときに、図3に示すように、外部電極12bにおける底面S2に折り返されている部分の先端Tdと重なっている。更に、ダミー導体層40,41のz軸方向の厚みは、コンデンサ導体層30,31のz軸方向の厚みよりも大きい。これにより、基板分割工程時に、電子部品10及び回路基板に歪みが発生して外部電極12a,12bが引っ張られることにより、先端Tb,Tdからz軸方向の正方向側に向かって延びるクラックが発生したとしても、ダミー導体層40、41において、厚みが大きい(すなわち、カバレッジが高い)ため、該クラックは、ダミー導体層40f,41fよりz軸方向の正方向側に進行することが抑制される。その結果、積層体11にコンデンサ導体層30,31へ到達するほどのクラックが形成されることが抑制される。

【0038】

また、電子部品10では、ダミー導体層40,41が厚く形成され、コンデンサ導体層30,31は厚く形成されない。そのため、積層体11の構造欠陥を防止できる。

【0039】

また、外部電極12a,12bには、めっきが施されている。そのため、めっき処理の際に、積層体11内にめっき液が侵入するおそれがある。しかしながら、電子部品10では、ダミー導体層40,41のカバレッジが高いので、積層体11内にめっき液が侵入することが抑制される。

【0040】

また、セラミック層17の破壊靭性値は、3MPa√m〜7MPa√mである。一方、カバレッジの高いダミー導体層40,41の破壊靭性値は、セラミック層7の破壊靭性値の10倍以上である。したがって、電子部品10において、破損しやすい先端Tb,Td近傍にダミー導体層40,41が設けられることにより、積層体11の破損が抑制される。

【0041】

また、電子部品10では、外部電極12a,12bの先端Ta〜Tdがダミー導体層40,41と同電位で、かつ、ダミー導体層40,41のカバレッジが高くなっているために、外部電極12a,12bの先端Ta〜Tdから流れる漏れ電流がコンデンサ導体層30,31に入力することが抑制される。

【0042】

(シミュレーション結果)

本願発明者は、電子部品10が奏する効果をより明確にするために、以下に説明するシミュレーションを行った。図4は、比較例に用いた電子部品110の断面構造図である。

【0043】

本願発明者は、電子部品10の構成を有する第1のモデル及び電子部品110の構成を有する第2のモデルを作成した。第1のモデルと第2のモデルとの相違点は、ダミー導体層40,41の有無である。そして、第1のモデル及び第2のモデルにおいて、外部電極12bの先端Tdで発生したクラックの進行を解析した。図5は、解析結果を示したグラフである。横軸は、x座標を示し、縦軸は、z座標を示している。x座標の原点は端面S3であり、及びz座標の原点は上面S1である。

【0044】

図5によれば、第2のモデルでは、第1のモデルでダミー導体層41が設けられている位置を通過してz軸方向の正方向側に進行していることが分かる。一方、第1のモデルでは、クラックは、ダミー導体層41が設けられている位置において、z軸方向の正方向側への進行をやめて、ダミー導体層41に沿ってx軸方向の正方向側へと進行していることが分かる。すなわち、クラックは、残留応力が高い部分を進行している。本シミュレーションによれば、カバレッジが高く厚みの大きいダミー導体層40,41が設けられることにより残留応力が高くなり、大きなクラックの進行方向を制御できていることが分かる。

【0045】

(第1の変形例)

以下に、第1の変形例に係る電子部品10aについて図面を参照しながら説明する。図6は、第1の変形例に係る電子部品10aの断面構造図である。

【0046】

図6に示すように、ダミー導体層40,41は、上面S1及び底面S2の近傍に設けられていてもよい。すなわち、ダミー導体層40,41は、コンデンサ導体層30,31から離されて設けられている。これにより、ダミー導体層40,41とコンデンサ導体層30,31との間において静電容量が発生することが抑制される。その結果、電子部品10aでは、目標の静電容量値を得るための設計が容易となる。

【0047】

また、ダミー導体層40,41がコンデンサ導体層30,31から離れていると、ダミー導体層40,41とコンデンサ導体層30,31との間に発生する静電容量が小さくなるので、ダミー導体層40,41に積みずれが発生しても、該静電容量の変動値が小さくて済む。その結果、電子部品10aでは、目標の静電容量値を得るための設計が容易となる。

【0048】

(第2の変形例)

以下に、第2の変形例に係る電子部品10bについて図面を参照しながら説明する。図7は、第2の変形例に係る電子部品10bの断面構造図である。

【0049】

図7に示すように、ダミー導体層40,41は、コンデンサ導体層30,31の近傍に設けられていてもよい。すなわち、ダミー導体層40,41は、上面S1及び底面S2から離されて設けられている。これにより、積層体11のz軸方向の両端にダミー導体層40,41が位置しなくなる。その結果、積層体11において、ダミー導体層40,41とセラミック層17との間で相関剥離が発生することが抑制される。

【0050】

(第3の変形例及び第4の変形例)

以下に、第3の変形例に係る電子部品10c及び第4の変形例に係る電子部品10dについて図面を参照しながら説明する。図8は、第3の変形例に係る電子部品10cの断面構造図である。図9は、第4の変形例に係る電子部品10dの断面構造図である。

【0051】

図8及び図9に示すように、ダミー導体層40,41のx軸方向の端部は、揃っていなくてもよい。なお、電子部品10cにおいて、z軸方向の正方向側から平面視したときに、外部電極12a,12bの先端Ta〜Tdと重なっているダミー導体層は、ダミー導体層40c,40d,41c,41dである。同様に、電子部品10dにおいて、z軸方向の正方向側から平面視したときに、外部電極12a,12bの先端Ta〜Tdと重なっているダミー導体層は、ダミー導体層40a,40f,41a,41fである。

【0052】

(第5の変形例及び第6の変形例)

以下に、第5の変形例に係る電子部品10e及び第6の変形例に係る電子部品10fについて図面を参照しながら説明する。図10は、第5の変形例に係る電子部品10eの内部平面図である。図11は、第6の変形例に係る電子部品10fの内部平面図である。

【0053】

図10及び図11に示すように、ダミー導体層40は、外部電極12aの端面S3に形成されている部分のみならず、外部電極12aの側面S5,S6に形成されている部分にも接続されていてもよい。同様に、ダミー導体層41は、外部電極12bの端面S4に形成されている部分のみならず、外部電極12bの側面S5,S6に形成されている部分にも接続されていてもよい。

【0054】

以上のような構成を有する電子部品10e,10fでは、ダミー導体層40,41のy軸方向の幅が広くなる。これにより、側面S5又は側面S6が実装面として用いられて電子部品10e,10fが回路基板に実装されたとしても、積層体11にクラックが発生することを抑制することが可能となる。

【0055】

(第7の変形例及び第8の変形例)

以下に、第7の変形例に係る電子部品10g及び第8の変形例に係る電子部品10hについて図面を参照しながら説明する。図12は、第7の変形例に係る電子部品10gの内部平面図である。図13は、第8の変形例に係る電子部品10hの内部平面図である。

【0056】

図12及び図13に示すように、ダミー導体層40,41は、複数に分割されていてもよい。

【0057】

(第9の変形例)

以下に、第9の変形例に係る電子部品10iについて図面を参照しながら説明する。図14は、第9の変形例に係る電子部品10iの断面構造図である。図15は、第9の変形例に係る電子部品10iの内部平面図である。

【0058】

図14及び図15に示すように、ダミー導体層40,41は、外部電極12a,12bに接続されていなくてもよい。

【0059】

以上のように、ダミー導体層40,41が外部電極12a,12bに接続されないことにより、ダミー導体層40,41の面積が小さくなる。その結果、ダミー導体層40,41が設けられているセラミック層17間において層間剥離が発生することが抑制される。

【0060】

また、ダミー導体層40,41が外部電極12a,12bに接続されないことにより、積層体11の端面S3,S4及び側面S5,S6にダミー導体層40,41が露出しなくなる。そのため、積層体11のカット時やバレル時に、ダミー導体層40,41が設けられているセラミック層17間において層間剥離が発生することが抑制される。更に、ダミー導体層40,41が設けられているセラミック層17間から水分が侵入することが抑制される。

【0061】

(第10の変形例)

以下に、第10の変形例に係る電子部品10jについて図面を参照しながら説明する。図16は、第10の変形例に係る電子部品10jの断面構造図である。

【0062】

図16に示すように、ダミー導体層40,41は、上面S1及び底面S2の近傍に設けられていてもよい。これにより、第1の変形例に係る電子部品10aと同様に、電子部品10jでは、目標の静電容量値を得るための設計が容易となる。

【0063】

(第11の変形例)

以下に、第11の変形例に係る電子部品10kについて図面を参照しながら説明する。図17は、第11の変形例に係る電子部品10kの断面構造図である。

【0064】

図17に示すように、ダミー導体層40,41は、コンデンサ導体層30,31の近傍に設けられていてもよい。これにより、第2の変形例に係る電子部品10bと同様に、電子部品10kでは、積層体11において、ダミー導体層40,41とセラミック層17との間で相関剥離が発生することが抑制される。

【0065】

(第12の変形例及び第13の変形例)

以下に、第12の変形例に係る電子部品10l及び第13の変形例に係る電子部品10mについて図面を参照しながら説明する。図18は、第12の変形例に係る電子部品10lの内部平面図である。図19は、第13の変形例に係る電子部品10mの内部平面図である。

【0066】

図18及び図19に示すように、ダミー導体層40は、外部電極12aの側面S5,S6に形成されている部分においてのみ接続されていてもよい。同様に、ダミー導体層41は、外部電極12bの側面S5,S6に形成されている部分においてのみ接続されていてもよい。

【0067】

(第14の変形例及び第15の変形例)

以下に、第14の変形例に係る電子部品10n及び第15の変形例に係る電子部品10oについて図面を参照しながら説明する。図20は、第14の変形例に係る電子部品10nの内部平面図である。図21は、第15の変形例に係る電子部品10oの内部平面図である。

【0068】

図20及び図21に示すように、ダミー導体層40,41は、複数に分割されていてもよい。

【0069】

(その他の実施形態)

以上のように構成された電子部品は、前記実施形態に係る電子部品10,10a〜10oに限らず、その要旨の範囲内において変更可能である。

【0070】

電子部品10の製造方法では、ダミー導体層40,41は、印刷法により形成されるとしたが、他の方法によって形成されてもよい。他の方法とは、例えば、金属箔をセラミックグリーンシートに貼り付けてダミー導体層40,41を形成する方法や、射出成形によってダミー導体層40,41を形成する方法等が挙げられる。

【0071】

まず、金属箔をセラミックグリーンシートに貼り付けてダミー導体層40,41を形成する方法について説明する。

【0072】

金属箔をフィルムに静電気により貼りつける。次に、セラミックグリーンシートのダミー導体層40,41を形成する部分に接着剤を印刷する。金属箔が貼り付けられたフィルムをセラミックグリーンシートに貼り合わせ、フィルムのみをセラミックグリーンシートから剥離する。これにより、ダミー導体層40,41が形成される。

【0073】

また、金属箔をセラミックグリーンシートに貼り付けてダミー導体層40,41を形成する方法は、以下の射出成型によって実現されてもよい。

【0074】

具体的には、セラミックグリーンシートのダミー導体層40,41を形成する部分に、カーボン入りのセラミックペーストを印刷し積層、カット、焼成する。カーボン入りの部分にセラミックペーストを塗った部分が焼失し、空洞となる。その空洞に金属ペーストを注入することによりダミー導体層40,41を形成する。

【産業上の利用可能性】

【0075】

以上のように、本発明は、電子部品に有用であり、特に、ダミー導体層を超えてコンデンサ導体近くにまでクラックが到達することを抑制できる点で優れている。

【符号の説明】

【0076】

S1 上面

S2 底面

S3,S4 端面

S5,S6 側面

Ta〜Td 先端

10,10a〜10o 電子部品

11 積層体

12a,12b 外部電極

17a〜17o セラミック層

30a〜30d,31a〜31c コンデンサ導体層

40a〜40f,41a〜41f ダミー導体層

【技術分野】

【0001】

本発明は、電子部品に関し、より特定的には、コンデンサを内蔵している電子部品に関する。

【背景技術】

【0002】

従来の電子部品としては、例えば、特許文献1に記載のチップ型電子部品が知られている。図22は、特許文献1に記載のチップ型電子部品500の断面構造図である。

【0003】

チップ型電子部品500は、図22に示すように、積層体502、外部電極504a,504b、補強層506及びコンデンサCを備えている。積層体502は、複数のセラミック層が積層されて構成されており、直方体状をなしている。外部電極504a,504bはそれぞれ、積層体502の互いに対向する端面を覆うように設けられており、上面、下面及び側面に折り返されている。

【0004】

コンデンサCは、積層体502内に内蔵されており、複数のコンデンサ導体層がセラミック層と交互に積層されて構成されている。補強層506は、積層体502に内蔵されており、コンデンサCよりも積層方向の上側及び下側に設けられている。補強層506は、積層方向から平面視したときに、外部電極504a,504bの端部と重なっている。

【0005】

以上のように構成されたチップ型電子部品500では、曲げや引っ張り等の機械的応力に対する耐久性が高い。より詳細には、回路基板に実装後、回路基板を分割する場合があるが、その際、チップ型電子部品に曲げ応力が加わって、外部電極504aと504b近傍にクラックが形成される。しかし、チップ型電子部品500では、補強層506が設けられているため、外部電極504a,504b近傍にクラックが形成されたとしても、補強層506でクラックの伸展を抑制している。すなわち、チップ型電子部品500では、曲げや引っ張り等の機械的応力に対する耐久性が高い。

【0006】

しかしながら、チップ型電子部品500では、依然として、積層体502にクラックが形成され、クラックがコンデンサ導体層に到達する場合がある。なぜなら、チップ型電子部品500では、コンデンサ電極に加えて補強層506を持つため、電極枚数が増加し構造欠陥が発生し易くなるため、補強層506及びコンデンサ導体層の厚みを薄く形成する必要がある。このように補強層506及びコンデンサ導体層を薄く形成すると、補強層506及びコンデンサ導体層には、空孔が多く形成されることになるため、補強層506を避けて空孔を通過するようにクラックがコンデンサ導体層近くまで伸展する。その結果、クラックを通して水分がコンデンサ導体層に侵入し、コンデンサとしての信頼性を低下させてしまうことになる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2002−75780号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

そこで、本発明の目的は、ダミー導体層を超えてコンデンサ導体近くにまでクラックが到達することを抑制できる電子部品を提供することである。

【課題を解決するための手段】

【0009】

本発明の一形態に係る電子部品によれば、複数の誘電体層が積層されてなる積層体であって、積層方向の両端に位置し互いに対向している上面及び底面、互いに対向している2つの側面、並びに、互いに対向している2つの端面を有している直方体状の積層体と、前記誘電体層上に設けられているコンデンサ導体層であって、コンデンサを構成しているコンデンサ導体層と、前記端面を覆っていると共に、前記上面及び前記底面に折り返されている外部電極と、前記複数のコンデンサ導体が設けられている前記誘電体層よりも前記底面の近くに位置している前記誘電体層上に設けられているダミー導体層であって、積層方向から平面視したときに、前記外部電極における該底面に折り返されている部分の先端と重なっているダミー導体層と、を備えており、前記ダミー導体層の厚みは、前記コンデンサ導体層の厚みよりも大きいこと、を特徴とする。

【発明の効果】

【0010】

本発明によれば、ダミー導体層を超えてコンデンサ導体近くにまでクラックが到達することを抑制できる。

【図面の簡単な説明】

【0011】

【図1】一実施形態に係る電子部品の外観斜視図である。

【図2】図1の電子部品の積層体の分解斜視図である。

【図3】図1の電子部品の断面構造図である。

【図4】比較例に用いた電子部品の断面構造図である。

【図5】解析結果を示したグラフである。

【図6】第1の変形例に係る電子部品の断面構造図である。

【図7】第2の変形例に係る電子部品の断面構造図である。

【図8】第3の変形例に係る電子部品の断面構造図である。

【図9】第4の変形例に係る電子部品の断面構造図である。

【図10】第5の変形例に係る電子部品の内部平面図である。

【図11】第6の変形例に係る電子部品の内部平面図である。

【図12】第7の変形例に係る電子部品の内部平面図である。

【図13】第8の変形例に係る電子部品の内部平面図である。

【図14】第9の変形例に係る電子部品の断面構造図である。

【図15】第9の変形例に係る電子部品の内部平面図である。

【図16】第10の変形例に係る電子部品の断面構造図である。

【図17】第11の変形例に係る電子部品の断面構造図である。

【図18】第12の変形例に係る電子部品の内部平面図である。

【図19】第13の変形例に係る電子部品の内部平面図である。

【図20】第14の変形例に係る電子部品の内部平面図である。

【図21】第15の変形例に係る電子部品の内部平面図である。

【図22】特許文献1に記載のチップ型電子部品の断面構造図である。

【発明を実施するための形態】

【0012】

以下に、本発明の実施形態に係る電子部品について図面を参照しながら説明する。

【0013】

(電子部品の構成)

まず、一実施形態に係る電子部品の構成について図面を参照しながら説明する。図1は、一実施形態に係る電子部品10の外観斜視図である。図2は、図1の電子部品10の積層体11の分解斜視図である。図2では、セラミック層17g〜17iについては省略してある。図3は、図1の電子部品の断面構造図である。以下では、積層体11の積層方向をz軸方向と定義する。積層体11をz軸方向から平面視したときに、積層体11の長辺が延在している方向をx軸方向と定義する。積層体11をz軸方向から平面視したときに、積層体11の短辺が延在している方向をy軸方向と定義する。

【0014】

電子部品10は、チップコンデンサであり、図1ないし図3に示すように、積層体11、外部電極12(12a,12b)、コンデンサ導体層30(30a〜30d),31(31a〜31c)(図1には図示せず)及びダミー導体層40(40a〜40f),41(41a〜41f)(図1には図示せず)を備えている。

【0015】

積層体11は、z軸方向の両端に位置している上面S1及び底面S2、互いに対向している端面S3,S4、並びに、互いに対向している側面S5,S6を有する直方体状をなしている。ただし、積層体11は、面取りが施されることにより角及び稜線において丸みを帯びた形状をなしている。以下では、積層体11において、z軸方向の正方向側の面を上面S1とし、z軸方向の負方向側の面を底面S2とする。また、x軸方向の負方向側の面を端面S3とし、x軸方向の正方向側の面を端面S4とする。また、y軸方向の正方向側の面を側面S5とし、y軸方向の負方向側の面を側面S6とする。底面S2は、電子部品10が回路基板に実装される際に、該回路基板の主面と対向する実装面である。

【0016】

積層体11は、図2に示すように、複数のセラミック層(誘電体層)17(17a〜17o)がz軸方向の正方向側から負方向側へとこの順に並ぶように積層されることにより構成されている。セラミック層17は、長方形状をなしており、BaTiO3を主成分としBi2O3を含む誘電体セラミックにより作製されている。以下では、セラミック層17のz軸方向の正方向側の主面を表面と称し、セラミック層17のz軸方向の負方向側の主面を裏面と称す。

【0017】

積層体11の上面S1は、z軸方向の最も正方向側に設けられているセラミック層17aの表面により構成されている。積層体11の底面S2は、z軸方向の最も負方向側に設けられているセラミック層17oの裏面により構成されている。また、端面S3は、セラミック層17a〜17oのx軸方向の負方向側の短辺が連なることによって構成されている。端面S4は、セラミック層17a〜17oのx軸方向の正方向側の短辺が連なることによって構成されている。側面S5は、セラミック層17a〜17oのy軸方向の正方向側の長辺が連なることによって構成されている。側面S6は、セラミック層17a〜17oのy軸方向の負方向側の長辺が連なることによって構成されている。

【0018】

コンデンサ導体層30a〜30d,31a〜31cは、Al、Ni,Cuなどを主成分とする材料により作製されている導体層であり、セラミック層17を介して互いに対向することによってコンデンサを構成している。

【0019】

コンデンサ導体層30a〜30dはそれぞれ、図2及び図3に示すように、セラミック層17e,17g,17i,17kの表面上に設けられており、積層体11に内蔵されている。コンデンサ導体層30a〜30dは、長方形状をなしており、セラミック層17e,17g,17i,17kのx軸方向の負方向側の短辺に引き出されている。

【0020】

コンデンサ導体層31a〜31cはそれぞれ、図2及び図3に示すように、セラミック層17f,17h,17jの表面上に設けられており、積層体11に内蔵されている。コンデンサ導体層31a〜31cは、長方形状をなしており、セラミック層17f,17h,17jのx軸方向の正方向側の短辺に引き出されている。コンデンサ導体層30a〜30dとコンデンサ導体層31a〜31cとは、z軸方向から平面視したときに、重なりあっている。これにより、コンデンサ導体層30,31間にはコンデンサCが形成されている。

【0021】

外部電極12a,12bは、Ag、Cu、Niペーストが塗布されて形成される電極である。外部電極12aは、端面S3を覆っていると共に、上面S1、底面S2及び側面S5,S6とに折り返されている。また、外部電極12aは、コンデンサ導体層30a〜30dに接続されている。より詳細には、外部電極12aは、コンデンサ導体層30a〜30dが端面S3から露出している部分を覆うように、積層体11の端面S3の全面を覆っている。

【0022】

外部電極12bは、端面S4を覆っていると共に、上面S1、底面S2及び側面S5,S6とに折り返されている。また、外部電極12bは、コンデンサ導体層31a〜31cに接続されている。より詳細には、外部電極12bは、コンデンサ導体層31a〜31cが端面S4から露出している部分を覆うように、積層体11の端面S4の全面を覆っている。

【0023】

ダミー導体層40a〜40f,41a〜41fは、Al、Ni、Cuを主成分とする材料により作製されている導体層である。ダミー導体層40a〜40c,41a〜41cはそれぞれ、コンデンサ導体層30a〜30d,31a〜31cが設けられているセラミック層17e〜17kよりも上面S1の近くに位置しているセラミック層17b〜17dの表面上に設けられている。ダミー導体層40d〜40f,41d〜41fはそれぞれ、コンデンサ導体層30a〜30d,31a〜31cが設けられているセラミック層17e〜17kよりも底面S2の近くに位置しているセラミック層17l〜17nの表面上に設けられている。

【0024】

ダミー導体層40a〜40fは、長方形状をなしており、セラミック層17b〜17d,17l〜17nのx軸方向の負方向側の短辺に引き出されている。これにより、ダミー導体層40a〜40fは、外部電極12aに接続されている。また、ダミー導体層40a〜40cは、z軸方向から平面視したときに、図3に示すように、外部電極12aにおける上面S1に折り返されている部分の先端Taと重なっている。ダミー導体層40d〜40fは、z軸方向から平面視したときに、図3に示すように、外部電極12aにおける底面S2に折り返されている部分の先端Tbと重なっている。

【0025】

ダミー導体層41a〜41fは、長方形状をなしており、セラミック層17b〜17d,17l〜17nのx軸方向の正方向側の短辺に引き出されている。これにより、ダミー導体層41a〜41fは、外部電極12bに接続されている。また、ダミー導体層41a〜41cは、z軸方向から平面視したときに、図3に示すように、外部電極12bにおける上面S1に折り返されている部分の先端Tcと重なっている。ダミー導体層41d〜41fは、z軸方向から平面視したときに、図3に示すように、外部電極12bにおける底面S2に折り返されている部分の先端Tdと重なっている。

【0026】

ところで、電子部品10では、クラックがコンデンサ導体層へ到達することを抑制するため、ダミー導体層40,41の空孔量を減らし、カバレッジを増加させている。ダミー導体層40,41のカバレッジは、70%以上100%以下であることが好ましい。複数枚のダミー導体層を有する場合は、すべて上記範囲内であることが好ましい。また、積層体11の構造欠陥を防止するため、コンデンサ導体層30,31は薄く、カバレッジは60%以上70%未満であることが好ましい。

【0027】

カバレッジは、コンデンサ導体層30,31及びダミー導体層40,41をz軸方向から平面視したときに、コンデンサ導体層30,31及びダミー導体層40,41の面積に対するコンデンサ導体層30,31及びダミー導体層40,41に形成されている空孔の面積の割合を100%から減算した値である。ダミー導体層が複数枚ある場合は、各層の平均値とする。カバレッジの測定は、以下の手順により行われる。

【0028】

まず、電子部品10のセラミック層17を剥離して、コンデンサ導体層30,31及びダミー導体層40,41を露出させて、SEMにより撮影を行う。SEMにより得られた画像に2値化処理を施して、コンデンサ導体層30,31及びダミー導体層40,41の隙間(空孔)から見えるセラミック層17の面積を求める。そして、コンデンサ導体層30,31及びダミー導体層40,41の隙間(空孔)から見えるセラミック層17の面積をコンデンサ導体層30,31及びダミー導体層40,41の面積で割って100を掛けた値を100%から減算する。これにより、カバレッジが算出される。

【0029】

(電子部品の製造方法)

次に、電子部品10の製造方法について説明する。なお、図面は、図1ないし図3を援用する。

【0030】

まず、BaTiO3、Bi2O3、BaCO3の原料粉末に対して、ポリビニルブチラール系バインダ及びエタノール等の有機溶剤を加えてボールミルに投入し、湿式調合を行って、セラミックスラリーを得る。原料粉末は、BaTiO3が100モル部、Bi2O3が3モル部、BaCO3が2モル部の割合で混合されて構成されている。得られたセラミックスラリーをドクターブレード法により、キャリアシート上にシート状に形成して乾燥させ、セラミック層17となるべきセラミックグリーンシートを作製する。セラミック層17となるべきセラミックグリーンシートの厚さは、例えば、6μmである。

【0031】

次に、セラミック層17となるべきセラミックグリーンシート上に、導電性材料からなるペーストをスクリーン印刷法で塗布することにより、コンデンサ導体層30,31及びダミー導体層40,41を形成する。導電性材料からなるペーストは、金属粉末に、有機バインダ及び有機溶剤が加えられたものである。金属粉末は、Al、Cu、Niである。コンデンサ導体層30,31の厚さは、0.1μm以上2.0μm以下である。ダミー導体層40,41の厚さは、0.1μm以上10.0μm以下である。

【0032】

次に、セラミック層17となるべきセラミックグリーンシートを積層して未焼成のマザー積層体を得る。この後、未焼成のマザー積層体に対して、静水圧プレスにて圧着を施す。

【0033】

次に、未焼成のマザー積層体を所定寸法にカットして、複数の未焼成の積層体11を得る。この後、積層体11の表面に、バレル研磨加工等の研磨加工を施す。

【0034】

次に、未焼成の積層体11を大気中で270℃に加熱して、未焼成の積層体11中のバインダを燃焼させる。更に、未焼成の積層体11を焼成する。焼成温度は、例えば、650℃である。

【0035】

次に、積層体11に外部電極12を形成する。具体的には、公知のディップ法やスリット工法等により、積層体11の表面にBi2O3−SiO2−BaO系ガラスフリットを含有するAgペーストを塗布する。そして、大気中でAg、Cu、Niペーストを600〜900℃で焼付けを行うことにより、外部電極12を形成する。以上の工程により、電子部品10が完成する。

【0036】

(効果)

以上の電子部品10によれば、以下に説明するように、カバレッジが高く空孔が少なくカバレッジが高いため、積層体11にクラックが形成されても、ダミー導体層によってコンデンサ導体層付近にまでクラックが到達することが抑制され、水分が侵入せずにコンデンサとして信頼性を高めることが可能になる。

【0037】

電子部品10では、ダミー導体層40d〜40f,41d〜41fはそれぞれ、コンデンサ導体層30a〜30d,31a〜31cが設けられているセラミック層17e〜17kよりも底面S2の近くに位置しているセラミック層17l〜17nの表面上に設けられている。更に、ダミー導体層40d〜40fは、z軸方向から平面視したときに、図3に示すように、外部電極12aにおける底面S2に折り返されている部分の先端Tbと重なっている。ダミー導体層41d〜41fは、z軸方向から平面視したときに、図3に示すように、外部電極12bにおける底面S2に折り返されている部分の先端Tdと重なっている。更に、ダミー導体層40,41のz軸方向の厚みは、コンデンサ導体層30,31のz軸方向の厚みよりも大きい。これにより、基板分割工程時に、電子部品10及び回路基板に歪みが発生して外部電極12a,12bが引っ張られることにより、先端Tb,Tdからz軸方向の正方向側に向かって延びるクラックが発生したとしても、ダミー導体層40、41において、厚みが大きい(すなわち、カバレッジが高い)ため、該クラックは、ダミー導体層40f,41fよりz軸方向の正方向側に進行することが抑制される。その結果、積層体11にコンデンサ導体層30,31へ到達するほどのクラックが形成されることが抑制される。

【0038】

また、電子部品10では、ダミー導体層40,41が厚く形成され、コンデンサ導体層30,31は厚く形成されない。そのため、積層体11の構造欠陥を防止できる。

【0039】

また、外部電極12a,12bには、めっきが施されている。そのため、めっき処理の際に、積層体11内にめっき液が侵入するおそれがある。しかしながら、電子部品10では、ダミー導体層40,41のカバレッジが高いので、積層体11内にめっき液が侵入することが抑制される。

【0040】

また、セラミック層17の破壊靭性値は、3MPa√m〜7MPa√mである。一方、カバレッジの高いダミー導体層40,41の破壊靭性値は、セラミック層7の破壊靭性値の10倍以上である。したがって、電子部品10において、破損しやすい先端Tb,Td近傍にダミー導体層40,41が設けられることにより、積層体11の破損が抑制される。

【0041】

また、電子部品10では、外部電極12a,12bの先端Ta〜Tdがダミー導体層40,41と同電位で、かつ、ダミー導体層40,41のカバレッジが高くなっているために、外部電極12a,12bの先端Ta〜Tdから流れる漏れ電流がコンデンサ導体層30,31に入力することが抑制される。

【0042】

(シミュレーション結果)

本願発明者は、電子部品10が奏する効果をより明確にするために、以下に説明するシミュレーションを行った。図4は、比較例に用いた電子部品110の断面構造図である。

【0043】

本願発明者は、電子部品10の構成を有する第1のモデル及び電子部品110の構成を有する第2のモデルを作成した。第1のモデルと第2のモデルとの相違点は、ダミー導体層40,41の有無である。そして、第1のモデル及び第2のモデルにおいて、外部電極12bの先端Tdで発生したクラックの進行を解析した。図5は、解析結果を示したグラフである。横軸は、x座標を示し、縦軸は、z座標を示している。x座標の原点は端面S3であり、及びz座標の原点は上面S1である。

【0044】

図5によれば、第2のモデルでは、第1のモデルでダミー導体層41が設けられている位置を通過してz軸方向の正方向側に進行していることが分かる。一方、第1のモデルでは、クラックは、ダミー導体層41が設けられている位置において、z軸方向の正方向側への進行をやめて、ダミー導体層41に沿ってx軸方向の正方向側へと進行していることが分かる。すなわち、クラックは、残留応力が高い部分を進行している。本シミュレーションによれば、カバレッジが高く厚みの大きいダミー導体層40,41が設けられることにより残留応力が高くなり、大きなクラックの進行方向を制御できていることが分かる。

【0045】

(第1の変形例)

以下に、第1の変形例に係る電子部品10aについて図面を参照しながら説明する。図6は、第1の変形例に係る電子部品10aの断面構造図である。

【0046】

図6に示すように、ダミー導体層40,41は、上面S1及び底面S2の近傍に設けられていてもよい。すなわち、ダミー導体層40,41は、コンデンサ導体層30,31から離されて設けられている。これにより、ダミー導体層40,41とコンデンサ導体層30,31との間において静電容量が発生することが抑制される。その結果、電子部品10aでは、目標の静電容量値を得るための設計が容易となる。

【0047】

また、ダミー導体層40,41がコンデンサ導体層30,31から離れていると、ダミー導体層40,41とコンデンサ導体層30,31との間に発生する静電容量が小さくなるので、ダミー導体層40,41に積みずれが発生しても、該静電容量の変動値が小さくて済む。その結果、電子部品10aでは、目標の静電容量値を得るための設計が容易となる。

【0048】

(第2の変形例)

以下に、第2の変形例に係る電子部品10bについて図面を参照しながら説明する。図7は、第2の変形例に係る電子部品10bの断面構造図である。

【0049】

図7に示すように、ダミー導体層40,41は、コンデンサ導体層30,31の近傍に設けられていてもよい。すなわち、ダミー導体層40,41は、上面S1及び底面S2から離されて設けられている。これにより、積層体11のz軸方向の両端にダミー導体層40,41が位置しなくなる。その結果、積層体11において、ダミー導体層40,41とセラミック層17との間で相関剥離が発生することが抑制される。

【0050】

(第3の変形例及び第4の変形例)

以下に、第3の変形例に係る電子部品10c及び第4の変形例に係る電子部品10dについて図面を参照しながら説明する。図8は、第3の変形例に係る電子部品10cの断面構造図である。図9は、第4の変形例に係る電子部品10dの断面構造図である。

【0051】

図8及び図9に示すように、ダミー導体層40,41のx軸方向の端部は、揃っていなくてもよい。なお、電子部品10cにおいて、z軸方向の正方向側から平面視したときに、外部電極12a,12bの先端Ta〜Tdと重なっているダミー導体層は、ダミー導体層40c,40d,41c,41dである。同様に、電子部品10dにおいて、z軸方向の正方向側から平面視したときに、外部電極12a,12bの先端Ta〜Tdと重なっているダミー導体層は、ダミー導体層40a,40f,41a,41fである。

【0052】

(第5の変形例及び第6の変形例)

以下に、第5の変形例に係る電子部品10e及び第6の変形例に係る電子部品10fについて図面を参照しながら説明する。図10は、第5の変形例に係る電子部品10eの内部平面図である。図11は、第6の変形例に係る電子部品10fの内部平面図である。

【0053】

図10及び図11に示すように、ダミー導体層40は、外部電極12aの端面S3に形成されている部分のみならず、外部電極12aの側面S5,S6に形成されている部分にも接続されていてもよい。同様に、ダミー導体層41は、外部電極12bの端面S4に形成されている部分のみならず、外部電極12bの側面S5,S6に形成されている部分にも接続されていてもよい。

【0054】

以上のような構成を有する電子部品10e,10fでは、ダミー導体層40,41のy軸方向の幅が広くなる。これにより、側面S5又は側面S6が実装面として用いられて電子部品10e,10fが回路基板に実装されたとしても、積層体11にクラックが発生することを抑制することが可能となる。

【0055】

(第7の変形例及び第8の変形例)

以下に、第7の変形例に係る電子部品10g及び第8の変形例に係る電子部品10hについて図面を参照しながら説明する。図12は、第7の変形例に係る電子部品10gの内部平面図である。図13は、第8の変形例に係る電子部品10hの内部平面図である。

【0056】

図12及び図13に示すように、ダミー導体層40,41は、複数に分割されていてもよい。

【0057】

(第9の変形例)

以下に、第9の変形例に係る電子部品10iについて図面を参照しながら説明する。図14は、第9の変形例に係る電子部品10iの断面構造図である。図15は、第9の変形例に係る電子部品10iの内部平面図である。

【0058】

図14及び図15に示すように、ダミー導体層40,41は、外部電極12a,12bに接続されていなくてもよい。

【0059】

以上のように、ダミー導体層40,41が外部電極12a,12bに接続されないことにより、ダミー導体層40,41の面積が小さくなる。その結果、ダミー導体層40,41が設けられているセラミック層17間において層間剥離が発生することが抑制される。

【0060】

また、ダミー導体層40,41が外部電極12a,12bに接続されないことにより、積層体11の端面S3,S4及び側面S5,S6にダミー導体層40,41が露出しなくなる。そのため、積層体11のカット時やバレル時に、ダミー導体層40,41が設けられているセラミック層17間において層間剥離が発生することが抑制される。更に、ダミー導体層40,41が設けられているセラミック層17間から水分が侵入することが抑制される。

【0061】

(第10の変形例)

以下に、第10の変形例に係る電子部品10jについて図面を参照しながら説明する。図16は、第10の変形例に係る電子部品10jの断面構造図である。

【0062】

図16に示すように、ダミー導体層40,41は、上面S1及び底面S2の近傍に設けられていてもよい。これにより、第1の変形例に係る電子部品10aと同様に、電子部品10jでは、目標の静電容量値を得るための設計が容易となる。

【0063】

(第11の変形例)

以下に、第11の変形例に係る電子部品10kについて図面を参照しながら説明する。図17は、第11の変形例に係る電子部品10kの断面構造図である。

【0064】

図17に示すように、ダミー導体層40,41は、コンデンサ導体層30,31の近傍に設けられていてもよい。これにより、第2の変形例に係る電子部品10bと同様に、電子部品10kでは、積層体11において、ダミー導体層40,41とセラミック層17との間で相関剥離が発生することが抑制される。

【0065】

(第12の変形例及び第13の変形例)

以下に、第12の変形例に係る電子部品10l及び第13の変形例に係る電子部品10mについて図面を参照しながら説明する。図18は、第12の変形例に係る電子部品10lの内部平面図である。図19は、第13の変形例に係る電子部品10mの内部平面図である。

【0066】

図18及び図19に示すように、ダミー導体層40は、外部電極12aの側面S5,S6に形成されている部分においてのみ接続されていてもよい。同様に、ダミー導体層41は、外部電極12bの側面S5,S6に形成されている部分においてのみ接続されていてもよい。

【0067】

(第14の変形例及び第15の変形例)

以下に、第14の変形例に係る電子部品10n及び第15の変形例に係る電子部品10oについて図面を参照しながら説明する。図20は、第14の変形例に係る電子部品10nの内部平面図である。図21は、第15の変形例に係る電子部品10oの内部平面図である。

【0068】

図20及び図21に示すように、ダミー導体層40,41は、複数に分割されていてもよい。

【0069】

(その他の実施形態)

以上のように構成された電子部品は、前記実施形態に係る電子部品10,10a〜10oに限らず、その要旨の範囲内において変更可能である。

【0070】

電子部品10の製造方法では、ダミー導体層40,41は、印刷法により形成されるとしたが、他の方法によって形成されてもよい。他の方法とは、例えば、金属箔をセラミックグリーンシートに貼り付けてダミー導体層40,41を形成する方法や、射出成形によってダミー導体層40,41を形成する方法等が挙げられる。

【0071】

まず、金属箔をセラミックグリーンシートに貼り付けてダミー導体層40,41を形成する方法について説明する。

【0072】

金属箔をフィルムに静電気により貼りつける。次に、セラミックグリーンシートのダミー導体層40,41を形成する部分に接着剤を印刷する。金属箔が貼り付けられたフィルムをセラミックグリーンシートに貼り合わせ、フィルムのみをセラミックグリーンシートから剥離する。これにより、ダミー導体層40,41が形成される。

【0073】

また、金属箔をセラミックグリーンシートに貼り付けてダミー導体層40,41を形成する方法は、以下の射出成型によって実現されてもよい。

【0074】

具体的には、セラミックグリーンシートのダミー導体層40,41を形成する部分に、カーボン入りのセラミックペーストを印刷し積層、カット、焼成する。カーボン入りの部分にセラミックペーストを塗った部分が焼失し、空洞となる。その空洞に金属ペーストを注入することによりダミー導体層40,41を形成する。

【産業上の利用可能性】

【0075】

以上のように、本発明は、電子部品に有用であり、特に、ダミー導体層を超えてコンデンサ導体近くにまでクラックが到達することを抑制できる点で優れている。

【符号の説明】

【0076】

S1 上面

S2 底面

S3,S4 端面

S5,S6 側面

Ta〜Td 先端

10,10a〜10o 電子部品

11 積層体

12a,12b 外部電極

17a〜17o セラミック層

30a〜30d,31a〜31c コンデンサ導体層

40a〜40f,41a〜41f ダミー導体層

【特許請求の範囲】

【請求項1】

複数の誘電体層が積層されてなる積層体であって、積層方向の両端に位置し互いに対向している上面及び底面、互いに対向している2つの側面、並びに、互いに対向している2つの端面を有している直方体状の積層体と、

前記誘電体層上に設けられているコンデンサ導体層であって、コンデンサを構成しているコンデンサ導体層と、

前記端面を覆っていると共に、前記上面及び前記底面に折り返されている外部電極と、

前記複数のコンデンサ導体が設けられている前記誘電体層よりも前記底面の近くに位置している前記誘電体層上に設けられているダミー導体層であって、積層方向から平面視したときに、前記外部電極における該底面に折り返されている部分の先端と重なっているダミー導体層と、

を備えており、

前記ダミー導体層の厚みは、前記コンデンサ導体層の厚みよりも大きいこと、

を特徴とする電子部品。

【請求項2】

前記ダミー導体層のカバレッジは、70%以上100%以下であること、

を特徴とする請求項1に記載の電子部品。

【請求項3】

カバレッジは、前記ダミー導体層を積層方向から平面視したときに、該ダミー導体層の面積に対する該ダミー導体層に形成されている空孔の面積の割合を100%から減算した値であること、

を特徴とする請求項2に記載の電子部品。

【請求項4】

前記ダミー導体層は、前記外部電極に接続されていること、

を特徴とする請求項1ないし請求項3のいずれかに記載の電子部品。

【請求項5】

前記ダミー導体層は、前記外部電極に接続されていないこと、

を特徴とする請求項1ないし請求項3のいずれかに記載の電子部品。

【請求項6】

前記外部電極は、2つの前記側面に折り返されていること、

を特徴とする請求項1ないし請求項5のいずれかに記載の電子部品。

【請求項1】

複数の誘電体層が積層されてなる積層体であって、積層方向の両端に位置し互いに対向している上面及び底面、互いに対向している2つの側面、並びに、互いに対向している2つの端面を有している直方体状の積層体と、

前記誘電体層上に設けられているコンデンサ導体層であって、コンデンサを構成しているコンデンサ導体層と、

前記端面を覆っていると共に、前記上面及び前記底面に折り返されている外部電極と、

前記複数のコンデンサ導体が設けられている前記誘電体層よりも前記底面の近くに位置している前記誘電体層上に設けられているダミー導体層であって、積層方向から平面視したときに、前記外部電極における該底面に折り返されている部分の先端と重なっているダミー導体層と、

を備えており、

前記ダミー導体層の厚みは、前記コンデンサ導体層の厚みよりも大きいこと、

を特徴とする電子部品。

【請求項2】

前記ダミー導体層のカバレッジは、70%以上100%以下であること、

を特徴とする請求項1に記載の電子部品。

【請求項3】

カバレッジは、前記ダミー導体層を積層方向から平面視したときに、該ダミー導体層の面積に対する該ダミー導体層に形成されている空孔の面積の割合を100%から減算した値であること、

を特徴とする請求項2に記載の電子部品。

【請求項4】

前記ダミー導体層は、前記外部電極に接続されていること、

を特徴とする請求項1ないし請求項3のいずれかに記載の電子部品。

【請求項5】

前記ダミー導体層は、前記外部電極に接続されていないこと、

を特徴とする請求項1ないし請求項3のいずれかに記載の電子部品。

【請求項6】

前記外部電極は、2つの前記側面に折り返されていること、

を特徴とする請求項1ないし請求項5のいずれかに記載の電子部品。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【公開番号】特開2013−93374(P2013−93374A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−233106(P2011−233106)

【出願日】平成23年10月24日(2011.10.24)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月24日(2011.10.24)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]