電極構造体の形成方法及び半導体装置の製造方法

【課題】 ポリメタル構造を有するゲート電極において、ポリシリコン膜と高融点金属膜との間の界面抵抗を低くする。

【解決手段】 半導体基板10上にゲート絶縁膜11を介してポリシリコン膜12を堆積した後、該ポリシリコン膜12の上に、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16からなるバリア膜を形成する。バリア膜の上にタングステン膜18を堆積して、ポリシリコン膜12、第1の窒化チタン膜14、チタン膜15、第2の窒化チタン膜16及びタングステン膜18からなる電極構造体を形成した後、該電極構造体に対して750℃以上の熱処理を施す。このようにすると、第1の窒化チタン膜14中の窒素がチタン膜15及びポリシリコン膜12に拡散して、ポリシリコン膜12とタングステン膜18との間に新たな窒化チタン膜19が形成されると共に、ポリシリコン膜12の表面に窒化シリコンからなり厚さの小さい反応層20が形成される。

【解決手段】 半導体基板10上にゲート絶縁膜11を介してポリシリコン膜12を堆積した後、該ポリシリコン膜12の上に、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16からなるバリア膜を形成する。バリア膜の上にタングステン膜18を堆積して、ポリシリコン膜12、第1の窒化チタン膜14、チタン膜15、第2の窒化チタン膜16及びタングステン膜18からなる電極構造体を形成した後、該電極構造体に対して750℃以上の熱処理を施す。このようにすると、第1の窒化チタン膜14中の窒素がチタン膜15及びポリシリコン膜12に拡散して、ポリシリコン膜12とタングステン膜18との間に新たな窒化チタン膜19が形成されると共に、ポリシリコン膜12の表面に窒化シリコンからなり厚さの小さい反応層20が形成される。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、ポリシリコン又はアモルファスシリコンからなる下層膜と、高融点金属からなる上層膜とを有する電極構造体の製造方法、及び該電極構造体からなるゲート電極を有する半導体装置の製造方法に関する。

【0002】

【従来の技術】従来のMOSトランジスタにおいては、ゲート電極はポリシリコン膜により形成されていたが、LSIの微細化及び高速化の進展に伴って、MOSトランジスタのゲート電極の低抵抗化の要求が大きくなってきた。

【0003】そこで、ゲート電極の低抵抗化を図るべく、ゲート電極として、下層のポリシリコン膜と上層の高融点金属膜との積層膜からなるポリメタルゲート電極を用いる技術が提案されていると共に、上層の高融点金属膜としてはタングステン膜が提案されている。上層の高融点金属膜としてタングステン膜を用いると、ゲート電極の抵抗値を小さくすることができる。

【0004】ところで、ポリシリコン膜とタングステン膜との間には、ポリシリコン膜中に導入された不純物(例えば、B、P、As)のタングステン膜への拡散を防止するために、窒化タングステン(WNx )又は窒化チタン(TiN)からなるバリア膜が必要になる(例えば、特開平11−261059号公報又は特開平7−235542号公報を参照)。

【0005】図12(a)は、第1の従来例に係る電極構造体の断面構造を示している。図12(a)に示すように、半導体基板1の上にゲート絶縁膜2を介してゲート電極が形成されており、該ゲート電極は、下側から順次形成された、ポリシリコン膜3、窒化タングステン(WNx )からなるバリア膜4A及びタングステン膜5により構成されている。

【0006】図12(b)は、第2の従来例に係る電極構造体の断面構造を示している。図12(a)に示すように、半導体基板1の上にゲート絶縁膜2を介してゲート電極が形成されており、該ゲート電極は、下側から順次形成された、ポリシリコン膜3、窒化チタン(TiN)からなるバリア膜4B及びタングステン膜5により構成されている。

【0007】ところで、第1の従来例においては、後工程において熱処理が施されると、図12(c)に示すように、窒化タングステンからなるバリア膜4Aの窒素が蒸発してバリア膜4Aがタングステン膜5に変化すると共に、バリア膜4Aの窒素とポリシリコン膜3のシリコンとが反応して、ポリシリコン膜3とタングステン膜5との間に抵抗値が極めて大きい窒化シリコン(SiN)からなる反応層6が形成され、これによって、ゲート電極の抵抗値が大きくなってしまうという問題がある。

【0008】そこで、特開平7−235542号公報においては、窒化シリコンからなる反応層6の窒素の面密度を所定値以下にすると、反応層6のシート抵抗が低くなって、ゲート電極の抵抗値を低減することができると提案している。

【0009】

【発明が解決しようとする課題】ところで、本件発明者は、第1の従来例において、反応層6の窒素の面密度を所定値以下にしても、ゲート電極の抵抗値を低減することはできないという事実に直面した。

【0010】そこで、第1の従来例においてゲート電極の抵抗値を低減することができない理由について種々の検討を加えた結果、以下のことを見い出した。すなわち、反応層6における窒素の面密度を低減するべく、バリア膜4Aの厚さを0.1〜1.0nm程度に小さくすると、バリア膜4Aがバリア機能を発揮することができずタングステンシリサイド(WSix )が形成されてしまうため、ゲート電極の抵抗値を低くすることができない。一方、バリア膜4Aの厚さを1.0nmを超える程度に大きくすると、バリア機能は発揮されるが、ポリシリコン膜3とタングステン膜5との間に、抵抗値が極めて大きい窒化シリコンからなる反応層6が形成されるので、ポリシリコン膜3とタングステン膜5との間の界面抵抗値が大きくなってしまう。

【0011】また、窒化タングステン膜は耐熱性に劣るため、750℃以上の熱処理が施されると、窒化タングステン膜中の窒素が多量に拡散してしまいタングステン膜になってしまうという問題もある。

【0012】第2の従来例のように、窒化チタンからなるバリア膜を用いた場合には、以下に説明する理由によって、ポリシリコン膜とタングステン膜との間に、抵抗値が極めて大きい窒化シリコンからなる反応層6が形成されるので、ポリシリコン膜3とタングステン膜5との間の界面抵抗値が大きくなってしまう。

【0013】まず、図13(a)に示すように、半導体基板1の上にはゲート絶縁膜2を介してポリシリコン膜3が形成されており、該ポリシリコン膜3には、p型のゲート電極を形成する場合にはボロン等のp型不純物がドーピングされていると共に、n型のゲート電極を形成する場合にはリン等のn型不純物がドーピングされている。次に、ポリシリコン膜3の上に窒化チタン膜4Bを堆積するため、半導体基板1を、チタンを主成分とするチタンターゲット7が配置されたチャンバー内に搬入した後、該チャンバー内にアルゴンガスと窒素ガスとの混合ガスを導入すると共に該チャンバー内において放電を起こさせる。このようにすると、アルゴンガスと窒素ガスからなるプラズマが発生し、プラズマ中の窒素イオンとポリシリコン膜3中のシリコンとが反応して、ポリシリコン膜3の表面に窒化シリコン膜からなる反応層6が形成される。そして、図13(b)に示すように、チタンターゲット7が窒化されて窒化チタン膜8が形成されると共に、窒化チタン膜8から窒化チタンが弾き飛ばされ、反応層6の上に窒化チタンからなるバリア膜4Bが形成される。

【0014】次に、半導体基板1を、タングステンを主成分とするタングステンターゲット9が配置されたチャンバー内に移送した後、該チャンバー内にアルゴンガスを導入すると共に該チャンバー内において放電を起こさせる。このようにすると、アルゴンガスからなるプラズマが発生し、プラズマ中のアルゴンイオンのスパッタリングによりタングステンターゲット9からタングステンが弾き飛ばされ、弾き飛ばされたタングステンが窒化チタン膜4Bの表面に堆積されるので、図13(c)に示すように、窒化チタン膜4Bの上に反応層6を介してタングステン膜5が形成される。

【0015】次に、半導体基板1に、MOSトランジスタのソース又はドレインとなる不純物層を形成した後、該不純物層を活性化するために例えば750℃以上の熱処理を施すと、図14(a)に示すように、バリア膜4B中の余剰な窒素がポリシリコン膜3の上部に拡散するため、図14(b)に示すように、窒化チタンからなる反応層6の厚さが大きくなる。

【0016】また、本件発明者は、熱処理温度と熱処理後のバリア膜の界面抵抗との関係についても検討を加えた。図15は、熱処理温度(℃)と、熱処理後のポリシリコン膜と高融点金属膜との間の界面抵抗(Rc )との関係を示しており、図15において、●はn型のポリシリコン膜(NPSと表示)の上に窒化タングステン(WNx )からなるバリア膜を形成した場合を示し、○はp型のポリシリコン膜(PPSと表示)の上に窒化タングステンからなるバリア膜を形成した場合を示し、◆はn型のポリシリコン膜の上に窒化チタン(TiN)からなるバリア膜を形成した場合を示し、◇はp型のポリシリコン膜の上に窒化チタンからなるバリア膜を形成した場合を示している。また、図15においては、非オーミックであるため、界面抵抗としては1mA/μm2 の電流を流した場合の抵抗値を示している。

【0017】図15から、窒化チタンからなるバリア膜4Bを用いた場合には、熱処理の温度が低くても界面抵抗が高いことが分かる。また、本件発明者らの実験では、窒化チタンからなるバリア膜4Bを用いた場合には、熱処理を施さなくても界面抵抗は高い。その理由は、図13(a)〜(c)に示すように、ポリシリコン膜3とバリア膜4Bとの間に窒化チタンからなる反応層6が形成されているためである。

【0018】また、窒化タングステンからなるバリア膜4Aを用いた場合には、窒化チタンからなるバリア膜4Bを用いた場合に比べて界面抵抗は低いが、750℃以上の温度の熱処理を施すと、界面抵抗は急激に高くなることが分かる。その理由は、窒化タングステンからなるバリア膜4Aを用いた場合に750℃以上の温度の熱処理を施すと、窒化タングステン中の窒素が拡散し、ポリシリコン膜3とタングステン膜5との間に窒化シリコンからなる反応層6が形成されるためである。

【0019】ポリシリコン膜3とタングステン膜5との間の界面抵抗(Rc )が大きくなるとMOSトランジスタの動作速度は遅くなる。すなわち、ゲート電極がAC(交流)動作をする場合、ゲート絶縁膜に発生する分布容量に対して充放電が繰り返し行なわれるため、分布界面抵抗に電流が流れるので、分布界面抵抗の影響が現われ、これによって、MOSトランジスタの動作速度は遅くなるのである。MOSトランジスタの動作速度が遅くなると、LSIの動作速度が遅くなって信号遅延時間が増加するという問題がある。LSIの動作速度が重要視される現在においては、MOSトランジスタの動作速度は、数%程度劣化するだけでも大きな問題となる。

【0020】前記に鑑み、本発明は、ポリシリコン膜と高融点金属膜との間の界面抵抗を低くすることを目的とする。

【0021】

【課題を解決するための手段】前記の目的を達成するため、本発明に係る電極構造体の形成方法は、シリコンを主成分とするシリコン含有膜の上にバリア膜を形成する工程と、前記バリア膜の上に高融点金属膜を堆積して、前記シリコン含有膜、前記バリア膜及び前記高融点金属膜からなる積層膜を形成する工程と、前記積層膜に対して750℃以上の温度で熱処理を施す工程とを備えた電極構造体の形成方法を前提とし、前記バリア膜を形成する工程は、前記シリコン含有膜の上に金属の窒化物からなる第1の金属膜を形成する工程と、前記第1の金属膜の上に、前記金属からなるか又は前記金属の窒化物からなり前記第1の金属膜よりも窒素の含有量が少ない第2の金属膜を形成する工程と、前記第2の金属膜の上に、前記金属の窒化物からなり前記第2の金属膜よりも窒素の含有量が多い第3の金属膜を形成する工程とを含む。

【0022】本発明に係る電極構造体の形成方法によると、熱処理を施した際に、第1の金属膜に含まれる窒素及び第3の金属膜に含まれる窒素の各一部は第2の金属膜の窒化に消費され、第1の金属膜に含まれる窒素のうちシリコン含有膜の窒化に寄与する窒素の量は少なくなるため、シリコン含有膜とバリア膜との界面には、シリコン窒化膜からなり抵抗値の極めて大きい反応層が形成されないか又は形成されてもその厚さは小さいので、シリコン含有膜と高融点金属膜との間の界面抵抗は低くなる。

【0023】本発明に係る電極構造体の形成方法において、前記金属はチタンであることが好ましい。

【0024】本発明に係る電極構造体の形成方法において、前記バリア膜を形成する工程は、前記金属を主成分とするターゲットの表面に形成された前記金属の窒化物膜に対して、窒素ガスが実質的に含まれない不活性ガスを用いるスパッタリングを行なうことにより、前記金属の窒化物を前記シリコン含有膜の上に堆積して前記第1の金属膜を形成した後、前記金属を前記第1の金属膜の上に堆積して前記第2の金属膜を形成する工程と、前記ターゲットに対して、窒素ガスと不活性ガスとの混合ガスを用いるスパッタリングを行なうことにより、前記金属と前記混合ガスに含まれる窒素とが反応してなる前記金属の窒化物を前記第2の金属膜の上に堆積して前記第3の金属膜を形成する工程とを含むことが好ましい。

【0025】このように、第1の金属膜を形成する工程は、窒素ガスが実質的に含まれない不活性ガスを用いるスパッタリングを行なうため、シリコン含有膜の表面にシリコン窒化膜が形成されないので、シリコン含有膜と高融点金属膜との間の界面抵抗は一層低くなる。また、同一のターゲットを用いて、スパッタリング用のガスを切り替えるだけで、第1の金属膜、第2の金属膜及び第3の金属膜を連続的に形成することができるので、スループットが向上する。

【0026】この場合、前記バリア膜を形成する工程の後に、前記第3の金属膜を形成する工程において前記ターゲットの表面に形成された前記金属の窒化物膜に対して、窒素ガスが実質的に含まれない不活性ガスを用いてスパッタリングを行なう工程をさらに備えていることが好ましい。

【0027】このように、第3の金属膜を形成する工程においてターゲットの表面に形成された金属窒化物膜を、窒素ガスが実質的に含まれない不活性ガスによりスパッタリングする工程を備えていると、金属窒化物膜に含まれる窒素の濃度が低くなるため、該金属窒化物膜を用いて形成される第1の金属膜の窒素濃度が低減するので、シリコン含有膜の窒化に寄与する窒素の量が一層少なくなる。このため、シリコン含有膜とバリア膜との界面には、シリコン窒化膜からなる反応層が一層形成され難くなると共に形成されてもその厚さは一層小さくなるので、シリコン含有膜と高融点金属膜との間の界面抵抗は一層低くなる。

【0028】本発明に係る電極構造体の形成方法において、前記バリア膜を形成する工程は、表面に前記金属の窒化物膜が形成されている前記金属を主成分とするターゲットが配置されているチャンバー内に窒素ガスが実質的に含まれない不活性ガスを導入すると共に前記チャンバー内に放電を起こさせて、前記金属の窒化物膜から弾き飛ばされた前記金属の窒化物を前記シリコン含有膜の上に堆積することにより前記第1の金属膜を形成した後、前記金属を前記第1の金属膜の上に堆積することにより前記第2の金属膜を形成する工程と、前記ターゲットが配置されている前記チャンバー内に窒素ガスと不活性ガスとの混合ガスを導入すると共に、前記チャンバー内に放電を起こさせて、前記金属と前記混合ガスに含まれる窒素とが反応してなる前記金属の窒化物を前記第2の金属膜の上に堆積することにより前記第3の金属膜を形成する工程とを含むことが好ましい。

【0029】このようにすると、第1の金属膜を形成する工程は、チャンバー内に窒素ガスが実質的に含まれない不活性ガスを導入するため、シリコン含有膜の表面にシリコン窒化膜が形成されないので、シリコン含有膜と高融点金属膜との間の界面抵抗は一層低くなる。また、同一のチャンバー内に配置された同一のターゲットを用いて、スパッタリング用のガスを切り替えるだけで、第1の金属膜、第2の金属膜及び第3の金属膜を連続的に形成することができるので、スループットが向上する。

【0030】この場合、前記バリア膜を形成する工程の後に、前記チャンバー内に窒素ガスが実質的に含まれない不活性ガスを導入すると共に前記チャンバー内に放電を起こさせる工程をさらに備えていることが好ましい。

【0031】このように、バリア膜を形成する工程の後に、チャンバー内に窒素ガスが実質的に含まれない不活性ガスを導入すると共にチャンバー内に放電を起こさせる工程を備えていると、第3の金属膜を形成する工程においてターゲットの表面に形成された金属窒化物膜を、窒素ガスが実質的に含まれない不活性ガスによりスパッタリングすることができるため、金属窒化物膜に含まれる窒素の濃度が低くなり、該金属窒化物膜を用いて形成される第1の金属膜の窒素濃度が低減する。従って、シリコン含有膜の窒化に寄与する窒素の量が一層少なくなるため、シリコン含有膜とバリア膜との界面には、シリコン窒化膜からなる反応層が一層形成され難くなると共に形成されてもその厚さは一層小さくなるので、シリコン含有膜と高融点金属膜との間の界面抵抗は一層低くなる。

【0032】本発明に係る半導体装置の製造方法は、半導体領域上にポリシリコン膜を形成する工程と、前記ポリシリコン膜の上にバリア膜を形成する工程と、前記バリア膜の上に高融点金属膜を堆積して、前記シリコン含有膜、前記バリア膜及び前記高融点金属膜からなるゲート電極を形成する工程と、前記半導体領域に前記ゲート電極をマスクとして不純物をイオン注入してソース又はドレインとなる不純物層を形成する工程と、750℃以上の温度で熱処理を施して前記不純物層を活性化させる工程とを備えた半導体装置の製造方法を前提とし、前記バリア膜を形成する工程は、前記シリコン含有膜の上に金属の窒化物からなる第1の金属膜を形成する工程と、前記第1の金属膜の上に、前記金属からなるか又は前記金属の窒化物からなり前記第1の金属膜よりも窒素の含有量が少ない第2の金属膜を形成する工程と、前記第2の金属膜の上に、前記金属の窒化物からなり前記第2の金属膜よりも窒素の含有量が多い第3の金属膜を形成する工程とを含む。

【0033】本発明に係る半導体装置の製造方法によると、本発明に係る電極構造体の形成方法を用いて半導体装置を製造するため、ソース又はドレインとなる不純物層を活性化するために750℃以上の熱処理を施しても、ゲート電極におけるポリシリコン膜と高融点金属膜との間の界面抵抗を低くすることができる。

【0034】本発明に係る半導体装置の製造方法において、前記金属はチタンであることが好ましい。

【0035】

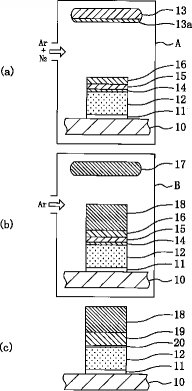

【発明の実施の形態】(第1の実施形態)以下、本発明の第1の実施形態に係る電極構造体の形成方法として、ゲート電極の形成方法について、図1(a)〜(c)、図2(a)〜(c)及び図3を参照しながら説明する。

【0036】まず、図1(a)に示すように、シリコン基板10の上にシリコン酸化膜からなるゲート絶縁膜11を形成した後、該ゲート絶縁膜11の上に、減圧CVD法によりアモルファスシリコン膜を堆積する。

【0037】次に、アモルファスシリコン膜におけるn型ゲート電極形成領域にリン(P)イオンを10KeVの注入エネルギー及び8×1015cm-2のドーズ量でドーピングすると共に、アモルファスシリコン膜におけるp型ゲート電極形成領域にボロン(B)イオンを5KeVの注入エネルギー及び5×1015cm-2のドーズ量でドーピングする。次に、リンイオン又はボロンイオンがドーピングされたアモルファスシリコン膜に対して800℃の温度下で30秒間の熱処理を施すことにより、アモルファスシリコン膜を結晶化してn型又はp型のポリシリコン膜12を形成した後、ポリシリコン膜12の表面に形成されているシリコン酸化膜をフッ酸系の洗浄液を用いて除去する。

【0038】次に、準備工程として、図3に示すように、チタンを主成分とするチタンターゲットが配置されているチャンバー内にアルゴンガスと窒素ガスとの混合ガスを導入すると共にチャンバー内に放電を起こさせて、チタンターゲットの表面に窒化チタン膜を形成する。

【0039】次に、ウエハ入れ替え工程として、準備工程で用いた半導体基板(ウエハ)を搬出した後、図1(b)に示すように、半導体基板10を、表面に窒化チタン膜13aが形成されているチタンターゲット13が配置されたチャンバーA内に搬入する。

【0040】次に、図3に示すように、該チャンバーA内にアルゴンガスを導入すると共に該チャンバーA内において放電を起こさせる。このようにすると、アルゴンガスからなるプラズマが発生し、プラズマ中のアルゴンイオンがチタンターゲット13の表面の窒化チタン膜13aをスパッタリングするので、図1(b)に示すように、ポリシリコン膜12の表面には第1の金属膜としての第1の窒化チタン膜14が堆積される。尚、この工程において、チタンターゲット13の表面に形成されている窒化チタン膜13aは消滅する。

【0041】次に、チャンバーA内へのアルゴンガスの導入及びチャンバー内での放電を継続すると、プラズマ中のアルゴンイオンがチタンターゲット13をスパッタリングするので、図1(c)に示すように、第1の窒化チタン膜14の上には第2の金属膜としてのチタン膜15が堆積される。

【0042】次に、図3に示すように、放電を一旦停止した後、チャンバーA内にアルゴンガスと窒素ガスとの混合ガスを導入すると共に、再び放電を起こさせると、図2(a)に示すように、チタン膜15の表面に、第3の金属膜としての第2の窒化チタン膜16が形成されると共に、チタンターゲット13の表面にも窒化チタン膜13aが形成される。

【0043】第1の実施形態によると、表面に窒化チタン膜13aが形成されているチタンターゲット13が配置されたチャンバーA内にアルゴンガスを導入することにより、第1の金属膜としての窒化チタン膜14と第2の金属膜としてのチタン膜15とを連続して堆積することができると共に、その後、チャンバーA内にアルゴンガスと窒素ガスとの混合ガスを導入することにより、チタン膜15の上に第3の金属膜としての窒化チタン膜16を形成することができる。すなわち、チタンターゲット13を取り替えることなく、チャンバーA内に導入するガスを切り替えるのみで、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16を連続的に形成することができるので、スループットが向上する。

【0044】尚、第2の窒化チタン膜16を形成する工程においてチタンターゲット13の表面に形成された窒化チタン膜13aを、ポリシリコン膜12の表面に第1の窒化チタン膜14を堆積する工程に用いることができる。つまり、第3の金属膜の形成工程と前述した準備工程とを同じ工程で行なうことができる。このようにするとスループットが一層向上する。

【0045】次に、図2(b)に示すように、半導体基板10を、タングステンを主成分とするタングステンターゲット17が配置されたチャンバーB内に移送した後、該チャンバーB内にアルゴンガスを導入すると共に該チャンバーB内に放電を起こさせる。このようにすると、アルゴンガスからなるプラズマが発生し、プラズマ中のアルゴンイオンがタングステンターゲット17をスパッタリングするので、第2の窒化チタン膜16の上に高融点金属膜としてのタングステン膜18が堆積される。以上説明した、ポリシリコン膜12、第1の窒化チタン膜14、チタン膜15、第2の窒化チタン膜16及びタングステン膜18により電極構造体としてのゲート電極が構成され、また、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16によりバリア膜が構成される。尚、バリア膜の厚さとしては、ゲート電極の厚さが大きくなり過ぎないようにするため、5nm〜20nm程度であることが好ましい。

【0046】次に、図示は省略しているが、半導体基板10にゲート電極をマスクとして不純物をドーピングして、ソース又はドレインとなる不純物層を形成した後、不純物を活性化するために例えば750℃以上の熱処理を施す。

【0047】ところで、ポリシリコン膜12とチタン膜15との間には第1の窒化チタン膜14が介在しているため、750℃以上の熱処理を施しても、ポリシリコン膜12の表面には、抵抗値の高いチタンシリサイド(TiSi2 )が形成されない。

【0048】また、750℃以上の熱処理工程において、第1の窒化チタン膜14中に存在する窒素はチタン膜15及びポリシリコン膜12に拡散する。この際、第1の窒化チタン膜14中及び第2の窒化チタン膜16中の過剰な窒素がチタン膜15に拡散することにより、チタン膜15が窒化チタン膜に変化するので、図2(c)に示すように、新たな窒化チタン膜19が形成される。また、第1の窒化チタン膜14中の窒素がポリシリコン膜12に拡散することにより、ポリシリコン膜12と窒化チタン膜19との界面に、シリコン及び窒素を主成分とする反応層20が形成される。

【0049】前述したように、シリコン及び窒素を主成分とする反応層20の抵抗値は極めて大きいため、反応層20の厚さが大きい場合には、ポリシリコン膜12とタングステン膜18との間の界面抵抗は高くなる。

【0050】ところが、第1の実施形態においては、第1の窒化チタン膜14の上にチタン膜15が形成されているため、第1の窒化チタン膜15中の窒素はチタン膜15の窒化に消費され、ポリシリコン膜12の窒化に寄与する窒素の量は少なくなるので、反応層20の厚さは従来に比べて著しく小さくなる。

【0051】また、熱処理工程において、第2の窒化チタン膜16中の窒素も拡散するが、第2の窒化チタン膜16の下側にチタン膜15が存在しているため、第2の窒化チタン膜16中の窒素はチタン膜15の窒化に費やされるためポリシリコン膜12に到達せず、これにより、第2の窒化チタン膜16中の窒素に起因する反応層は形成されない。

【0052】従って、第1の実施形態によると、ポリシリコン膜12とタングステン膜18との間の界面抵抗は大きく低減する。

【0053】また、第1の窒化チタン膜14の厚さとしては、3nm以下が好ましく2nm程度が最も好ましい。その理由は、第1の窒化チタン膜14の厚さが3nmを超えると、750℃以上の熱処理工程において形成される反応層20の厚さが大きくなって、ポリシリコン膜12とタングステン膜18との間の界面抵抗が高くなる恐れがあるためである。

【0054】図4(a)、(b)は、バリア膜を構成する、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16における窒素含有量の分布を示しており、横軸はバリア膜とポリシリコン膜との界面から基板側にかけての距離を示している。

【0055】図4(a)に示す窒素含有量分布においては、第1の金属膜(第1の窒化チタン膜14)のポリシリコン膜との界面ではTiNであるが、基板側に向かうにつれて窒素含有量が徐々に低下し、第1の金属膜と第2の金属膜(チタン膜15)との界面では窒素含有量は0になっている。また、第2の金属膜と第3の金属膜(第2の窒化チタン膜16)との界面では窒素含有量は0であるが、基板側に向かうにつれて窒素含有量は徐々に増加し、やがてTiNになっている。

【0056】図4(b)に示す窒素含有量分布においては、第1の金属膜(第1の窒化チタン膜14)のポリシリコン膜との界面ではTiNであるが、基板側に向かうにつれて窒素含有量が徐々に低下し、第1の金属膜と第2の金属膜(チタン膜15)との界面では窒素含有量はTiNの半分程度になっており、第2の金属膜の深さ方向の中央部では窒素含有量が大きく低減している。また、第2の金属膜と第3の金属膜(第2の窒化チタン膜16)との界面では窒素含有量はTiNの半分程度であるが、基板側に向かうにつれて窒素含有量は徐々に増加し、やがてTiNになっている。

【0057】図4(b)に示すような窒素含有量分布を実現するためには、チタン膜15を形成するためにアルゴンガスを導入する時間を短縮したり又は放電のパワーを低くしたりするとよい。

【0058】尚、第1の実施形態においては、表面に窒化チタン膜13aが形成されたチタンターゲット13を用いて、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16を連続的に形成したため、窒素含有量は徐々に減少していると共に徐々に増加しているが、窒化チタンを主成分とするターゲットとチタンを主成分とするターゲットとを使い分けると、窒素含有量は連続的に変化せずに第1及び第2の窒化チタン膜14、16と、チタン膜15との間で窒素含有量は一気に変化する。

【0059】(第2の実施形態)以下、本発明の第2の実施形態に係る電極構造体の形成方法として、ゲート電極の形成方法について、図1(a)〜(c)、図5(a)〜(c)及び図6を参照しながら説明する。

【0060】第1の実施形態と同様、図1(a)に示すように、シリコン基板10の上にゲート絶縁膜11を形成した後、該ゲート絶縁膜11の上にポリシリコン膜12を堆積する。

【0061】次に、準備工程として、図6に示すように、チタンを主成分とするチタンターゲットが配置されているチャンバー内にアルゴンガスと窒素ガスとの混合ガスを導入すると共にチャンバー内に放電を起こさせて、チタンターゲットの表面に窒化チタン膜を形成する。

【0062】次に、半導体基板10を、表面に窒化チタン膜13aが形成されているチタンターゲット13が配置されたチャンバーA内に搬入して、第1の実施形態と同様、図1(b)に示すように、ポリシリコン膜12の表面に第1の金属膜としての窒化チタン膜14を形成した後、図1(c)に示すように、第1の窒化膜14の上にチタン膜15を形成する。

【0063】次に、図6に示すように、放電をいったん停止した後、チャンバーA内にアルゴンガスと窒素ガスとの混合ガスを導入すると共に再び放電を起こさせて、図5(a)に示すように、チタン膜15の表面に、第3の金属膜としての第2の窒化チタン膜16を形成すると共に、チタンターゲット13の表面にも窒化チタン膜13aを形成する。

【0064】次に、図6に示すように、チャンバーA内にアルゴンガスのみを導入すると共にチャンバーA内での放電を継続するターゲットクリーニング工程を行なう。このようにすると、チタンターゲット13の表面の窒化チタン膜13aがアルゴンイオンによりスパッタリングされるので、窒化チタン膜13aの窒素含有量が低くなると共に、図5(b)に示すように、第2の窒化チタン膜16の上に第3の窒化チタン膜21が堆積される。

【0065】次に、図5(c)に示すように、半導体基板10を、タングステンを主成分とするタングステンターゲット17が配置されたチャンバーB内に移送した後、該チャンバーB内にアルゴンガスを導入すると共に該チャンバーB内に放電を起こさせて、第3の窒化チタン膜21の上に高融点金属膜としてのタングステン膜18を堆積する。以上説明した、ポリシリコン膜12、第1の窒化チタン膜14、チタン膜15、第2の窒化チタン膜16、第3の窒化チタン膜21及びタングステン膜18により電極構造体としてのゲート電極が構成され、また、第1の窒化チタン膜14、チタン膜15、第2の窒化チタン膜16及び第3の窒化チタン膜21によりバリア膜が構成される。

【0066】図7(a)、(b)は、バリア膜を構成する、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16における窒素含有量の分布を示しており、横軸はバリア膜とポリシリコン膜との界面から基板側にかけての距離を示している。尚、第3の窒化チタン膜21における窒素含有量については省略している。

【0067】図7(a)に示す窒素含有量分布においては、第1の金属膜(第1の窒化チタン膜14)のポリシリコン膜との界面ではTiNよりも窒素含有量が少ないと共に、基板側に向かうにつれて窒素含有量が徐々に低下し、第1の金属膜と第2の金属膜(チタン膜15)との界面では窒素含有量は0になっている。また、第2の金属膜と第3の金属膜(第2の窒化チタン膜16)との界面では窒素含有量は0であるが、基板側に向かうにつれて窒素含有量は徐々に増加し、やがてTiNになっている。

【0068】図7(b)に示す窒素含有量分布においては、第1の金属膜(第1の窒化チタン膜14)のポリシリコン膜との界面ではTiNよりも窒素含有量が少ないと共に、基板側に向かうにつれて窒素含有量が徐々に低下し、第1の金属膜と第2の金属膜(チタン膜15)との界面では窒素含有量はTiNの半分以下になっている。また、第2の金属膜と第3の金属膜(第2の窒化チタン膜16)との界面では窒素含有量はTiNの半分程度であるが、基板側に向かうにつれて窒素含有量は徐々に増加し、やがてTiNになっている。

【0069】第2の実施形態によると、チタン膜15の表面に第2の窒化チタン膜16を形成した後、チャンバーA内にアルゴンガスのみを導入するターゲットクリーニング工程を行なうため、第1の窒化チタン膜14の堆積に用いられる窒化チタン膜13aの窒素含有量が低くなる。従って、図7(a)と図4(a)との対比、及び図7(b)と図4(b)との対比から分かるように、第1の窒化チタン膜14におけるポリシリコン膜12との界面近傍の窒素含有量は第1の実施形態に比べて低減している。このため、電極構造体に対して750℃以上の熱処理が施されたときに、第1の窒化チタン膜14からポリシリコン膜12に拡散する窒素の量が低減するので、ポリシリコン膜12の表面に形成される反応層20(図2(c)を参照)の厚さが一層薄くなるか又は反応層20は実質的に形成されなくなり、ポリシリコン膜12とタングステン膜18との間の界面抵抗は一層低くなる。

【0070】図8は、ターゲットクリーニング工程の時間を0秒、1秒、2秒、3秒、5秒及び7秒と変化させた場合における、第1の窒化チタン膜14及びチタン膜15からなる積層膜の膜厚と、ポリシリコン膜12とタングステン膜18との間の界面抵抗との関係を示している。この場合、ポリシリコン膜12はp型ゲート電極を構成する。尚、図8は、300WのDCパワーで第1の窒化チタン膜14及びチタン膜15を形成し、2000WのDCパワーで20秒間放電を行なって10nmの一定の厚さを持つ第2の窒化チタン膜16を形成し、1000WのDCパワーでターゲットクリーニング工程を行なった場合の実験データである。また、第2の窒化膜16の上には、1000WのDCパワーで60nmの膜厚を持つタングステン膜18を形成した。尚、積層膜を形成した後の熱処理として、760℃の温度下における240分の炉処理と、975℃の温度下における30秒のランプアニール処理とを実施した。

【0071】図8から分かるように、ターゲットクリーニング工程の時間が長くなると、第1の窒化チタン膜14における窒素の含有量が低減するため、反応膜20が形成され難くなり、これによって、界面抵抗が低くなる。また、この傾向は第1の窒化チタン膜14及びチタン膜15の合計膜厚が小さいときに顕著に現われる。尚、図8における膜厚が0である点は、従来例(窒化チタンの単層膜)に相当する。

【0072】図9は、ターゲットクリーニング時間と、第1の窒化チタン膜14とチタン膜15との積層膜に含まれる窒素の量との関係を示している。図9において、●はターゲットクリーニングを行なわない第1の実施形態に相当し、○はターゲットクリーニングを行なう第2の実施形態に相当する。図9から分かるように、ターゲットクリーニングの時間の増加と、積層膜中の窒素量の減少とは直線的な関係を有している。

【0073】(第3の実施形態)以下、本発明の第3の実施形態に係る半導体装置の製造方法について、図10(a)、(b)及び図11(a)、(b)を参照しながら説明する。

【0074】まず、図10(a)に示すように、半導体基板30の上に、ゲート絶縁膜となるシリコン酸化膜31を形成した後、該シリコン酸化膜31の上にポリシリコン膜32を堆積する。

【0075】次に、第1の実施形態と同様の方法で、ポリシリコン膜32の上に、バリア膜となる第1の窒化チタン膜34、チタン膜35及び第2の窒化チタン膜36を順次形成した後、第2の窒化チタン膜36の上にタングステン膜38を堆積して、ポリシリコン膜32、第1の窒化チタン膜34、チタン膜35、第2の窒化チタン膜36及びタングステン膜38からなる積層体を形成し、その後、該積層体の上に、窒化シリコン膜からなりゲート電極を形成するためのハードマスク39を形成する。

【0076】次に、図10(b)に示すように、積層体に対してハードマスク39を用いてエッチングを行なって積層体からなるゲート電極を形成した後、該ゲート電極を洗浄する。

【0077】次に、半導体基板30にゲート電極をマスクとして不純物をドーピングして低濃度不純物層40を形成した後、半導体基板30の上に全面に亘ってシリコン窒化膜を堆積し、その後、該シリコン窒化膜に対して異方性エッチングを行なうことにより、図11(a)に示すように、ゲート電極の壁面にサイドウォール41を形成する。次に、半導体基板30にゲート電極及びサイドウォール41をマスクとして不純物をドーピングして高濃度不純物層43を形成する。

【0078】次に、半導体基板30に対して750℃以上の温度の熱処理を施して、低濃度不純物層40及び高濃度不純物層43を活性化する。このようにすると、第1の窒化チタン膜34及び第2の窒化チタン膜36中に存在する窒素がチタン膜35に拡散するため、図11(b)に示すように、ポリシリコン膜32とタングステン膜38との間に新たな窒化チタン膜45が形成されると共に、ポリシリコン膜32と窒化チタン膜45との界面に、シリコン及び窒素を主成分とする反応層56が形成される。

【0079】第3の実施形態によると、750℃以上の熱処理の後においても、チタンシリサイド層が形成されないと共に界面抵抗を低減できるので、MOSトランジスタの動作速度の低下を防止することができる。また、チタンシリサイド層が形成されることに起因してタングステン膜38が膜剥がれする事態も防止できる。

【0080】尚、第1〜第3の実施形態においては、高融点金属膜として、タングステン膜を用いたが、これに代えて、モリブデン(Mo)膜、タングステンシリサイド(WSix )膜又はモリブデンシリサイド(MoSi2 )膜を用いてもよい。

【0081】また、バリア膜を構成する金属としては、チタンを用いたが、これに代えて、タンタル(Ta)又はタングステン(W)等を用いてもよい。

【0082】さらに、第1〜第3の実施形態においては、シリコン基板を用いたが、これに代えて、SOI基板を用いてもよい。

【0083】

【発明の効果】本発明に係る電極構造体の形成方法によると、750℃以上の熱処理を施しても、シリコン含有膜の表面には抵抗値の大きい金属シリサイドが形成され難いと共に、シリコン含有膜とバリア膜との界面に抵抗値の極めて大きい反応層が形成されないか又は形成されてもその厚さは小さくなるので、シリコン含有膜と高融点金属膜との間の界面抵抗は低くなる。

【0084】また、本発明に係る半導体装置の製造方法によると、ソース又はドレインとなる不純物層を活性化するために750℃以上の熱処理を施しても、ゲート電極におけるポリシリコン膜と高融点金属膜との間の界面抵抗を低くすることができる。従って、MOSトランジスタの遅延時間を低減して、MOSトランジスタの動作速度の向上を図ることができる。

【図面の簡単な説明】

【図1】(a)〜(c)は、第1の実施形態に係る電極構造体の形成方法の各工程を示す断面図である。

【図2】(a)〜(c)は、第1の実施形態に係る電極構造体の形成方法の各工程を示す断面図である。

【図3】第1の実施形態においてチャンバー内に導入するガスの種類と放電との関係を示すシーケンス図である。

【図4】(a)、(b)は第1の実施形態により得られるバリア膜における、界面からの距離と窒素含有量との関係を示す図である。

【図5】(a)〜(c)は、第2の実施形態に係る電極構造体の形成方法の各工程を示す断面図である。

【図6】第2の実施形態においてチャンバー内に導入するガスの種類と放電との関係を示すシーケンス図である。

【図7】(a)、(b)は第2の実施形態により得られるバリア膜における、界面からの距離と窒素含有量との関係を示す図である。

【図8】第2の実施形態により得られる第1の窒化チタン膜及びチタン膜からなる積層膜の膜厚と、ポリシリコン膜とタングステン膜との間の界面抵抗との関係を示す図である。

【図9】第2の実施形態において行なわれるターゲットクリーニング時間と、第1の窒化チタン膜及びチタン膜からなる積層膜に含まれる窒素の量との関係を示す図である。

【図10】(a)、(b)は第3の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図11】(a)、(b)は第3の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図12】(a)は第1の従来例に係る電極構造体の断面図であり、(b)は第2の従来例に係る電極構造体の断面図であり、(c)は第1の従来例に係る電極構造体に対して750℃以上の熱処理を施したときの断面図である。

【図13】(a)〜(c)は第2の従来例に係る電極構造体の形成方法の各工程を示す断面図である。

【図14】(a)、(b)は第2の従来例に係る電極構造体の形成方法の問題点を説明する断面図である。

【図15】第1の従来例及び第2の従来例に係る電極構造体の形成方法により得られるゲート電極に対する熱処理の温度と、熱処理後の界面抵抗との関係を示す図である。

【符号の説明】

A チャンバー

B チャンバー

10 半導体基板

11 ゲート絶縁膜

12 ポリシリコン膜

13 チタンターゲット

13a 窒化チタン膜

14 第1の窒化チタン膜(第1の金属膜)

15 チタン膜(第2の金属膜)

16 第2の窒化チタン膜(第3の金属膜)

17 タングステンターゲット

18 タングステン膜

19 窒化チタン膜

20 反応層

21 第3の窒化チタン膜

30 半導体基板

31 ゲート絶縁膜

32 ポリシリコン膜

34 第1の窒化チタン膜

35 チタン膜

36 第2の窒化チタン膜

38 タングステン膜

39 ハードマスク

40 低濃度不純物層

41 サイドウォール

43 高濃度不純物層

45 窒化チタン膜

46 反応層

【0001】

【発明の属する技術分野】本発明は、ポリシリコン又はアモルファスシリコンからなる下層膜と、高融点金属からなる上層膜とを有する電極構造体の製造方法、及び該電極構造体からなるゲート電極を有する半導体装置の製造方法に関する。

【0002】

【従来の技術】従来のMOSトランジスタにおいては、ゲート電極はポリシリコン膜により形成されていたが、LSIの微細化及び高速化の進展に伴って、MOSトランジスタのゲート電極の低抵抗化の要求が大きくなってきた。

【0003】そこで、ゲート電極の低抵抗化を図るべく、ゲート電極として、下層のポリシリコン膜と上層の高融点金属膜との積層膜からなるポリメタルゲート電極を用いる技術が提案されていると共に、上層の高融点金属膜としてはタングステン膜が提案されている。上層の高融点金属膜としてタングステン膜を用いると、ゲート電極の抵抗値を小さくすることができる。

【0004】ところで、ポリシリコン膜とタングステン膜との間には、ポリシリコン膜中に導入された不純物(例えば、B、P、As)のタングステン膜への拡散を防止するために、窒化タングステン(WNx )又は窒化チタン(TiN)からなるバリア膜が必要になる(例えば、特開平11−261059号公報又は特開平7−235542号公報を参照)。

【0005】図12(a)は、第1の従来例に係る電極構造体の断面構造を示している。図12(a)に示すように、半導体基板1の上にゲート絶縁膜2を介してゲート電極が形成されており、該ゲート電極は、下側から順次形成された、ポリシリコン膜3、窒化タングステン(WNx )からなるバリア膜4A及びタングステン膜5により構成されている。

【0006】図12(b)は、第2の従来例に係る電極構造体の断面構造を示している。図12(a)に示すように、半導体基板1の上にゲート絶縁膜2を介してゲート電極が形成されており、該ゲート電極は、下側から順次形成された、ポリシリコン膜3、窒化チタン(TiN)からなるバリア膜4B及びタングステン膜5により構成されている。

【0007】ところで、第1の従来例においては、後工程において熱処理が施されると、図12(c)に示すように、窒化タングステンからなるバリア膜4Aの窒素が蒸発してバリア膜4Aがタングステン膜5に変化すると共に、バリア膜4Aの窒素とポリシリコン膜3のシリコンとが反応して、ポリシリコン膜3とタングステン膜5との間に抵抗値が極めて大きい窒化シリコン(SiN)からなる反応層6が形成され、これによって、ゲート電極の抵抗値が大きくなってしまうという問題がある。

【0008】そこで、特開平7−235542号公報においては、窒化シリコンからなる反応層6の窒素の面密度を所定値以下にすると、反応層6のシート抵抗が低くなって、ゲート電極の抵抗値を低減することができると提案している。

【0009】

【発明が解決しようとする課題】ところで、本件発明者は、第1の従来例において、反応層6の窒素の面密度を所定値以下にしても、ゲート電極の抵抗値を低減することはできないという事実に直面した。

【0010】そこで、第1の従来例においてゲート電極の抵抗値を低減することができない理由について種々の検討を加えた結果、以下のことを見い出した。すなわち、反応層6における窒素の面密度を低減するべく、バリア膜4Aの厚さを0.1〜1.0nm程度に小さくすると、バリア膜4Aがバリア機能を発揮することができずタングステンシリサイド(WSix )が形成されてしまうため、ゲート電極の抵抗値を低くすることができない。一方、バリア膜4Aの厚さを1.0nmを超える程度に大きくすると、バリア機能は発揮されるが、ポリシリコン膜3とタングステン膜5との間に、抵抗値が極めて大きい窒化シリコンからなる反応層6が形成されるので、ポリシリコン膜3とタングステン膜5との間の界面抵抗値が大きくなってしまう。

【0011】また、窒化タングステン膜は耐熱性に劣るため、750℃以上の熱処理が施されると、窒化タングステン膜中の窒素が多量に拡散してしまいタングステン膜になってしまうという問題もある。

【0012】第2の従来例のように、窒化チタンからなるバリア膜を用いた場合には、以下に説明する理由によって、ポリシリコン膜とタングステン膜との間に、抵抗値が極めて大きい窒化シリコンからなる反応層6が形成されるので、ポリシリコン膜3とタングステン膜5との間の界面抵抗値が大きくなってしまう。

【0013】まず、図13(a)に示すように、半導体基板1の上にはゲート絶縁膜2を介してポリシリコン膜3が形成されており、該ポリシリコン膜3には、p型のゲート電極を形成する場合にはボロン等のp型不純物がドーピングされていると共に、n型のゲート電極を形成する場合にはリン等のn型不純物がドーピングされている。次に、ポリシリコン膜3の上に窒化チタン膜4Bを堆積するため、半導体基板1を、チタンを主成分とするチタンターゲット7が配置されたチャンバー内に搬入した後、該チャンバー内にアルゴンガスと窒素ガスとの混合ガスを導入すると共に該チャンバー内において放電を起こさせる。このようにすると、アルゴンガスと窒素ガスからなるプラズマが発生し、プラズマ中の窒素イオンとポリシリコン膜3中のシリコンとが反応して、ポリシリコン膜3の表面に窒化シリコン膜からなる反応層6が形成される。そして、図13(b)に示すように、チタンターゲット7が窒化されて窒化チタン膜8が形成されると共に、窒化チタン膜8から窒化チタンが弾き飛ばされ、反応層6の上に窒化チタンからなるバリア膜4Bが形成される。

【0014】次に、半導体基板1を、タングステンを主成分とするタングステンターゲット9が配置されたチャンバー内に移送した後、該チャンバー内にアルゴンガスを導入すると共に該チャンバー内において放電を起こさせる。このようにすると、アルゴンガスからなるプラズマが発生し、プラズマ中のアルゴンイオンのスパッタリングによりタングステンターゲット9からタングステンが弾き飛ばされ、弾き飛ばされたタングステンが窒化チタン膜4Bの表面に堆積されるので、図13(c)に示すように、窒化チタン膜4Bの上に反応層6を介してタングステン膜5が形成される。

【0015】次に、半導体基板1に、MOSトランジスタのソース又はドレインとなる不純物層を形成した後、該不純物層を活性化するために例えば750℃以上の熱処理を施すと、図14(a)に示すように、バリア膜4B中の余剰な窒素がポリシリコン膜3の上部に拡散するため、図14(b)に示すように、窒化チタンからなる反応層6の厚さが大きくなる。

【0016】また、本件発明者は、熱処理温度と熱処理後のバリア膜の界面抵抗との関係についても検討を加えた。図15は、熱処理温度(℃)と、熱処理後のポリシリコン膜と高融点金属膜との間の界面抵抗(Rc )との関係を示しており、図15において、●はn型のポリシリコン膜(NPSと表示)の上に窒化タングステン(WNx )からなるバリア膜を形成した場合を示し、○はp型のポリシリコン膜(PPSと表示)の上に窒化タングステンからなるバリア膜を形成した場合を示し、◆はn型のポリシリコン膜の上に窒化チタン(TiN)からなるバリア膜を形成した場合を示し、◇はp型のポリシリコン膜の上に窒化チタンからなるバリア膜を形成した場合を示している。また、図15においては、非オーミックであるため、界面抵抗としては1mA/μm2 の電流を流した場合の抵抗値を示している。

【0017】図15から、窒化チタンからなるバリア膜4Bを用いた場合には、熱処理の温度が低くても界面抵抗が高いことが分かる。また、本件発明者らの実験では、窒化チタンからなるバリア膜4Bを用いた場合には、熱処理を施さなくても界面抵抗は高い。その理由は、図13(a)〜(c)に示すように、ポリシリコン膜3とバリア膜4Bとの間に窒化チタンからなる反応層6が形成されているためである。

【0018】また、窒化タングステンからなるバリア膜4Aを用いた場合には、窒化チタンからなるバリア膜4Bを用いた場合に比べて界面抵抗は低いが、750℃以上の温度の熱処理を施すと、界面抵抗は急激に高くなることが分かる。その理由は、窒化タングステンからなるバリア膜4Aを用いた場合に750℃以上の温度の熱処理を施すと、窒化タングステン中の窒素が拡散し、ポリシリコン膜3とタングステン膜5との間に窒化シリコンからなる反応層6が形成されるためである。

【0019】ポリシリコン膜3とタングステン膜5との間の界面抵抗(Rc )が大きくなるとMOSトランジスタの動作速度は遅くなる。すなわち、ゲート電極がAC(交流)動作をする場合、ゲート絶縁膜に発生する分布容量に対して充放電が繰り返し行なわれるため、分布界面抵抗に電流が流れるので、分布界面抵抗の影響が現われ、これによって、MOSトランジスタの動作速度は遅くなるのである。MOSトランジスタの動作速度が遅くなると、LSIの動作速度が遅くなって信号遅延時間が増加するという問題がある。LSIの動作速度が重要視される現在においては、MOSトランジスタの動作速度は、数%程度劣化するだけでも大きな問題となる。

【0020】前記に鑑み、本発明は、ポリシリコン膜と高融点金属膜との間の界面抵抗を低くすることを目的とする。

【0021】

【課題を解決するための手段】前記の目的を達成するため、本発明に係る電極構造体の形成方法は、シリコンを主成分とするシリコン含有膜の上にバリア膜を形成する工程と、前記バリア膜の上に高融点金属膜を堆積して、前記シリコン含有膜、前記バリア膜及び前記高融点金属膜からなる積層膜を形成する工程と、前記積層膜に対して750℃以上の温度で熱処理を施す工程とを備えた電極構造体の形成方法を前提とし、前記バリア膜を形成する工程は、前記シリコン含有膜の上に金属の窒化物からなる第1の金属膜を形成する工程と、前記第1の金属膜の上に、前記金属からなるか又は前記金属の窒化物からなり前記第1の金属膜よりも窒素の含有量が少ない第2の金属膜を形成する工程と、前記第2の金属膜の上に、前記金属の窒化物からなり前記第2の金属膜よりも窒素の含有量が多い第3の金属膜を形成する工程とを含む。

【0022】本発明に係る電極構造体の形成方法によると、熱処理を施した際に、第1の金属膜に含まれる窒素及び第3の金属膜に含まれる窒素の各一部は第2の金属膜の窒化に消費され、第1の金属膜に含まれる窒素のうちシリコン含有膜の窒化に寄与する窒素の量は少なくなるため、シリコン含有膜とバリア膜との界面には、シリコン窒化膜からなり抵抗値の極めて大きい反応層が形成されないか又は形成されてもその厚さは小さいので、シリコン含有膜と高融点金属膜との間の界面抵抗は低くなる。

【0023】本発明に係る電極構造体の形成方法において、前記金属はチタンであることが好ましい。

【0024】本発明に係る電極構造体の形成方法において、前記バリア膜を形成する工程は、前記金属を主成分とするターゲットの表面に形成された前記金属の窒化物膜に対して、窒素ガスが実質的に含まれない不活性ガスを用いるスパッタリングを行なうことにより、前記金属の窒化物を前記シリコン含有膜の上に堆積して前記第1の金属膜を形成した後、前記金属を前記第1の金属膜の上に堆積して前記第2の金属膜を形成する工程と、前記ターゲットに対して、窒素ガスと不活性ガスとの混合ガスを用いるスパッタリングを行なうことにより、前記金属と前記混合ガスに含まれる窒素とが反応してなる前記金属の窒化物を前記第2の金属膜の上に堆積して前記第3の金属膜を形成する工程とを含むことが好ましい。

【0025】このように、第1の金属膜を形成する工程は、窒素ガスが実質的に含まれない不活性ガスを用いるスパッタリングを行なうため、シリコン含有膜の表面にシリコン窒化膜が形成されないので、シリコン含有膜と高融点金属膜との間の界面抵抗は一層低くなる。また、同一のターゲットを用いて、スパッタリング用のガスを切り替えるだけで、第1の金属膜、第2の金属膜及び第3の金属膜を連続的に形成することができるので、スループットが向上する。

【0026】この場合、前記バリア膜を形成する工程の後に、前記第3の金属膜を形成する工程において前記ターゲットの表面に形成された前記金属の窒化物膜に対して、窒素ガスが実質的に含まれない不活性ガスを用いてスパッタリングを行なう工程をさらに備えていることが好ましい。

【0027】このように、第3の金属膜を形成する工程においてターゲットの表面に形成された金属窒化物膜を、窒素ガスが実質的に含まれない不活性ガスによりスパッタリングする工程を備えていると、金属窒化物膜に含まれる窒素の濃度が低くなるため、該金属窒化物膜を用いて形成される第1の金属膜の窒素濃度が低減するので、シリコン含有膜の窒化に寄与する窒素の量が一層少なくなる。このため、シリコン含有膜とバリア膜との界面には、シリコン窒化膜からなる反応層が一層形成され難くなると共に形成されてもその厚さは一層小さくなるので、シリコン含有膜と高融点金属膜との間の界面抵抗は一層低くなる。

【0028】本発明に係る電極構造体の形成方法において、前記バリア膜を形成する工程は、表面に前記金属の窒化物膜が形成されている前記金属を主成分とするターゲットが配置されているチャンバー内に窒素ガスが実質的に含まれない不活性ガスを導入すると共に前記チャンバー内に放電を起こさせて、前記金属の窒化物膜から弾き飛ばされた前記金属の窒化物を前記シリコン含有膜の上に堆積することにより前記第1の金属膜を形成した後、前記金属を前記第1の金属膜の上に堆積することにより前記第2の金属膜を形成する工程と、前記ターゲットが配置されている前記チャンバー内に窒素ガスと不活性ガスとの混合ガスを導入すると共に、前記チャンバー内に放電を起こさせて、前記金属と前記混合ガスに含まれる窒素とが反応してなる前記金属の窒化物を前記第2の金属膜の上に堆積することにより前記第3の金属膜を形成する工程とを含むことが好ましい。

【0029】このようにすると、第1の金属膜を形成する工程は、チャンバー内に窒素ガスが実質的に含まれない不活性ガスを導入するため、シリコン含有膜の表面にシリコン窒化膜が形成されないので、シリコン含有膜と高融点金属膜との間の界面抵抗は一層低くなる。また、同一のチャンバー内に配置された同一のターゲットを用いて、スパッタリング用のガスを切り替えるだけで、第1の金属膜、第2の金属膜及び第3の金属膜を連続的に形成することができるので、スループットが向上する。

【0030】この場合、前記バリア膜を形成する工程の後に、前記チャンバー内に窒素ガスが実質的に含まれない不活性ガスを導入すると共に前記チャンバー内に放電を起こさせる工程をさらに備えていることが好ましい。

【0031】このように、バリア膜を形成する工程の後に、チャンバー内に窒素ガスが実質的に含まれない不活性ガスを導入すると共にチャンバー内に放電を起こさせる工程を備えていると、第3の金属膜を形成する工程においてターゲットの表面に形成された金属窒化物膜を、窒素ガスが実質的に含まれない不活性ガスによりスパッタリングすることができるため、金属窒化物膜に含まれる窒素の濃度が低くなり、該金属窒化物膜を用いて形成される第1の金属膜の窒素濃度が低減する。従って、シリコン含有膜の窒化に寄与する窒素の量が一層少なくなるため、シリコン含有膜とバリア膜との界面には、シリコン窒化膜からなる反応層が一層形成され難くなると共に形成されてもその厚さは一層小さくなるので、シリコン含有膜と高融点金属膜との間の界面抵抗は一層低くなる。

【0032】本発明に係る半導体装置の製造方法は、半導体領域上にポリシリコン膜を形成する工程と、前記ポリシリコン膜の上にバリア膜を形成する工程と、前記バリア膜の上に高融点金属膜を堆積して、前記シリコン含有膜、前記バリア膜及び前記高融点金属膜からなるゲート電極を形成する工程と、前記半導体領域に前記ゲート電極をマスクとして不純物をイオン注入してソース又はドレインとなる不純物層を形成する工程と、750℃以上の温度で熱処理を施して前記不純物層を活性化させる工程とを備えた半導体装置の製造方法を前提とし、前記バリア膜を形成する工程は、前記シリコン含有膜の上に金属の窒化物からなる第1の金属膜を形成する工程と、前記第1の金属膜の上に、前記金属からなるか又は前記金属の窒化物からなり前記第1の金属膜よりも窒素の含有量が少ない第2の金属膜を形成する工程と、前記第2の金属膜の上に、前記金属の窒化物からなり前記第2の金属膜よりも窒素の含有量が多い第3の金属膜を形成する工程とを含む。

【0033】本発明に係る半導体装置の製造方法によると、本発明に係る電極構造体の形成方法を用いて半導体装置を製造するため、ソース又はドレインとなる不純物層を活性化するために750℃以上の熱処理を施しても、ゲート電極におけるポリシリコン膜と高融点金属膜との間の界面抵抗を低くすることができる。

【0034】本発明に係る半導体装置の製造方法において、前記金属はチタンであることが好ましい。

【0035】

【発明の実施の形態】(第1の実施形態)以下、本発明の第1の実施形態に係る電極構造体の形成方法として、ゲート電極の形成方法について、図1(a)〜(c)、図2(a)〜(c)及び図3を参照しながら説明する。

【0036】まず、図1(a)に示すように、シリコン基板10の上にシリコン酸化膜からなるゲート絶縁膜11を形成した後、該ゲート絶縁膜11の上に、減圧CVD法によりアモルファスシリコン膜を堆積する。

【0037】次に、アモルファスシリコン膜におけるn型ゲート電極形成領域にリン(P)イオンを10KeVの注入エネルギー及び8×1015cm-2のドーズ量でドーピングすると共に、アモルファスシリコン膜におけるp型ゲート電極形成領域にボロン(B)イオンを5KeVの注入エネルギー及び5×1015cm-2のドーズ量でドーピングする。次に、リンイオン又はボロンイオンがドーピングされたアモルファスシリコン膜に対して800℃の温度下で30秒間の熱処理を施すことにより、アモルファスシリコン膜を結晶化してn型又はp型のポリシリコン膜12を形成した後、ポリシリコン膜12の表面に形成されているシリコン酸化膜をフッ酸系の洗浄液を用いて除去する。

【0038】次に、準備工程として、図3に示すように、チタンを主成分とするチタンターゲットが配置されているチャンバー内にアルゴンガスと窒素ガスとの混合ガスを導入すると共にチャンバー内に放電を起こさせて、チタンターゲットの表面に窒化チタン膜を形成する。

【0039】次に、ウエハ入れ替え工程として、準備工程で用いた半導体基板(ウエハ)を搬出した後、図1(b)に示すように、半導体基板10を、表面に窒化チタン膜13aが形成されているチタンターゲット13が配置されたチャンバーA内に搬入する。

【0040】次に、図3に示すように、該チャンバーA内にアルゴンガスを導入すると共に該チャンバーA内において放電を起こさせる。このようにすると、アルゴンガスからなるプラズマが発生し、プラズマ中のアルゴンイオンがチタンターゲット13の表面の窒化チタン膜13aをスパッタリングするので、図1(b)に示すように、ポリシリコン膜12の表面には第1の金属膜としての第1の窒化チタン膜14が堆積される。尚、この工程において、チタンターゲット13の表面に形成されている窒化チタン膜13aは消滅する。

【0041】次に、チャンバーA内へのアルゴンガスの導入及びチャンバー内での放電を継続すると、プラズマ中のアルゴンイオンがチタンターゲット13をスパッタリングするので、図1(c)に示すように、第1の窒化チタン膜14の上には第2の金属膜としてのチタン膜15が堆積される。

【0042】次に、図3に示すように、放電を一旦停止した後、チャンバーA内にアルゴンガスと窒素ガスとの混合ガスを導入すると共に、再び放電を起こさせると、図2(a)に示すように、チタン膜15の表面に、第3の金属膜としての第2の窒化チタン膜16が形成されると共に、チタンターゲット13の表面にも窒化チタン膜13aが形成される。

【0043】第1の実施形態によると、表面に窒化チタン膜13aが形成されているチタンターゲット13が配置されたチャンバーA内にアルゴンガスを導入することにより、第1の金属膜としての窒化チタン膜14と第2の金属膜としてのチタン膜15とを連続して堆積することができると共に、その後、チャンバーA内にアルゴンガスと窒素ガスとの混合ガスを導入することにより、チタン膜15の上に第3の金属膜としての窒化チタン膜16を形成することができる。すなわち、チタンターゲット13を取り替えることなく、チャンバーA内に導入するガスを切り替えるのみで、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16を連続的に形成することができるので、スループットが向上する。

【0044】尚、第2の窒化チタン膜16を形成する工程においてチタンターゲット13の表面に形成された窒化チタン膜13aを、ポリシリコン膜12の表面に第1の窒化チタン膜14を堆積する工程に用いることができる。つまり、第3の金属膜の形成工程と前述した準備工程とを同じ工程で行なうことができる。このようにするとスループットが一層向上する。

【0045】次に、図2(b)に示すように、半導体基板10を、タングステンを主成分とするタングステンターゲット17が配置されたチャンバーB内に移送した後、該チャンバーB内にアルゴンガスを導入すると共に該チャンバーB内に放電を起こさせる。このようにすると、アルゴンガスからなるプラズマが発生し、プラズマ中のアルゴンイオンがタングステンターゲット17をスパッタリングするので、第2の窒化チタン膜16の上に高融点金属膜としてのタングステン膜18が堆積される。以上説明した、ポリシリコン膜12、第1の窒化チタン膜14、チタン膜15、第2の窒化チタン膜16及びタングステン膜18により電極構造体としてのゲート電極が構成され、また、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16によりバリア膜が構成される。尚、バリア膜の厚さとしては、ゲート電極の厚さが大きくなり過ぎないようにするため、5nm〜20nm程度であることが好ましい。

【0046】次に、図示は省略しているが、半導体基板10にゲート電極をマスクとして不純物をドーピングして、ソース又はドレインとなる不純物層を形成した後、不純物を活性化するために例えば750℃以上の熱処理を施す。

【0047】ところで、ポリシリコン膜12とチタン膜15との間には第1の窒化チタン膜14が介在しているため、750℃以上の熱処理を施しても、ポリシリコン膜12の表面には、抵抗値の高いチタンシリサイド(TiSi2 )が形成されない。

【0048】また、750℃以上の熱処理工程において、第1の窒化チタン膜14中に存在する窒素はチタン膜15及びポリシリコン膜12に拡散する。この際、第1の窒化チタン膜14中及び第2の窒化チタン膜16中の過剰な窒素がチタン膜15に拡散することにより、チタン膜15が窒化チタン膜に変化するので、図2(c)に示すように、新たな窒化チタン膜19が形成される。また、第1の窒化チタン膜14中の窒素がポリシリコン膜12に拡散することにより、ポリシリコン膜12と窒化チタン膜19との界面に、シリコン及び窒素を主成分とする反応層20が形成される。

【0049】前述したように、シリコン及び窒素を主成分とする反応層20の抵抗値は極めて大きいため、反応層20の厚さが大きい場合には、ポリシリコン膜12とタングステン膜18との間の界面抵抗は高くなる。

【0050】ところが、第1の実施形態においては、第1の窒化チタン膜14の上にチタン膜15が形成されているため、第1の窒化チタン膜15中の窒素はチタン膜15の窒化に消費され、ポリシリコン膜12の窒化に寄与する窒素の量は少なくなるので、反応層20の厚さは従来に比べて著しく小さくなる。

【0051】また、熱処理工程において、第2の窒化チタン膜16中の窒素も拡散するが、第2の窒化チタン膜16の下側にチタン膜15が存在しているため、第2の窒化チタン膜16中の窒素はチタン膜15の窒化に費やされるためポリシリコン膜12に到達せず、これにより、第2の窒化チタン膜16中の窒素に起因する反応層は形成されない。

【0052】従って、第1の実施形態によると、ポリシリコン膜12とタングステン膜18との間の界面抵抗は大きく低減する。

【0053】また、第1の窒化チタン膜14の厚さとしては、3nm以下が好ましく2nm程度が最も好ましい。その理由は、第1の窒化チタン膜14の厚さが3nmを超えると、750℃以上の熱処理工程において形成される反応層20の厚さが大きくなって、ポリシリコン膜12とタングステン膜18との間の界面抵抗が高くなる恐れがあるためである。

【0054】図4(a)、(b)は、バリア膜を構成する、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16における窒素含有量の分布を示しており、横軸はバリア膜とポリシリコン膜との界面から基板側にかけての距離を示している。

【0055】図4(a)に示す窒素含有量分布においては、第1の金属膜(第1の窒化チタン膜14)のポリシリコン膜との界面ではTiNであるが、基板側に向かうにつれて窒素含有量が徐々に低下し、第1の金属膜と第2の金属膜(チタン膜15)との界面では窒素含有量は0になっている。また、第2の金属膜と第3の金属膜(第2の窒化チタン膜16)との界面では窒素含有量は0であるが、基板側に向かうにつれて窒素含有量は徐々に増加し、やがてTiNになっている。

【0056】図4(b)に示す窒素含有量分布においては、第1の金属膜(第1の窒化チタン膜14)のポリシリコン膜との界面ではTiNであるが、基板側に向かうにつれて窒素含有量が徐々に低下し、第1の金属膜と第2の金属膜(チタン膜15)との界面では窒素含有量はTiNの半分程度になっており、第2の金属膜の深さ方向の中央部では窒素含有量が大きく低減している。また、第2の金属膜と第3の金属膜(第2の窒化チタン膜16)との界面では窒素含有量はTiNの半分程度であるが、基板側に向かうにつれて窒素含有量は徐々に増加し、やがてTiNになっている。

【0057】図4(b)に示すような窒素含有量分布を実現するためには、チタン膜15を形成するためにアルゴンガスを導入する時間を短縮したり又は放電のパワーを低くしたりするとよい。

【0058】尚、第1の実施形態においては、表面に窒化チタン膜13aが形成されたチタンターゲット13を用いて、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16を連続的に形成したため、窒素含有量は徐々に減少していると共に徐々に増加しているが、窒化チタンを主成分とするターゲットとチタンを主成分とするターゲットとを使い分けると、窒素含有量は連続的に変化せずに第1及び第2の窒化チタン膜14、16と、チタン膜15との間で窒素含有量は一気に変化する。

【0059】(第2の実施形態)以下、本発明の第2の実施形態に係る電極構造体の形成方法として、ゲート電極の形成方法について、図1(a)〜(c)、図5(a)〜(c)及び図6を参照しながら説明する。

【0060】第1の実施形態と同様、図1(a)に示すように、シリコン基板10の上にゲート絶縁膜11を形成した後、該ゲート絶縁膜11の上にポリシリコン膜12を堆積する。

【0061】次に、準備工程として、図6に示すように、チタンを主成分とするチタンターゲットが配置されているチャンバー内にアルゴンガスと窒素ガスとの混合ガスを導入すると共にチャンバー内に放電を起こさせて、チタンターゲットの表面に窒化チタン膜を形成する。

【0062】次に、半導体基板10を、表面に窒化チタン膜13aが形成されているチタンターゲット13が配置されたチャンバーA内に搬入して、第1の実施形態と同様、図1(b)に示すように、ポリシリコン膜12の表面に第1の金属膜としての窒化チタン膜14を形成した後、図1(c)に示すように、第1の窒化膜14の上にチタン膜15を形成する。

【0063】次に、図6に示すように、放電をいったん停止した後、チャンバーA内にアルゴンガスと窒素ガスとの混合ガスを導入すると共に再び放電を起こさせて、図5(a)に示すように、チタン膜15の表面に、第3の金属膜としての第2の窒化チタン膜16を形成すると共に、チタンターゲット13の表面にも窒化チタン膜13aを形成する。

【0064】次に、図6に示すように、チャンバーA内にアルゴンガスのみを導入すると共にチャンバーA内での放電を継続するターゲットクリーニング工程を行なう。このようにすると、チタンターゲット13の表面の窒化チタン膜13aがアルゴンイオンによりスパッタリングされるので、窒化チタン膜13aの窒素含有量が低くなると共に、図5(b)に示すように、第2の窒化チタン膜16の上に第3の窒化チタン膜21が堆積される。

【0065】次に、図5(c)に示すように、半導体基板10を、タングステンを主成分とするタングステンターゲット17が配置されたチャンバーB内に移送した後、該チャンバーB内にアルゴンガスを導入すると共に該チャンバーB内に放電を起こさせて、第3の窒化チタン膜21の上に高融点金属膜としてのタングステン膜18を堆積する。以上説明した、ポリシリコン膜12、第1の窒化チタン膜14、チタン膜15、第2の窒化チタン膜16、第3の窒化チタン膜21及びタングステン膜18により電極構造体としてのゲート電極が構成され、また、第1の窒化チタン膜14、チタン膜15、第2の窒化チタン膜16及び第3の窒化チタン膜21によりバリア膜が構成される。

【0066】図7(a)、(b)は、バリア膜を構成する、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16における窒素含有量の分布を示しており、横軸はバリア膜とポリシリコン膜との界面から基板側にかけての距離を示している。尚、第3の窒化チタン膜21における窒素含有量については省略している。

【0067】図7(a)に示す窒素含有量分布においては、第1の金属膜(第1の窒化チタン膜14)のポリシリコン膜との界面ではTiNよりも窒素含有量が少ないと共に、基板側に向かうにつれて窒素含有量が徐々に低下し、第1の金属膜と第2の金属膜(チタン膜15)との界面では窒素含有量は0になっている。また、第2の金属膜と第3の金属膜(第2の窒化チタン膜16)との界面では窒素含有量は0であるが、基板側に向かうにつれて窒素含有量は徐々に増加し、やがてTiNになっている。

【0068】図7(b)に示す窒素含有量分布においては、第1の金属膜(第1の窒化チタン膜14)のポリシリコン膜との界面ではTiNよりも窒素含有量が少ないと共に、基板側に向かうにつれて窒素含有量が徐々に低下し、第1の金属膜と第2の金属膜(チタン膜15)との界面では窒素含有量はTiNの半分以下になっている。また、第2の金属膜と第3の金属膜(第2の窒化チタン膜16)との界面では窒素含有量はTiNの半分程度であるが、基板側に向かうにつれて窒素含有量は徐々に増加し、やがてTiNになっている。

【0069】第2の実施形態によると、チタン膜15の表面に第2の窒化チタン膜16を形成した後、チャンバーA内にアルゴンガスのみを導入するターゲットクリーニング工程を行なうため、第1の窒化チタン膜14の堆積に用いられる窒化チタン膜13aの窒素含有量が低くなる。従って、図7(a)と図4(a)との対比、及び図7(b)と図4(b)との対比から分かるように、第1の窒化チタン膜14におけるポリシリコン膜12との界面近傍の窒素含有量は第1の実施形態に比べて低減している。このため、電極構造体に対して750℃以上の熱処理が施されたときに、第1の窒化チタン膜14からポリシリコン膜12に拡散する窒素の量が低減するので、ポリシリコン膜12の表面に形成される反応層20(図2(c)を参照)の厚さが一層薄くなるか又は反応層20は実質的に形成されなくなり、ポリシリコン膜12とタングステン膜18との間の界面抵抗は一層低くなる。

【0070】図8は、ターゲットクリーニング工程の時間を0秒、1秒、2秒、3秒、5秒及び7秒と変化させた場合における、第1の窒化チタン膜14及びチタン膜15からなる積層膜の膜厚と、ポリシリコン膜12とタングステン膜18との間の界面抵抗との関係を示している。この場合、ポリシリコン膜12はp型ゲート電極を構成する。尚、図8は、300WのDCパワーで第1の窒化チタン膜14及びチタン膜15を形成し、2000WのDCパワーで20秒間放電を行なって10nmの一定の厚さを持つ第2の窒化チタン膜16を形成し、1000WのDCパワーでターゲットクリーニング工程を行なった場合の実験データである。また、第2の窒化膜16の上には、1000WのDCパワーで60nmの膜厚を持つタングステン膜18を形成した。尚、積層膜を形成した後の熱処理として、760℃の温度下における240分の炉処理と、975℃の温度下における30秒のランプアニール処理とを実施した。

【0071】図8から分かるように、ターゲットクリーニング工程の時間が長くなると、第1の窒化チタン膜14における窒素の含有量が低減するため、反応膜20が形成され難くなり、これによって、界面抵抗が低くなる。また、この傾向は第1の窒化チタン膜14及びチタン膜15の合計膜厚が小さいときに顕著に現われる。尚、図8における膜厚が0である点は、従来例(窒化チタンの単層膜)に相当する。

【0072】図9は、ターゲットクリーニング時間と、第1の窒化チタン膜14とチタン膜15との積層膜に含まれる窒素の量との関係を示している。図9において、●はターゲットクリーニングを行なわない第1の実施形態に相当し、○はターゲットクリーニングを行なう第2の実施形態に相当する。図9から分かるように、ターゲットクリーニングの時間の増加と、積層膜中の窒素量の減少とは直線的な関係を有している。

【0073】(第3の実施形態)以下、本発明の第3の実施形態に係る半導体装置の製造方法について、図10(a)、(b)及び図11(a)、(b)を参照しながら説明する。

【0074】まず、図10(a)に示すように、半導体基板30の上に、ゲート絶縁膜となるシリコン酸化膜31を形成した後、該シリコン酸化膜31の上にポリシリコン膜32を堆積する。

【0075】次に、第1の実施形態と同様の方法で、ポリシリコン膜32の上に、バリア膜となる第1の窒化チタン膜34、チタン膜35及び第2の窒化チタン膜36を順次形成した後、第2の窒化チタン膜36の上にタングステン膜38を堆積して、ポリシリコン膜32、第1の窒化チタン膜34、チタン膜35、第2の窒化チタン膜36及びタングステン膜38からなる積層体を形成し、その後、該積層体の上に、窒化シリコン膜からなりゲート電極を形成するためのハードマスク39を形成する。

【0076】次に、図10(b)に示すように、積層体に対してハードマスク39を用いてエッチングを行なって積層体からなるゲート電極を形成した後、該ゲート電極を洗浄する。

【0077】次に、半導体基板30にゲート電極をマスクとして不純物をドーピングして低濃度不純物層40を形成した後、半導体基板30の上に全面に亘ってシリコン窒化膜を堆積し、その後、該シリコン窒化膜に対して異方性エッチングを行なうことにより、図11(a)に示すように、ゲート電極の壁面にサイドウォール41を形成する。次に、半導体基板30にゲート電極及びサイドウォール41をマスクとして不純物をドーピングして高濃度不純物層43を形成する。

【0078】次に、半導体基板30に対して750℃以上の温度の熱処理を施して、低濃度不純物層40及び高濃度不純物層43を活性化する。このようにすると、第1の窒化チタン膜34及び第2の窒化チタン膜36中に存在する窒素がチタン膜35に拡散するため、図11(b)に示すように、ポリシリコン膜32とタングステン膜38との間に新たな窒化チタン膜45が形成されると共に、ポリシリコン膜32と窒化チタン膜45との界面に、シリコン及び窒素を主成分とする反応層56が形成される。

【0079】第3の実施形態によると、750℃以上の熱処理の後においても、チタンシリサイド層が形成されないと共に界面抵抗を低減できるので、MOSトランジスタの動作速度の低下を防止することができる。また、チタンシリサイド層が形成されることに起因してタングステン膜38が膜剥がれする事態も防止できる。

【0080】尚、第1〜第3の実施形態においては、高融点金属膜として、タングステン膜を用いたが、これに代えて、モリブデン(Mo)膜、タングステンシリサイド(WSix )膜又はモリブデンシリサイド(MoSi2 )膜を用いてもよい。

【0081】また、バリア膜を構成する金属としては、チタンを用いたが、これに代えて、タンタル(Ta)又はタングステン(W)等を用いてもよい。

【0082】さらに、第1〜第3の実施形態においては、シリコン基板を用いたが、これに代えて、SOI基板を用いてもよい。

【0083】

【発明の効果】本発明に係る電極構造体の形成方法によると、750℃以上の熱処理を施しても、シリコン含有膜の表面には抵抗値の大きい金属シリサイドが形成され難いと共に、シリコン含有膜とバリア膜との界面に抵抗値の極めて大きい反応層が形成されないか又は形成されてもその厚さは小さくなるので、シリコン含有膜と高融点金属膜との間の界面抵抗は低くなる。

【0084】また、本発明に係る半導体装置の製造方法によると、ソース又はドレインとなる不純物層を活性化するために750℃以上の熱処理を施しても、ゲート電極におけるポリシリコン膜と高融点金属膜との間の界面抵抗を低くすることができる。従って、MOSトランジスタの遅延時間を低減して、MOSトランジスタの動作速度の向上を図ることができる。

【図面の簡単な説明】

【図1】(a)〜(c)は、第1の実施形態に係る電極構造体の形成方法の各工程を示す断面図である。

【図2】(a)〜(c)は、第1の実施形態に係る電極構造体の形成方法の各工程を示す断面図である。

【図3】第1の実施形態においてチャンバー内に導入するガスの種類と放電との関係を示すシーケンス図である。

【図4】(a)、(b)は第1の実施形態により得られるバリア膜における、界面からの距離と窒素含有量との関係を示す図である。

【図5】(a)〜(c)は、第2の実施形態に係る電極構造体の形成方法の各工程を示す断面図である。

【図6】第2の実施形態においてチャンバー内に導入するガスの種類と放電との関係を示すシーケンス図である。

【図7】(a)、(b)は第2の実施形態により得られるバリア膜における、界面からの距離と窒素含有量との関係を示す図である。

【図8】第2の実施形態により得られる第1の窒化チタン膜及びチタン膜からなる積層膜の膜厚と、ポリシリコン膜とタングステン膜との間の界面抵抗との関係を示す図である。

【図9】第2の実施形態において行なわれるターゲットクリーニング時間と、第1の窒化チタン膜及びチタン膜からなる積層膜に含まれる窒素の量との関係を示す図である。

【図10】(a)、(b)は第3の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図11】(a)、(b)は第3の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図12】(a)は第1の従来例に係る電極構造体の断面図であり、(b)は第2の従来例に係る電極構造体の断面図であり、(c)は第1の従来例に係る電極構造体に対して750℃以上の熱処理を施したときの断面図である。

【図13】(a)〜(c)は第2の従来例に係る電極構造体の形成方法の各工程を示す断面図である。

【図14】(a)、(b)は第2の従来例に係る電極構造体の形成方法の問題点を説明する断面図である。

【図15】第1の従来例及び第2の従来例に係る電極構造体の形成方法により得られるゲート電極に対する熱処理の温度と、熱処理後の界面抵抗との関係を示す図である。

【符号の説明】

A チャンバー

B チャンバー

10 半導体基板

11 ゲート絶縁膜

12 ポリシリコン膜

13 チタンターゲット

13a 窒化チタン膜

14 第1の窒化チタン膜(第1の金属膜)

15 チタン膜(第2の金属膜)

16 第2の窒化チタン膜(第3の金属膜)

17 タングステンターゲット

18 タングステン膜

19 窒化チタン膜

20 反応層

21 第3の窒化チタン膜

30 半導体基板

31 ゲート絶縁膜

32 ポリシリコン膜

34 第1の窒化チタン膜

35 チタン膜

36 第2の窒化チタン膜

38 タングステン膜

39 ハードマスク

40 低濃度不純物層

41 サイドウォール

43 高濃度不純物層

45 窒化チタン膜

46 反応層

【特許請求の範囲】

【請求項1】 シリコンを主成分とするシリコン含有膜の上にバリア膜を形成する工程と、前記バリア膜の上に高融点金属膜を堆積して、前記シリコン含有膜、前記バリア膜及び前記高融点金属膜からなる積層膜を形成する工程と、前記積層膜に対して750℃以上の温度で熱処理を施す工程とを備えた電極構造体の形成方法において、前記バリア膜を形成する工程は、前記シリコン含有膜の上に金属の窒化物からなる第1の金属膜を形成する工程と、前記第1の金属膜の上に、前記金属からなるか又は前記金属の窒化物からなり前記第1の金属膜よりも窒素の含有量が少ない第2の金属膜を形成する工程と、前記第2の金属膜の上に、前記金属の窒化物からなり前記第2の金属膜よりも窒素の含有量が多い第3の金属膜を形成する工程とを含むことを特徴とする電極構造体の形成方法。

【請求項2】 前記金属はチタンであることを特徴とする請求項1に記載の電極構造体の形成方法。

【請求項3】 前記バリア膜を形成する工程は、前記金属を主成分とするターゲットの表面に形成された前記金属の窒化物膜に対して、窒素ガスが実質的に含まれない不活性ガスを用いるスパッタリングを行なうことにより、前記金属の窒化物を前記シリコン含有膜の上に堆積して前記第1の金属膜を形成した後、前記金属を前記第1の金属膜の上に堆積して前記第2の金属膜を形成する工程と、前記ターゲットに対して、窒素ガスと不活性ガスとの混合ガスを用いるスパッタリングを行なうことにより、前記金属と前記混合ガスに含まれる窒素とが反応してなる前記金属の窒化物を前記第2の金属膜の上に堆積して前記第3の金属膜を形成する工程とを含むことを特徴とする請求項1に記載の電極構造体の形成方法。

【請求項4】 前記バリア膜を形成する工程の後に、前記第3の金属膜を形成する工程において前記ターゲットの表面に形成された前記金属の窒化物膜に対して、窒素ガスが実質的に含まれない不活性ガスを用いてスパッタリングを行なう工程をさらに備えていることを特徴とする請求項3に記載の電極構造体の形成方法。

【請求項5】 前記バリア膜を形成する工程は、表面に前記金属の窒化物膜が形成されている前記金属を主成分とするターゲットが配置されているチャンバー内に窒素ガスが実質的に含まれない不活性ガスを導入すると共に前記チャンバー内に放電を起こさせて、前記金属の窒化物膜から弾き飛ばされた前記金属の窒化物を前記シリコン含有膜の上に堆積することにより前記第1の金属膜を形成した後、前記金属を前記第1の金属膜の上に堆積することにより前記第2の金属膜を形成する工程と、前記ターゲットが配置されている前記チャンバー内に窒素ガスと不活性ガスとの混合ガスを導入すると共に、前記チャンバー内に放電を起こさせて、前記金属と前記混合ガスに含まれる窒素とが反応してなる前記金属の窒化物を前記第2の金属膜の上に堆積することにより前記第3の金属膜を形成する工程とを含むことを特徴とする請求項1に記載の電極構造体の形成方法。

【請求項6】 前記バリア膜を形成する工程の後に、前記チャンバー内に窒素ガスが実質的に含まれない不活性ガスを導入すると共に前記チャンバー内に放電を起こさせる工程をさらに備えていることを特徴とする請求項5に記載の電極構造体の形成方法。

【請求項7】 半導体領域上にポリシリコン膜を形成する工程と、前記ポリシリコン膜の上にバリア膜を形成する工程と、前記バリア膜の上に高融点金属膜を堆積して、前記シリコン含有膜、前記バリア膜及び前記高融点金属膜からなるゲート電極を形成する工程と、前記半導体領域に前記ゲート電極をマスクとして不純物をイオン注入してソース又はドレインとなる不純物層を形成する工程と、750℃以上の温度で熱処理を施して前記不純物層を活性化させる工程とを備えた半導体装置の製造方法において、前記バリア膜を形成する工程は、前記シリコン含有膜の上に金属の窒化物からなる第1の金属膜を形成する工程と、前記第1の金属膜の上に、前記金属からなるか又は前記金属の窒化物からなり前記第1の金属膜よりも窒素の含有量が少ない第2の金属膜を形成する工程と、前記第2の金属膜の上に、前記金属の窒化物からなり前記第2の金属膜よりも窒素の含有量が多い第3の金属膜を形成する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項8】 前記金属はチタンであることを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項1】 シリコンを主成分とするシリコン含有膜の上にバリア膜を形成する工程と、前記バリア膜の上に高融点金属膜を堆積して、前記シリコン含有膜、前記バリア膜及び前記高融点金属膜からなる積層膜を形成する工程と、前記積層膜に対して750℃以上の温度で熱処理を施す工程とを備えた電極構造体の形成方法において、前記バリア膜を形成する工程は、前記シリコン含有膜の上に金属の窒化物からなる第1の金属膜を形成する工程と、前記第1の金属膜の上に、前記金属からなるか又は前記金属の窒化物からなり前記第1の金属膜よりも窒素の含有量が少ない第2の金属膜を形成する工程と、前記第2の金属膜の上に、前記金属の窒化物からなり前記第2の金属膜よりも窒素の含有量が多い第3の金属膜を形成する工程とを含むことを特徴とする電極構造体の形成方法。

【請求項2】 前記金属はチタンであることを特徴とする請求項1に記載の電極構造体の形成方法。

【請求項3】 前記バリア膜を形成する工程は、前記金属を主成分とするターゲットの表面に形成された前記金属の窒化物膜に対して、窒素ガスが実質的に含まれない不活性ガスを用いるスパッタリングを行なうことにより、前記金属の窒化物を前記シリコン含有膜の上に堆積して前記第1の金属膜を形成した後、前記金属を前記第1の金属膜の上に堆積して前記第2の金属膜を形成する工程と、前記ターゲットに対して、窒素ガスと不活性ガスとの混合ガスを用いるスパッタリングを行なうことにより、前記金属と前記混合ガスに含まれる窒素とが反応してなる前記金属の窒化物を前記第2の金属膜の上に堆積して前記第3の金属膜を形成する工程とを含むことを特徴とする請求項1に記載の電極構造体の形成方法。

【請求項4】 前記バリア膜を形成する工程の後に、前記第3の金属膜を形成する工程において前記ターゲットの表面に形成された前記金属の窒化物膜に対して、窒素ガスが実質的に含まれない不活性ガスを用いてスパッタリングを行なう工程をさらに備えていることを特徴とする請求項3に記載の電極構造体の形成方法。

【請求項5】 前記バリア膜を形成する工程は、表面に前記金属の窒化物膜が形成されている前記金属を主成分とするターゲットが配置されているチャンバー内に窒素ガスが実質的に含まれない不活性ガスを導入すると共に前記チャンバー内に放電を起こさせて、前記金属の窒化物膜から弾き飛ばされた前記金属の窒化物を前記シリコン含有膜の上に堆積することにより前記第1の金属膜を形成した後、前記金属を前記第1の金属膜の上に堆積することにより前記第2の金属膜を形成する工程と、前記ターゲットが配置されている前記チャンバー内に窒素ガスと不活性ガスとの混合ガスを導入すると共に、前記チャンバー内に放電を起こさせて、前記金属と前記混合ガスに含まれる窒素とが反応してなる前記金属の窒化物を前記第2の金属膜の上に堆積することにより前記第3の金属膜を形成する工程とを含むことを特徴とする請求項1に記載の電極構造体の形成方法。

【請求項6】 前記バリア膜を形成する工程の後に、前記チャンバー内に窒素ガスが実質的に含まれない不活性ガスを導入すると共に前記チャンバー内に放電を起こさせる工程をさらに備えていることを特徴とする請求項5に記載の電極構造体の形成方法。

【請求項7】 半導体領域上にポリシリコン膜を形成する工程と、前記ポリシリコン膜の上にバリア膜を形成する工程と、前記バリア膜の上に高融点金属膜を堆積して、前記シリコン含有膜、前記バリア膜及び前記高融点金属膜からなるゲート電極を形成する工程と、前記半導体領域に前記ゲート電極をマスクとして不純物をイオン注入してソース又はドレインとなる不純物層を形成する工程と、750℃以上の温度で熱処理を施して前記不純物層を活性化させる工程とを備えた半導体装置の製造方法において、前記バリア膜を形成する工程は、前記シリコン含有膜の上に金属の窒化物からなる第1の金属膜を形成する工程と、前記第1の金属膜の上に、前記金属からなるか又は前記金属の窒化物からなり前記第1の金属膜よりも窒素の含有量が少ない第2の金属膜を形成する工程と、前記第2の金属膜の上に、前記金属の窒化物からなり前記第2の金属膜よりも窒素の含有量が多い第3の金属膜を形成する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項8】 前記金属はチタンであることを特徴とする請求項7に記載の半導体装置の製造方法。

【図1】

【図2】

【図12】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図11】

【図13】

【図14】

【図15】

【図2】

【図12】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図11】

【図13】

【図14】

【図15】

【公開番号】特開2001−332511(P2001−332511A)

【公開日】平成13年11月30日(2001.11.30)

【国際特許分類】

【出願番号】特願2000−218326(P2000−218326)

【出願日】平成12年7月19日(2000.7.19)

【出願人】(000005821)松下電器産業株式会社 (73,050)

【Fターム(参考)】

【公開日】平成13年11月30日(2001.11.30)

【国際特許分類】

【出願日】平成12年7月19日(2000.7.19)

【出願人】(000005821)松下電器産業株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]