電気信号の伝送回路、IC、プリント配線板、機器およびシステム

【課題】CMOS伝送回路において、レシーバの動作を不安定にしたり不要輻射を放出したりするリンギングの発生を抑制した電気信号の伝送回路を提供する。

【解決手段】本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、CMOSドライバのPMOS FET1と並列にアノード電極がドライバ出力端子につながれるように第1のダイオード6を接続し、CMOSドライバのNMOS FET2と並列にカソード電極がドライバ出力端子につながれるように第2のダイオード7を接続し、PMOS FET1のデバイストランスコンダクタンスと第1のダイオード6の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにし、NMOS FET2のデバイストランスコンダクタンスと第2のダイオード7の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路である。

【解決手段】本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、CMOSドライバのPMOS FET1と並列にアノード電極がドライバ出力端子につながれるように第1のダイオード6を接続し、CMOSドライバのNMOS FET2と並列にカソード電極がドライバ出力端子につながれるように第2のダイオード7を接続し、PMOS FET1のデバイストランスコンダクタンスと第1のダイオード6の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにし、NMOS FET2のデバイストランスコンダクタンスと第2のダイオード7の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電気信号の伝送回路、IC、プリント配線板および電子・情報・通信の機器やシステムに関する。

【背景技術】

【0002】

電気信号の伝送回路は、図11および図12(a)に示すように、信号を送り出すドライバ、信号を伝える伝送線および信号を受け取るレシーバとで構成される。

このような伝送回路において信号がレシーバとドライバの間で反射を繰り返すと、図12(b)に示すようにリンギングを生じる。リンギングはレシーバの動作を不安定にしたり不要輻射を放出したりする。特に不要輻射は、他の電子部品・機器にノイズを誘導するため、大きな問題になっている。

【0003】

信号がレシーバやドライバで反射されないようにするためには、「インピーダンスを整合させること」すなわち「ドライバの出力インピーダンス、伝送線の特性インピーダンスそしてレシーバの入力インピーダンスを等しい値にすること」が求められる。インピーダンスを一致させることにより、信号がレシーバやドライバで反射されることがなくなり、図12(c)に示すようにリンギングを生じない。

【0004】

しかし、現実にはドライバの出力インピーダンスやレシーバの入力インピーダンスを伝送線の特性インピーダンスと一致させることが難しい。そこで「リンギング発生の第一要因」すなわち「レシーバでの反射」を無くすための工夫が施される。その基本的な方法が、図13〜図15に示すように、伝送線のレシーバ側に終端抵抗を挿入することである(例えば特許文献1参照)。

【0005】

一方、信号伝送の主流はCMOS伝送回路であり、ドライバやレシーバの入力段には図16に示すようなCMOS回路(ドライバに例を採るとPMOSFET1とNMOSFET2が対になって構成される回路)が用いられている。したがって、CMOSレシーバの入力インピーダンスは図17の等価回路に示すように、伝送線の特性インピーダンスZ0が純抵抗であるのに対して容量性になる。しかも、CMOSレシーバの入力容量は入力電圧に依存して変化する。すなわち、伝送線の特性インピーダンスZ0とCMOSレシーバの入力インピーダンスを一致させることは理論的に不可能である。そこで、CMOS伝送回路では、信号がレシーバで反射されることを前提として、レシーバからの反射波をドライバ側で吸収させるために図18に示すような方式が一般的に用いられている。

【0006】

しかし、CMOSドライバの出力抵抗も非線形であり、抵抗値がドライバの出力電圧に依存して変化する。このため、図18のように伝送線のドライバ側に終端抵抗を接続したとしても、CMOSドライバの出力インピーダンスを伝送線の特性インピーダンスと完全に一致させることはできない。

すなわち、従来の方法ではCMOS伝送回路のリンギングが全く生じないようにすることはできない。

【0007】

なお、終端抵抗は次のような方法で取り付けられたり、形成されたりする。

1)CMOS ICに終端抵抗を外付けする方法

個別抵抗素子をCMOSドライバと伝送線との間に接続する。ただし、リード線や抵抗素子が持っている寄生成分の影響が大きいために、完全な整合をとることは難しい。

2)CMOS IC内に終端抵抗を組み込む方法

i) ポリシリコン膜で抵抗を形成する。

ii) 拡散層あるいはウエルで抵抗を形成する。

iii) FETで抵抗を形成する。

【0008】

FET抵抗の基本的な形としては、図19に示すような2素子終端と図20に示すような相補型パスゲートがある。広い電圧範囲で線形性を確保できることから相補型パスゲートが広く用いられる。また、抵抗値の調整を可能とするため、図21に例を示すように、複数のFET抵抗を並列に接続したり、それらを構成する個別のFET抵抗ごとにデジタル信号で制御したりする方法がある。

なお、i)とii)は抵抗値を十分な精度で制御することが難しい。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開平8−195775号公報(段落[0018]、図1)

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明の一態様は、CMOS伝送回路において、レシーバの動作を不安定にしたり不要輻射を放出したりするリンギングの発生を抑制することを課題とする。

【課題を解決するための手段】

【0011】

課題を解決する上で最大の障害は、CMOSドライバの出力インピーダンスが出力電圧に依存して変化することである。本発明の一態様では、この障害を乗り越えるためにCMOSドライバのPMOS FET1と並列にゲート端子がドライバ出力端子につながれているNMOS FETを接続し、CMOSドライバのNMOS FET2と並列にゲート端子がドライバ出力端子につながれているPMOS FETを接続し、これら4つのMOS FETをデバイストランスコンダクタンスが等しい値となるようにする。こうすることによって、CMOSドライバの出力インピーダンスが電圧に依存しない一定値となる。その結果、CMOSドライバの出力インピーダンスを伝送線の特性インピーダンスに一致させることが可能になる。

【0012】

また、本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、

前記CMOSドライバのPMOS FETと並列にアノード電極がドライバ出力端子につながれるように第1のダイオードを接続し、

前記CMOSドライバのNMOS FETと並列にカソード電極がドライバ出力端子につながれるように第2のダイオードを接続し、

前記PMOS FETのデバイストランスコンダクタンスと前記第1のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにし、

前記NMOS FETのデバイストランスコンダクタンスと前記第2のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路である。

【0013】

本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、

前記CMOSドライバは、PMOS FETと、NMOS FETと、第1および第2のダイオードとを有し、

前記PMOS FETおよび前記NMOS FETそれぞれのゲート端子はドライバ入力端子に電気的に接続され、

前記PMOS FETのドレイン端子および前記第1のダイオードのカソード電極それぞれは、電源線に電気的に接続され、

前記PMOS FETのソース端子、前記第1のダイオードのアノード電極、前記NMOS FETのドレイン端子および前記第2のダイオードのカソード電極それぞれは、ドライバ出力端子に電気的に接続され、

前記NMOS FETのソース端子および前記第2のダイオードのアノード電極それぞれは、接地線に電気的に接続され、

前記ドライバ出力端子は、前記伝送線の始端に電気的に接続され、

前記伝送線の終端は、前記CMOSレシーバの入力端子に電気的に接続され、

前記PMOS FETのデバイストランスコンダクタンスは、前記第1のダイオードの(飽和電流)/(理想係数×熱電圧)2と等しく、

前記NMOS FETのデバイストランスコンダクタンスは、前記第2のダイオードの(飽和電流)/(理想係数×熱電圧)2と等しいことを特徴とする電気信号の伝送回路である。

【0014】

ただし、前記PMOS FETのデバイストランスコンダクタンスと前記第1のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しい、および前記NMOS FETのデバイストランスコンダクタンスと前記第2のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しいそれぞれの「等しい」の意味は、設計仕様あるいは製造仕様の上で等しいという意味であり物理的に全く同じ値になるという意味ではない。設計仕様あるいは製造仕様の上で等しいとは、物理量が設計上あるいは製造上の許容ばらつきの範囲内にあることを意味している。なお、このように「等しい」の意味を解釈するのは、本明細書中においてすべて同様である。

【0015】

また、上記の本発明の一態様において、前記PMOS FETのデバイストランスコンダクタンスと前記第1のダイオードの(飽和電流)/(理想係数×熱電圧)2と前記NMOS FETのデバイストランスコンダクタンスと前記第2のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにすることが好ましい。

【0016】

本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、

前記CMOSドライバの第1のPMOS FETと並列にゲート端子がドライバ出力端子につながれている第2のNMOS FETを接続し、

前記CMOSドライバの第1のNMOS FETと並列にゲート端子がドライバ出力端子につながれている第2のPMOS FETを接続し、

前記第1のPMOS FETのデバイストランスコンダクタンスと前記第2のNMOS FETのデバイストランスコンダクタンスが等しくなるようにし、

前記第1のNMOS FETのデバイストランスコンダクタンスと前記第2のPMOS FETのデバイストランスコンダクタンスが等しくなるようにしたことを特徴とする電気信号の伝送回路である。

【0017】

本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、

前記CMOSドライバは、第1および第2のPMOS FETと、第1および第2のNMOS FETとを有し、

前記第1のPMOS FETおよび前記第1のNMOS FETそれぞれのゲート端子はドライバ入力端子に電気的に接続され、

前記第1のPMOS FETのドレイン端子および前記第2のNMOS FETのドレイン端子それぞれは、電源線に電気的に接続され、

前記第1のPMOS FETのソース端子、前記第2のNMOS FETのソース端子、前記第2のNMOS FETのゲート端子、前記第1のNMOS FETのドレイン端子、前記第2のPMOS FETのドレイン端子および前記第2のPMOS FETのゲート端子それぞれは、ドライバ出力端子に電気的に接続され、

前記第1のNMOS FETのソース端子および前記第2のPMOS FETのソース端子それぞれは、接地線に電気的に接続され、

前記ドライバ出力端子は、前記伝送線の始端に電気的に接続され、

前記伝送線の終端は、前記CMOSレシーバの入力端子に電気的に接続され、

前記第1のPMOS FETのデバイストランスコンダクタンスは、前記第2のNMOS FETのデバイストランスコンダクタンスと等しく、

前記第1のNMOS FETのデバイストランスコンダクタンスは、前記第2のPMOS FETのデバイストランスコンダクタンスと等しいことを特徴とする電気信号の伝送回路である。

【0018】

ただし、前記第1のPMOS FETのデバイストランスコンダクタンスと前記第2のNMOS FETのデバイストランスコンダクタンスとが等しい、および前記第1のNMOS FETのデバイストランスコンダクタンスと前記第2のPMOS FETのデバイストランスコンダクタンスとが等しいそれぞれの「等しい」の意味は、設計仕様あるいは製造仕様の上で等しいという意味であり物理的に全く同じ値になるという意味ではない。設計仕様あるいは製造仕様の上で等しいとは、物理量が設計上あるいは製造上の許容ばらつきの範囲内にあることを意味している。なお、このように「等しい」の意味を解釈するのは、本明細書中においてすべて同様である。

【0019】

また、上記の本発明の一態様において、前記第1のPMOS FET、前記第2のPMOS FET、前記第1のNMOS FETおよび前記第2のNMOS FETそれぞれのデバイストランスコンダクタンスが等しい値となるようにすることが好ましい。

【0020】

また、上記の本発明の一態様において、前記第1のPMOS FET、前記第2のPMOS FET、前記第1のNMOS FETおよび前記第2のNMOS FETそれぞれを同一半導体基板上に集積回路として構成することも可能である。

【0021】

本発明の一態様は、上記の本発明の一態様の電気信号の伝送回路を備えたIC、プリント配線板、機器またはシステムである。

【発明の効果】

【0022】

本発明の一態様を適用することにより、CMOSドライバの出力インピーダンスと伝送線の特性インピーダンスとを等しくすることが可能となり、CMOSレシーバからの反射波を吸収できるので、リンギングの発生を抑制することができる。したがって、本発明の一態様を用いて構成された伝送回路を搭載したIC、プリント配線板および電子・情報・通信の機器やシステムは全て大きな性能向上が図られる。

【図面の簡単な説明】

【0023】

【図1】本発明の一態様を示すための図。

【図2】本発明の一態様の動作を説明するための図。

【図3】本発明の一態様におけるPMOSFETおよびダイオードの電圧-電流特性を示すための図。

【図4】本発明の一態様における電圧-電流特性を示すための図。

【図5】本発明の一態様であるMOSダイオードを用いた場合の例を示すための図。

【図6】MOSダイオードを用いた場合の本発明の一態様の動作を説明するための図。

【図7】MOSダイオードを用いた場合の本発明の一態様における各MOSFETの電圧-電流特性を示すための図。

【図8】本発明の一態様における電圧-電流特性を示すための図。

【図9】CMOSドライバのレイアウト例を示すための図であり、(a)は平面図、(b)は(a)に示すA−A'部(PMOS FET)の断面図。

【図10】本発明の一態様を示すための図。

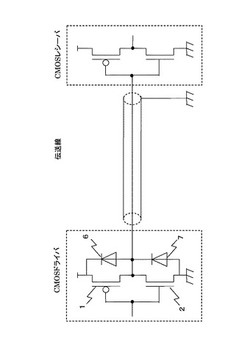

【図11】本発明の対象となる信号伝送回路がドライバ、伝送線およびレシーバで構成されることを示すための図。

【図12】信号を伝送する際にリンギングが生じることを示すための図であり、(a)は信号伝送回路の構成図、(b)はレシーバおよびドライバで反射がある場合(インピーダンスが整合していない場合)の波形、(c)はレシーバおよびドライバでの反射がない場合(インピーダンスが整合している場合)の波形。

【図13】レシーバ側に付けられた終端抵抗の例を示すための図。

【図14】レシーバ側に付けられた終端抵抗の例を示すための図。

【図15】レシーバ側に付けられた終端抵抗の例を示すための図。

【図16】CMOS回路を用いた伝送回路の代表的な構成を示すための図。

【図17】CMOS伝送回路の等価回路図であり、伝送線の特性インピーダンスが抵抗であるのに対しCMOS回路の入力インピーダンスが容量性であることを示すための図。

【図18】「CMOS伝送回路で広く用いられている抵抗終端法」すなわち「伝送線のレシーバ側に終端抵抗を挿入する方法」を示すための図。

【図19】CMOSIC内で終端抵抗を作りこむ際に広く用いられるのがFET抵抗であり、その一つの例としての2素子終端回路を示すための図であり、(a)はPMOS FETで構成した2素子終端回路、(b)はNMOS FETで構成した2素子終端回路。

【図20】CMOSIC内で終端抵抗を作りこむ際に広く用いられるのがFET抵抗であり、その一つの例としての相補型パスゲートを示すための図であり、(a)は相補型パスゲート回路、(b)は相補型パスゲート回路の電圧‐電流特性を示す図。

【図21】複数の相補型パスゲートを並列に接続して抵抗値を調整できるように構成された終端抵抗の回路の例を示すための図。

【発明を実施するための形態】

【0024】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0025】

(第1の実施形態)

図1は、本発明の一態様を説明するための図である。

本発明の一態様のCMOSドライバは、PMOS FETとNMOS FETに第1および第2のダイオード6,7を加えて構成される。PMOS FET1とNMOS FET2が通常のドライバを構成するトランジスタであり、第1のダイオード6と第2のダイオード7が本発明の一態様の特徴をなすものである。

【0026】

第1のダイオード6は、カソード電極がPMOS FET1のドレイン端子すなわち電源線に接続され、アノード電極がPMOS FET1のソース端子すなわちドライバ出力端子に接続されている。第2のダイオード7は、カソード電極がNMOS FET2のドレイン端子すなわちドライバ出力端子に接続され、アノード電極がNMOS FET2のソース端子すなわち接地線に接続されている。

【0027】

PMOS FET1と第1のダイオード6は対になって働き、ドライバ入力信号が高い電圧値(以降"H"と記す)から低い電圧値(以降"L"と記す)に変わると導通状態になり、伝送線およびレシーバ入力部を"H"状態にする。

一方、NMOS FET2は第2のダイオード7と対になって働き、ドライバ入力信号が"L"から"H"に変わると導通状態になり、伝送線およびレシーバ入力部を"L"状態にする。

【0028】

以下、「ドライバの入力信号電圧が"H"から"L"に変わって伝送線およびレシーバ入力部の電圧が"L"から"H"へ切り替わる場合」を例として動作の詳細を述べる。

「ドライバの入力電圧vinが"H"から"L"に変わり、レシーバで反射された信号波が戻ってくるまで"L"の状態が続いている場合」には、ドライバ出力端子すなわち伝送線始端の電圧vは図2に示すように階段状の変化をする。もしドライバの出力インピーダンスが伝送線の特性インピーダンスと一致していない場合は、この反射波がドライバで再反射されてレシーバに戻って行く。このようにしてレシーバとドライバの間で反射が繰り返されると、リンギングが発生する。

【0029】

このようなリンギングを発生させないためには、ドライバの出力インピーダンスを伝送線の特性インピーダンスと等しくすることで、ドライバがレシーバから戻されてきた最初の反射波を吸収するようにしなければならない。そのためには、図3に示すPMOSFET1と第1のダイオード6の電圧-電流特性において負電圧領域におけるPMOSFET1の電流値と第1のダイオード6の電流値の和が図4に示すように直線的に変化するようにすればよい。そうすることにより、ドライバの出力インピーダンスが電圧に依存しない一定の抵抗値となり、ドライバの出力インピーダンスと伝送線の特性インピーダンスを一致させることが可能になる。

【0030】

具体的には、図2においてPMOSFET1のデバイストランスコンダクタンスβpと第1のダイオード6の飽和電流ISをβp=(q/ηkT)2IS の関係にする。そうすれば、ドライバの出力インピーダンスが電圧に依存しないほぼ一定の抵抗値となり、ドライバの出力インピーダンスと伝送線の特性インピーダンスを一致させることが可能になる。

【0031】

なお、ここでkT/qは熱電圧であり、素電荷q=1.60218×10−19Cとボルツマン定数k=1.38066×10−23J/Kと温度T[K]によって決まる。常温のT=300Kにおける熱電圧は0.02582Vになる。また、ηは理想係数であり、理想的なダイオードでは1となるが、一般的には温度やダイオードの材質・製法に依存して1〜2の間の値をとる。

【0032】

以下に、その理由を説明する。

PMOSFET1のしきい値電圧をVthp(<0 )、PMOSFET1を通して伝送線に流れる電流をiDSp、第1のダイオード6の飽和電流をIS1、理想係数をη1、第1のダイオード6を通して伝送線に流れる電流をiD1とする。

【0033】

(1) レシーバで反射された信号波がドライバに戻ってくるまでのiDSpとiD1

PMOSFET1は線形領域で動作し、第1のダイオード6は非導通状態になる。したがって、iDSpとiD1は次のように表される。

iDSp=βp{(VDD+Vthp)(v-VDD)-(1/2)(v-VDD)2}

iD1=Is≒0

これらは図3の電圧が正の領域の電圧-電流特性に相当する。

【0034】

PMOSFET1と第1のダイオード6を通って伝送線に流れる電流の合計iは次のようになる。

i=iDSp+iD1≒βp{(VDD+Vthp)(v-VDD)-(1/2)(v-VDD)2}

これは図4の電圧が正の領域の電圧-電流特性に相当する。電圧-電流特性は非線形となり、∂v/∂iで表される抵抗値は電圧vに依存して変化する。

【0035】

(2) レシーバで反射された信号波がドライバに戻ってきた後のiDSpとiD1

PMOSFET1は線形領域で動作し、第1のダイオード6は導通状態になる。したがって、iDSpとiD1は次のように表される。

iDSp=βp{(-v-Vthp)(VDD-v) -(1/2)(VDD-v)2}

=βp{(v-VDD+VDD+Vthp)(v-VDD)-(1/2)(v-VDD)2}

=βp{(VDD+Vthp)(v-VDD)+(1/2)(v-VDD)2}

iD1=-Is1{exp((q/η1kT)(v-VDD))-1}

≒-Is1{(q/η1kT)(v-VDD)+(1/2)(q/η1kT)2(v-VDD)2 + …}

これらは図3の電圧が負の領域の電圧-電流特性に相当する。電流は伝送線から電圧源VDDに向かって流れる。なお、iD1の展開式において(v-VDD)の3次以上の項は十分に小さいと見なされることから省略されている。

【0036】

PMOSFET1と第1のダイオード6を通って伝送線に流れる電流の合計iは次のようになる。

i=iDSp+iD1

≒{βp(VDD+Vthp)- Is1(q/η1kT)}(v-VDD)+(1/2)(v-VDD)2{βp- Is1(q/η1kT)2}

上式において、βp= Is1(q/η1kT)2となるようにすれば、第2項が0となり

i={βp(VDD+Vthp)- Is1(q/η1kT)}(v-VDD)

になる。

これは図4の電圧が負の領域の電圧-電流特性に相当する。電圧-電流特性は線形であり、∂v/∂iで表される抵抗値は電圧vに依存しない一定値になる。

【0037】

「ドライバの入力信号電圧が"L"から"H"に変わって伝送線およびレシーバ入力部の電圧が"H"から"L"へ切り替わる場合」についても、PMOS FETとNMOS FET、および正電圧と負電圧が入れ替わるだけで同様の結果が得られる。すなわち、NMOS FET2のデバイストランスコンダクタンスβnを第2のダイオード7のIs2(q/η2kT)2と等しくすることにより、伝送線およびレシーバ入力部の電圧が "H"から"L"へ切り替わる場合もレシーバから反射されてきた信号波に対する出力抵抗は一定の値Rになる。

Rを伝送線の特性インピーダンスと一致させることでリンギングを防ぐことが可能になる。

【0038】

なお、一般的には信号の立ち上がり時間と立下り時間を等しくするために、βp=βnに設定される。この場合は、PMOS FETのβp= NMOS FETのβn= 第1のダイオード6のIs1(q/η1kT)2=ダイオード7の Is2(q/η2kT)2になる。

【0039】

また、βp=βnあるいはβp= Is(q/ηkT)2などの等号"="は、設計仕様あるいは製造仕様の上で等しいという意味であり物理的に全く同じ値になるという意味ではない。すなわち、本実施例の数式で示される等号は、物理量が設計上あるいは製造上の許容ばらつきの範囲内にあることを意味している。

【0040】

(第2の実施形態)

図5は、本発明の一態様を説明するための図である。ダイオードとしてMOSダイオードを用いるものである。すなわち本実施形態のCMOSドライバは「4つのMOS FET」すなわち「2個のNMOS FETと2個のPMOS FET」で構成される。第1のPMOS FET1と第1のNMOS FET2が通常のドライバを構成するトランジスタであり、第2のNMOS FET3と第2のPMOS FET4が本実施形態の特徴をなすトランジスタである。

【0041】

第2のNMOS FET3は、ソース端子が第1のPMOS FET1のソース端子すなわちドライバ出力端子に接続され、ドレイン端子が第1のPMOS FET1のドレイン端子すなわち電源線に接続され、ゲート端子がドライバ出力端子に接続されている。

第2のPMOS FET4は、ソース端子が第2のNMOS FET2のソース端子すなわち接地線に接続され、ドレイン端子が第1のNMOS FET2のドレイン端子すなわちドライバ出力端子に接続され、ゲート端子がドライバ出力端子に接続されている。

【0042】

第1のPMOS FET1と第2のNMOS FET3は対になって働き、ドライバ入力信号が高い電圧値(以降"H"と記す)から低い電圧値(以降"L"と記す)に変わると導通状態になり、伝送線およびレシーバ入力部を"H"状態にする。

一方、第1のNMOS FET2は第2のPMOS FET4と対になって働き、ドライバ入力信号が"L"から"H"に変わると導通状態になり、伝送線およびレシーバ入力部を"L"状態にする。

【0043】

以下、「ドライバの入力信号電圧が"H"から"L"に変わって伝送線およびレシーバ入力部の電圧が"L"から"H"へ切り替わる場合」を例として動作の詳細を述べる。

「ドライバの入力電圧vinが"H"から"L"に変わり、レシーバで反射された信号波が戻ってくるまで"L"の状態が続いている場合」には、ドライバ出力端子すなわち伝送線始端の電圧vは図6に示すように階段状の変化をする。もしドライバの出力インピーダンスが伝送線の特性インピーダンスと一致していない場合は、この反射波がドライバで再反射されてレシーバに戻って行く。このようにしてレシーバとドライバの間で反射が繰り返されると、リンギングが発生する。

【0044】

このようなリンギングを発生させないためには、ドライバの出力インピーダンスを伝送線の特性インピーダンスと等しくすることで、ドライバがレシーバから戻されてきた最初の反射波を吸収するようにしなければならない。そのためには、図5において第1のPMOSFET1のデバイストランスコンダクタンスβpと第2のNMOSFET3のデバイストランスコンダクタンスβnを同じ値にする。そうすれば、ドライバの出力インピーダンスが電圧に依存しない一定の抵抗値となり、ドライバの出力インピーダンスと伝送線の特性インピーダンスを一致させることが可能になる。

【0045】

以下に、その理由を説明する。

第1のPMOSFET1のしきい値電圧をVthp(<0 )、第1のPMOSFET1を通して伝送線に流れる電流をiDSp、第2のNMOSFET3のしきい値電圧をVthn(>0 )、第2のNMOSFET3を通して伝送線に流れる電流をiDSnとする。

【0046】

(1) レシーバで反射された信号波がドライバに戻ってくるまでのiDSpとiDSn

第1のPMOSFET1は線形領域で動作し、第2のNMOSFET3はオフ状態にある。したがって、iDSpとiDSnは次のように表される。

iDSp=βp{(VDD+Vthp)(v-VDD)-(1/2)(v-VDD)2}

iDSn=0

これらは図7の電圧が正の領域の電圧-電流特性に相当する。

【0047】

第1のPMOSFET1と第2のNMOSFET3を通って伝送線に流れる電流の合計iは次のようになる。

i=iDSp+iDSn=βp{(VDD+Vthp)(v-VDD)-(1/2)(v-VDD)2}

これは図8の電圧が正の領域の電圧-電流特性に相当する。電圧-電流特性は非線形となり、∂v/∂iで表される抵抗値は電圧vに依存して変化する。

【0048】

(2) レシーバで反射された信号波がドライバに戻ってきた後のiDSpとiDSn

第1のPMOSFET1、第2のNMOSFET3ともに線形領域で動作する。したがって、iDSpとiDSnは次のように表される。

iDSp=βp{(-v-Vthp)(VDD-v) -(1/2)(VDD-v)2}

=βp{(v-VDD+VDD+Vthp)(v-VDD)-(1/2)(v-VDD)2}

=βp{(VDD+Vthp)(v-VDD)+(1/2)(v-VDD)2}

iDSn=-βn{(v-VDD-Vthn)(v-VDD)-(1/2)(v-VDD)2}

=-βn{-Vthn(v-VDD)+(1/2)(v-VDD)2 }

これらは図7の電圧が負の領域の電圧-電流特性に相当する。電流は伝送線から電圧源VDDに向かって流れる。

【0049】

第1のPMOSFET1と第2のNMOSFET3を通って伝送線に流れる電流の合計iは次のようになる。

i=iDSp+iDSn

=(βpVDD+βpVthp+βnVthn)(v-VDD)+(1/2)(v-VDD)2(βp-βn)

上式において、βnとβpが等しい値を取りβn=βp=βとなるようにすれば、

i=β(VDD+Vthp+Vthn)(v-VDD)

になる。

これは図8の電圧が負の領域の電圧-電流特性に相当する。電圧-電流特性は線形であり、∂v/∂iで表される抵抗値は電圧vに依存しない一定値になる。

【0050】

上述したことを纏めると、レシーバで反射されドライバへ戻ってきた信号波に対するドライバの入力抵抗Rは、βn=βp=βとすることで

R=∂v/∂i=1/{β(VDD+Vthp+Vthn)}

の一定値になる。

【0051】

「ドライバの入力信号電圧が"L"から"H"に変わって伝送線およびレシーバ入力部の電圧が"H"から"L"へ切り替わる場合」についても、PMOS FETとNMOS FET、および正電圧と負電圧が入れ替わるだけで同様の結果が得られる。すなわち、2つのトランジスタすなわち第1のNMOS FET2と第2のPMOS FET4のデバイストランスコンダクタンスを同じ値のβとすることにより、伝送線およびレシーバ入力部の電圧が"H"から"L"へ切り替わる場合もレシーバから反射されてきた信号波に対する出力抵抗は一定の値Rになる。

Rを伝送線の特性インピーダンスと一致させることでリンギングを防ぐことが可能になる。

【0052】

なお、一般的には信号の立ち上がり時間と立下り時間を等しくするために、βp=βnに設定される。この場合は、4つのMOS FETのデバイストランスコンダクタンスは全て同じ値になる。

【0053】

4つのMOS FETのデバイストランスコンダクタンスを同じ値にする場合は、1つの半導体基板上に4つのMOS FETを形成するのが望ましい。4つのMOS FETを1つの半導体基板上に構成した場合のレイアウト例を図9に示す。MOS FETを図9に示すように配置することで、場所による材料特性のばらつきやパターン加工のばらつきなどを最小に抑えることができる。

【0054】

また、βp=βnなどの等号"="は、設計仕様あるいは製造仕様の上で等しいという意味であり物理的に全く同じ値になるという意味ではない。すなわち、本実施例の数式で示される等号は、物理量が設計上あるいは製造上の許容ばらつきの範囲内にあることを意味している。

【0055】

もしもRが伝送線の特性インピーダンスよりも小さな値をとらざるを得ない場合は、図10に示すように抵抗5を追加し、抵抗5の抵抗値が「R+(抵抗5の抵抗値)=(伝送線の特性インピーダンス)」となるように設定すればよい。

【0056】

なお、MOS FETのデバイストランスコンダクタンスを等しくすることは、PMOS FETとNMOS FETの(チャネル幅/チャネル長)比を或る一定の関係に保つことに相当する。たとえば、PMOSFET1のホール移動度をμp、チャネル長をLp、チャネル幅をWpとし、NMOSFET3の電子移動度をμn、チャネル長をLn、チャネル幅をWnとする。すると第1のPMOSFET1のデバイストランスコンダクンスβpおよび第2のNMOSFET3のデバイストランスコンダクンスβnは、それぞれ次のように表される。

βp=μp(εox/tox)(Wp/Lp)

βn=μn(εox/tox)(Wn/Ln)

したがって、βp=βn=βとなるようにするには

μn/μp=(Wp/Lp)/(Wn/Ln)

であればよい。たとえば、μp=500cm2/Vs、μn=1500cm2/Vsとすれば、(Wp/Lp)/(Wn/Ln)=3となる。

【符号の説明】

【0057】

1:CMOSドライバを構成する第1のPMOS FET

2:CMOSドライバを構成する第1のNMOS FET

3:本発明の特徴をなす第2のNMOS FET

4:本発明の特徴をなす第2のPMOS FET

5:インピーダンスを整合させるために挿入された抵抗値調整用の抵抗

6:CMOSドライバを構成するPMOSMETと並列に接続された第1のダイオード

7:CMOSドライバを構成するPMOSMETと並列に接続された第2のダイオード

【技術分野】

【0001】

本発明は、電気信号の伝送回路、IC、プリント配線板および電子・情報・通信の機器やシステムに関する。

【背景技術】

【0002】

電気信号の伝送回路は、図11および図12(a)に示すように、信号を送り出すドライバ、信号を伝える伝送線および信号を受け取るレシーバとで構成される。

このような伝送回路において信号がレシーバとドライバの間で反射を繰り返すと、図12(b)に示すようにリンギングを生じる。リンギングはレシーバの動作を不安定にしたり不要輻射を放出したりする。特に不要輻射は、他の電子部品・機器にノイズを誘導するため、大きな問題になっている。

【0003】

信号がレシーバやドライバで反射されないようにするためには、「インピーダンスを整合させること」すなわち「ドライバの出力インピーダンス、伝送線の特性インピーダンスそしてレシーバの入力インピーダンスを等しい値にすること」が求められる。インピーダンスを一致させることにより、信号がレシーバやドライバで反射されることがなくなり、図12(c)に示すようにリンギングを生じない。

【0004】

しかし、現実にはドライバの出力インピーダンスやレシーバの入力インピーダンスを伝送線の特性インピーダンスと一致させることが難しい。そこで「リンギング発生の第一要因」すなわち「レシーバでの反射」を無くすための工夫が施される。その基本的な方法が、図13〜図15に示すように、伝送線のレシーバ側に終端抵抗を挿入することである(例えば特許文献1参照)。

【0005】

一方、信号伝送の主流はCMOS伝送回路であり、ドライバやレシーバの入力段には図16に示すようなCMOS回路(ドライバに例を採るとPMOSFET1とNMOSFET2が対になって構成される回路)が用いられている。したがって、CMOSレシーバの入力インピーダンスは図17の等価回路に示すように、伝送線の特性インピーダンスZ0が純抵抗であるのに対して容量性になる。しかも、CMOSレシーバの入力容量は入力電圧に依存して変化する。すなわち、伝送線の特性インピーダンスZ0とCMOSレシーバの入力インピーダンスを一致させることは理論的に不可能である。そこで、CMOS伝送回路では、信号がレシーバで反射されることを前提として、レシーバからの反射波をドライバ側で吸収させるために図18に示すような方式が一般的に用いられている。

【0006】

しかし、CMOSドライバの出力抵抗も非線形であり、抵抗値がドライバの出力電圧に依存して変化する。このため、図18のように伝送線のドライバ側に終端抵抗を接続したとしても、CMOSドライバの出力インピーダンスを伝送線の特性インピーダンスと完全に一致させることはできない。

すなわち、従来の方法ではCMOS伝送回路のリンギングが全く生じないようにすることはできない。

【0007】

なお、終端抵抗は次のような方法で取り付けられたり、形成されたりする。

1)CMOS ICに終端抵抗を外付けする方法

個別抵抗素子をCMOSドライバと伝送線との間に接続する。ただし、リード線や抵抗素子が持っている寄生成分の影響が大きいために、完全な整合をとることは難しい。

2)CMOS IC内に終端抵抗を組み込む方法

i) ポリシリコン膜で抵抗を形成する。

ii) 拡散層あるいはウエルで抵抗を形成する。

iii) FETで抵抗を形成する。

【0008】

FET抵抗の基本的な形としては、図19に示すような2素子終端と図20に示すような相補型パスゲートがある。広い電圧範囲で線形性を確保できることから相補型パスゲートが広く用いられる。また、抵抗値の調整を可能とするため、図21に例を示すように、複数のFET抵抗を並列に接続したり、それらを構成する個別のFET抵抗ごとにデジタル信号で制御したりする方法がある。

なお、i)とii)は抵抗値を十分な精度で制御することが難しい。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開平8−195775号公報(段落[0018]、図1)

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明の一態様は、CMOS伝送回路において、レシーバの動作を不安定にしたり不要輻射を放出したりするリンギングの発生を抑制することを課題とする。

【課題を解決するための手段】

【0011】

課題を解決する上で最大の障害は、CMOSドライバの出力インピーダンスが出力電圧に依存して変化することである。本発明の一態様では、この障害を乗り越えるためにCMOSドライバのPMOS FET1と並列にゲート端子がドライバ出力端子につながれているNMOS FETを接続し、CMOSドライバのNMOS FET2と並列にゲート端子がドライバ出力端子につながれているPMOS FETを接続し、これら4つのMOS FETをデバイストランスコンダクタンスが等しい値となるようにする。こうすることによって、CMOSドライバの出力インピーダンスが電圧に依存しない一定値となる。その結果、CMOSドライバの出力インピーダンスを伝送線の特性インピーダンスに一致させることが可能になる。

【0012】

また、本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、

前記CMOSドライバのPMOS FETと並列にアノード電極がドライバ出力端子につながれるように第1のダイオードを接続し、

前記CMOSドライバのNMOS FETと並列にカソード電極がドライバ出力端子につながれるように第2のダイオードを接続し、

前記PMOS FETのデバイストランスコンダクタンスと前記第1のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにし、

前記NMOS FETのデバイストランスコンダクタンスと前記第2のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路である。

【0013】

本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、

前記CMOSドライバは、PMOS FETと、NMOS FETと、第1および第2のダイオードとを有し、

前記PMOS FETおよび前記NMOS FETそれぞれのゲート端子はドライバ入力端子に電気的に接続され、

前記PMOS FETのドレイン端子および前記第1のダイオードのカソード電極それぞれは、電源線に電気的に接続され、

前記PMOS FETのソース端子、前記第1のダイオードのアノード電極、前記NMOS FETのドレイン端子および前記第2のダイオードのカソード電極それぞれは、ドライバ出力端子に電気的に接続され、

前記NMOS FETのソース端子および前記第2のダイオードのアノード電極それぞれは、接地線に電気的に接続され、

前記ドライバ出力端子は、前記伝送線の始端に電気的に接続され、

前記伝送線の終端は、前記CMOSレシーバの入力端子に電気的に接続され、

前記PMOS FETのデバイストランスコンダクタンスは、前記第1のダイオードの(飽和電流)/(理想係数×熱電圧)2と等しく、

前記NMOS FETのデバイストランスコンダクタンスは、前記第2のダイオードの(飽和電流)/(理想係数×熱電圧)2と等しいことを特徴とする電気信号の伝送回路である。

【0014】

ただし、前記PMOS FETのデバイストランスコンダクタンスと前記第1のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しい、および前記NMOS FETのデバイストランスコンダクタンスと前記第2のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しいそれぞれの「等しい」の意味は、設計仕様あるいは製造仕様の上で等しいという意味であり物理的に全く同じ値になるという意味ではない。設計仕様あるいは製造仕様の上で等しいとは、物理量が設計上あるいは製造上の許容ばらつきの範囲内にあることを意味している。なお、このように「等しい」の意味を解釈するのは、本明細書中においてすべて同様である。

【0015】

また、上記の本発明の一態様において、前記PMOS FETのデバイストランスコンダクタンスと前記第1のダイオードの(飽和電流)/(理想係数×熱電圧)2と前記NMOS FETのデバイストランスコンダクタンスと前記第2のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにすることが好ましい。

【0016】

本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、

前記CMOSドライバの第1のPMOS FETと並列にゲート端子がドライバ出力端子につながれている第2のNMOS FETを接続し、

前記CMOSドライバの第1のNMOS FETと並列にゲート端子がドライバ出力端子につながれている第2のPMOS FETを接続し、

前記第1のPMOS FETのデバイストランスコンダクタンスと前記第2のNMOS FETのデバイストランスコンダクタンスが等しくなるようにし、

前記第1のNMOS FETのデバイストランスコンダクタンスと前記第2のPMOS FETのデバイストランスコンダクタンスが等しくなるようにしたことを特徴とする電気信号の伝送回路である。

【0017】

本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、

前記CMOSドライバは、第1および第2のPMOS FETと、第1および第2のNMOS FETとを有し、

前記第1のPMOS FETおよび前記第1のNMOS FETそれぞれのゲート端子はドライバ入力端子に電気的に接続され、

前記第1のPMOS FETのドレイン端子および前記第2のNMOS FETのドレイン端子それぞれは、電源線に電気的に接続され、

前記第1のPMOS FETのソース端子、前記第2のNMOS FETのソース端子、前記第2のNMOS FETのゲート端子、前記第1のNMOS FETのドレイン端子、前記第2のPMOS FETのドレイン端子および前記第2のPMOS FETのゲート端子それぞれは、ドライバ出力端子に電気的に接続され、

前記第1のNMOS FETのソース端子および前記第2のPMOS FETのソース端子それぞれは、接地線に電気的に接続され、

前記ドライバ出力端子は、前記伝送線の始端に電気的に接続され、

前記伝送線の終端は、前記CMOSレシーバの入力端子に電気的に接続され、

前記第1のPMOS FETのデバイストランスコンダクタンスは、前記第2のNMOS FETのデバイストランスコンダクタンスと等しく、

前記第1のNMOS FETのデバイストランスコンダクタンスは、前記第2のPMOS FETのデバイストランスコンダクタンスと等しいことを特徴とする電気信号の伝送回路である。

【0018】

ただし、前記第1のPMOS FETのデバイストランスコンダクタンスと前記第2のNMOS FETのデバイストランスコンダクタンスとが等しい、および前記第1のNMOS FETのデバイストランスコンダクタンスと前記第2のPMOS FETのデバイストランスコンダクタンスとが等しいそれぞれの「等しい」の意味は、設計仕様あるいは製造仕様の上で等しいという意味であり物理的に全く同じ値になるという意味ではない。設計仕様あるいは製造仕様の上で等しいとは、物理量が設計上あるいは製造上の許容ばらつきの範囲内にあることを意味している。なお、このように「等しい」の意味を解釈するのは、本明細書中においてすべて同様である。

【0019】

また、上記の本発明の一態様において、前記第1のPMOS FET、前記第2のPMOS FET、前記第1のNMOS FETおよび前記第2のNMOS FETそれぞれのデバイストランスコンダクタンスが等しい値となるようにすることが好ましい。

【0020】

また、上記の本発明の一態様において、前記第1のPMOS FET、前記第2のPMOS FET、前記第1のNMOS FETおよび前記第2のNMOS FETそれぞれを同一半導体基板上に集積回路として構成することも可能である。

【0021】

本発明の一態様は、上記の本発明の一態様の電気信号の伝送回路を備えたIC、プリント配線板、機器またはシステムである。

【発明の効果】

【0022】

本発明の一態様を適用することにより、CMOSドライバの出力インピーダンスと伝送線の特性インピーダンスとを等しくすることが可能となり、CMOSレシーバからの反射波を吸収できるので、リンギングの発生を抑制することができる。したがって、本発明の一態様を用いて構成された伝送回路を搭載したIC、プリント配線板および電子・情報・通信の機器やシステムは全て大きな性能向上が図られる。

【図面の簡単な説明】

【0023】

【図1】本発明の一態様を示すための図。

【図2】本発明の一態様の動作を説明するための図。

【図3】本発明の一態様におけるPMOSFETおよびダイオードの電圧-電流特性を示すための図。

【図4】本発明の一態様における電圧-電流特性を示すための図。

【図5】本発明の一態様であるMOSダイオードを用いた場合の例を示すための図。

【図6】MOSダイオードを用いた場合の本発明の一態様の動作を説明するための図。

【図7】MOSダイオードを用いた場合の本発明の一態様における各MOSFETの電圧-電流特性を示すための図。

【図8】本発明の一態様における電圧-電流特性を示すための図。

【図9】CMOSドライバのレイアウト例を示すための図であり、(a)は平面図、(b)は(a)に示すA−A'部(PMOS FET)の断面図。

【図10】本発明の一態様を示すための図。

【図11】本発明の対象となる信号伝送回路がドライバ、伝送線およびレシーバで構成されることを示すための図。

【図12】信号を伝送する際にリンギングが生じることを示すための図であり、(a)は信号伝送回路の構成図、(b)はレシーバおよびドライバで反射がある場合(インピーダンスが整合していない場合)の波形、(c)はレシーバおよびドライバでの反射がない場合(インピーダンスが整合している場合)の波形。

【図13】レシーバ側に付けられた終端抵抗の例を示すための図。

【図14】レシーバ側に付けられた終端抵抗の例を示すための図。

【図15】レシーバ側に付けられた終端抵抗の例を示すための図。

【図16】CMOS回路を用いた伝送回路の代表的な構成を示すための図。

【図17】CMOS伝送回路の等価回路図であり、伝送線の特性インピーダンスが抵抗であるのに対しCMOS回路の入力インピーダンスが容量性であることを示すための図。

【図18】「CMOS伝送回路で広く用いられている抵抗終端法」すなわち「伝送線のレシーバ側に終端抵抗を挿入する方法」を示すための図。

【図19】CMOSIC内で終端抵抗を作りこむ際に広く用いられるのがFET抵抗であり、その一つの例としての2素子終端回路を示すための図であり、(a)はPMOS FETで構成した2素子終端回路、(b)はNMOS FETで構成した2素子終端回路。

【図20】CMOSIC内で終端抵抗を作りこむ際に広く用いられるのがFET抵抗であり、その一つの例としての相補型パスゲートを示すための図であり、(a)は相補型パスゲート回路、(b)は相補型パスゲート回路の電圧‐電流特性を示す図。

【図21】複数の相補型パスゲートを並列に接続して抵抗値を調整できるように構成された終端抵抗の回路の例を示すための図。

【発明を実施するための形態】

【0024】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0025】

(第1の実施形態)

図1は、本発明の一態様を説明するための図である。

本発明の一態様のCMOSドライバは、PMOS FETとNMOS FETに第1および第2のダイオード6,7を加えて構成される。PMOS FET1とNMOS FET2が通常のドライバを構成するトランジスタであり、第1のダイオード6と第2のダイオード7が本発明の一態様の特徴をなすものである。

【0026】

第1のダイオード6は、カソード電極がPMOS FET1のドレイン端子すなわち電源線に接続され、アノード電極がPMOS FET1のソース端子すなわちドライバ出力端子に接続されている。第2のダイオード7は、カソード電極がNMOS FET2のドレイン端子すなわちドライバ出力端子に接続され、アノード電極がNMOS FET2のソース端子すなわち接地線に接続されている。

【0027】

PMOS FET1と第1のダイオード6は対になって働き、ドライバ入力信号が高い電圧値(以降"H"と記す)から低い電圧値(以降"L"と記す)に変わると導通状態になり、伝送線およびレシーバ入力部を"H"状態にする。

一方、NMOS FET2は第2のダイオード7と対になって働き、ドライバ入力信号が"L"から"H"に変わると導通状態になり、伝送線およびレシーバ入力部を"L"状態にする。

【0028】

以下、「ドライバの入力信号電圧が"H"から"L"に変わって伝送線およびレシーバ入力部の電圧が"L"から"H"へ切り替わる場合」を例として動作の詳細を述べる。

「ドライバの入力電圧vinが"H"から"L"に変わり、レシーバで反射された信号波が戻ってくるまで"L"の状態が続いている場合」には、ドライバ出力端子すなわち伝送線始端の電圧vは図2に示すように階段状の変化をする。もしドライバの出力インピーダンスが伝送線の特性インピーダンスと一致していない場合は、この反射波がドライバで再反射されてレシーバに戻って行く。このようにしてレシーバとドライバの間で反射が繰り返されると、リンギングが発生する。

【0029】

このようなリンギングを発生させないためには、ドライバの出力インピーダンスを伝送線の特性インピーダンスと等しくすることで、ドライバがレシーバから戻されてきた最初の反射波を吸収するようにしなければならない。そのためには、図3に示すPMOSFET1と第1のダイオード6の電圧-電流特性において負電圧領域におけるPMOSFET1の電流値と第1のダイオード6の電流値の和が図4に示すように直線的に変化するようにすればよい。そうすることにより、ドライバの出力インピーダンスが電圧に依存しない一定の抵抗値となり、ドライバの出力インピーダンスと伝送線の特性インピーダンスを一致させることが可能になる。

【0030】

具体的には、図2においてPMOSFET1のデバイストランスコンダクタンスβpと第1のダイオード6の飽和電流ISをβp=(q/ηkT)2IS の関係にする。そうすれば、ドライバの出力インピーダンスが電圧に依存しないほぼ一定の抵抗値となり、ドライバの出力インピーダンスと伝送線の特性インピーダンスを一致させることが可能になる。

【0031】

なお、ここでkT/qは熱電圧であり、素電荷q=1.60218×10−19Cとボルツマン定数k=1.38066×10−23J/Kと温度T[K]によって決まる。常温のT=300Kにおける熱電圧は0.02582Vになる。また、ηは理想係数であり、理想的なダイオードでは1となるが、一般的には温度やダイオードの材質・製法に依存して1〜2の間の値をとる。

【0032】

以下に、その理由を説明する。

PMOSFET1のしきい値電圧をVthp(<0 )、PMOSFET1を通して伝送線に流れる電流をiDSp、第1のダイオード6の飽和電流をIS1、理想係数をη1、第1のダイオード6を通して伝送線に流れる電流をiD1とする。

【0033】

(1) レシーバで反射された信号波がドライバに戻ってくるまでのiDSpとiD1

PMOSFET1は線形領域で動作し、第1のダイオード6は非導通状態になる。したがって、iDSpとiD1は次のように表される。

iDSp=βp{(VDD+Vthp)(v-VDD)-(1/2)(v-VDD)2}

iD1=Is≒0

これらは図3の電圧が正の領域の電圧-電流特性に相当する。

【0034】

PMOSFET1と第1のダイオード6を通って伝送線に流れる電流の合計iは次のようになる。

i=iDSp+iD1≒βp{(VDD+Vthp)(v-VDD)-(1/2)(v-VDD)2}

これは図4の電圧が正の領域の電圧-電流特性に相当する。電圧-電流特性は非線形となり、∂v/∂iで表される抵抗値は電圧vに依存して変化する。

【0035】

(2) レシーバで反射された信号波がドライバに戻ってきた後のiDSpとiD1

PMOSFET1は線形領域で動作し、第1のダイオード6は導通状態になる。したがって、iDSpとiD1は次のように表される。

iDSp=βp{(-v-Vthp)(VDD-v) -(1/2)(VDD-v)2}

=βp{(v-VDD+VDD+Vthp)(v-VDD)-(1/2)(v-VDD)2}

=βp{(VDD+Vthp)(v-VDD)+(1/2)(v-VDD)2}

iD1=-Is1{exp((q/η1kT)(v-VDD))-1}

≒-Is1{(q/η1kT)(v-VDD)+(1/2)(q/η1kT)2(v-VDD)2 + …}

これらは図3の電圧が負の領域の電圧-電流特性に相当する。電流は伝送線から電圧源VDDに向かって流れる。なお、iD1の展開式において(v-VDD)の3次以上の項は十分に小さいと見なされることから省略されている。

【0036】

PMOSFET1と第1のダイオード6を通って伝送線に流れる電流の合計iは次のようになる。

i=iDSp+iD1

≒{βp(VDD+Vthp)- Is1(q/η1kT)}(v-VDD)+(1/2)(v-VDD)2{βp- Is1(q/η1kT)2}

上式において、βp= Is1(q/η1kT)2となるようにすれば、第2項が0となり

i={βp(VDD+Vthp)- Is1(q/η1kT)}(v-VDD)

になる。

これは図4の電圧が負の領域の電圧-電流特性に相当する。電圧-電流特性は線形であり、∂v/∂iで表される抵抗値は電圧vに依存しない一定値になる。

【0037】

「ドライバの入力信号電圧が"L"から"H"に変わって伝送線およびレシーバ入力部の電圧が"H"から"L"へ切り替わる場合」についても、PMOS FETとNMOS FET、および正電圧と負電圧が入れ替わるだけで同様の結果が得られる。すなわち、NMOS FET2のデバイストランスコンダクタンスβnを第2のダイオード7のIs2(q/η2kT)2と等しくすることにより、伝送線およびレシーバ入力部の電圧が "H"から"L"へ切り替わる場合もレシーバから反射されてきた信号波に対する出力抵抗は一定の値Rになる。

Rを伝送線の特性インピーダンスと一致させることでリンギングを防ぐことが可能になる。

【0038】

なお、一般的には信号の立ち上がり時間と立下り時間を等しくするために、βp=βnに設定される。この場合は、PMOS FETのβp= NMOS FETのβn= 第1のダイオード6のIs1(q/η1kT)2=ダイオード7の Is2(q/η2kT)2になる。

【0039】

また、βp=βnあるいはβp= Is(q/ηkT)2などの等号"="は、設計仕様あるいは製造仕様の上で等しいという意味であり物理的に全く同じ値になるという意味ではない。すなわち、本実施例の数式で示される等号は、物理量が設計上あるいは製造上の許容ばらつきの範囲内にあることを意味している。

【0040】

(第2の実施形態)

図5は、本発明の一態様を説明するための図である。ダイオードとしてMOSダイオードを用いるものである。すなわち本実施形態のCMOSドライバは「4つのMOS FET」すなわち「2個のNMOS FETと2個のPMOS FET」で構成される。第1のPMOS FET1と第1のNMOS FET2が通常のドライバを構成するトランジスタであり、第2のNMOS FET3と第2のPMOS FET4が本実施形態の特徴をなすトランジスタである。

【0041】

第2のNMOS FET3は、ソース端子が第1のPMOS FET1のソース端子すなわちドライバ出力端子に接続され、ドレイン端子が第1のPMOS FET1のドレイン端子すなわち電源線に接続され、ゲート端子がドライバ出力端子に接続されている。

第2のPMOS FET4は、ソース端子が第2のNMOS FET2のソース端子すなわち接地線に接続され、ドレイン端子が第1のNMOS FET2のドレイン端子すなわちドライバ出力端子に接続され、ゲート端子がドライバ出力端子に接続されている。

【0042】

第1のPMOS FET1と第2のNMOS FET3は対になって働き、ドライバ入力信号が高い電圧値(以降"H"と記す)から低い電圧値(以降"L"と記す)に変わると導通状態になり、伝送線およびレシーバ入力部を"H"状態にする。

一方、第1のNMOS FET2は第2のPMOS FET4と対になって働き、ドライバ入力信号が"L"から"H"に変わると導通状態になり、伝送線およびレシーバ入力部を"L"状態にする。

【0043】

以下、「ドライバの入力信号電圧が"H"から"L"に変わって伝送線およびレシーバ入力部の電圧が"L"から"H"へ切り替わる場合」を例として動作の詳細を述べる。

「ドライバの入力電圧vinが"H"から"L"に変わり、レシーバで反射された信号波が戻ってくるまで"L"の状態が続いている場合」には、ドライバ出力端子すなわち伝送線始端の電圧vは図6に示すように階段状の変化をする。もしドライバの出力インピーダンスが伝送線の特性インピーダンスと一致していない場合は、この反射波がドライバで再反射されてレシーバに戻って行く。このようにしてレシーバとドライバの間で反射が繰り返されると、リンギングが発生する。

【0044】

このようなリンギングを発生させないためには、ドライバの出力インピーダンスを伝送線の特性インピーダンスと等しくすることで、ドライバがレシーバから戻されてきた最初の反射波を吸収するようにしなければならない。そのためには、図5において第1のPMOSFET1のデバイストランスコンダクタンスβpと第2のNMOSFET3のデバイストランスコンダクタンスβnを同じ値にする。そうすれば、ドライバの出力インピーダンスが電圧に依存しない一定の抵抗値となり、ドライバの出力インピーダンスと伝送線の特性インピーダンスを一致させることが可能になる。

【0045】

以下に、その理由を説明する。

第1のPMOSFET1のしきい値電圧をVthp(<0 )、第1のPMOSFET1を通して伝送線に流れる電流をiDSp、第2のNMOSFET3のしきい値電圧をVthn(>0 )、第2のNMOSFET3を通して伝送線に流れる電流をiDSnとする。

【0046】

(1) レシーバで反射された信号波がドライバに戻ってくるまでのiDSpとiDSn

第1のPMOSFET1は線形領域で動作し、第2のNMOSFET3はオフ状態にある。したがって、iDSpとiDSnは次のように表される。

iDSp=βp{(VDD+Vthp)(v-VDD)-(1/2)(v-VDD)2}

iDSn=0

これらは図7の電圧が正の領域の電圧-電流特性に相当する。

【0047】

第1のPMOSFET1と第2のNMOSFET3を通って伝送線に流れる電流の合計iは次のようになる。

i=iDSp+iDSn=βp{(VDD+Vthp)(v-VDD)-(1/2)(v-VDD)2}

これは図8の電圧が正の領域の電圧-電流特性に相当する。電圧-電流特性は非線形となり、∂v/∂iで表される抵抗値は電圧vに依存して変化する。

【0048】

(2) レシーバで反射された信号波がドライバに戻ってきた後のiDSpとiDSn

第1のPMOSFET1、第2のNMOSFET3ともに線形領域で動作する。したがって、iDSpとiDSnは次のように表される。

iDSp=βp{(-v-Vthp)(VDD-v) -(1/2)(VDD-v)2}

=βp{(v-VDD+VDD+Vthp)(v-VDD)-(1/2)(v-VDD)2}

=βp{(VDD+Vthp)(v-VDD)+(1/2)(v-VDD)2}

iDSn=-βn{(v-VDD-Vthn)(v-VDD)-(1/2)(v-VDD)2}

=-βn{-Vthn(v-VDD)+(1/2)(v-VDD)2 }

これらは図7の電圧が負の領域の電圧-電流特性に相当する。電流は伝送線から電圧源VDDに向かって流れる。

【0049】

第1のPMOSFET1と第2のNMOSFET3を通って伝送線に流れる電流の合計iは次のようになる。

i=iDSp+iDSn

=(βpVDD+βpVthp+βnVthn)(v-VDD)+(1/2)(v-VDD)2(βp-βn)

上式において、βnとβpが等しい値を取りβn=βp=βとなるようにすれば、

i=β(VDD+Vthp+Vthn)(v-VDD)

になる。

これは図8の電圧が負の領域の電圧-電流特性に相当する。電圧-電流特性は線形であり、∂v/∂iで表される抵抗値は電圧vに依存しない一定値になる。

【0050】

上述したことを纏めると、レシーバで反射されドライバへ戻ってきた信号波に対するドライバの入力抵抗Rは、βn=βp=βとすることで

R=∂v/∂i=1/{β(VDD+Vthp+Vthn)}

の一定値になる。

【0051】

「ドライバの入力信号電圧が"L"から"H"に変わって伝送線およびレシーバ入力部の電圧が"H"から"L"へ切り替わる場合」についても、PMOS FETとNMOS FET、および正電圧と負電圧が入れ替わるだけで同様の結果が得られる。すなわち、2つのトランジスタすなわち第1のNMOS FET2と第2のPMOS FET4のデバイストランスコンダクタンスを同じ値のβとすることにより、伝送線およびレシーバ入力部の電圧が"H"から"L"へ切り替わる場合もレシーバから反射されてきた信号波に対する出力抵抗は一定の値Rになる。

Rを伝送線の特性インピーダンスと一致させることでリンギングを防ぐことが可能になる。

【0052】

なお、一般的には信号の立ち上がり時間と立下り時間を等しくするために、βp=βnに設定される。この場合は、4つのMOS FETのデバイストランスコンダクタンスは全て同じ値になる。

【0053】

4つのMOS FETのデバイストランスコンダクタンスを同じ値にする場合は、1つの半導体基板上に4つのMOS FETを形成するのが望ましい。4つのMOS FETを1つの半導体基板上に構成した場合のレイアウト例を図9に示す。MOS FETを図9に示すように配置することで、場所による材料特性のばらつきやパターン加工のばらつきなどを最小に抑えることができる。

【0054】

また、βp=βnなどの等号"="は、設計仕様あるいは製造仕様の上で等しいという意味であり物理的に全く同じ値になるという意味ではない。すなわち、本実施例の数式で示される等号は、物理量が設計上あるいは製造上の許容ばらつきの範囲内にあることを意味している。

【0055】

もしもRが伝送線の特性インピーダンスよりも小さな値をとらざるを得ない場合は、図10に示すように抵抗5を追加し、抵抗5の抵抗値が「R+(抵抗5の抵抗値)=(伝送線の特性インピーダンス)」となるように設定すればよい。

【0056】

なお、MOS FETのデバイストランスコンダクタンスを等しくすることは、PMOS FETとNMOS FETの(チャネル幅/チャネル長)比を或る一定の関係に保つことに相当する。たとえば、PMOSFET1のホール移動度をμp、チャネル長をLp、チャネル幅をWpとし、NMOSFET3の電子移動度をμn、チャネル長をLn、チャネル幅をWnとする。すると第1のPMOSFET1のデバイストランスコンダクンスβpおよび第2のNMOSFET3のデバイストランスコンダクンスβnは、それぞれ次のように表される。

βp=μp(εox/tox)(Wp/Lp)

βn=μn(εox/tox)(Wn/Ln)

したがって、βp=βn=βとなるようにするには

μn/μp=(Wp/Lp)/(Wn/Ln)

であればよい。たとえば、μp=500cm2/Vs、μn=1500cm2/Vsとすれば、(Wp/Lp)/(Wn/Ln)=3となる。

【符号の説明】

【0057】

1:CMOSドライバを構成する第1のPMOS FET

2:CMOSドライバを構成する第1のNMOS FET

3:本発明の特徴をなす第2のNMOS FET

4:本発明の特徴をなす第2のPMOS FET

5:インピーダンスを整合させるために挿入された抵抗値調整用の抵抗

6:CMOSドライバを構成するPMOSMETと並列に接続された第1のダイオード

7:CMOSドライバを構成するPMOSMETと並列に接続された第2のダイオード

【特許請求の範囲】

【請求項1】

CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、

前記CMOSドライバの第1のPMOS FETと並列にゲート端子がドライバ出力端子につながれている第2のNMOS FETを接続し、

前記CMOSドライバの第1のNMOS FETと並列にゲート端子がドライバ出力端子につながれている第2のPMOS FETを接続し、

前記第1のPMOS FETのデバイストランスコンダクタンスと前記第2のNMOS FETのデバイストランスコンダクタンスが等しくなるようにし、

前記第1のNMOS FETのデバイストランスコンダクタンスと前記第2のPMOS FETのデバイストランスコンダクタンスが等しくなるようにしたことを特徴とする電気信号の伝送回路。

【請求項2】

請求項1において、

前記第1のPMOS FET、前記第2のPMOS FET、前記第1のNMOS FETおよび前記第2のNMOS FETそれぞれのデバイストランスコンダクタンスが等しい値となるようにしたことを特徴とする電気信号の伝送回路。

【請求項3】

請求項1あるいは請求項2において、

前記第1のPMOS FET、前記第2のPMOS FET、前記第1のNMOS FETおよび前記第2のNMOS FETそれぞれを同一半導体基板上に集積回路として構成したことを特徴とする電気信号の伝送回路。

【請求項4】

CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、

前記CMOSドライバのPMOS FETと並列にアノード電極がドライバ出力端子につながれるように第1のダイオードを接続し、

前記CMOSドライバのNMOS FETと並列にカソード電極がドライバ出力端子につながれるように第2のダイオードを接続し、

前記PMOS FETのデバイストランスコンダクタンスと前記第1のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにし、

前記NMOS FETのデバイストランスコンダクタンスと前記第2のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路。

【請求項5】

請求項4において、

前記PMOS FETのデバイストランスコンダクタンスと前記第1のダイオードの(飽和電流)/(理想係数×熱電圧)2と前記NMOS FETのデバイストランスコンダクタンスと前記第2のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路。

【請求項6】

請求項1〜請求項5のいずれか一項に記載の電気信号の伝送回路を備えたIC、プリント配線板、機器またはシステム。

【請求項1】

CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、

前記CMOSドライバの第1のPMOS FETと並列にゲート端子がドライバ出力端子につながれている第2のNMOS FETを接続し、

前記CMOSドライバの第1のNMOS FETと並列にゲート端子がドライバ出力端子につながれている第2のPMOS FETを接続し、

前記第1のPMOS FETのデバイストランスコンダクタンスと前記第2のNMOS FETのデバイストランスコンダクタンスが等しくなるようにし、

前記第1のNMOS FETのデバイストランスコンダクタンスと前記第2のPMOS FETのデバイストランスコンダクタンスが等しくなるようにしたことを特徴とする電気信号の伝送回路。

【請求項2】

請求項1において、

前記第1のPMOS FET、前記第2のPMOS FET、前記第1のNMOS FETおよび前記第2のNMOS FETそれぞれのデバイストランスコンダクタンスが等しい値となるようにしたことを特徴とする電気信号の伝送回路。

【請求項3】

請求項1あるいは請求項2において、

前記第1のPMOS FET、前記第2のPMOS FET、前記第1のNMOS FETおよび前記第2のNMOS FETそれぞれを同一半導体基板上に集積回路として構成したことを特徴とする電気信号の伝送回路。

【請求項4】

CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、

前記CMOSドライバのPMOS FETと並列にアノード電極がドライバ出力端子につながれるように第1のダイオードを接続し、

前記CMOSドライバのNMOS FETと並列にカソード電極がドライバ出力端子につながれるように第2のダイオードを接続し、

前記PMOS FETのデバイストランスコンダクタンスと前記第1のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにし、

前記NMOS FETのデバイストランスコンダクタンスと前記第2のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路。

【請求項5】

請求項4において、

前記PMOS FETのデバイストランスコンダクタンスと前記第1のダイオードの(飽和電流)/(理想係数×熱電圧)2と前記NMOS FETのデバイストランスコンダクタンスと前記第2のダイオードの(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路。

【請求項6】

請求項1〜請求項5のいずれか一項に記載の電気信号の伝送回路を備えたIC、プリント配線板、機器またはシステム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2012−120020(P2012−120020A)

【公開日】平成24年6月21日(2012.6.21)

【国際特許分類】

【出願番号】特願2010−269219(P2010−269219)

【出願日】平成22年12月2日(2010.12.2)

【出願人】(500132214)学校法人明星学苑 (23)

【Fターム(参考)】

【公開日】平成24年6月21日(2012.6.21)

【国際特許分類】

【出願日】平成22年12月2日(2010.12.2)

【出願人】(500132214)学校法人明星学苑 (23)

【Fターム(参考)】

[ Back to top ]