電気光学装置、その製造方法、および電子機器

【課題】表示ムラ、コントラスト等の画像表示品質の面で優れ、さらに高速駆動が可能な電気光学装置を提供する。

【解決手段】第2導電膜400上に積層され、開口領域に第2のコンタクトホール86が形成された第2絶縁層44と、第2のコンタクトホール86を介して延在部に電気的に接続され、少なくとも前記一方の画素の開口領域に形成された画素電極9aと、を少なくとも備え、第2のコンタクトホール86の内部は、画素電極9aよりも比抵抗が低い透明導電性材料によって充填されていることを特徴としている。

【解決手段】第2導電膜400上に積層され、開口領域に第2のコンタクトホール86が形成された第2絶縁層44と、第2のコンタクトホール86を介して延在部に電気的に接続され、少なくとも前記一方の画素の開口領域に形成された画素電極9aと、を少なくとも備え、第2のコンタクトホール86の内部は、画素電極9aよりも比抵抗が低い透明導電性材料によって充填されていることを特徴としている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電気光学装置、およびその製造方法、ならびに当該電気光学装置を備えた電子機器に関するものである。

【背景技術】

【0002】

従来より、電気光学装置の一例である透過型の液晶表示装置は、例えばプロジェクターのような投射型表示装置の光変調手段(ライトバルブ)として多用されている。そして、ライトバルブ用途に用いられる液晶表示装置には、小型、高密度、高精細であることに加えて、画素の開口率の高さが求められていた。

このような高密度化、高精細化に伴う画素の狭ピッチ化と、開口率の向上に伴い、各画素を区画するBM(Black Matrix)の幅が狭くなり、十分な配線スペースを確保することが困難になってきている。

そこで、出願人等はコンタクトホールをBM領域(非開口領域)のみならず、開口領域にも配置した構造を提案している(特許文献1)。

【0003】

この構成により、狭ピッチ化が進んでも、必要な配線スペース(ギャップも含む)を確保することができるため、隣の画素に誤った画像が表示されてしまうといった混線を防止することを可能にしている。さらに特許文献1では、開口領域にコンタクトホールを配置するため、表示画像の品質に影響を与えないように、コンタクトホールを画素電極と同じ透明導電性材料で形成することも提案している。

図16は、従来の画素電極近傍における側断面図であり、画素電極9aを延在して形成したコンタクトホール86が示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−192975号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1の技術では、開口領域に設けたコンタクトホールの上部における平坦性が確保できないため、所期の画像品質を得ることが困難であるという課題があった。詳しくは、図16に示すように、開口領域に形成されたコンタクトホールは、すり鉢状の凹部となっており、画素電極の平坦性を損なっていた。

このため、平坦性が損なわれた部分で生じる透過光の散乱や反射に起因して、画像表示にムラが生じたり、コントラストが低下するなど、画像品質に影響を及ぼしていた。

【0006】

また、上記課題を解決するために、画素電極の形成時において、コンタクトホールの内部を透明導電性材料で埋め込み、平坦性を確保することも考えられるが、実現性が乏しかった。

これは、画素電極部分と、コンタクトホール部分とに要求される膜質が異なるにも拘らず、同一工程で両者を形成することに無理があるからである。

詳しくは、画素電極部分には、透明性と表面の平坦度とが要求されるため、これらを満たす膜質(グレインサイズなど)が得られる条件設定のスパッタリング法で形成される。他方、コンタクトホール部分には、透明性と、電気配線としての導電性とが要求されるが、画素電極部分と同じ条件設定で形成した場合には、必要な導電性を確保することが困難であった。さらに、スパッタリング法の原理からして、コンタクトホールの凹部の膜厚を選択的に厚く形成することも困難であった。

つまり、コンタクトホールにおける透明性と、平坦性とを確保(両立)することは困難であるという課題があった。

【0007】

また、このように、画素電極部分と同じ膜質で形成されたコンタクトホールでは、十分な導電性が得られないため、高速駆動への対応が困難であるという課題があった。詳しくは、ITO(Indium Tin Oxide)で形成されたコンタクトホールは、BM内部に形成された金属配線に比べて高抵抗であるため、残像を誘発してしまう恐れがあった。

【0008】

また、前述の高抵抗対策として、コンタクトホールの大きさ(直径)を大きくすることで、内壁の面積を大きくし、画素電極との接触面積を広く取ることも考えられるが、この場合、平坦性がより悪くなってしまうという課題があった。

つまり、コンタクトホールの平坦性と導電性とは、トレードオフの関係にあり、これらを両立することは、困難であるという課題があった。

【課題を解決するための手段】

【0009】

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態または適用例として実現することが可能である。

【0010】

(適用例1)

本適用例に係る電気光学装置は、基板と、前記基板上で互いに交差する複数の走査線及び複数のデータ線と、前記走査線及び前記データ線の交差に対応して設けられた複数の画素と、前記複数の画素毎に設けられたスイッチング素子と、前記複数の画素のうち互いに隣り合う2つの画素の夫々の開口領域の間隙に位置する非開口領域に設けられており、前記スイッチング素子に電気的に接続された第1導電膜と、少なくとも前記第1導電膜に重なり、前記非開口領域に第1のコンタクトホールが形成された第1絶縁層と、前記第1のコンタクトホールを介して前記第1導電膜に電気的に接続され、前記第1絶縁層上に形成されており、前記2つの画素のうち一方の画素の開口領域に延びる延在部を有する透明な第2導電膜と、前記第2導電膜上に積層され、前記開口領域に第2のコンタクトホールが形成された第2絶縁層と、前記第2のコンタクトホールを介して前記延在部に電気的に接続され、少なくとも前記一方の画素の開口領域に形成された画素電極と、を少なくとも備え、前記第2のコンタクトホールの内部は、前記画素電極よりも比抵抗が低い透明導電性材料によって充填されていることを、特徴とする。

【0011】

本適用例に係る電気光学装置によれば、開口領域に形成された第2のコンタクトホールの内部には、画素電極よりも比抵抗が低い透明導電性材料が充填されている。この充填は、好適には塗布法を用いて行なわれるため、当該コンタクトホール内をしっかりと充填した上で、その上部を平坦化することができる。また、所期の透明性も確保することができる。

よって、第2のコンタクトホールの上部における平坦性の確保が困難であった従来の電気光学装置よりも、優れた画像品質を得ることができる。

従って、所期の画像品質が得られる電気光学装置を提供することができる。

【0012】

さらに、充填される透明導電性材料は、画素電極よりも比抵抗が低いため、第2のコンタクトホールが画素電極部分と同じ膜質で形成されていた従来の電気光学装置よりも、当該コンタクトホールの導電性を高めることができる。つまり、電気配線として必要な導電性を確保することができる。よって、高速駆動にも対応することができる。

このように、本適用例に係る電気光学装置は、第2のコンタクトホールの透明性と平坦性とを両立することができるばかりでなく、電気配線として必要な導電性をも確保することができるという、格段の効果を奏するものである。

【0013】

(適用例2)

本適用例に係る電気光学装置の製造方法は、上述する課題を解決するために、基板と前記基板上で互いに交差する複数の走査線及び複数のデータ線と、前記走査線及び前記データ線の交差に対応して設けられた複数の画素と、前記複数の画素毎に設けられたスイッチング素子と、前記複数の画素のうち互いに隣り合う2つの画素の夫々の開口領域の間隙に位置する非開口領域に設けられており、前記スイッチング素子に電気的に接続された第1導電膜を形成する工程と、少なくとも前記第1導電膜に重なり、前記非開口領域に第1のコンタクトホールが設けられた第1絶縁層を形成する工程と、前記第1のコンタクトホールを介して前記第1導電膜に電気的に接続され、前記第1絶縁層上に設けられており、前記2つの画素のうち一方の画素の開口領域に延びる延在部を有する透明な第2導電膜を形成する工程と、前記第2導電膜上に積層され、第2のコンタクトホールが設けられた第2絶縁層を形成する工程と、前記第2のコンタクトホールの内部に、透明導電性材料を充填する工程と、前記第2のコンタクトホールを介して前記延在部に電気的に接続され、少なくとも前記一方の画素の開口領域に画素電極を形成する工程と、を含み前記透明導電性材料は、前記画素電極よりも比抵抗が低いことを特徴とする。

【0014】

本適用例の電気光学装置の製造方法によれば、上述した本適用例の電気光学装置を好適に製造することができる。

【0015】

(適用例3)

本適用例の電気光学装置の製造方法は、上述する課題を解決するために、透明導電性材料を充填する工程には、前記透明導電性材料を塗布する工程と、前記塗布した透明導電性材料を焼結する焼結工程と、を含むことを特徴とする。

【0016】

本適用例によれば、上述した本適用例の電気光学装置のうち、第2のコンタクトホールの内部に、好適に透明導電性材料を塗布し焼結することができる。換言すれば、第2のコンタクトホールの内部に、好適に透明導電性材料を充填することができる。

【0017】

(適用例4)

本適用例の電気光学装置の製造方法は、上述する課題を解決するために、塗布工程には、化学気相堆積法を用いることを特徴とする。

【0018】

本適用例によれば、上述した本適用例の電気光学装置のうち、第2のコンタクトホールの内部に、好適に透明導電性材料を充填することができる。

【0019】

(適用例5)

本適用例の電気光学装置の製造方法は、透明導電性材料を充填する工程の後に、前記第2のコンタクトホールが形成された部分を含む前記第2絶縁層の表面に対して、平坦化処理を施す工程を含むことを特徴とする。

【0020】

本適用例によれば、上述した本適用例の電気光学装置のうち、第2のコンタクトホールが形成された第2絶縁層の表面に、透明導電性材料の突出部分あるいは凸部があった場合でも、当該突出部分を平坦化することができる。

このように、第2絶縁層の表面を平坦化処理することにより、その後に形成される画素電極、配向膜などの平坦度を高めることができるため、表示ムラや、コントラスト低下などを低減することができる。

【0021】

(適用例6)

本適用例の電気光学装置の製造方法の一態様では、平坦化処理を施す工程には化学機械研磨法を含むことを特徴とする。

【0022】

本適用例によれば、効率的に平坦化処理を行なうことができる。

【0023】

(適用例7)

本適用例の電子機器は、上述の電気光学装置を備えたことを特徴とする。

【0024】

本適用例の電子機器によれば、上述した本発明に係る電気光学装置を具備してなるので、画像表示の高コントラスト化、高駆動化が達成され、より高画質の、投射型の液晶表示装置、テレビ、携帯電話、電子手帳、ワードプロセッサー、ビューファインダー型又はモニター直視型ビデオテープレコーダー、ワークステーション、テレビ電話、POS端末、タッチパネルなどの各種電子機器を実現することができる。また、本発明の電子機器として、例えば電子ペーパーなどの電気泳動装置、電界放出装置(Field Emission Display及びconduction Electro−Emitter Display)、これら電気泳動装置、電界放出装置を用いた表示装置を実現することも可能である。

【図面の簡単な説明】

【0025】

【図1】実施形態1に係る電気光学装置の平面図。

【図2】図1のH−H’側断面図。

【図3】実施形態1に係る電気光学装置の等価回路図。

【図4】実施形態1に係る電気光学装置の画素部の平面図(下層側)。

【図5】実施形態1に係る電気光学装置の画素部の平面図(中層側)。

【図6】実施形態1に係る電気光学装置の画素部の平面図(上層側)。

【図7】図4ないし図6のA−A’側断面図。

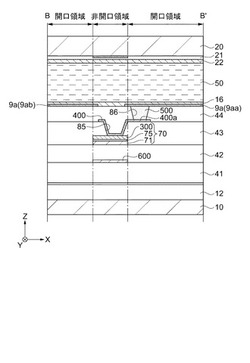

【図8】図4ないし図6のB−B’側断面図。

【図9】実施形態1に係る電気光学装置の製造方法におけるフローチャート図。

【図10】実施形態1に係る電気光学装置の製造方法の各工程断面図。

【図11】実施形態1に係る電気光学装置の製造方法の各工程断面図。

【図12】実施形態2に係る電気光学装置の画素部の平面図(下層側)。

【図13】実施形態2に係る電気光学装置の画素部の平面図(上層側)。

【図14】図12ないし図13のC−C’側断面図。

【図15】電子機器としてのプロジェクターの平面図。

【図16】従来の電気光学装置における画素部の側断面図。

【発明を実施するための形態】

【0026】

以下、本発明の実施形態について、図面を参照して説明する。なお、以下の各図においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材ごとに縮尺を異ならしめてある。

【0027】

(実施形態1)

「電気光学装置の全体構成」

図1及び図2を参照しながら、本実施形態に係る電気光学装置を説明する。図1は素子基板10を、その上に形成された各構成要素と共に対向基板20の方向から見た電気光学装置の平面図である。図2は図1のH−H’断面における側断面図である。本実施形態では、電気光学装置の一例として、駆動回路内蔵型のTFTアクティブマトリックス駆動方式の液晶表示装置を例にあげる。

【0028】

図1及び図2において、液晶表示装置1では素子基板10と対向基板20とが、向かい合う形で配置されている。素子基板10と対向基板20との間には液晶層50が封入されており、素子基板10と対向基板20とは、複数の画素部が設けられる画像表示領域10aの周囲に位置されるシール領域に設けられた、シール材52によって相互に接着されている。

【0029】

素子基板10は、好適例として石英基板を用いている。なお、石英基板に限定するものではなく、可視光領域において透明性を有する基板であれば良い。

対向基板20は、好適例として無アルカリガラスを用いている。なお、この構成に限定するものではなく、素子基板10、および対向基板20ともに、可視光領域において透明性を有する基板であれば良い。

液晶層50は、好適例として、一種、または数種類のネマティック液晶を混合した誘電率異方性が負の液晶を用いている。当該液晶は、電圧がかかっていない状態で液晶分子が垂直に配列し、電圧が印加されると液晶分子が寝た状態になるネガ液晶であれば一種類からなるものでも良いし、複数種の液晶を混合したものでも良い。なお、ネガ液晶を用いることに限定するものではなく、ポジ液晶を用いても良い。言い換えれば、ノーマリーブラックモードに限定するものではなく、ノーマリーホワイトモードであっても良い。

また、液晶モードも、VA(Vertical Aligned)モードに限定するものではなく、TN(Twisted Nematic)モードや、IPS(In−Plane Switching)モードなどの各種動作モードを用いても良い。

【0030】

シール材52は、両基板を貼り合わせるため、例えば紫外線硬化樹脂や熱硬化性樹脂等の接着剤からなり、素子基板10上に塗布された後、紫外線照射もしくは加熱等により硬化させられたものである。なお、シール材52中には、素子基板10と対向基板20との間隔(基板間ギャップ)を所定値とするためのグラスファイバーや、ガラスビーズ等のギャップ材が散布されている。

【0031】

対向基板20には、シール材52が配置されたシール領域の内側に沿って、画像表示領域10aの見切りを規定する遮光性の額縁遮光膜53が設けられている。ただし、このような額縁遮光膜53の一部又は全部は、素子基板10側に内蔵される遮光膜として設けられてもよい。

【0032】

ここで、画像表示領域10aの周辺には、周辺領域が存在する。具体的には、額縁遮光膜53より外側を周辺領域として規定する。また、対向基板20に対して素子基板10が張り出している領域を張出し領域と規定する。

【0033】

周辺領域のうち、シール材52が配置されたシール領域の外側に位置する領域であって、素子基板10の張出し領域にある一辺に、データ線駆動回路101及び外部回路接続端子102が設けられている。走査線駆動回路104は、この一辺の両端部から延びる2辺に沿い、且つ、額縁遮光膜53に重ねて配置されている。また、周辺領域のうちシール領域より内側に位置する領域には、画像表示領域10aの一辺に沿ってかつ額縁遮光膜53に重なるようにしてサンプリング回路7が配置されている。

【0034】

さらに、画像表示領域10aの両側に設けられた2つの走査線駆動回路104を電気的に接続するため、素子基板10の残る1辺に沿って、かつ額縁遮光膜53に重なるようにして複数の配線(図示せず)が設けられている。

【0035】

また、シール材52の外周における4つのコーナーには、素子基板10と対向基板20との間の上下導通をとるための上下導通部106が配置されている。上下導通部106には、例えば、異方性導電材料107が用いられており、当該異方性導電材料107を挟むように配置された各基板の配線間の電気的な接続が取られている。

さらに、素子基板10には、外部回路接続端子102と、データ線駆動回路101、走査線駆動回路104、上下導通部106などとを電気的に接続するための引き回し配線90が形成されている。

【0036】

ここで、図1にて横長の長方形をなした画像表示領域10aには、画像を表示する複数の画素がマトリックス状に形成されている。

なお、図1を含む各図においては、横長の長方形をなした画像表示領域10aにおける横方向をX軸方向とし、当該方向と交差する縦方向をY軸として定義している。また、液晶表示装置1の厚さ方向をZ軸方向としている。また、素子基板10から対向基板20へ向かう方向(+Z)を上層とし、その反対の方向(−Z)を下層と定義している。

【0037】

図2の素子基板10において、マトリックス状に形成された画素は、画素電極9aを最上層として、画素のスイッチング素子用のトランジスター(Thin Firm Transistor)や、走査線、データ線、層間絶縁膜などを積層した積層構造となっている。

また、画素電極9a上には、各画素電極9aを覆うように、ラビング処理等の所定の配向処理がされた配向膜が形成されている。他方、対向基板20の上(素子基板10と向かい合う面側)には、ITO等の透明導電性材料からなる対向電極21が複数の画素電極9aと対向して、略全面(共通電極)に形成されている。また対向電極21上にも配向膜が形成されている。なお、入射光がスイッチング素子30やその周辺へ侵入することを、確実に防止するために、格子状又はストライプ状の遮光膜23を設けるようにしてもよい。

【0038】

そして、液晶層50には、これら一対の配向膜間で、所定の配向状態を取ることになる。

【0039】

なお、素子基板10には、データ線駆動回路101、走査線駆動回路104の他に、図示は省略するが、製造と出荷時の当該液晶表示装置の品質、欠陥等を検査するための検査回路、検査用パターンなどが更に形成されていてもよい。

【0040】

「画素回路」

次に、図3を参照しながら液晶表示装置1の画素部の電気的な接続構成を詳細に説明する。図3は、液晶表示装置1の画像表示領域10aを構成するマトリックス状に形成された複数の画素における、各種素子、配線等の走査回路である。

【0041】

図3に示すように、液晶表示装置1の画像表示領域10aには、複数の走査線11aが、X軸方向に沿って延在している。複数の走査線11aと交差して、複数のデータ線6aがY軸方向に沿って延在している。

また、複数の走査線11aの延在方向に沿って複数の容量線350が配線されている。なお、容量線350は、データ線6aの延在方向(Y軸方向)に沿って配線されてもよい。画像表示領域10aを形成する複数の画素の各々は、走査線11aとデータ線6aとが交差する交差点ごとに形成されている。

【0042】

各画素は、画素電極9aに加えて、スイッチング素子30、および蓄積容量70を備えている。なお、好適例として、スイッチング素子30は、電界効果型のN型トランジスターを用いている。

各スイッチング素子30において、ゲート電極3aは対応する走査線11aに接続され、ソース端子は対応するデータ線6aに接続され、ドレイン端子は画素電極9a、および蓄積容量70の一端に接続されている。また、蓄積容量70の他の一端は所定の電位に設定された容量線350に接続されている。

【0043】

スイッチング素子30は、走査線11aに供給される走査信号G1、G2、…Gmによって選択されたタイミングで、データ線6aのデータ信号S1、S2、…Snを対応する画素電極9aに書き込む。つまり、走査線駆動回路104から各走査線11aに供給される走査信号G1、G2、…Gmのタイミングに従って、各画素が線順次に選択される。

また、データ線駆動回路101およびサンプリング回路7からは、走査信号による各画素の選択と同期して、データ信号S1、S2、…、Snが各データ線6aに供給される。詳しくは、サンプリング回路7は、連続する6本のデータ線に対して、データ線駆動回路101から供給されるサンプリング信号のタイミングに従って、6つに相展開された画像信号を同時にサンプリングし、各データ線に供給する。なお、ここでは、好適例として6相の相展開駆動を行う場合について説明したが、これに限定するものではなく、定められたフレームレートで違和感なく、画像を表示可能な駆動方法であれば良い。

【0044】

このようにして、画素電極9aを介して液晶層50に書き込まれた所定レベルのデータ信号S1、S2、…、Snは、対向基板20に形成された対向電極21との間で一定期間保持される。

また、書き込まれたデータ信号の電位を保持するために、画素電極9aと対向電極21との間に形成される液晶容量に対して電気的に並列に蓄積容量70が形成されている。

また、対向基板20の対向電極21(図2)は、対向電極生成回路(図示せず)に接続されており、周期的に極性が反転する対向電圧が供給され、反転駆動が行われる。反転駆動としては、ライン反転駆動や、フレーム反転駆動、ドット反転駆動などを用いることができる。

【0045】

「画素部の具体的な構成」

次に、図4ないし図8を参照しながら画素部の具体的な構成を説明する。図4ないし図6は、データ線6a、走査線11a、画素電極9a等が形成された素子基板10の互いに隣り合う複数の画素の平面図である。図7は、図4ないし図6のA−A’断面における側断面図であり、図8は、図4ないし図6のB−B’断面における側断面図である。

【0046】

図4ないし図8では、上述した画素部の各回路要素が、パターン化され、積層された導電膜として素子基板10上に形成されている。

図7では、各回路要素は、下から順に、走査線11aを含む第1層、スイッチング素子30等を含む第2層、データ線6a等を含む第3層、蓄積容量70等を含む第4層、第2導電膜としての中継層400等を含む第5層、画素電極9a等を含む第6層からなる。

【0047】

第1層−第2層間には下地絶縁膜12、第2層−第3層間には第1層間絶縁膜41、第3層−第4層間には第2層間絶縁膜42、第4層−第5層間には第1絶縁層としての第3層間絶縁膜43、第5層及び第6層間には第2絶縁層としての第4層間絶縁膜44が夫々設けられ、前述の各要素間が短絡することを防止している。このうち、第1層から第3層が下層部分として図4に示され、第4層が中層部分として図5に示され、第5層及び第6層が上層部分として図6に示されており、図4ないし図6では、説明の便宜上、画素電極9aより上側に位置する部分の図示を省略している。

尚、以下説明する各種配線、各種素子、および絶縁膜などは、蒸着法、スパッタリング法、CVD(Chemical Vapor Deposition)法、フォトリソ法、エッチング法などを単独、または組み合わせることによって、形成することができる。

【0048】

「第1層の構成−走査線等−」

図4及び図7において、第1層は、走査線11aで構成されている。走査線11aは、図4のX方向に沿って延びる本線部と、データ線6aが延在する図4のY方向に延びる突出部とからなる形状にパターニングされている。走査線11aは、例えば導電性ポリシリコンからなり、その他にもチタン(Ti)、クロム(Cr)、タングステン(W)、タンタル(Ta)、モリブデン(Mo)等の高融点金属のうちの少なくとも一つを含む金属単体、合金、金属シリサイド、ポリシリサイド又はこれらの積層体等により形成することができる。本実施形態では特に、走査線11aは、スイッチング素子30の下層側に、半導体層1aに対向する領域を含むように配置された導電膜である。このため、素子基板10における裏面反射や、液晶表示装置をライトバルブとして用いて複板式のプロジェクターを構築した場合に、他の液晶表示装置から発せられプリズム等の合成光学系を突き抜けてくる光などの、戻り光についても、走査線11aにより半導体層1aを下層側から遮光できる。

【0049】

「第2層の構成−スイッチング素子等−」

第2層は、スイッチング素子30で構成されている。スイッチング素子30は、例えばLDD(Lightly Doped Drain)構造とされ、ゲート電極3a、半導体層1a、ゲート電極3aと半導体層1aを絶縁するゲート絶縁膜を含んだ絶縁膜2を備えている。ゲート電極3aは、例えば導電性ポリシリコンで形成される。半導体層1aは、例えばポリシリコンからなり、チャネル領域1a’、低濃度ソース領域1b及び低濃度ドレイン領域1c、並びに高濃度ソース領域1d及び高濃度ドレイン領域1eからなる。

【0050】

尚、スイッチング素子30は、LDD構造を有することが好ましいが、低濃度ソース領域1b、低濃度ドレイン領域1cに不純物打ち込みを行わないオフセット構造であってもよいし、ゲート電極3aをマスクとして不純物を高濃度に打ち込んで高濃度ソース領域1d及び高濃度ドレイン領域1eを形成する自己整合型であってもよい。

【0051】

スイッチング素子30のゲート電極3aは、その一部分3bにおいて、下地絶縁膜12に形成されたコンタクトホール12cvを介して走査線11aに電気的に接続されている。下地絶縁膜12は、例えばシリコン酸化膜等からなり、第1層と第2層の層間絶縁機能の他、素子基板10の全面に形成されることで、基板表面の研磨による荒れや汚れ等が惹き起こすスイッチング素子30の素子特性の変化を防止する機能を有している。

【0052】

ちなみに、本実施形態に係るスイッチング素子30は、トップゲート型であるが、ボトムゲート型であってもかまわない。また、前述のトランジスターでも構わないし、薄膜ダイオード、バルクトランジスター等の2端子型又は3端子型のスイッチング素子からなるものでもよい。

【0053】

「第3層の構成−データ線等−」

第3層は、データ線6a及び中継層600で構成されている。

【0054】

データ線6aは、下から順にアルミニウム、窒化チタン、窒化シリコンの3層膜として形成されている。データ線6aは、スイッチング素子30のチャネル領域1a’を部分的に覆うように形成されている。このため、チャネル領域1a’に近接配置可能なデータ線6aによって、上層側からの入射光に対して、スイッチング素子30のチャネル領域1a’を遮光できる。また、データ線6aは、第1層間絶縁膜41を貫通するコンタクトホール81を介して、スイッチング素子30の高濃度ソース領域1dと電気的に接続されている。

【0055】

中継層600は、データ線6aと同一膜として形成されている。中継層600及びデータ線6aは、図4に示したように、夫々が分断されるように形成されている。中継層600は、第1層間絶縁膜41を貫通するコンタクトホール83を介して、スイッチング素子30の高濃度ドレイン領域1eと電気的に接続されている。

【0056】

第1層間絶縁膜41は、例えばNSG(ノンシリケートガラス)によって形成されている。その他、第1層間絶縁膜41には、PSG(リンシリケートガラス)、BSG(ボロンシリケートガラス)、BPSG(ボロンリンシリケートガラス)等のシリケートガラス、窒化シリコンや酸化シリコン等を用いることができる。

【0057】

「第4層の構成−蓄積容量等−」

図5及び図7において、第4層は、蓄積容量70で構成されている。ここで、蓄積容量70を液晶容量に並列に電気的に接続することで、画素電極9aの電圧を、実際に画像信号が印加されている時間よりも、例えば3桁も長い時間だけ保持することが可能となり、液晶層50の保持特性が改善されるため、高コントラスト比を有する液晶表示装置を実現することができる。

【0058】

蓄積容量70は、第1導電膜としての上部容量電極300と、下部容量電極71とが誘電体膜75を介して対向配置された構成となっている。上部容量電極300は、第2層間絶縁膜42を貫通するコンタクトホール84を介して、中継層600と電気的に接続されている。

【0059】

上部容量電極300は、液晶表示装置1の動作時に、スイッチング素子30を介してデータ線6aから画像信号が供給される。走査線11aを介して供給された走査信号に応じて、オンオフが切り換えられたスイッチング素子30は、データ線6aから供給された画像信号を、スイッチング素子30のドレイン側に電気的に接続された上部容量電極300に供給する。

【0060】

上部容量電極300又は下部容量電極71は、例えば、Al、Ti、Cr、W、Ta、Mo等の金属のうちの少なくとも一つを含む金属単体、合金、金属シリサイド、ポリシリサイド、ナイトライドこれらを積層したものからなる。このため、データ線6a上に第2層間絶縁膜42を介して近接配置可能な蓄積容量70によって、上層側からの入射光に対してスイッチング素子30のチャネル領域1a’を、より一層確実に遮光できる。

【0061】

誘電体膜75は、素子基板10上において、画素毎の開口領域の間隙に位置する非開口領域に形成されている、即ち、開口領域に殆ど形成されていない。よって、誘電体膜75が、仮に不透明な膜であっても、開口領域における透過率を低下させないで済む。従って、誘電体膜75は、透過率を考慮せず、誘電率が高いシリコン窒化膜等から形成されている。

このため、誘電体膜75は、水分や湿気を防ぐための膜としても機能させることが可能となり、耐水性、耐湿性を高めることも可能となる。尚、誘電体膜75としては、シリコン窒化膜の他、例えば、酸化ハフニュウム(HfO2)、アルミナ(Al2O3)、酸化タンタル(Ta2O5)等の単層膜又は多層膜を用いてもよい。

【0062】

第2層間絶縁膜42は、例えばNSG(ノンシリケートガラス)によって形成されている。その他、第2層間絶縁膜42には、PSG、BSG、BPSG等のシリケートガラス、窒化シリコンや酸化シリコン等の透明性を有する絶縁材料を用いて形成することができる。

第2層間絶縁膜42の表面は、化学機械研磨法(Chemical Mechanical Polishing:CMP)やスピンコート処理等の平坦化処理がなされていている。よって、下層側のこれらの要素に起因した凹凸が除去され、第2層間絶縁膜42の表面は平坦化されている。このため、素子基板10と対向基板20との間に挟みこまれた液晶層50の配向状態に乱れを生じさせる可能性を低減することができ、より高品位な表示が可能となる。尚、このような平坦化処理は、他の層間絶縁膜の表面に対して行ってもよい。

【0063】

「第5層の構成−中継層等−」

第4層の全面には、第1のコンタクトホールとしてのコンタクトホール85が設けられた(開口した)、第3層間絶縁膜43が形成されている。コンタクトホール85の底部には、上部容量電極300が露出している。中継層400は、コンタクトホール85内から第3層間絶縁膜43の表面に沿って延在されている。

ここで、中継層400は、ITO等の透明導電性材料から構成されている。

中継層400は、後に図8を参照しながら説明するように、画素における第4層間絶縁膜44の表面に延在される画素電極9a(9aa)に電気的に接続されており、画像信号を画素電極9a(9aa)に供給する。

【0064】

第3層間絶縁膜43は、例えばNSGによって形成されている。その他、第3層間絶縁膜43には、PSG、BSG、BPSG等のシリケートガラス、窒化シリコンや酸化シリコン等の透明性を有する絶縁材料を用いることができる。第3層間絶縁膜43の表面は、第2層間絶縁膜42と同様にCMP等の平坦化処理がなされていてもよい。

【0065】

「第6層の構成−画素電極等−」

図6及び図7において、第5層の全面には第4層間絶縁膜44が形成され、更にその上に、第6層として画素電極9aが形成されている。第4層間絶縁膜44は、例えばNSGによって形成されている。その他、第4層間絶縁膜44には、PSG、BSG、BPSG等のシリケートガラス、窒化シリコンや酸化シリコン等の透明性を有する絶縁材料を用いることができる。第4層間絶縁膜44の表面は、第3層間絶縁膜43と同様にCMP等の平坦化処理がなされていてもよい。

【0066】

画素電極9a(図6中、破線9a’で輪郭が示されている)は、縦横に区画配列された画素の各々に配置され、その境界にデータ線6a及び走査線11aが格子状に配列するように形成されている。画素電極9aは、例えばITO等の透明導電性材料からなる。画素電極9aの上層には、ラビング処理等の所定の配向処理が施された配向膜16が設けられている。

ここで、本実施形態では、画素電極9aに重なり、光を透過(光変調)する領域のことを「開口領域」、データ線6a及び走査線11aなどが形成された格子状の遮光領域のことを「非開口領域」と定義している。開口領域は、実際には画素電極9aよりも若干小さくなるが、略画素電極9aのサイズと略同等と見なすことができる。非開口領域は、いわゆるブラックマトリックス(BM)である。

【0067】

次に、図6及び図8を参照しながら画素部における具体的な構成をより詳細に説明する。

【0068】

図6及び図8において、中継層400は、コンタクトホール85を介して上部容量電極300に電気的に接続されている。

ここで、素子基板10上において、蓄積容量70及び中継層600が形成された領域は、画素における光を透過させない非開口領域となる。中継層400は、非開口領域の両側に位置する開口領域の一方に延びる延在部400aを有している。延在部400aは、画素電極9aaの一領域でもあり、透明導電性材料からなる。したがって、開口領域に延びる延在部400aが、当該開口領域を透過する光を遮ることはなく、延在部400aによって開口領域が狭められることはない。

【0069】

第4層間絶縁膜44には、第2のコンタクトホールとしてのコンタクトホール86が、異方性エッチング法等を用いて第4層間絶縁膜44に形成されている。コンタクトホール86は、第4層間絶縁膜44のうち、XY平面上、延在部400aに重なる部分を除去することによって形成されている。

【0070】

コンタクトホール86の内部には、画素電極よりも比抵抗の低い透明導電性材料が充填された充填部500が形成されている。

ここで、画素電極よりも比抵抗の低い透明導電性材料とは、例えば、In(インジウム)などの金属の含有率が高い材料である。そして、充填部500によって、第2導電膜400と、後に形成される画素電極9a(9aa)との電気的接続を取っている。

【0071】

なお、図8において、充填部500はコンタクトホール86の内部を完全に満たしており、かつ、コンタクトホール86のZ軸(+)側の開口面(上面)と略同一面となっている。換言すれば、第4層間絶縁膜44の表面と略同一面となっている。

なお、充填部500は、コンタクトホール86の開口面に対して若干の凹部や突出部分があったとしても、従来のコンタクトホールにおける凹部よりも、平坦化されていれば、画質を向上させることができる。

【0072】

画素電極9a(9aa)は、例えばITO等の透明導電性材料をスパッタリング法等の既存の成膜方法を用いて、充填部500および第4層間絶縁膜44上に形成されている。なお、充填部500の存在により、画素電極9a(9aa)は、従来例(図16)のようにコンタクトホール86のすり鉢状の表面形状をなぞらえることなく、第4層間絶縁膜44に対して平坦性の高い膜となっている。

【0073】

配向膜16は、画素電極9a上に、例えばポリイミドなどの有機膜を用いて形成されている。配向膜16もまた、コンタクトホール86の内部に形成された充填部500の効果により、画素電極9a上において略平坦に形成することが可能となる。換言すれば、平坦度が高い下地に沿って、配向膜16が形成されている。

【0074】

対向基板20には、液晶層50側の略全面に対向電極21が設けられており、更にその上層(Z軸(−)側)に配向膜22が形成されている。

対向電極21は、画素電極9aと同様、例えばITO膜等の透明導電性材料からなる。尚、対向基板20と対向電極21の間には、スイッチング素子30における光リーク電流の発生等を防止するため、少なくともスイッチング素子30と正対する領域を覆うように遮光膜23が設けられている。

【0075】

このように構成された素子基板10と対向基板20の間には、液晶層50が設けられている。液晶層50は、素子基板10及び対向基板20の周縁部をシール材により封止して形成した空間に液晶を封入して形成される。液晶層50は、画素電極9aと対向電極21との間に電界が印加されていない状態において、ラビング処理等の配向処理が施された配向膜16及び配向膜22によって、所定の配向状態をとるようになっている。

【0076】

上述した画素部の構成は、図4ないし図6に示すように、各画素部に共通である。画像表示領域10a(図1参照)には、かかる画素部が周期的に形成されていることになる。他方、このような液晶表示装置1では、画像表示領域10aの周囲に位置する周辺領域に、図1及び図2を参照して説明したように、走査線駆動回路104及びデータ線駆動回路101等の駆動回路が形成され、画像表示が行われる。

【0077】

「電気光学装置の製造方法」

次に、図9ないし図11を参照しながら、本実施形態に係る電気光学装置の製造方法を説明する。図9は、本実施形態に係る電気光学装置の製造方法を示すフローチャートであり、図10および図11は、当該電気光学装置の製造工程のうち、コンタクトホール形成工程に関連のある部分を抽出して示した、各製造工程態様における断面図である。

【0078】

まず、ステップS1では、石英等の素子基板10を用意するとともに、素子基板10上に、走査線11a、下地絶縁膜12等を形成する。

走査線11aは、例えば導電性ポリシリコンや、その他Ti、Cr、W、Ta、Mo等の高融点金属のうち少なくとも1つを含む金属単体、合金、金属シリサイド、ポリシリサイド又はこれらの積層体等を用いてスパッタリング法により形成した後、フォトリソ及びエッチングによって格子状に形成される。

また、下地絶縁膜12は、例えば、常圧又は減圧CVD法等によりTEOS(テトラ・エチル・オルソ・シリケート)ガス、TEB(テトラ・エチル・ボートレート)ガス、TMOP(テトラ・メチル・オキシ・フォスレート)ガス等を用いて、例えばNSG、PSG、BSG、BPSG等のシリケートガラス膜、窒化シリコン膜や酸化シリコン膜等からなるように形成する。

【0079】

ステップS2では、下地絶縁膜12上に、半導体層1aを含むスイッチング素子30、第1層間絶縁膜41、データ線6a、第2層間絶縁膜42、及び蓄積容量70を順次、積層構造となるように形成する。

このうちスイッチング素子30は、半導体層1aに対する不純物イオンの導入工程の他、絶縁膜2の形成工程、及びゲート電極3aの形成工程を含むが、これらについては公知の方法を利用すればよく、その詳細な説明は省略する。

【0080】

また、第1層間絶縁膜41及び第2層間絶縁膜42は、下地絶縁膜12と同様な方法により形成される。

さらに、蓄積容量70は、上部容量電極300及び下部容量電極71、並びに誘電体膜75の各要素の形成工程を含む。2つの電極については、例えばAl、Ti、Cr、W、Ta、Mo等の金属のうちの少なくとも一つを含む金属単体、合金、金属シリサイド、ポリシリサイド、ナイトライドこれらを積層したもの等の適当な導電性材料からなり。スパッタリング法、フォトリソ法及びエッチング法等を用いて形成される。

誘電体膜75は、シリコン窒化膜の他、例えば、酸化ハフニュウム(HfO2)、アルミナ(Al2O3)、酸化タンタル(Ta2O5)等の適当な絶縁性材料の単層膜又は多層膜を用いて、形成することができる。

なお、図10(a)には、蓄積容量70までが形成された状態が示されている。

【0081】

ステップS3では、図10(b)に示すように、蓄積容量70上に、第3層間絶縁膜43を形成する。第3層間絶縁膜43は、下地絶縁膜12と同様な方法により形成される。

ステップS4では、図10(c)に示すように、第3層間絶縁膜43に対して、反応性イオンエッチング、反応性イオンビームエッチング等のドライエッチングを施すことにより、コンタクトホール85を形成する。

【0082】

ステップS5では、図10(d)に示すように、コンタクトホール85の内部および周縁部に対して、中継層400を形成する。中継層400は、ITO等の透明導電性材料からなり、スパッタリング法等の既存の成膜方法を用いて形成されている。

ステップS6では、図10(e)に示すように、中継層400の上に、第4層間絶縁膜44を形成する。第4層間絶縁膜44は、下地絶縁膜12と同様な方法により形成される。

ステップS7では、図10(f)に示すように、第4層間絶縁膜44に対して、コンタクトホール86を形成する。コンタクトホール86は、コンタクトホール85と同様の方法で形成される。

【0083】

ステップS8では、図11(g)に示すように、コンタクトホール86に対して、画素電極よりも比抵抗が低い透明導電性材料を塗布する。

塗布にあたっては、まず、画素電極よりも比抵抗が低い透明導電性材料を含有したインクの前駆体から、塗布に最適な粘性等を満たしたインクを準備する。好適例におけるインクの前駆体としては、トリメチル、トリエチル、テトラメチル、テトラエチルのいずれかの有機In(インジウム)と有機Sn(スズ)とが低沸点低分子量の有機溶媒、特に炭化水素系有機溶剤、例えば、DMF、トルエン、ジブチルエーテル、ジフライム、メチルエチルケトン、メチルジクロヘキサノン、セロソルブアセテートなどに混合されて成るものである。さらに、In、Snの粒子径を調整したITOナノインクでも良い。

続いて、該インクをニードル方式、インクジェット方式など公知の吐出方法を用いて、コンタクトホール86へ塗布(充填)する。ここで、塗布するにあたって、該インクは第4層間絶縁膜44の表面よりも突出した形となるまで形成してもよい。

なお、本工程は大気圧中で行なっても良いが、減圧雰囲気で行なうことがより好ましい。減圧雰囲気であれば、透明導電性材料をコンタクトホール86に充填する際に、充填部500の内部に気泡を内在させないよう、脱泡しながら行うことが可能であるからである。また、塗布時間、塗布圧などは、使用する該インクの性質により適宜調整する。

また、ここで述べた塗布とは、液状のインクをコンタクトホール86に対して、滴下することに限定するものではなく、コンタクトホール86内に、透明導電性材料を充填可能な方法であれば良い。例えば、ペースト状のインクをスクリーン印刷しても良いし、粘度の低いインクをスピンコート法で第4層間絶縁膜44の全面に塗布する方法であっても良い。

【0084】

ステップS9では、図11(h)に示すように、塗布された透明導電性材料を焼結する。

焼結するにあたって、例えばN2+O2などの酸素雰囲気下で、300〜500℃、30分〜6時間の熱処理を施すと良い。本熱処理により、有機溶媒の揮発と共に有機In、有機Snの酸化が行われ、所期の透明性と、導電性とを有する充填部500が形成される。

なお、この熱処理に変えて、紫外線照射によって、炭化系有機溶剤である有機In、有機Snを解離させると同時に、酸素雰囲気下でIn、Snを酸化させて透明導電性材料を焼結させる方法を用いても良い。

【0085】

ステップS10では、図11(i)に示すように、コンタクトホール86の充填部500を含む第4層間絶縁膜44の表面に対して、平坦化処理を施す。好適例としては、CMP(Chemical Mechanical Polishing)処理を用いる。なお、その他、種々の平坦化技術を利用しても良い。

CMP処理とは、被処理基板と研磨布(パッド)の両者を回転等させながら、それぞれの表面同士を当接させるとともに、該当接部位にシリカ粒等を含んだ研磨液(スラリー)を供給することによって、被処理基板表面を、機械的作用と化学作用の兼ね合いにより研磨し、当該表面を平坦化する技術である。

本実施形態においては、コンタクトホール86に対する充填部500の形成が完了している素子基板10を、上述の「被処理基板」に当てはめて考えればよい。

なお、研磨処理の終了時点の調整は、適当な時間の経過によるか、あるいは適当なストッパー層を素子基板10上の所定位置に形成しておくこと等によって行う。この研磨処理の終了の時点において、コンタクトホール86が完成したとみることができる。

【0086】

ステップS11では、図11(j)に示すように、第4層間絶縁膜44の表面上に対して、画素電極9a及び配向膜16(図示せず)を形成する。

具体的には、第4層間絶縁膜44の表面上に、透明導電性材料を用いてスパッタリング法、フォトリソ法及びエッチング法を実施することで画素電極9aが形成される。そして画素電極9a上に、透明なポリイミド材料等からなる配向膜16が形成される。

ここで、スパッタリング法で形成される画素電極9aは、その原理上、第4層間絶縁膜44の表面形状に沿った形状となる。つまり、画素電極9aは、平坦化処理された第4層間絶縁膜44の平坦度を略踏襲したものとなる。

【0087】

以上述べたように、本実施形態に係る液晶表示装置1、およびその製造方法によれば、以下の効果を得ることができる。

液晶表示装置1によれば、開口領域に形成されたコンタクトホール86の内部には、画素電極よりも比抵抗が低い透明導電性材料が充填された充填部500が形成されている。

この充填は、好適には塗布法を用いて行なわれるため、当該コンタクトホール内をしっかりと充填した上で、その上部を平坦化することができる。また、所期の透明性も確保することができる。

よって、コンタクトホール86の上部における平坦性の確保が困難であった従来の電気光学装置よりも、優れた画像品質を得ることができる。

従って、所期の画像品質が得られる液晶表示装置1を提供することができる。

【0088】

さらに、充填される透明導電性材料は、画素電極よりも比抵抗が低いため、コンタクトホール86が画素電極部分と同じ膜質で形成されていた従来の電気光学装置よりも、当該コンタクトホールの導電性を高めることができる。つまり、電気配線として必要な導電性を確保することができる。よって、高速駆動にも対応することができる。

このように、液晶表示装置1は、コンタクトホール86の透明性と平坦性とを両立することができるばかりでなく、電気配線として必要な導電性をも確保することができるという、格段の効果を奏するものである。

【0089】

(実施形態2)

図12ないし図14を参照しながら、実施形態2に係る液晶表示装置を説明する。

図12および図13は、本実施形態に係る素子基板10の平面図である。図14は、図12及び図13のC−C’断面における側断面図を示すものである。図12では、中継層91及び92より下層側(−Z)の各層を示しており、図13では、中継層91及び92より上層側(+Z)の各層を示している。

【0090】

なお、本実施形態の液晶表示装置は、実施形態1の液晶表示装置1における積層(平面)構造とは異なる積層構造を有する液晶表示装置である。詳しくは、スイッチング素子30を含む第2層より上層の構造が液晶表示装置1と異なる。それ以外の走査線11aを含む第1層から、スイッチング素子30を含む第2層までの構造は、液晶表示装置1と同様である。

よって、実施形態1と同一の構成部位については、同一の番号を附し、重複する説明は省略する。

以下、図12ないし図14を用いて、実施形態1との相違点を中心に説明する。

【0091】

まず、第1の相違点として、スイッチング素子30を、データ線6aおよび中継層92の双方で覆うように配置していることにある。本構成により、スイッチング素子30の遮光性が高まるために、スイッチング素子30の誤動作を防止でき、信頼性の高い液晶表示装置を提供できる。

第2の相違点として、蓄積容量170を開口領域に設けていることにある。本構成により、蓄積容量170の容量値を大きくし、且つ開口領域のサイズを広げることができる。

第3の相違点として、蓄積容量170を画素間で分離するための容量分離膜80が形成されていることにある。本構成により、好適な容量値を選択することができる。

順を追って説明する。

【0092】

図12ないし図14において、データ線6aは、層間絶縁膜46に形成されたコンタクトホール34、層間絶縁膜45上に形成された中継層91、コンタクトホール31を介して、スイッチング素子30の高濃度ソース領域1dと電気的に接続されている。

一方、層間絶縁膜45上にある中継層92は、コンタクトホール32を介して、スイッチング素子30の高濃度ドレイン領域1eと電気的に接続されている。

【0093】

そして、データ線6aは、スイッチング素子30に対して重なるように配置されている。一方、中継層92は、スイッチング素子30の少なくともチャネル領域1a’の一部から、高濃度ドレイン領域1eを覆うように配置されている。つまり、データ線6aと中継層92とが、スイッチング素子30を覆うように配置されている。

【0094】

続いて、第2の相違点について詳しく説明する。

図13および図14によれば、蓄積容量170は、上部容量電極として機能する画素電極9a、下部容量電極171、および誘電体膜175で構成されている。

画素電極9aは、スイッチング素子30の高濃度ドレイン領域1eと、中継層92、中継層93、及び層間絶縁膜47上にある中継層400、本発明に係る画素電極よりも比抵抗の低い透明導電性材料を充填した充填部500を介して電気的に接続されている。

下部容量電極171は、蓄積容量170の片方の電極として機能し、容量線350に電気的に接続されることによって、固定電位に保持されている。

誘電体膜175は、下部容量電極171上に、下部容量電極171を覆うようにベタ状に形成されている。

【0095】

ここで、画素電極9aと下部容量電極171とはITO等の透明導電性材料で構成されている。また、誘電体膜175は、透明な誘電性材料である窒化シリコン等で構成されている。よって、これらで構成される蓄積容量170は、可視光に対して透明となるため、光透過率を殆ど低下させることはなく、透過光を有効に利用することができる。すなわち、蓄積容量170を、開口領域に形成することが出来るため、蓄積容量170の容量を大きくし、かつ開口領域のサイズを広げることが出来る。

【0096】

続いて、第3の相違点について説明する。

図13に示すように、蓄積容量を画素間で分離するための容量分離膜80は、隣り合う画素に跨る下部容量電極171の開口部を避けるように、容量分離膜80の開口部を略H型の形状に有している。

そしてこの容量分離膜80の開口部の形状に、概ね沿った状態で下部容量電極171と画素電極9aとが対向配置されて、蓄積容量170を構成する。

すなわち、隣り合うデータ線6aの間に設けられる下部容量電極171の開口部と、隣り合うデータ線6aの間にもそれぞれ容量分離膜80の開口部が設けられて(図13でドットハッチにて図示している領域)蓄積容量170を構成することで、画素電極9aの内側における蓄積容量領域の平面的な面積をできるだけ多く確保している。

【0097】

ここで仮に、蓄積容量170の容量値が小さい場合、画像信号を保持できる時間が短くなるため、表示画像の画質はあまり改善しない。

一方、蓄積容量170の容量値が大きい場合、画像信号を長期間保持できるため表示画像の画質の改善を期待することができるものの、画像信号の供給回路や配線等が大型化してしまう。

そのため、実際の液晶表示装置では、蓄積容量170の容量値が好適な値に調整される。本適用例によれば、容量分離膜80によって、蓄積容量170の容量値を大きくできると共に、容量分離膜80の面積の加減により好適な容量値を選択し、設計自由度を高めることが出来る。

【0098】

なお、本実施形態における製造方法については、実施形態1の製造方法を適用することができる。

【0099】

以上説明したように、実施形態2に係る液晶表示装置によれば、実施形態1における効果に加えて、以下の効果を得ることができる。

【0100】

本実施形態の液晶表示装置によれば、従来の液晶表示装置よりも、遮光性が高く、蓄積容量170の容量値を大きくし、且つ開口領域のサイズを広げることが可能であるため、液晶表示装置の表示性能を向上させることが可能である。

従って、表示ムラがなく、高コントラストで優れた画像品質の液晶表示装置を提供することができる。

【0101】

なお、本発明は上述した実施形態に限定されず、上述した実施形態に種々の変更や改良などを加えることが可能である。変形例を以下に述べる。

【0102】

(変形例)

前述した「電気光学装置の製造方法」において、図9に示すステップS8及びS9に変えて、スプレー式CVDにて行うことも可能である。本方法を用いることにより、コンタクトホール86に画素電極9aよりも、より比抵抗の低い透明導電性材料を充填することが可能となる。

【0103】

ここで、スプレー式CVD法とは、透明導電性材料の原材料となる金属塩化物の水溶液や金属錯体を溶質とする有機溶液(本適用例の場合は、InCl3、SnCl2、SnCl4など)を霧化して、素子基板上に吹き付ける方法であって、大気中のその場で結晶性の薄膜を成長させることが可能な方法である。

なお、超音波振動によって霧化する場合を特にパイロゾル法と呼んでいるが、本発明においては、超音波振動の有無を問わず適用可能であるため、スプレー式CVD法と表記した場合には、パイロゾル法も含むこととする。

【0104】

一般に、透明導電性材料の比抵抗は、各種物理量の中で、不純物などの格子欠陥の存在に最も敏感であり、例えば、純金属への微量不純物の添加によってその比抵抗は、顕著に増加する。

しかしながら、スプレー式CVD法に使用される有機溶液は、高純度の薬品から加工なしで調整することが可能であるため、不純物の混入が極めて少ない、つまり比抵抗の低い透明導電性材料を製造するのに大変有利である。

【0105】

なお、画素電極9aの製造方法で用いられる前述のスパッタリング法には、一般的に、酸化Inと酸化Snとの粉末を熱焼結法で作成したターゲット材を使用する。

この熱焼結法の過程で、ターゲット中に重金属不純物(Fe、Cuなど)が混入し、低純度のターゲットとなってしまうため、画素電極9aと同じ製造方法でコンタクトホール86を充填した場合、比抵抗の高い充填部500を形成してしまうのである。

【0106】

以下、具体的にスプレー式CVD法を用いた製造方法について記す。

本発明に用いられるスプレー式CVD法は、例えば前述した有機溶液を用いて、基板雰囲気、基板温度、処理時間を適宜設定することにより、所望の特性を有する透明導電性材料を得ることが可能となる。

これにより、本変形例に係る電気光学装置の製造方法によれば、コンタクトホール86に画素電極9aよりも比抵抗が低い透明導電性材料を充填することが可能となる。

【0107】

以上から、表示ムラ、コントラストの面で優れた画像表示が可能となり、さらに画像表示の高速駆動が可能になる。

【0108】

「電子機器」

次に、図15を参照しながら、上述した液晶表示装置を、電子機器の一例であるプロジェクターにライトバルブとして適用した例を説明する。図15は、プロジェクターの構成例を示す平面図である。

【0109】

図15において、プロジェクター1100の内部には、ハロゲンランプ等の白色光源からなるランプユニット1102が設けられている。このランプユニット1102から射出された投射光は、ライトガイド1104内に配置された4枚のミラー1106及び2枚のダイクロイックミラー1108によってRGBの3原色に分離され、各原色に対応するライトバルブとしての液晶パネル1110R、1110B及び1110Gに入射される。

【0110】

液晶パネル1110R、1110B及び1110Gの構成は、上述した電気光学装置と同等であり、画像信号処理回路から供給されるR、G、Bの原色信号でそれぞれ駆動されるものである。そして、これらの液晶パネルによって変調された光は、ダイクロイックプリズム1112に3方向から入射される。このダイクロイックプリズム1112においては、R及びBの光が90度に屈折する一方、Gの光が直進する。従って、各色の画像が合成される結果、投射レンズ1114を介して、スクリーン等にカラー画像が投射されることとなる。

【0111】

ここで、各液晶パネル1110R、1110B及び1110Gによる表示画像について着目すると、液晶パネル1110Gによる表示画像は、液晶パネル1110R、1110Bによる表示画像に対して左右反転することが必要となる。

【0112】

尚、液晶パネル1110R、1110B及び1110Gには、ダイクロイックミラー1108によって、R、G、Bの各原色に対する光が入射するので、カラーフィルターを設ける必要はない。

【0113】

尚、図15を参照して説明した電子機器の他にも、モバイル型のパーソナルコンピューターや、携帯電話、液晶テレビ、ビューファインダー型もしくはモニター直視型のビデオテープレコーダー、カーナビゲーション装置、ページャー、電子手帳、電卓、ワードプロセッサー、ワークステーション、テレビ電話、POS端末、タッチパネルを備えた装置等があげられる。そして、これら各種電子機器に適用可能なのは言うまでもない。

【0114】

また、本発明は上述の各実施形態で説明した液晶装置以外にも、反射型液晶装置(LCOS)、プラズマディスプレイ(PDP)、電解放出型ディスプレイ(FED、SED)、有機ELディスプレイ、デジタルマイクロミラーデバイス(DMD)、電気泳動装置等にも適用可能である。

【0115】

本発明は、上述した実施形態に限られるものではなく、請求の範囲及び明細書全体から読み取れる発明の要旨或は思想に反しない範囲で適宜変更可能であり、そのような変更を伴う電気光学装置、及び該電気光学装置を備えた電子機器もまた本発明の技術的範囲に含まれるものである。

【符号の説明】

【0116】

1a…半導体層、1a´…チャネル領域、1b…低濃度ソース領域、1c…低濃度ドレイン領域、1d…高濃度ソース領域、1e…高濃度ドレイン領域、2…絶縁膜、3a…ゲート電極、6a…データ線、7…サンプリング回路、9a…画素電極、10…素子基板、11a…データ線、12…下地絶縁膜、16…配向膜、20…対向基板、21…対向電極、22…配向膜、23…遮光膜、30…スイッチング素子、31/32/34…コンタクトホール、41…第1層間絶縁膜、42…第2層間絶縁膜、43…第3層間絶縁膜、44…第4層間絶縁膜、45…層間絶縁膜、46…層間絶縁膜、47…層間絶縁膜、50…液晶層、52…シール材、53…額縁遮光膜、70…蓄積容量、71…下部容量電極、75…誘電体膜、81/83/84/85/86…コンタクトホール、90…引き回し配線、91/92…中継層、101…データ線駆動回路、102…外部回路接続端子、104…走査線駆動回路、106…上下導通部、107…異方性導電材料、171…下部容量電極、175…誘電体膜、300…上部容量電極、350…容量線、400/600…中継層、1100…プロジェクター、1102…ランプユニット、1104…ライトガイド、1106…ミラー、1108…ダイクロイックミラー、1110R(1110G、1110B)…液晶パネル、G1〜Gm…走査信号、S1〜Sn…データ信号。

【技術分野】

【0001】

本発明は、電気光学装置、およびその製造方法、ならびに当該電気光学装置を備えた電子機器に関するものである。

【背景技術】

【0002】

従来より、電気光学装置の一例である透過型の液晶表示装置は、例えばプロジェクターのような投射型表示装置の光変調手段(ライトバルブ)として多用されている。そして、ライトバルブ用途に用いられる液晶表示装置には、小型、高密度、高精細であることに加えて、画素の開口率の高さが求められていた。

このような高密度化、高精細化に伴う画素の狭ピッチ化と、開口率の向上に伴い、各画素を区画するBM(Black Matrix)の幅が狭くなり、十分な配線スペースを確保することが困難になってきている。

そこで、出願人等はコンタクトホールをBM領域(非開口領域)のみならず、開口領域にも配置した構造を提案している(特許文献1)。

【0003】

この構成により、狭ピッチ化が進んでも、必要な配線スペース(ギャップも含む)を確保することができるため、隣の画素に誤った画像が表示されてしまうといった混線を防止することを可能にしている。さらに特許文献1では、開口領域にコンタクトホールを配置するため、表示画像の品質に影響を与えないように、コンタクトホールを画素電極と同じ透明導電性材料で形成することも提案している。

図16は、従来の画素電極近傍における側断面図であり、画素電極9aを延在して形成したコンタクトホール86が示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−192975号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1の技術では、開口領域に設けたコンタクトホールの上部における平坦性が確保できないため、所期の画像品質を得ることが困難であるという課題があった。詳しくは、図16に示すように、開口領域に形成されたコンタクトホールは、すり鉢状の凹部となっており、画素電極の平坦性を損なっていた。

このため、平坦性が損なわれた部分で生じる透過光の散乱や反射に起因して、画像表示にムラが生じたり、コントラストが低下するなど、画像品質に影響を及ぼしていた。

【0006】

また、上記課題を解決するために、画素電極の形成時において、コンタクトホールの内部を透明導電性材料で埋め込み、平坦性を確保することも考えられるが、実現性が乏しかった。

これは、画素電極部分と、コンタクトホール部分とに要求される膜質が異なるにも拘らず、同一工程で両者を形成することに無理があるからである。

詳しくは、画素電極部分には、透明性と表面の平坦度とが要求されるため、これらを満たす膜質(グレインサイズなど)が得られる条件設定のスパッタリング法で形成される。他方、コンタクトホール部分には、透明性と、電気配線としての導電性とが要求されるが、画素電極部分と同じ条件設定で形成した場合には、必要な導電性を確保することが困難であった。さらに、スパッタリング法の原理からして、コンタクトホールの凹部の膜厚を選択的に厚く形成することも困難であった。

つまり、コンタクトホールにおける透明性と、平坦性とを確保(両立)することは困難であるという課題があった。

【0007】

また、このように、画素電極部分と同じ膜質で形成されたコンタクトホールでは、十分な導電性が得られないため、高速駆動への対応が困難であるという課題があった。詳しくは、ITO(Indium Tin Oxide)で形成されたコンタクトホールは、BM内部に形成された金属配線に比べて高抵抗であるため、残像を誘発してしまう恐れがあった。

【0008】

また、前述の高抵抗対策として、コンタクトホールの大きさ(直径)を大きくすることで、内壁の面積を大きくし、画素電極との接触面積を広く取ることも考えられるが、この場合、平坦性がより悪くなってしまうという課題があった。

つまり、コンタクトホールの平坦性と導電性とは、トレードオフの関係にあり、これらを両立することは、困難であるという課題があった。

【課題を解決するための手段】

【0009】

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態または適用例として実現することが可能である。

【0010】

(適用例1)

本適用例に係る電気光学装置は、基板と、前記基板上で互いに交差する複数の走査線及び複数のデータ線と、前記走査線及び前記データ線の交差に対応して設けられた複数の画素と、前記複数の画素毎に設けられたスイッチング素子と、前記複数の画素のうち互いに隣り合う2つの画素の夫々の開口領域の間隙に位置する非開口領域に設けられており、前記スイッチング素子に電気的に接続された第1導電膜と、少なくとも前記第1導電膜に重なり、前記非開口領域に第1のコンタクトホールが形成された第1絶縁層と、前記第1のコンタクトホールを介して前記第1導電膜に電気的に接続され、前記第1絶縁層上に形成されており、前記2つの画素のうち一方の画素の開口領域に延びる延在部を有する透明な第2導電膜と、前記第2導電膜上に積層され、前記開口領域に第2のコンタクトホールが形成された第2絶縁層と、前記第2のコンタクトホールを介して前記延在部に電気的に接続され、少なくとも前記一方の画素の開口領域に形成された画素電極と、を少なくとも備え、前記第2のコンタクトホールの内部は、前記画素電極よりも比抵抗が低い透明導電性材料によって充填されていることを、特徴とする。

【0011】

本適用例に係る電気光学装置によれば、開口領域に形成された第2のコンタクトホールの内部には、画素電極よりも比抵抗が低い透明導電性材料が充填されている。この充填は、好適には塗布法を用いて行なわれるため、当該コンタクトホール内をしっかりと充填した上で、その上部を平坦化することができる。また、所期の透明性も確保することができる。

よって、第2のコンタクトホールの上部における平坦性の確保が困難であった従来の電気光学装置よりも、優れた画像品質を得ることができる。

従って、所期の画像品質が得られる電気光学装置を提供することができる。

【0012】

さらに、充填される透明導電性材料は、画素電極よりも比抵抗が低いため、第2のコンタクトホールが画素電極部分と同じ膜質で形成されていた従来の電気光学装置よりも、当該コンタクトホールの導電性を高めることができる。つまり、電気配線として必要な導電性を確保することができる。よって、高速駆動にも対応することができる。

このように、本適用例に係る電気光学装置は、第2のコンタクトホールの透明性と平坦性とを両立することができるばかりでなく、電気配線として必要な導電性をも確保することができるという、格段の効果を奏するものである。

【0013】

(適用例2)

本適用例に係る電気光学装置の製造方法は、上述する課題を解決するために、基板と前記基板上で互いに交差する複数の走査線及び複数のデータ線と、前記走査線及び前記データ線の交差に対応して設けられた複数の画素と、前記複数の画素毎に設けられたスイッチング素子と、前記複数の画素のうち互いに隣り合う2つの画素の夫々の開口領域の間隙に位置する非開口領域に設けられており、前記スイッチング素子に電気的に接続された第1導電膜を形成する工程と、少なくとも前記第1導電膜に重なり、前記非開口領域に第1のコンタクトホールが設けられた第1絶縁層を形成する工程と、前記第1のコンタクトホールを介して前記第1導電膜に電気的に接続され、前記第1絶縁層上に設けられており、前記2つの画素のうち一方の画素の開口領域に延びる延在部を有する透明な第2導電膜を形成する工程と、前記第2導電膜上に積層され、第2のコンタクトホールが設けられた第2絶縁層を形成する工程と、前記第2のコンタクトホールの内部に、透明導電性材料を充填する工程と、前記第2のコンタクトホールを介して前記延在部に電気的に接続され、少なくとも前記一方の画素の開口領域に画素電極を形成する工程と、を含み前記透明導電性材料は、前記画素電極よりも比抵抗が低いことを特徴とする。

【0014】

本適用例の電気光学装置の製造方法によれば、上述した本適用例の電気光学装置を好適に製造することができる。

【0015】

(適用例3)

本適用例の電気光学装置の製造方法は、上述する課題を解決するために、透明導電性材料を充填する工程には、前記透明導電性材料を塗布する工程と、前記塗布した透明導電性材料を焼結する焼結工程と、を含むことを特徴とする。

【0016】

本適用例によれば、上述した本適用例の電気光学装置のうち、第2のコンタクトホールの内部に、好適に透明導電性材料を塗布し焼結することができる。換言すれば、第2のコンタクトホールの内部に、好適に透明導電性材料を充填することができる。

【0017】

(適用例4)

本適用例の電気光学装置の製造方法は、上述する課題を解決するために、塗布工程には、化学気相堆積法を用いることを特徴とする。

【0018】

本適用例によれば、上述した本適用例の電気光学装置のうち、第2のコンタクトホールの内部に、好適に透明導電性材料を充填することができる。

【0019】

(適用例5)

本適用例の電気光学装置の製造方法は、透明導電性材料を充填する工程の後に、前記第2のコンタクトホールが形成された部分を含む前記第2絶縁層の表面に対して、平坦化処理を施す工程を含むことを特徴とする。

【0020】

本適用例によれば、上述した本適用例の電気光学装置のうち、第2のコンタクトホールが形成された第2絶縁層の表面に、透明導電性材料の突出部分あるいは凸部があった場合でも、当該突出部分を平坦化することができる。

このように、第2絶縁層の表面を平坦化処理することにより、その後に形成される画素電極、配向膜などの平坦度を高めることができるため、表示ムラや、コントラスト低下などを低減することができる。

【0021】

(適用例6)

本適用例の電気光学装置の製造方法の一態様では、平坦化処理を施す工程には化学機械研磨法を含むことを特徴とする。

【0022】

本適用例によれば、効率的に平坦化処理を行なうことができる。

【0023】

(適用例7)

本適用例の電子機器は、上述の電気光学装置を備えたことを特徴とする。

【0024】

本適用例の電子機器によれば、上述した本発明に係る電気光学装置を具備してなるので、画像表示の高コントラスト化、高駆動化が達成され、より高画質の、投射型の液晶表示装置、テレビ、携帯電話、電子手帳、ワードプロセッサー、ビューファインダー型又はモニター直視型ビデオテープレコーダー、ワークステーション、テレビ電話、POS端末、タッチパネルなどの各種電子機器を実現することができる。また、本発明の電子機器として、例えば電子ペーパーなどの電気泳動装置、電界放出装置(Field Emission Display及びconduction Electro−Emitter Display)、これら電気泳動装置、電界放出装置を用いた表示装置を実現することも可能である。

【図面の簡単な説明】

【0025】

【図1】実施形態1に係る電気光学装置の平面図。

【図2】図1のH−H’側断面図。

【図3】実施形態1に係る電気光学装置の等価回路図。

【図4】実施形態1に係る電気光学装置の画素部の平面図(下層側)。

【図5】実施形態1に係る電気光学装置の画素部の平面図(中層側)。

【図6】実施形態1に係る電気光学装置の画素部の平面図(上層側)。

【図7】図4ないし図6のA−A’側断面図。

【図8】図4ないし図6のB−B’側断面図。

【図9】実施形態1に係る電気光学装置の製造方法におけるフローチャート図。

【図10】実施形態1に係る電気光学装置の製造方法の各工程断面図。

【図11】実施形態1に係る電気光学装置の製造方法の各工程断面図。

【図12】実施形態2に係る電気光学装置の画素部の平面図(下層側)。

【図13】実施形態2に係る電気光学装置の画素部の平面図(上層側)。

【図14】図12ないし図13のC−C’側断面図。

【図15】電子機器としてのプロジェクターの平面図。

【図16】従来の電気光学装置における画素部の側断面図。

【発明を実施するための形態】

【0026】

以下、本発明の実施形態について、図面を参照して説明する。なお、以下の各図においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材ごとに縮尺を異ならしめてある。

【0027】

(実施形態1)

「電気光学装置の全体構成」

図1及び図2を参照しながら、本実施形態に係る電気光学装置を説明する。図1は素子基板10を、その上に形成された各構成要素と共に対向基板20の方向から見た電気光学装置の平面図である。図2は図1のH−H’断面における側断面図である。本実施形態では、電気光学装置の一例として、駆動回路内蔵型のTFTアクティブマトリックス駆動方式の液晶表示装置を例にあげる。

【0028】

図1及び図2において、液晶表示装置1では素子基板10と対向基板20とが、向かい合う形で配置されている。素子基板10と対向基板20との間には液晶層50が封入されており、素子基板10と対向基板20とは、複数の画素部が設けられる画像表示領域10aの周囲に位置されるシール領域に設けられた、シール材52によって相互に接着されている。

【0029】

素子基板10は、好適例として石英基板を用いている。なお、石英基板に限定するものではなく、可視光領域において透明性を有する基板であれば良い。

対向基板20は、好適例として無アルカリガラスを用いている。なお、この構成に限定するものではなく、素子基板10、および対向基板20ともに、可視光領域において透明性を有する基板であれば良い。

液晶層50は、好適例として、一種、または数種類のネマティック液晶を混合した誘電率異方性が負の液晶を用いている。当該液晶は、電圧がかかっていない状態で液晶分子が垂直に配列し、電圧が印加されると液晶分子が寝た状態になるネガ液晶であれば一種類からなるものでも良いし、複数種の液晶を混合したものでも良い。なお、ネガ液晶を用いることに限定するものではなく、ポジ液晶を用いても良い。言い換えれば、ノーマリーブラックモードに限定するものではなく、ノーマリーホワイトモードであっても良い。

また、液晶モードも、VA(Vertical Aligned)モードに限定するものではなく、TN(Twisted Nematic)モードや、IPS(In−Plane Switching)モードなどの各種動作モードを用いても良い。

【0030】

シール材52は、両基板を貼り合わせるため、例えば紫外線硬化樹脂や熱硬化性樹脂等の接着剤からなり、素子基板10上に塗布された後、紫外線照射もしくは加熱等により硬化させられたものである。なお、シール材52中には、素子基板10と対向基板20との間隔(基板間ギャップ)を所定値とするためのグラスファイバーや、ガラスビーズ等のギャップ材が散布されている。

【0031】

対向基板20には、シール材52が配置されたシール領域の内側に沿って、画像表示領域10aの見切りを規定する遮光性の額縁遮光膜53が設けられている。ただし、このような額縁遮光膜53の一部又は全部は、素子基板10側に内蔵される遮光膜として設けられてもよい。

【0032】

ここで、画像表示領域10aの周辺には、周辺領域が存在する。具体的には、額縁遮光膜53より外側を周辺領域として規定する。また、対向基板20に対して素子基板10が張り出している領域を張出し領域と規定する。

【0033】

周辺領域のうち、シール材52が配置されたシール領域の外側に位置する領域であって、素子基板10の張出し領域にある一辺に、データ線駆動回路101及び外部回路接続端子102が設けられている。走査線駆動回路104は、この一辺の両端部から延びる2辺に沿い、且つ、額縁遮光膜53に重ねて配置されている。また、周辺領域のうちシール領域より内側に位置する領域には、画像表示領域10aの一辺に沿ってかつ額縁遮光膜53に重なるようにしてサンプリング回路7が配置されている。

【0034】

さらに、画像表示領域10aの両側に設けられた2つの走査線駆動回路104を電気的に接続するため、素子基板10の残る1辺に沿って、かつ額縁遮光膜53に重なるようにして複数の配線(図示せず)が設けられている。

【0035】

また、シール材52の外周における4つのコーナーには、素子基板10と対向基板20との間の上下導通をとるための上下導通部106が配置されている。上下導通部106には、例えば、異方性導電材料107が用いられており、当該異方性導電材料107を挟むように配置された各基板の配線間の電気的な接続が取られている。

さらに、素子基板10には、外部回路接続端子102と、データ線駆動回路101、走査線駆動回路104、上下導通部106などとを電気的に接続するための引き回し配線90が形成されている。

【0036】

ここで、図1にて横長の長方形をなした画像表示領域10aには、画像を表示する複数の画素がマトリックス状に形成されている。

なお、図1を含む各図においては、横長の長方形をなした画像表示領域10aにおける横方向をX軸方向とし、当該方向と交差する縦方向をY軸として定義している。また、液晶表示装置1の厚さ方向をZ軸方向としている。また、素子基板10から対向基板20へ向かう方向(+Z)を上層とし、その反対の方向(−Z)を下層と定義している。

【0037】

図2の素子基板10において、マトリックス状に形成された画素は、画素電極9aを最上層として、画素のスイッチング素子用のトランジスター(Thin Firm Transistor)や、走査線、データ線、層間絶縁膜などを積層した積層構造となっている。

また、画素電極9a上には、各画素電極9aを覆うように、ラビング処理等の所定の配向処理がされた配向膜が形成されている。他方、対向基板20の上(素子基板10と向かい合う面側)には、ITO等の透明導電性材料からなる対向電極21が複数の画素電極9aと対向して、略全面(共通電極)に形成されている。また対向電極21上にも配向膜が形成されている。なお、入射光がスイッチング素子30やその周辺へ侵入することを、確実に防止するために、格子状又はストライプ状の遮光膜23を設けるようにしてもよい。

【0038】

そして、液晶層50には、これら一対の配向膜間で、所定の配向状態を取ることになる。

【0039】

なお、素子基板10には、データ線駆動回路101、走査線駆動回路104の他に、図示は省略するが、製造と出荷時の当該液晶表示装置の品質、欠陥等を検査するための検査回路、検査用パターンなどが更に形成されていてもよい。

【0040】

「画素回路」

次に、図3を参照しながら液晶表示装置1の画素部の電気的な接続構成を詳細に説明する。図3は、液晶表示装置1の画像表示領域10aを構成するマトリックス状に形成された複数の画素における、各種素子、配線等の走査回路である。

【0041】

図3に示すように、液晶表示装置1の画像表示領域10aには、複数の走査線11aが、X軸方向に沿って延在している。複数の走査線11aと交差して、複数のデータ線6aがY軸方向に沿って延在している。

また、複数の走査線11aの延在方向に沿って複数の容量線350が配線されている。なお、容量線350は、データ線6aの延在方向(Y軸方向)に沿って配線されてもよい。画像表示領域10aを形成する複数の画素の各々は、走査線11aとデータ線6aとが交差する交差点ごとに形成されている。

【0042】

各画素は、画素電極9aに加えて、スイッチング素子30、および蓄積容量70を備えている。なお、好適例として、スイッチング素子30は、電界効果型のN型トランジスターを用いている。

各スイッチング素子30において、ゲート電極3aは対応する走査線11aに接続され、ソース端子は対応するデータ線6aに接続され、ドレイン端子は画素電極9a、および蓄積容量70の一端に接続されている。また、蓄積容量70の他の一端は所定の電位に設定された容量線350に接続されている。

【0043】

スイッチング素子30は、走査線11aに供給される走査信号G1、G2、…Gmによって選択されたタイミングで、データ線6aのデータ信号S1、S2、…Snを対応する画素電極9aに書き込む。つまり、走査線駆動回路104から各走査線11aに供給される走査信号G1、G2、…Gmのタイミングに従って、各画素が線順次に選択される。

また、データ線駆動回路101およびサンプリング回路7からは、走査信号による各画素の選択と同期して、データ信号S1、S2、…、Snが各データ線6aに供給される。詳しくは、サンプリング回路7は、連続する6本のデータ線に対して、データ線駆動回路101から供給されるサンプリング信号のタイミングに従って、6つに相展開された画像信号を同時にサンプリングし、各データ線に供給する。なお、ここでは、好適例として6相の相展開駆動を行う場合について説明したが、これに限定するものではなく、定められたフレームレートで違和感なく、画像を表示可能な駆動方法であれば良い。

【0044】

このようにして、画素電極9aを介して液晶層50に書き込まれた所定レベルのデータ信号S1、S2、…、Snは、対向基板20に形成された対向電極21との間で一定期間保持される。

また、書き込まれたデータ信号の電位を保持するために、画素電極9aと対向電極21との間に形成される液晶容量に対して電気的に並列に蓄積容量70が形成されている。

また、対向基板20の対向電極21(図2)は、対向電極生成回路(図示せず)に接続されており、周期的に極性が反転する対向電圧が供給され、反転駆動が行われる。反転駆動としては、ライン反転駆動や、フレーム反転駆動、ドット反転駆動などを用いることができる。

【0045】

「画素部の具体的な構成」

次に、図4ないし図8を参照しながら画素部の具体的な構成を説明する。図4ないし図6は、データ線6a、走査線11a、画素電極9a等が形成された素子基板10の互いに隣り合う複数の画素の平面図である。図7は、図4ないし図6のA−A’断面における側断面図であり、図8は、図4ないし図6のB−B’断面における側断面図である。

【0046】

図4ないし図8では、上述した画素部の各回路要素が、パターン化され、積層された導電膜として素子基板10上に形成されている。

図7では、各回路要素は、下から順に、走査線11aを含む第1層、スイッチング素子30等を含む第2層、データ線6a等を含む第3層、蓄積容量70等を含む第4層、第2導電膜としての中継層400等を含む第5層、画素電極9a等を含む第6層からなる。

【0047】

第1層−第2層間には下地絶縁膜12、第2層−第3層間には第1層間絶縁膜41、第3層−第4層間には第2層間絶縁膜42、第4層−第5層間には第1絶縁層としての第3層間絶縁膜43、第5層及び第6層間には第2絶縁層としての第4層間絶縁膜44が夫々設けられ、前述の各要素間が短絡することを防止している。このうち、第1層から第3層が下層部分として図4に示され、第4層が中層部分として図5に示され、第5層及び第6層が上層部分として図6に示されており、図4ないし図6では、説明の便宜上、画素電極9aより上側に位置する部分の図示を省略している。

尚、以下説明する各種配線、各種素子、および絶縁膜などは、蒸着法、スパッタリング法、CVD(Chemical Vapor Deposition)法、フォトリソ法、エッチング法などを単独、または組み合わせることによって、形成することができる。

【0048】

「第1層の構成−走査線等−」

図4及び図7において、第1層は、走査線11aで構成されている。走査線11aは、図4のX方向に沿って延びる本線部と、データ線6aが延在する図4のY方向に延びる突出部とからなる形状にパターニングされている。走査線11aは、例えば導電性ポリシリコンからなり、その他にもチタン(Ti)、クロム(Cr)、タングステン(W)、タンタル(Ta)、モリブデン(Mo)等の高融点金属のうちの少なくとも一つを含む金属単体、合金、金属シリサイド、ポリシリサイド又はこれらの積層体等により形成することができる。本実施形態では特に、走査線11aは、スイッチング素子30の下層側に、半導体層1aに対向する領域を含むように配置された導電膜である。このため、素子基板10における裏面反射や、液晶表示装置をライトバルブとして用いて複板式のプロジェクターを構築した場合に、他の液晶表示装置から発せられプリズム等の合成光学系を突き抜けてくる光などの、戻り光についても、走査線11aにより半導体層1aを下層側から遮光できる。

【0049】

「第2層の構成−スイッチング素子等−」

第2層は、スイッチング素子30で構成されている。スイッチング素子30は、例えばLDD(Lightly Doped Drain)構造とされ、ゲート電極3a、半導体層1a、ゲート電極3aと半導体層1aを絶縁するゲート絶縁膜を含んだ絶縁膜2を備えている。ゲート電極3aは、例えば導電性ポリシリコンで形成される。半導体層1aは、例えばポリシリコンからなり、チャネル領域1a’、低濃度ソース領域1b及び低濃度ドレイン領域1c、並びに高濃度ソース領域1d及び高濃度ドレイン領域1eからなる。

【0050】

尚、スイッチング素子30は、LDD構造を有することが好ましいが、低濃度ソース領域1b、低濃度ドレイン領域1cに不純物打ち込みを行わないオフセット構造であってもよいし、ゲート電極3aをマスクとして不純物を高濃度に打ち込んで高濃度ソース領域1d及び高濃度ドレイン領域1eを形成する自己整合型であってもよい。

【0051】

スイッチング素子30のゲート電極3aは、その一部分3bにおいて、下地絶縁膜12に形成されたコンタクトホール12cvを介して走査線11aに電気的に接続されている。下地絶縁膜12は、例えばシリコン酸化膜等からなり、第1層と第2層の層間絶縁機能の他、素子基板10の全面に形成されることで、基板表面の研磨による荒れや汚れ等が惹き起こすスイッチング素子30の素子特性の変化を防止する機能を有している。

【0052】

ちなみに、本実施形態に係るスイッチング素子30は、トップゲート型であるが、ボトムゲート型であってもかまわない。また、前述のトランジスターでも構わないし、薄膜ダイオード、バルクトランジスター等の2端子型又は3端子型のスイッチング素子からなるものでもよい。

【0053】

「第3層の構成−データ線等−」

第3層は、データ線6a及び中継層600で構成されている。

【0054】

データ線6aは、下から順にアルミニウム、窒化チタン、窒化シリコンの3層膜として形成されている。データ線6aは、スイッチング素子30のチャネル領域1a’を部分的に覆うように形成されている。このため、チャネル領域1a’に近接配置可能なデータ線6aによって、上層側からの入射光に対して、スイッチング素子30のチャネル領域1a’を遮光できる。また、データ線6aは、第1層間絶縁膜41を貫通するコンタクトホール81を介して、スイッチング素子30の高濃度ソース領域1dと電気的に接続されている。

【0055】

中継層600は、データ線6aと同一膜として形成されている。中継層600及びデータ線6aは、図4に示したように、夫々が分断されるように形成されている。中継層600は、第1層間絶縁膜41を貫通するコンタクトホール83を介して、スイッチング素子30の高濃度ドレイン領域1eと電気的に接続されている。

【0056】

第1層間絶縁膜41は、例えばNSG(ノンシリケートガラス)によって形成されている。その他、第1層間絶縁膜41には、PSG(リンシリケートガラス)、BSG(ボロンシリケートガラス)、BPSG(ボロンリンシリケートガラス)等のシリケートガラス、窒化シリコンや酸化シリコン等を用いることができる。

【0057】

「第4層の構成−蓄積容量等−」

図5及び図7において、第4層は、蓄積容量70で構成されている。ここで、蓄積容量70を液晶容量に並列に電気的に接続することで、画素電極9aの電圧を、実際に画像信号が印加されている時間よりも、例えば3桁も長い時間だけ保持することが可能となり、液晶層50の保持特性が改善されるため、高コントラスト比を有する液晶表示装置を実現することができる。

【0058】

蓄積容量70は、第1導電膜としての上部容量電極300と、下部容量電極71とが誘電体膜75を介して対向配置された構成となっている。上部容量電極300は、第2層間絶縁膜42を貫通するコンタクトホール84を介して、中継層600と電気的に接続されている。

【0059】

上部容量電極300は、液晶表示装置1の動作時に、スイッチング素子30を介してデータ線6aから画像信号が供給される。走査線11aを介して供給された走査信号に応じて、オンオフが切り換えられたスイッチング素子30は、データ線6aから供給された画像信号を、スイッチング素子30のドレイン側に電気的に接続された上部容量電極300に供給する。

【0060】

上部容量電極300又は下部容量電極71は、例えば、Al、Ti、Cr、W、Ta、Mo等の金属のうちの少なくとも一つを含む金属単体、合金、金属シリサイド、ポリシリサイド、ナイトライドこれらを積層したものからなる。このため、データ線6a上に第2層間絶縁膜42を介して近接配置可能な蓄積容量70によって、上層側からの入射光に対してスイッチング素子30のチャネル領域1a’を、より一層確実に遮光できる。

【0061】

誘電体膜75は、素子基板10上において、画素毎の開口領域の間隙に位置する非開口領域に形成されている、即ち、開口領域に殆ど形成されていない。よって、誘電体膜75が、仮に不透明な膜であっても、開口領域における透過率を低下させないで済む。従って、誘電体膜75は、透過率を考慮せず、誘電率が高いシリコン窒化膜等から形成されている。

このため、誘電体膜75は、水分や湿気を防ぐための膜としても機能させることが可能となり、耐水性、耐湿性を高めることも可能となる。尚、誘電体膜75としては、シリコン窒化膜の他、例えば、酸化ハフニュウム(HfO2)、アルミナ(Al2O3)、酸化タンタル(Ta2O5)等の単層膜又は多層膜を用いてもよい。

【0062】

第2層間絶縁膜42は、例えばNSG(ノンシリケートガラス)によって形成されている。その他、第2層間絶縁膜42には、PSG、BSG、BPSG等のシリケートガラス、窒化シリコンや酸化シリコン等の透明性を有する絶縁材料を用いて形成することができる。

第2層間絶縁膜42の表面は、化学機械研磨法(Chemical Mechanical Polishing:CMP)やスピンコート処理等の平坦化処理がなされていている。よって、下層側のこれらの要素に起因した凹凸が除去され、第2層間絶縁膜42の表面は平坦化されている。このため、素子基板10と対向基板20との間に挟みこまれた液晶層50の配向状態に乱れを生じさせる可能性を低減することができ、より高品位な表示が可能となる。尚、このような平坦化処理は、他の層間絶縁膜の表面に対して行ってもよい。

【0063】

「第5層の構成−中継層等−」

第4層の全面には、第1のコンタクトホールとしてのコンタクトホール85が設けられた(開口した)、第3層間絶縁膜43が形成されている。コンタクトホール85の底部には、上部容量電極300が露出している。中継層400は、コンタクトホール85内から第3層間絶縁膜43の表面に沿って延在されている。

ここで、中継層400は、ITO等の透明導電性材料から構成されている。

中継層400は、後に図8を参照しながら説明するように、画素における第4層間絶縁膜44の表面に延在される画素電極9a(9aa)に電気的に接続されており、画像信号を画素電極9a(9aa)に供給する。

【0064】

第3層間絶縁膜43は、例えばNSGによって形成されている。その他、第3層間絶縁膜43には、PSG、BSG、BPSG等のシリケートガラス、窒化シリコンや酸化シリコン等の透明性を有する絶縁材料を用いることができる。第3層間絶縁膜43の表面は、第2層間絶縁膜42と同様にCMP等の平坦化処理がなされていてもよい。

【0065】

「第6層の構成−画素電極等−」

図6及び図7において、第5層の全面には第4層間絶縁膜44が形成され、更にその上に、第6層として画素電極9aが形成されている。第4層間絶縁膜44は、例えばNSGによって形成されている。その他、第4層間絶縁膜44には、PSG、BSG、BPSG等のシリケートガラス、窒化シリコンや酸化シリコン等の透明性を有する絶縁材料を用いることができる。第4層間絶縁膜44の表面は、第3層間絶縁膜43と同様にCMP等の平坦化処理がなされていてもよい。

【0066】

画素電極9a(図6中、破線9a’で輪郭が示されている)は、縦横に区画配列された画素の各々に配置され、その境界にデータ線6a及び走査線11aが格子状に配列するように形成されている。画素電極9aは、例えばITO等の透明導電性材料からなる。画素電極9aの上層には、ラビング処理等の所定の配向処理が施された配向膜16が設けられている。

ここで、本実施形態では、画素電極9aに重なり、光を透過(光変調)する領域のことを「開口領域」、データ線6a及び走査線11aなどが形成された格子状の遮光領域のことを「非開口領域」と定義している。開口領域は、実際には画素電極9aよりも若干小さくなるが、略画素電極9aのサイズと略同等と見なすことができる。非開口領域は、いわゆるブラックマトリックス(BM)である。

【0067】

次に、図6及び図8を参照しながら画素部における具体的な構成をより詳細に説明する。

【0068】

図6及び図8において、中継層400は、コンタクトホール85を介して上部容量電極300に電気的に接続されている。

ここで、素子基板10上において、蓄積容量70及び中継層600が形成された領域は、画素における光を透過させない非開口領域となる。中継層400は、非開口領域の両側に位置する開口領域の一方に延びる延在部400aを有している。延在部400aは、画素電極9aaの一領域でもあり、透明導電性材料からなる。したがって、開口領域に延びる延在部400aが、当該開口領域を透過する光を遮ることはなく、延在部400aによって開口領域が狭められることはない。

【0069】

第4層間絶縁膜44には、第2のコンタクトホールとしてのコンタクトホール86が、異方性エッチング法等を用いて第4層間絶縁膜44に形成されている。コンタクトホール86は、第4層間絶縁膜44のうち、XY平面上、延在部400aに重なる部分を除去することによって形成されている。

【0070】

コンタクトホール86の内部には、画素電極よりも比抵抗の低い透明導電性材料が充填された充填部500が形成されている。

ここで、画素電極よりも比抵抗の低い透明導電性材料とは、例えば、In(インジウム)などの金属の含有率が高い材料である。そして、充填部500によって、第2導電膜400と、後に形成される画素電極9a(9aa)との電気的接続を取っている。

【0071】

なお、図8において、充填部500はコンタクトホール86の内部を完全に満たしており、かつ、コンタクトホール86のZ軸(+)側の開口面(上面)と略同一面となっている。換言すれば、第4層間絶縁膜44の表面と略同一面となっている。

なお、充填部500は、コンタクトホール86の開口面に対して若干の凹部や突出部分があったとしても、従来のコンタクトホールにおける凹部よりも、平坦化されていれば、画質を向上させることができる。

【0072】

画素電極9a(9aa)は、例えばITO等の透明導電性材料をスパッタリング法等の既存の成膜方法を用いて、充填部500および第4層間絶縁膜44上に形成されている。なお、充填部500の存在により、画素電極9a(9aa)は、従来例(図16)のようにコンタクトホール86のすり鉢状の表面形状をなぞらえることなく、第4層間絶縁膜44に対して平坦性の高い膜となっている。

【0073】

配向膜16は、画素電極9a上に、例えばポリイミドなどの有機膜を用いて形成されている。配向膜16もまた、コンタクトホール86の内部に形成された充填部500の効果により、画素電極9a上において略平坦に形成することが可能となる。換言すれば、平坦度が高い下地に沿って、配向膜16が形成されている。

【0074】

対向基板20には、液晶層50側の略全面に対向電極21が設けられており、更にその上層(Z軸(−)側)に配向膜22が形成されている。

対向電極21は、画素電極9aと同様、例えばITO膜等の透明導電性材料からなる。尚、対向基板20と対向電極21の間には、スイッチング素子30における光リーク電流の発生等を防止するため、少なくともスイッチング素子30と正対する領域を覆うように遮光膜23が設けられている。

【0075】

このように構成された素子基板10と対向基板20の間には、液晶層50が設けられている。液晶層50は、素子基板10及び対向基板20の周縁部をシール材により封止して形成した空間に液晶を封入して形成される。液晶層50は、画素電極9aと対向電極21との間に電界が印加されていない状態において、ラビング処理等の配向処理が施された配向膜16及び配向膜22によって、所定の配向状態をとるようになっている。

【0076】

上述した画素部の構成は、図4ないし図6に示すように、各画素部に共通である。画像表示領域10a(図1参照)には、かかる画素部が周期的に形成されていることになる。他方、このような液晶表示装置1では、画像表示領域10aの周囲に位置する周辺領域に、図1及び図2を参照して説明したように、走査線駆動回路104及びデータ線駆動回路101等の駆動回路が形成され、画像表示が行われる。

【0077】

「電気光学装置の製造方法」

次に、図9ないし図11を参照しながら、本実施形態に係る電気光学装置の製造方法を説明する。図9は、本実施形態に係る電気光学装置の製造方法を示すフローチャートであり、図10および図11は、当該電気光学装置の製造工程のうち、コンタクトホール形成工程に関連のある部分を抽出して示した、各製造工程態様における断面図である。

【0078】

まず、ステップS1では、石英等の素子基板10を用意するとともに、素子基板10上に、走査線11a、下地絶縁膜12等を形成する。

走査線11aは、例えば導電性ポリシリコンや、その他Ti、Cr、W、Ta、Mo等の高融点金属のうち少なくとも1つを含む金属単体、合金、金属シリサイド、ポリシリサイド又はこれらの積層体等を用いてスパッタリング法により形成した後、フォトリソ及びエッチングによって格子状に形成される。

また、下地絶縁膜12は、例えば、常圧又は減圧CVD法等によりTEOS(テトラ・エチル・オルソ・シリケート)ガス、TEB(テトラ・エチル・ボートレート)ガス、TMOP(テトラ・メチル・オキシ・フォスレート)ガス等を用いて、例えばNSG、PSG、BSG、BPSG等のシリケートガラス膜、窒化シリコン膜や酸化シリコン膜等からなるように形成する。

【0079】

ステップS2では、下地絶縁膜12上に、半導体層1aを含むスイッチング素子30、第1層間絶縁膜41、データ線6a、第2層間絶縁膜42、及び蓄積容量70を順次、積層構造となるように形成する。

このうちスイッチング素子30は、半導体層1aに対する不純物イオンの導入工程の他、絶縁膜2の形成工程、及びゲート電極3aの形成工程を含むが、これらについては公知の方法を利用すればよく、その詳細な説明は省略する。

【0080】

また、第1層間絶縁膜41及び第2層間絶縁膜42は、下地絶縁膜12と同様な方法により形成される。

さらに、蓄積容量70は、上部容量電極300及び下部容量電極71、並びに誘電体膜75の各要素の形成工程を含む。2つの電極については、例えばAl、Ti、Cr、W、Ta、Mo等の金属のうちの少なくとも一つを含む金属単体、合金、金属シリサイド、ポリシリサイド、ナイトライドこれらを積層したもの等の適当な導電性材料からなり。スパッタリング法、フォトリソ法及びエッチング法等を用いて形成される。

誘電体膜75は、シリコン窒化膜の他、例えば、酸化ハフニュウム(HfO2)、アルミナ(Al2O3)、酸化タンタル(Ta2O5)等の適当な絶縁性材料の単層膜又は多層膜を用いて、形成することができる。

なお、図10(a)には、蓄積容量70までが形成された状態が示されている。

【0081】

ステップS3では、図10(b)に示すように、蓄積容量70上に、第3層間絶縁膜43を形成する。第3層間絶縁膜43は、下地絶縁膜12と同様な方法により形成される。

ステップS4では、図10(c)に示すように、第3層間絶縁膜43に対して、反応性イオンエッチング、反応性イオンビームエッチング等のドライエッチングを施すことにより、コンタクトホール85を形成する。

【0082】

ステップS5では、図10(d)に示すように、コンタクトホール85の内部および周縁部に対して、中継層400を形成する。中継層400は、ITO等の透明導電性材料からなり、スパッタリング法等の既存の成膜方法を用いて形成されている。

ステップS6では、図10(e)に示すように、中継層400の上に、第4層間絶縁膜44を形成する。第4層間絶縁膜44は、下地絶縁膜12と同様な方法により形成される。

ステップS7では、図10(f)に示すように、第4層間絶縁膜44に対して、コンタクトホール86を形成する。コンタクトホール86は、コンタクトホール85と同様の方法で形成される。

【0083】

ステップS8では、図11(g)に示すように、コンタクトホール86に対して、画素電極よりも比抵抗が低い透明導電性材料を塗布する。

塗布にあたっては、まず、画素電極よりも比抵抗が低い透明導電性材料を含有したインクの前駆体から、塗布に最適な粘性等を満たしたインクを準備する。好適例におけるインクの前駆体としては、トリメチル、トリエチル、テトラメチル、テトラエチルのいずれかの有機In(インジウム)と有機Sn(スズ)とが低沸点低分子量の有機溶媒、特に炭化水素系有機溶剤、例えば、DMF、トルエン、ジブチルエーテル、ジフライム、メチルエチルケトン、メチルジクロヘキサノン、セロソルブアセテートなどに混合されて成るものである。さらに、In、Snの粒子径を調整したITOナノインクでも良い。

続いて、該インクをニードル方式、インクジェット方式など公知の吐出方法を用いて、コンタクトホール86へ塗布(充填)する。ここで、塗布するにあたって、該インクは第4層間絶縁膜44の表面よりも突出した形となるまで形成してもよい。

なお、本工程は大気圧中で行なっても良いが、減圧雰囲気で行なうことがより好ましい。減圧雰囲気であれば、透明導電性材料をコンタクトホール86に充填する際に、充填部500の内部に気泡を内在させないよう、脱泡しながら行うことが可能であるからである。また、塗布時間、塗布圧などは、使用する該インクの性質により適宜調整する。

また、ここで述べた塗布とは、液状のインクをコンタクトホール86に対して、滴下することに限定するものではなく、コンタクトホール86内に、透明導電性材料を充填可能な方法であれば良い。例えば、ペースト状のインクをスクリーン印刷しても良いし、粘度の低いインクをスピンコート法で第4層間絶縁膜44の全面に塗布する方法であっても良い。

【0084】

ステップS9では、図11(h)に示すように、塗布された透明導電性材料を焼結する。

焼結するにあたって、例えばN2+O2などの酸素雰囲気下で、300〜500℃、30分〜6時間の熱処理を施すと良い。本熱処理により、有機溶媒の揮発と共に有機In、有機Snの酸化が行われ、所期の透明性と、導電性とを有する充填部500が形成される。

なお、この熱処理に変えて、紫外線照射によって、炭化系有機溶剤である有機In、有機Snを解離させると同時に、酸素雰囲気下でIn、Snを酸化させて透明導電性材料を焼結させる方法を用いても良い。

【0085】

ステップS10では、図11(i)に示すように、コンタクトホール86の充填部500を含む第4層間絶縁膜44の表面に対して、平坦化処理を施す。好適例としては、CMP(Chemical Mechanical Polishing)処理を用いる。なお、その他、種々の平坦化技術を利用しても良い。

CMP処理とは、被処理基板と研磨布(パッド)の両者を回転等させながら、それぞれの表面同士を当接させるとともに、該当接部位にシリカ粒等を含んだ研磨液(スラリー)を供給することによって、被処理基板表面を、機械的作用と化学作用の兼ね合いにより研磨し、当該表面を平坦化する技術である。

本実施形態においては、コンタクトホール86に対する充填部500の形成が完了している素子基板10を、上述の「被処理基板」に当てはめて考えればよい。

なお、研磨処理の終了時点の調整は、適当な時間の経過によるか、あるいは適当なストッパー層を素子基板10上の所定位置に形成しておくこと等によって行う。この研磨処理の終了の時点において、コンタクトホール86が完成したとみることができる。

【0086】

ステップS11では、図11(j)に示すように、第4層間絶縁膜44の表面上に対して、画素電極9a及び配向膜16(図示せず)を形成する。

具体的には、第4層間絶縁膜44の表面上に、透明導電性材料を用いてスパッタリング法、フォトリソ法及びエッチング法を実施することで画素電極9aが形成される。そして画素電極9a上に、透明なポリイミド材料等からなる配向膜16が形成される。

ここで、スパッタリング法で形成される画素電極9aは、その原理上、第4層間絶縁膜44の表面形状に沿った形状となる。つまり、画素電極9aは、平坦化処理された第4層間絶縁膜44の平坦度を略踏襲したものとなる。

【0087】

以上述べたように、本実施形態に係る液晶表示装置1、およびその製造方法によれば、以下の効果を得ることができる。

液晶表示装置1によれば、開口領域に形成されたコンタクトホール86の内部には、画素電極よりも比抵抗が低い透明導電性材料が充填された充填部500が形成されている。

この充填は、好適には塗布法を用いて行なわれるため、当該コンタクトホール内をしっかりと充填した上で、その上部を平坦化することができる。また、所期の透明性も確保することができる。

よって、コンタクトホール86の上部における平坦性の確保が困難であった従来の電気光学装置よりも、優れた画像品質を得ることができる。

従って、所期の画像品質が得られる液晶表示装置1を提供することができる。

【0088】

さらに、充填される透明導電性材料は、画素電極よりも比抵抗が低いため、コンタクトホール86が画素電極部分と同じ膜質で形成されていた従来の電気光学装置よりも、当該コンタクトホールの導電性を高めることができる。つまり、電気配線として必要な導電性を確保することができる。よって、高速駆動にも対応することができる。

このように、液晶表示装置1は、コンタクトホール86の透明性と平坦性とを両立することができるばかりでなく、電気配線として必要な導電性をも確保することができるという、格段の効果を奏するものである。

【0089】

(実施形態2)

図12ないし図14を参照しながら、実施形態2に係る液晶表示装置を説明する。

図12および図13は、本実施形態に係る素子基板10の平面図である。図14は、図12及び図13のC−C’断面における側断面図を示すものである。図12では、中継層91及び92より下層側(−Z)の各層を示しており、図13では、中継層91及び92より上層側(+Z)の各層を示している。

【0090】

なお、本実施形態の液晶表示装置は、実施形態1の液晶表示装置1における積層(平面)構造とは異なる積層構造を有する液晶表示装置である。詳しくは、スイッチング素子30を含む第2層より上層の構造が液晶表示装置1と異なる。それ以外の走査線11aを含む第1層から、スイッチング素子30を含む第2層までの構造は、液晶表示装置1と同様である。

よって、実施形態1と同一の構成部位については、同一の番号を附し、重複する説明は省略する。

以下、図12ないし図14を用いて、実施形態1との相違点を中心に説明する。

【0091】

まず、第1の相違点として、スイッチング素子30を、データ線6aおよび中継層92の双方で覆うように配置していることにある。本構成により、スイッチング素子30の遮光性が高まるために、スイッチング素子30の誤動作を防止でき、信頼性の高い液晶表示装置を提供できる。

第2の相違点として、蓄積容量170を開口領域に設けていることにある。本構成により、蓄積容量170の容量値を大きくし、且つ開口領域のサイズを広げることができる。

第3の相違点として、蓄積容量170を画素間で分離するための容量分離膜80が形成されていることにある。本構成により、好適な容量値を選択することができる。

順を追って説明する。

【0092】

図12ないし図14において、データ線6aは、層間絶縁膜46に形成されたコンタクトホール34、層間絶縁膜45上に形成された中継層91、コンタクトホール31を介して、スイッチング素子30の高濃度ソース領域1dと電気的に接続されている。

一方、層間絶縁膜45上にある中継層92は、コンタクトホール32を介して、スイッチング素子30の高濃度ドレイン領域1eと電気的に接続されている。

【0093】

そして、データ線6aは、スイッチング素子30に対して重なるように配置されている。一方、中継層92は、スイッチング素子30の少なくともチャネル領域1a’の一部から、高濃度ドレイン領域1eを覆うように配置されている。つまり、データ線6aと中継層92とが、スイッチング素子30を覆うように配置されている。

【0094】

続いて、第2の相違点について詳しく説明する。

図13および図14によれば、蓄積容量170は、上部容量電極として機能する画素電極9a、下部容量電極171、および誘電体膜175で構成されている。

画素電極9aは、スイッチング素子30の高濃度ドレイン領域1eと、中継層92、中継層93、及び層間絶縁膜47上にある中継層400、本発明に係る画素電極よりも比抵抗の低い透明導電性材料を充填した充填部500を介して電気的に接続されている。

下部容量電極171は、蓄積容量170の片方の電極として機能し、容量線350に電気的に接続されることによって、固定電位に保持されている。

誘電体膜175は、下部容量電極171上に、下部容量電極171を覆うようにベタ状に形成されている。

【0095】

ここで、画素電極9aと下部容量電極171とはITO等の透明導電性材料で構成されている。また、誘電体膜175は、透明な誘電性材料である窒化シリコン等で構成されている。よって、これらで構成される蓄積容量170は、可視光に対して透明となるため、光透過率を殆ど低下させることはなく、透過光を有効に利用することができる。すなわち、蓄積容量170を、開口領域に形成することが出来るため、蓄積容量170の容量を大きくし、かつ開口領域のサイズを広げることが出来る。

【0096】

続いて、第3の相違点について説明する。

図13に示すように、蓄積容量を画素間で分離するための容量分離膜80は、隣り合う画素に跨る下部容量電極171の開口部を避けるように、容量分離膜80の開口部を略H型の形状に有している。

そしてこの容量分離膜80の開口部の形状に、概ね沿った状態で下部容量電極171と画素電極9aとが対向配置されて、蓄積容量170を構成する。

すなわち、隣り合うデータ線6aの間に設けられる下部容量電極171の開口部と、隣り合うデータ線6aの間にもそれぞれ容量分離膜80の開口部が設けられて(図13でドットハッチにて図示している領域)蓄積容量170を構成することで、画素電極9aの内側における蓄積容量領域の平面的な面積をできるだけ多く確保している。

【0097】

ここで仮に、蓄積容量170の容量値が小さい場合、画像信号を保持できる時間が短くなるため、表示画像の画質はあまり改善しない。

一方、蓄積容量170の容量値が大きい場合、画像信号を長期間保持できるため表示画像の画質の改善を期待することができるものの、画像信号の供給回路や配線等が大型化してしまう。

そのため、実際の液晶表示装置では、蓄積容量170の容量値が好適な値に調整される。本適用例によれば、容量分離膜80によって、蓄積容量170の容量値を大きくできると共に、容量分離膜80の面積の加減により好適な容量値を選択し、設計自由度を高めることが出来る。

【0098】

なお、本実施形態における製造方法については、実施形態1の製造方法を適用することができる。

【0099】

以上説明したように、実施形態2に係る液晶表示装置によれば、実施形態1における効果に加えて、以下の効果を得ることができる。

【0100】

本実施形態の液晶表示装置によれば、従来の液晶表示装置よりも、遮光性が高く、蓄積容量170の容量値を大きくし、且つ開口領域のサイズを広げることが可能であるため、液晶表示装置の表示性能を向上させることが可能である。

従って、表示ムラがなく、高コントラストで優れた画像品質の液晶表示装置を提供することができる。

【0101】

なお、本発明は上述した実施形態に限定されず、上述した実施形態に種々の変更や改良などを加えることが可能である。変形例を以下に述べる。

【0102】

(変形例)

前述した「電気光学装置の製造方法」において、図9に示すステップS8及びS9に変えて、スプレー式CVDにて行うことも可能である。本方法を用いることにより、コンタクトホール86に画素電極9aよりも、より比抵抗の低い透明導電性材料を充填することが可能となる。

【0103】

ここで、スプレー式CVD法とは、透明導電性材料の原材料となる金属塩化物の水溶液や金属錯体を溶質とする有機溶液(本適用例の場合は、InCl3、SnCl2、SnCl4など)を霧化して、素子基板上に吹き付ける方法であって、大気中のその場で結晶性の薄膜を成長させることが可能な方法である。

なお、超音波振動によって霧化する場合を特にパイロゾル法と呼んでいるが、本発明においては、超音波振動の有無を問わず適用可能であるため、スプレー式CVD法と表記した場合には、パイロゾル法も含むこととする。

【0104】

一般に、透明導電性材料の比抵抗は、各種物理量の中で、不純物などの格子欠陥の存在に最も敏感であり、例えば、純金属への微量不純物の添加によってその比抵抗は、顕著に増加する。

しかしながら、スプレー式CVD法に使用される有機溶液は、高純度の薬品から加工なしで調整することが可能であるため、不純物の混入が極めて少ない、つまり比抵抗の低い透明導電性材料を製造するのに大変有利である。

【0105】

なお、画素電極9aの製造方法で用いられる前述のスパッタリング法には、一般的に、酸化Inと酸化Snとの粉末を熱焼結法で作成したターゲット材を使用する。

この熱焼結法の過程で、ターゲット中に重金属不純物(Fe、Cuなど)が混入し、低純度のターゲットとなってしまうため、画素電極9aと同じ製造方法でコンタクトホール86を充填した場合、比抵抗の高い充填部500を形成してしまうのである。

【0106】

以下、具体的にスプレー式CVD法を用いた製造方法について記す。

本発明に用いられるスプレー式CVD法は、例えば前述した有機溶液を用いて、基板雰囲気、基板温度、処理時間を適宜設定することにより、所望の特性を有する透明導電性材料を得ることが可能となる。

これにより、本変形例に係る電気光学装置の製造方法によれば、コンタクトホール86に画素電極9aよりも比抵抗が低い透明導電性材料を充填することが可能となる。

【0107】

以上から、表示ムラ、コントラストの面で優れた画像表示が可能となり、さらに画像表示の高速駆動が可能になる。

【0108】

「電子機器」

次に、図15を参照しながら、上述した液晶表示装置を、電子機器の一例であるプロジェクターにライトバルブとして適用した例を説明する。図15は、プロジェクターの構成例を示す平面図である。

【0109】

図15において、プロジェクター1100の内部には、ハロゲンランプ等の白色光源からなるランプユニット1102が設けられている。このランプユニット1102から射出された投射光は、ライトガイド1104内に配置された4枚のミラー1106及び2枚のダイクロイックミラー1108によってRGBの3原色に分離され、各原色に対応するライトバルブとしての液晶パネル1110R、1110B及び1110Gに入射される。

【0110】

液晶パネル1110R、1110B及び1110Gの構成は、上述した電気光学装置と同等であり、画像信号処理回路から供給されるR、G、Bの原色信号でそれぞれ駆動されるものである。そして、これらの液晶パネルによって変調された光は、ダイクロイックプリズム1112に3方向から入射される。このダイクロイックプリズム1112においては、R及びBの光が90度に屈折する一方、Gの光が直進する。従って、各色の画像が合成される結果、投射レンズ1114を介して、スクリーン等にカラー画像が投射されることとなる。

【0111】

ここで、各液晶パネル1110R、1110B及び1110Gによる表示画像について着目すると、液晶パネル1110Gによる表示画像は、液晶パネル1110R、1110Bによる表示画像に対して左右反転することが必要となる。

【0112】

尚、液晶パネル1110R、1110B及び1110Gには、ダイクロイックミラー1108によって、R、G、Bの各原色に対する光が入射するので、カラーフィルターを設ける必要はない。

【0113】

尚、図15を参照して説明した電子機器の他にも、モバイル型のパーソナルコンピューターや、携帯電話、液晶テレビ、ビューファインダー型もしくはモニター直視型のビデオテープレコーダー、カーナビゲーション装置、ページャー、電子手帳、電卓、ワードプロセッサー、ワークステーション、テレビ電話、POS端末、タッチパネルを備えた装置等があげられる。そして、これら各種電子機器に適用可能なのは言うまでもない。

【0114】

また、本発明は上述の各実施形態で説明した液晶装置以外にも、反射型液晶装置(LCOS)、プラズマディスプレイ(PDP)、電解放出型ディスプレイ(FED、SED)、有機ELディスプレイ、デジタルマイクロミラーデバイス(DMD)、電気泳動装置等にも適用可能である。

【0115】

本発明は、上述した実施形態に限られるものではなく、請求の範囲及び明細書全体から読み取れる発明の要旨或は思想に反しない範囲で適宜変更可能であり、そのような変更を伴う電気光学装置、及び該電気光学装置を備えた電子機器もまた本発明の技術的範囲に含まれるものである。

【符号の説明】

【0116】

1a…半導体層、1a´…チャネル領域、1b…低濃度ソース領域、1c…低濃度ドレイン領域、1d…高濃度ソース領域、1e…高濃度ドレイン領域、2…絶縁膜、3a…ゲート電極、6a…データ線、7…サンプリング回路、9a…画素電極、10…素子基板、11a…データ線、12…下地絶縁膜、16…配向膜、20…対向基板、21…対向電極、22…配向膜、23…遮光膜、30…スイッチング素子、31/32/34…コンタクトホール、41…第1層間絶縁膜、42…第2層間絶縁膜、43…第3層間絶縁膜、44…第4層間絶縁膜、45…層間絶縁膜、46…層間絶縁膜、47…層間絶縁膜、50…液晶層、52…シール材、53…額縁遮光膜、70…蓄積容量、71…下部容量電極、75…誘電体膜、81/83/84/85/86…コンタクトホール、90…引き回し配線、91/92…中継層、101…データ線駆動回路、102…外部回路接続端子、104…走査線駆動回路、106…上下導通部、107…異方性導電材料、171…下部容量電極、175…誘電体膜、300…上部容量電極、350…容量線、400/600…中継層、1100…プロジェクター、1102…ランプユニット、1104…ライトガイド、1106…ミラー、1108…ダイクロイックミラー、1110R(1110G、1110B)…液晶パネル、G1〜Gm…走査信号、S1〜Sn…データ信号。

【特許請求の範囲】

【請求項1】

基板と、

前記基板上で互いに交差する複数の走査線及び複数のデータ線と、

前記走査線及び前記データ線の交差に対応して設けられた複数の画素と、

前記複数の画素毎に設けられたスイッチング素子と、

前記複数の画素のうち互いに隣り合う2つの画素の夫々の開口領域の間隙に位置する非開口領域に設けられており、前記スイッチング素子に電気的に接続された第1導電膜と、

少なくとも前記第1導電膜に重なり、前記非開口領域に第1のコンタクトホールが形成された第1絶縁層と、

前記第1のコンタクトホールを介して前記第1導電膜に電気的に接続され、前記第1絶縁層上に形成されており、前記2つの画素のうち一方の画素の開口領域に延びる延在部を有する透明な第2導電膜と、

前記第2導電膜上に積層され、前記開口領域に第2のコンタクトホールが形成された第2絶縁層と、

前記第2のコンタクトホールを介して前記延在部に電気的に接続され、少なくとも前記一方の画素の開口領域に形成された画素電極と、を少なくとも備え、

前記第2のコンタクトホールの内部は、前記画素電極よりも比抵抗が低い透明導電性材料によって充填されていることを特徴とする電気光学装置。

【請求項2】

基板と前記基板上で互いに交差する複数の走査線及び複数のデータ線と、前記走査線及び前記データ線の交差に対応して設けられた複数の画素と、前記複数の画素毎に設けられたスイッチング素子と、前記複数の画素のうち互いに隣り合う2つの画素の夫々の開口領域の間隙に位置する非開口領域に設けられており、前記スイッチング素子に電気的に接続された第1導電膜を形成する工程と、

少なくとも前記第1導電膜に重なり、前記非開口領域に第1のコンタクトホールが設けられた第1絶縁層を形成する工程と、

前記第1のコンタクトホールを介して前記第1導電膜に電気的に接続され、前記第1絶縁層上に設けられており、前記2つの画素のうち一方の画素の開口領域に延びる延在部を有する透明な第2導電膜を形成する工程と、

前記第2導電膜上に積層され、第2のコンタクトホールが設けられた第2絶縁層を形成する工程と、

前記第2のコンタクトホールの内部に、透明導電性材料を充填する工程と、

前記第2のコンタクトホールを介して前記延在部に電気的に接続され、少なくとも前記一方の画素の開口領域に画素電極を形成する工程と、を含み、

前記透明導電性材料は、前記画素電極よりも比抵抗が低いことを特徴とする電気光学装置の製造方法。

【請求項3】

前記透明導電性材料を充填する工程は、

前記透明導電性材料を塗布する工程と、

前記塗布した透明導電性材料を焼結する焼結工程と、を含むことを特徴とする請求項2に記載の電気光学装置の製造方法。

【請求項4】

前記塗布工程は、

化学気相堆積法を用いることを特徴とする請求項3に記載の電気光学装置の製造方法。

【請求項5】

前記透明導電性材料を充填する工程の後に、前記第2のコンタクトホールが形成された部分を含む前記第2絶縁層の表面に対して、平坦化処理を施す工程を含むことを特徴とする請求項3ないし請求項4に記載の電気光学装置の製造方法。

【請求項6】

前記平坦化処理を施す工程は、化学機械研磨法を用いることを特徴とする請求項5に記載の電気光学装置の製造方法。

【請求項7】

請求項1に記載の電気光学装置を備えたことを特徴とする電子機器。

【請求項1】

基板と、

前記基板上で互いに交差する複数の走査線及び複数のデータ線と、

前記走査線及び前記データ線の交差に対応して設けられた複数の画素と、

前記複数の画素毎に設けられたスイッチング素子と、

前記複数の画素のうち互いに隣り合う2つの画素の夫々の開口領域の間隙に位置する非開口領域に設けられており、前記スイッチング素子に電気的に接続された第1導電膜と、

少なくとも前記第1導電膜に重なり、前記非開口領域に第1のコンタクトホールが形成された第1絶縁層と、

前記第1のコンタクトホールを介して前記第1導電膜に電気的に接続され、前記第1絶縁層上に形成されており、前記2つの画素のうち一方の画素の開口領域に延びる延在部を有する透明な第2導電膜と、

前記第2導電膜上に積層され、前記開口領域に第2のコンタクトホールが形成された第2絶縁層と、

前記第2のコンタクトホールを介して前記延在部に電気的に接続され、少なくとも前記一方の画素の開口領域に形成された画素電極と、を少なくとも備え、

前記第2のコンタクトホールの内部は、前記画素電極よりも比抵抗が低い透明導電性材料によって充填されていることを特徴とする電気光学装置。

【請求項2】

基板と前記基板上で互いに交差する複数の走査線及び複数のデータ線と、前記走査線及び前記データ線の交差に対応して設けられた複数の画素と、前記複数の画素毎に設けられたスイッチング素子と、前記複数の画素のうち互いに隣り合う2つの画素の夫々の開口領域の間隙に位置する非開口領域に設けられており、前記スイッチング素子に電気的に接続された第1導電膜を形成する工程と、

少なくとも前記第1導電膜に重なり、前記非開口領域に第1のコンタクトホールが設けられた第1絶縁層を形成する工程と、

前記第1のコンタクトホールを介して前記第1導電膜に電気的に接続され、前記第1絶縁層上に設けられており、前記2つの画素のうち一方の画素の開口領域に延びる延在部を有する透明な第2導電膜を形成する工程と、

前記第2導電膜上に積層され、第2のコンタクトホールが設けられた第2絶縁層を形成する工程と、

前記第2のコンタクトホールの内部に、透明導電性材料を充填する工程と、

前記第2のコンタクトホールを介して前記延在部に電気的に接続され、少なくとも前記一方の画素の開口領域に画素電極を形成する工程と、を含み、

前記透明導電性材料は、前記画素電極よりも比抵抗が低いことを特徴とする電気光学装置の製造方法。

【請求項3】

前記透明導電性材料を充填する工程は、

前記透明導電性材料を塗布する工程と、

前記塗布した透明導電性材料を焼結する焼結工程と、を含むことを特徴とする請求項2に記載の電気光学装置の製造方法。

【請求項4】

前記塗布工程は、

化学気相堆積法を用いることを特徴とする請求項3に記載の電気光学装置の製造方法。

【請求項5】

前記透明導電性材料を充填する工程の後に、前記第2のコンタクトホールが形成された部分を含む前記第2絶縁層の表面に対して、平坦化処理を施す工程を含むことを特徴とする請求項3ないし請求項4に記載の電気光学装置の製造方法。

【請求項6】

前記平坦化処理を施す工程は、化学機械研磨法を用いることを特徴とする請求項5に記載の電気光学装置の製造方法。

【請求項7】

請求項1に記載の電気光学装置を備えたことを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2012−108408(P2012−108408A)

【公開日】平成24年6月7日(2012.6.7)

【国際特許分類】

【出願番号】特願2010−258643(P2010−258643)

【出願日】平成22年11月19日(2010.11.19)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成24年6月7日(2012.6.7)

【国際特許分類】

【出願日】平成22年11月19日(2010.11.19)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]