電気光学装置、電子機器および制御方法

【課題】ベイヤー配置された画素を有する電気光学装置においてサブフィールド方式を用いる場合において、階調表現能力の低下を抑制すること。

【解決手段】電気光学装置は、第1色の画素、第2色の画素、および第3色の画素がベイヤー配置された複数の画素と、前記複数の画素のうち前記第1色の画素を選択するための複数の走査線を含む第1走査線群と、前記複数の画素のうち前記第2色および前記第3色の画素を選択するための複数の走査線を含む第2走査線群と、単位期間を区分したa個のサブ期間のうち走査に用いられる一のサブ期間を選択するためのb系統のイネーブル信号(b≧a)に応じて、前記第1走査線群および前記第2走査線群の中から順次一の走査線を選択する第1走査、および前記第1走査線群の中から順次一の走査線を選択する第2走査のいずれかの走査を行う走査線駆動回路とを有する。

【解決手段】電気光学装置は、第1色の画素、第2色の画素、および第3色の画素がベイヤー配置された複数の画素と、前記複数の画素のうち前記第1色の画素を選択するための複数の走査線を含む第1走査線群と、前記複数の画素のうち前記第2色および前記第3色の画素を選択するための複数の走査線を含む第2走査線群と、単位期間を区分したa個のサブ期間のうち走査に用いられる一のサブ期間を選択するためのb系統のイネーブル信号(b≧a)に応じて、前記第1走査線群および前記第2走査線群の中から順次一の走査線を選択する第1走査、および前記第1走査線群の中から順次一の走査線を選択する第2走査のいずれかの走査を行う走査線駆動回路とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ベイヤー配置された複数の画素をサブフィールド駆動する技術に関する。

【背景技術】

【0002】

液晶素子等の電気光学素子における階調制御方法として、電気光学素子に印加される電圧を変調する電圧変調方式の他、電気光学素子に一定電圧が印加される時間を変調する、いわゆるサブフィールド駆動方式が知られている。サブフィールド駆動方式において、1フレームは複数のサブフィールドに分割される。複数のサブフィールドのうち電圧印加をオンするサブフィールドとオフするサブフィールドとの組み合わせ(正確には順列)により、電気光学素子の階調が制御される。

【0003】

サブフィールド駆動において階調表現を向上させる手法の一つに、一つのサブフィールドを短くするものがある。サブフィールドを短くする技術としては、いわゆる領域走査駆動が知られている(特許文献1)。

【0004】

赤(R)、緑(G)、および青(B)の3原色を2次元的に配置する方法として、いわゆるベイヤー配置が知られている(特許文献2)。ベイヤー配置は、RおよびB各1画素、G2画素を1組とした配置である。ベイヤー配置では、単位面積あたり、GはRおよびBの2倍の情報量を有する。これは人間の視感度特性を考慮したものである。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2004−177930号公報

【特許文献2】米国特許第3971065号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

ベイヤー配置された画素を有する電気光学装置においてホワイトバランスをとるには、Gの画素の輝度をRおよびBの画素の輝度の半分にすることが考えられる。これをサブフィールド駆動方式で実現しようとすると、Gの画素において1フレームのほぼ半分の期間を輝度ゼロの状態にする必要がある。これは、Gの画素において階調表現に使えるサブフィールド数がRおよびBの画素よりも少なくなることを意味する。すなわち、Gの階調表現力が低下してしまう。

これに対し本発明は、ベイヤー配置された画素を有する電気光学装置においてサブフィールド方式を用いる場合において、階調表現能力の低下を抑制する技術を提供する。

【課題を解決するための手段】

【0007】

本発明は、第1色の画素が2つ、第2色の画素、および第3色の画素がベイヤー配置された複数の画素と、前記複数の画素のうち前記第1色の画素を選択するための複数の走査線を含む第1走査線群と、前記複数の画素のうち前記第2色および前記第3色の画素を選択するための複数の走査線を含む第2走査線群と、単位期間を区分したa個のサブ期間のうち走査に用いられる一のサブ期間を選択するためのb系統のイネーブル信号(b≧a)に応じて、前記第1走査線群および前記第2走査線群の中から順次一の走査線を選択する第1走査、および前記第1走査線群の中から順次一の走査線を選択する第2走査のいずれかの走査を行う走査線駆動回路とを有する電気光学装置を提供する。

この電気光学装置によれば、第1走査線群の走査と第2走査線群の走査とが分離していない構成と比較して、階調表現能力の低下を抑制することができる。

【0008】

好ましい態様において、前記イネーブル信号は、連続する2つの単位期間において同一のサブ期間を選択するための波形を有し、前記a個のサブ期間のうち、前記第2走査に用いられるサブ期間については、前記連続する2つの単位期間の一方においてのみ選択するための波形を有してもよい。

この電気光学装置によれば、イネーブル信号を変形することにより、第1走査線群の走査と第2走査線群の走査とを分離させることができる。

【0009】

別の好ましい態様において、前記複数の画素は、m行n列のマトリクス状に配置され、前記第1走査線群および前記第2走査線群は、あわせて(m+1)本の走査線を有し、前記第1走査線群の走査線と、前記第2走査線群の走査線とは、交互に配置され、前記走査線駆動回路は、スタートパルス信号を1段ずつ転送させた信号を出力する(m+1)段のシフトレジスターと、前記シフトレジスターの出力信号と、前記b系統のイネーブル信号のうち対応する一のイネーブル信号の論理積に応じた信号を出力する出力回路とを有してもよい。

この電気光学装置によれば、スタートパルス信号により走査を開始する場合において、階調表現能力の低下を抑制することができる。

【0010】

さらに別の好ましい態様において、b≦NSF1+NSF2−1(ただし、NSF1は前記第1色の画素におけるサブフィールド数を示し、NSF2は前記第2色の画素におけるサブフィールド数を示す)であってもよい。

この電気光学装置によれば、第2走査線群の走査が第1走査線群の走査と共通している構成と比較して、サブフィールド構成の自由度を向上させることができる。

【0011】

さらに別の好ましい態様において、前記複数の画素は、m行n列のマトリクス状に配置され、前記第1走査線群および前記第2走査線群は、あわせて(m+1)本の走査線を有し、前記第1走査線群の走査線と、前記第2走査線群の走査線とは、交互に配置され、前記走査線駆動回路は、第1スタートパルス信号を1段ずつ転送させた信号を出力する(m+1)段の第1シフトレジスターと、前記第1シフトレジスターの出力信号と、前記b系統のイネーブル信号のうち対応する一のイネーブル信号の論理積に応じた信号を、前記(m+1)行の走査線のうち奇数行または偶数行の一方に出力する第1出力回路と、第2スタートパルス信号を1段ずつ転送させた信号を出力する(m+1)段の第2シフトレジスターと、前記第2シフトレジスターの出力信号と、前記b系統のイネーブル信号のうち対応する一のイネーブル信号の論理積に応じた信号を、前記(m+1)行の走査線のうち奇数行または偶数行の他方に出力する第2出力回路とを有してもよい。

この電気光学装置によれば、スタートパルス信号により走査を開始する場合において、階調表現能力の低下を抑制することができる。

【0012】

さらに別の好ましい態様において、前記(m+1)本の走査線の各々に接続される画素の数が等しくてもよい。

この電気光学装置によれば、画素(負荷)の数が異なる場合と比較して、階調表現への悪影響を低減することができる。

【0013】

また、本発明は、上記いずれかの電気光学装置を有する電子機器を提供する。

この電子機器によれば、第1走査線群の走査と第2走査線群の走査とが分離していない構成と比較して、階調表現能力の低下を抑制することができる。

【0014】

さらに、本発明は、第1色の画素が2つ、第2色の画素、および第3色の画素がベイヤー配置された複数の画素と、前記複数の画素のうち前記第1色の画素を選択するための複数の走査線を含む第1走査線群と、前記複数の画素のうち前記第2色および前記第3色の画素を選択するための複数の走査線を含む第2走査線群とを有する電気光学装置の制御方法であって、単位期間を区分したa個のサブ期間のうち走査に用いられる一のサブ期間を選択するためのb系統のイネーブル信号(b≧a)に応じて、前記第1走査線群および前記第2走査線群の中から順次一の走査線を選択する第1走査、および前記第1走査線群の中から順次一の走査線を選択する第2走査のいずれかの走査を行うステップを有する制御方法を提供する。

この制御方法によれば、第1走査線群の走査と第2走査線群の走査とが分離していない構成と比較して、階調表現能力の低下を抑制することができる。

【図面の簡単な説明】

【0015】

【図1】第1実施形態に係る電子機器1の概要を示す図。

【図2】液晶パネル100の回路構成を示すブロック図。

【図3】画素111の等価回路を示す図。

【図4】画素と走査線との対応関係を示す図。

【図5】走査線駆動回路130の構成を示す図。

【図6】シフト回路1311の構成を示す図。

【図7】データ線駆動回路140の構成を示す図。

【図8】走査線駆動回路130の動作の概要を説明する図。

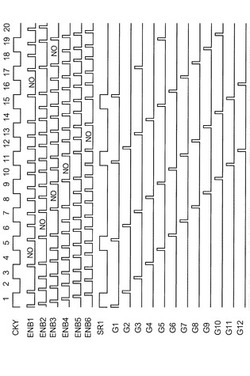

【図9】走査線駆動回路130のタイミングチャートを例示する図。

【図10】第2実施形態に係る液晶パネル100の構成を示す図。

【図11】走査線駆動回路230の構成を示す図。

【図12】走査線駆動回路330の構成を示す図。

【図13】第2実施形態に係る走査線駆動回路タイミングチャートを例示する図。

【図14】第1実施形態と第2実施形態のサブフィールド構成の相違を説明する図。

【図15】変形例1に係る液晶パネル100の構成を示す図。

【発明を実施するための形態】

【0016】

1.第1実施形態

1−1.構成

図1は、第1実施形態に係る電子機器1の概要を示す図である。電子機器1は、映像を表示する装置、この例ではプロジェクターである。「映像」とは、静止画および動画を含む概念である。電子機器1は、上位装置から供給される映像信号Vid−inにより示される画像を、同期信号Syncに基づいたタイミングで、液晶パネル100に表示する装置である。

【0017】

電子機器1は、電気光学装置10と、映像処理回路20とを有する。電気光学装置10は、液晶パネル100(電気光学パネルの一例)と、制御回路と、光源と、光学系(液晶パネル100以外は図示略)とを有する。液晶パネル100は、m行n列のマトリクス状に配置された複数の画素を有する。液晶パネル100はカラー液晶パネルであり、赤(R)、緑(G)、および青(B)の3原色の画素を有する。

【0018】

R、G、およびBの画素は、ベイヤー配置されている。ベイヤー配置において、R、G、およびBの画素は、2行2列の4画素を単位(以下「単位領域」という)として配置されている。単位領域には、R画素およびB画素が各1つ、G画素が2つ含まれる。2つのG画素は、斜めに配置されている。

【0019】

映像処理回路20は、入力された画像データに対して画像処理、例えばモザイキング処理を行う。以下、入力された画像データを「入力画像データ」といい、入力画像データにより示される画像を「入力画像」という。入力画像データは、1画素につき、R、G、およびBの3つの色成分を含んでいる。いま、入力画像の画素数がm×n個、すなわち液晶パネル100の画素数と等しい場合を考える。この場合、RおよびBについては、液晶パネル100の画素数は入力画像の1/4、Gについては、液晶パネル100の画素数は入力画像の1/2である。例えばRについて考えると、入力画像の4画素のデータを1画素のデータに変換する処理(モザイキング処理)が必要である。モザイキング処理のアルゴリズムとしては種々のものが知られており、ここではどのようなアルゴリズムが用いられてもよい。

【0020】

図2は、液晶パネル100の回路構成を示すブロック図である。液晶パネル100は、供給される信号に応じた画像を表示する装置である。液晶パネル100は、表示領域101と、走査線駆動回路130と、データ線駆動回路140とを有する。表示領域101には、複数の画素111が配置されている。この例では、m行n列の画素111がマトリクス状に配置されている。液晶パネル100は、素子基板100aと、対向基板100bと、液晶層105とを有する。素子基板100aおよび対向基板100bは一定の間隔を保って貼り合わせられている。素子基板100aおよび対向基板100bの間隙には、液晶層105が挟まれている。素子基板100aには、(m+1)本の走査線112およびn本のデータ線114が設けられている。走査線112およびデータ線114は、対向基板100bと対向する面に設けられている。走査線112とデータ線114とは、電気的に絶縁されている。走査線112とデータ線114との交差に対応して、画素111が設けられている。以下において、複数の走査線112を区別する場合には、図2において上から順に、第1、第2、第3、…、第(m−1)、第m行の走査線112という。同様に、複数のデータ線114を区別する場合には、図2において左から順に、第1、第2、第3、…、第(n−1)、第n列のデータ線114という。なお、図8において、素子基板100aの対向面は紙面裏側であるので、この対向面に設けられる走査線112、およびデータ線114ついては破線で示すべきであるが、見難くなるので、それぞれ実線で示している。

【0021】

対向基板100bには、コモン電極108が設けられている。コモン電極108は、素子基板100aと対向する1面に設けられている。コモン電極108は、すべての画素111について共通である。すなわち、コモン電極108は、対向基板100bのほぼ全面にわたって設けられている、いわゆるベタ電極である。

【0022】

液晶パネル100は、さらに、複数のイネーブル信号線、この例では6本のイネーブル信号線ENB1〜ENB6を有する。イネーブル信号については後述する。

【0023】

図3は、画素111の等価回路を示す図である。画素111は、TFT116、液晶素子120、および容量素子125を有する。TFT116は、液晶素子120への電圧の印加を制御するスイッチング手段の一例であり、この例ではnチャネル型の電界効果トランジスターである。液晶素子120は、印加される電圧に応じて光学状態が変化する素子である。この例で、液晶パネル100は透過型の液晶パネルであり、変化する光学状態は透過率である。液晶素子120は、画素電極118、液晶層105、およびコモン電極108を有する。第i行第j列の画素111において、TFT116のゲートおよびソースは、それぞれ、第i行の走査線112および第j列のデータ線114に接続されている。TFT116のドレインは、画素電極118に接続されている。容量素子125は、画素電極118に書き込まれた電圧を保持する素子である。容量素子125の一端は画素電極118に接続されており、他端は容量線Vcomに接続されている。

【0024】

第i行の走査線112にHレベルの電圧を示す信号が入力されると、TFT116のソース・ドレイン間は導通する。TFT116のソース・ドレイン間が導通すると、画素電極118は、(TFT116のソース・ドレイン間のオン抵抗を無視すれば)第j列のデータ線114と同電位になる。第j列のデータ線114には、映像信号Vid−inに応じて、第i行第j列の画素111の階調値に応じた電圧(以下、「データ電圧」といい、データ電圧を示す信号を「データ信号」という)が印加される。コモン電極108には、図示しない回路により、共通電位LCcomが与えられる。容量線Vcomには、図示しない回路により、時間的に一定の電位Vcom(この例では、Vcom=LCcom)が与えられる。すなわち、液晶素子120には、データ電圧と共通電位LCcomとの差に応じた電圧が印加される。以下、液晶層105がVA(Vertical Alignment)型であり、電圧無印加時において液晶素子120の階調が暗状態(黒状態)となるノーマリーブラックモードである例を用いて説明する。なお、特に説明しない限り、図示を省略した接地電位を電圧の基準(ゼロV)とする。

【0025】

液晶パネル100はサブフィールド駆動されるので、液晶素子120に印加される電圧の絶対値は、VH(第1電圧の一例、例えば5V)またはVL(第2電圧の一例、例えばゼロV)の2値のいずれかである。

【0026】

図4は、画素と走査線との対応関係を示す図である。この例で、G画素は奇数行(第(2k+1)行:kはゼロを含む自然数)の走査線112に、R画素およびB画素は偶数行(第(2k+2)行)の走査線112に、それぞれ接続されている。すなわち、奇数行の走査線112を選択するとG画素のみを選択し(R画素およびB画素を選択せず)、偶数行の走査線112を選択するとR画素およびB画素のみを選択する(G画素を選択しない)ことができる。奇数行の走査線112は、第1走査線群の一例であり、偶数行の走査線112は第2走査線群の一例である。

【0027】

図5は、走査線駆動回路130の構成を示す図である。走査線駆動回路130は、入力される制御信号に従って、走査線112を選択するための走査信号Gを出力する回路である。制御信号としては、スタートパルス信号SPY、クロック信号CKY、およびイネーブル信号ENB1〜ENB6が用いられる。第i行の走査線112に供給される走査信号を、走査信号Giという。走査信号Giは、m本の走査線112の中から一の走査線112を選択するための信号である。走査信号Giは、選択される走査線112に対しては選択電圧(Hレベル)となり、それ以外の走査線112に対しては非選択電圧(Lレベル)となる信号である。選択電圧を示す信号を選択信号といい、非選択電圧を示す信号を非選択信号という。

【0028】

この例において、走査線駆動回路130は、単一のクロックにおいて複数の走査線112を選択する。より詳細には、1クロックはさらに複数の期間に区分されており(以下この細分化された期間を「番地」といい、サブ期間の一例である)、単一の番地において単一の走査線112が選択される。1クロックがa個の番地で構成される場合、1クロックで最大a本の走査線112を選択することができる。イネーブル信号は、a個の番地のうち使用される番地を特定するための信号である。この例で、液晶パネル100は6本のイネーブル信号線ENB1〜ENB6を有するので、1クロックは6番地に区分される(a=6)。

【0029】

走査線駆動回路130は、シフトレジスター131と、出力回路132とを有する。シフトレジスター131は、スタートパルス信号SPYを、クロック信号CKYにより示されるクロック毎に、1段(1行)ずつ転送(シフト)する回路である。シフトレジスター131は、(m+1)段のシフト回路1311を有する。第i段のシフト回路1311を、シフト回路1311(i)と表す。他の要素についても同様である。各シフト回路1311は、走査線112と一対一に対応している。

【0030】

図6は、シフト回路1311の構成を示す図である。シフト回路1311は、クロックドインバーター13111、クロックドインバーター13112、およびインバーター13113を有する。奇数段のクロックドインバーター13111は、クロック信号CKがHレベルのときにインバーターとして機能し、クロック信号CKがLレベルのときに高インピーダンスとなる回路である。クロックドインバーター13112は、クロック信号CKBがHレベルのときにインバーターとして機能し、クロック信号CKがLレベルのときに高インピーダンスとなる回路である。

【0031】

奇数段のシフト回路1311(i)には、クロック信号CKとしてクロック信号CKYが、クロック信号CKBとしてクロック信号CKYの反転信号が、それぞれ入力される。偶数段のシフト回路1311(i+1)には、クロック信号CKとしてクロック信号CKYの反転信号が、クロック信号CKBとしてクロック信号が、それぞれ入力される。クロック信号CKYがHレベルのとき、奇数段のシフト回路1311(i)の入力INに入力した入力信号に応じた出力信号を出力OUTに出力する。奇数段のシフト回路1311(i)の入力INの電位がHレベルになっていれば、出力OUTの電位もHレベルである。このとき、次段(偶数段)のシフト回路1311(i+1)は高インピーダンス状態である。クロック信号CKYが反転してLレベルになると、シフト回路1311(i)は高インピーダンス状態になり、シフト回路1311(i+1)の入力INに入力した入力信号に応じた出力信号を出力OUTに出力する。前のクロックでシフト回路1311(i)の出力OUTがHレベルであれば、シフト回路1311(i+1)の出力OUTがHレベルになる。このようにして、Hレベルの信号が1クロックずつ後段のシフト回路1311に転送される。

【0032】

再び図5を参照する。シフトレジスター131と出力回路132との間には、NAND回路133およびインバーター134が設けられている。NAND回路133およびインバーター134は、シフト回路1311と一対一に対応している。第i段のNAND回路133およびインバーター134を、NAND回路133(i)およびインバーター134(i)と表す。NAND回路133(i)には、シフト回路133(i)の入力INおよび出力OUTが入力される。インバーター134(i)は、NAND回路133(i)の出力を反転する。インバーター134(i)から出力される信号を、信号SRiと表す。信号SRiは、スタートパルス信号SPYが第i段に転送された場合にHレベルとなり、それ以外の場合はLレベルとなる信号である。

【0033】

出力回路132(i)は、信号SRiと、イネーブル信号ENBrとの論理積を出力する回路である。ここで、rは、偶数行(すなわちiが偶数のとき)についてはi/2をaで除算したときの剰余、すなわちr=((i/2) mod a)である(ただし((i/2) mod a)=0の場合、r=a)。奇数行(すなわちiが奇数のとき)については、1行前(すなわち第(i−1)行)のrと同じ値である。例えば、a=6の場合を考える。第1段の出力回路132(1)は、イネーブル信号ENB1と、信号SR1との論理積を出力する回路である。第2段の出力回路132(2)は、イネーブル信号ENB1と、信号SR2との論理積を出力する回路である。第3段の出力回路132(3)は、イネーブル信号ENB2と、信号SR3との論理積を出力する回路である。第12段の出力回路132(12)は、イネーブル信号ENB6と、信号SR12との論理積を出力する回路である。第13段の出力回路132(13)は、イネーブル信号ENB1と、信号SR13との論理積を出力する回路である。第14段の出力回路132(14)は、イネーブル信号ENB1と、信号SR14との論理積を出力する回路である。

【0034】

図7は、データ線駆動回路140の構成を示す図である。データ線駆動回路140は、入力される制御信号に従ってデータ信号DATをサンプリングし、画素111に書き込まれるデータ電圧を示すデータ信号Sを出力する回路である。第j列のデータ線114に供給されるデータ信号を、データ信号Sjという。制御信号としては、スタートパルス信号SPY、クロック信号CKX、およびラッチ信号LATが用いられる。なお図7中では第2ラッチ回路143の内部に、データ線Sjへの電圧出力回路部を含むものとして省略して記載している。本願の本質の説明では電圧出力回路部の詳細は省略しても問題ない。

【0035】

データ線駆動回路140は、シフトレジスター141と、第1ラッチ回路142と、第2ラッチ回路143とを有する。シフトレジスター141は、スタートパルス信号SPXを、クロック信号CKXにより示されるクロック毎に1段(1列)ずつ転送する回路である。第1ラッチ回路142は、データ信号DATを、シフトレジスター141からの出力信号により示されるタイミングでラッチする回路である。データ信号DATは点順次のデータであり、第1ラッチ回路142は、各画素のデータを順次ラッチする。第2ラッチ回路143は、信号LATにより示されるタイミングで第1ラッチ回路142からの出力信号をラッチし、線順次のデータ信号Sjとしてデータ線114に出力する回路である。データ信号Sjは、サブフィールドコードがオンのときは電圧VHを示し、サブフィールドコードがオフのときは電圧VLを示す。

【0036】

映像処理回路20は、入力映像データに基づいて、データ信号DATおよび制御信号を生成する回路である(制御回路の一例)。映像処理回路20はにより生成された制御信号が、走査線駆動回路130およびデータ線駆動回路140に入力される。この例で、映像処理回路20は、モザイキング処理およびサブフィールドコード変換処理を行う。モザイキング処理は、1画素につきR、G、およびBの3つの色成分を含んでいる入力画像のデータを、ベイヤー配置された画素の階調値を示すデータに変換する処理である。

【0037】

サブフィールドコード変換処理は、モザイキング処理後の各画素の階調値をサブフィールドコードに変換する処理である。サブフィールドは、例えば、基本単位(4SFまたは6SF)を所定回数繰り返す構成を有している。例えば、1フレームにおいて基本単位が5回繰り返される場合において、基本単位が4SF(R画素およびB画素)であったときは、1フレームは20SFで構成される。この場合、サブフィールドコードは各サブフィールドについてオンおよびオフのいずれかを示す20ビットのデータである。また、この場合において、基本単位が6SF(G画素)であったときは、1フレームは30SFで構成される。この場合、サブフィールドコードは30ビットのデータである。この例で、サブフィールドコード変換処理は、変換テーブル(図示略)を参照して行われる。変換テーブルは、例えば映像処理回路20の内蔵メモリに記憶されている。

【0038】

1−2.動作

図8は、走査線駆動回路130の動作の概要を説明する図である。図8において、横軸は時間を、縦軸は選択される行を示している。図面が煩雑になるのを避けるため、図8では、番地については考慮せず、同時に複数の走査線112が選択されるように描かれている。RおよびBの画素は、実線(SCAN1、SCAN2、SCAN3、およびSCAN6)のとおり選択され、データが書き込まれる。すなわち、RおよびBの画素について、サブフィールドの基本単位は4サブフィールド(SF1〜SF4)により構成される。Gの画素は、実線に加え、破線(SCAN4およびSCAN5)のとおり選択され、データが書き込まれる。すなわち、Gの画素について、サブフィールドの基本単位は6サブフィールド(SF1G〜SF6G)により構成される。

【0039】

この例で、仮にG画素のみの走査を行わなかった場合、サブフィールド数は、すべての色の画素について、SF1〜SF4の4つである。この条件で、Gの輝度をRおよびBの半分にするには、G画素では例えば常にSF4をオフにすることになる。すると階調表現に使えるサブフィールド数は3つになってしまう。サブフィールド駆動方式においては、理論的には、2k通りの階調表現が可能である(kはサブフィールド数)。したがって、階調表現に使えるサブフィールド数が一つ減ると、理論的には、階調表現能力は半分になってしまう。これに対し、G画素のみの走査を用いれば、以下で説明するように階調表現能力の低下を抑制することができる。

【0040】

図9は、走査線駆動回路130のタイミングチャートを例示する図である。この例では、イネーブル信号ENB1〜ENB6と、出力信号SR1と、走査信号G1〜G12のみ図示している。クロック信号CKYは、HレベルとLレベルが交互に切り換わる信号である。HレベルとLレベルの切り換わりのタイミングが、クロックの始期を示している。イネーブル信号ENB1〜6は、1クロックのうち使用する番地を示す信号である。イネーブル信号がHレベルになっている期間が、使用する番地を示している。例えば、第1クロックおよび第2クロックにおいて、イネーブル信号ENB1は、第1番地においてHレベルになっている。同一のイネーブル信号についてみると、Hレベルとなる番地は、原則として2クロック毎に1番地ずつ移動している。例えば、イネーブル信号ENB1について、Hレベルとなる番地は、第1クロックから順に、第1番地、第1番地、第6番地、なし、第5番地、第5番地、第4番地、第4番地、第3番地、第3番地、第2番地、第2番地、第1番地、第1番地、第6番地、…というように変化している。ここで、同一の番地が2クロック連続しているが、第6番地については、連続する2クロックのうち1クロックでしかHレベルになっていない。この点については後述する。また、同一のクロックについてみると、Hレベルとなる番地は、イネーブル信号によって異なっている。例えば、第1クロックについて、イネーブル信号ENB1〜6がHレベルとなる番地は、それぞれ、第1番地〜第6番地である。

【0041】

信号SRiは、スタートパルス信号SPYが転送される信号である。図9では、このうち信号SR1のみが示されている。スタートパルス信号SPYが入力されないとき(Lレベルのとき)は、信号SRiはLレベルである。スタートパルス信号が入力されると、Hレベルの状態が信号SR1から順に転送される。信号SRiがHレベルであるクロックのうち、対応するイネーブル信号がHレベルである番地において、走査信号GiはHレベルとなる。例えば、第1クロックにおいてスタートパルス信号SPYが入力されると、信号SR1がHレベルになる。第1クロックにおいて信号SR1がHレベルであり、このときイネーブル信号ENB1は第1番地においてHレベルであるので、走査信号G1は第1番地においてHレベルとなる。第2クロックにおいて信号SR2がHレベルであり、このときイネーブル信号ENB1は第1番地においてHレベルであるので、走査信号G2は第1番地においてHレベルとなる。第3クロックにおいて信号SR3がHレベルであり、このときイネーブル信号ENB2は第1番地においてHレベルであるので、走査信号G3は第1番地においてHレベルとなる。走査信号G4以降の信号は順次、第1番地においてHレベルとなる。

【0042】

別の例で、第5クロックにおいてスタートパルス信号SPYが入力されると、信号SR1がHレベルになる。第5クロックにおいて信号SR1がHレベルであり、このときイネーブル信号ENB1は第5番地においてHレベルであるので、走査信号G1は第5番地においてHレベルとなる。走査信号G2以降の信号は順次、第5番地においてHレベルとなる。

【0043】

さらに別の例で、第11クロックにおいてスタートパルス信号SPYが入力されると、信号SR1がHレベルになる。第11クロックにおいて信号SR1がHレベルであり、このときイネーブル信号ENB1は第2番地においてHレベルであるので、走査信号G1は第2番地においてHレベルとなる。走査信号G2以降の信号は順次、第2番地においてHレベルとなる。

【0044】

既に説明したように、走査線駆動回路130は、a個(この例では6つ)の走査を並列させることができる。第1番地を使って走査をするときは、第1行に対応するイネーブル信号(この例ではイネーブル信号ENB1)が第1番地においてHレベルとなるクロックにおいて、スタートパルス信号SPYを入力すればよい。

【0045】

この例では、第6番地は連続する2クロックのうち一方(この例では先のクロック)でのみHレベルとなり、他方のクロック(この例では後のクロック)ではLレベルのままである(図において対応する箇所に「NO」という記号を付している)。第15クロックにおいてスタートパルス信号SPYが入力されると、信号SR1がHレベルになる。第15クロックにおいて信号SR1がHレベルであり、このときイネーブル信号ENB1は第6番地においてHレベルであるので、走査信号G1は第6番地においてHレベルとなる。第16クロックにおいて信号SR2がHレベルであり、このときイネーブル信号ENB1はすべての番地においてLレベルである。したがって、走査信号G2は非選択信号のままであり、選択信号は出力されない。第17クロックにおいてにおいて信号SR3がHレベルであり、このときイネーブル信号ENB2は第6番地においてHレベルであるので、走査信号G3は第6番地においてHレベルとなる。第18クロックにおいて信号SR4がHレベルであり、このときイネーブル信号ENB1はすべての番地においてLレベルである。したがって、走査信号G4は非選択信号のままであり、選択信号は出力されない。以下同様にして、第15クロックにおいて入力されたスタートパルス信号に起因する走査は、奇数行のみを順次選択し、偶数行を選択しない走査である。すなわち、特定の走査線(この例ではG画素に対応する走査線112)のみが、順次選択される。

【0046】

図8のSCAN1、SCAN2、SCAN3、およびSCAN6の走査を行うときは、連続する2クロックで同一の番地がHレベルとなるイネーブル信号が用いられる。図8のSCAN4およびSCAN5の走査を行うときは、連続する2クロックのうち一方のクロックですべての番地がLレベルのままであるイネーブル信号が用いられる。映像処理回路20は、例えば、番地毎に使用/未使用を示すフラグを記憶することにより、番地の使用状況を把握している。映像処理回路20は、走査を開始する際、走査に使用する番を決定する。走査に使用する番地は未使用の番地(空き番地)の中から選択される。例えば、第6番地を使用することを決定した場合において、その走査がG画素のみを対象にするときは、映像処理回路20は、第6番地について、連続する2クロックのうち後のクロックにおいてLレベルのままとなるように変形したイネーブル信号を出力する。

【0047】

以上で説明したように本実施形態によれば、G画素に対応する走査線112のみを走査することができる。これにより、G画素とR画素およびB画素とのサブフィールド数を異ならせることができる。例えば、G画素の輝度をR画素およびB画素の半分にするとき。SF6Gを常にオフとしても、SF1G〜SF5Gの5つのサブフィールドを用いて階調表現をすることができる。すなわち、ベイヤー配置された画素を有する電気光学装置においてサブフィールド方式を用いる場合において、毎回、R画素、G画素、およびB画素をすべて走査するときと比較して、階調表現能力の低下を抑制することができる。

【0048】

なお、この例では、映像処理回路20は、SCAN1、SCAN2、SCAN3、およびSCAN6の走査と同期して、R画素、G画素、およびB画素のサブフィールドコードに応じたデータをデータ線駆動回路140に出力する。また、映像処理回路20は、SCAN4およびSCAN5の走査と同期して、G画素のSF4GおよびSF5Gのサブフィールドコードに応じたデータをデータ線駆動回路140に出力する。

【0049】

2.第2実施形態

図10は、第2実施形態に係る液晶パネル100の構成を示す図である。以下、第1実施形態と共通する事項については説明を省略する。第2実施形態において、液晶パネル100は、走査線駆動回路230および走査線駆動回路330の2つの走査線駆動回路を有する。走査線駆動回路230は、偶数行の走査線112、すなわち、R画素およびB画素に対応する走査線112に対し走査信号を出力する回路である。走査線駆動回路330は、奇数行の走査線112、すなわち、G画素に対応する112に対し走査信号を出力する回路である。また、液晶パネル100は、イネーブル信号ENB1〜ENB8の8系統のイネーブル信号を伝送するための8つのイネーブル信号線を有する。

【0050】

第1実施形態の構成においては、例えば図8で説明したように、R画素およびB画素とG画素とで共通する走査(例えば、SCAN1、SCAN2、SCAN3、およびSCAN6)については、共通のタイミングで走査を行っていた。しかし、例えば図8でG画素についてはSF6Gを常にオフにする場合には、他のサブフィールドについては、R画素およびB画素のサブフィールド長とは独立してサブフィールド長を設定できた方が、より高い階調表現能力を実現できる場合がある。第2実施形態の液晶パネル100は、このような動作が可能である。

【0051】

第2実施形態において、イネーブル信号線の数bは、次式により決定される。

b=NSF1+NSF2−NSFcom ・・・(1)

ここで、NSF1はG画素におけるサブフィールドの基本単位に含まれるサブフィールド数を、NSF2はR画素およびB画素における基本単位に含まれるサブフィールド数を、NSFcomは、R画素およびB画素とG画素とで共通の走査の数を示す。この例で、G画素の基本単位は5SFであり、R画素およびB画素のサブフィールドの基本単位は4SFである。また、フレームの始期を統一するため、第1番目の走査は共通である。すなわち、NSF1=6、NSF2=4、NSFcom=1である。以上を式(1)に代入すると、

b=5+4−1=8

である。したがって、第2実施形態において8系統のイネーブル信号が用いられている。なお、共通の走査の数NSFcomは、任意に設計が可能であるが、NSFcom≧1である。したがって、式(1)からbの最大値は、

b≦NSF1+NSF2−1 ・・・(2)

である。

【0052】

図11は、走査線駆動回路230の構成を示す図である。走査線駆動回路230は、入力される制御信号に従って、偶数行の走査線112を選択するための走査信号Gを出力する回路である。制御信号としては、スタートパルス信号SPY1、クロック信号CKY、およびイネーブル信号ENB1〜ENB8が用いられる。走査線駆動回路230は、シフトレジスター231と出力回路232とを有する。シフトレジスター231の構成は、シフトレジスター131と同様である。出力回路232は、出力回路132とほぼ同様の構成を有するが、奇数行の走査線112と接続されていない点が出力回路132と異なっている。

【0053】

出力回路232(i)は、信号SRiLと、イネーブル信号ENBrとの論理積を出力する回路である。シフトレジスター231の出力と後述するシフトレジスター331の出力とを区別するため、シフトレジスター231の出力信号は、信号SRiLのように添字Lを用いる。ここで、rは、偶数行(すなわちiが偶数のとき)についてはi/2をbで除算したときの剰余、すなわちr=((i/2) mod b)である(ただし((i/2) mod b)=0のときr=b)。例えば、b=8の場合を考える。第1段の出力回路232(1)は、信号を出力しない。第2段の出力回路232(2)は、イネーブル信号ENB1と、信号SR2Lとの論理積を出力する回路である。第3段の出力回路232(3)は、信号を出力しない。第16段の出力回路232(16)は、イネーブル信号ENB8と、信号SR16Lとの論理積を出力する回路である。第17段の出力回路232(17)は、信号を出力しない。第18段の出力回路232(18)は、イネーブル信号ENB1と、信号SR18Lとの論理積を出力する回路である。

【0054】

図12は、走査線駆動回路330の構成を示す図である。走査線駆動回路330は、入力される制御信号に従って、奇数行の走査線112を選択するための走査信号Gを出力する回路である。制御信号としては、スタートパルス信号SPY2、クロック信号CKY、およびイネーブル信号ENB1〜ENB8が用いられる。走査線駆動回路330は、シフトレジスター331と出力回路332とを有する。シフトレジスター331の構成は、シフトレジスター231と同様である。出力回路332は、出力回路132とほぼ同様の構成を有するが、偶数行の走査線112と接続されていない点が出力回路132と異なっている。シフトレジスター331の出力信号は、信号SRiRのように添字Rを用いる。

【0055】

出力回路332(i)は、信号SRiRと、イネーブル信号ENBrとの論理積を出力する回路である。ここで、rは、偶数行(すなわちiが偶数のとき)についてはi/2をbで除算したときの剰余、すなわちr=i mod bである。奇数行については、rは、1つ後の偶数行と同じ値である。例えば、b=8の場合を考える。第1段の出力回路332(1)は、イネーブル信号ENB1と、信号SR1Rとの論理積を出力する回路である。第2段の出力回路332(2)は、信号を出力しない。第3段の出力回路332(3)は、イネーブル信号ENB2と、信号SR3Rとの論理積を出力する回路である。第4段の出力回路332(4)は、信号を出力しない。第15段の出力回路332(15)は、イネーブル信号ENB8と、信号SR15Rとの論理積を出力する回路である。第16段の出力回路332(16)は、信号を出力しない。第17段の出力回路332(17)は、イネーブル信号ENB1と、信号SR17Rとの論理積を出力する回路である。第18段の出力回路232(18)は、信号を出力しない。第19弾の出力回路332(19)は、イネーブル信号ENB1と、信号SR19Rとの論理積を出力する回路である。

【0056】

図13は、走査線駆動回路230および走査線駆動回路330のタイミングチャートを例示する図である。この例では、イネーブル信号ENB1〜ENB8と、信号SR1LおよびSR2Rと、走査信号G1〜G12のみ図示されている。この例では、同一のイネーブル信号についてみると、Hレベルとなる番地は、2クロック毎に1番地ずつ移動している。例えば、イネーブル信号ENB1について、Hレベルとなる番地は、第1クロックから順に、第1番地、第1番地、第8番地、第8番地、第7番地、第7番地、第6番地、第6番地、第5番地、第5番地、第4番地、第4番地、第3番地、第3番地、第2番地、第2番地、第1番地、第1番地、第8番地、…というように変化している。また、同一のクロックについてみると、Hレベルとなる番地は、イネーブル信号によって異なっている。例えば、第1クロックについて、イネーブル信号ENB1〜8がHレベルとなる番地は、それぞれ、第1番地〜第8番地である。

【0057】

信号SRiLは、スタートパルス信号SPY1が転送される信号である。信号SRiRは、スタートパルス信号SPY2が転送される信号である。図13では、これらのうち信号SR1RおよびSR2Lのみが示されている。例えば、第1クロックにおいてスタートパルス信号SPY1およびSPY2が入力されると、信号SR1RがHレベルになる。第1クロックにおいて信号SR1RがHレベルであり、このときイネーブル信号ENB1は第1番地においてHレベルであるので、走査信号G1は第1番地においてHレベルとなる。第2クロックにおいて信号SR2LがHレベルであり、このときイネーブル信号ENB1は第1番地においてHレベルであるので、走査信号G2は第1番地においてHレベルとなる。第3クロックにおいて信号SR3RがHレベルであり、このときイネーブル信号ENB2は第1番地においてHレベルであるので、走査信号G3は第1番地においてHレベルとなる。走査信号G4以降の信号は順次、第1番地においてHレベルとなる。

【0058】

別の例で、第3クロックにおいてスタートパルス信号SPY2が入力されると(このときスタートパルス信号SPY1は入力されない)、信号SR1RがHレベルになる。第3クロックにおいて信号SR1RがHレベルであり、このときイネーブル信号ENB1は第8番地においてHレベルであるので、走査信号G1は第8番地においてHレベルとなる。第2クロックにおいて信号SR2LはLレベルであり、走査信号G2はLレベルのままである。第3クロックにおいて信号SR3RがHレベルであり、このときイネーブル信号ENB2は第8番地においてHレベルであるので、走査信号G3は第8番地においてHレベルとなる。第4クロックにおいて信号SR4LはLレベルであり、走査信号G4はLレベルのままである。以降、奇数行の走査信号Giは順次、第8番地においてHレベルとなる。偶数行の走査信号GiはLレベルのままである。

【0059】

さらに別の例で、第4クロックにおいてスタートパルス信号SPY1が入力されると(このときスタートパルス信号SPY2は入力されない)、第5クロックにおいて信号SR2LがHレベルになる。第5クロックにおいて信号SR2LがHレベルであり、このときイネーブル信号ENB1は第7番地においてHレベルであるので、走査信号G2は第7番地においてHレベルとなる。第6クロックにおいて信号SR3RはLレベルであり、走査信号G3はLレベルのままである。第7クロックにおいて信号SR4LがHレベルであり、このときイネーブル信号ENB2は第7番地においてHレベルであるので、走査信号G4は第7番地においてHレベルとなる。以降、偶数行の走査信号Giは順次、第7番地においてHレベルとなる。奇数行の走査信号GiはLレベルのままである。

【0060】

このように、本実施形態によれば、R画素およびB画素の走査と、G画素の走査とを異なるスタートパルス信号を用いて、それぞれ独立に開始させることができる。

【0061】

図14は、第1実施形態と第2実施形態のサブフィールド構成の相違を説明する図である。第1実施形態においては、G画素のサブフィールド長は、SF1G、SF2G、およびSF6Gは、それぞれ、SF1、SF2、およびSF4とサブフィールド長が等しく、また、SF3G、SF4G、およびSF5Gのサブフィールド長の合計は、SF3に等しいという制限があった。すなわち、SCAN4およびSCAN5の開始タイミングは任意に設計できるが、SCAN1、SCAN2、SCAN3、およびSCAN6の開始タイミングは、R画素およびB画素の走査と共通にしなければならなかった。

【0062】

これに対し第2実施形態においては、R画素およびB画素とG画素とで、サブフィールドの基本単位の長さが同一である限りにおいては、R画素およびB画素のサブフィールド構成とG画素のサブフィールド構成とを、それぞれ独自に設定することができる。すなわち、最初の走査(SCAN1)が共通であれば、R画素およびB画素の走査(SCAN3、SCAN5、およびSCAN8)の開始タイミングと、G画素の走査(SCAN2、SCAN4、SCAN6、およびSCAN7)の開始タイミングとを異ならせることができる。このように、第2実施形態においては、第1実施形態と比較してサブフィールド構成の自由度を向上させることができる。

【0063】

3.変形例

本発明は上述の実施形態に限定されるものでなく、種々の変形実施が可能である。以下、変形例をいくつか説明する。以下の変形例のうち、2つ以上のものが組み合わせて用いられてもよい。

【0064】

3−1.変形例1

図15は、変形例1に係る液晶パネル100の構成を示す図である。図15は、第1実施形態の液晶パネル100の変形例を示す図である。変形例1において、第1行および第(m+1)行の走査線112には、それぞれn/2個のダミー画素が接続されている(図において斜線で示している)。これは以下の理由による。第1実施形態の液晶パネル100において、第1行および第(m+1)行の走査線112に接続されている負荷(TFT116および画素電極118)の数は、他の走査線112の半分である。このように負荷の数が異なると、階調に悪影響を与える場合がある。この悪影響を回避するため、第1行および第(m+1)行の走査線112に、ダミー画素を接続してもよい。ダミー画素とは、構造は画素111と同様であるが、画像の表示に貢献しない画素をいう。ダミー画素により負荷の差を低減することにより、階調に与える悪影響を低減することができる。

【0065】

3−2.変形例2

ベイヤー配置の具体例は、実施形態で説明したものに限定されない。ベイヤー配置において、第1色、第2色、および第3色の画素が、2行2列の4画素を基本単位として配置される。基本単位には、第1色の画素が2つ、第2色および第3色の画素が1つずつ含まれる。第1色の画素は、基本単位において斜めに配置される。実施形態において、第1色がG、第2色がR、第3色がBである例を説明したが、各色はこれに限定されない。

【0066】

3−3.変形例3

電気光学装置10における画素111の配置は、図2で例示したものに限定されない。図2の配置においては、第1行の走査線112に接続されている負荷(TFT116および画素電極118)および第(m+1)行の走査線112に接続されている負荷の数は、第2行〜第m行の走査線112に接続されている負荷の半分である。このように負荷の数が異なると、階調に悪影響を与える場合がある。この悪影響を回避するため、第1行および第(m+1)行の走査線112に、ダミー画素を接続してもよい。ダミー画素とは、構造は画素111と同様であるが、画像の表示に貢献しない画素をいう。ダミー画素により負荷の差を低減することにより、階調に与える悪影響を低減することができる。

【0067】

3−4.他の変形例

本発明に係る電子機器はプロジェクターに限定されない。テレビジョン、ビューファインダー型・モニター直視型のビデオテープレコーダー、カーナビゲーション装置、ページャー、電子手帳、電卓、ワードプロセッサー、ワークステーション、テレビ電話、POS端末、デジタルスチルカメラ、携帯電話機、タッチパネルを備えた機器等に本発明が用いられてもよい。

【0068】

電気光学装置10の構成は、実施形態で説明したものに限定されない。えば、電気光学装置10において用いられる電気光学素子は、液晶素子120に限定されない。液晶素子120に代わり、有機EL(Electro-Luminescence)素子等、他の電気光学素子が用いられてもよい。また、電気光学装置10が、実施形態で説明した映像処理回路20を有していてもよい。

【0069】

実施形態で説明したパラメーター(例えば、サブフィールド数やフレーム速度、画素数など)および信号の極性やレベルはあくまで例示であり、本発明はこれに限定されない。

【符号の説明】

【0070】

1…電子機器、10…電気光学装置、20…映像処理回路、100…液晶パネル、101…表示領域、105…液晶層、108…コモン電極、111…画素、112…走査線、114…データ線、116…TFT、118…画素電極、120…液晶素子、125…容量素子、130…走査線駆動回路、131…シフトレジスター、132…出力回路、140…データ線駆動回路、141…シフトレジスター、142…第1ラッチ回路、143…第2ラッチ回路、230…走査線駆動回路、231…シフトレジスター、232…出力回路、330…走査線駆動回路、331…シフトレジスター、332…出力回路、1311…シフト回路、13111…クロックドインバーター、13112…クロックドインバーター、13113…インバーター

【技術分野】

【0001】

本発明は、ベイヤー配置された複数の画素をサブフィールド駆動する技術に関する。

【背景技術】

【0002】

液晶素子等の電気光学素子における階調制御方法として、電気光学素子に印加される電圧を変調する電圧変調方式の他、電気光学素子に一定電圧が印加される時間を変調する、いわゆるサブフィールド駆動方式が知られている。サブフィールド駆動方式において、1フレームは複数のサブフィールドに分割される。複数のサブフィールドのうち電圧印加をオンするサブフィールドとオフするサブフィールドとの組み合わせ(正確には順列)により、電気光学素子の階調が制御される。

【0003】

サブフィールド駆動において階調表現を向上させる手法の一つに、一つのサブフィールドを短くするものがある。サブフィールドを短くする技術としては、いわゆる領域走査駆動が知られている(特許文献1)。

【0004】

赤(R)、緑(G)、および青(B)の3原色を2次元的に配置する方法として、いわゆるベイヤー配置が知られている(特許文献2)。ベイヤー配置は、RおよびB各1画素、G2画素を1組とした配置である。ベイヤー配置では、単位面積あたり、GはRおよびBの2倍の情報量を有する。これは人間の視感度特性を考慮したものである。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2004−177930号公報

【特許文献2】米国特許第3971065号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

ベイヤー配置された画素を有する電気光学装置においてホワイトバランスをとるには、Gの画素の輝度をRおよびBの画素の輝度の半分にすることが考えられる。これをサブフィールド駆動方式で実現しようとすると、Gの画素において1フレームのほぼ半分の期間を輝度ゼロの状態にする必要がある。これは、Gの画素において階調表現に使えるサブフィールド数がRおよびBの画素よりも少なくなることを意味する。すなわち、Gの階調表現力が低下してしまう。

これに対し本発明は、ベイヤー配置された画素を有する電気光学装置においてサブフィールド方式を用いる場合において、階調表現能力の低下を抑制する技術を提供する。

【課題を解決するための手段】

【0007】

本発明は、第1色の画素が2つ、第2色の画素、および第3色の画素がベイヤー配置された複数の画素と、前記複数の画素のうち前記第1色の画素を選択するための複数の走査線を含む第1走査線群と、前記複数の画素のうち前記第2色および前記第3色の画素を選択するための複数の走査線を含む第2走査線群と、単位期間を区分したa個のサブ期間のうち走査に用いられる一のサブ期間を選択するためのb系統のイネーブル信号(b≧a)に応じて、前記第1走査線群および前記第2走査線群の中から順次一の走査線を選択する第1走査、および前記第1走査線群の中から順次一の走査線を選択する第2走査のいずれかの走査を行う走査線駆動回路とを有する電気光学装置を提供する。

この電気光学装置によれば、第1走査線群の走査と第2走査線群の走査とが分離していない構成と比較して、階調表現能力の低下を抑制することができる。

【0008】

好ましい態様において、前記イネーブル信号は、連続する2つの単位期間において同一のサブ期間を選択するための波形を有し、前記a個のサブ期間のうち、前記第2走査に用いられるサブ期間については、前記連続する2つの単位期間の一方においてのみ選択するための波形を有してもよい。

この電気光学装置によれば、イネーブル信号を変形することにより、第1走査線群の走査と第2走査線群の走査とを分離させることができる。

【0009】

別の好ましい態様において、前記複数の画素は、m行n列のマトリクス状に配置され、前記第1走査線群および前記第2走査線群は、あわせて(m+1)本の走査線を有し、前記第1走査線群の走査線と、前記第2走査線群の走査線とは、交互に配置され、前記走査線駆動回路は、スタートパルス信号を1段ずつ転送させた信号を出力する(m+1)段のシフトレジスターと、前記シフトレジスターの出力信号と、前記b系統のイネーブル信号のうち対応する一のイネーブル信号の論理積に応じた信号を出力する出力回路とを有してもよい。

この電気光学装置によれば、スタートパルス信号により走査を開始する場合において、階調表現能力の低下を抑制することができる。

【0010】

さらに別の好ましい態様において、b≦NSF1+NSF2−1(ただし、NSF1は前記第1色の画素におけるサブフィールド数を示し、NSF2は前記第2色の画素におけるサブフィールド数を示す)であってもよい。

この電気光学装置によれば、第2走査線群の走査が第1走査線群の走査と共通している構成と比較して、サブフィールド構成の自由度を向上させることができる。

【0011】

さらに別の好ましい態様において、前記複数の画素は、m行n列のマトリクス状に配置され、前記第1走査線群および前記第2走査線群は、あわせて(m+1)本の走査線を有し、前記第1走査線群の走査線と、前記第2走査線群の走査線とは、交互に配置され、前記走査線駆動回路は、第1スタートパルス信号を1段ずつ転送させた信号を出力する(m+1)段の第1シフトレジスターと、前記第1シフトレジスターの出力信号と、前記b系統のイネーブル信号のうち対応する一のイネーブル信号の論理積に応じた信号を、前記(m+1)行の走査線のうち奇数行または偶数行の一方に出力する第1出力回路と、第2スタートパルス信号を1段ずつ転送させた信号を出力する(m+1)段の第2シフトレジスターと、前記第2シフトレジスターの出力信号と、前記b系統のイネーブル信号のうち対応する一のイネーブル信号の論理積に応じた信号を、前記(m+1)行の走査線のうち奇数行または偶数行の他方に出力する第2出力回路とを有してもよい。

この電気光学装置によれば、スタートパルス信号により走査を開始する場合において、階調表現能力の低下を抑制することができる。

【0012】

さらに別の好ましい態様において、前記(m+1)本の走査線の各々に接続される画素の数が等しくてもよい。

この電気光学装置によれば、画素(負荷)の数が異なる場合と比較して、階調表現への悪影響を低減することができる。

【0013】

また、本発明は、上記いずれかの電気光学装置を有する電子機器を提供する。

この電子機器によれば、第1走査線群の走査と第2走査線群の走査とが分離していない構成と比較して、階調表現能力の低下を抑制することができる。

【0014】

さらに、本発明は、第1色の画素が2つ、第2色の画素、および第3色の画素がベイヤー配置された複数の画素と、前記複数の画素のうち前記第1色の画素を選択するための複数の走査線を含む第1走査線群と、前記複数の画素のうち前記第2色および前記第3色の画素を選択するための複数の走査線を含む第2走査線群とを有する電気光学装置の制御方法であって、単位期間を区分したa個のサブ期間のうち走査に用いられる一のサブ期間を選択するためのb系統のイネーブル信号(b≧a)に応じて、前記第1走査線群および前記第2走査線群の中から順次一の走査線を選択する第1走査、および前記第1走査線群の中から順次一の走査線を選択する第2走査のいずれかの走査を行うステップを有する制御方法を提供する。

この制御方法によれば、第1走査線群の走査と第2走査線群の走査とが分離していない構成と比較して、階調表現能力の低下を抑制することができる。

【図面の簡単な説明】

【0015】

【図1】第1実施形態に係る電子機器1の概要を示す図。

【図2】液晶パネル100の回路構成を示すブロック図。

【図3】画素111の等価回路を示す図。

【図4】画素と走査線との対応関係を示す図。

【図5】走査線駆動回路130の構成を示す図。

【図6】シフト回路1311の構成を示す図。

【図7】データ線駆動回路140の構成を示す図。

【図8】走査線駆動回路130の動作の概要を説明する図。

【図9】走査線駆動回路130のタイミングチャートを例示する図。

【図10】第2実施形態に係る液晶パネル100の構成を示す図。

【図11】走査線駆動回路230の構成を示す図。

【図12】走査線駆動回路330の構成を示す図。

【図13】第2実施形態に係る走査線駆動回路タイミングチャートを例示する図。

【図14】第1実施形態と第2実施形態のサブフィールド構成の相違を説明する図。

【図15】変形例1に係る液晶パネル100の構成を示す図。

【発明を実施するための形態】

【0016】

1.第1実施形態

1−1.構成

図1は、第1実施形態に係る電子機器1の概要を示す図である。電子機器1は、映像を表示する装置、この例ではプロジェクターである。「映像」とは、静止画および動画を含む概念である。電子機器1は、上位装置から供給される映像信号Vid−inにより示される画像を、同期信号Syncに基づいたタイミングで、液晶パネル100に表示する装置である。

【0017】

電子機器1は、電気光学装置10と、映像処理回路20とを有する。電気光学装置10は、液晶パネル100(電気光学パネルの一例)と、制御回路と、光源と、光学系(液晶パネル100以外は図示略)とを有する。液晶パネル100は、m行n列のマトリクス状に配置された複数の画素を有する。液晶パネル100はカラー液晶パネルであり、赤(R)、緑(G)、および青(B)の3原色の画素を有する。

【0018】

R、G、およびBの画素は、ベイヤー配置されている。ベイヤー配置において、R、G、およびBの画素は、2行2列の4画素を単位(以下「単位領域」という)として配置されている。単位領域には、R画素およびB画素が各1つ、G画素が2つ含まれる。2つのG画素は、斜めに配置されている。

【0019】

映像処理回路20は、入力された画像データに対して画像処理、例えばモザイキング処理を行う。以下、入力された画像データを「入力画像データ」といい、入力画像データにより示される画像を「入力画像」という。入力画像データは、1画素につき、R、G、およびBの3つの色成分を含んでいる。いま、入力画像の画素数がm×n個、すなわち液晶パネル100の画素数と等しい場合を考える。この場合、RおよびBについては、液晶パネル100の画素数は入力画像の1/4、Gについては、液晶パネル100の画素数は入力画像の1/2である。例えばRについて考えると、入力画像の4画素のデータを1画素のデータに変換する処理(モザイキング処理)が必要である。モザイキング処理のアルゴリズムとしては種々のものが知られており、ここではどのようなアルゴリズムが用いられてもよい。

【0020】

図2は、液晶パネル100の回路構成を示すブロック図である。液晶パネル100は、供給される信号に応じた画像を表示する装置である。液晶パネル100は、表示領域101と、走査線駆動回路130と、データ線駆動回路140とを有する。表示領域101には、複数の画素111が配置されている。この例では、m行n列の画素111がマトリクス状に配置されている。液晶パネル100は、素子基板100aと、対向基板100bと、液晶層105とを有する。素子基板100aおよび対向基板100bは一定の間隔を保って貼り合わせられている。素子基板100aおよび対向基板100bの間隙には、液晶層105が挟まれている。素子基板100aには、(m+1)本の走査線112およびn本のデータ線114が設けられている。走査線112およびデータ線114は、対向基板100bと対向する面に設けられている。走査線112とデータ線114とは、電気的に絶縁されている。走査線112とデータ線114との交差に対応して、画素111が設けられている。以下において、複数の走査線112を区別する場合には、図2において上から順に、第1、第2、第3、…、第(m−1)、第m行の走査線112という。同様に、複数のデータ線114を区別する場合には、図2において左から順に、第1、第2、第3、…、第(n−1)、第n列のデータ線114という。なお、図8において、素子基板100aの対向面は紙面裏側であるので、この対向面に設けられる走査線112、およびデータ線114ついては破線で示すべきであるが、見難くなるので、それぞれ実線で示している。

【0021】

対向基板100bには、コモン電極108が設けられている。コモン電極108は、素子基板100aと対向する1面に設けられている。コモン電極108は、すべての画素111について共通である。すなわち、コモン電極108は、対向基板100bのほぼ全面にわたって設けられている、いわゆるベタ電極である。

【0022】

液晶パネル100は、さらに、複数のイネーブル信号線、この例では6本のイネーブル信号線ENB1〜ENB6を有する。イネーブル信号については後述する。

【0023】

図3は、画素111の等価回路を示す図である。画素111は、TFT116、液晶素子120、および容量素子125を有する。TFT116は、液晶素子120への電圧の印加を制御するスイッチング手段の一例であり、この例ではnチャネル型の電界効果トランジスターである。液晶素子120は、印加される電圧に応じて光学状態が変化する素子である。この例で、液晶パネル100は透過型の液晶パネルであり、変化する光学状態は透過率である。液晶素子120は、画素電極118、液晶層105、およびコモン電極108を有する。第i行第j列の画素111において、TFT116のゲートおよびソースは、それぞれ、第i行の走査線112および第j列のデータ線114に接続されている。TFT116のドレインは、画素電極118に接続されている。容量素子125は、画素電極118に書き込まれた電圧を保持する素子である。容量素子125の一端は画素電極118に接続されており、他端は容量線Vcomに接続されている。

【0024】

第i行の走査線112にHレベルの電圧を示す信号が入力されると、TFT116のソース・ドレイン間は導通する。TFT116のソース・ドレイン間が導通すると、画素電極118は、(TFT116のソース・ドレイン間のオン抵抗を無視すれば)第j列のデータ線114と同電位になる。第j列のデータ線114には、映像信号Vid−inに応じて、第i行第j列の画素111の階調値に応じた電圧(以下、「データ電圧」といい、データ電圧を示す信号を「データ信号」という)が印加される。コモン電極108には、図示しない回路により、共通電位LCcomが与えられる。容量線Vcomには、図示しない回路により、時間的に一定の電位Vcom(この例では、Vcom=LCcom)が与えられる。すなわち、液晶素子120には、データ電圧と共通電位LCcomとの差に応じた電圧が印加される。以下、液晶層105がVA(Vertical Alignment)型であり、電圧無印加時において液晶素子120の階調が暗状態(黒状態)となるノーマリーブラックモードである例を用いて説明する。なお、特に説明しない限り、図示を省略した接地電位を電圧の基準(ゼロV)とする。

【0025】

液晶パネル100はサブフィールド駆動されるので、液晶素子120に印加される電圧の絶対値は、VH(第1電圧の一例、例えば5V)またはVL(第2電圧の一例、例えばゼロV)の2値のいずれかである。

【0026】

図4は、画素と走査線との対応関係を示す図である。この例で、G画素は奇数行(第(2k+1)行:kはゼロを含む自然数)の走査線112に、R画素およびB画素は偶数行(第(2k+2)行)の走査線112に、それぞれ接続されている。すなわち、奇数行の走査線112を選択するとG画素のみを選択し(R画素およびB画素を選択せず)、偶数行の走査線112を選択するとR画素およびB画素のみを選択する(G画素を選択しない)ことができる。奇数行の走査線112は、第1走査線群の一例であり、偶数行の走査線112は第2走査線群の一例である。

【0027】

図5は、走査線駆動回路130の構成を示す図である。走査線駆動回路130は、入力される制御信号に従って、走査線112を選択するための走査信号Gを出力する回路である。制御信号としては、スタートパルス信号SPY、クロック信号CKY、およびイネーブル信号ENB1〜ENB6が用いられる。第i行の走査線112に供給される走査信号を、走査信号Giという。走査信号Giは、m本の走査線112の中から一の走査線112を選択するための信号である。走査信号Giは、選択される走査線112に対しては選択電圧(Hレベル)となり、それ以外の走査線112に対しては非選択電圧(Lレベル)となる信号である。選択電圧を示す信号を選択信号といい、非選択電圧を示す信号を非選択信号という。

【0028】

この例において、走査線駆動回路130は、単一のクロックにおいて複数の走査線112を選択する。より詳細には、1クロックはさらに複数の期間に区分されており(以下この細分化された期間を「番地」といい、サブ期間の一例である)、単一の番地において単一の走査線112が選択される。1クロックがa個の番地で構成される場合、1クロックで最大a本の走査線112を選択することができる。イネーブル信号は、a個の番地のうち使用される番地を特定するための信号である。この例で、液晶パネル100は6本のイネーブル信号線ENB1〜ENB6を有するので、1クロックは6番地に区分される(a=6)。

【0029】

走査線駆動回路130は、シフトレジスター131と、出力回路132とを有する。シフトレジスター131は、スタートパルス信号SPYを、クロック信号CKYにより示されるクロック毎に、1段(1行)ずつ転送(シフト)する回路である。シフトレジスター131は、(m+1)段のシフト回路1311を有する。第i段のシフト回路1311を、シフト回路1311(i)と表す。他の要素についても同様である。各シフト回路1311は、走査線112と一対一に対応している。

【0030】

図6は、シフト回路1311の構成を示す図である。シフト回路1311は、クロックドインバーター13111、クロックドインバーター13112、およびインバーター13113を有する。奇数段のクロックドインバーター13111は、クロック信号CKがHレベルのときにインバーターとして機能し、クロック信号CKがLレベルのときに高インピーダンスとなる回路である。クロックドインバーター13112は、クロック信号CKBがHレベルのときにインバーターとして機能し、クロック信号CKがLレベルのときに高インピーダンスとなる回路である。

【0031】

奇数段のシフト回路1311(i)には、クロック信号CKとしてクロック信号CKYが、クロック信号CKBとしてクロック信号CKYの反転信号が、それぞれ入力される。偶数段のシフト回路1311(i+1)には、クロック信号CKとしてクロック信号CKYの反転信号が、クロック信号CKBとしてクロック信号が、それぞれ入力される。クロック信号CKYがHレベルのとき、奇数段のシフト回路1311(i)の入力INに入力した入力信号に応じた出力信号を出力OUTに出力する。奇数段のシフト回路1311(i)の入力INの電位がHレベルになっていれば、出力OUTの電位もHレベルである。このとき、次段(偶数段)のシフト回路1311(i+1)は高インピーダンス状態である。クロック信号CKYが反転してLレベルになると、シフト回路1311(i)は高インピーダンス状態になり、シフト回路1311(i+1)の入力INに入力した入力信号に応じた出力信号を出力OUTに出力する。前のクロックでシフト回路1311(i)の出力OUTがHレベルであれば、シフト回路1311(i+1)の出力OUTがHレベルになる。このようにして、Hレベルの信号が1クロックずつ後段のシフト回路1311に転送される。

【0032】

再び図5を参照する。シフトレジスター131と出力回路132との間には、NAND回路133およびインバーター134が設けられている。NAND回路133およびインバーター134は、シフト回路1311と一対一に対応している。第i段のNAND回路133およびインバーター134を、NAND回路133(i)およびインバーター134(i)と表す。NAND回路133(i)には、シフト回路133(i)の入力INおよび出力OUTが入力される。インバーター134(i)は、NAND回路133(i)の出力を反転する。インバーター134(i)から出力される信号を、信号SRiと表す。信号SRiは、スタートパルス信号SPYが第i段に転送された場合にHレベルとなり、それ以外の場合はLレベルとなる信号である。

【0033】

出力回路132(i)は、信号SRiと、イネーブル信号ENBrとの論理積を出力する回路である。ここで、rは、偶数行(すなわちiが偶数のとき)についてはi/2をaで除算したときの剰余、すなわちr=((i/2) mod a)である(ただし((i/2) mod a)=0の場合、r=a)。奇数行(すなわちiが奇数のとき)については、1行前(すなわち第(i−1)行)のrと同じ値である。例えば、a=6の場合を考える。第1段の出力回路132(1)は、イネーブル信号ENB1と、信号SR1との論理積を出力する回路である。第2段の出力回路132(2)は、イネーブル信号ENB1と、信号SR2との論理積を出力する回路である。第3段の出力回路132(3)は、イネーブル信号ENB2と、信号SR3との論理積を出力する回路である。第12段の出力回路132(12)は、イネーブル信号ENB6と、信号SR12との論理積を出力する回路である。第13段の出力回路132(13)は、イネーブル信号ENB1と、信号SR13との論理積を出力する回路である。第14段の出力回路132(14)は、イネーブル信号ENB1と、信号SR14との論理積を出力する回路である。

【0034】

図7は、データ線駆動回路140の構成を示す図である。データ線駆動回路140は、入力される制御信号に従ってデータ信号DATをサンプリングし、画素111に書き込まれるデータ電圧を示すデータ信号Sを出力する回路である。第j列のデータ線114に供給されるデータ信号を、データ信号Sjという。制御信号としては、スタートパルス信号SPY、クロック信号CKX、およびラッチ信号LATが用いられる。なお図7中では第2ラッチ回路143の内部に、データ線Sjへの電圧出力回路部を含むものとして省略して記載している。本願の本質の説明では電圧出力回路部の詳細は省略しても問題ない。

【0035】

データ線駆動回路140は、シフトレジスター141と、第1ラッチ回路142と、第2ラッチ回路143とを有する。シフトレジスター141は、スタートパルス信号SPXを、クロック信号CKXにより示されるクロック毎に1段(1列)ずつ転送する回路である。第1ラッチ回路142は、データ信号DATを、シフトレジスター141からの出力信号により示されるタイミングでラッチする回路である。データ信号DATは点順次のデータであり、第1ラッチ回路142は、各画素のデータを順次ラッチする。第2ラッチ回路143は、信号LATにより示されるタイミングで第1ラッチ回路142からの出力信号をラッチし、線順次のデータ信号Sjとしてデータ線114に出力する回路である。データ信号Sjは、サブフィールドコードがオンのときは電圧VHを示し、サブフィールドコードがオフのときは電圧VLを示す。

【0036】

映像処理回路20は、入力映像データに基づいて、データ信号DATおよび制御信号を生成する回路である(制御回路の一例)。映像処理回路20はにより生成された制御信号が、走査線駆動回路130およびデータ線駆動回路140に入力される。この例で、映像処理回路20は、モザイキング処理およびサブフィールドコード変換処理を行う。モザイキング処理は、1画素につきR、G、およびBの3つの色成分を含んでいる入力画像のデータを、ベイヤー配置された画素の階調値を示すデータに変換する処理である。

【0037】

サブフィールドコード変換処理は、モザイキング処理後の各画素の階調値をサブフィールドコードに変換する処理である。サブフィールドは、例えば、基本単位(4SFまたは6SF)を所定回数繰り返す構成を有している。例えば、1フレームにおいて基本単位が5回繰り返される場合において、基本単位が4SF(R画素およびB画素)であったときは、1フレームは20SFで構成される。この場合、サブフィールドコードは各サブフィールドについてオンおよびオフのいずれかを示す20ビットのデータである。また、この場合において、基本単位が6SF(G画素)であったときは、1フレームは30SFで構成される。この場合、サブフィールドコードは30ビットのデータである。この例で、サブフィールドコード変換処理は、変換テーブル(図示略)を参照して行われる。変換テーブルは、例えば映像処理回路20の内蔵メモリに記憶されている。

【0038】

1−2.動作

図8は、走査線駆動回路130の動作の概要を説明する図である。図8において、横軸は時間を、縦軸は選択される行を示している。図面が煩雑になるのを避けるため、図8では、番地については考慮せず、同時に複数の走査線112が選択されるように描かれている。RおよびBの画素は、実線(SCAN1、SCAN2、SCAN3、およびSCAN6)のとおり選択され、データが書き込まれる。すなわち、RおよびBの画素について、サブフィールドの基本単位は4サブフィールド(SF1〜SF4)により構成される。Gの画素は、実線に加え、破線(SCAN4およびSCAN5)のとおり選択され、データが書き込まれる。すなわち、Gの画素について、サブフィールドの基本単位は6サブフィールド(SF1G〜SF6G)により構成される。

【0039】

この例で、仮にG画素のみの走査を行わなかった場合、サブフィールド数は、すべての色の画素について、SF1〜SF4の4つである。この条件で、Gの輝度をRおよびBの半分にするには、G画素では例えば常にSF4をオフにすることになる。すると階調表現に使えるサブフィールド数は3つになってしまう。サブフィールド駆動方式においては、理論的には、2k通りの階調表現が可能である(kはサブフィールド数)。したがって、階調表現に使えるサブフィールド数が一つ減ると、理論的には、階調表現能力は半分になってしまう。これに対し、G画素のみの走査を用いれば、以下で説明するように階調表現能力の低下を抑制することができる。

【0040】

図9は、走査線駆動回路130のタイミングチャートを例示する図である。この例では、イネーブル信号ENB1〜ENB6と、出力信号SR1と、走査信号G1〜G12のみ図示している。クロック信号CKYは、HレベルとLレベルが交互に切り換わる信号である。HレベルとLレベルの切り換わりのタイミングが、クロックの始期を示している。イネーブル信号ENB1〜6は、1クロックのうち使用する番地を示す信号である。イネーブル信号がHレベルになっている期間が、使用する番地を示している。例えば、第1クロックおよび第2クロックにおいて、イネーブル信号ENB1は、第1番地においてHレベルになっている。同一のイネーブル信号についてみると、Hレベルとなる番地は、原則として2クロック毎に1番地ずつ移動している。例えば、イネーブル信号ENB1について、Hレベルとなる番地は、第1クロックから順に、第1番地、第1番地、第6番地、なし、第5番地、第5番地、第4番地、第4番地、第3番地、第3番地、第2番地、第2番地、第1番地、第1番地、第6番地、…というように変化している。ここで、同一の番地が2クロック連続しているが、第6番地については、連続する2クロックのうち1クロックでしかHレベルになっていない。この点については後述する。また、同一のクロックについてみると、Hレベルとなる番地は、イネーブル信号によって異なっている。例えば、第1クロックについて、イネーブル信号ENB1〜6がHレベルとなる番地は、それぞれ、第1番地〜第6番地である。

【0041】

信号SRiは、スタートパルス信号SPYが転送される信号である。図9では、このうち信号SR1のみが示されている。スタートパルス信号SPYが入力されないとき(Lレベルのとき)は、信号SRiはLレベルである。スタートパルス信号が入力されると、Hレベルの状態が信号SR1から順に転送される。信号SRiがHレベルであるクロックのうち、対応するイネーブル信号がHレベルである番地において、走査信号GiはHレベルとなる。例えば、第1クロックにおいてスタートパルス信号SPYが入力されると、信号SR1がHレベルになる。第1クロックにおいて信号SR1がHレベルであり、このときイネーブル信号ENB1は第1番地においてHレベルであるので、走査信号G1は第1番地においてHレベルとなる。第2クロックにおいて信号SR2がHレベルであり、このときイネーブル信号ENB1は第1番地においてHレベルであるので、走査信号G2は第1番地においてHレベルとなる。第3クロックにおいて信号SR3がHレベルであり、このときイネーブル信号ENB2は第1番地においてHレベルであるので、走査信号G3は第1番地においてHレベルとなる。走査信号G4以降の信号は順次、第1番地においてHレベルとなる。

【0042】

別の例で、第5クロックにおいてスタートパルス信号SPYが入力されると、信号SR1がHレベルになる。第5クロックにおいて信号SR1がHレベルであり、このときイネーブル信号ENB1は第5番地においてHレベルであるので、走査信号G1は第5番地においてHレベルとなる。走査信号G2以降の信号は順次、第5番地においてHレベルとなる。

【0043】

さらに別の例で、第11クロックにおいてスタートパルス信号SPYが入力されると、信号SR1がHレベルになる。第11クロックにおいて信号SR1がHレベルであり、このときイネーブル信号ENB1は第2番地においてHレベルであるので、走査信号G1は第2番地においてHレベルとなる。走査信号G2以降の信号は順次、第2番地においてHレベルとなる。

【0044】

既に説明したように、走査線駆動回路130は、a個(この例では6つ)の走査を並列させることができる。第1番地を使って走査をするときは、第1行に対応するイネーブル信号(この例ではイネーブル信号ENB1)が第1番地においてHレベルとなるクロックにおいて、スタートパルス信号SPYを入力すればよい。

【0045】

この例では、第6番地は連続する2クロックのうち一方(この例では先のクロック)でのみHレベルとなり、他方のクロック(この例では後のクロック)ではLレベルのままである(図において対応する箇所に「NO」という記号を付している)。第15クロックにおいてスタートパルス信号SPYが入力されると、信号SR1がHレベルになる。第15クロックにおいて信号SR1がHレベルであり、このときイネーブル信号ENB1は第6番地においてHレベルであるので、走査信号G1は第6番地においてHレベルとなる。第16クロックにおいて信号SR2がHレベルであり、このときイネーブル信号ENB1はすべての番地においてLレベルである。したがって、走査信号G2は非選択信号のままであり、選択信号は出力されない。第17クロックにおいてにおいて信号SR3がHレベルであり、このときイネーブル信号ENB2は第6番地においてHレベルであるので、走査信号G3は第6番地においてHレベルとなる。第18クロックにおいて信号SR4がHレベルであり、このときイネーブル信号ENB1はすべての番地においてLレベルである。したがって、走査信号G4は非選択信号のままであり、選択信号は出力されない。以下同様にして、第15クロックにおいて入力されたスタートパルス信号に起因する走査は、奇数行のみを順次選択し、偶数行を選択しない走査である。すなわち、特定の走査線(この例ではG画素に対応する走査線112)のみが、順次選択される。

【0046】

図8のSCAN1、SCAN2、SCAN3、およびSCAN6の走査を行うときは、連続する2クロックで同一の番地がHレベルとなるイネーブル信号が用いられる。図8のSCAN4およびSCAN5の走査を行うときは、連続する2クロックのうち一方のクロックですべての番地がLレベルのままであるイネーブル信号が用いられる。映像処理回路20は、例えば、番地毎に使用/未使用を示すフラグを記憶することにより、番地の使用状況を把握している。映像処理回路20は、走査を開始する際、走査に使用する番を決定する。走査に使用する番地は未使用の番地(空き番地)の中から選択される。例えば、第6番地を使用することを決定した場合において、その走査がG画素のみを対象にするときは、映像処理回路20は、第6番地について、連続する2クロックのうち後のクロックにおいてLレベルのままとなるように変形したイネーブル信号を出力する。

【0047】

以上で説明したように本実施形態によれば、G画素に対応する走査線112のみを走査することができる。これにより、G画素とR画素およびB画素とのサブフィールド数を異ならせることができる。例えば、G画素の輝度をR画素およびB画素の半分にするとき。SF6Gを常にオフとしても、SF1G〜SF5Gの5つのサブフィールドを用いて階調表現をすることができる。すなわち、ベイヤー配置された画素を有する電気光学装置においてサブフィールド方式を用いる場合において、毎回、R画素、G画素、およびB画素をすべて走査するときと比較して、階調表現能力の低下を抑制することができる。

【0048】

なお、この例では、映像処理回路20は、SCAN1、SCAN2、SCAN3、およびSCAN6の走査と同期して、R画素、G画素、およびB画素のサブフィールドコードに応じたデータをデータ線駆動回路140に出力する。また、映像処理回路20は、SCAN4およびSCAN5の走査と同期して、G画素のSF4GおよびSF5Gのサブフィールドコードに応じたデータをデータ線駆動回路140に出力する。

【0049】

2.第2実施形態

図10は、第2実施形態に係る液晶パネル100の構成を示す図である。以下、第1実施形態と共通する事項については説明を省略する。第2実施形態において、液晶パネル100は、走査線駆動回路230および走査線駆動回路330の2つの走査線駆動回路を有する。走査線駆動回路230は、偶数行の走査線112、すなわち、R画素およびB画素に対応する走査線112に対し走査信号を出力する回路である。走査線駆動回路330は、奇数行の走査線112、すなわち、G画素に対応する112に対し走査信号を出力する回路である。また、液晶パネル100は、イネーブル信号ENB1〜ENB8の8系統のイネーブル信号を伝送するための8つのイネーブル信号線を有する。

【0050】

第1実施形態の構成においては、例えば図8で説明したように、R画素およびB画素とG画素とで共通する走査(例えば、SCAN1、SCAN2、SCAN3、およびSCAN6)については、共通のタイミングで走査を行っていた。しかし、例えば図8でG画素についてはSF6Gを常にオフにする場合には、他のサブフィールドについては、R画素およびB画素のサブフィールド長とは独立してサブフィールド長を設定できた方が、より高い階調表現能力を実現できる場合がある。第2実施形態の液晶パネル100は、このような動作が可能である。

【0051】

第2実施形態において、イネーブル信号線の数bは、次式により決定される。

b=NSF1+NSF2−NSFcom ・・・(1)

ここで、NSF1はG画素におけるサブフィールドの基本単位に含まれるサブフィールド数を、NSF2はR画素およびB画素における基本単位に含まれるサブフィールド数を、NSFcomは、R画素およびB画素とG画素とで共通の走査の数を示す。この例で、G画素の基本単位は5SFであり、R画素およびB画素のサブフィールドの基本単位は4SFである。また、フレームの始期を統一するため、第1番目の走査は共通である。すなわち、NSF1=6、NSF2=4、NSFcom=1である。以上を式(1)に代入すると、

b=5+4−1=8

である。したがって、第2実施形態において8系統のイネーブル信号が用いられている。なお、共通の走査の数NSFcomは、任意に設計が可能であるが、NSFcom≧1である。したがって、式(1)からbの最大値は、

b≦NSF1+NSF2−1 ・・・(2)

である。

【0052】

図11は、走査線駆動回路230の構成を示す図である。走査線駆動回路230は、入力される制御信号に従って、偶数行の走査線112を選択するための走査信号Gを出力する回路である。制御信号としては、スタートパルス信号SPY1、クロック信号CKY、およびイネーブル信号ENB1〜ENB8が用いられる。走査線駆動回路230は、シフトレジスター231と出力回路232とを有する。シフトレジスター231の構成は、シフトレジスター131と同様である。出力回路232は、出力回路132とほぼ同様の構成を有するが、奇数行の走査線112と接続されていない点が出力回路132と異なっている。

【0053】

出力回路232(i)は、信号SRiLと、イネーブル信号ENBrとの論理積を出力する回路である。シフトレジスター231の出力と後述するシフトレジスター331の出力とを区別するため、シフトレジスター231の出力信号は、信号SRiLのように添字Lを用いる。ここで、rは、偶数行(すなわちiが偶数のとき)についてはi/2をbで除算したときの剰余、すなわちr=((i/2) mod b)である(ただし((i/2) mod b)=0のときr=b)。例えば、b=8の場合を考える。第1段の出力回路232(1)は、信号を出力しない。第2段の出力回路232(2)は、イネーブル信号ENB1と、信号SR2Lとの論理積を出力する回路である。第3段の出力回路232(3)は、信号を出力しない。第16段の出力回路232(16)は、イネーブル信号ENB8と、信号SR16Lとの論理積を出力する回路である。第17段の出力回路232(17)は、信号を出力しない。第18段の出力回路232(18)は、イネーブル信号ENB1と、信号SR18Lとの論理積を出力する回路である。

【0054】

図12は、走査線駆動回路330の構成を示す図である。走査線駆動回路330は、入力される制御信号に従って、奇数行の走査線112を選択するための走査信号Gを出力する回路である。制御信号としては、スタートパルス信号SPY2、クロック信号CKY、およびイネーブル信号ENB1〜ENB8が用いられる。走査線駆動回路330は、シフトレジスター331と出力回路332とを有する。シフトレジスター331の構成は、シフトレジスター231と同様である。出力回路332は、出力回路132とほぼ同様の構成を有するが、偶数行の走査線112と接続されていない点が出力回路132と異なっている。シフトレジスター331の出力信号は、信号SRiRのように添字Rを用いる。

【0055】

出力回路332(i)は、信号SRiRと、イネーブル信号ENBrとの論理積を出力する回路である。ここで、rは、偶数行(すなわちiが偶数のとき)についてはi/2をbで除算したときの剰余、すなわちr=i mod bである。奇数行については、rは、1つ後の偶数行と同じ値である。例えば、b=8の場合を考える。第1段の出力回路332(1)は、イネーブル信号ENB1と、信号SR1Rとの論理積を出力する回路である。第2段の出力回路332(2)は、信号を出力しない。第3段の出力回路332(3)は、イネーブル信号ENB2と、信号SR3Rとの論理積を出力する回路である。第4段の出力回路332(4)は、信号を出力しない。第15段の出力回路332(15)は、イネーブル信号ENB8と、信号SR15Rとの論理積を出力する回路である。第16段の出力回路332(16)は、信号を出力しない。第17段の出力回路332(17)は、イネーブル信号ENB1と、信号SR17Rとの論理積を出力する回路である。第18段の出力回路232(18)は、信号を出力しない。第19弾の出力回路332(19)は、イネーブル信号ENB1と、信号SR19Rとの論理積を出力する回路である。

【0056】

図13は、走査線駆動回路230および走査線駆動回路330のタイミングチャートを例示する図である。この例では、イネーブル信号ENB1〜ENB8と、信号SR1LおよびSR2Rと、走査信号G1〜G12のみ図示されている。この例では、同一のイネーブル信号についてみると、Hレベルとなる番地は、2クロック毎に1番地ずつ移動している。例えば、イネーブル信号ENB1について、Hレベルとなる番地は、第1クロックから順に、第1番地、第1番地、第8番地、第8番地、第7番地、第7番地、第6番地、第6番地、第5番地、第5番地、第4番地、第4番地、第3番地、第3番地、第2番地、第2番地、第1番地、第1番地、第8番地、…というように変化している。また、同一のクロックについてみると、Hレベルとなる番地は、イネーブル信号によって異なっている。例えば、第1クロックについて、イネーブル信号ENB1〜8がHレベルとなる番地は、それぞれ、第1番地〜第8番地である。

【0057】

信号SRiLは、スタートパルス信号SPY1が転送される信号である。信号SRiRは、スタートパルス信号SPY2が転送される信号である。図13では、これらのうち信号SR1RおよびSR2Lのみが示されている。例えば、第1クロックにおいてスタートパルス信号SPY1およびSPY2が入力されると、信号SR1RがHレベルになる。第1クロックにおいて信号SR1RがHレベルであり、このときイネーブル信号ENB1は第1番地においてHレベルであるので、走査信号G1は第1番地においてHレベルとなる。第2クロックにおいて信号SR2LがHレベルであり、このときイネーブル信号ENB1は第1番地においてHレベルであるので、走査信号G2は第1番地においてHレベルとなる。第3クロックにおいて信号SR3RがHレベルであり、このときイネーブル信号ENB2は第1番地においてHレベルであるので、走査信号G3は第1番地においてHレベルとなる。走査信号G4以降の信号は順次、第1番地においてHレベルとなる。

【0058】

別の例で、第3クロックにおいてスタートパルス信号SPY2が入力されると(このときスタートパルス信号SPY1は入力されない)、信号SR1RがHレベルになる。第3クロックにおいて信号SR1RがHレベルであり、このときイネーブル信号ENB1は第8番地においてHレベルであるので、走査信号G1は第8番地においてHレベルとなる。第2クロックにおいて信号SR2LはLレベルであり、走査信号G2はLレベルのままである。第3クロックにおいて信号SR3RがHレベルであり、このときイネーブル信号ENB2は第8番地においてHレベルであるので、走査信号G3は第8番地においてHレベルとなる。第4クロックにおいて信号SR4LはLレベルであり、走査信号G4はLレベルのままである。以降、奇数行の走査信号Giは順次、第8番地においてHレベルとなる。偶数行の走査信号GiはLレベルのままである。

【0059】

さらに別の例で、第4クロックにおいてスタートパルス信号SPY1が入力されると(このときスタートパルス信号SPY2は入力されない)、第5クロックにおいて信号SR2LがHレベルになる。第5クロックにおいて信号SR2LがHレベルであり、このときイネーブル信号ENB1は第7番地においてHレベルであるので、走査信号G2は第7番地においてHレベルとなる。第6クロックにおいて信号SR3RはLレベルであり、走査信号G3はLレベルのままである。第7クロックにおいて信号SR4LがHレベルであり、このときイネーブル信号ENB2は第7番地においてHレベルであるので、走査信号G4は第7番地においてHレベルとなる。以降、偶数行の走査信号Giは順次、第7番地においてHレベルとなる。奇数行の走査信号GiはLレベルのままである。

【0060】

このように、本実施形態によれば、R画素およびB画素の走査と、G画素の走査とを異なるスタートパルス信号を用いて、それぞれ独立に開始させることができる。

【0061】

図14は、第1実施形態と第2実施形態のサブフィールド構成の相違を説明する図である。第1実施形態においては、G画素のサブフィールド長は、SF1G、SF2G、およびSF6Gは、それぞれ、SF1、SF2、およびSF4とサブフィールド長が等しく、また、SF3G、SF4G、およびSF5Gのサブフィールド長の合計は、SF3に等しいという制限があった。すなわち、SCAN4およびSCAN5の開始タイミングは任意に設計できるが、SCAN1、SCAN2、SCAN3、およびSCAN6の開始タイミングは、R画素およびB画素の走査と共通にしなければならなかった。

【0062】

これに対し第2実施形態においては、R画素およびB画素とG画素とで、サブフィールドの基本単位の長さが同一である限りにおいては、R画素およびB画素のサブフィールド構成とG画素のサブフィールド構成とを、それぞれ独自に設定することができる。すなわち、最初の走査(SCAN1)が共通であれば、R画素およびB画素の走査(SCAN3、SCAN5、およびSCAN8)の開始タイミングと、G画素の走査(SCAN2、SCAN4、SCAN6、およびSCAN7)の開始タイミングとを異ならせることができる。このように、第2実施形態においては、第1実施形態と比較してサブフィールド構成の自由度を向上させることができる。

【0063】

3.変形例

本発明は上述の実施形態に限定されるものでなく、種々の変形実施が可能である。以下、変形例をいくつか説明する。以下の変形例のうち、2つ以上のものが組み合わせて用いられてもよい。

【0064】

3−1.変形例1

図15は、変形例1に係る液晶パネル100の構成を示す図である。図15は、第1実施形態の液晶パネル100の変形例を示す図である。変形例1において、第1行および第(m+1)行の走査線112には、それぞれn/2個のダミー画素が接続されている(図において斜線で示している)。これは以下の理由による。第1実施形態の液晶パネル100において、第1行および第(m+1)行の走査線112に接続されている負荷(TFT116および画素電極118)の数は、他の走査線112の半分である。このように負荷の数が異なると、階調に悪影響を与える場合がある。この悪影響を回避するため、第1行および第(m+1)行の走査線112に、ダミー画素を接続してもよい。ダミー画素とは、構造は画素111と同様であるが、画像の表示に貢献しない画素をいう。ダミー画素により負荷の差を低減することにより、階調に与える悪影響を低減することができる。

【0065】

3−2.変形例2

ベイヤー配置の具体例は、実施形態で説明したものに限定されない。ベイヤー配置において、第1色、第2色、および第3色の画素が、2行2列の4画素を基本単位として配置される。基本単位には、第1色の画素が2つ、第2色および第3色の画素が1つずつ含まれる。第1色の画素は、基本単位において斜めに配置される。実施形態において、第1色がG、第2色がR、第3色がBである例を説明したが、各色はこれに限定されない。

【0066】

3−3.変形例3

電気光学装置10における画素111の配置は、図2で例示したものに限定されない。図2の配置においては、第1行の走査線112に接続されている負荷(TFT116および画素電極118)および第(m+1)行の走査線112に接続されている負荷の数は、第2行〜第m行の走査線112に接続されている負荷の半分である。このように負荷の数が異なると、階調に悪影響を与える場合がある。この悪影響を回避するため、第1行および第(m+1)行の走査線112に、ダミー画素を接続してもよい。ダミー画素とは、構造は画素111と同様であるが、画像の表示に貢献しない画素をいう。ダミー画素により負荷の差を低減することにより、階調に与える悪影響を低減することができる。

【0067】

3−4.他の変形例

本発明に係る電子機器はプロジェクターに限定されない。テレビジョン、ビューファインダー型・モニター直視型のビデオテープレコーダー、カーナビゲーション装置、ページャー、電子手帳、電卓、ワードプロセッサー、ワークステーション、テレビ電話、POS端末、デジタルスチルカメラ、携帯電話機、タッチパネルを備えた機器等に本発明が用いられてもよい。

【0068】

電気光学装置10の構成は、実施形態で説明したものに限定されない。えば、電気光学装置10において用いられる電気光学素子は、液晶素子120に限定されない。液晶素子120に代わり、有機EL(Electro-Luminescence)素子等、他の電気光学素子が用いられてもよい。また、電気光学装置10が、実施形態で説明した映像処理回路20を有していてもよい。

【0069】

実施形態で説明したパラメーター(例えば、サブフィールド数やフレーム速度、画素数など)および信号の極性やレベルはあくまで例示であり、本発明はこれに限定されない。

【符号の説明】

【0070】

1…電子機器、10…電気光学装置、20…映像処理回路、100…液晶パネル、101…表示領域、105…液晶層、108…コモン電極、111…画素、112…走査線、114…データ線、116…TFT、118…画素電極、120…液晶素子、125…容量素子、130…走査線駆動回路、131…シフトレジスター、132…出力回路、140…データ線駆動回路、141…シフトレジスター、142…第1ラッチ回路、143…第2ラッチ回路、230…走査線駆動回路、231…シフトレジスター、232…出力回路、330…走査線駆動回路、331…シフトレジスター、332…出力回路、1311…シフト回路、13111…クロックドインバーター、13112…クロックドインバーター、13113…インバーター

【特許請求の範囲】

【請求項1】

第1色の画素が2つ、第2色の画素、および第3色の画素がベイヤー配置された複数の画素と、

前記複数の画素のうち前記第1色の画素を選択するための複数の走査線を含む第1走査線群と、

前記複数の画素のうち前記第2色および前記第3色の画素を選択するための複数の走査線を含む第2走査線群と、

単位期間を区分したa個のサブ期間のうち走査に用いられる一のサブ期間を選択するためのb系統のイネーブル信号(b≧a)に応じて、前記第1走査線群および前記第2走査線群の中から順次一の走査線を選択する第1走査、および前記第1走査線群の中から順次一の走査線を選択する第2走査のいずれかの走査を行う走査線駆動回路と

を有する電気光学装置。

【請求項2】

前記イネーブル信号は、連続する2つの単位期間において同一のサブ期間を選択するための波形を有し、前記a個のサブ期間のうち、前記第2走査に用いられるサブ期間については、前記連続する2つの単位期間の一方においてのみ選択するための波形を有する

ことを特徴とする請求項1に記載の電気光学装置。

【請求項3】

前記複数の画素は、m行n列のマトリクス状に配置され、

前記第1走査線群および前記第2走査線群は、あわせて(m+1)本の走査線を有し、

前記第1走査線群の走査線と、前記第2走査線群の走査線とは、交互に配置され、

前記走査線駆動回路は、

スタートパルス信号を1段ずつ転送させた信号を出力する(m+1)段のシフトレジスターと、

前記シフトレジスターの出力信号と、前記b系統のイネーブル信号のうち対応する一のイネーブル信号の論理積に応じた信号を出力する出力回路と

を有する

ことを特徴とする請求項2に記載の電気光学装置。

【請求項4】

b≦NSF1+NSF2−1

である(ただし、NSF1は前記第1色の画素におけるサブフィールド数を示し、NSF2は前記第2色の画素におけるサブフィールド数を示す)

ことを特徴とする請求項1に記載の電気光学装置。

【請求項5】

前記複数の画素は、m行n列のマトリクス状に配置され、

前記第1走査線群および前記第2走査線群は、あわせて(m+1)本の走査線を有し、

前記第1走査線群の走査線と、前記第2走査線群の走査線とは、交互に配置され、

前記走査線駆動回路は、

第1スタートパルス信号を1段ずつ転送させた信号を出力する(m+1)段の第1シフトレジスターと、

前記第1シフトレジスターの出力信号と、前記b系統のイネーブル信号のうち対応する一のイネーブル信号の論理積に応じた信号を、前記(m+1)行の走査線のうち奇数行または偶数行の一方に出力する第1出力回路と

第2スタートパルス信号を1段ずつ転送させた信号を出力する(m+1)段の第2シフトレジスターと、

前記第2シフトレジスターの出力信号と、前記b系統のイネーブル信号のうち対応する一のイネーブル信号の論理積に応じた信号を、前記(m+1)行の走査線のうち奇数行または偶数行の他方に出力する第2出力回路と

を有する

ことを特徴とする請求項4に記載の電気光学装置。

【請求項6】

前記(m+1)本の走査線の各々に接続される画素の数が等しい

ことを特徴とする請求項3または5に記載の電気光学装置。

【請求項7】

請求項1ないし6のいずれか一項に記載の電気光学装置を有する電子機器。

【請求項8】

第1色の画素が2つ、第2色の画素、および第3色の画素がベイヤー配置された複数の画素と、前記複数の画素のうち前記第1色の画素を選択するための複数の走査線を含む第1走査線群と、前記複数の画素のうち前記第2色および前記第3色の画素を選択するための複数の走査線を含む第2走査線群とを有する電気光学装置の制御方法であって、

単位期間を区分したa個のサブ期間のうち走査に用いられる一のサブ期間を選択するためのb系統のイネーブル信号(b≧a)に応じて、前記第1走査線群および前記第2走査線群の中から順次一の走査線を選択する第1走査、および前記第1走査線群の中から順次一の走査線を選択する第2走査のいずれかの走査を行うステップ

を有する制御方法。

【請求項1】

第1色の画素が2つ、第2色の画素、および第3色の画素がベイヤー配置された複数の画素と、

前記複数の画素のうち前記第1色の画素を選択するための複数の走査線を含む第1走査線群と、

前記複数の画素のうち前記第2色および前記第3色の画素を選択するための複数の走査線を含む第2走査線群と、

単位期間を区分したa個のサブ期間のうち走査に用いられる一のサブ期間を選択するためのb系統のイネーブル信号(b≧a)に応じて、前記第1走査線群および前記第2走査線群の中から順次一の走査線を選択する第1走査、および前記第1走査線群の中から順次一の走査線を選択する第2走査のいずれかの走査を行う走査線駆動回路と

を有する電気光学装置。

【請求項2】

前記イネーブル信号は、連続する2つの単位期間において同一のサブ期間を選択するための波形を有し、前記a個のサブ期間のうち、前記第2走査に用いられるサブ期間については、前記連続する2つの単位期間の一方においてのみ選択するための波形を有する

ことを特徴とする請求項1に記載の電気光学装置。

【請求項3】

前記複数の画素は、m行n列のマトリクス状に配置され、

前記第1走査線群および前記第2走査線群は、あわせて(m+1)本の走査線を有し、

前記第1走査線群の走査線と、前記第2走査線群の走査線とは、交互に配置され、

前記走査線駆動回路は、

スタートパルス信号を1段ずつ転送させた信号を出力する(m+1)段のシフトレジスターと、

前記シフトレジスターの出力信号と、前記b系統のイネーブル信号のうち対応する一のイネーブル信号の論理積に応じた信号を出力する出力回路と

を有する

ことを特徴とする請求項2に記載の電気光学装置。

【請求項4】

b≦NSF1+NSF2−1

である(ただし、NSF1は前記第1色の画素におけるサブフィールド数を示し、NSF2は前記第2色の画素におけるサブフィールド数を示す)

ことを特徴とする請求項1に記載の電気光学装置。

【請求項5】

前記複数の画素は、m行n列のマトリクス状に配置され、

前記第1走査線群および前記第2走査線群は、あわせて(m+1)本の走査線を有し、

前記第1走査線群の走査線と、前記第2走査線群の走査線とは、交互に配置され、

前記走査線駆動回路は、

第1スタートパルス信号を1段ずつ転送させた信号を出力する(m+1)段の第1シフトレジスターと、

前記第1シフトレジスターの出力信号と、前記b系統のイネーブル信号のうち対応する一のイネーブル信号の論理積に応じた信号を、前記(m+1)行の走査線のうち奇数行または偶数行の一方に出力する第1出力回路と

第2スタートパルス信号を1段ずつ転送させた信号を出力する(m+1)段の第2シフトレジスターと、

前記第2シフトレジスターの出力信号と、前記b系統のイネーブル信号のうち対応する一のイネーブル信号の論理積に応じた信号を、前記(m+1)行の走査線のうち奇数行または偶数行の他方に出力する第2出力回路と

を有する

ことを特徴とする請求項4に記載の電気光学装置。

【請求項6】

前記(m+1)本の走査線の各々に接続される画素の数が等しい

ことを特徴とする請求項3または5に記載の電気光学装置。

【請求項7】

請求項1ないし6のいずれか一項に記載の電気光学装置を有する電子機器。

【請求項8】

第1色の画素が2つ、第2色の画素、および第3色の画素がベイヤー配置された複数の画素と、前記複数の画素のうち前記第1色の画素を選択するための複数の走査線を含む第1走査線群と、前記複数の画素のうち前記第2色および前記第3色の画素を選択するための複数の走査線を含む第2走査線群とを有する電気光学装置の制御方法であって、

単位期間を区分したa個のサブ期間のうち走査に用いられる一のサブ期間を選択するためのb系統のイネーブル信号(b≧a)に応じて、前記第1走査線群および前記第2走査線群の中から順次一の走査線を選択する第1走査、および前記第1走査線群の中から順次一の走査線を選択する第2走査のいずれかの走査を行うステップ

を有する制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2013−114019(P2013−114019A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−259910(P2011−259910)

【出願日】平成23年11月29日(2011.11.29)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月29日(2011.11.29)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]