電気光学装置および電子機器

【課題】トランジスター群の位置に依存したスジを抑制すること。

【解決手段】電気光学装置は、ゲート信号入力端子と、ゲート信号入力端子に接続され、ゲート信号が供給されるゲート信号線と、ソース信号入力端子と、複数のソース信号入力端子の各々に接続され、ソース信号が供給される複数のソース信号線と、ゲート信号線に接続されたゲート電極、および複数のソース信号線のうち第1ソース信号線に接続されたソース電極を有する第1トランジスター群と、第1トランジスター群よりも下流側の位置においてゲート信号線に接続されたゲート電極、および複数のソース信号線のうち第2ソース信号線に接続されたソース電極を有する第2トランジスター群と、第1ソース信号線に挿入された第1抵抗と、第2ソース信号線に挿入され、第1抵抗と異なる抵抗値を有する第2抵抗とを有する。

【解決手段】電気光学装置は、ゲート信号入力端子と、ゲート信号入力端子に接続され、ゲート信号が供給されるゲート信号線と、ソース信号入力端子と、複数のソース信号入力端子の各々に接続され、ソース信号が供給される複数のソース信号線と、ゲート信号線に接続されたゲート電極、および複数のソース信号線のうち第1ソース信号線に接続されたソース電極を有する第1トランジスター群と、第1トランジスター群よりも下流側の位置においてゲート信号線に接続されたゲート電極、および複数のソース信号線のうち第2ソース信号線に接続されたソース電極を有する第2トランジスター群と、第1ソース信号線に挿入された第1抵抗と、第2ソース信号線に挿入され、第1抵抗と異なる抵抗値を有する第2抵抗とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電気光学装置および電子機器に関する。

【背景技術】

【0002】

特許文献1は、走査信号線の寄生容量に起因して画素電位に生じるレベルシフトを表示面内で均一にするため、共通した遅延量を持つ波形を入力する技術を開示している。特許文献2は、N本のデータ線を1群とするデータ線群毎に、データ線を駆動する技術を開示している。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006−139317号公報

【特許文献2】特開2006−39352号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

1群のトランジスターのなかからオンにするトランジスターをゲート信号により選択する構成の電気光学装置により表示される画像おいて、各トランジスター群がゲート信号線において接続されている位置の違いにより、トランジスター群に依存したスジが発生してしまう場合があった。

これに対し本発明は、トランジスター群の位置に依存したスジを抑制する技術を提供する。

【課題を解決するための手段】

【0005】

本発明は、ゲート信号が入力されるゲート信号入力端子と、前記ゲート信号入力端子に接続され、前記ゲート信号が供給されるゲート信号線と、ソース信号が入力される複数のソース信号入力端子と、前記複数のソース信号入力端子の各々に接続され、前記ソース信号が供給される複数のソース信号線と、前記ゲート信号線に接続されたゲート電極、および前記複数のソース信号線のうち第1ソース信号線に接続されたソース電極を有する第1トランジスター群と、前記ゲート信号入力端子から見て前記第1トランジスター群よりも下流側の位置において前記ゲート信号線に接続されたゲート電極、および前記複数のソース信号線のうち第2ソース信号線に接続されたソース電極を有する第2トランジスター群と、前記第1ソース信号線において前記ソース電極と前記ソース信号入力端子との間に挿入された第1抵抗と、前記第2ソース信号線において前記ソース電極と前記ソース信号入力端子との間に挿入され、前記第1抵抗と異なる抵抗値を有する第2抵抗とを有する電気光学装置を提供する。

この電気光学装置によれば、トランジスター群の位置に依存したスジを抑制することができる。

【0006】

好ましい態様において、前記第1抵抗の抵抗値が、前記第2抵抗の抵抗値よりも小さくてもよい。

この電気光学装置によれば、第2トランジスター群に入力されるゲート信号が第1トランジスター群に入力されるゲート信号よりもなまっている場合において、トランジスター群の位置に依存したスジを抑制することができる。

【0007】

別の好ましい態様において、前記第1トランジスター群および前記第2トランジスター群を含む複数のトランジスター群と、前記複数のトランジスター群の各々に対応し、前記第1抵抗および前記第2抵抗を含む複数の抵抗とを有し、前記複数の抵抗の抵抗値は、当該抵抗に対応するトランジスター群が前記ゲート信号線に接続されている位置が前記ゲート信号入力端子から見て下流側になるほど大きくてもよい。

この電気光学装置によれば、複数のトランジスター群に入力されるゲート信号が上流側から下流側にいくにつれてなまっていく場合において、トランジスター群の位置に依存したスジを抑制することができる。

【0008】

さらに別の好ましい態様において、前記第1トランジスター群は、複数のトランジスターを含み、前記第1ソース信号線は、前記抵抗と前記複数のトランジスターとの間で複数に分岐していてもよい。

この電気光学装置によれば、トランジスター群が複数のトランジスターを含む場合において、トランジスター群の位置に依存したスジを抑制することができる。

【0009】

さらに別の好ましい態様において、前記第1抵抗および前記第2抵抗は、ある長さ、幅、および厚さを有する抵抗素子により形成され、前記第1抵抗および前記第2抵抗は、前記長さ、前記幅、および前記厚さの少なくとも1つが異なっていてもよい。

この電気光学装置によれば、抵抗素子の長さ、幅、または厚さを調整することにより、トランジスター群の位置に依存したスジを抑制することができる。

【0010】

また、本発明は、上記いずれかの電気光学装置を有する電子機器を提供する。

この電子機器によれば、トランジスター群の位置に依存したスジを抑制することができる。

【図面の簡単な説明】

【0011】

【図1】一実施形態に係る電気光学装置1を用いた電子機器の外観を示す図。

【図2】電気光学装置1の構成を示す模式図。

【図3】液晶パネル100の構造を示す図。

【図4】画素111の等価回路を示す図。

【図5】電気光学装置1の動作を示すタイミングチャート。

【図6】従来技術の問題点を説明する図。

【図7】上流および下流のスイッチング回路に入力されるゲート信号を示す。

【図8】書き込み前後の画素電極118の電位を例示する図。

【図9】液晶パネル100の構造を説明する図。

【図10】プロジェクター2100の構成を示す図。

【発明を実施するための形態】

【0012】

1.構成

図1は、一実施形態に係る電気光学装置1を用いた電子機器の(一部の)外観を示す図である。この例で、電気光学装置1は、プロジェクターのライトバルブとして用いられる液晶装置である。電子機器は、液晶パネル100と、データ線駆動回路200と、FPC(Flexible Printed Circuits)基板300と、回路基板400とを有する。FPC基板300上には、データ線駆動回路200が設けられている。回路基板400上には、電気光学装置1を制御する回路が設けられている。回路基板400と液晶パネル100とは、FPC基板300を介して電気的に接続される。回路基板400とFPC基板300とは、コネクタ410およびコネクタ320を介して接続される。FPC基板300と液晶パネル100とはコネクタ310およびコネクタ107を介して接続される。

【0013】

図2は、電気光学装置1の構成を示す模式図である。データ線駆動回路200は、他の回路から入力されるクロック信号、制御信号、および映像信号に従って、液晶パネル100に表示させる画像を示すソース信号を出力する。液晶パネル100は、データ線駆動回路200および他の回路から入力されるクロック信号およびソース信号に従って、画像を表示する。

【0014】

液晶パネル100は、画素領域110と、走査線駆動回路130と、データ線選択回路150と、複数のソース信号線160と、複数のソース信号入力端子161と、複数のゲート信号線(ゲート信号線141、ゲート信号線142、およびゲート信号線143)と、複数のゲート信号入力端子(ゲート信号入力端子146、ゲート信号入力端子147、およびゲート信号入力端子148)と、複数の抵抗Rを有する。

【0015】

画素領域110は、画像を表示する領域である。画素領域110は、m本の走査線112と、(k×n)本のデータ線114と、(m×k×n)個の画素111とを有する。走査線112は、走査信号を伝送する信号線であり、行(x)方向に沿って設けられている。データ線114は、データ信号を伝送する信号線であり、列(y)方向に沿って設けられている。走査線112とデータ線114とは、電気的に絶縁されている。画素111は、液晶パネル100をz方向(x方向およびy方向に垂直な方向)に見たときに、走査線112とデータ線114との交差に対応して設けられている。すなわち、画素111は、m行×(k×n)列のマトリクス状に配列されている。また、この例では、行方向において連続するk個の画素111が、1つの画素群を形成している(図2の例ではk=3)。すなわち、液晶パネル100は、m行n列の画素群を有する。画素111の詳細は後述する。以下の説明において、複数の走査線112の各々を区別する必要があるときは、第1行、第2行、第3行、…、第m行の走査線112と表す。複数のデータ線114の各々を区別する必要があるときは、第1列、第2列、第3列、…、第(k×n)列のデータ線114と表す。ソース信号線160についても同様である。

【0016】

走査線駆動回路130は、複数の走査線112の中から1本の走査線112を選択するための走査信号を出力する。走査線駆動回路130は、第1行、第2行、第3行、…、第m行の走査線112に、走査信号Y1、Y2、Y3、…、Ymを供給する。走査信号Y1、Y2、Y3、…、Ymは、順次排他的にH(High)レベルとなる信号である。

【0017】

ゲート信号線141、ゲート信号線142、およびゲート信号線143は、ゲート信号入力端子146、ゲート信号入力端子147、およびゲート信号入力端子148から入力されたゲート信号G1、G2、およびG3を伝送する信号線である。ゲート信号G1、G2、およびG3は、順次排他的にHレベルとなる信号である。

【0018】

データ線選択回路150は、各画素群において、k本のデータ線114の中から1本のデータ線114を選択する回路である。データ線選択回路150は、n列の画素群の各々に対応する、n個のスイッチング回路151を有する。スイッチング回路151は、ゲート信号G1、G2、およびG3に応じて、対応する画素群に接続されているk本のデータ線114の中から、1本のデータ線114を選択する。スイッチング回路151の詳細は後述する。

【0019】

ソース信号線160は、ソース信号入力端子161から入力されたソース信号Sを、データ線選択回路150に伝送する信号線である。ソース信号Sは、画素111に書き込まれるデータを示す信号である。ソース信号線160においては、抵抗Rが直列に挿入されている。抵抗Rについては後述する。

【0020】

データ線駆動回路200は、第1列、第2列、第3列、…、第n列のソース信号入力端子161に、ソース信号S1、S2、S3、…、Snを出力する。また、データ線駆動回路200は、ゲート信号入力端子146、ゲート信号入力端子147、およびゲート信号入力端子148に、ゲート信号G1、G2、G3を出力する。

【0021】

図3(A)は、液晶パネル100の構造を示す斜視図である。図3(B)は、図3(A)におけるH−h線における断面を示す模式図である。液晶パネル100は、素子基板101と、対向基板102と、液晶105とを有する。素子基板101と対向基板102とは、スペーサー(図示省略)を含むシール材90によって一定の間隙を保って、互いに電極形成面が対向するように貼り合わせられている。液晶105は、この間隙に封入されている。液晶105は、例えばVA(Vertical Alignment)型の液晶である。

【0022】

素子基板101および対向基板102は、それぞれガラスや石英などの透明性を有する基板を有する。素子基板101にあっては、対向基板102よりもY方向のサイズが長い。奥側(h側)が揃えられているので、素子基板101の手前側(H側)の一辺が対向基板102から張り出している。この張り出した領域にX方向に沿って複数の端子107が設けられている。複数の端子107は、FPC基板300に接続される。FPC基板300には、データ線駆動回路200が形成される。複数の端子107は、外部の回路から各種信号や各種電圧、映像信号などを供給するための端子であり、上述のゲート信号入力端子146、ゲート信号入力端子147、ゲート信号入力端子148、およびソース信号入力端子161を含む。

【0023】

素子基板101において対向基板102と対向する面には、画素電極118が形成されている。画素電極118は、ITO(Indium Tin Oxide)などの透明性を有する導電層をパターニングしたものである。また、素子基板101には、走査線駆動回路130が形成されている。対向基板102において、素子基板101と対向する面に設けられた共通電極108は、同じくITOなどの透明性を有する導電層である。

【0024】

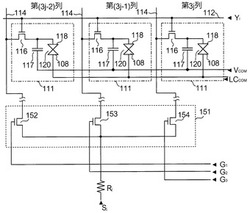

図4は、画素111の等価回路を示す図である。図4では、第i行第j列の画素群およびこの画素群に対応するスイッチング回路151が示されている(iおよびjは、1≦i≦mおよび1≦j≦nを満たす整数)。一つの画素群は、k個(この例ではk=3)の画素111から構成される。画素111は、TFT(Thin Film Transistor)116と、画素電極118と、液晶層120と、共通電極108と、保持容量130とを有する。TFT116は、画素電極118へのデータの書き込み(電圧の印加)を制御するスイッチング素子であり、この例ではnチャネル型の電界効果トランジスターである。TFT116のゲート電極は走査線112に接続され、ソース電極はデータ線114に接続され、ドレイン電極は画素電極118に接続されている。走査線112にHレベルの走査信号が供給されるとTFT116はオン状態になり、データ線114と画素電極118とが導通する。すなわち、画素電極118にデータが書き込まれる。走査線112にL(Low)レベルの走査信号が供給されるとTFT116はオフ状態になり、データ線114と画素電極118とは絶縁する。共通電極108はすべての画素111について共通である。共通電極108には、例えばデータ線駆動回路200により、共通電圧LCCOMが印加される。液晶層120には、画素電極118と共通電極108との電位差に相当する電圧が印加され、この電圧に応じて光学的特性(反射率または透過率)が変化する。保持容量117は、液晶層120に並列に接続されており、画素電極118と共通電圧VCOMとの電位差に相当する電荷を保持する(この例では、VCOM=LCCOMである)。以下、単一の画素群において、画素111の各々を区別するときは、画素111−sのように添字を用いて区別する(sは、1≦s≦kを満たす整数)。TFT116等、画素111に含まれる要素についても同様である。

【0025】

スイッチング回路151は、k個(この例ではk=3)のスイッチング素子として、TFT152、TFT153、およびTFT154を有する。TFT152のゲート電極は、ゲート信号線141に接続され、ソース電極は第j列のソース信号線160に接続され、ドレイン電極は第(3j−2)列のデータ線114(すなわち、第j列の画素群のTFT116−1のソース電極)に接続されている。ゲート信号線141にHレベルのゲート信号G1が供給されるとTFT152はオン状態になり、第j列のソース信号線160と第(3j−2)列のデータ線114とが導通する。すなわち、第(3j−2)列のデータ線114にソース信号Sjが供給される。ゲート信号線141にLレベルのゲート信号G1が供給されるとTFT152はオフ状態になり、第j列のソース信号線160と第(3j−2)列のデータ線114とが絶縁する。

【0026】

TFT153のゲート電極は、ゲート信号線142に接続され、ソース電極は第j列のソース信号線160に接続され、ドレイン電極は第(3j−1)列のデータ線114(すなわち、第j列の画素群のTFT116−2のソース電極)に接続されている。ゲート信号線142にHレベルのゲート信号G2が供給されるとTFT153はオン状態になり、第j列のソース信号線160と第(3j−1)列のデータ線114とが導通する。すなわち、第(3j−1)列のデータ線114にソース信号Sjが供給される。ゲート信号線142にLレベルのゲート信号G2が供給されるとTFT153はオフ状態になり、第j列のソース信号線160と第(3j−1)列のデータ線114とが絶縁する。

【0027】

TFT154のゲート電極は、ゲート信号線143に接続され、ソース電極は第j列のソース信号線160に接続され、ドレイン電極は第3j列のデータ線114(すなわち、第j列の画素群のTFT116−3のソース電極)に接続されている。ゲート信号線143にHレベルのゲート信号G3が供給されるとTFT154はオン状態になり、第j列のソース信号線160と第3j列のデータ線114とが導通する。すなわち、第3j列のデータ線114にソース信号Sjが供給される。ゲート信号線143にLレベルのゲート信号G3が供給されるとTFT154はオフ状態になり、第j列のソース信号線160と第3j列のデータ線114とが絶縁する。

【0028】

スイッチング回路151には、ソース信号入力端子161から入力されたソース信号Sが、ソース信号線160を介して供給される。スイッチング回路151においては、ソース信号線160が、抵抗RとTFT152、TFT153、およびTFT154との間で複数に分岐している。

【0029】

以上、まとめると、電気光学装置1は、ゲート信号が入力されるゲート信号入力端子146(または、ゲート信号入力端子147もしくはゲート信号入力端子148)と、これらゲート信号入力端子に接続され、ゲート信号が供給されるゲート信号線141(または、ゲート信号線142もしくはゲート信号線143)と、ソース信号が入力される複数のソース信号入力端子161と、複数のソース信号入力端子の各々に接続され、ソース信号が供給される複数のソース信号線160と、ゲート信号線141(または、ゲート信号入力端子147もしくはゲート信号入力端子148)に接続されたゲート電極、および複数のソース信号線160のうち第1ソース信号線(例えば、第n列のソース信号線160)に接続されたソース電極を有する第1トランジスター群(TFT152、TFT153、およびTFT154)と、ゲート信号入力端子146(または、ゲート信号入力端子147もしくはゲート信号入力端子148)から見て第1トランジスター群よりも下流側の位置においてゲート信号線141(または、ゲート信号線142もしくはゲート信号線143)に接続されたゲート電極、および複数のソース信号線160のうち第2ソース信号線(例えば、第1列のソース信号線160)に接続されたソース電極を有する第2トランジスター群(TFT152、TFT153、およびTFT154)と、第1ソース信号線においてソース電極とソース信号入力端子161との間に挿入された第1抵抗(例えば抵抗Rn)と、第2ソース信号線においてソース電極とソース信号入力端子161との間に挿入され、第1抵抗と異なる抵抗値を有する第2抵抗(例えば抵抗R1)とを有する。

【0030】

2.動作

図5は、電気光学装置1の動作を示すタイミングチャートである。ここでは、第i行第j列の画素群に対するデータの書き込み動作を例として説明する。時刻t1の直前において、操作信号Yi、ゲート信号G1、ゲート信号G2、およびゲート信号G3はLレベルである。時刻t1において、走査線駆動回路130は、走査信号YiをLレベルからHレベルに変化させる。走査信号YiがHレベルになると、TFT116がオン状態になり、データ線114と画素電極118とが導通する。

【0031】

時刻t2において、データ線駆動回路200は、ゲート信号G1をHレベルに変化させる。ゲート信号G1がHレベルになると、TFT152がオン状態になり、第j列のソース信号線160と第(3j−2)列のデータ線114とが導通する。このとき、データ線駆動回路200は、第j列のソース信号線160にソース信号Sj(1)を供給している。したがって、画素電極118−1には、ソース信号Sj(1)に応じたデータが書き込まれる。時刻t3において、データ線駆動回路200は、ゲート信号G1をLレベルに変化させる。ゲート信号G1がLレベルになると、TFT152がオフ状態になり、第j列のソース信号線160と第(3j−2)列のデータ線114とが絶縁する。

【0032】

時刻t4において、データ線駆動回路200は、ゲート信号G2をHレベルに変化させる。ゲート信号G2がHレベルになると、TFT153がオン状態になり、第j列のソース信号線160と第(3j−1)列のデータ線114とが導通する。このとき、データ線駆動回路200は、第j列のソース信号線160にソース信号Sj(2)を供給している。したがって、画素電極118−2には、ソース信号Sj(2)に応じたデータが書き込まれる。時刻t5において、データ線駆動回路200は、ゲート信号G2をLレベルに変化させる。ゲート信号G2がLレベルになると、TFT152がオフ状態になり、第j列のソース信号線160と第(3j−1)列のデータ線114とが絶縁する。

【0033】

時刻t6において、データ線駆動回路200は、ゲート信号G3をHレベルに変化させる。ゲート信号G3がHレベルになると、TFT154がオン状態になり、第j列のソース信号線160と第3j列のデータ線114とが導通する。このとき、データ線駆動回路200は、第j列のソース信号線160にソース信号Sj(3)を供給している。したがって、画素電極118−3には、ソース信号Sj(3)に応じたデータが書き込まれる。時刻t7において、データ線駆動回路200は、ゲート信号G3をLレベルに変化させる。ゲート信号G3がLレベルになると、TFT154がオフ状態になり、第j列のソース信号線160と第3j列のデータ線114とが絶縁する。

【0034】

時刻t8において、走査線駆動回路130は、走査信号YiをHレベルからLレベルに変化させる。走査信号YiがLレベルになると、TFT116がオフ状態になり、データ線114と画素電極118とが絶縁する。以上により、第j列の画素群へのデータの書き込みは終了する。液晶層120の容量および保持容量117により、データとして書き込まれた電荷は、新たなデータが書き込まれるまで保持される。走査線駆動回路130は、次に走査信号Yi+1をLレベルからHレベルに変化させる。こうして第i+1行の画素群にデータが書き込まれる。走査線駆動回路130は、第1行、第2行、第3行、…、第m行の走査線112に、順次排他的にHレベルとなる走査信号を供給する。第1行から第m行まで書き込みが終わると、1フレームの画像の書き込みが完了する。走査線駆動回路130は、再び、第1行の走査線112から順に、順次排他的にHレベルとなる走査信号を供給する。こうして、次のフレームの画像の書き込みが行われる。データ線駆動回路200は、ソース信号Sの共通電圧LCCOMに対する極性を、1フレーム毎に正負が交互に入れ替わるように制御する。すなわち、液晶層120に印加される電圧の極性は、1フレーム毎に正負が入れ替わる。

【0035】

図6は、従来技術の問題点を説明する図である。ここでは、説明を簡単にするため、ゲート信号線141、第1列のTFT152、ソース信号線160および抵抗R1、並びに第n列のTFT152、ソース信号線160および抵抗Rnだけを考える。抵抗R1および抵抗Rnの抵抗値は等しい。第1列のTFT152は、第n列のTFT152よりも、ゲート信号入力端子から見て下流側の位置においてゲート信号線141に接続されている。より詳細には、第1列のTFT152は最下流の位置において、第n列のTFT152は最上流の位置において、ゲート信号線141に接続されている。ゲート信号線141は、ある抵抗率を有する材料により形成されているので、線長により抵抗値が異なる。具体的には、第1列のTFT152のゲート信号線141の方が、第n列のTFT152のゲート信号線141よりも抵抗が高い。この高い抵抗のため、第1列のTFT152のゲート電極に入力されるゲート信号G1は、第n列のTFT152のゲート電極に入力されるゲート信号G1よりもなまってしまう。

【0036】

図7は、上流および下流のスイッチング回路151に入力されるゲート信号を示す模式図である。図7(A)は第n列すなわち最上流のTFT152に入力されるゲート信号G1(以下「ゲート信号G1U」という)を、図7(B)は第1列すなわち最下流のTFT152に入力されるゲート信号G1(以下「ゲート信号G1L」という)を、それぞれ示す。ゲート信号G1Uは、時刻t2においてLレベルからHレベルに変化し、時刻t2から時刻t3まではHレベルを保ち、時刻t3においてHレベルからLレベルに変化する、理想的な矩形波の特性を有している。一方、ゲート信号G1Lは、時刻t2においてLレベルから変化を始めるものの、立ち上がりはなだらかであり、Lレベルから徐々にHレベルに達する。さらに、ゲート信号G1Lは、時刻t3においてHレベルから変化を始めるものの、立ち下がりはなだらかである。第1列のTFT152をオン状態からオフ状態に切り替えるときを考えると、オン状態からオフ状態に切り替えるゲート電圧のしきい値Vthを下回る時刻は、ゲート信号G1Lにおいては時刻t3よりも遅い時刻t3’である。以下、上流および下流のスイッチング回路151に入力されるゲート信号に図7のような差異があるという前提で、ある画素群についてデータの書き込みが終わった直後、具体的には、図5の時刻t3の直後の状態を考える。

【0037】

図8は、書き込み前後の画素電極118の電位を例示する図である。図8の縦軸および横軸は、画素電極118の電圧Vpおよび時刻を示す。走査信号YiがHレベルからLレベルに変化するとTFT116はオン状態からオフ状態に変化するが、このとき、ゲート−ドレイン間の容量性結合により、画素電圧Vpが低下する現象(いわゆるプッシュダウン現象)が起こる。プッシュダウン現象による電圧変化ΔVpは次式(1)で表されることが知られている。

ΔVp=Cgd・Vg/(Cgd+Cs) …(1)

ここで、CgdはTFT152のゲート−ドレイン間の容量を、CsはTFT152における寄生容量を、Vgはゲート電圧を表す。

【0038】

プッシュダウン現象は、詳細には2つの段階に分けられると考えられる。第1段階は、式(1)に従って画素電圧Vpが低下する段階である。図8の例では、時刻t3から時刻t31までが第1段階である。第2段階は、低下した画素電圧Vpが回復(再び上昇)する段階である。図8の例では、時刻t31以降が第2段階である。第2段階においては、図7で説明したゲート信号G1の波形の差異が問題になる。ゲート信号G1Lはゲート信号G1Hよりもなまっているので、例えば時刻t3と時刻t3’(図6(B))との間の時刻において、第n列のTFT152はオフ状態であるのに対し、第1列のTFT152は完全にオフ状態になっていない。そのため、プッシュダウンで画素電圧Vpが低下した後で第1列のTFT152を介して電荷の移動が起こり、第1列のTFT152が接続されている画素111(第1列の画素111)の画素電圧Vpは回復する。第n列のTFT153が接続されている画素111(第(3n−2)列の画素111)の画素電圧も回復するが、回復する電圧の大きさは第1列の画素111よりも小さい。ここで、第1列の画素111および第(3n−2)列の画素111に同じデータ、例えば12.5Vの電圧が書き込まれ、プッシュダウンによりこれが例えば11.5Vまで低下した場合を考える。第(3n−2)列の画素111においては、第2段階に画素電圧が0.2V回復し、画素電圧Vpは11.7Vになる。第1列の画素111においては、第2段階の回復量が第(3n−2)列の画素111よりも多く、0.4Vである。したがって、第1列の画素111において画素電圧Vpは11.9Vになる。このように、第1列の画素111と第(3n−2)列の画素111にたとえ同じデータを書き込んだとしても、保持する電圧は同じにならない。これにより、表示される画像においてスジが視認されてしまうという問題がある。

【0039】

図9は、液晶パネル100の構造を説明する図である。図6の構成と対比するため、ゲート信号線141、第1列のTFT152、ソース信号線160および抵抗R1、並びに第n列のTFT152、ソース信号線160および抵抗Rnだけを考える。ここでは、抵抗R1および抵抗Rnの抵抗値は異なっており、具体的にはR1>Rnである。データ線駆動回路200から出力されるソース信号S1およびSnが同じ電圧であっても、抵抗R1と抵抗Rnとの抵抗値の違いにより、第1列の画素111および第(3n−2)列の画素111に書き込まれる電圧は異なる。具体的には、第1列の画素111に書き込まれる電圧の方が第(3n−2)列に書き込まれる電圧よりも低くなる。図8で説明したように、画素111に書き込まれた電圧と画素111が保持する電圧との差は、第(3n−2)列の画素111がの方が大きいが、そもそも書き込まれる電圧が第1列の画素111の方が低いので、この差が補償される。このように、すべてのソース信号線160について抵抗Rの抵抗値が等しい構成と比較して、電気光学装置1によれば、表示される画像におけるスジの発生を低減することができる。

【0040】

図9では簡単のため抵抗R1と抵抗Rnだけを取り出して説明したが、液晶パネル100に含まれるすべての抵抗Rについて、上記の考え方が適用される。すなわち、ソース信号線160に接続された抵抗R1、R2、R3、…、およびRnについて、その抵抗値が、R1>R2>R3>…>Rnとなるように設計される。換言すると、ソース信号線160に接続された抵抗Rの抵抗値は、ソース信号入力端子161からの距離に応じて階調的に変化するように(距離が遠くなるほど抵抗値が大きくなるように)設計される。さらに換言すると、抵抗Rの抵抗値は、その抵抗に対応するトランジスター群(スイッチング回路151)がゲート信号線141(またはゲート信号線142もしくはゲート信号線143)に接続されている位置がゲート信号入力端子146(またはゲート信号入力端子147もしくはゲート信号入力端子148)から見て下流側になるほど大きくなるように設計される。

【0041】

3.他の実施形態

本発明は上述の実施形態に限定されるものではなく、種々の変形実施が可能である。以下、変形例をいくつか説明する。以下の変形例のうち2つ以上のものが組み合わせて用いられてもよい。

【0042】

複数の抵抗Rの抵抗値の関係は、実施形態で説明したものに限定されない。複数の抵抗Rのうち任意の2つの抵抗RpおよびRqについて(pおよびqは、p<q、1≦p≦nかつ1≦q≦nを満たす整数。すなわち、RpはRqよりも下流側のソース信号線160に対応)、Rp≧RqかつR1>Rnという関係を満たせばよい。例えば、R1=R2=R3>R4=R5=R6>・・・>R(n−2)=R(n−1)=Rnというように、ある数の抵抗を単位として段階的に抵抗値を変化させてもよい。

【0043】

トランジスター群(すなわちスイッチング回路151)に含まれるTFTの数、すなわちkの値は実施形態で説明したものに限定されない。例えば、スイッチング回路151は、1個のTFTを有していてもよい(k=1)。別の例で、スイッチング回路151は、4個以上、例えば8個のTFTを有していてもよい。これらの場合、画素群に含まれる画素111の数も同様に、1個または8個である。

【0044】

実施形態においては、下流側のソース信号線160に接続された抵抗Rの方が上流側よりも大きい抵抗値を有する例を説明したが、下流側のソース信号線160に接続された抵抗Rの方が上流側よりも小さい抵抗値を有していてもよい。

【0045】

抵抗Rは、素子基板101においてある長さ、幅、および厚さを有する抵抗素子により形成され、長さ、幅、および厚さの少なくとも1つを異ならせることにより、抵抗値を異ならせてもよい。

【0046】

液晶層120は、透過型に限られず、反射型であってもよい。さらに、液晶層120は、ノーマリーブラックモードに限られず、例えばTN方式として、電圧無印加時において液晶層120が白状態となるノーマリーホワイトモードであってもよい。

また、TFTはnチャネル型の電界効果トランジスターに限定されず、pチャネル型の電界効果トランジスターであってもよい。この場合、プッシュダウン現象ではなく、プッシュアップ現象が起こる。

【0047】

実施形態においてはデータ線駆動回路200がソース信号Sおよびゲート信号Gを供給する構成を説明したが、ソース信号Sおよびゲート信号Gは、それぞれ別の回路により供給されてもよい。

【0048】

図10は、プロジェクター2100の構成を示す図である。プロジェクター2100は、一実施形態にかかる電子機器の一例である。プロジェクター2100の内部には、ハロゲンランプ等の白色光源からなるランプユニット2102が設けられている。ランプユニット2102から射出された投射光は、内部に配置された3枚のミラー2106および2枚のダイクロイックミラー2108によってR(赤)色、G(緑)色、B(青)色の3原色に分離されて、各原色に対応するライトバルブ100R、100Gおよび100Bにそれぞれ導かれる。なお、B色の光は、他のR色やG色と比較すると、光路が長いので、その損失を防ぐために、入射レンズ2122、リレーレンズ2123および出射レンズ2124からなるリレーレンズ系2121を介して導かれる。

【0049】

プロジェクター2100では、実施形態に係る電気光学装置1が、R色、G色、B色のそれぞれに対応して3組設けられる。そして、R色、G色、B色のそれぞれに対応する映像データがそれぞれ上位回路から供給されて、各色に対応するデータ信号Vidに変換される構成となっている。ライトバルブ100R、100Gおよび100Bの構成は、上述した液晶パネル100と同様であり、R色、G色、B色のそれぞれに対応する映像信号に応じて駆動される。

【0050】

ライトバルブ100R、100G、100Bによってそれぞれ変調された光は、ダイクロイックプリズム2112に3方向から入射する。ダイクロイックプリズム2112において、R色およびB色の光は90度に屈折する一方、G色の光は直進する。したがって、各色の画像が合成された後、スクリーン2120には、投射レンズ2114によってカラー画像が投射される。

【0051】

なお、ライトバルブ100R、100Gおよび100Bには、ダイクロイックミラー2108によって、R色、G色、B色のそれぞれに対応する光が入射するので、カラーフィルターを設ける必要はない。また、ライトバルブ100R、100Bの透過像は、ダイクロイックプリズム2112により反射した後に投射されるのに対し、ライトバルブ100Gの透過像はそのまま投射されるので、ライトバルブ100R、100Bによる水平走査方向は、ライトバルブ100Gによる水平走査方向と逆向きにして、左右を反転させた像を表示する構成となっている。

【0052】

この電子機器は、図10で説明したプロジェクターの他、電子ビューファインダーや、リヤ・プロジェクション型のテレビジョン、ヘッドマウントディスプレイなどであってもよい。

【符号の説明】

【0053】

1…電気光学装置、100R・100G・100B…ライトバルブ、100…液晶パネル、101…素子基板、102…対向基板、105…液晶、107…コネクタ、108…共通電極、110…画素領域、111…画素、112…走査線、114…データ線、116…TFT、117…保持容量、118…画素電極、120…液晶層、130…走査線駆動回路、141…ゲート信号線、142…ゲート信号線、143…ゲート信号線、146…ゲート信号入力端子、147…ゲート信号入力端子、148…ゲート信号入力端子、150…データ線選択回路、151…スイッチング回路、152…TFT、153…TFT、154…TFT、160…ソース信号線、161…ソース信号入力端子、200…データ線駆動回路、300…FPC基板、310…コネクタ、320…コネクタ、400…回路基板、410…コネクタ、2100…プロジェクター、2102…ランプユニット、2106…ミラー、2108…ダイクロイックミラー、2114…投射レンズ、2120…スクリーン、2121…リレーレンズ系、2122…入射レンズ、2123…リレーレンズ、2124…出射レンズ

【技術分野】

【0001】

本発明は、電気光学装置および電子機器に関する。

【背景技術】

【0002】

特許文献1は、走査信号線の寄生容量に起因して画素電位に生じるレベルシフトを表示面内で均一にするため、共通した遅延量を持つ波形を入力する技術を開示している。特許文献2は、N本のデータ線を1群とするデータ線群毎に、データ線を駆動する技術を開示している。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006−139317号公報

【特許文献2】特開2006−39352号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

1群のトランジスターのなかからオンにするトランジスターをゲート信号により選択する構成の電気光学装置により表示される画像おいて、各トランジスター群がゲート信号線において接続されている位置の違いにより、トランジスター群に依存したスジが発生してしまう場合があった。

これに対し本発明は、トランジスター群の位置に依存したスジを抑制する技術を提供する。

【課題を解決するための手段】

【0005】

本発明は、ゲート信号が入力されるゲート信号入力端子と、前記ゲート信号入力端子に接続され、前記ゲート信号が供給されるゲート信号線と、ソース信号が入力される複数のソース信号入力端子と、前記複数のソース信号入力端子の各々に接続され、前記ソース信号が供給される複数のソース信号線と、前記ゲート信号線に接続されたゲート電極、および前記複数のソース信号線のうち第1ソース信号線に接続されたソース電極を有する第1トランジスター群と、前記ゲート信号入力端子から見て前記第1トランジスター群よりも下流側の位置において前記ゲート信号線に接続されたゲート電極、および前記複数のソース信号線のうち第2ソース信号線に接続されたソース電極を有する第2トランジスター群と、前記第1ソース信号線において前記ソース電極と前記ソース信号入力端子との間に挿入された第1抵抗と、前記第2ソース信号線において前記ソース電極と前記ソース信号入力端子との間に挿入され、前記第1抵抗と異なる抵抗値を有する第2抵抗とを有する電気光学装置を提供する。

この電気光学装置によれば、トランジスター群の位置に依存したスジを抑制することができる。

【0006】

好ましい態様において、前記第1抵抗の抵抗値が、前記第2抵抗の抵抗値よりも小さくてもよい。

この電気光学装置によれば、第2トランジスター群に入力されるゲート信号が第1トランジスター群に入力されるゲート信号よりもなまっている場合において、トランジスター群の位置に依存したスジを抑制することができる。

【0007】

別の好ましい態様において、前記第1トランジスター群および前記第2トランジスター群を含む複数のトランジスター群と、前記複数のトランジスター群の各々に対応し、前記第1抵抗および前記第2抵抗を含む複数の抵抗とを有し、前記複数の抵抗の抵抗値は、当該抵抗に対応するトランジスター群が前記ゲート信号線に接続されている位置が前記ゲート信号入力端子から見て下流側になるほど大きくてもよい。

この電気光学装置によれば、複数のトランジスター群に入力されるゲート信号が上流側から下流側にいくにつれてなまっていく場合において、トランジスター群の位置に依存したスジを抑制することができる。

【0008】

さらに別の好ましい態様において、前記第1トランジスター群は、複数のトランジスターを含み、前記第1ソース信号線は、前記抵抗と前記複数のトランジスターとの間で複数に分岐していてもよい。

この電気光学装置によれば、トランジスター群が複数のトランジスターを含む場合において、トランジスター群の位置に依存したスジを抑制することができる。

【0009】

さらに別の好ましい態様において、前記第1抵抗および前記第2抵抗は、ある長さ、幅、および厚さを有する抵抗素子により形成され、前記第1抵抗および前記第2抵抗は、前記長さ、前記幅、および前記厚さの少なくとも1つが異なっていてもよい。

この電気光学装置によれば、抵抗素子の長さ、幅、または厚さを調整することにより、トランジスター群の位置に依存したスジを抑制することができる。

【0010】

また、本発明は、上記いずれかの電気光学装置を有する電子機器を提供する。

この電子機器によれば、トランジスター群の位置に依存したスジを抑制することができる。

【図面の簡単な説明】

【0011】

【図1】一実施形態に係る電気光学装置1を用いた電子機器の外観を示す図。

【図2】電気光学装置1の構成を示す模式図。

【図3】液晶パネル100の構造を示す図。

【図4】画素111の等価回路を示す図。

【図5】電気光学装置1の動作を示すタイミングチャート。

【図6】従来技術の問題点を説明する図。

【図7】上流および下流のスイッチング回路に入力されるゲート信号を示す。

【図8】書き込み前後の画素電極118の電位を例示する図。

【図9】液晶パネル100の構造を説明する図。

【図10】プロジェクター2100の構成を示す図。

【発明を実施するための形態】

【0012】

1.構成

図1は、一実施形態に係る電気光学装置1を用いた電子機器の(一部の)外観を示す図である。この例で、電気光学装置1は、プロジェクターのライトバルブとして用いられる液晶装置である。電子機器は、液晶パネル100と、データ線駆動回路200と、FPC(Flexible Printed Circuits)基板300と、回路基板400とを有する。FPC基板300上には、データ線駆動回路200が設けられている。回路基板400上には、電気光学装置1を制御する回路が設けられている。回路基板400と液晶パネル100とは、FPC基板300を介して電気的に接続される。回路基板400とFPC基板300とは、コネクタ410およびコネクタ320を介して接続される。FPC基板300と液晶パネル100とはコネクタ310およびコネクタ107を介して接続される。

【0013】

図2は、電気光学装置1の構成を示す模式図である。データ線駆動回路200は、他の回路から入力されるクロック信号、制御信号、および映像信号に従って、液晶パネル100に表示させる画像を示すソース信号を出力する。液晶パネル100は、データ線駆動回路200および他の回路から入力されるクロック信号およびソース信号に従って、画像を表示する。

【0014】

液晶パネル100は、画素領域110と、走査線駆動回路130と、データ線選択回路150と、複数のソース信号線160と、複数のソース信号入力端子161と、複数のゲート信号線(ゲート信号線141、ゲート信号線142、およびゲート信号線143)と、複数のゲート信号入力端子(ゲート信号入力端子146、ゲート信号入力端子147、およびゲート信号入力端子148)と、複数の抵抗Rを有する。

【0015】

画素領域110は、画像を表示する領域である。画素領域110は、m本の走査線112と、(k×n)本のデータ線114と、(m×k×n)個の画素111とを有する。走査線112は、走査信号を伝送する信号線であり、行(x)方向に沿って設けられている。データ線114は、データ信号を伝送する信号線であり、列(y)方向に沿って設けられている。走査線112とデータ線114とは、電気的に絶縁されている。画素111は、液晶パネル100をz方向(x方向およびy方向に垂直な方向)に見たときに、走査線112とデータ線114との交差に対応して設けられている。すなわち、画素111は、m行×(k×n)列のマトリクス状に配列されている。また、この例では、行方向において連続するk個の画素111が、1つの画素群を形成している(図2の例ではk=3)。すなわち、液晶パネル100は、m行n列の画素群を有する。画素111の詳細は後述する。以下の説明において、複数の走査線112の各々を区別する必要があるときは、第1行、第2行、第3行、…、第m行の走査線112と表す。複数のデータ線114の各々を区別する必要があるときは、第1列、第2列、第3列、…、第(k×n)列のデータ線114と表す。ソース信号線160についても同様である。

【0016】

走査線駆動回路130は、複数の走査線112の中から1本の走査線112を選択するための走査信号を出力する。走査線駆動回路130は、第1行、第2行、第3行、…、第m行の走査線112に、走査信号Y1、Y2、Y3、…、Ymを供給する。走査信号Y1、Y2、Y3、…、Ymは、順次排他的にH(High)レベルとなる信号である。

【0017】

ゲート信号線141、ゲート信号線142、およびゲート信号線143は、ゲート信号入力端子146、ゲート信号入力端子147、およびゲート信号入力端子148から入力されたゲート信号G1、G2、およびG3を伝送する信号線である。ゲート信号G1、G2、およびG3は、順次排他的にHレベルとなる信号である。

【0018】

データ線選択回路150は、各画素群において、k本のデータ線114の中から1本のデータ線114を選択する回路である。データ線選択回路150は、n列の画素群の各々に対応する、n個のスイッチング回路151を有する。スイッチング回路151は、ゲート信号G1、G2、およびG3に応じて、対応する画素群に接続されているk本のデータ線114の中から、1本のデータ線114を選択する。スイッチング回路151の詳細は後述する。

【0019】

ソース信号線160は、ソース信号入力端子161から入力されたソース信号Sを、データ線選択回路150に伝送する信号線である。ソース信号Sは、画素111に書き込まれるデータを示す信号である。ソース信号線160においては、抵抗Rが直列に挿入されている。抵抗Rについては後述する。

【0020】

データ線駆動回路200は、第1列、第2列、第3列、…、第n列のソース信号入力端子161に、ソース信号S1、S2、S3、…、Snを出力する。また、データ線駆動回路200は、ゲート信号入力端子146、ゲート信号入力端子147、およびゲート信号入力端子148に、ゲート信号G1、G2、G3を出力する。

【0021】

図3(A)は、液晶パネル100の構造を示す斜視図である。図3(B)は、図3(A)におけるH−h線における断面を示す模式図である。液晶パネル100は、素子基板101と、対向基板102と、液晶105とを有する。素子基板101と対向基板102とは、スペーサー(図示省略)を含むシール材90によって一定の間隙を保って、互いに電極形成面が対向するように貼り合わせられている。液晶105は、この間隙に封入されている。液晶105は、例えばVA(Vertical Alignment)型の液晶である。

【0022】

素子基板101および対向基板102は、それぞれガラスや石英などの透明性を有する基板を有する。素子基板101にあっては、対向基板102よりもY方向のサイズが長い。奥側(h側)が揃えられているので、素子基板101の手前側(H側)の一辺が対向基板102から張り出している。この張り出した領域にX方向に沿って複数の端子107が設けられている。複数の端子107は、FPC基板300に接続される。FPC基板300には、データ線駆動回路200が形成される。複数の端子107は、外部の回路から各種信号や各種電圧、映像信号などを供給するための端子であり、上述のゲート信号入力端子146、ゲート信号入力端子147、ゲート信号入力端子148、およびソース信号入力端子161を含む。

【0023】

素子基板101において対向基板102と対向する面には、画素電極118が形成されている。画素電極118は、ITO(Indium Tin Oxide)などの透明性を有する導電層をパターニングしたものである。また、素子基板101には、走査線駆動回路130が形成されている。対向基板102において、素子基板101と対向する面に設けられた共通電極108は、同じくITOなどの透明性を有する導電層である。

【0024】

図4は、画素111の等価回路を示す図である。図4では、第i行第j列の画素群およびこの画素群に対応するスイッチング回路151が示されている(iおよびjは、1≦i≦mおよび1≦j≦nを満たす整数)。一つの画素群は、k個(この例ではk=3)の画素111から構成される。画素111は、TFT(Thin Film Transistor)116と、画素電極118と、液晶層120と、共通電極108と、保持容量130とを有する。TFT116は、画素電極118へのデータの書き込み(電圧の印加)を制御するスイッチング素子であり、この例ではnチャネル型の電界効果トランジスターである。TFT116のゲート電極は走査線112に接続され、ソース電極はデータ線114に接続され、ドレイン電極は画素電極118に接続されている。走査線112にHレベルの走査信号が供給されるとTFT116はオン状態になり、データ線114と画素電極118とが導通する。すなわち、画素電極118にデータが書き込まれる。走査線112にL(Low)レベルの走査信号が供給されるとTFT116はオフ状態になり、データ線114と画素電極118とは絶縁する。共通電極108はすべての画素111について共通である。共通電極108には、例えばデータ線駆動回路200により、共通電圧LCCOMが印加される。液晶層120には、画素電極118と共通電極108との電位差に相当する電圧が印加され、この電圧に応じて光学的特性(反射率または透過率)が変化する。保持容量117は、液晶層120に並列に接続されており、画素電極118と共通電圧VCOMとの電位差に相当する電荷を保持する(この例では、VCOM=LCCOMである)。以下、単一の画素群において、画素111の各々を区別するときは、画素111−sのように添字を用いて区別する(sは、1≦s≦kを満たす整数)。TFT116等、画素111に含まれる要素についても同様である。

【0025】

スイッチング回路151は、k個(この例ではk=3)のスイッチング素子として、TFT152、TFT153、およびTFT154を有する。TFT152のゲート電極は、ゲート信号線141に接続され、ソース電極は第j列のソース信号線160に接続され、ドレイン電極は第(3j−2)列のデータ線114(すなわち、第j列の画素群のTFT116−1のソース電極)に接続されている。ゲート信号線141にHレベルのゲート信号G1が供給されるとTFT152はオン状態になり、第j列のソース信号線160と第(3j−2)列のデータ線114とが導通する。すなわち、第(3j−2)列のデータ線114にソース信号Sjが供給される。ゲート信号線141にLレベルのゲート信号G1が供給されるとTFT152はオフ状態になり、第j列のソース信号線160と第(3j−2)列のデータ線114とが絶縁する。

【0026】

TFT153のゲート電極は、ゲート信号線142に接続され、ソース電極は第j列のソース信号線160に接続され、ドレイン電極は第(3j−1)列のデータ線114(すなわち、第j列の画素群のTFT116−2のソース電極)に接続されている。ゲート信号線142にHレベルのゲート信号G2が供給されるとTFT153はオン状態になり、第j列のソース信号線160と第(3j−1)列のデータ線114とが導通する。すなわち、第(3j−1)列のデータ線114にソース信号Sjが供給される。ゲート信号線142にLレベルのゲート信号G2が供給されるとTFT153はオフ状態になり、第j列のソース信号線160と第(3j−1)列のデータ線114とが絶縁する。

【0027】

TFT154のゲート電極は、ゲート信号線143に接続され、ソース電極は第j列のソース信号線160に接続され、ドレイン電極は第3j列のデータ線114(すなわち、第j列の画素群のTFT116−3のソース電極)に接続されている。ゲート信号線143にHレベルのゲート信号G3が供給されるとTFT154はオン状態になり、第j列のソース信号線160と第3j列のデータ線114とが導通する。すなわち、第3j列のデータ線114にソース信号Sjが供給される。ゲート信号線143にLレベルのゲート信号G3が供給されるとTFT154はオフ状態になり、第j列のソース信号線160と第3j列のデータ線114とが絶縁する。

【0028】

スイッチング回路151には、ソース信号入力端子161から入力されたソース信号Sが、ソース信号線160を介して供給される。スイッチング回路151においては、ソース信号線160が、抵抗RとTFT152、TFT153、およびTFT154との間で複数に分岐している。

【0029】

以上、まとめると、電気光学装置1は、ゲート信号が入力されるゲート信号入力端子146(または、ゲート信号入力端子147もしくはゲート信号入力端子148)と、これらゲート信号入力端子に接続され、ゲート信号が供給されるゲート信号線141(または、ゲート信号線142もしくはゲート信号線143)と、ソース信号が入力される複数のソース信号入力端子161と、複数のソース信号入力端子の各々に接続され、ソース信号が供給される複数のソース信号線160と、ゲート信号線141(または、ゲート信号入力端子147もしくはゲート信号入力端子148)に接続されたゲート電極、および複数のソース信号線160のうち第1ソース信号線(例えば、第n列のソース信号線160)に接続されたソース電極を有する第1トランジスター群(TFT152、TFT153、およびTFT154)と、ゲート信号入力端子146(または、ゲート信号入力端子147もしくはゲート信号入力端子148)から見て第1トランジスター群よりも下流側の位置においてゲート信号線141(または、ゲート信号線142もしくはゲート信号線143)に接続されたゲート電極、および複数のソース信号線160のうち第2ソース信号線(例えば、第1列のソース信号線160)に接続されたソース電極を有する第2トランジスター群(TFT152、TFT153、およびTFT154)と、第1ソース信号線においてソース電極とソース信号入力端子161との間に挿入された第1抵抗(例えば抵抗Rn)と、第2ソース信号線においてソース電極とソース信号入力端子161との間に挿入され、第1抵抗と異なる抵抗値を有する第2抵抗(例えば抵抗R1)とを有する。

【0030】

2.動作

図5は、電気光学装置1の動作を示すタイミングチャートである。ここでは、第i行第j列の画素群に対するデータの書き込み動作を例として説明する。時刻t1の直前において、操作信号Yi、ゲート信号G1、ゲート信号G2、およびゲート信号G3はLレベルである。時刻t1において、走査線駆動回路130は、走査信号YiをLレベルからHレベルに変化させる。走査信号YiがHレベルになると、TFT116がオン状態になり、データ線114と画素電極118とが導通する。

【0031】

時刻t2において、データ線駆動回路200は、ゲート信号G1をHレベルに変化させる。ゲート信号G1がHレベルになると、TFT152がオン状態になり、第j列のソース信号線160と第(3j−2)列のデータ線114とが導通する。このとき、データ線駆動回路200は、第j列のソース信号線160にソース信号Sj(1)を供給している。したがって、画素電極118−1には、ソース信号Sj(1)に応じたデータが書き込まれる。時刻t3において、データ線駆動回路200は、ゲート信号G1をLレベルに変化させる。ゲート信号G1がLレベルになると、TFT152がオフ状態になり、第j列のソース信号線160と第(3j−2)列のデータ線114とが絶縁する。

【0032】

時刻t4において、データ線駆動回路200は、ゲート信号G2をHレベルに変化させる。ゲート信号G2がHレベルになると、TFT153がオン状態になり、第j列のソース信号線160と第(3j−1)列のデータ線114とが導通する。このとき、データ線駆動回路200は、第j列のソース信号線160にソース信号Sj(2)を供給している。したがって、画素電極118−2には、ソース信号Sj(2)に応じたデータが書き込まれる。時刻t5において、データ線駆動回路200は、ゲート信号G2をLレベルに変化させる。ゲート信号G2がLレベルになると、TFT152がオフ状態になり、第j列のソース信号線160と第(3j−1)列のデータ線114とが絶縁する。

【0033】

時刻t6において、データ線駆動回路200は、ゲート信号G3をHレベルに変化させる。ゲート信号G3がHレベルになると、TFT154がオン状態になり、第j列のソース信号線160と第3j列のデータ線114とが導通する。このとき、データ線駆動回路200は、第j列のソース信号線160にソース信号Sj(3)を供給している。したがって、画素電極118−3には、ソース信号Sj(3)に応じたデータが書き込まれる。時刻t7において、データ線駆動回路200は、ゲート信号G3をLレベルに変化させる。ゲート信号G3がLレベルになると、TFT154がオフ状態になり、第j列のソース信号線160と第3j列のデータ線114とが絶縁する。

【0034】

時刻t8において、走査線駆動回路130は、走査信号YiをHレベルからLレベルに変化させる。走査信号YiがLレベルになると、TFT116がオフ状態になり、データ線114と画素電極118とが絶縁する。以上により、第j列の画素群へのデータの書き込みは終了する。液晶層120の容量および保持容量117により、データとして書き込まれた電荷は、新たなデータが書き込まれるまで保持される。走査線駆動回路130は、次に走査信号Yi+1をLレベルからHレベルに変化させる。こうして第i+1行の画素群にデータが書き込まれる。走査線駆動回路130は、第1行、第2行、第3行、…、第m行の走査線112に、順次排他的にHレベルとなる走査信号を供給する。第1行から第m行まで書き込みが終わると、1フレームの画像の書き込みが完了する。走査線駆動回路130は、再び、第1行の走査線112から順に、順次排他的にHレベルとなる走査信号を供給する。こうして、次のフレームの画像の書き込みが行われる。データ線駆動回路200は、ソース信号Sの共通電圧LCCOMに対する極性を、1フレーム毎に正負が交互に入れ替わるように制御する。すなわち、液晶層120に印加される電圧の極性は、1フレーム毎に正負が入れ替わる。

【0035】

図6は、従来技術の問題点を説明する図である。ここでは、説明を簡単にするため、ゲート信号線141、第1列のTFT152、ソース信号線160および抵抗R1、並びに第n列のTFT152、ソース信号線160および抵抗Rnだけを考える。抵抗R1および抵抗Rnの抵抗値は等しい。第1列のTFT152は、第n列のTFT152よりも、ゲート信号入力端子から見て下流側の位置においてゲート信号線141に接続されている。より詳細には、第1列のTFT152は最下流の位置において、第n列のTFT152は最上流の位置において、ゲート信号線141に接続されている。ゲート信号線141は、ある抵抗率を有する材料により形成されているので、線長により抵抗値が異なる。具体的には、第1列のTFT152のゲート信号線141の方が、第n列のTFT152のゲート信号線141よりも抵抗が高い。この高い抵抗のため、第1列のTFT152のゲート電極に入力されるゲート信号G1は、第n列のTFT152のゲート電極に入力されるゲート信号G1よりもなまってしまう。

【0036】

図7は、上流および下流のスイッチング回路151に入力されるゲート信号を示す模式図である。図7(A)は第n列すなわち最上流のTFT152に入力されるゲート信号G1(以下「ゲート信号G1U」という)を、図7(B)は第1列すなわち最下流のTFT152に入力されるゲート信号G1(以下「ゲート信号G1L」という)を、それぞれ示す。ゲート信号G1Uは、時刻t2においてLレベルからHレベルに変化し、時刻t2から時刻t3まではHレベルを保ち、時刻t3においてHレベルからLレベルに変化する、理想的な矩形波の特性を有している。一方、ゲート信号G1Lは、時刻t2においてLレベルから変化を始めるものの、立ち上がりはなだらかであり、Lレベルから徐々にHレベルに達する。さらに、ゲート信号G1Lは、時刻t3においてHレベルから変化を始めるものの、立ち下がりはなだらかである。第1列のTFT152をオン状態からオフ状態に切り替えるときを考えると、オン状態からオフ状態に切り替えるゲート電圧のしきい値Vthを下回る時刻は、ゲート信号G1Lにおいては時刻t3よりも遅い時刻t3’である。以下、上流および下流のスイッチング回路151に入力されるゲート信号に図7のような差異があるという前提で、ある画素群についてデータの書き込みが終わった直後、具体的には、図5の時刻t3の直後の状態を考える。

【0037】

図8は、書き込み前後の画素電極118の電位を例示する図である。図8の縦軸および横軸は、画素電極118の電圧Vpおよび時刻を示す。走査信号YiがHレベルからLレベルに変化するとTFT116はオン状態からオフ状態に変化するが、このとき、ゲート−ドレイン間の容量性結合により、画素電圧Vpが低下する現象(いわゆるプッシュダウン現象)が起こる。プッシュダウン現象による電圧変化ΔVpは次式(1)で表されることが知られている。

ΔVp=Cgd・Vg/(Cgd+Cs) …(1)

ここで、CgdはTFT152のゲート−ドレイン間の容量を、CsはTFT152における寄生容量を、Vgはゲート電圧を表す。

【0038】

プッシュダウン現象は、詳細には2つの段階に分けられると考えられる。第1段階は、式(1)に従って画素電圧Vpが低下する段階である。図8の例では、時刻t3から時刻t31までが第1段階である。第2段階は、低下した画素電圧Vpが回復(再び上昇)する段階である。図8の例では、時刻t31以降が第2段階である。第2段階においては、図7で説明したゲート信号G1の波形の差異が問題になる。ゲート信号G1Lはゲート信号G1Hよりもなまっているので、例えば時刻t3と時刻t3’(図6(B))との間の時刻において、第n列のTFT152はオフ状態であるのに対し、第1列のTFT152は完全にオフ状態になっていない。そのため、プッシュダウンで画素電圧Vpが低下した後で第1列のTFT152を介して電荷の移動が起こり、第1列のTFT152が接続されている画素111(第1列の画素111)の画素電圧Vpは回復する。第n列のTFT153が接続されている画素111(第(3n−2)列の画素111)の画素電圧も回復するが、回復する電圧の大きさは第1列の画素111よりも小さい。ここで、第1列の画素111および第(3n−2)列の画素111に同じデータ、例えば12.5Vの電圧が書き込まれ、プッシュダウンによりこれが例えば11.5Vまで低下した場合を考える。第(3n−2)列の画素111においては、第2段階に画素電圧が0.2V回復し、画素電圧Vpは11.7Vになる。第1列の画素111においては、第2段階の回復量が第(3n−2)列の画素111よりも多く、0.4Vである。したがって、第1列の画素111において画素電圧Vpは11.9Vになる。このように、第1列の画素111と第(3n−2)列の画素111にたとえ同じデータを書き込んだとしても、保持する電圧は同じにならない。これにより、表示される画像においてスジが視認されてしまうという問題がある。

【0039】

図9は、液晶パネル100の構造を説明する図である。図6の構成と対比するため、ゲート信号線141、第1列のTFT152、ソース信号線160および抵抗R1、並びに第n列のTFT152、ソース信号線160および抵抗Rnだけを考える。ここでは、抵抗R1および抵抗Rnの抵抗値は異なっており、具体的にはR1>Rnである。データ線駆動回路200から出力されるソース信号S1およびSnが同じ電圧であっても、抵抗R1と抵抗Rnとの抵抗値の違いにより、第1列の画素111および第(3n−2)列の画素111に書き込まれる電圧は異なる。具体的には、第1列の画素111に書き込まれる電圧の方が第(3n−2)列に書き込まれる電圧よりも低くなる。図8で説明したように、画素111に書き込まれた電圧と画素111が保持する電圧との差は、第(3n−2)列の画素111がの方が大きいが、そもそも書き込まれる電圧が第1列の画素111の方が低いので、この差が補償される。このように、すべてのソース信号線160について抵抗Rの抵抗値が等しい構成と比較して、電気光学装置1によれば、表示される画像におけるスジの発生を低減することができる。

【0040】

図9では簡単のため抵抗R1と抵抗Rnだけを取り出して説明したが、液晶パネル100に含まれるすべての抵抗Rについて、上記の考え方が適用される。すなわち、ソース信号線160に接続された抵抗R1、R2、R3、…、およびRnについて、その抵抗値が、R1>R2>R3>…>Rnとなるように設計される。換言すると、ソース信号線160に接続された抵抗Rの抵抗値は、ソース信号入力端子161からの距離に応じて階調的に変化するように(距離が遠くなるほど抵抗値が大きくなるように)設計される。さらに換言すると、抵抗Rの抵抗値は、その抵抗に対応するトランジスター群(スイッチング回路151)がゲート信号線141(またはゲート信号線142もしくはゲート信号線143)に接続されている位置がゲート信号入力端子146(またはゲート信号入力端子147もしくはゲート信号入力端子148)から見て下流側になるほど大きくなるように設計される。

【0041】

3.他の実施形態

本発明は上述の実施形態に限定されるものではなく、種々の変形実施が可能である。以下、変形例をいくつか説明する。以下の変形例のうち2つ以上のものが組み合わせて用いられてもよい。

【0042】

複数の抵抗Rの抵抗値の関係は、実施形態で説明したものに限定されない。複数の抵抗Rのうち任意の2つの抵抗RpおよびRqについて(pおよびqは、p<q、1≦p≦nかつ1≦q≦nを満たす整数。すなわち、RpはRqよりも下流側のソース信号線160に対応)、Rp≧RqかつR1>Rnという関係を満たせばよい。例えば、R1=R2=R3>R4=R5=R6>・・・>R(n−2)=R(n−1)=Rnというように、ある数の抵抗を単位として段階的に抵抗値を変化させてもよい。

【0043】

トランジスター群(すなわちスイッチング回路151)に含まれるTFTの数、すなわちkの値は実施形態で説明したものに限定されない。例えば、スイッチング回路151は、1個のTFTを有していてもよい(k=1)。別の例で、スイッチング回路151は、4個以上、例えば8個のTFTを有していてもよい。これらの場合、画素群に含まれる画素111の数も同様に、1個または8個である。

【0044】

実施形態においては、下流側のソース信号線160に接続された抵抗Rの方が上流側よりも大きい抵抗値を有する例を説明したが、下流側のソース信号線160に接続された抵抗Rの方が上流側よりも小さい抵抗値を有していてもよい。

【0045】

抵抗Rは、素子基板101においてある長さ、幅、および厚さを有する抵抗素子により形成され、長さ、幅、および厚さの少なくとも1つを異ならせることにより、抵抗値を異ならせてもよい。

【0046】

液晶層120は、透過型に限られず、反射型であってもよい。さらに、液晶層120は、ノーマリーブラックモードに限られず、例えばTN方式として、電圧無印加時において液晶層120が白状態となるノーマリーホワイトモードであってもよい。

また、TFTはnチャネル型の電界効果トランジスターに限定されず、pチャネル型の電界効果トランジスターであってもよい。この場合、プッシュダウン現象ではなく、プッシュアップ現象が起こる。

【0047】

実施形態においてはデータ線駆動回路200がソース信号Sおよびゲート信号Gを供給する構成を説明したが、ソース信号Sおよびゲート信号Gは、それぞれ別の回路により供給されてもよい。

【0048】

図10は、プロジェクター2100の構成を示す図である。プロジェクター2100は、一実施形態にかかる電子機器の一例である。プロジェクター2100の内部には、ハロゲンランプ等の白色光源からなるランプユニット2102が設けられている。ランプユニット2102から射出された投射光は、内部に配置された3枚のミラー2106および2枚のダイクロイックミラー2108によってR(赤)色、G(緑)色、B(青)色の3原色に分離されて、各原色に対応するライトバルブ100R、100Gおよび100Bにそれぞれ導かれる。なお、B色の光は、他のR色やG色と比較すると、光路が長いので、その損失を防ぐために、入射レンズ2122、リレーレンズ2123および出射レンズ2124からなるリレーレンズ系2121を介して導かれる。

【0049】

プロジェクター2100では、実施形態に係る電気光学装置1が、R色、G色、B色のそれぞれに対応して3組設けられる。そして、R色、G色、B色のそれぞれに対応する映像データがそれぞれ上位回路から供給されて、各色に対応するデータ信号Vidに変換される構成となっている。ライトバルブ100R、100Gおよび100Bの構成は、上述した液晶パネル100と同様であり、R色、G色、B色のそれぞれに対応する映像信号に応じて駆動される。

【0050】

ライトバルブ100R、100G、100Bによってそれぞれ変調された光は、ダイクロイックプリズム2112に3方向から入射する。ダイクロイックプリズム2112において、R色およびB色の光は90度に屈折する一方、G色の光は直進する。したがって、各色の画像が合成された後、スクリーン2120には、投射レンズ2114によってカラー画像が投射される。

【0051】

なお、ライトバルブ100R、100Gおよび100Bには、ダイクロイックミラー2108によって、R色、G色、B色のそれぞれに対応する光が入射するので、カラーフィルターを設ける必要はない。また、ライトバルブ100R、100Bの透過像は、ダイクロイックプリズム2112により反射した後に投射されるのに対し、ライトバルブ100Gの透過像はそのまま投射されるので、ライトバルブ100R、100Bによる水平走査方向は、ライトバルブ100Gによる水平走査方向と逆向きにして、左右を反転させた像を表示する構成となっている。

【0052】

この電子機器は、図10で説明したプロジェクターの他、電子ビューファインダーや、リヤ・プロジェクション型のテレビジョン、ヘッドマウントディスプレイなどであってもよい。

【符号の説明】

【0053】

1…電気光学装置、100R・100G・100B…ライトバルブ、100…液晶パネル、101…素子基板、102…対向基板、105…液晶、107…コネクタ、108…共通電極、110…画素領域、111…画素、112…走査線、114…データ線、116…TFT、117…保持容量、118…画素電極、120…液晶層、130…走査線駆動回路、141…ゲート信号線、142…ゲート信号線、143…ゲート信号線、146…ゲート信号入力端子、147…ゲート信号入力端子、148…ゲート信号入力端子、150…データ線選択回路、151…スイッチング回路、152…TFT、153…TFT、154…TFT、160…ソース信号線、161…ソース信号入力端子、200…データ線駆動回路、300…FPC基板、310…コネクタ、320…コネクタ、400…回路基板、410…コネクタ、2100…プロジェクター、2102…ランプユニット、2106…ミラー、2108…ダイクロイックミラー、2114…投射レンズ、2120…スクリーン、2121…リレーレンズ系、2122…入射レンズ、2123…リレーレンズ、2124…出射レンズ

【特許請求の範囲】

【請求項1】

ゲート信号が入力されるゲート信号入力端子と、

前記ゲート信号入力端子に接続され、前記ゲート信号が供給されるゲート信号線と、

ソース信号が入力される複数のソース信号入力端子と、

前記複数のソース信号入力端子の各々に接続され、前記ソース信号が供給される複数のソース信号線と、

前記ゲート信号線に接続されたゲート電極、および前記複数のソース信号線のうち第1ソース信号線に接続されたソース電極を有する第1トランジスター群と、

前記ゲート信号入力端子から見て前記第1トランジスター群よりも下流側の位置において前記ゲート信号線に接続されたゲート電極、および前記複数のソース信号線のうち第2ソース信号線に接続されたソース電極を有する第2トランジスター群と、

前記第1ソース信号線において前記ソース電極と前記ソース信号入力端子との間に挿入された第1抵抗と、

前記第2ソース信号線において前記ソース電極と前記ソース信号入力端子との間に挿入され、前記第1抵抗と異なる抵抗値を有する第2抵抗と

を有する電気光学装置。

【請求項2】

前記第1抵抗の抵抗値が、前記第2抵抗の抵抗値よりも小さい

ことを特徴とする請求項1に記載の電気光学装置。

【請求項3】

前記第1トランジスター群および前記第2トランジスター群を含む複数のトランジスター群と、

前記複数のトランジスター群の各々に対応し、前記第1抵抗および前記第2抵抗を含む複数の抵抗と

を有し、

前記複数の抵抗の抵抗値は、当該抵抗に対応するトランジスター群が前記ゲート信号線に接続されている位置が前記ゲート信号入力端子から見て下流側になるほど大きい

ことを特徴とする請求項2に記載の電気光学装置。

【請求項4】

前記第1トランジスター群は、複数のトランジスターを含み、

前記第1ソース信号線は、前記抵抗と前記複数のトランジスターとの間で複数に分岐している

ことを特徴とする請求項1ないし3のいずれか一項に記載の電気光学装置。

【請求項5】

前記第1抵抗および前記第2抵抗は、ある長さ、幅、および厚さを有する抵抗素子により形成され、

前記第1抵抗および前記第2抵抗は、前記長さ、前記幅、および前記厚さの少なくとも1つが異なっている

ことを特徴とする請求項1ないし4のいずれか一項に記載の電気光学装置。

【請求項6】

請求項1ないし5のいずれか一項に記載の電気光学装置を有する電子機器。

【請求項1】

ゲート信号が入力されるゲート信号入力端子と、

前記ゲート信号入力端子に接続され、前記ゲート信号が供給されるゲート信号線と、

ソース信号が入力される複数のソース信号入力端子と、

前記複数のソース信号入力端子の各々に接続され、前記ソース信号が供給される複数のソース信号線と、

前記ゲート信号線に接続されたゲート電極、および前記複数のソース信号線のうち第1ソース信号線に接続されたソース電極を有する第1トランジスター群と、

前記ゲート信号入力端子から見て前記第1トランジスター群よりも下流側の位置において前記ゲート信号線に接続されたゲート電極、および前記複数のソース信号線のうち第2ソース信号線に接続されたソース電極を有する第2トランジスター群と、

前記第1ソース信号線において前記ソース電極と前記ソース信号入力端子との間に挿入された第1抵抗と、

前記第2ソース信号線において前記ソース電極と前記ソース信号入力端子との間に挿入され、前記第1抵抗と異なる抵抗値を有する第2抵抗と

を有する電気光学装置。

【請求項2】

前記第1抵抗の抵抗値が、前記第2抵抗の抵抗値よりも小さい

ことを特徴とする請求項1に記載の電気光学装置。

【請求項3】

前記第1トランジスター群および前記第2トランジスター群を含む複数のトランジスター群と、

前記複数のトランジスター群の各々に対応し、前記第1抵抗および前記第2抵抗を含む複数の抵抗と

を有し、

前記複数の抵抗の抵抗値は、当該抵抗に対応するトランジスター群が前記ゲート信号線に接続されている位置が前記ゲート信号入力端子から見て下流側になるほど大きい

ことを特徴とする請求項2に記載の電気光学装置。

【請求項4】

前記第1トランジスター群は、複数のトランジスターを含み、

前記第1ソース信号線は、前記抵抗と前記複数のトランジスターとの間で複数に分岐している

ことを特徴とする請求項1ないし3のいずれか一項に記載の電気光学装置。

【請求項5】

前記第1抵抗および前記第2抵抗は、ある長さ、幅、および厚さを有する抵抗素子により形成され、

前記第1抵抗および前記第2抵抗は、前記長さ、前記幅、および前記厚さの少なくとも1つが異なっている

ことを特徴とする請求項1ないし4のいずれか一項に記載の電気光学装置。

【請求項6】

請求項1ないし5のいずれか一項に記載の電気光学装置を有する電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−133097(P2012−133097A)

【公開日】平成24年7月12日(2012.7.12)

【国際特許分類】

【出願番号】特願2010−284654(P2010−284654)

【出願日】平成22年12月21日(2010.12.21)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成24年7月12日(2012.7.12)

【国際特許分類】

【出願日】平成22年12月21日(2010.12.21)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]