電気光学装置および電子機器

【課題】複数の信号線駆動回路が配線ブロック内の各信号線への階調電圧の印加順序の更新制御を行う電子機器において、各信号線駆動回路間で階調電圧の印加順序が不一致になることを防止する。

【解決手段】電気光学装置100R、100Gおよび100Bの各制御回路30は、互いに非同期に階調電圧の印加順序の更新制御を行う。ホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に対し、階調電圧の印加順序の更新周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングで、初期化用同期信号ISYNCを供給し、電気光学装置100R、100Gおよび100Bの各制御回路30において、階調電圧の印加順序の更新制御の動作を一斉に初期化させる。

【解決手段】電気光学装置100R、100Gおよび100Bの各制御回路30は、互いに非同期に階調電圧の印加順序の更新制御を行う。ホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に対し、階調電圧の印加順序の更新周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングで、初期化用同期信号ISYNCを供給し、電気光学装置100R、100Gおよび100Bの各制御回路30において、階調電圧の印加順序の更新制御の動作を一斉に初期化させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶パネル等の電気光学装置を利用して画像を表示する技術に関する。

【背景技術】

【0002】

周知のように、液晶パネル等の電気光学装置は、複数の信号線と複数の走査線との各交差に対応して画素回路が設けられている。このような電気光学装置では、1本の走査線に対応付けられた全ての画素回路に対する画像信号の書き込みを一水平走査期間内に完了させる必要がある。従って、1本の走査線に対応付けられた画素回路の数が多くなると、1個の画素回路への画像信号の書き込みに利用可能な時間が短くなり、要求される表示品質を実現するのが困難になる。

【0003】

そこで、表示品質を劣化させることなく、電気光学装置の高精細化を実現するための手段として、次の技術が採用されるに至った。すなわち、電気光学装置の複数の信号線を各々所定本数の信号線からなる複数の配線ブロックに分け、配線ブロック毎に、配線ブロック内の各信号線を順次選択して階調電圧の印加を行う技術である。

【0004】

この技術によれば、一水平走査期間内に、配線ブロック内の複数の信号線への階調電圧の印加を複数のブロックにおいて並列的に進めるので、電気光学装置全体としての信号線の本数が多い場合でも、信号線1本当たりの階調電圧の印加時間を十分に長くすることができる。従って、表示品質を劣化させることなく、電気光学装置の高精細化を実現することができる。

【0005】

しかしながら、この技術を採用した場合、以下に述べる問題が発生する。すなわち、一水平走査期間内において配線ブロック内の各信号線を順次選択して各画素の画像信号に応じた階調電圧の印加を行う場合、たとえ同じ値の画像信号に対応した階調電圧を各信号線に印加する場合でも、各信号線に接続された各画素回路の液晶の透過率は厳密には同じ値にならず、電気光学装置の表示画像に表示ムラが発生するのである。

【0006】

そこで、この問題を解決するための手段として、例えば特許文献1は、駆動回路による各画素回路の駆動条件、具体的には一水平走査期間内における配線ブロック内の各信号線への階調電圧の印加順序を、垂直走査周期に同期しあるいは水平走査周期に同期して切り換える技術を提案している。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2004−45967号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

特許文献1に開示されているように、配線ブロック内の各信号線への階調電圧の印加順序の更新制御を例えば垂直走査周期に同期して行うと、複数の垂直走査期間を通じて見た場合に、各画素回路の液晶の透過率が各信号線間で均一化される。このため、電気光学装置の表示画像に現れる表示ムラが軽減される。各信号線への階調電圧の印加順序の更新を水平走査周期に同期して行う場合も同様である。このように、1個の電気光学装置に着目した場合には、各信号線への階調電圧の印加順序の更新を行う技術は、表示ムラを軽減する効果を奏する。

【0009】

しかしながら、例えば投射型表示装置のように、複数の電気光学装置(液晶ライトバルブ)を用いて画像表示を行う電子機器において、各電気光学装置では、互いに独立して駆動回路の駆動条件の更新制御、具体的には配線ブロック内の各信号線への階調電圧の印加順序の更新制御を実行する。従って、各液晶ライトバルブ間で階調電圧の印加順序の更新制御にいわば位相ずれが発生し、ある水平走査周期において、R色に対応した液晶ライトバルブでは、配線ブロック内の各信号線を例えば第1信号線、第2信号線、第3信号線、第4信号線という順に選択して階調電圧を印加するのに対し、同じ水平走査期間にG色に対応した液晶ライトバルブでは、配線ブロック内の各信号線を第3信号線、第4信号線、第1信号線、第2信号線という順に選択して階調電圧を印加する場合も起こり得る。

【0010】

この場合、R色に対応した液晶ライトバルブとG色に対応した液晶ライトバルブとでは、一水平走査期間内における第1信号線への階調電圧の印加タイミングと第3信号線への階調電圧の印加タイミングと位置関係が逆になっている。このため、例えば投射画像における第1信号線に対応した部分に関しては、G色よりR色が強調され易くなり、第3信号線に対応した部分に関しては、R色よりG色が強調され易くなる、といったことが起こり得る。このように配線ブロック内の各信号線への階調電圧の印加順序がR、G、Bの各色に対応した各液晶ライトバルブ間で異なると、各信号線に対応した投射画像の色バランスが信号線間で異なり、投射画像に色つきが発生するのである。

【0011】

このような問題は、投射型表示装置以外の他の装置においても生じる。例えば画素部を複数の領域に分割し、領域毎に異なる信号線駆動回路が各領域内の信号線を駆動する構成の電気光学装置がある。このような電気光学装置において、各信号線駆動回路の駆動対象である複数の信号線を複数の配線ブロックに分け、信号線駆動回路が配線ブロック毎に配線ブロック内の各信号線を順次選択して画像信号を供給し、かつ、各信号線への階調電圧の印加順序を例えば垂直走査周期に同期して切り換えるように構成することが考えられる。この場合において、隣り合う2つの領域の駆動を行う2つの信号線駆動回路における配線ブロック内の各信号線への階調電圧の印加順序が異なったものであると、電気光学装置の表示画像に表示ムラが発生する。

【0012】

以上述べた例の他にも、表示品質の向上等の目的のために、例えば複数の電気光学装置間で、互いに独立に駆動回路による各画素回路の駆動条件の更新制御を進める場合がある。この場合も、例えばノイズ等の影響により、各電気光学装置間で駆動条件の更新制御のいわば位相ずれが生じると、同様な問題が発生する。

【0013】

この発明は、以上説明した事情に鑑みてなされたものであり、複数の駆動回路による画素部の駆動条件の更新制御を互いに独立して進める電気光学装置または電子機器において、各駆動回路間で駆動条件に不一致が生じることを防止する技術的手段を提供することを解決課題とする。

【課題を解決するための手段】

【0014】

上述した課題を解決するため、この発明は、互いに交差する複数の走査線および複数の信号線を有するとともに、前記複数の走査線と前記複数の信号線との各交差に対応して各々配置された複数の画素回路を有する画素部と、一垂直走査期間内に前記複数の走査線を順次選択し、選択した走査線と前記複数の信号線との各交差に対応付けられた複数の画素回路を前記複数の信号線に接続する走査線駆動回路と、前記複数の信号線を複数の配線ブロックに分け、配線ブロック毎に、一水平走査期間内に当該配線ブロックに属する各信号線を順次選択し、選択した信号線に階調電圧を印加する信号線駆動回路と、前記複数の配線ブロックにおける配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を実行する制御回路とを各々具備する複数の電気光学装置と、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を一斉に初期化する動作を時間を空けて繰り返すことにより、前記複数の電気光学装置の各々における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を同期化する同期化手段とを具備することを特徴とする電子機器を提供する。

【0015】

かかる電子機器によれば、同期化手段が複数の制御回路の各々による配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を一斉に初期化する動作を時間を空けて繰り返し実行することにより、複数の制御回路の各々による配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御が同期化する。従って、各電気光学装置間で配線ブロック内の複数の信号線への階調電圧の印加順序に不一致が生じることを防止することができる。

【0016】

好ましい態様において、前記同期化手段は、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を一斉に初期化する動作を繰り返す。

【0017】

この態様によれば、各電気光学装置において配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御の周期性を極力損なうことなく、各電気光学装置間で配線ブロック内の複数の信号線への階調電圧の印加順序に不一致が生じることを防止することができる。

【0018】

また、この発明は、互いに交差する複数の走査線および複数の信号線を有するとともに、前記複数の走査線と前記複数の信号線との各交差に対応して各々配置された複数の画素回路を各々有する複数の画素部と、前記複数の画素部の各画素部における前記複数の走査線を一垂直走査期間内に順次選択し、選択した走査線と前記複数の信号線との各交差に対応付けられた複数の画素回路を前記複数の信号線に接続する走査線駆動手段と、前記複数の画素部に各々対応付けられた複数の信号線駆動回路であって、各画素部の前記複数の信号線を複数の配線ブロックに分け、配線ブロック毎に、一水平走査期間内に当該配線ブロックに属する各信号線を順次選択し、選択した信号線に階調電圧を印加する複数の信号線駆動回路と、前記複数の信号線駆動回路の各々における前記複数の配線ブロックにおける配線ブロック内の複数の信号線への階調電圧の印加順序を各々周期的に更新する複数の制御回路と、前記複数の制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を一斉に初期化する動作を時間を空けて繰り返し実行する同期化手段とを具備することを特徴とする電気光学装置を提供する。

【0019】

かかる電気光学装置によれば、同期化手段が複数の制御回路の各々による配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を一斉に初期化する動作を時間を空けて繰り返し実行することにより、複数の制御回路の各々による配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御が同期化する。従って、複数の画素部間で配線ブロック内の複数の信号線への階調電圧の印加順序に不一致が生じることを防止することができる。

【0020】

また、実施の形態からは、以下の発明を把握することができる。この発明は、複数の画素部と、前記複数の画素部を各々駆動する複数の駆動回路と、前記複数の駆動回路の各々による画素部の駆動条件の周期的な更新制御を互いに独立に実行する複数の制御回路と、前記複数の制御回路の各々による駆動条件の更新制御を一斉に初期化する動作を時間を空けて繰り返し実行することにより、前記複数の制御回路の各々による駆動条件の更新制御を同期化する同期化手段とを具備することを特徴とする電子機器を提供する。

【0021】

かかる電子機器によれば、同期化手段が複数の制御回路の各々による駆動条件の更新制御を一斉に初期化する動作を時間を空けて繰り返し実行することにより、複数の制御回路の各々による駆動条件の更新制御が同期化する。従って、各駆動回路間で駆動条件に不一致が生じることを防止することができる。

【0022】

好ましい態様において、前記同期化手段は、前記複数の制御回路の各々による駆動条件の周期的な更新制御の周期の整数倍の長さの周期で、前記複数の制御回路の各々による駆動条件の更新制御を一斉に初期化する動作を繰り返す。

【0023】

ここで、同期化手段により駆動条件の更新制御を一斉に初期化する動作が行われると、複数の駆動回路の駆動条件は初期状態となり、その後、複数の制御回路では、この初期状態から駆動条件の更新制御が進められる。そして、各制御回路による駆動条件の更新制御が支障なく進行する場合、初期化後、駆動条件の更新制御の一周期に相当する時間が経過したとき、複数の駆動回路の駆動条件は同じ初期状態に戻る。このとき、同期化手段により駆動条件の更新制御を一斉に初期化する動作が行われるが、その際に各駆動回路の駆動条件は初期状態になるので、この初期化の動作は各制御回路および各駆動回路の動作に全く影響を与えない。従って、各駆動回路の駆動条件の更新制御の周期性が損なわれない。一方、初期化後、例えばノイズの影響により、複数の制御回路の中のいずれかの制御回路による駆動条件の更新制御に誤動作が生じた場合、初期化から駆動条件の更新制御の一周期に相当する時間が経過したとき、複数の駆動回路のうち誤動作しなかった制御回路の制御下にある駆動回路の駆動条件は初期状態に戻るが、誤動作した制御回路の制御下にある駆動回路の駆動条件は初期状態に戻らない。このとき、同期化手段により駆動条件の更新制御の動作を一斉に初期化する動作が行われると、全ての駆動回路の駆動条件が初期状態になる。従って、この態様によれば、各駆動回路の駆動条件の更新制御の周期性を極力損なうことなく、各駆動回路間で駆動条件に不一致が生じることを防止することができる。

【図面の簡単な説明】

【0024】

【図1】この発明の第1実施形態である投射型表示装置の構成を示す模式図である。

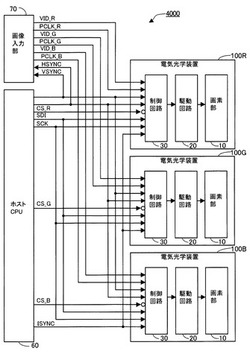

【図2】同投射型表示装置の電気的構成を示すブロック図である。

【図3】同投射型表示装置における電気光学装置の画素部、駆動回路および制御回路の構成を示すブロック図である。

【図4】同電気光学装置の画素回路の構成を示す回路図である。

【図5】同電気光学装置の信号線駆動回路の構成を示すブロック図である。

【図6】同電気光学装置の制御回路の構成を示すブロック図である。

【図7】同制御回路のパターンジェネレーターに記憶された選択パターンデータの内容を例示する図である。

【図8】同実施形態の動作を示すタイムチャートである。

【図9】同実施形態において行われる配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の様子を例示する図である。

【図10】同実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図11】この発明の第2実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図12】この発明の第3実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図13】この発明の第4実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図14】この発明の第5実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図15】この発明の第6実施形態である投射型表示装置の構成を示す模式図である。

【図16】同実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図17】この発明の第7実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図18】この発明の第8実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図19】この発明の第9実施形態である電気光学装置の構成を示すブロック図である。

【図20】この発明の適用例である他の電子機器の形態(パーソナルコンピューター)を示す斜視図である。

【図21】この発明の適用例である他の電子機器の形態(携帯電話機)を示す斜視図である。

【発明を実施するための形態】

【0025】

<1.第1実施形態>

図1は、この発明による電子機器の第1実施形態である投射型表示装置(3板式のプロジェクタ)4000の構成を示す模式図である。この投射型表示装置4000は、相異なる表示色R、G、Bに各々対応する3個の電気光学装置100(100R,100G,100B)を含んでいる。照明光学系4001は、照明装置(光源)4002からの出射光のうち赤色成分rを電気光学装置100Rに供給し、緑色成分gを電気光学装置100Gに供給し、青色成分bを電気光学装置100Bに供給する。各電気光学装置100は、照明光学系4001から供給される各単色光を表示画像に応じて変調する光変調器(ライトバルブ)として機能する。投射光学系4003は、各電気光学装置100からの出射光を合成して投射面4004に投射する。

【0026】

図2は投射型表示装置4000の電気的構成を示すブロック図である。図2に示すように、投射型表示装置4000は、電気光学装置100R、100Gおよび100Bと、外部から画像信号を取り込む画像入力部70と、これらを制御するホストCPU60とを有している。電気光学装置100R、100Gおよび100Bの各々は、画素部10と、駆動回路20と、制御回路30とを有する。ここで、制御回路30は、ホストCPU60から供給される各種の制御信号に従い、駆動回路20等の電気光学装置内の各部を制御する回路である。

【0027】

ホストCPU60は、垂直同期信号VSYNCおよび水平同期信号HSYNCを画像入力部70に供給するとともに、電気光学装置100R、100Gおよび100Bの各々の制御回路30に供給する。画像入力部70は、垂直同期信号VSYNCが与えられる毎に、外部から取り込んだ画像信号に基づいて、1フレーム分のR、G、Bの各色の画像信号VID_R、VID_G、VID_Bを生成する。そして、画像入力部70は、水平同期信号HSYNCが与えられる毎に、1ライン分の各画素の画像信号VID_Rを画素クロックPCLK_Rに同期させて電気光学装置100Rの制御回路30に供給し、1ライン分の各画素の画像信号VID_Gを画素クロックPCLK_Gに同期させて電気光学装置100Gの制御回路30に供給し、1ライン分の各画素の画像信号VID_Bを画素クロックPCLK_Bに同期させて電気光学装置100Bの制御回路30に供給する。

【0028】

また、ホストCPU60と電気光学装置100R、100Gおよび100Bの各々との間には3線(CS、SDI、SCK)のシリアルインタフェースが設けられている。ホストCPU60は、電気光学装置100Rの制御回路30に対して送信すべきデータがある場合、チップセレクト信号CS_RをアクティブレベルであるLレベルとし、その間にシリアルクロックSCKに同期させてシリアルデータSDIを出力する。電気光学装置100Rの制御回路30は、チップセレクト信号CS_Rがアクティブレベルであることから、シリアルデータSDIをシリアルクロックSCKにより取り込む。同様にホストCPU60は、電気光学装置100G(100B)の制御回路30に対して送信すべきデータがある場合、チップセレクト信号CS_G(CS_B)をアクティブレベルであるLレベルとし、その間にシリアルクロックSCKに同期させてシリアルデータSDIを出力する。電気光学装置100G(100B)の制御回路30は、チップセレクト信号CS_G(CS_B)がアクティブレベルであることから、シリアルデータSDIをシリアルクロックSCKにより取り込む。

【0029】

また、ホストCPU60は、所定周期毎に初期化用同期信号ISYNCを電気光学装置100R、100Gおよび100Bの各々の制御回路30に供給する機能を有している。なお、この初期化用同期信号ISYNCの役割については後述する。

【0030】

図3は、1個の電気光学装置100における画素部10、駆動回路20および制御回路30の構成を示すブロック図である。図3に示すように、画素部10は、複数の画素回路PIXが平面状に配列されてなるものである。駆動回路20は、各画素回路PIXを駆動する回路であり、走査線駆動回路22と信号線駆動回路24とを含んでいる。

【0031】

画素部10には、相互に交差するM本の走査線12とN本の信号線14とが形成されている(M,Nは自然数)。複数の画素回路PIXは、各走査線12と各信号線14との交差に対応して設けられており、縦M行×横N列の行列状に配列されている。そして、画素部10内のN本の信号線14は、相隣接するK本(Kは2以上の自然数)を単位としてJ個の配線ブロックB[1]〜B[J]に区分されている(J=N/K)。

【0032】

図4は、各画素回路PIXの構成を示す回路図である。図4に示すように、各画素回路PIXは、液晶素子42と選択スイッチ44とを含んでいる。液晶素子42は、相対向する画素電極421および共通電極423と両電極間の液晶425とで構成された電気光学素子である。画素電極421と共通電極423との間の印加電圧に応じて液晶425の透過率が変化する。なお、以下の説明では便宜的に、画素電極421が共通電極423と比較して高電位である場合の液晶素子42の印加電圧を正極性と表記し、画素電極421が低電位である場合の印加電圧を負極性と表記する。

【0033】

選択スイッチ44は、走査線12にゲートが接続されたNチャネル型の薄膜トランジスターで構成され、液晶素子42(画素電極421)と信号線14との間に介在して両者の電気的な接続(導通/非導通)を制御する。従って、画素回路PIX(液晶素子42)は、選択スイッチ44がON状態であるときの信号線14の電圧(後述の階調電圧VG)に応じた階調を表示する。

以上が図3における各画素回路PIXの構成である。

【0034】

図3において、走査線駆動回路22は、制御回路3から内部水平同期信号HSが出力されるのに応じて、各走査線12に対する走査信号G[1]〜G[M]を一水平走査期間Hずつ順次アクティブレベルとし、M本の走査線12の各々を順次に選択する。ここで、第m行に対応した走査信号G[m]がアクティブレベルである期間は、第m行のN個の画素回路PIXの各選択スイッチ44がON状態となり、これらの選択スイッチ44を各々介してN本の信号線14が第m行のN個の画素回路PIXの各画素電極421に各々接続される。

【0035】

信号線駆動回路24は、走査線駆動回路22による各走査線12の選択に同期してN本の信号線14の各々を駆動する回路である。図5は、この信号線駆動回路24の構成を示すブロック図である。上述したように、画素部10内のN本の信号線14は、J個の配線ブロックB[1]〜B[J]に区分されている。信号線駆動回路24には、このJ個の配線ブロックB[1]〜B[J]に各々対応付けて、J個のデマルチプレクタ57[1]〜57[J]と、J個の駆動電圧発生回路56[1]〜56[J]と、J個のマルチプレクタ53[1]〜53[J]とが設けられている。また、信号線駆動回路24には、画像信号記憶部51が設けられている。この画像信号記憶部51は、1ラインを構成するN画素分のデジタル形式の画像信号VIDを各々記憶するN個のレジスター(図示略)により構成されている。このN個のレジスターは、J個の配線ブロックB[1]〜B[J]に対応付けて、各々K(=N/J)個のレジスターからなるレジスターブロック52[1]〜52[J]に区分されている。

【0036】

マルチプレクサー53[j](j=1〜J)の各々は、K個のスイッチ54[1]〜54[K]により構成されている。ここで、j番目の配線ブロックB[j]に対応した1個のマルチプレクサー53[j]に着目すると、K個のスイッチ54[1]〜54[K]の各々の一方の接点には、j番目のレジスターブロック52[j]に記憶されたK画素分の画像信号の各々がK本の信号線17を各々介して供給される。また、このK個のスイッチ54[1]〜54[K]の各々の他方の接点は、1本の信号線16に共通接続され、同信号線16を介してj番目の駆動電圧発生回路56[j]の入力端子に接続されている。

【0037】

各マルチプレクサー53[j](j=1〜J)のK個のスイッチ54[1]〜54[K]のON/OFFは、制御回路30が出力するK個の選択信号SELa[1]〜SELa[K]により各々切り換えられる。ここで、1個の選択信号SELa[k]がアクティブレベル、他のK−1個の選択信号SELa[k’](k’≠k)が非アクティブレベルである場合には、マルチプレクサー53[j](j=1〜J)に各々属するJ個のスイッチ54[k]のみがONとなる。従って、マルチプレクサー53[j](j=1〜J)の各々は、各々に対応するレジスターブロック52[j]に記憶された水平方向K画素分の画像信号のうちj番目の画素の画像信号を画像信号D[j]として選択し、信号線16を介して各々に対応した駆動電圧発生回路56[j]に供給する。

【0038】

駆動電圧発生回路56[1]〜56[J]は、プリチャージ電圧を発生する機能と、信号線16を介して供給される画像信号D[1]〜D[J]に各々対応した階調電圧を発生する機能とを有する。駆動電圧発生回路56[1]〜56[J]は、一水平走査期間Hをプリチャージ期間TPREと書込期間TWRTとに分け、プリチャージ期間TPREはプリチャージ電圧を、書込期間TWRTは画像信号D[1]〜D[J]に応じた階調電圧を信号線駆動信号C[1]〜C[J]としてJ本の信号線15に各々出力する。

【0039】

デマルチプレクサー57[j](j=1〜J)の各々は、K個のスイッチ58[1]〜58[K]により構成されている。ここで、j番目の配線ブロックB[j]に対応した1個のデマルチプレクサー57[j]に着目すると、K個のスイッチ54[1]〜54[K]の各々の一方の接点は、1本の信号線15に共通接続され、同信号線15を介してj番目の駆動電圧発生回路56[j]の出力端子に接続されている。また、このK個のスイッチ54[1]〜54[K]の各々の他方の接点は、j番目の配線ブロックB[j]を構成するK本の信号線14に各々接続されている。

【0040】

各デマルチプレクサー57[j](j=1〜J)のK個のスイッチ58[1]〜58[K]のON/OFFは、制御回路30が出力するK個の選択信号SELb[1]〜SELb[K]により各々切り換えられる。ここで、1個の選択信号SELb[k]がアクティブレベル、他のK−1個の選択信号SELb[k’](k’≠k)が非アクティブレベルである場合には、デマルチプレクサー57[j](j=1〜J)に各々属するJ個のスイッチ58[k]のみがONとなる。従って、デマルチプレクサー57[j](j=1〜J)の各々は、駆動電圧発生回路56[1]〜56[J]から出力される信号線駆動信号C[1]〜C[J]を各配線ブロックB[1]〜B[J]のk番目の信号線14に各々出力する。

以上が図3における信号線駆動回路24の構成である。

【0041】

図3において、制御回路30は、画像信号VID、極性信号POL、選択信号SELa[k](k=1〜K)、SELb[k](k=1〜K)および電気光学装置100内の各部を制御するための各種の制御信号を発生する回路である。図6は、この制御回路30の一部の構成を示すブロック図である。図6に示すように、制御回路30は、制御信号処理部31と、カウンター32および33と、加算器34と、パターンジェネレーター35とを有する。

【0042】

制御信号処理部31には、ホストCPU60(図2参照)から3線シルアルインタフェースを介してチップセレクト信号CS、シリアルデータSDIおよびシリアルクロックSCKが供給される。制御信号処理部31は、チップセレクト信号CSがアクティブレベルであるLレベルである期間、シリアルクロックSCKに同期してシリアルデータSDIを取り込む。シルアルデータSDIとして供給されるデータには、駆動回路20の駆動条件の設定を指示する各種のコマンドが含まれる。また、制御信号処理部31には、ホストCPU60(図2参照)から垂直同期信号VSYNCおよび水平同期信号HSYNCが供給される。また、制御信号処理部31には、画像入力部70(図2参照)から画面を構成する各画素の画像信号VIDが画素クロックPCLKに同期して供給される。制御信号処理部31は、この画素クロックPCLKにより画像データVIDを取り込む。

【0043】

制御信号処理回路31は、垂直同期信号VSYNCが供給されるのに応じて内部垂直同期信号VSを出力する。また、制御信号処理回路31は、水平同期信号HSYNCが供給されるのに応じて内部水平同期信号HSを出力する。そして、制御信号処理回路31は、この内部水平同期信号HSを出力する都度、ホストCPU60から取り込んだ1ライン分(N画素分)の各画素の画像信号VIDを信号線駆動回路24に出力する。信号線駆動回路24では、このN画素分の画像信号VIDが各々K画素分の画像信号からなるJ個のブロックに区分され、上述したレジスターブロック52[1]〜52[J]に各々格納される。

【0044】

カウンター32は、内部水平同期信号HSの立ち上がりエッジが発生する都度、制御信号処理部31から与えられるステップ値STP1だけカウント値CNT1を増加させるカウンターである。また、カウンター33は、内部垂直同期信号VSの立ち上がりエッジが発生する都度、制御信号処理部31から与えられるステップ値STP2だけカウント値CNT2を増加させるカウンターである。ここで、ステップ値STP1およびSTP2は、ホストCPU60から受信されるコマンドに従って設定されるようになっている。加算器34は、カウンター32のカウント値CNT1とカウンター33のカウント値CNT2とを加算し、加算結果CNT1+CNT2を示すパターン番号PNをパターンジェネレーター35に出力する。

【0045】

カウンター32および33は、カウント値の初期化が可能な構成となっている。制御信号処理部31は、カウンター32のカウント値CNT1を「0」に初期化するための第1の初期化信号RES1を発生する機能と、カウンター33のカウント値CNT2を「0」に初期化するための第2の初期化信号RES2を発生する機能とを備えている。

【0046】

制御信号処理部31は、一垂直走査期間が終了して新たな垂直走査期間が始まるときに、第1の初期化信号RES1を発生してカウンター32のカウント値CNT1を「0」に初期化する。

【0047】

ホストCPU60から上述した初期化用同期信号ISYNCが供給された場合、制御信号処理部31は、第2の初期化信号RES2を発生してカウンター33のカウント値CNT2を「0」に初期化する。なお、ホストCPU60および制御信号処理部31間の初期化用同期信号ISYNCの伝送の詳細については後述する。

【0048】

パターンジェネレーター35は、水平走査期間Hをプリチャージ期間TPREと書込期間TWRTとに分け、期間毎に異なった態様で、選択信号SELa[1]〜SELa[K]および選択信号SELb[1]〜SELb[K]の切り換え制御を行う回路である。

【0049】

各水平走査期間Hのプリチャージ期間TPREにおいて、パターンジェネレーター35は、選択信号SELa[1]〜SELa[K]をLレベル、選択信号SELb[1]〜SELb[K]をHレベルとする。

【0050】

また、各水平走査期間Hの書込期間TWRTにおいて、パターンジェネレーター25は、配線ブロックB[1]〜B[J]の各々のK本の信号線14への階調電圧の印加を順次行わせるための選択信号SELa[1]〜SELa[K]および選択信号SELb[1]〜SELb[K]の切り換え制御を行う。

【0051】

この書込期間TWRT内における選択信号の切換制御を可能にするため、パターンジェネレーター35は、例えばK種類を選択パターンデータを記憶している。図7はこのK種類の選択パターンデータの内容を例示するものである。K種類の選択パターンデータには、0からK−1までのパターン番号PNが各々対応付けられている。

【0052】

個々の選択パターンデータは、書込期間TWRTにおいて配線ブロックB[1]〜B[K]の各々を構成するK本の信号線14への階調電圧の印加順序を指定するデータである。例えばパターン番号PN=「0」に対応した選択パターンデータは、書込期間TWRT内の最初の階調電圧印加期間U[1]に各配線ブロックの1番目の信号線14への階調電圧の印加を、2番目の階調電圧印加期間U[2]に2番目の信号線14への階調電圧の印加を、…、最後の階調電圧印加期間U[K]にK番目の信号線14への階調電圧の印加を行うことを指示している。また、パターン番号PN=「1」に対応した選択パターンデータは、書込期間TWRT内の最初の階調電圧印加期間U[1]に各配線ブロックのK番目の信号線14への階調電圧の印加を、2番目の階調電圧印加期間U[2]に1番目の信号線14への階調電圧の印加を、…、最後の階調電圧印加期間U[K]にK−1番目の信号線14への階調電圧の印加を行うことを指示している。

【0053】

パターンジェネレーター35は、各水平走査期間Hの書込期間TWRTにおいて、加算器34から与えられるパターン番号PNに対応した選択パターンデータに従って、選択信号SELa[1]〜SELa[K]および選択信号SELb[1]〜SELb[K]を変化させる。

【0054】

パターンジェネレーター35にK種類の選択パターンデータを記憶させる場合、カウンター32および33としては、0〜K−1の範囲内のカウントを行うカウンターが用いられる。また、加算器34としては、上述した加算結果CNT1+CNT2をKにより乗算した余りをパターン番号PNとして出力する構成のものが用いられる。

以上が制御回路30の構成である。

【0055】

図8は電気光学装置100の動作例を示すタイムチャートである。図8には、ある垂直走査期間V1内における各部の波形と、その次の垂直走査期間V2内の各部の波形が例示されている。本実施形態において、制御回路30は、垂直走査期間が切り換わる都度、極性信号POLを反転させる。図8に示す例における極性信号POLは、垂直走査期間V1では負極性(−)を指示しており、垂直走査期間V2では正極性(+)を指示している。ここで、極性信号POLが負極性(−)を指示する垂直走査期間V1では、正の電圧が上述した共通電極423に印加され、極性信号POLが正極性(+)を指示する垂直走査期間V2では、負の電圧が上述した共通電極423に印加される。

【0056】

各垂直走査期間において、走査線駆動回路22は、制御回路30の制御信号処理回路31が内部水平同期信号HSを発生するのに同期して、M本の走査線12を順次選択し、選択した走査線12に対応した走査信号G[j]を一水平走査期間Hに亙ってアクティブレベルであるHレベルとする。

【0057】

各水平走査期間Hのプリチャージ期間TPREにおいて、制御回路30のパターンジェネレーター35は、選択信号SELa[1]〜SELa[K]を全てLレベルとして、マルチプレクサー53[1]〜53[J]の全てのスイッチ54[1]〜54[K]をOFFにするとともに、選択信号SELb[1]〜SELb[K]を全てHレベルとして、デマルチプレクサー57[1]〜57[J]の全てのスイッチ58[1]〜58[K]をONにする。また、各水平走査期間Hのプリチャージ期間TPREにおいて、駆動電圧発生回路56[1]〜56[J]は、極性信号POLが示す極性のプリチャージ電圧を出力する。1個の駆動電圧発生回路56[j]が出力したプリチャージ電圧はデマルチプレクサー57[j]のK個のスイッチ58[1]〜58[J]を各々介して配線ブロックB[j]のK本の信号線14に印加される。従って、プリチャージ期間TPREにおいて、画素部10の全ての信号線14にプリチャージ電圧が印加される。

【0058】

各水平走査期間Hの書込期間TWRTにおいて、パターンジェネレーター35は、その時点におけるパターン番号PNに対応した選択信号パターンデータに従って選択信号SELa[1]〜SELa[K]および選択信号SELb[1]〜SELb[K]を変化させる。

【0059】

図8の下段左側には、垂直走査期間V1のある水平走査期間H(例えば垂直走査期間V1内のm番目の水平走査期間Hとする。)内に発生する選択信号SELa[1]〜SELa[K]および選択信号SELb[1]〜SELb[K]の波形が例示されている。この例では、階調電圧印加期間U[1]において、選択信号SELa[1]およびSELb[1]の組のみがHレベルとされ、マルチプレクサー53[1]〜53[J]におけるスイッチ54[1]と、デマルチプレクサー57[1]〜57[J]におけるスイッチ58[1]がONになる。この結果、レジスターブロック52[1]〜52[J]の各々における1番目の画素の画像信号VIDがマルチプレクサー53[1]〜53[J]のスイッチ54[1]を各々通過し、画像信号D[1]〜D[J]として駆動電圧発生回路56[1]〜56[J]に各々供給される。この時点において、極性信号POLは負極性(−)を指示しているので、駆動電圧発生回路56[1]〜56[J]は、基準電位VREFに対して負極性の範囲で、各々に供給される画像信号D[1]〜D[J]の指定階調に応じた階調電圧VGを各々出力する。駆動電圧発生回路56[1]〜56[J]が各々出力する階調電圧VGは、デマルチプレクサー57[1]〜57[J]におけるスイッチ58[1]を各々通過し、信号線駆動信号C[1]〜C[J]として配線ブロックB[1]〜B[J]の各々の1番目の信号線14に印加される。

【0060】

階調電圧印加期間U[2]では、選択信号SELa[2]およびSELb[2]の組のみがHレベルとされ、マルチプレクサー53[1]〜53[J]におけるスイッチ54[2]と、デマルチプレクサー57[1]〜57[J]におけるスイッチ58[2]がONになる。この結果、レジスターブロック52[1]〜52[J]の各々における2番目の画素の画像信号VIDに応じた各階調電圧VGが発生され、デマルチプレクサー57[1]〜57[J]におけるスイッチ58[2]を各々通過し、信号線駆動信号C[1]〜C[J]として配線ブロックB[1]〜B[J]の各々の2番目の信号線14に印加される。

【0061】

以下、同様であり、階調電圧印加期間U[3]では各レジスターブロックにおける3番目の画素の画像信号に応じた各階調電圧VGが各配線ブロックの3番目の信号線14に印加され、階調電圧印加期間U[4]では各レジスターブロックにおける4番目の画素の画像信号に応じた各階調電圧VGが各配線ブロックの4番目の信号線14に印加され、…、最後の階調電圧印加期間U[K]では各レジスターブロックにおけるK番目の画素の画像信号に応じた各階調電圧VGが各配線ブロックのK番目の信号線14に印加される。

以上が垂直走査期間V1のm番目の水平走査期間H内における各部の動作である。

【0062】

図8の下段右側には、垂直走査期間V1の次の垂直走査期間V2の同じ水平走査期間H(すなわち、垂直走査期間V2内のm番目の水平走査期間H)内に発生する選択信号SELa[1]〜SELa[K]および選択信号SELb[1]〜SELb[K]の波形が示されている。

【0063】

ここで、垂直走査期間V2におけるm番目の水平走査期間Hにおけるカウンター32のカウント値CNT1は、垂直走査期間V1におけるm番目の水平走査期間Hにおけるカウンター32のカウント値CNT1と同じになる。何故ならば、カウンター32のカウント値CNT1は、垂直走査期間が切り換わる毎に「0」に初期化されるからである。しかし、垂直走査期間V1から垂直走査期間V2に切り換わるとき、制御信号処理部31が出力する内部垂直同期信号VSにより、カウンター33のカウント値CNT2がステップ値STP2だけインクリメントされる。このため、垂直走査期間V2におけるm番目の水平走査期間Hにおいて、パターンジェネレーター35に与えられるパターン番号PNは、垂直走査期間V1におけるm番目の水平走査期間Hにおいて与えられるパターン番号PNと異なったものとなる。従って、垂直走査期間V2のm番目の水平走査期間Hの書込期間TWRTでは、垂直走査期間V1のm番目の水平走査期間Hの書込期間TWRTとは異なった順序で、各配線ブロックのK本の信号線14への階調電圧の印加が行われる。

【0064】

図8の下段右側に示す例では、書込期間TWRTの階調電圧印加期間U[1]では、各レジスターブロックにおけるK番目の画素の画像信号に応じた各階調電圧VGが各配線ブロックのK番目の信号線14に印加され、階調電圧印加期間U[2]では各レジスターブロックにおける1番目の画素の画像信号に応じた各階調電圧VGが各配線ブロックの1番目の信号線14に印加され、…、最後の階調電圧印加期間U[K]では各レジスターブロックにおけるK−1番目の画素の画像信号に応じた各階調電圧VGが各配線ブロックのK−1番目の信号線14に印加される。

【0065】

なお、垂直走査期間V2においては、極性信号POLは正極性(+)を指示しているので、駆動電圧発生回路56[1]〜56[J]は、基準電位VREFに対して正極性の範囲で、各々に供給される画像信号の指定階調に応じた階調電圧VGを各々出力する。

【0066】

以上のように、垂直走査期間V1のm番目の水平走査期間Hと垂直走査期間V2のm番目の水平走査期間Hとでは、異なる順序で、各配線ブロックのK本の信号線14への階調電圧の印加が行われる。このように本実施形態において各配線ブロックのK本の信号線14への階調電圧の印加の順序は、垂直走査期間の切り換わりに応じて変更されるが、それだけでなく、水平走査期間Hの切り換わりに応じて変更される。図9は、ステップ値STP1およびSTP2の両方が「1」である場合における各配線ブロック内のK本の信号線14への階調電圧の印加順序の変化の様子を例示するものである。図9において、縦方向は水平走査期間Hの遷移方向に対応しており、横方向は水平走査期間H内に発生するK個の階調電圧印加期間U[1]〜U[K]の並びに対応している。図9に示す例では、同一の垂直走査周期内において、配線ブロック内の各信号線14に階調電圧の印加が行われる順序は、水平走査期間Hが切り換わる毎に1番ずつ後方へローテートシフトされる。また、図9に示す例において、各垂直走査期間内の同一水平走査期間Hに着目すると、配線ブロック内の各信号線14に階調電圧の印加が行われる順序は、垂直走査期間が切り換わる毎に1番ずつ後方へローテートシフトされる。

【0067】

従って、複数の水平走査期間および複数の垂直走査期間を通じて見た場合に、各信号線14間で、一水平走査期間内における階調電圧の印加順序の時間平均値が均一化される。従って、電気光学装置単体として見た場合、表示ムラが軽減される。

【0068】

ところで、本実施形態による投射型表示装置では、3個の電気光学装置100R、100Gおよび100Rの各々において、独立して以上のような各信号線14への階調電圧の印加順序の更新制御が進められる。ここで、投射型表示装置の例えばパワーオン時に各電気光学装置100R、100Gおよび100Rの各々のカウンター32のカウント値CNT1およびカウンター33のカウント値CNT2を同時に初期化すれば、3個の電気光学装置100R、100Gおよび100R間で、各信号線14への階調電圧の印加順序の更新制御を初期状態から同時に開始させることができる。しかしながら、投射型表示装置の稼働中に発生するノイズ等の影響により、3個の電気光学装置100R、100Gおよび100R間で、カウンター32のカウント値CNT1またはカウンター33のカウント値CNT2に相違が発生する可能性がある。この場合、各信号線14への階調電圧の印加順序が3個の電気光学装置100R、100Gおよび100R間で異なったものとなる。この結果、上述したように表示画像に色つきが発生する。

【0069】

本実施形態の特徴は、このような問題の発生を防止するために、各配線ブロック内の複数の信号線14への階調電圧の印加順序の更新制御を電気光学装置100R、100Gおよび100R間で同期化させるための手段を投射型表示装置に設けた点にある。すなわち、本実施形態において、ホストCPU60は、上述した初期化用同期信号ISYNCを周期的に電気光学装置100R、100Gおよび100Bの各々の制御回路30に供給することにより階調電圧の印加順序の更新制御を電気光学装置100R、100Gおよび100R間で同期化させる。

【0070】

図10は本実施形態における初期化用同期信号ISYNCの発生タイミングを示すタイムチャートである。図10に示すようにホストCPU60は、階調電圧の印加順序の更新制御の周期の整数倍、すなわち、一垂直走査期間内の各水平走査期間における配線ブロック内のK本の信号線14への階調電圧の印加順序がある順序になってから再び同じ順序に更新されるまでに要する期間の整数倍の周期で発生するタイミングあって、垂直同期信号VSYNCに同期したタイミングにおいて発生する。例えば図9に示す例では、フレーム番号FN=FN0の画面の表示を行う垂直走査周期において、一垂直走査期間内の各水平走査期間における配線ブロック内のK本の信号線14への階調電圧の印加順序がある順序となり、その後、フレーム番号FN=FN0+K−1の画面の表示を行う垂直走査周期において、一垂直走査期間内の各水平走査期間における配線ブロック内のK本の信号線14への階調電圧の印加順序が再び同じ順序となる。従って、この場合の印加順序の更新制御の周期は、垂直走査期間のK倍の長さの周期であり、ホストCPU60は、垂直走査期間の例えばL×K倍(Lは整数)の周期で初期化用同期信号ISYNCを電気光学装置100R、100Gおよび100Bの各々の制御回路30に供給する。

【0071】

電気光学装置100R、100Gおよび100Bの各制御回路30の制御信号処理回路31は、ホストCPU60から初期化用同期信号ISYNCが与えられるのに応じて、第2の初期化信号RES2をアクティブレベルとし、カウンター33のカウント値CNT2を「0」に初期化する。

【0072】

このように本実施形態によれば、印加順序の更新制御の周期の整数倍の周期で発生し、かつ、垂直同期信号VSYNCに同期したタイミングで、ホストCPU60から電気光学装置100R、100Gおよび100Bの各制御回路30に初期化用同期信号ISYNCが供給され、各電気光学装置100R、100Gおよび100Bのカウンター33のカウント値CNT2が「0」に初期化される。従って、その後の垂直走査期間以降、電気光学装置100R、100Gおよび100B間では、同じ印加順序で、配線ブロック内のK本の信号線14への階調電圧の印加が行われ、色つきの発生が防止される。

【0073】

<2.第2実施形態>

本実施形態においても、上記第1実施形態と同様、ホストCPU60は、印加順序の更新制御の周期の整数倍の周期で電気光学装置100R、100Gおよび100Bの各々のカウンター33のカウント値CNT2を初期化するための処理を行う。本実施形態と上記第1実施形態との相違は、この初期化のために行うホストCPU60および各制御回路30間の信号の授受の手順にある。後述する第3〜第8実施形態も同様である。

【0074】

図11は本実施形態による投射型表示装置の動作を示すタイムチャートである。本実施形態において、ホストCPU60は、印加順序の更新制御の周期の整数倍の周期の切り換わりタイミングの所定時間前のタイミングになると、まず、電気光学装置100R、100Gおよび100Bの各制御回路30に対し、カウント値CNT2の初期化を命じる初期化コマンドを送る。具体的には、チップセレクト信号CS_Rをアクティブレベルとし、初期化コマンドの構成ビットからなるシリアルデータSDIをシリアルクロックSCKに同期させて出力し、このシリアルデータSDIを電気光学装置100Rの制御回路30に受信させる。次にチップセレクト信号CS_Rを非アクティブレベルに戻した後、チップセレクト信号CS_Gをアクティブレベルとし、初期化コマンドの構成ビットからなるシリアルデータSDIをシリアルクロックSCKに同期させて出力し、このシリアルデータSDIを電気光学装置100Gの制御回路30に受信させる。次にチップセレクト信号CS_Gを非アクティブレベルに戻した後、チップセレクト信号CS_Bをアクティブレベルとし、初期化コマンドの構成ビットからなるシリアルデータSDIをシリアルクロックSCKに同期させて出力し、このシリアルデータSDIを電気光学装置100Bの制御回路30に受信させるのである。

【0075】

このように電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを受信させた後、ホストCPU60は、印加順序の更新制御の周期の整数倍の周期の切り換わりタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、初期化用同期信号ISYNCを各制御回路30に供給する。本実施形態において、制御回路30内の制御信号処理部31は、初期化用同期信号ISYNCを事前に受信したコマンドの実行の指示と解釈する。この場合、電気光学装置100R、100Gおよび100Bの各制御信号処理部31は、初期化用同期信号ISYNCが供給される前に初期化コマンドを取り込んでいるので、初期化コマンドを実行し、カウンター33のカウント値CNT2を「0」に初期化する。

本実施形態においても上記第1実施形態と同様な効果が得られる。

【0076】

<3.第3実施形態>

図12は本実施形態による投射型表示装置の動作を示すタイムチャートである。本実施形態において、電気光学装置100Rの制御回路30は、チップセレクト信号CS_Rが非アクティブレベルからアクティブレベルになった後、シリアルクロックSCKに同期して伝送されてくる所定ビット数からなるシリアルデータSDIを当該制御回路30宛てのコマンドと認識して受信する。同様に、電気光学装置100G(100B)の制御回路30は、チップセレクト信号CS_G(CS_B)が非アクティブレベルからアクティブレベルになった後、シリアルクロックSCKに同期して伝送されてくる所定ビット数からなるシリアルデータSDIを当該制御回路30宛てのコマンドと認識して受信する。

【0077】

そこで、ホストCPU60は、印加順序の更新制御の周期の整数倍の周期の切り換わりタイミングの所定時間だけ前になったとき、次のようにして電気光学装置100R、100Gおよび100Bの各制御回路30宛てに初期化コマンドを送信する。まず、ホストCPU60は、チップセレクト信号CS_Rをアクティブレベルとし、初期化コマンドの構成ビットからなるシリアルデータSDIをシリアルクロックSCKに同期させて送出し、初期化コマンドを電気光学装置100Rの制御回路30に受信させる。次にホストCPU60は、チップセレクト信号CS_Rをアクティブレベルに維持した状態で、チップセレクト信号CS_Gをアクティブレベルとし、初期化コマンドの構成ビットからなるシリアルデータSDIをシリアルクロックSCKに同期させて送出し、初期化コマンドを電気光学装置100Gの制御回路30に受信させる。このとき電気光学装置100Rの制御回路30は、チップセレクト信号CS_Rがアクティブレベルになった後、所定ビット数からなる初期化コマンドを受信しているので、電気光学装置100Gの制御回路30宛ての初期化コマンドを誤って受信することはない。次にホストCPU60は、チップセレクト信号CS_RおよびCS_Gをアクティブレベルに維持した状態で、チップセレクト信号CS_Bをアクティブレベルとし、初期化コマンドの構成ビットからなるシリアルデータSDIをシリアルクロックSCKに同期させて送出し、初期化コマンドを電気光学装置100Bの制御回路30に受信させる。

【0078】

このようにして電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを受信させた後、ホストCPU60はチップセレクト信号CS_R、CS_GおよびCS_Bを同時にアクティブレベルから非アクティブレベルへ変化させる。本実施形態において、電気光学装置100Rの制御回路30の制御信号処理部31は、チップセレクト信号CS_Rのアクティブレベルから非アクティブレベルへの変化を初期化コマンドの実行指示と解釈し、カウント値CNT2の初期化を行う。同様に、電気光学装置100G(100B)の制御回路30の制御信号処理部31は、チップセレクト信号CS_G(CS_B)のアクティブレベルから非アクティブレベルへの変化を初期化コマンドの実行指示と解釈し、カウント値CNT2の初期化を行う。従って、本実施形態では、チップセレクト信号CS_R、CS_GおよびCS_Bが同時にアクティブレベルから非アクティブレベルに変化するタイミングにおいて、電気光学装置100R、100Gおよび100Bの各々におけるカウント値CNT2の初期化が同時に行われる。

【0079】

そして、本実施形態では、このチップセレクト信号CS_R、CS_GおよびCS_Bのアクティブレベルから非アクティブレベルへの一斉変化タイミングが、垂直同期信号VSYNCに同期したタイミングとなるように、ホストCPU60は、垂直同期信号VSYNCの発生タイミングの所定時間だけ前のタイミングに電気光学装置100R、100Gおよび100Bの各制御回路30宛ての初期化コマンドの送出を行うのである。

本実施形態においても上記第1および第2実施形態と同様な効果が得られる。

【0080】

<4.第4実施形態>

図13はこの発明の第4実施形態である投射型表示装置の動作を示すタイムチャートである。上記第2実施形態(図11)において、ホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを送った後、階調電圧の印加順序の更新制御の周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、初期化用同期信号ISYNCを電気光学装置100R、100Gおよび100Bの各制御回路30に送信した。これに対し、本実施形態においてホストCPU60は、当該垂直同期信号VSYNCに同期したタイミングよりも前に初期化用同期信号ISYNCを送信する。電気光学装置100R、100Gおよび100Bの各制御回路30の各制御信号処理部31は、初期化コマンドおよび初期化用同期信号ISYNCを受信した後の垂直同期信号VSYNCに同期してカウンター33のカウント値CNT2を初期化する。

【0081】

本実施形態においても上記第1〜第3実施形態と同様な効果が得られる。また、本実施形態では、電気光学装置100R、100Gおよび100Bの各制御信号処理部31が垂直同期信号VSYNCに同期してカウンター33のカウント値CNT2を初期化するので、ホストCPU60による初期化用同期信号ISYNCの送出タイミングに関して厳しい時間精度が要求されないという利点がある。

【0082】

<5.第5実施形態>

図14はこの発明の第5実施形態である投射型表示装置の動作を示すタイムチャートである。上記第3実施形態(図12)において、ホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを送った後、階調電圧の印加順序の更新制御の周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、チップセレクト信号CS_R、CS_GおよびCS_Bを一斉にアクティブレベルから非アクティブレベルに変化させた。これに対し、本実施形態においてホストCPU60は、当該垂直同期信号VSYNCに同期したタイミングよりも前にチップセレクト信号CS_R、CS_GおよびCS_Bを一斉にアクティブレベルから非アクティブレベルに変化させる。電気光学装置100R、100Gおよび100Bの各制御回路30の各制御信号処理部31は、初期化コマンドを受信し、かつ、各々に対するチップセレクト信号のアクティブレベルから非アクティブレベルへの変化を検知した後の垂直同期信号VSYNCに同期してカウンター33のカウント値CNT2を初期化する。

本実施形態においても上記第4実施形態と同様な効果が得られる。

【0083】

<6.第6実施形態>

図15はこの発明の第6実施形態である投射型表示装置4000aの電気的構成を示すブロック図である。また、図16は本実施形態の動作を示すタイムチャートである。上記第1〜第5実施形態において、ホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に対して個別的なチップセレクト信号CS_R、CS_GおよびCS_Bを各々供給した。これに対し、本実施形態においてホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に対して共通のチップセレクト信号CSを供給する。そして、ホストCPU60は、印加順序の更新制御の周期の整数倍の周期の切り換わりタイミングの所定時間だけ前になったとき、電気光学装置100R、100Gおよび100Bの各々においてカウント値CNT2の初期化を行わせるための以下の処理を開始する。

【0084】

まず、ホストCPU60は、図16に示すように、チップセレクト信号CSをアクティブレベルとし、電気光学装置100R、100Gおよび100Bの各制御回路30に対する3個の初期化コマンドを各々示すシリアルデータSDIを、シリアルクロックSCLKに同期させて順次送出する。電気光学装置100Rの制御回路30は、シリアルクロックSCLKに同期して伝送されてくるシリアルデータSDIの中から最初の初期化コマンドを選択して受信する。次に、電気光学装置100Gの制御回路30は、シリアツクロックSCLKに同期して伝送されてくるシリアルデータSDIの中から2番目の初期化コマンドを選択して受信する。次に、電気光学装置100Bの制御回路30は、シリアツクロックSCLKに同期して伝送されてくるシリアルデータSDIの中から3番目の初期化コマンドを選択して受信する。

【0085】

このようにして初期化コマンドを電気光学装置100A、100Bおよび100Cの各制御回路30に受信させた後、ホストCPU60は、印加順序の更新制御の周期の整数倍の周期の切り換わりタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、初期化用同期信号ISYNCを電気光学装置100A、100Bおよび100Cの各制御回路30に供給する。

【0086】

電気光学装置100R、100Gおよび100Bの各制御回路30の制御信号処理部31は、初期化用同期信号ISYNCが与えられることにより、事前に受信した初期化コマンドを実行し、カウント値CNT2の初期化を行う。

本実施形態においても上記第1〜第3実施形態と同様な効果が得られる。

【0087】

<7.第7実施形態>

図17はこの発明の第7実施形態である投射型表示装置の動作を示すタイムチャートである。上記第6実施形態(図16)においてホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを送った後、階調電圧の印加順序の更新制御の周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、初期化用同期信号ISYNCを電気光学装置100R、100Gおよび100Bの各制御回路30に送信した。本実施形態において、ホストCPU60は、初期化用同期信号ISYNCを送信しない。その代わりに、ホストCPU60は、チップセレクト信号CSをアクティブレベルにして、電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを送った後、階調電圧の印加順序の更新制御の周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、チップセレクト信号CSを非アクティブレベルにする。

【0088】

電気光学装置100R、100Gおよび100Bの各制御回路30の制御信号処理部31は、初期化コマンドを受信した後、各々に対するチップセレクト信号のアクティブレベルから非アクティブレベルへの変化を検知したタイミングにおいて初期化コマンドを実行し、カウンター33のカウント値CNT2を初期化する。

本実施形態においても上記第3実施形態と同様な効果が得られる。

【0089】

<8.第8実施形態>

図18はこの発明の第8実施形態である投射型表示装置の動作を示すタイムチャートである。上記第7実施形態(図17)においてホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを送った後、階調電圧の印加順序の更新制御の周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、チップセレクト信号CSをアクティブレベルから非アクティブレベルに変化させた。これに対し、本実施形態において、ホストCPU60は、チップセレクト信号CSをアクティブレベルにして、電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを送った後、当該垂直同期信号VSYNCに同期したタイミングより前のタイミングにおいて、チップセレクト信号CSを非アクティブレベルにする。

【0090】

電気光学装置100R、100Gおよび100Bの各制御回路30の制御信号処理部31は、初期化コマンドを受信し、かつ、各々に対するチップセレクト信号のアクティブレベルから非アクティブレベルへの変化を検知した後の垂直同期信号VSYNCに同期したタイミングにおいて初期化コマンドを実行し、カウンター33のカウント値CNT2を初期化する。

本実施形態においても上記第5および第6実施形態と同様な効果が得られる。

【0091】

なお、第7実施形態(図17)から第8実施形態(図18)への変形を第6実施形態(図16)に適用してもよい。すなわち、ホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを送った後、階調電圧の印加順序の更新制御の周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングよりも前に初期化用同期信号ISYNCを送信する。電気光学装置100R、100Gおよび100Bの各制御回路30の制御信号処理部31は、初期化コマンドを受信し、かつ、初期化用同期信号ISYNCを受信した後の垂直同期信号VSYNCに同期したタイミングにおいてカウンター33のカウント値CNT2を初期化するのである。

【0092】

<9.第9実施形態>

図19はこの発明の第9実施形態である電気光学装置の構成を示すブロック図である。本実施形態では、画素部全体が2つの画素部10aおよび10bに区分されている。そして、画素部10aの駆動を行うために走査線駆動回路22aおよび信号線駆動回路24aからなる駆動回路20aが設けられ、画素部10bの駆動を行うために走査線駆動回路22bおよび信号線駆動回路24bからなる駆動回路20bが設けられている。また、駆動回路20aの制御を行うために制御回路30aが設けられ、駆動回路20bの制御を行うために制御回路30bが設けられている。そして、制御回路30aおよび30bでは、上記第1実施形態において説明したものと同様な配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御が行われる。

【0093】

ここで、制御回路30aおよび30bでは、例えば前掲図6のカウンター32、33、加算器34およびパターンジェネレーター35からなる回路を用いて、階調電圧の印加順序の更新制御が互いに独立して行われる。従って、例えばノイズ等の影響により、画素部10aを対象とした階調電圧の印加順序の更新制御と、画素部10bを対象とした階調電圧の印加順序の更新制御との間に位相ずれが発生する可能性がある。このような位相ずれが発生すると、画素部10aと画素部10bとの境界において表示ムラが発生する。

【0094】

そこで、本実施形態では、図示しない同期化制御手段(例えば上記第1〜第8実施形態におけるホストCPU60に相当するもの)が、印加順序の更新制御の周期の整数倍の周期の切り換わりタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、制御回路30aおよび30bの各々における印加順序の更新制御を初期化する。これにより画素部10aと画素部10bとで階調電圧の印加順序の更新制御を同期化し、画素部10aと画素部10bとの境界に表示ムラが発生するのを防止することができる。

【0095】

<10.変形例>

以上、この発明の第1〜第9実施形態について説明したが、この発明には、上述した実施形態に限定されるものではなく、例えば、以下の変形が可能である。

【0096】

(1)上記第1〜第8実施形態において、ホストCPU60は、電気光学装置100A、100Bおよび100Cの各制御回路30に初期化コマンドを送出した後、初期化コマンドの実行タイミングを指示するために、初期化用同期信号ISYNCを供給し、またはチップセレクト信号CSの立ち上げを行った。しかし、そのようにする代わりに、電気光学装置100A、100Bおよび100Cの各制御回路30が、初期化コマンドの受信後の最初の垂直同期信号VSYNCにおいて初期化コマンドを実行する構成としてもよい。この態様においても、上記各実施形態と同様の効果が得られる。

【0097】

(2)上記第1実施形態では、内部垂直同期信号VSが発生する都度、カウンター32のカウント値CNT1を初期化する構成としたため、制御信号処理部31は、初期化コマンドの実行時、カウンター33のカウント値CNT2のみを初期化した。しかし、内部垂直同期信号VSの発生時にカウンター32のカウント値CNT1を初期化しない構成もあり得る。この場合、制御信号処理部31は、初期化コマンドの実行時、カウンター33のカウント値CNT2とカウンター32のカウント値CNT1の両方を初期化する構成とすればよい。

【0098】

(3)上記各実施形態において、配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期は、垂直走査期間の整数倍の長さの周期であった。しかし、投射型表示装置や電気光学装置において、垂直走査期間の整数倍の長さの周期ではなく、水平走査期間の整数倍の周期で、配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を行う場合もあり得る。このような場合、ホストCPU60は、この更新制御の周期である水平走査期間の整数倍の周期に同期して、複数の駆動回路の各々における配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の初期化を行えばよい。

【0099】

(4)上記各実施形態では、複数の駆動回路が互いに独立して行う階調電圧の印加順序の更新制御を同期化の対象とした。しかし、この発明の適用対象はこれに限定されるものではない。画素部を駆動する複数の駆動回路が互いに独立して実行する何らかの駆動条件の周期的な更新制御を実行する場合に、この周期的な更新制御を同期化の対象としてもよい。

【0100】

(5)液晶素子42は電気光学素子の例示に過ぎない。本発明に適用される電気光学素子について、自身が発光する自発光型と外光の透過率や反射率を変化させる非発光型(例えば液晶素子42)との区別や、電流の供給によって駆動される電流駆動型と電界(電圧)の印加によって駆動される電圧駆動型との区別は不問である。例えば、有機EL素子,無機EL素子,LED(Light Emitting Diode),電界電子放出素子(FE(Field−Emission)素子),表面伝導型電子放出素子(SE(Surface conduction Electron emitter)素子),弾道電子放出素子(BS(Ballistic electron Emitting)素子),電気泳動素子、エレクトロクロミック素子など様々な電気光学素子を利用した電気光学装置100に本発明は適用される。すなわち、電気光学素子は、電流の供給や電圧(電界)の印加といった電気的な作用に応じて階調(透過率や輝度などの光学的な特性)が変化する電気光学物質(例えば液晶425)を利用した被駆動素子(典型的には、階調信号に応じて階調が制御される表示素子)として包括される。

【0101】

<11.応用例>

この発明は、投射型表示装置以外の各種の電子機器に利用され得る。図20および図21は、この発明の適用対象となる電子機器の具体的な形態を例示するものである。

【0102】

図20は、電気光学装置を採用した可搬型のパーソナルコンピューターの斜視図である。パーソナルコンピューター2000は、各種の画像を表示する電気光学装置100と、電源スイッチ2001やキーボード2002が設置された本体部2010とを具備する。このようなパーソナルコンピューター2000の中には、電気光学装置100が複数の画素部からなり、各画素部毎に上述した階調電圧の印加順序の更新制御を行う構成のものがある。このようなパーソナルコンピューター2000に対して本発明を適用することにより上述した縦ノイズの発生を防止することができる。

【0103】

図21は、携帯電話機の斜視図である。携帯電話機3000は、複数の操作ボタン3001およびスクロールボタン3002と、各種の画像を表示する電気光学装置100とを備える。スクロールボタン3002を操作することによって、電気光学装置100に表示される画面がスクロールされる。本発明はこのような携帯電話機にも適用可能である。

【0104】

なお、本発明が適用される電子機器としては、図1、図20および図21に例示した機器のほか、携帯情報端末(PDA:Personal Digital Assistants),デジタルスチルカメラ,テレビ,ビデオカメラ,カーナビゲーション装置,車載用の表示器(インパネ),電子手帳,電子ペーパー,電卓,ワードプロセッサ,ワークステーション,テレビ電話,POS端末,プリンタ,スキャナ,複写機,ビデオプレーヤ,タッチパネルを備えた機器等などが挙げられる。

【符号の説明】

【0105】

100,100R,100G,100B……電気光学装置、10,10a,10b……画素部、PIX……画素回路、12……走査線、14……信号線、20,20a,20b……駆動回路、22,22a,22b……走査線駆動回路、24,24a,24b……信号線駆動回路、30,30a,30b……制御回路、42……液晶素子、44……選択スイッチ、57[1]〜57[J]……デマルチプレクサー、53[1]〜53[J]……マルチプレクサー、56[1]〜56[J]……駆動電圧発生回路、60……ホストCPU、70……画像入力部、31……制御信号処理部、32,33……カウンター、34……加算器、35……パターンジェネレーター。

【技術分野】

【0001】

本発明は、液晶パネル等の電気光学装置を利用して画像を表示する技術に関する。

【背景技術】

【0002】

周知のように、液晶パネル等の電気光学装置は、複数の信号線と複数の走査線との各交差に対応して画素回路が設けられている。このような電気光学装置では、1本の走査線に対応付けられた全ての画素回路に対する画像信号の書き込みを一水平走査期間内に完了させる必要がある。従って、1本の走査線に対応付けられた画素回路の数が多くなると、1個の画素回路への画像信号の書き込みに利用可能な時間が短くなり、要求される表示品質を実現するのが困難になる。

【0003】

そこで、表示品質を劣化させることなく、電気光学装置の高精細化を実現するための手段として、次の技術が採用されるに至った。すなわち、電気光学装置の複数の信号線を各々所定本数の信号線からなる複数の配線ブロックに分け、配線ブロック毎に、配線ブロック内の各信号線を順次選択して階調電圧の印加を行う技術である。

【0004】

この技術によれば、一水平走査期間内に、配線ブロック内の複数の信号線への階調電圧の印加を複数のブロックにおいて並列的に進めるので、電気光学装置全体としての信号線の本数が多い場合でも、信号線1本当たりの階調電圧の印加時間を十分に長くすることができる。従って、表示品質を劣化させることなく、電気光学装置の高精細化を実現することができる。

【0005】

しかしながら、この技術を採用した場合、以下に述べる問題が発生する。すなわち、一水平走査期間内において配線ブロック内の各信号線を順次選択して各画素の画像信号に応じた階調電圧の印加を行う場合、たとえ同じ値の画像信号に対応した階調電圧を各信号線に印加する場合でも、各信号線に接続された各画素回路の液晶の透過率は厳密には同じ値にならず、電気光学装置の表示画像に表示ムラが発生するのである。

【0006】

そこで、この問題を解決するための手段として、例えば特許文献1は、駆動回路による各画素回路の駆動条件、具体的には一水平走査期間内における配線ブロック内の各信号線への階調電圧の印加順序を、垂直走査周期に同期しあるいは水平走査周期に同期して切り換える技術を提案している。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2004−45967号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

特許文献1に開示されているように、配線ブロック内の各信号線への階調電圧の印加順序の更新制御を例えば垂直走査周期に同期して行うと、複数の垂直走査期間を通じて見た場合に、各画素回路の液晶の透過率が各信号線間で均一化される。このため、電気光学装置の表示画像に現れる表示ムラが軽減される。各信号線への階調電圧の印加順序の更新を水平走査周期に同期して行う場合も同様である。このように、1個の電気光学装置に着目した場合には、各信号線への階調電圧の印加順序の更新を行う技術は、表示ムラを軽減する効果を奏する。

【0009】

しかしながら、例えば投射型表示装置のように、複数の電気光学装置(液晶ライトバルブ)を用いて画像表示を行う電子機器において、各電気光学装置では、互いに独立して駆動回路の駆動条件の更新制御、具体的には配線ブロック内の各信号線への階調電圧の印加順序の更新制御を実行する。従って、各液晶ライトバルブ間で階調電圧の印加順序の更新制御にいわば位相ずれが発生し、ある水平走査周期において、R色に対応した液晶ライトバルブでは、配線ブロック内の各信号線を例えば第1信号線、第2信号線、第3信号線、第4信号線という順に選択して階調電圧を印加するのに対し、同じ水平走査期間にG色に対応した液晶ライトバルブでは、配線ブロック内の各信号線を第3信号線、第4信号線、第1信号線、第2信号線という順に選択して階調電圧を印加する場合も起こり得る。

【0010】

この場合、R色に対応した液晶ライトバルブとG色に対応した液晶ライトバルブとでは、一水平走査期間内における第1信号線への階調電圧の印加タイミングと第3信号線への階調電圧の印加タイミングと位置関係が逆になっている。このため、例えば投射画像における第1信号線に対応した部分に関しては、G色よりR色が強調され易くなり、第3信号線に対応した部分に関しては、R色よりG色が強調され易くなる、といったことが起こり得る。このように配線ブロック内の各信号線への階調電圧の印加順序がR、G、Bの各色に対応した各液晶ライトバルブ間で異なると、各信号線に対応した投射画像の色バランスが信号線間で異なり、投射画像に色つきが発生するのである。

【0011】

このような問題は、投射型表示装置以外の他の装置においても生じる。例えば画素部を複数の領域に分割し、領域毎に異なる信号線駆動回路が各領域内の信号線を駆動する構成の電気光学装置がある。このような電気光学装置において、各信号線駆動回路の駆動対象である複数の信号線を複数の配線ブロックに分け、信号線駆動回路が配線ブロック毎に配線ブロック内の各信号線を順次選択して画像信号を供給し、かつ、各信号線への階調電圧の印加順序を例えば垂直走査周期に同期して切り換えるように構成することが考えられる。この場合において、隣り合う2つの領域の駆動を行う2つの信号線駆動回路における配線ブロック内の各信号線への階調電圧の印加順序が異なったものであると、電気光学装置の表示画像に表示ムラが発生する。

【0012】

以上述べた例の他にも、表示品質の向上等の目的のために、例えば複数の電気光学装置間で、互いに独立に駆動回路による各画素回路の駆動条件の更新制御を進める場合がある。この場合も、例えばノイズ等の影響により、各電気光学装置間で駆動条件の更新制御のいわば位相ずれが生じると、同様な問題が発生する。

【0013】

この発明は、以上説明した事情に鑑みてなされたものであり、複数の駆動回路による画素部の駆動条件の更新制御を互いに独立して進める電気光学装置または電子機器において、各駆動回路間で駆動条件に不一致が生じることを防止する技術的手段を提供することを解決課題とする。

【課題を解決するための手段】

【0014】

上述した課題を解決するため、この発明は、互いに交差する複数の走査線および複数の信号線を有するとともに、前記複数の走査線と前記複数の信号線との各交差に対応して各々配置された複数の画素回路を有する画素部と、一垂直走査期間内に前記複数の走査線を順次選択し、選択した走査線と前記複数の信号線との各交差に対応付けられた複数の画素回路を前記複数の信号線に接続する走査線駆動回路と、前記複数の信号線を複数の配線ブロックに分け、配線ブロック毎に、一水平走査期間内に当該配線ブロックに属する各信号線を順次選択し、選択した信号線に階調電圧を印加する信号線駆動回路と、前記複数の配線ブロックにおける配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を実行する制御回路とを各々具備する複数の電気光学装置と、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を一斉に初期化する動作を時間を空けて繰り返すことにより、前記複数の電気光学装置の各々における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を同期化する同期化手段とを具備することを特徴とする電子機器を提供する。

【0015】

かかる電子機器によれば、同期化手段が複数の制御回路の各々による配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を一斉に初期化する動作を時間を空けて繰り返し実行することにより、複数の制御回路の各々による配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御が同期化する。従って、各電気光学装置間で配線ブロック内の複数の信号線への階調電圧の印加順序に不一致が生じることを防止することができる。

【0016】

好ましい態様において、前記同期化手段は、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を一斉に初期化する動作を繰り返す。

【0017】

この態様によれば、各電気光学装置において配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御の周期性を極力損なうことなく、各電気光学装置間で配線ブロック内の複数の信号線への階調電圧の印加順序に不一致が生じることを防止することができる。

【0018】

また、この発明は、互いに交差する複数の走査線および複数の信号線を有するとともに、前記複数の走査線と前記複数の信号線との各交差に対応して各々配置された複数の画素回路を各々有する複数の画素部と、前記複数の画素部の各画素部における前記複数の走査線を一垂直走査期間内に順次選択し、選択した走査線と前記複数の信号線との各交差に対応付けられた複数の画素回路を前記複数の信号線に接続する走査線駆動手段と、前記複数の画素部に各々対応付けられた複数の信号線駆動回路であって、各画素部の前記複数の信号線を複数の配線ブロックに分け、配線ブロック毎に、一水平走査期間内に当該配線ブロックに属する各信号線を順次選択し、選択した信号線に階調電圧を印加する複数の信号線駆動回路と、前記複数の信号線駆動回路の各々における前記複数の配線ブロックにおける配線ブロック内の複数の信号線への階調電圧の印加順序を各々周期的に更新する複数の制御回路と、前記複数の制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を一斉に初期化する動作を時間を空けて繰り返し実行する同期化手段とを具備することを特徴とする電気光学装置を提供する。

【0019】

かかる電気光学装置によれば、同期化手段が複数の制御回路の各々による配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を一斉に初期化する動作を時間を空けて繰り返し実行することにより、複数の制御回路の各々による配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御が同期化する。従って、複数の画素部間で配線ブロック内の複数の信号線への階調電圧の印加順序に不一致が生じることを防止することができる。

【0020】

また、実施の形態からは、以下の発明を把握することができる。この発明は、複数の画素部と、前記複数の画素部を各々駆動する複数の駆動回路と、前記複数の駆動回路の各々による画素部の駆動条件の周期的な更新制御を互いに独立に実行する複数の制御回路と、前記複数の制御回路の各々による駆動条件の更新制御を一斉に初期化する動作を時間を空けて繰り返し実行することにより、前記複数の制御回路の各々による駆動条件の更新制御を同期化する同期化手段とを具備することを特徴とする電子機器を提供する。

【0021】

かかる電子機器によれば、同期化手段が複数の制御回路の各々による駆動条件の更新制御を一斉に初期化する動作を時間を空けて繰り返し実行することにより、複数の制御回路の各々による駆動条件の更新制御が同期化する。従って、各駆動回路間で駆動条件に不一致が生じることを防止することができる。

【0022】

好ましい態様において、前記同期化手段は、前記複数の制御回路の各々による駆動条件の周期的な更新制御の周期の整数倍の長さの周期で、前記複数の制御回路の各々による駆動条件の更新制御を一斉に初期化する動作を繰り返す。

【0023】

ここで、同期化手段により駆動条件の更新制御を一斉に初期化する動作が行われると、複数の駆動回路の駆動条件は初期状態となり、その後、複数の制御回路では、この初期状態から駆動条件の更新制御が進められる。そして、各制御回路による駆動条件の更新制御が支障なく進行する場合、初期化後、駆動条件の更新制御の一周期に相当する時間が経過したとき、複数の駆動回路の駆動条件は同じ初期状態に戻る。このとき、同期化手段により駆動条件の更新制御を一斉に初期化する動作が行われるが、その際に各駆動回路の駆動条件は初期状態になるので、この初期化の動作は各制御回路および各駆動回路の動作に全く影響を与えない。従って、各駆動回路の駆動条件の更新制御の周期性が損なわれない。一方、初期化後、例えばノイズの影響により、複数の制御回路の中のいずれかの制御回路による駆動条件の更新制御に誤動作が生じた場合、初期化から駆動条件の更新制御の一周期に相当する時間が経過したとき、複数の駆動回路のうち誤動作しなかった制御回路の制御下にある駆動回路の駆動条件は初期状態に戻るが、誤動作した制御回路の制御下にある駆動回路の駆動条件は初期状態に戻らない。このとき、同期化手段により駆動条件の更新制御の動作を一斉に初期化する動作が行われると、全ての駆動回路の駆動条件が初期状態になる。従って、この態様によれば、各駆動回路の駆動条件の更新制御の周期性を極力損なうことなく、各駆動回路間で駆動条件に不一致が生じることを防止することができる。

【図面の簡単な説明】

【0024】

【図1】この発明の第1実施形態である投射型表示装置の構成を示す模式図である。

【図2】同投射型表示装置の電気的構成を示すブロック図である。

【図3】同投射型表示装置における電気光学装置の画素部、駆動回路および制御回路の構成を示すブロック図である。

【図4】同電気光学装置の画素回路の構成を示す回路図である。

【図5】同電気光学装置の信号線駆動回路の構成を示すブロック図である。

【図6】同電気光学装置の制御回路の構成を示すブロック図である。

【図7】同制御回路のパターンジェネレーターに記憶された選択パターンデータの内容を例示する図である。

【図8】同実施形態の動作を示すタイムチャートである。

【図9】同実施形態において行われる配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の様子を例示する図である。

【図10】同実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図11】この発明の第2実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図12】この発明の第3実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図13】この発明の第4実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図14】この発明の第5実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図15】この発明の第6実施形態である投射型表示装置の構成を示す模式図である。

【図16】同実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図17】この発明の第7実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図18】この発明の第8実施形態においてホストCPUと複数の電気光学装置の各制御回路との間で行われる階調電圧の印加順序の更新制御の初期化手順を例示するタイムチャートである。

【図19】この発明の第9実施形態である電気光学装置の構成を示すブロック図である。

【図20】この発明の適用例である他の電子機器の形態(パーソナルコンピューター)を示す斜視図である。

【図21】この発明の適用例である他の電子機器の形態(携帯電話機)を示す斜視図である。

【発明を実施するための形態】

【0025】

<1.第1実施形態>

図1は、この発明による電子機器の第1実施形態である投射型表示装置(3板式のプロジェクタ)4000の構成を示す模式図である。この投射型表示装置4000は、相異なる表示色R、G、Bに各々対応する3個の電気光学装置100(100R,100G,100B)を含んでいる。照明光学系4001は、照明装置(光源)4002からの出射光のうち赤色成分rを電気光学装置100Rに供給し、緑色成分gを電気光学装置100Gに供給し、青色成分bを電気光学装置100Bに供給する。各電気光学装置100は、照明光学系4001から供給される各単色光を表示画像に応じて変調する光変調器(ライトバルブ)として機能する。投射光学系4003は、各電気光学装置100からの出射光を合成して投射面4004に投射する。

【0026】

図2は投射型表示装置4000の電気的構成を示すブロック図である。図2に示すように、投射型表示装置4000は、電気光学装置100R、100Gおよび100Bと、外部から画像信号を取り込む画像入力部70と、これらを制御するホストCPU60とを有している。電気光学装置100R、100Gおよび100Bの各々は、画素部10と、駆動回路20と、制御回路30とを有する。ここで、制御回路30は、ホストCPU60から供給される各種の制御信号に従い、駆動回路20等の電気光学装置内の各部を制御する回路である。

【0027】

ホストCPU60は、垂直同期信号VSYNCおよび水平同期信号HSYNCを画像入力部70に供給するとともに、電気光学装置100R、100Gおよび100Bの各々の制御回路30に供給する。画像入力部70は、垂直同期信号VSYNCが与えられる毎に、外部から取り込んだ画像信号に基づいて、1フレーム分のR、G、Bの各色の画像信号VID_R、VID_G、VID_Bを生成する。そして、画像入力部70は、水平同期信号HSYNCが与えられる毎に、1ライン分の各画素の画像信号VID_Rを画素クロックPCLK_Rに同期させて電気光学装置100Rの制御回路30に供給し、1ライン分の各画素の画像信号VID_Gを画素クロックPCLK_Gに同期させて電気光学装置100Gの制御回路30に供給し、1ライン分の各画素の画像信号VID_Bを画素クロックPCLK_Bに同期させて電気光学装置100Bの制御回路30に供給する。

【0028】

また、ホストCPU60と電気光学装置100R、100Gおよび100Bの各々との間には3線(CS、SDI、SCK)のシリアルインタフェースが設けられている。ホストCPU60は、電気光学装置100Rの制御回路30に対して送信すべきデータがある場合、チップセレクト信号CS_RをアクティブレベルであるLレベルとし、その間にシリアルクロックSCKに同期させてシリアルデータSDIを出力する。電気光学装置100Rの制御回路30は、チップセレクト信号CS_Rがアクティブレベルであることから、シリアルデータSDIをシリアルクロックSCKにより取り込む。同様にホストCPU60は、電気光学装置100G(100B)の制御回路30に対して送信すべきデータがある場合、チップセレクト信号CS_G(CS_B)をアクティブレベルであるLレベルとし、その間にシリアルクロックSCKに同期させてシリアルデータSDIを出力する。電気光学装置100G(100B)の制御回路30は、チップセレクト信号CS_G(CS_B)がアクティブレベルであることから、シリアルデータSDIをシリアルクロックSCKにより取り込む。

【0029】

また、ホストCPU60は、所定周期毎に初期化用同期信号ISYNCを電気光学装置100R、100Gおよび100Bの各々の制御回路30に供給する機能を有している。なお、この初期化用同期信号ISYNCの役割については後述する。

【0030】

図3は、1個の電気光学装置100における画素部10、駆動回路20および制御回路30の構成を示すブロック図である。図3に示すように、画素部10は、複数の画素回路PIXが平面状に配列されてなるものである。駆動回路20は、各画素回路PIXを駆動する回路であり、走査線駆動回路22と信号線駆動回路24とを含んでいる。

【0031】

画素部10には、相互に交差するM本の走査線12とN本の信号線14とが形成されている(M,Nは自然数)。複数の画素回路PIXは、各走査線12と各信号線14との交差に対応して設けられており、縦M行×横N列の行列状に配列されている。そして、画素部10内のN本の信号線14は、相隣接するK本(Kは2以上の自然数)を単位としてJ個の配線ブロックB[1]〜B[J]に区分されている(J=N/K)。

【0032】

図4は、各画素回路PIXの構成を示す回路図である。図4に示すように、各画素回路PIXは、液晶素子42と選択スイッチ44とを含んでいる。液晶素子42は、相対向する画素電極421および共通電極423と両電極間の液晶425とで構成された電気光学素子である。画素電極421と共通電極423との間の印加電圧に応じて液晶425の透過率が変化する。なお、以下の説明では便宜的に、画素電極421が共通電極423と比較して高電位である場合の液晶素子42の印加電圧を正極性と表記し、画素電極421が低電位である場合の印加電圧を負極性と表記する。

【0033】

選択スイッチ44は、走査線12にゲートが接続されたNチャネル型の薄膜トランジスターで構成され、液晶素子42(画素電極421)と信号線14との間に介在して両者の電気的な接続(導通/非導通)を制御する。従って、画素回路PIX(液晶素子42)は、選択スイッチ44がON状態であるときの信号線14の電圧(後述の階調電圧VG)に応じた階調を表示する。

以上が図3における各画素回路PIXの構成である。

【0034】

図3において、走査線駆動回路22は、制御回路3から内部水平同期信号HSが出力されるのに応じて、各走査線12に対する走査信号G[1]〜G[M]を一水平走査期間Hずつ順次アクティブレベルとし、M本の走査線12の各々を順次に選択する。ここで、第m行に対応した走査信号G[m]がアクティブレベルである期間は、第m行のN個の画素回路PIXの各選択スイッチ44がON状態となり、これらの選択スイッチ44を各々介してN本の信号線14が第m行のN個の画素回路PIXの各画素電極421に各々接続される。

【0035】

信号線駆動回路24は、走査線駆動回路22による各走査線12の選択に同期してN本の信号線14の各々を駆動する回路である。図5は、この信号線駆動回路24の構成を示すブロック図である。上述したように、画素部10内のN本の信号線14は、J個の配線ブロックB[1]〜B[J]に区分されている。信号線駆動回路24には、このJ個の配線ブロックB[1]〜B[J]に各々対応付けて、J個のデマルチプレクタ57[1]〜57[J]と、J個の駆動電圧発生回路56[1]〜56[J]と、J個のマルチプレクタ53[1]〜53[J]とが設けられている。また、信号線駆動回路24には、画像信号記憶部51が設けられている。この画像信号記憶部51は、1ラインを構成するN画素分のデジタル形式の画像信号VIDを各々記憶するN個のレジスター(図示略)により構成されている。このN個のレジスターは、J個の配線ブロックB[1]〜B[J]に対応付けて、各々K(=N/J)個のレジスターからなるレジスターブロック52[1]〜52[J]に区分されている。

【0036】

マルチプレクサー53[j](j=1〜J)の各々は、K個のスイッチ54[1]〜54[K]により構成されている。ここで、j番目の配線ブロックB[j]に対応した1個のマルチプレクサー53[j]に着目すると、K個のスイッチ54[1]〜54[K]の各々の一方の接点には、j番目のレジスターブロック52[j]に記憶されたK画素分の画像信号の各々がK本の信号線17を各々介して供給される。また、このK個のスイッチ54[1]〜54[K]の各々の他方の接点は、1本の信号線16に共通接続され、同信号線16を介してj番目の駆動電圧発生回路56[j]の入力端子に接続されている。

【0037】

各マルチプレクサー53[j](j=1〜J)のK個のスイッチ54[1]〜54[K]のON/OFFは、制御回路30が出力するK個の選択信号SELa[1]〜SELa[K]により各々切り換えられる。ここで、1個の選択信号SELa[k]がアクティブレベル、他のK−1個の選択信号SELa[k’](k’≠k)が非アクティブレベルである場合には、マルチプレクサー53[j](j=1〜J)に各々属するJ個のスイッチ54[k]のみがONとなる。従って、マルチプレクサー53[j](j=1〜J)の各々は、各々に対応するレジスターブロック52[j]に記憶された水平方向K画素分の画像信号のうちj番目の画素の画像信号を画像信号D[j]として選択し、信号線16を介して各々に対応した駆動電圧発生回路56[j]に供給する。

【0038】

駆動電圧発生回路56[1]〜56[J]は、プリチャージ電圧を発生する機能と、信号線16を介して供給される画像信号D[1]〜D[J]に各々対応した階調電圧を発生する機能とを有する。駆動電圧発生回路56[1]〜56[J]は、一水平走査期間Hをプリチャージ期間TPREと書込期間TWRTとに分け、プリチャージ期間TPREはプリチャージ電圧を、書込期間TWRTは画像信号D[1]〜D[J]に応じた階調電圧を信号線駆動信号C[1]〜C[J]としてJ本の信号線15に各々出力する。

【0039】

デマルチプレクサー57[j](j=1〜J)の各々は、K個のスイッチ58[1]〜58[K]により構成されている。ここで、j番目の配線ブロックB[j]に対応した1個のデマルチプレクサー57[j]に着目すると、K個のスイッチ54[1]〜54[K]の各々の一方の接点は、1本の信号線15に共通接続され、同信号線15を介してj番目の駆動電圧発生回路56[j]の出力端子に接続されている。また、このK個のスイッチ54[1]〜54[K]の各々の他方の接点は、j番目の配線ブロックB[j]を構成するK本の信号線14に各々接続されている。

【0040】

各デマルチプレクサー57[j](j=1〜J)のK個のスイッチ58[1]〜58[K]のON/OFFは、制御回路30が出力するK個の選択信号SELb[1]〜SELb[K]により各々切り換えられる。ここで、1個の選択信号SELb[k]がアクティブレベル、他のK−1個の選択信号SELb[k’](k’≠k)が非アクティブレベルである場合には、デマルチプレクサー57[j](j=1〜J)に各々属するJ個のスイッチ58[k]のみがONとなる。従って、デマルチプレクサー57[j](j=1〜J)の各々は、駆動電圧発生回路56[1]〜56[J]から出力される信号線駆動信号C[1]〜C[J]を各配線ブロックB[1]〜B[J]のk番目の信号線14に各々出力する。

以上が図3における信号線駆動回路24の構成である。

【0041】

図3において、制御回路30は、画像信号VID、極性信号POL、選択信号SELa[k](k=1〜K)、SELb[k](k=1〜K)および電気光学装置100内の各部を制御するための各種の制御信号を発生する回路である。図6は、この制御回路30の一部の構成を示すブロック図である。図6に示すように、制御回路30は、制御信号処理部31と、カウンター32および33と、加算器34と、パターンジェネレーター35とを有する。

【0042】

制御信号処理部31には、ホストCPU60(図2参照)から3線シルアルインタフェースを介してチップセレクト信号CS、シリアルデータSDIおよびシリアルクロックSCKが供給される。制御信号処理部31は、チップセレクト信号CSがアクティブレベルであるLレベルである期間、シリアルクロックSCKに同期してシリアルデータSDIを取り込む。シルアルデータSDIとして供給されるデータには、駆動回路20の駆動条件の設定を指示する各種のコマンドが含まれる。また、制御信号処理部31には、ホストCPU60(図2参照)から垂直同期信号VSYNCおよび水平同期信号HSYNCが供給される。また、制御信号処理部31には、画像入力部70(図2参照)から画面を構成する各画素の画像信号VIDが画素クロックPCLKに同期して供給される。制御信号処理部31は、この画素クロックPCLKにより画像データVIDを取り込む。

【0043】

制御信号処理回路31は、垂直同期信号VSYNCが供給されるのに応じて内部垂直同期信号VSを出力する。また、制御信号処理回路31は、水平同期信号HSYNCが供給されるのに応じて内部水平同期信号HSを出力する。そして、制御信号処理回路31は、この内部水平同期信号HSを出力する都度、ホストCPU60から取り込んだ1ライン分(N画素分)の各画素の画像信号VIDを信号線駆動回路24に出力する。信号線駆動回路24では、このN画素分の画像信号VIDが各々K画素分の画像信号からなるJ個のブロックに区分され、上述したレジスターブロック52[1]〜52[J]に各々格納される。

【0044】

カウンター32は、内部水平同期信号HSの立ち上がりエッジが発生する都度、制御信号処理部31から与えられるステップ値STP1だけカウント値CNT1を増加させるカウンターである。また、カウンター33は、内部垂直同期信号VSの立ち上がりエッジが発生する都度、制御信号処理部31から与えられるステップ値STP2だけカウント値CNT2を増加させるカウンターである。ここで、ステップ値STP1およびSTP2は、ホストCPU60から受信されるコマンドに従って設定されるようになっている。加算器34は、カウンター32のカウント値CNT1とカウンター33のカウント値CNT2とを加算し、加算結果CNT1+CNT2を示すパターン番号PNをパターンジェネレーター35に出力する。

【0045】

カウンター32および33は、カウント値の初期化が可能な構成となっている。制御信号処理部31は、カウンター32のカウント値CNT1を「0」に初期化するための第1の初期化信号RES1を発生する機能と、カウンター33のカウント値CNT2を「0」に初期化するための第2の初期化信号RES2を発生する機能とを備えている。

【0046】

制御信号処理部31は、一垂直走査期間が終了して新たな垂直走査期間が始まるときに、第1の初期化信号RES1を発生してカウンター32のカウント値CNT1を「0」に初期化する。

【0047】

ホストCPU60から上述した初期化用同期信号ISYNCが供給された場合、制御信号処理部31は、第2の初期化信号RES2を発生してカウンター33のカウント値CNT2を「0」に初期化する。なお、ホストCPU60および制御信号処理部31間の初期化用同期信号ISYNCの伝送の詳細については後述する。

【0048】

パターンジェネレーター35は、水平走査期間Hをプリチャージ期間TPREと書込期間TWRTとに分け、期間毎に異なった態様で、選択信号SELa[1]〜SELa[K]および選択信号SELb[1]〜SELb[K]の切り換え制御を行う回路である。

【0049】

各水平走査期間Hのプリチャージ期間TPREにおいて、パターンジェネレーター35は、選択信号SELa[1]〜SELa[K]をLレベル、選択信号SELb[1]〜SELb[K]をHレベルとする。

【0050】

また、各水平走査期間Hの書込期間TWRTにおいて、パターンジェネレーター25は、配線ブロックB[1]〜B[J]の各々のK本の信号線14への階調電圧の印加を順次行わせるための選択信号SELa[1]〜SELa[K]および選択信号SELb[1]〜SELb[K]の切り換え制御を行う。

【0051】

この書込期間TWRT内における選択信号の切換制御を可能にするため、パターンジェネレーター35は、例えばK種類を選択パターンデータを記憶している。図7はこのK種類の選択パターンデータの内容を例示するものである。K種類の選択パターンデータには、0からK−1までのパターン番号PNが各々対応付けられている。

【0052】

個々の選択パターンデータは、書込期間TWRTにおいて配線ブロックB[1]〜B[K]の各々を構成するK本の信号線14への階調電圧の印加順序を指定するデータである。例えばパターン番号PN=「0」に対応した選択パターンデータは、書込期間TWRT内の最初の階調電圧印加期間U[1]に各配線ブロックの1番目の信号線14への階調電圧の印加を、2番目の階調電圧印加期間U[2]に2番目の信号線14への階調電圧の印加を、…、最後の階調電圧印加期間U[K]にK番目の信号線14への階調電圧の印加を行うことを指示している。また、パターン番号PN=「1」に対応した選択パターンデータは、書込期間TWRT内の最初の階調電圧印加期間U[1]に各配線ブロックのK番目の信号線14への階調電圧の印加を、2番目の階調電圧印加期間U[2]に1番目の信号線14への階調電圧の印加を、…、最後の階調電圧印加期間U[K]にK−1番目の信号線14への階調電圧の印加を行うことを指示している。

【0053】

パターンジェネレーター35は、各水平走査期間Hの書込期間TWRTにおいて、加算器34から与えられるパターン番号PNに対応した選択パターンデータに従って、選択信号SELa[1]〜SELa[K]および選択信号SELb[1]〜SELb[K]を変化させる。

【0054】

パターンジェネレーター35にK種類の選択パターンデータを記憶させる場合、カウンター32および33としては、0〜K−1の範囲内のカウントを行うカウンターが用いられる。また、加算器34としては、上述した加算結果CNT1+CNT2をKにより乗算した余りをパターン番号PNとして出力する構成のものが用いられる。

以上が制御回路30の構成である。

【0055】

図8は電気光学装置100の動作例を示すタイムチャートである。図8には、ある垂直走査期間V1内における各部の波形と、その次の垂直走査期間V2内の各部の波形が例示されている。本実施形態において、制御回路30は、垂直走査期間が切り換わる都度、極性信号POLを反転させる。図8に示す例における極性信号POLは、垂直走査期間V1では負極性(−)を指示しており、垂直走査期間V2では正極性(+)を指示している。ここで、極性信号POLが負極性(−)を指示する垂直走査期間V1では、正の電圧が上述した共通電極423に印加され、極性信号POLが正極性(+)を指示する垂直走査期間V2では、負の電圧が上述した共通電極423に印加される。

【0056】

各垂直走査期間において、走査線駆動回路22は、制御回路30の制御信号処理回路31が内部水平同期信号HSを発生するのに同期して、M本の走査線12を順次選択し、選択した走査線12に対応した走査信号G[j]を一水平走査期間Hに亙ってアクティブレベルであるHレベルとする。

【0057】

各水平走査期間Hのプリチャージ期間TPREにおいて、制御回路30のパターンジェネレーター35は、選択信号SELa[1]〜SELa[K]を全てLレベルとして、マルチプレクサー53[1]〜53[J]の全てのスイッチ54[1]〜54[K]をOFFにするとともに、選択信号SELb[1]〜SELb[K]を全てHレベルとして、デマルチプレクサー57[1]〜57[J]の全てのスイッチ58[1]〜58[K]をONにする。また、各水平走査期間Hのプリチャージ期間TPREにおいて、駆動電圧発生回路56[1]〜56[J]は、極性信号POLが示す極性のプリチャージ電圧を出力する。1個の駆動電圧発生回路56[j]が出力したプリチャージ電圧はデマルチプレクサー57[j]のK個のスイッチ58[1]〜58[J]を各々介して配線ブロックB[j]のK本の信号線14に印加される。従って、プリチャージ期間TPREにおいて、画素部10の全ての信号線14にプリチャージ電圧が印加される。

【0058】

各水平走査期間Hの書込期間TWRTにおいて、パターンジェネレーター35は、その時点におけるパターン番号PNに対応した選択信号パターンデータに従って選択信号SELa[1]〜SELa[K]および選択信号SELb[1]〜SELb[K]を変化させる。

【0059】

図8の下段左側には、垂直走査期間V1のある水平走査期間H(例えば垂直走査期間V1内のm番目の水平走査期間Hとする。)内に発生する選択信号SELa[1]〜SELa[K]および選択信号SELb[1]〜SELb[K]の波形が例示されている。この例では、階調電圧印加期間U[1]において、選択信号SELa[1]およびSELb[1]の組のみがHレベルとされ、マルチプレクサー53[1]〜53[J]におけるスイッチ54[1]と、デマルチプレクサー57[1]〜57[J]におけるスイッチ58[1]がONになる。この結果、レジスターブロック52[1]〜52[J]の各々における1番目の画素の画像信号VIDがマルチプレクサー53[1]〜53[J]のスイッチ54[1]を各々通過し、画像信号D[1]〜D[J]として駆動電圧発生回路56[1]〜56[J]に各々供給される。この時点において、極性信号POLは負極性(−)を指示しているので、駆動電圧発生回路56[1]〜56[J]は、基準電位VREFに対して負極性の範囲で、各々に供給される画像信号D[1]〜D[J]の指定階調に応じた階調電圧VGを各々出力する。駆動電圧発生回路56[1]〜56[J]が各々出力する階調電圧VGは、デマルチプレクサー57[1]〜57[J]におけるスイッチ58[1]を各々通過し、信号線駆動信号C[1]〜C[J]として配線ブロックB[1]〜B[J]の各々の1番目の信号線14に印加される。

【0060】

階調電圧印加期間U[2]では、選択信号SELa[2]およびSELb[2]の組のみがHレベルとされ、マルチプレクサー53[1]〜53[J]におけるスイッチ54[2]と、デマルチプレクサー57[1]〜57[J]におけるスイッチ58[2]がONになる。この結果、レジスターブロック52[1]〜52[J]の各々における2番目の画素の画像信号VIDに応じた各階調電圧VGが発生され、デマルチプレクサー57[1]〜57[J]におけるスイッチ58[2]を各々通過し、信号線駆動信号C[1]〜C[J]として配線ブロックB[1]〜B[J]の各々の2番目の信号線14に印加される。

【0061】

以下、同様であり、階調電圧印加期間U[3]では各レジスターブロックにおける3番目の画素の画像信号に応じた各階調電圧VGが各配線ブロックの3番目の信号線14に印加され、階調電圧印加期間U[4]では各レジスターブロックにおける4番目の画素の画像信号に応じた各階調電圧VGが各配線ブロックの4番目の信号線14に印加され、…、最後の階調電圧印加期間U[K]では各レジスターブロックにおけるK番目の画素の画像信号に応じた各階調電圧VGが各配線ブロックのK番目の信号線14に印加される。

以上が垂直走査期間V1のm番目の水平走査期間H内における各部の動作である。

【0062】

図8の下段右側には、垂直走査期間V1の次の垂直走査期間V2の同じ水平走査期間H(すなわち、垂直走査期間V2内のm番目の水平走査期間H)内に発生する選択信号SELa[1]〜SELa[K]および選択信号SELb[1]〜SELb[K]の波形が示されている。

【0063】

ここで、垂直走査期間V2におけるm番目の水平走査期間Hにおけるカウンター32のカウント値CNT1は、垂直走査期間V1におけるm番目の水平走査期間Hにおけるカウンター32のカウント値CNT1と同じになる。何故ならば、カウンター32のカウント値CNT1は、垂直走査期間が切り換わる毎に「0」に初期化されるからである。しかし、垂直走査期間V1から垂直走査期間V2に切り換わるとき、制御信号処理部31が出力する内部垂直同期信号VSにより、カウンター33のカウント値CNT2がステップ値STP2だけインクリメントされる。このため、垂直走査期間V2におけるm番目の水平走査期間Hにおいて、パターンジェネレーター35に与えられるパターン番号PNは、垂直走査期間V1におけるm番目の水平走査期間Hにおいて与えられるパターン番号PNと異なったものとなる。従って、垂直走査期間V2のm番目の水平走査期間Hの書込期間TWRTでは、垂直走査期間V1のm番目の水平走査期間Hの書込期間TWRTとは異なった順序で、各配線ブロックのK本の信号線14への階調電圧の印加が行われる。

【0064】

図8の下段右側に示す例では、書込期間TWRTの階調電圧印加期間U[1]では、各レジスターブロックにおけるK番目の画素の画像信号に応じた各階調電圧VGが各配線ブロックのK番目の信号線14に印加され、階調電圧印加期間U[2]では各レジスターブロックにおける1番目の画素の画像信号に応じた各階調電圧VGが各配線ブロックの1番目の信号線14に印加され、…、最後の階調電圧印加期間U[K]では各レジスターブロックにおけるK−1番目の画素の画像信号に応じた各階調電圧VGが各配線ブロックのK−1番目の信号線14に印加される。

【0065】

なお、垂直走査期間V2においては、極性信号POLは正極性(+)を指示しているので、駆動電圧発生回路56[1]〜56[J]は、基準電位VREFに対して正極性の範囲で、各々に供給される画像信号の指定階調に応じた階調電圧VGを各々出力する。

【0066】

以上のように、垂直走査期間V1のm番目の水平走査期間Hと垂直走査期間V2のm番目の水平走査期間Hとでは、異なる順序で、各配線ブロックのK本の信号線14への階調電圧の印加が行われる。このように本実施形態において各配線ブロックのK本の信号線14への階調電圧の印加の順序は、垂直走査期間の切り換わりに応じて変更されるが、それだけでなく、水平走査期間Hの切り換わりに応じて変更される。図9は、ステップ値STP1およびSTP2の両方が「1」である場合における各配線ブロック内のK本の信号線14への階調電圧の印加順序の変化の様子を例示するものである。図9において、縦方向は水平走査期間Hの遷移方向に対応しており、横方向は水平走査期間H内に発生するK個の階調電圧印加期間U[1]〜U[K]の並びに対応している。図9に示す例では、同一の垂直走査周期内において、配線ブロック内の各信号線14に階調電圧の印加が行われる順序は、水平走査期間Hが切り換わる毎に1番ずつ後方へローテートシフトされる。また、図9に示す例において、各垂直走査期間内の同一水平走査期間Hに着目すると、配線ブロック内の各信号線14に階調電圧の印加が行われる順序は、垂直走査期間が切り換わる毎に1番ずつ後方へローテートシフトされる。

【0067】

従って、複数の水平走査期間および複数の垂直走査期間を通じて見た場合に、各信号線14間で、一水平走査期間内における階調電圧の印加順序の時間平均値が均一化される。従って、電気光学装置単体として見た場合、表示ムラが軽減される。

【0068】

ところで、本実施形態による投射型表示装置では、3個の電気光学装置100R、100Gおよび100Rの各々において、独立して以上のような各信号線14への階調電圧の印加順序の更新制御が進められる。ここで、投射型表示装置の例えばパワーオン時に各電気光学装置100R、100Gおよび100Rの各々のカウンター32のカウント値CNT1およびカウンター33のカウント値CNT2を同時に初期化すれば、3個の電気光学装置100R、100Gおよび100R間で、各信号線14への階調電圧の印加順序の更新制御を初期状態から同時に開始させることができる。しかしながら、投射型表示装置の稼働中に発生するノイズ等の影響により、3個の電気光学装置100R、100Gおよび100R間で、カウンター32のカウント値CNT1またはカウンター33のカウント値CNT2に相違が発生する可能性がある。この場合、各信号線14への階調電圧の印加順序が3個の電気光学装置100R、100Gおよび100R間で異なったものとなる。この結果、上述したように表示画像に色つきが発生する。

【0069】

本実施形態の特徴は、このような問題の発生を防止するために、各配線ブロック内の複数の信号線14への階調電圧の印加順序の更新制御を電気光学装置100R、100Gおよび100R間で同期化させるための手段を投射型表示装置に設けた点にある。すなわち、本実施形態において、ホストCPU60は、上述した初期化用同期信号ISYNCを周期的に電気光学装置100R、100Gおよび100Bの各々の制御回路30に供給することにより階調電圧の印加順序の更新制御を電気光学装置100R、100Gおよび100R間で同期化させる。

【0070】

図10は本実施形態における初期化用同期信号ISYNCの発生タイミングを示すタイムチャートである。図10に示すようにホストCPU60は、階調電圧の印加順序の更新制御の周期の整数倍、すなわち、一垂直走査期間内の各水平走査期間における配線ブロック内のK本の信号線14への階調電圧の印加順序がある順序になってから再び同じ順序に更新されるまでに要する期間の整数倍の周期で発生するタイミングあって、垂直同期信号VSYNCに同期したタイミングにおいて発生する。例えば図9に示す例では、フレーム番号FN=FN0の画面の表示を行う垂直走査周期において、一垂直走査期間内の各水平走査期間における配線ブロック内のK本の信号線14への階調電圧の印加順序がある順序となり、その後、フレーム番号FN=FN0+K−1の画面の表示を行う垂直走査周期において、一垂直走査期間内の各水平走査期間における配線ブロック内のK本の信号線14への階調電圧の印加順序が再び同じ順序となる。従って、この場合の印加順序の更新制御の周期は、垂直走査期間のK倍の長さの周期であり、ホストCPU60は、垂直走査期間の例えばL×K倍(Lは整数)の周期で初期化用同期信号ISYNCを電気光学装置100R、100Gおよび100Bの各々の制御回路30に供給する。

【0071】

電気光学装置100R、100Gおよび100Bの各制御回路30の制御信号処理回路31は、ホストCPU60から初期化用同期信号ISYNCが与えられるのに応じて、第2の初期化信号RES2をアクティブレベルとし、カウンター33のカウント値CNT2を「0」に初期化する。

【0072】

このように本実施形態によれば、印加順序の更新制御の周期の整数倍の周期で発生し、かつ、垂直同期信号VSYNCに同期したタイミングで、ホストCPU60から電気光学装置100R、100Gおよび100Bの各制御回路30に初期化用同期信号ISYNCが供給され、各電気光学装置100R、100Gおよび100Bのカウンター33のカウント値CNT2が「0」に初期化される。従って、その後の垂直走査期間以降、電気光学装置100R、100Gおよび100B間では、同じ印加順序で、配線ブロック内のK本の信号線14への階調電圧の印加が行われ、色つきの発生が防止される。

【0073】

<2.第2実施形態>

本実施形態においても、上記第1実施形態と同様、ホストCPU60は、印加順序の更新制御の周期の整数倍の周期で電気光学装置100R、100Gおよび100Bの各々のカウンター33のカウント値CNT2を初期化するための処理を行う。本実施形態と上記第1実施形態との相違は、この初期化のために行うホストCPU60および各制御回路30間の信号の授受の手順にある。後述する第3〜第8実施形態も同様である。

【0074】

図11は本実施形態による投射型表示装置の動作を示すタイムチャートである。本実施形態において、ホストCPU60は、印加順序の更新制御の周期の整数倍の周期の切り換わりタイミングの所定時間前のタイミングになると、まず、電気光学装置100R、100Gおよび100Bの各制御回路30に対し、カウント値CNT2の初期化を命じる初期化コマンドを送る。具体的には、チップセレクト信号CS_Rをアクティブレベルとし、初期化コマンドの構成ビットからなるシリアルデータSDIをシリアルクロックSCKに同期させて出力し、このシリアルデータSDIを電気光学装置100Rの制御回路30に受信させる。次にチップセレクト信号CS_Rを非アクティブレベルに戻した後、チップセレクト信号CS_Gをアクティブレベルとし、初期化コマンドの構成ビットからなるシリアルデータSDIをシリアルクロックSCKに同期させて出力し、このシリアルデータSDIを電気光学装置100Gの制御回路30に受信させる。次にチップセレクト信号CS_Gを非アクティブレベルに戻した後、チップセレクト信号CS_Bをアクティブレベルとし、初期化コマンドの構成ビットからなるシリアルデータSDIをシリアルクロックSCKに同期させて出力し、このシリアルデータSDIを電気光学装置100Bの制御回路30に受信させるのである。

【0075】

このように電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを受信させた後、ホストCPU60は、印加順序の更新制御の周期の整数倍の周期の切り換わりタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、初期化用同期信号ISYNCを各制御回路30に供給する。本実施形態において、制御回路30内の制御信号処理部31は、初期化用同期信号ISYNCを事前に受信したコマンドの実行の指示と解釈する。この場合、電気光学装置100R、100Gおよび100Bの各制御信号処理部31は、初期化用同期信号ISYNCが供給される前に初期化コマンドを取り込んでいるので、初期化コマンドを実行し、カウンター33のカウント値CNT2を「0」に初期化する。

本実施形態においても上記第1実施形態と同様な効果が得られる。

【0076】

<3.第3実施形態>

図12は本実施形態による投射型表示装置の動作を示すタイムチャートである。本実施形態において、電気光学装置100Rの制御回路30は、チップセレクト信号CS_Rが非アクティブレベルからアクティブレベルになった後、シリアルクロックSCKに同期して伝送されてくる所定ビット数からなるシリアルデータSDIを当該制御回路30宛てのコマンドと認識して受信する。同様に、電気光学装置100G(100B)の制御回路30は、チップセレクト信号CS_G(CS_B)が非アクティブレベルからアクティブレベルになった後、シリアルクロックSCKに同期して伝送されてくる所定ビット数からなるシリアルデータSDIを当該制御回路30宛てのコマンドと認識して受信する。

【0077】

そこで、ホストCPU60は、印加順序の更新制御の周期の整数倍の周期の切り換わりタイミングの所定時間だけ前になったとき、次のようにして電気光学装置100R、100Gおよび100Bの各制御回路30宛てに初期化コマンドを送信する。まず、ホストCPU60は、チップセレクト信号CS_Rをアクティブレベルとし、初期化コマンドの構成ビットからなるシリアルデータSDIをシリアルクロックSCKに同期させて送出し、初期化コマンドを電気光学装置100Rの制御回路30に受信させる。次にホストCPU60は、チップセレクト信号CS_Rをアクティブレベルに維持した状態で、チップセレクト信号CS_Gをアクティブレベルとし、初期化コマンドの構成ビットからなるシリアルデータSDIをシリアルクロックSCKに同期させて送出し、初期化コマンドを電気光学装置100Gの制御回路30に受信させる。このとき電気光学装置100Rの制御回路30は、チップセレクト信号CS_Rがアクティブレベルになった後、所定ビット数からなる初期化コマンドを受信しているので、電気光学装置100Gの制御回路30宛ての初期化コマンドを誤って受信することはない。次にホストCPU60は、チップセレクト信号CS_RおよびCS_Gをアクティブレベルに維持した状態で、チップセレクト信号CS_Bをアクティブレベルとし、初期化コマンドの構成ビットからなるシリアルデータSDIをシリアルクロックSCKに同期させて送出し、初期化コマンドを電気光学装置100Bの制御回路30に受信させる。

【0078】

このようにして電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを受信させた後、ホストCPU60はチップセレクト信号CS_R、CS_GおよびCS_Bを同時にアクティブレベルから非アクティブレベルへ変化させる。本実施形態において、電気光学装置100Rの制御回路30の制御信号処理部31は、チップセレクト信号CS_Rのアクティブレベルから非アクティブレベルへの変化を初期化コマンドの実行指示と解釈し、カウント値CNT2の初期化を行う。同様に、電気光学装置100G(100B)の制御回路30の制御信号処理部31は、チップセレクト信号CS_G(CS_B)のアクティブレベルから非アクティブレベルへの変化を初期化コマンドの実行指示と解釈し、カウント値CNT2の初期化を行う。従って、本実施形態では、チップセレクト信号CS_R、CS_GおよびCS_Bが同時にアクティブレベルから非アクティブレベルに変化するタイミングにおいて、電気光学装置100R、100Gおよび100Bの各々におけるカウント値CNT2の初期化が同時に行われる。

【0079】

そして、本実施形態では、このチップセレクト信号CS_R、CS_GおよびCS_Bのアクティブレベルから非アクティブレベルへの一斉変化タイミングが、垂直同期信号VSYNCに同期したタイミングとなるように、ホストCPU60は、垂直同期信号VSYNCの発生タイミングの所定時間だけ前のタイミングに電気光学装置100R、100Gおよび100Bの各制御回路30宛ての初期化コマンドの送出を行うのである。

本実施形態においても上記第1および第2実施形態と同様な効果が得られる。

【0080】

<4.第4実施形態>

図13はこの発明の第4実施形態である投射型表示装置の動作を示すタイムチャートである。上記第2実施形態(図11)において、ホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを送った後、階調電圧の印加順序の更新制御の周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、初期化用同期信号ISYNCを電気光学装置100R、100Gおよび100Bの各制御回路30に送信した。これに対し、本実施形態においてホストCPU60は、当該垂直同期信号VSYNCに同期したタイミングよりも前に初期化用同期信号ISYNCを送信する。電気光学装置100R、100Gおよび100Bの各制御回路30の各制御信号処理部31は、初期化コマンドおよび初期化用同期信号ISYNCを受信した後の垂直同期信号VSYNCに同期してカウンター33のカウント値CNT2を初期化する。

【0081】

本実施形態においても上記第1〜第3実施形態と同様な効果が得られる。また、本実施形態では、電気光学装置100R、100Gおよび100Bの各制御信号処理部31が垂直同期信号VSYNCに同期してカウンター33のカウント値CNT2を初期化するので、ホストCPU60による初期化用同期信号ISYNCの送出タイミングに関して厳しい時間精度が要求されないという利点がある。

【0082】

<5.第5実施形態>

図14はこの発明の第5実施形態である投射型表示装置の動作を示すタイムチャートである。上記第3実施形態(図12)において、ホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを送った後、階調電圧の印加順序の更新制御の周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、チップセレクト信号CS_R、CS_GおよびCS_Bを一斉にアクティブレベルから非アクティブレベルに変化させた。これに対し、本実施形態においてホストCPU60は、当該垂直同期信号VSYNCに同期したタイミングよりも前にチップセレクト信号CS_R、CS_GおよびCS_Bを一斉にアクティブレベルから非アクティブレベルに変化させる。電気光学装置100R、100Gおよび100Bの各制御回路30の各制御信号処理部31は、初期化コマンドを受信し、かつ、各々に対するチップセレクト信号のアクティブレベルから非アクティブレベルへの変化を検知した後の垂直同期信号VSYNCに同期してカウンター33のカウント値CNT2を初期化する。

本実施形態においても上記第4実施形態と同様な効果が得られる。

【0083】

<6.第6実施形態>

図15はこの発明の第6実施形態である投射型表示装置4000aの電気的構成を示すブロック図である。また、図16は本実施形態の動作を示すタイムチャートである。上記第1〜第5実施形態において、ホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に対して個別的なチップセレクト信号CS_R、CS_GおよびCS_Bを各々供給した。これに対し、本実施形態においてホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に対して共通のチップセレクト信号CSを供給する。そして、ホストCPU60は、印加順序の更新制御の周期の整数倍の周期の切り換わりタイミングの所定時間だけ前になったとき、電気光学装置100R、100Gおよび100Bの各々においてカウント値CNT2の初期化を行わせるための以下の処理を開始する。

【0084】

まず、ホストCPU60は、図16に示すように、チップセレクト信号CSをアクティブレベルとし、電気光学装置100R、100Gおよび100Bの各制御回路30に対する3個の初期化コマンドを各々示すシリアルデータSDIを、シリアルクロックSCLKに同期させて順次送出する。電気光学装置100Rの制御回路30は、シリアルクロックSCLKに同期して伝送されてくるシリアルデータSDIの中から最初の初期化コマンドを選択して受信する。次に、電気光学装置100Gの制御回路30は、シリアツクロックSCLKに同期して伝送されてくるシリアルデータSDIの中から2番目の初期化コマンドを選択して受信する。次に、電気光学装置100Bの制御回路30は、シリアツクロックSCLKに同期して伝送されてくるシリアルデータSDIの中から3番目の初期化コマンドを選択して受信する。

【0085】

このようにして初期化コマンドを電気光学装置100A、100Bおよび100Cの各制御回路30に受信させた後、ホストCPU60は、印加順序の更新制御の周期の整数倍の周期の切り換わりタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、初期化用同期信号ISYNCを電気光学装置100A、100Bおよび100Cの各制御回路30に供給する。

【0086】

電気光学装置100R、100Gおよび100Bの各制御回路30の制御信号処理部31は、初期化用同期信号ISYNCが与えられることにより、事前に受信した初期化コマンドを実行し、カウント値CNT2の初期化を行う。

本実施形態においても上記第1〜第3実施形態と同様な効果が得られる。

【0087】

<7.第7実施形態>

図17はこの発明の第7実施形態である投射型表示装置の動作を示すタイムチャートである。上記第6実施形態(図16)においてホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを送った後、階調電圧の印加順序の更新制御の周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、初期化用同期信号ISYNCを電気光学装置100R、100Gおよび100Bの各制御回路30に送信した。本実施形態において、ホストCPU60は、初期化用同期信号ISYNCを送信しない。その代わりに、ホストCPU60は、チップセレクト信号CSをアクティブレベルにして、電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを送った後、階調電圧の印加順序の更新制御の周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、チップセレクト信号CSを非アクティブレベルにする。

【0088】

電気光学装置100R、100Gおよび100Bの各制御回路30の制御信号処理部31は、初期化コマンドを受信した後、各々に対するチップセレクト信号のアクティブレベルから非アクティブレベルへの変化を検知したタイミングにおいて初期化コマンドを実行し、カウンター33のカウント値CNT2を初期化する。

本実施形態においても上記第3実施形態と同様な効果が得られる。

【0089】

<8.第8実施形態>

図18はこの発明の第8実施形態である投射型表示装置の動作を示すタイムチャートである。上記第7実施形態(図17)においてホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを送った後、階調電圧の印加順序の更新制御の周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、チップセレクト信号CSをアクティブレベルから非アクティブレベルに変化させた。これに対し、本実施形態において、ホストCPU60は、チップセレクト信号CSをアクティブレベルにして、電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを送った後、当該垂直同期信号VSYNCに同期したタイミングより前のタイミングにおいて、チップセレクト信号CSを非アクティブレベルにする。

【0090】

電気光学装置100R、100Gおよび100Bの各制御回路30の制御信号処理部31は、初期化コマンドを受信し、かつ、各々に対するチップセレクト信号のアクティブレベルから非アクティブレベルへの変化を検知した後の垂直同期信号VSYNCに同期したタイミングにおいて初期化コマンドを実行し、カウンター33のカウント値CNT2を初期化する。

本実施形態においても上記第5および第6実施形態と同様な効果が得られる。

【0091】

なお、第7実施形態(図17)から第8実施形態(図18)への変形を第6実施形態(図16)に適用してもよい。すなわち、ホストCPU60は、電気光学装置100R、100Gおよび100Bの各制御回路30に初期化コマンドを送った後、階調電圧の印加順序の更新制御の周期の整数倍の周期で発生するタイミングであって、垂直同期信号VSYNCに同期したタイミングよりも前に初期化用同期信号ISYNCを送信する。電気光学装置100R、100Gおよび100Bの各制御回路30の制御信号処理部31は、初期化コマンドを受信し、かつ、初期化用同期信号ISYNCを受信した後の垂直同期信号VSYNCに同期したタイミングにおいてカウンター33のカウント値CNT2を初期化するのである。

【0092】

<9.第9実施形態>

図19はこの発明の第9実施形態である電気光学装置の構成を示すブロック図である。本実施形態では、画素部全体が2つの画素部10aおよび10bに区分されている。そして、画素部10aの駆動を行うために走査線駆動回路22aおよび信号線駆動回路24aからなる駆動回路20aが設けられ、画素部10bの駆動を行うために走査線駆動回路22bおよび信号線駆動回路24bからなる駆動回路20bが設けられている。また、駆動回路20aの制御を行うために制御回路30aが設けられ、駆動回路20bの制御を行うために制御回路30bが設けられている。そして、制御回路30aおよび30bでは、上記第1実施形態において説明したものと同様な配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御が行われる。

【0093】

ここで、制御回路30aおよび30bでは、例えば前掲図6のカウンター32、33、加算器34およびパターンジェネレーター35からなる回路を用いて、階調電圧の印加順序の更新制御が互いに独立して行われる。従って、例えばノイズ等の影響により、画素部10aを対象とした階調電圧の印加順序の更新制御と、画素部10bを対象とした階調電圧の印加順序の更新制御との間に位相ずれが発生する可能性がある。このような位相ずれが発生すると、画素部10aと画素部10bとの境界において表示ムラが発生する。

【0094】

そこで、本実施形態では、図示しない同期化制御手段(例えば上記第1〜第8実施形態におけるホストCPU60に相当するもの)が、印加順序の更新制御の周期の整数倍の周期の切り換わりタイミングであって、垂直同期信号VSYNCに同期したタイミングにおいて、制御回路30aおよび30bの各々における印加順序の更新制御を初期化する。これにより画素部10aと画素部10bとで階調電圧の印加順序の更新制御を同期化し、画素部10aと画素部10bとの境界に表示ムラが発生するのを防止することができる。

【0095】

<10.変形例>

以上、この発明の第1〜第9実施形態について説明したが、この発明には、上述した実施形態に限定されるものではなく、例えば、以下の変形が可能である。

【0096】

(1)上記第1〜第8実施形態において、ホストCPU60は、電気光学装置100A、100Bおよび100Cの各制御回路30に初期化コマンドを送出した後、初期化コマンドの実行タイミングを指示するために、初期化用同期信号ISYNCを供給し、またはチップセレクト信号CSの立ち上げを行った。しかし、そのようにする代わりに、電気光学装置100A、100Bおよび100Cの各制御回路30が、初期化コマンドの受信後の最初の垂直同期信号VSYNCにおいて初期化コマンドを実行する構成としてもよい。この態様においても、上記各実施形態と同様の効果が得られる。

【0097】

(2)上記第1実施形態では、内部垂直同期信号VSが発生する都度、カウンター32のカウント値CNT1を初期化する構成としたため、制御信号処理部31は、初期化コマンドの実行時、カウンター33のカウント値CNT2のみを初期化した。しかし、内部垂直同期信号VSの発生時にカウンター32のカウント値CNT1を初期化しない構成もあり得る。この場合、制御信号処理部31は、初期化コマンドの実行時、カウンター33のカウント値CNT2とカウンター32のカウント値CNT1の両方を初期化する構成とすればよい。

【0098】

(3)上記各実施形態において、配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期は、垂直走査期間の整数倍の長さの周期であった。しかし、投射型表示装置や電気光学装置において、垂直走査期間の整数倍の長さの周期ではなく、水平走査期間の整数倍の周期で、配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を行う場合もあり得る。このような場合、ホストCPU60は、この更新制御の周期である水平走査期間の整数倍の周期に同期して、複数の駆動回路の各々における配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の初期化を行えばよい。

【0099】

(4)上記各実施形態では、複数の駆動回路が互いに独立して行う階調電圧の印加順序の更新制御を同期化の対象とした。しかし、この発明の適用対象はこれに限定されるものではない。画素部を駆動する複数の駆動回路が互いに独立して実行する何らかの駆動条件の周期的な更新制御を実行する場合に、この周期的な更新制御を同期化の対象としてもよい。

【0100】

(5)液晶素子42は電気光学素子の例示に過ぎない。本発明に適用される電気光学素子について、自身が発光する自発光型と外光の透過率や反射率を変化させる非発光型(例えば液晶素子42)との区別や、電流の供給によって駆動される電流駆動型と電界(電圧)の印加によって駆動される電圧駆動型との区別は不問である。例えば、有機EL素子,無機EL素子,LED(Light Emitting Diode),電界電子放出素子(FE(Field−Emission)素子),表面伝導型電子放出素子(SE(Surface conduction Electron emitter)素子),弾道電子放出素子(BS(Ballistic electron Emitting)素子),電気泳動素子、エレクトロクロミック素子など様々な電気光学素子を利用した電気光学装置100に本発明は適用される。すなわち、電気光学素子は、電流の供給や電圧(電界)の印加といった電気的な作用に応じて階調(透過率や輝度などの光学的な特性)が変化する電気光学物質(例えば液晶425)を利用した被駆動素子(典型的には、階調信号に応じて階調が制御される表示素子)として包括される。

【0101】

<11.応用例>

この発明は、投射型表示装置以外の各種の電子機器に利用され得る。図20および図21は、この発明の適用対象となる電子機器の具体的な形態を例示するものである。

【0102】

図20は、電気光学装置を採用した可搬型のパーソナルコンピューターの斜視図である。パーソナルコンピューター2000は、各種の画像を表示する電気光学装置100と、電源スイッチ2001やキーボード2002が設置された本体部2010とを具備する。このようなパーソナルコンピューター2000の中には、電気光学装置100が複数の画素部からなり、各画素部毎に上述した階調電圧の印加順序の更新制御を行う構成のものがある。このようなパーソナルコンピューター2000に対して本発明を適用することにより上述した縦ノイズの発生を防止することができる。

【0103】

図21は、携帯電話機の斜視図である。携帯電話機3000は、複数の操作ボタン3001およびスクロールボタン3002と、各種の画像を表示する電気光学装置100とを備える。スクロールボタン3002を操作することによって、電気光学装置100に表示される画面がスクロールされる。本発明はこのような携帯電話機にも適用可能である。

【0104】

なお、本発明が適用される電子機器としては、図1、図20および図21に例示した機器のほか、携帯情報端末(PDA:Personal Digital Assistants),デジタルスチルカメラ,テレビ,ビデオカメラ,カーナビゲーション装置,車載用の表示器(インパネ),電子手帳,電子ペーパー,電卓,ワードプロセッサ,ワークステーション,テレビ電話,POS端末,プリンタ,スキャナ,複写機,ビデオプレーヤ,タッチパネルを備えた機器等などが挙げられる。

【符号の説明】

【0105】

100,100R,100G,100B……電気光学装置、10,10a,10b……画素部、PIX……画素回路、12……走査線、14……信号線、20,20a,20b……駆動回路、22,22a,22b……走査線駆動回路、24,24a,24b……信号線駆動回路、30,30a,30b……制御回路、42……液晶素子、44……選択スイッチ、57[1]〜57[J]……デマルチプレクサー、53[1]〜53[J]……マルチプレクサー、56[1]〜56[J]……駆動電圧発生回路、60……ホストCPU、70……画像入力部、31……制御信号処理部、32,33……カウンター、34……加算器、35……パターンジェネレーター。

【特許請求の範囲】

【請求項1】

互いに交差する複数の走査線および複数の信号線を有するとともに、前記複数の走査線と前記複数の信号線との各交差に対応して各々配置された複数の画素回路を有する画素部と、

一垂直走査期間内に前記複数の走査線を順次選択し、選択した走査線と前記複数の信号線との各交差に対応付けられた複数の画素回路を前記複数の信号線に接続する走査線駆動回路と、

前記複数の信号線を複数の配線ブロックに分け、配線ブロック毎に、一水平走査期間内に当該配線ブロックに属する各信号線を順次選択し、選択した信号線に階調電圧を印加する信号線駆動回路と、

前記複数の配線ブロックにおける配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を実行する制御回路と

を各々具備する複数の電気光学装置と、

前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を一斉に初期化する動作を時間を空けて繰り返すことにより、前記複数の電気光学装置の各々における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を同期化する同期化手段と

を具備することを特徴とする電子機器。

【請求項2】

前記同期化手段は、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を一斉に初期化する動作を繰り返すことを特徴とする請求項1に記載の電子機器。

【請求項3】

前記複数の電気光学装置の各制御回路は、前記垂直走査期間の整数倍の長さの周期で、前記配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を実行し、

前記同期化手段は、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で、前記垂直走査期間の切り換わりを指示する垂直同期信号に同期して、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を一斉に初期化する動作を繰り返すことを特徴とする請求項2に記載の電子機器。

【請求項4】

前記複数の電気光学装置の制御回路に対して各種の制御情報を供給するホストCPUが前記同期化手段として機能するものであり、

前記ホストCPUは、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で、前記垂直走査期間の切り換わりを指示する垂直同期信号に同期して前記初期化を指示する初期化用同期信号を前記複数の電気光学装置の各制御回路に送信し、前記複数の電気光学装置の各制御回路は、前記初期化用同期信号の受信タイミングにおいて前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を初期化することを特徴とする請求項3に記載の電子機器。

【請求項5】

前記複数の電気光学装置の制御回路に対して各種の制御情報を供給するホストCPUが前記同期化手段として機能するものであり、

前記ホストCPUは、予め前記初期化を指示する初期化コマンドを前記複数の電気光学装置の各制御回路に送信した後、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で発生するタイミングであって、前記垂直走査期間の切り換わりを指示する垂直同期信号に同期したタイミングにおいて、初期化用同期信号を前記複数の電気光学装置の各制御回路に送信し、前記複数の電気光学装置の各制御回路は、前記初期化コマンドの受信後、前記初期化用同期信号の受信タイミングにおいて前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を初期化することを特徴とする請求項3に記載の電子機器。

【請求項6】

前記複数の電気光学装置の制御回路に対して各種の制御情報を供給するホストCPUが前記同期化手段として機能するものであり、

前記ホストCPUは、予め前記複数の電気光学装置の制御回路の各々に対するチップセレクト信号をアクティブレベルとして、前記初期化を指示する初期化コマンドを前記複数の電気光学装置の制御回路に受信させた後、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で発生するタイミングであって、前記垂直走査期間の切り換わりを指示する垂直同期信号に同期したタイミングにおいて、前記複数の電気光学装置の制御回路の各々に対するチップセレクト信号をアクティブレベルから非アクティブレベルに一斉に変化させ、

前記複数の電気光学装置の制御回路は、前記初期化コマンドの受信後の前記チップセレクト信号のアクティブレベルから非アクティブレベルへの変化時に、前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を初期化することを特徴とする請求項3に記載の電子機器。

【請求項7】

前記複数の電気光学装置の制御回路に対して各種の制御情報を供給するホストCPUが前記同期化手段として機能するものであり、

前記ホストCPUは、予め前記複数の電気光学装置の制御回路の各々に対するチップセレクト信号をアクティブレベルとして、前記初期化を指示する初期化コマンドを前記複数の電気光学装置の制御回路に受信させ、その後、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で発生するタイミングであって、前記垂直走査期間の切り換わりを指示する垂直同期信号に同期したタイミングよりも所定時間だけ前に、初期化用同期信号を前記複数の電気光学装置の制御回路に送信し、

前記複数の電気光学装置の制御回路は、前記初期化コマンドおよび前記初期化用同期信号の受信後の最初の垂直同期信号に同期したタイミングにおいて、前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を初期化することを特徴とする請求項3に記載の電子機器。

【請求項8】

前記複数の電気光学装置の制御回路に対して各種の制御情報を供給するホストCPUが前記同期化手段として機能するものであり、

前記ホストCPUは、予め前記複数の電気光学装置の制御回路の各々に対するチップセレクト信号をアクティブレベルとして、前記初期化を指示する初期化コマンドを前記複数の電気光学装置の制御回路に受信させ、その後、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で発生するタイミングであって、前記垂直走査期間の切り換わりを指示する垂直同期信号に同期したタイミングよりも所定時間だけ前に、前記複数の電気光学装置の制御回路の各々に対するチップセレクト信号をアクティブレベルから非アクティブレベルに一斉に変化させ、

前記複数の電気光学装置の制御回路は、前記初期化コマンドを受信し、前記チップセレクト信号のアクティブレベルから非アクティブレベルへの変化があった後の最初の垂直同期信号に同期したタイミングにおいて、前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を初期化することを特徴とする請求項3に記載の電子機器。

【請求項9】

互いに交差する複数の走査線および複数の信号線を有するとともに、前記複数の走査線と前記複数の信号線との各交差に対応して各々配置された複数の画素回路を各々有する複数の画素部と、

前記複数の画素部の各画素部における前記複数の走査線を一垂直走査期間内に順次選択し、選択した走査線と前記複数の信号線との各交差に対応付けられた複数の画素回路を前記複数の信号線に接続する走査線駆動手段と、

前記複数の画素部に各々対応付けられた複数の信号線駆動回路であって、各画素部の前記複数の信号線を複数の配線ブロックに分け、配線ブロック毎に、一水平走査期間内に当該配線ブロックに属する各信号線を順次選択し、選択した信号線に階調電圧を印加する複数の信号線駆動回路と、

前記複数の信号線駆動回路の各々における前記複数の配線ブロックにおける配線ブロック内の複数の信号線への階調電圧の印加順序を各々周期的に更新する複数の制御回路と、

前記複数の制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を一斉に初期化する動作を時間を空けて繰り返し実行する同期化手段と

を具備することを特徴とする電気光学装置。

【請求項10】

前記同期化手段は、前記複数の制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で、前記複数の制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を一斉に初期化する動作を繰り返すことを特徴とする請求項9に記載の電気光学装置。

【請求項1】

互いに交差する複数の走査線および複数の信号線を有するとともに、前記複数の走査線と前記複数の信号線との各交差に対応して各々配置された複数の画素回路を有する画素部と、

一垂直走査期間内に前記複数の走査線を順次選択し、選択した走査線と前記複数の信号線との各交差に対応付けられた複数の画素回路を前記複数の信号線に接続する走査線駆動回路と、

前記複数の信号線を複数の配線ブロックに分け、配線ブロック毎に、一水平走査期間内に当該配線ブロックに属する各信号線を順次選択し、選択した信号線に階調電圧を印加する信号線駆動回路と、

前記複数の配線ブロックにおける配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を実行する制御回路と

を各々具備する複数の電気光学装置と、

前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を一斉に初期化する動作を時間を空けて繰り返すことにより、前記複数の電気光学装置の各々における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を同期化する同期化手段と

を具備することを特徴とする電子機器。

【請求項2】

前記同期化手段は、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を一斉に初期化する動作を繰り返すことを特徴とする請求項1に記載の電子機器。

【請求項3】

前記複数の電気光学装置の各制御回路は、前記垂直走査期間の整数倍の長さの周期で、前記配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を実行し、

前記同期化手段は、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で、前記垂直走査期間の切り換わりを指示する垂直同期信号に同期して、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を一斉に初期化する動作を繰り返すことを特徴とする請求項2に記載の電子機器。

【請求項4】

前記複数の電気光学装置の制御回路に対して各種の制御情報を供給するホストCPUが前記同期化手段として機能するものであり、

前記ホストCPUは、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で、前記垂直走査期間の切り換わりを指示する垂直同期信号に同期して前記初期化を指示する初期化用同期信号を前記複数の電気光学装置の各制御回路に送信し、前記複数の電気光学装置の各制御回路は、前記初期化用同期信号の受信タイミングにおいて前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を初期化することを特徴とする請求項3に記載の電子機器。

【請求項5】

前記複数の電気光学装置の制御回路に対して各種の制御情報を供給するホストCPUが前記同期化手段として機能するものであり、

前記ホストCPUは、予め前記初期化を指示する初期化コマンドを前記複数の電気光学装置の各制御回路に送信した後、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で発生するタイミングであって、前記垂直走査期間の切り換わりを指示する垂直同期信号に同期したタイミングにおいて、初期化用同期信号を前記複数の電気光学装置の各制御回路に送信し、前記複数の電気光学装置の各制御回路は、前記初期化コマンドの受信後、前記初期化用同期信号の受信タイミングにおいて前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を初期化することを特徴とする請求項3に記載の電子機器。

【請求項6】

前記複数の電気光学装置の制御回路に対して各種の制御情報を供給するホストCPUが前記同期化手段として機能するものであり、

前記ホストCPUは、予め前記複数の電気光学装置の制御回路の各々に対するチップセレクト信号をアクティブレベルとして、前記初期化を指示する初期化コマンドを前記複数の電気光学装置の制御回路に受信させた後、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で発生するタイミングであって、前記垂直走査期間の切り換わりを指示する垂直同期信号に同期したタイミングにおいて、前記複数の電気光学装置の制御回路の各々に対するチップセレクト信号をアクティブレベルから非アクティブレベルに一斉に変化させ、

前記複数の電気光学装置の制御回路は、前記初期化コマンドの受信後の前記チップセレクト信号のアクティブレベルから非アクティブレベルへの変化時に、前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を初期化することを特徴とする請求項3に記載の電子機器。

【請求項7】

前記複数の電気光学装置の制御回路に対して各種の制御情報を供給するホストCPUが前記同期化手段として機能するものであり、

前記ホストCPUは、予め前記複数の電気光学装置の制御回路の各々に対するチップセレクト信号をアクティブレベルとして、前記初期化を指示する初期化コマンドを前記複数の電気光学装置の制御回路に受信させ、その後、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で発生するタイミングであって、前記垂直走査期間の切り換わりを指示する垂直同期信号に同期したタイミングよりも所定時間だけ前に、初期化用同期信号を前記複数の電気光学装置の制御回路に送信し、

前記複数の電気光学装置の制御回路は、前記初期化コマンドおよび前記初期化用同期信号の受信後の最初の垂直同期信号に同期したタイミングにおいて、前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を初期化することを特徴とする請求項3に記載の電子機器。

【請求項8】

前記複数の電気光学装置の制御回路に対して各種の制御情報を供給するホストCPUが前記同期化手段として機能するものであり、

前記ホストCPUは、予め前記複数の電気光学装置の制御回路の各々に対するチップセレクト信号をアクティブレベルとして、前記初期化を指示する初期化コマンドを前記複数の電気光学装置の制御回路に受信させ、その後、前記複数の電気光学装置の各制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で発生するタイミングであって、前記垂直走査期間の切り換わりを指示する垂直同期信号に同期したタイミングよりも所定時間だけ前に、前記複数の電気光学装置の制御回路の各々に対するチップセレクト信号をアクティブレベルから非アクティブレベルに一斉に変化させ、

前記複数の電気光学装置の制御回路は、前記初期化コマンドを受信し、前記チップセレクト信号のアクティブレベルから非アクティブレベルへの変化があった後の最初の垂直同期信号に同期したタイミングにおいて、前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御を初期化することを特徴とする請求項3に記載の電子機器。

【請求項9】

互いに交差する複数の走査線および複数の信号線を有するとともに、前記複数の走査線と前記複数の信号線との各交差に対応して各々配置された複数の画素回路を各々有する複数の画素部と、

前記複数の画素部の各画素部における前記複数の走査線を一垂直走査期間内に順次選択し、選択した走査線と前記複数の信号線との各交差に対応付けられた複数の画素回路を前記複数の信号線に接続する走査線駆動手段と、

前記複数の画素部に各々対応付けられた複数の信号線駆動回路であって、各画素部の前記複数の信号線を複数の配線ブロックに分け、配線ブロック毎に、一水平走査期間内に当該配線ブロックに属する各信号線を順次選択し、選択した信号線に階調電圧を印加する複数の信号線駆動回路と、

前記複数の信号線駆動回路の各々における前記複数の配線ブロックにおける配線ブロック内の複数の信号線への階調電圧の印加順序を各々周期的に更新する複数の制御回路と、

前記複数の制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を一斉に初期化する動作を時間を空けて繰り返し実行する同期化手段と

を具備することを特徴とする電気光学装置。

【請求項10】

前記同期化手段は、前記複数の制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の更新制御の周期の整数倍の長さの周期で、前記複数の制御回路における前記配線ブロック内の複数の信号線への階調電圧の印加順序の周期的な更新制御を一斉に初期化する動作を繰り返すことを特徴とする請求項9に記載の電気光学装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2012−181413(P2012−181413A)

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願番号】特願2011−44970(P2011−44970)

【出願日】平成23年3月2日(2011.3.2)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願日】平成23年3月2日(2011.3.2)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]