電気光学装置の駆動方法、制御装置、表示装置および電子機器

【課題】隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制すること。

【解決手段】本発明の電気光学装置の駆動方法は、画素毎に電気光学素子の光学状態を指定する画像データに基づいて、少なくとも一の画素に対応する画素電極に、絶対値が電気光学素子の光学状態を異ならせる素子駆動電圧以上の第1の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、走査線、信号線および素子駆動電源線に印加される電圧を制御する第1ステップと、一の画素に対応する画素電極に、絶対値が素子駆動電圧未満の第2の電圧が印加された状態になるように、走査線、信号線および素子駆動電源線に印加される電圧を制御する第2ステップとを備えることを特徴とする。

【解決手段】本発明の電気光学装置の駆動方法は、画素毎に電気光学素子の光学状態を指定する画像データに基づいて、少なくとも一の画素に対応する画素電極に、絶対値が電気光学素子の光学状態を異ならせる素子駆動電圧以上の第1の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、走査線、信号線および素子駆動電源線に印加される電圧を制御する第1ステップと、一の画素に対応する画素電極に、絶対値が素子駆動電圧未満の第2の電圧が印加された状態になるように、走査線、信号線および素子駆動電源線に印加される電圧を制御する第2ステップとを備えることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電気光学装置を駆動する技術に関する。

【背景技術】

【0002】

電気光学装置の多くにおいて、1つの画素において1つのトランジスターと1つの容量素子とを有する方式(以下、この方式を「1T1C方式」という)が用いられている。電気泳動素子などの記憶性の電気光学素子を用いる場合、1T1C方式では、1枚の絵を出力するために1つの画素において複数回の書き込みを行う場合があった。一方、1つの画素において2つのトランジスターと1つの容量素子とを有する方式(以下、この方式を「2T1C方式」という)を用いると、1フレームにおける1つの画素に対する書き込み時間を長くすることができるため、書き込み回数を減じることができる。2T1C方式については、例えば、特許文献1に開示されている。また、1つの画素において4つのトランジスターと2つの容量素子とを有する方式(以下、この方式を「4T2C方式」という)を用いて低消費電力化を図る技術も開示されている(例えば、特許文献2)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−176330号公報

【特許文献2】特開2010−102299号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

2T1C方式では画素に白または黒の書き込みをするときには、画素電極に書き込みに必要な電圧が印加される。一方で、この書き込み中において書き込み対象外の画素の画素電極には0Vの電圧を書き込むことができないため、その画素電極はハイインピーダンスの状態になる。そのため、書き込み対象外の画素であっても書き込み対象の画素から横電界の影響を受けて、白または黒がわずかに書き込まれてしまい表示が滲んでしまうことがあった。

【0005】

本発明は、上述した事情に鑑みてなされたものであり、その目的の一つは、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することにある。

【課題を解決するための手段】

【0006】

上述の課題を解決するため、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持するメモリー回路と、前記メモリー回路に保持されたデータ電圧に応じて、素子駆動電源線に接続された状態またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路とを有する電気光学装置の駆動方法であって、前記画素毎に前記電気光学素子の光学状態を指定する画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる素子駆動電圧以上の第1の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第1ステップと、前記一の画素に対応する前記画素電極に、絶対値が前記素子駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第2ステップとを備えることを特徴とする電気光学装置の駆動方法を提供する。

この電気光学装置の駆動方法によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0007】

また、別の好ましい態様において、前記第1ステップは、前記素子駆動電源線に前記第2の電圧が印加された状態で、前記メモリー回路に前記データ電圧を保持させるステップと、前記メモリー回路に前記データ電圧が保持された状態で、前記素子駆動電源線に前記第1の電圧を印加するステップと、前記メモリー回路に前記データ電圧が保持された状態で、前記素子駆動電源線に前記第2の電圧を印加するステップとを有することを特徴とする。

この電気光学装置の駆動方法によれば、表示を滲みにくくしつつ書き込み時間を短縮することができる。

【0008】

また、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持する2つのメモリー回路と、前記2つのメモリー回路に保持されたデータ電圧に応じて、第1の素子駆動電源線に接続された状態または第2の素子駆動電源線に接続された状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路とを有する電気光学装置の駆動方法であって、前記画素毎に前記電気光学素子の光学状態を指定する画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第1ステップと、前記一の画素に対応する前記画素電極に前記第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第2ステップとを備えることを特徴とする電気光学装置の駆動方法を提供する。

この電気光学装置の駆動方法によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0009】

また、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持する2つのメモリー回路と、前記2つのメモリー回路に保持されたデータ電圧に応じて、第1の素子駆動電源線に接続された状態、第2の素子駆動電源線に接続された状態、またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路とを有する電気光学装置の駆動方法であって、前記画素毎に前記電気光学素子の光学状態を指定する画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、当該画素電極に前記第1の電圧の極性が反転した電圧であって、絶対値が前記最低駆動電圧以上の第3の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第1ステップと、前記一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第2ステップとを備えることを特徴とする電気光学装置の駆動方法を提供する。

この電気光学装置の駆動方法によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0010】

また、別の好ましい態様において、前記第1ステップは、n回(nは1以上の整数)のフレームで、前記一の画素に対応する前記画素電極に電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御することを特徴とする。

この電気光学装置の駆動方法によれば、書き込み時間を短縮することができる。

【0011】

また、別の好ましい態様において、前記第1ステップにおいて前記一の画素に対応する前記画素電極に電圧が印加された状態になる回数nは、前記画像データまたは設定値に基づいて設定可能であることを特徴とする。

この電気光学装置の駆動方法によれば、書き込む画像に応じて、表示の滲みの抑制を優先するか書き込み時間の短縮を優先するかを選択することができる。

【0012】

また、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持するメモリー回路と、前記メモリー回路に保持されたデータ電圧に応じて、素子駆動電源線に接続された状態またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路と、前記走査線を予め決められた順に選択する走査線駆動回路とを有する電気光学装置の駆動方法であって、前記走査線駆動回路により一の走査線が選択され、前記画素毎に前記電気光学素子の光学状態を指定する画像データに基づいて、当該一の走査線に接続された前記画素に対応する画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記信号線および前記素子駆動電源線に印加される電圧を制御する第1ステップと、前記走査線駆動回路により前記一の走査線とは異なる他の走査線が選択され、当該他の走査線に接続された一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第2ステップとを備え、前記走査線駆動回路は、前記他の走査線が次に選択されるまでの時間が、前記一の走査線が次に選択されるまでの時間よりも短くなるように、前記走査線を選択することを特徴とする電気光学装置の駆動方法を提供する。

この電気光学装置の駆動方法によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0013】

また、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持するメモリー回路と、前記メモリー回路に保持されたデータ電圧に応じて、素子駆動電源線に接続された状態またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路とを有する電気光学装置に制御信号を出力する出力手段と、前記複数の画素に対応する前記電気光学素子の光学状態を指定する画像データを取得する取得手段と、前記取得した画像データに基づいて前記電気光学装置を制御する前記制御信号を出力するように、前記出力手段を制御する制御手段とを具備し、前記制御手段は、前記取得した画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御し、前記一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御することを特徴とする制御装置を提供する。

この制御装置によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0014】

また、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持する2つのメモリー回路と、前記2つのメモリー回路に保持されたデータ電圧に応じて、第1の素子駆動電源線に接続された状態または第2の素子駆動電源線に接続された状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路とを有する電気光学装置に制御信号を出力する出力手段と、前記複数の画素に対応する前記電気光学素子の光学状態を指定する画像データを取得する取得手段と、前記取得した画像データに基づいて前記電気光学装置を制御する前記制御信号を出力するように、前記出力手段を制御する制御手段とを具備し、前記制御手段は、前記取得した画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御し、前記一の画素に対応する前記画素電極に前記第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御することを特徴とする制御装置を提供する。

この制御装置によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0015】

また、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持する2つのメモリー回路と、前記2つのメモリー回路に保持されたデータ電圧に応じて、第1の素子駆動電源線に接続された状態、第2の素子駆動電源線に接続された状態、またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路とを有する電気光学装置に制御信号を出力する出力手段と、前記複数の画素に対応する前記電気光学素子の光学状態を指定する画像データを取得する取得手段と、前記取得した画像データに基づいて前記電気光学装置を制御する前記制御信号を出力するように、前記出力手段を制御する制御手段とを具備し、前記制御手段は、前記取得した画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、当該画素電極に前記第1の電圧の極性が反転した電圧であって、絶対値が前記最低駆動電圧以上の第3の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御し、前記一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御することを特徴とする制御装置を提供する。

この制御装置によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0016】

また、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持するメモリー回路と、前記メモリー回路に保持されたデータ電圧に応じて、素子駆動電源線に接続された状態またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路と、前記走査線を予め決められた順に選択する走査線駆動回路とを有する電気光学装置に制御信号を出力する出力手段と、前記複数の画素に対応する前記電気光学素子の光学状態を指定する画像データを取得する取得手段と、前記取得した画像データに基づいて前記電気光学装置を制御する前記制御信号を出力するように、前記出力手段を制御する制御手段とを具備し、前記制御手段は、前記走査線駆動回路により一の走査線が選択され、前記画素毎に前記電気光学素子の光学状態を指定する画像データに基づいて、当該一の走査線に接続された前記画素に対応する画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記信号線および前記素子駆動電源線に印加される電圧を制御し、前記走査線駆動回路により前記一の走査線とは異なる他の走査線が選択され、当該他の走査線に接続された一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御し、前記他の走査線が次に選択されるまでの時間が、前記一の走査線が次に選択されるまでの時間よりも短くなるように、前記走査線駆動回路を制御することを特徴とする制御装置を提供する。

この制御装置によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0017】

また、本発明は、上記記載の制御装置と、前記制御装置から出力される前記制御信号により制御される前記電気光学装置とを具備することを特徴とする表示装置を提供する。

この表示装置によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0018】

また、本発明は、上記記載の表示装置を具備することを特徴とする電子機器を提供する。

この電子機器によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【図面の簡単な説明】

【0019】

【図1】電子機器1000の外観を示す図である。

【図2】電子機器1000のハードウエア構成を示すブロック図である。

【図3】表示部1の断面構造を示す模式図である。

【図4】第1実施形態における表示部1の回路構成を示す図である。

【図5】第1実施形態における画素13の等価回路を示す図である。

【図6】コントローラー2の機能構成を示すブロック図である。

【図7】第1実施形態における表示部1の動作を説明する図である。

【図8】第1実施形態における駆動信号を示すタイミングチャートである。

【図9】第1実施形態における黒書込画素の画素13の等価回路の各部における電圧の変化を示す図である。

【図10】第1実施形態における白書込画素の画素13の等価回路の各部における電圧の変化を示す図である。

【図11】第1実施形態における維持画素の画素13の等価回路の各部における電圧の変化を示す図である。

【図12】第1実施形態における画素電極104に印加される電圧の変化の例を説明する図である。

【図13】第2実施形態における駆動信号を示すタイミングチャートである。

【図14】第2実施形態における表示部1の動作を説明する図である。

【図15】第3実施形態における表示部1の動作を説明する図である。

【図16】第4実施形態における駆動信号を示すタイミングチャートである。

【図17】第5実施形態における表示部1Aの回路構成を示す図である。

【図18】第5実施形態における画素13Aの等価回路を示す図である。

【図19】第5実施形態における黒書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。

【図20】第5実施形態における白書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。

【図21】第5実施形態における維持画素の画素13Aの等価回路の各部における電圧の変化を示す図である。

【図22】第5実施形態における画素電極104に印加される電圧の変化の例を説明する図である。

【図23】第6実施形態における黒書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。

【図24】第6実施形態における白書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。

【図25】第6実施形態における維持画素の画素13Aの等価回路の各部における電圧の変化を示す図である。

【図26】第6実施形態における画素電極104に印加される電圧の変化の例を説明する図である。

【図27】変形例1における表示部1の動作を説明する図である。

【発明を実施するための形態】

【0020】

<第1実施形態>

[全体構成]

図1は、第1実施形態における電子機器1000の外観を示す図である。電子機器1000は画像を表示する表示装置である。この例においては、電子機器1000は電子書籍を閲覧するための装置、いわゆる電子ブックリーダーである。電子書籍は複数ページの画像を含むデータである。電子機器1000は電子書籍をある単位(例えば1ページずつ)で表示部1に表示する。電子書籍に含まれる複数ページのうち、表示の対象となる一のページを「選択ページ」という。選択ページはユーザーによるボタン8A〜8Fの操作に応じて変更される。ユーザーはボタン8A〜8Fの操作により電子書籍のページをめくること(ページ送りまたはページ戻し)ができる。

【0021】

図2は、電子機器1000のハードウェア構成を示すブロック図である。電子機器1000は、表示部1、コントローラー2、CPU(Central Processing Unit)3、VRAM(Video Random Access Memory)4、RAM(Random Access Memory)5、ROM(Read Only Memory)6、記憶部7、および操作部8を有する。これらの各構成はバスBUSを介して接続されている。

表示部1は、画像を表示する電気光学素子を含むディスプレイパネルを有する電気光学装置である。この例では、電圧の印加等によりエネルギーを与えなくても表示を保持するメモリー性の電気光学素子である、電気泳動粒子を用いている。この電気光学素子により、表示部1はモノクロ複数階調(この例では白黒2階調)の像を表示する。コントローラー2は表示部1を制御する制御装置である。CPU3は電子機器1000の各部を制御する処理装置(プロセッサー)である。

【0022】

CPU3は、RAM5をワークエリアとして、ROM6または記憶部7に記憶されたプログラムを実行する。VRAM4は表示部1に表示させる画像を示す画像データを記憶するメモリーである。画像データは表示部1に表示させる画像を示すデータであるから、以下に示すように、複数の画素13に対応する電気泳動層110における光学状態を指定するものとなる。

RAM5はデータを記憶するメモリーである。記憶部7は電子書籍のデータ(書籍データ)を記憶する不揮発性のメモリーである。記憶部7は複数の電子書籍のデータを記憶することができる。操作部8はユーザーの指示を入力するための入力装置であり、例えばタッチスクリーン、キーパッド、またはボタンを含む。図1に示したボタン8A〜8Fは、操作部8を構成する一部である。また、操作部8には、表示部1の表面に設けられたタッチセンサーなどを有していてもよい。バスBUSは構成要素間でデータまたは信号を伝送する伝送路である。

【0023】

図3は、表示部1の断面構造を示す模式図である。表示部1は、第1基板100、電気泳動層110、および第2基板120を有する。第1基板100および第2基板120は、電気泳動層110を挟持するための基板である。

【0024】

第1基板100は、基板101、接着層102、および回路層103を有する。基板101は絶縁性および可撓性を有する材料、例えばポリカーボネートで形成されている。なお基板101は軽量性、可撓性、弾性および絶縁性を有するものであれば、ポリカーボネート以外の樹脂材料により形成されてもよい。また、基板101は可撓性を有しないガラスにより形成されていてもよい。

接着層102は基板101と回路層103とを接着する層である。回路層103は電気泳動層110を駆動するための回路(後述する画素回路など)を有する層である。回路層103は画素電極104を有する。

【0025】

電気泳動層110はマイクロカプセル111およびバインダー112を有する。マイクロカプセル111はバインダー112によって固定されている。バインダー112としては、マイクロカプセル111との親和性が良好で電極との密着性が優れ、かつ高抵抗な材料が用いられる。マイクロカプセル111は内部に分散媒および電気泳動粒子が格納されたカプセルである。マイクロカプセル111は柔軟性を有する材料、例えばアラビアゴム・ゼラチン系の化合物またはウレタン系の化合物等が用いられる。なお、マイクロカプセル111と画素電極104との間には接着剤により形成された接着層が設けられてもよい。

【0026】

分散媒は、水、アルコール系溶媒(メタノール、エタノール、イソプロパノール、ブタノール、オクタノール、メチルセルソルブなど)、エステル類(酢酸エチル、酢酸ブチルなど)、ケトン類(アセトン、メチルエチルケトン、メチルイソブチルケトンなど)、脂肪族炭化水素(ぺンタン、ヘキサン、オクタンなど)、脂環式炭化水素(シクロへキサン、メチルシクロへキサンなど)、芳香族炭化水素(ベンゼン、トルエン、長鎖アルキル基を有するベンゼン類(キシレン、ヘキシルベンゼン、ヘブチルベンゼン、オクチルベンゼン、ノニルベンゼン、デシルベンゼン、ウンデシルベンゼン、ドデシルベンゼン、トリデシルベンゼン、テトラデシルベンゼンなど))、ハロゲン化炭化水素(塩化メチレン、クロロホルム、四塩化炭素、1,2−ジクロロエタンなど)、またはカルボン酸塩である。別の例で、分散媒はその他の油類であってもよい。また、分散媒はこれらの物質が混合されたものでもよい。さらに別の例で、分散媒には界面活性剤などが配合されてもよい。

【0027】

電気泳動粒子は分散媒中で電界によって移動する性質を有する粒子(高分子またはコロイド)である。この例においては白の電気泳動粒子と黒の電気泳動粒子がマイクロカプセル111内に格納されている。黒の電気泳動粒子は、例えば、アニリンブラックやカーボンブラック等の黒色顔料を含む粒子であり、この例においては正に帯電されている。白の電気泳動粒子は、例えば、二酸化チタンや酸化アルミニウム等の白色顔料を含む粒子であり、この例においては負に帯電されている。

【0028】

第2基板120はフィルム121および共通電極122を有する。フィルム121は電気泳動層110の封止および保護をするものである。フィルム121は透明で絶縁性を有する材料、例えばポリエチレンテレフタレートにより形成される。共通電極122は透明で導電性を有する材料、例えば酸化インジウムスズ(Indium Tin Oxide、ITO)により形成される。

マイクロカプセル111内の電気泳動粒子は画素電極104と共通電極122とに印加される電圧に応じてマイクロカプセル111内を移動することにより、電気泳動層110としての光学状態を異ならせる。電子機器1000のユーザーは電気泳動層110を第2基板120側から視認する。

【0029】

[表示部1の回路構成]

図4は、第1実施形態における表示部1の回路構成を示す図である。表示部1は、m本の走査線11、n本のデータ線12、m×n個の画素13、走査線駆動回路15、データ線駆動回路16、電源線駆動回路17、および電源線18を有する。表示領域14はm×n個の画素13を含む。以下、第j行第i列の画素を特に、画素13(i,j)という。画素13内の各要素についても同様である。

【0030】

走査線駆動回路15、データ線駆動回路16、および電源線駆動回路17は、コントローラー2により制御される。走査線11は行方向(X方向)に沿って配置され、走査線駆動回路15から出力される走査信号を伝達する。走査信号はm本の走査線11の中から一の走査線11を順次排他的に選択する信号である。データ線12(信号線)は列方向(Y方向)に沿って配置され、データ線駆動回路16から出力されるデータ信号を伝達する。データ信号は各画素13の階調に応じた信号である。

電源線18(素子駆動電源線)は行方向(X方向)に沿ってm本配置され、画素電極104に印加される素子駆動電圧を供給するための素子電源信号を伝達する配線である。電源線駆動回路17は、電源線18を介して画素13に素子駆動電圧を供給する。この例では、電源線駆動回路17はm本の電源線18にそれぞれ独立したタイミングで素子駆動電圧を供給する。

【0031】

画素13は走査線11およびデータ線12の交差に対応して設けられ、データ信号に応じた階調を示す。なお、複数の走査線11のうち第j行の走査線11を特に、第j行の走査線11という。データ線12についても同様である。

以下、データ信号、走査信号および素子電源信号など、画素13に伝達される各信号を駆動信号という。

【0032】

[画素13の回路構成]

図5は、第1実施形態における画素13(i,j)の等価回路(画素回路)を示す図である。この例においては、画素13は2T1C方式の回路構成になっている。画素13は、画素トランジスター131と、駆動トランジスター132と、容量素子133と、画素電極104とを有する。画素トランジスター131および駆動トランジスター132はスイッチング素子であり、この例ではアモルファスSiを用いたnチャネル型のTFT(Thin Film Transistor)である。

【0033】

画素トランジスター131のゲート端子は第j行の走査線11に接続されている。画素トランジスターのゲート電圧GATEは画素トランジスター131のゲート端子に印加される電圧である。画素トランジスター131のソース・ドレイン端子の一方は第i列のデータ線12に接続されている。データ電圧DATAは画素トランジスター131のデータ線12に接続されるソース・ドレイン端子に印加される電圧である。画素トランジスター131のソース・ドレイン端子の他方は駆動トランジスター132のゲート端子および容量素子133の一方の電極に接続されている。駆動トランジスターのゲート電圧GTは駆動トランジスター132のゲート端子に印加される電圧である。容量素子133の他方の電極は図示せぬ容量線に接続され、電圧VSTG(この例では接地電圧(基準電圧))に固定されている。以下の説明において、各電圧は基準電圧(0V)に対する値を示している。

なお、容量素子133は画素トランジスター131のソース・ドレイン端子と駆動トランジスター132のゲート端子とが接続された部分における寄生容量を含むものであり、必ずしも素子として存在していなくてもよい。

【0034】

駆動トランジスター132のソース・ドレイン端子の一方は電源線18に接続されている。電源線への供給電圧VEPは駆動トランジスター132の電源線18に接続されるソース・ドレイン端子に印加される電圧(素子駆動電圧)である。駆動トランジスター132のソース・ドレイン端子の他方は画素電極104に接続されている。画素電極の電圧PXは画素電極104に印加される電圧である。電気泳動層110は画素電極104および共通電極122に挟まれている。共通電極122は共通電圧COM(この例では接地電圧(基準電圧))に固定されている。

【0035】

ここで、画素トランジスター131および容量素子133は、メモリー回路134を構成している。メモリー回路134は、対応する走査線11が選択されているときにデータ線12に印加されたデータ電圧を保持する。駆動トランジスター132は、メモリー回路134に保持されたデータ電圧に応じて、画素電極104と電源線18との接続状態を切り替えるスイッチング回路を構成している。この例では、スイッチング回路はメモリー回路134に保持された電圧に応じて、画素電極104と電源線18とを電気的に接続した状態(駆動トランジスター132がオン状態)、または画素電極104がハイインピーダンスの状態(駆動トランジスター132がオフ状態)のいずれかに画素電極104の状態を切り替える。

【0036】

[コントローラー2の機能構成]

図6は、コントローラー2の機能構成を示すブロック図である。コントローラー2は、出力部21、取得部22、および制御部23を有する。出力部21は、表示部1に対して、走査線駆動回路15、データ線駆動回路16、および電源線駆動回路17を制御する制御信号を出力する。また、取得部22は、VRAM4に記憶されている画像データを取得し、制御部23に出力する。制御部23は、取得した画像データに基づいて各画素13に対応する電気泳動層110の光学状態を制御する制御信号を出力するように、出力部21を制御する。

【0037】

[動作]

CPU3は、OS(Operating System)またはアプリケーションプログラムに従って、コントローラー2の動作とは独立したタイミングでVRAM4のデータを書き替える。CPU3がVRAM4に記憶されている画像データを書き替えると、CPU3はVRAM4の書き替えを行った旨を示す書き替え通知をコントローラー2に出力する。コントローラー2は書き換え通知を受け取ると、VRAM4に記憶された画像データに基づいて、制御信号を表示部1に対して出力する。走査線駆動回路15、データ線駆動回路16、および電源線駆動回路17からこの制御信号に基づいて出力される駆動信号について説明する。

【0038】

図7は、第1実施形態における表示部1の動作を説明する図である。横軸は時刻の進行を示し、縦軸は走査線11のY方向の位置(Yj:jは1〜mの何れかの整数)を示している。「Scanning Line」とは、各フレームにおいて各走査線11が選択されたタイミングを示す線である。各走査線11が選択されるタイミングが異なるため、各画素13への書き込みが行われる期間は、接続される走査線11によって異なっている。各画素13への書き込みが行われる期間は、階調を白から黒へ変化させていくフレーム(以下、「Bフレーム」(黒フレーム、図では「BF」と記す))、階調を黒から白へ変化させていくフレーム(以下、「Wフレーム」(白フレーム、図では「WF」と記す))、および電気泳動層110の光学状態を異ならせない電圧(以下、Nt電圧といい、この例では基準電圧と同じ0V)を画素電極104に印加するフレーム(以下、「Nフレーム」(ニュートラルフレーム、図では「NF」と記す))に区別されている。この例では、Bフレーム、Nフレーム、Wフレーム、Nフレームが順に繰り返される。これらの各フレームを区別して説明する必要がない場合には、単に「フレーム」という。

【0039】

図8は、第1実施形態における駆動信号を示すタイミングチャートである。走査線駆動回路15は、図8のGATE(Yj:jは1〜mの何れかの整数)に示すように、複数の走査線11の中から一の走査線11を順次排他的に選択する走査信号を走査線11に供給する。選択された走査線11(電圧Gon)に接続された画素トランジスター131はオン状態となり、それ以外の走査線11(電圧Goff)に接続された画素トランジスター131はオフ状態となる。

【0040】

データ線駆動回路16は、夫々選択された走査線11に接続されている各画素13に対応して、表示させる階調に応じたデータ電圧のデータ信号をデータ線12に供給する。データ信号は、Bフレームにおいては、階調を白から黒へ変化させていく画素13(以下、「黒書込画素」という)に対してはデータ電圧をVdhとし、階調を黒から白へ変化させていく画素13(以下、「白書込画素」という)および階調を変化させない画素(以下、「維持画素」という)に対してはデータ電圧をVdlとする。Wフレームにおいては、データ信号は、白書込画素に対してはデータ電圧をVdh、黒書込画素および維持画素に対してはデータ電圧をVdlとする。また、Nフレームにおいては、黒書込画素、白書込画素および維持画素の総てに対してデータ電圧をVdhとする。

【0041】

電源線駆動回路17は、図8のVEP(Zj:jは1〜mの何れかの整数)に示すように、各フレームの選択期間Ts(図9参照)において、各行の電源線への供給電圧VEPがNt電圧となる素子電源信号を電源線18に出力する。選択期間Tsは各行に対応する走査線11が選択される期間であり、行毎に期間の開始タイミングが異なっている。

また、電源線駆動回路17は、各フレームの選択期間Ts以外の期間となる書込時間Tw(図9参照)において、電源線への供給電圧VEPがBフレームにおいては+Vepとなり、Wフレームにおいては−Vepとなり、NフレームにおいてはNt電圧となる素子電源信号を電源線18に供給する。Vepは、画素電極104に印加されると電気泳動層110の光学状態を異ならせることができる最低駆動電圧以上の電圧値である。書込期間Twも選択期間Tsと同様に、行毎に期間の開始タイミングが異なっている。

【0042】

続いて、一の走査線11に接続された画素13に注目して、黒書込画素、白書込画素および維持画素について、画素13の等価回路の各部における電圧の変化を順に説明する。

【0043】

[黒書込画素での電圧変化]

図9は、第1実施形態における黒書込画素の画素13の等価回路の各部における電圧の変化を示す図である。黒書込画素では、まずBフレームの選択期間Tsにおいて、画素トランジスターのゲート電圧GATEが電圧Gonとなることで、メモリー回路134にデータ電圧DATAが保持され、駆動トランジスターのゲート電圧GTはVdhとなる。Bフレームの書込期間Twにおいて、電源線への供給電圧VEPは+Vepとなり、画素電極の電圧PXもこれに追従して+Vepに変化する。画素電極の電圧PXが+Vepとなっているときに、画素13の階調が白から黒に変化していく。その後、電源線への供給電圧VEPはNt電圧となり、画素電極の電圧PXもこれに追従してNt電圧に変化する。

【0044】

続いてNフレームの選択期間Tsにおいて、画素トランジスターのゲート電圧GATEが電圧Gonとなることで、メモリー回路134にデータ電圧DATAが保持され、駆動トランジスターのゲート電圧GTはVdhとなる。Nフレームの書込期間Twにおいて、電源線への供給電圧VEPはNt電圧を維持し、画素電極の電圧PXもNt電圧を維持する。この状態では画素13の階調は変化しない。なお、この画素13と同じ走査線11に接続された他の総ての画素13についても、画素電極の電圧PXはNt電圧となる。

【0045】

続いてWフレームの選択期間Tsにおいて、画素トランジスターのゲート電圧GATEが電圧Gonとなることで、メモリー回路134にデータ電圧DATAが保持され、駆動トランジスターのゲート電圧GTはVdlとなる。Wフレームの書込期間Twにおいて、電源線への供給電圧VEPは−Vepとなる。一方で、駆動トランジスター132はオフ状態であるから、画素電極104がハイインピーダンスの状態となる。そのため、画素電極の電圧PXは、周囲の画素13における画素電極の電圧PXによる横電界の影響を受け電圧値が安定しない状態(Floating)となる。

【0046】

続くNフレームでは、上記のNフレームと同様に画素電極の電圧PXがNt電圧となり、画素電極の電圧PXの電圧値が安定した状態に戻る。

従来のようにNフレームが存在しない場合には、画素電極104がハイインピーダンスの状態となる期間、すなわち画素電極の電圧PXが不安定な状態が長い期間にわたって続くことになる。その場合、周囲の画素13からの横電界の影響により電気泳動層110の光学状態が変化してしまうため、ユーザーには表示の滲みが生じてきたように見えてしまう。一方、本発明のように画素電極の電圧PXの電圧値が不安定な状態となる期間が長く続かないようにすることで、表示の滲みを抑制することができる。以上が黒書込画素の電圧変化の説明である。

【0047】

[白書込画素での電圧変化]

図10は、第1実施形態における白書込画素の画素13の等価回路の各部における電圧の変化を示す図である。白書込画素では、まずBフレームにおいて駆動トランジスターのゲート電圧GTがVdlとなり、駆動トランジスター132がオフ状態となる。画素電極104がハイインピーダンスの状態となり、画素電極の電圧PXの電圧値が安定しない状態となる。続いてNフレームでは画素電極の電圧PXがNt電圧となり安定した状態に戻る。

続くWフレームでは駆動トランジスターのゲート電圧GTがVdhとなり、駆動トランジスター132がオン状態となる。Wフレームの書込期間Twにおいて、電源線への供給電圧VEPは−Vepとなり、画素電極の電圧PXもこれに追従して−Vepに変化する。画素電極の電圧PXが−Vepとなっているときに、画素13の階調が黒から白に変化していく。その後、電源線への供給電圧VEPはNt電圧となり、画素電極の電圧PXもこれに追従してNt電圧に変化する。続くNフレームでは画素電極の電圧PXはNt電圧となる。以上が白書込画素の電圧変化の説明である。

【0048】

[維持画素での電圧変化]

図11は、第1実施形態における維持画素の画素13の等価回路の各部における電圧の変化を示す図である。維持画素では、まずBフレームにおいて駆動トランジスターのゲート電圧GTがVdlとなり、駆動トランジスター132がオフ状態となる。画素電極104がハイインピーダンスの状態となり、画素電極の電圧PXの電圧値が安定しない状態となる。続いてNフレームでは画素電極の電圧PXがNt電圧となり安定した状態に戻る。

続くWフレームではBフレームと同様に駆動トランジスターのゲート電圧GTがVdlとなり、駆動トランジスター132がオフ状態となる。画素電極104がハイインピーダンスの状態となり、画素電極の電圧PXの電圧値が安定しない状態となる。続いてNフレームでは画素電極の電圧PXがNt電圧となり安定した状態に戻る。以上が維持画素の電圧変化の説明である。

【0049】

[画素電極の電圧PXの変化例]

続いて、黒が書き込まれている画素13を維持画素、白書込画素とする場合、および白が書き込まれている画素13を維持画素、黒書込画素とする場合の4画素について、各画素電極の電圧PXの変化の例を説明する。

【0050】

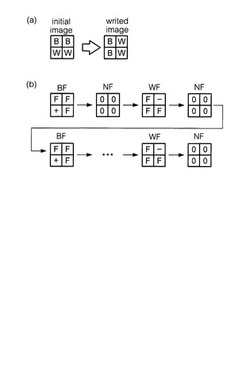

図12は、第1実施形態における画素電極104に印加される電圧の変化の例を説明する図である。図12(a)は、上記4画素に既に黒または白が書き込まれている初期状態(initial image)と、白または黒が書き込まれた書込み後の状態(writed image)とを示している。この図において「B」は黒、「W」は白を表す。図12(a)に示す例では、左上の画素および右下の画素は維持画素、右上の画素は白書込画素、左下の画素は黒書込画素となる。

図12(b)は、各フレームにおいて各画素に対応する画素電極の電圧PXがどのようになっているかを示している。図12(b)に示す例では、「F」はハイインピーダンスの状態により電圧値が不安定となっている状態、「+」は+Vepが印加されている状態、「−」は−Vepが印加されている状態、「0」はNt電圧(0V)が印加されている状態である。

【0051】

Bフレーム(BF)では、左下の画素が「+」となり、その他の画素が「F」となる。「+」の画素はBフレームの期間に黒が書き込まれる。一方、「F」の画素は「+」の画素の横電界の影響を受け、画素電極の電圧PXが+側に変化する。この期間が長く続くと電気泳動層110の光学状態が変化し始めることになるが、続くNフレーム(NF)で総ての画素が「0」となるため、Bフレームにおいて+側に電圧が変化した画素についてもNt電圧に安定することになる。そのため、Nフレームでは、電気泳動層110の光学状態がBフレーム終了時の状態で維持される。

【0052】

Wフレーム(WF)では、右上の画素が「−」となり、その他の画素が「F」となる。「−」の画素はWフレームの期間に白が書き込まれる。一方、「F」の画素は「−」の画素の横電界の影響を受け、画素電極の電圧PXが−側に変化する。この期間が長く続くと電気泳動層110の光学状態が変化し始めることになるが、続くNフレーム(NF)で総ての画素が「0」となるため、Wフレームにおいて−側に電圧が変化した画素についてもNt電圧に安定することになる。そのため、Nフレームでは、電気泳動層110の光学状態がWフレーム終了時の状態で維持される。

その後は、Bフレーム、Nフレーム、Wフレーム、Nフレームの順で予め決められた回数が繰り返されて、白書込画素に対応する画素13には白が書き込まれ、黒書込画素に対応する画素13には黒が書き込まれることになる。また、BフレームまたはWフレームにおいて「F」となった画素は、画素電極の電圧PXが不安定な状態となるが、NフレームにおいてNt電圧に安定した状態となるため、電気泳動層110の光学状態が変化しない、または変化したとしてもわずかな変化に抑えられる。したがって、Nフレームが存在しない場合に比べて、この電気泳動層110の光学状態の変化による表示の滲みが抑制される。

【0053】

<第2実施形態>

第1実施形態では電源線駆動回路17はm本の電源線18にそれぞれ独立したタイミングで素子駆動電圧を供給していたが、第2実施形態では総ての電源線18に共通の素子駆動電圧を供給する場合について説明する。

【0054】

図13は、第2実施形態における駆動信号を示すタイミングチャートである。この例においても第1実施形態の場合と同様にBフレーム、WフレームおよびNフレームが存在し、それぞれ選択期間Tsおよび書込期間Twが存在する。

走査線駆動回路15は、図13のGATE(Yj:jは1〜mの何れかの整数)に示すように、BフレームおよびWフレームの選択期間Tsにおいて、複数の走査線11の中から一の走査線11を順次排他的に選択する走査信号を走査線11に供給する。選択された走査線11に接続された画素トランジスター131はオン状態となり、それ以外の走査線11に接続された画素トランジスター131はオフ状態となる。一方、走査線駆動回路15は、Nフレームの選択期間Tsでは総ての走査線11をまとめて選択する走査信号を走査線11に供給する。そのため、Nフレームでは総ての画素トランジスター131がオン状態となる。Nフレームでは総ての走査線11がまとめて選択されるため、Nフレームの選択期間Tsは、BフレームおよびWフレームの選択期間Tsよりも短くなっている。

【0055】

データ線駆動回路16は、図13のDATAに示すように、各フレームの選択時間Tsにおいて、夫々選択された走査線11に接続されている各画素13に対応して、表示させる階調に応じたデータ電圧のデータ信号をデータ線12に供給する。Bフレームにおいてデータ信号は、黒書込画素に対してはデータ電圧をVdhとし、白書込画素および維持画素に対してはデータ電圧をVdlとする。Wフレームにおいてデータ信号は、白書込画素に対してはデータ電圧をVdh、黒書込画素および維持画素に対してはデータ電圧をVdlとする。Nフレームにおいてデータ信号は、総ての画素(黒書込画素、白書込画素および維持画素)に対してデータ電圧Vdhとする。

【0056】

電源線駆動回路17は、図13のVEPに示すように、各フレームの書込時間Twにおいて電源線への供給電圧VEPが、Bフレームでは+Vep、Wフレームでは−Vep、NフレームではNt電圧となる素子電源信号を電源線18に供給する。一方、選択期間Tsにおいて電源線駆動回路17は、電源線への供給電圧VEPがNt電圧となる素子電源信号を電源線18に供給する。

【0057】

図14は、第2実施形態における表示部1の動作を説明する図である。図7と同様に、横軸は時刻の進行を示し、縦軸は走査線11のY方向の位置(Yj:jは1〜mの何れかの整数)を示している。図14に示すようにNフレームは、BフレームおよびWフレームよりも選択期間Tsおよび書込期間Twが短くなっている。BフレームおよびWフレームの選択期間Tsでは、画素電極の電圧PXが、それぞれのフレームの直前のNフレームでの状態(Nt電圧)に維持されている。したがって、BフレームおよびWフレームの選択期間Tsは、実質的にはNフレームの状態と同様に画素電極の電圧PXがNt電圧に安定した状態であるため、図においては「(BF)」および「(WF)」として記載している。

このように総ての電源線18に共通の素子駆動電圧を供給する構成にしても、第1実施形態と同様に、Nフレームが存在しない場合に比べて、この電気泳動層110の光学状態の変化による表示の滲みを抑制することができる。

【0058】

<第3実施形態>

第1実施形態では走査線駆動回路15は、走査線11の並び順にしたがって順次排他的に選択する走査信号を走査線11に供給していたが、アドレス・デコーダ方式により飛び越し走査をするようにしてもよい。

【0059】

図15は、第3実施形態における表示部1の動作を説明する図である。図7と同様に、横軸は時刻の進行を示し、縦軸は走査線11のY方向の位置(Yj:jは1〜mの何れかの整数)を示している。飛び越し走査における走査線駆動回路15、データ線駆動回路16および電源線駆動回路17の動作例を説明する。

【0060】

(1)走査線駆動回路15が第Sb行の走査線11を選択するように走査信号を出力する。データ線駆動回路16および電源線駆動回路17がBフレームで画素13(i,Sb)に書き込むようにデータ信号および素子電源信号を出力する。具体的には、データ線駆動回路16は、第Sb行の走査線11が選択されているときに、画素13(i,Sb)のうち黒書込画素に対してはデータ電圧をVdhとし、白書込画素および維持画素に対してはデータ電圧をVdlとする。電源線駆動回路17は、電源線への供給電圧VEPが+Vepとなる素子電源信号を第Sb行の電源線18に出力する。

(2)走査線駆動回路15が第Sn1(=Sb+a)行の走査線11を選択するように走査信号を出力する。データ線駆動回路16および電源線駆動回路17がNフレームで画素13(i,Sn1)に書き込むようにデータ信号および素子電源信号を出力する。具体的には、データ線駆動回路16は、第Sn1行の走査線11が選択されているときに、画素13(i,Sn1)の総て(黒書込画素、白書込画素および維持画素)に対してデータ電圧をVdhとする。電源線駆動回路17は、電源線への供給電圧VEPがNt電圧となる素子電源信号を第Sn1行の電源線18に出力する。

(3)走査線駆動回路15が第Sw(=Sn1+b)行の走査線11を選択するように走査信号を出力する。データ線駆動回路16および電源線駆動回路17がWフレームで画素13(i,Sw)に書き込むようにデータ信号および素子電源信号を出力する。具体的には、データ線駆動回路16は、第Sw行の走査線11が選択されているときに、画素13(i,Sw)のうち白書込画素に対してはデータ電圧をVdhとし、黒書込画素および維持画素に対してはデータ電圧をVdlとする。電源線駆動回路17は、電源線への供給電圧VEPが−Vepとなる素子電源信号を第Sw行の電源線18に出力する。

(4)走査線駆動回路15が第Sn2(=Sw+a)行の走査線11を選択するように走査信号を出力する。データ線駆動回路16および電源線駆動回路17がNフレームで画素13(i,Sn2)に書き込むようにデータ信号および素子電源信号を出力する。具体的には、データ線駆動回路16は、第Sn2行の走査線11が選択されているときに、画素13(i,Sn2)の総て(黒書込画素、白書込画素および維持画素)に対してデータ電圧をVdhとする。電源線駆動回路17は、電源線への供給電圧VEPがNt電圧となる素子電源信号を第Sn2行の電源線18に出力する。

上記(1)から(4)の動作を繰り返し、動作を繰り返す度に、走査線駆動回路15は選択する走査線11を1行ずつずらしていく。また、Sb、Sw、Sn1、Sn2は、第m行を超えた場合には第1行に戻る。なお、Sb=Sn+cであるものとする。

【0061】

上述のように動作することで、一度選択された走査線11が次に選択されるまでの時間がa、b、cにより規定されるため、aはNフレームの時間、bはWフレームの時間、cはBフレームの時間に対応することになる。したがって、a、b、cを適宜設定することにより、各フレームの時間を設定することができる。例えば、bおよびcよりもaを小さくすれば、NフレームをWフレームおよびBフレームより短くすることができる。

このように飛び越し走査によってもNフレームを導入することができ、第1実施形態と同様に、Nフレームが存在しない場合に比べて、この電気泳動層110の光学状態の変化による表示の滲みを抑制することができる。また、飛び越し走査を用いることにより、各フレームの長さを適宜設定することができるため、短い時間のNフレームを挿入することもできる。

【0062】

<第4実施形態>

第1実施形態では電源線駆動回路17はm本の電源線18にそれぞれ独立したタイミングで素子駆動電圧を供給し、第2実施形態では総ての電源線18に共通の素子駆動電圧を供給していた。第4実施形態では電源線駆動回路17は、共通の素子駆動電圧が供給される複数本の電源線18を単位として、その単位毎に独立したタイミングで素子駆動電圧を供給する場合について説明する。

【0063】

図16は、第4実施形態における駆動信号を示すタイミングチャートである。この図に示す例では、共通の素子駆動電圧が供給される電源線18の単位は3本である。また、この図においては、2単位分(Y1〜Y3およびY4〜Y6の走査線11)に対応する部分のタイミングチャートとして示している。VEP1はY1〜Y3に対応する電源線への供給電圧、VEP2はY4〜Y6に対応する電源線への供給電圧を示している。タイミングチャートの上下に記載したフレーム(BF、WF、NF)、選択期間Tsおよび書込期間Twについては、Y1〜Y3に対応したものである。

図に示すように、Y1〜Y3でのNフレーム、Bフレーム(またはWフレーム)の選択期間Tsが終了した後、Y4〜Y6でのNフレーム、Bフレーム(またはWフレーム)の選択期間Tsが開始される。したがって、Y1〜Y3とY4〜Y6とはNフレーム+Bフレーム(またはWフレーム)の選択期間Tsだけ、各フレームのタイミングがずれている。

【0064】

このように電源線駆動回路17が複数本の電源線18を単位として素子駆動電圧を供給してもNフレームを導入することができ、第1実施形態と同様に、Nフレームが存在しない場合に比べて、この電気泳動層110の光学状態の変化による表示の滲みを抑制することができる。また、全フレームに占めるNフレームの割合を、第1実施形態と第2実施形態との中間にすることができる。また、電源線駆動回路17が素子駆動電圧を個別に制御する電源線18の数を、第1実施形態よりも少なくすることができる。

【0065】

<第5実施形態>

第1実施形態では「2T1C方式」を用いていたが、第5実施形態では「4T2C方式」を用いた場合について説明する。

【0066】

[表示部1Aの回路構成]

図17は、第5実施形態における表示部1Aの回路構成を示す図である。第1実施形態ではm×n個の画素13に対応してn本のデータ線12が設けられていたが、第5実施形態ではm×n個の画素13Aに対応してn本のデータ線12Aおよびn本のデータ線12Bが設けられている。また、第1実施形態ではm本の電源線18が設けられていたが、第5実施形態ではm本の電源線18Aおよびm本の電源線18Bが設けられている。このように、第5実施形態では各画素13Aに対して2本のデータ線(12A、12B)および2本の電源線(18A、18B)が設けられている。

【0067】

この例では、電源線18Aに出力される素子電源信号は第1実施形態と同様に+Vep、−Vep、Nt電圧のいずれかの電圧となる一方、電源線18Bに出力される素子電源信号はNt電圧となっている。

【0068】

[画素13Aの回路構成]

図18は、第5実施形態における画素13Aの等価回路を示す図である。この例では画素13Aは4T2C方式の回路構成になっている。そのため第1実施形態では各画素13にはメモリー回路134が1つ設けられていたが、第5実施形態では各画素13Aにはメモリー回路134Aおよびメモリー回路134Bの2つが設けられている。

【0069】

メモリー回路134Aは、対応する走査線11が選択されているときにデータ線12Aに印加されたデータ電圧を保持する。駆動トランジスター132Aは、メモリー回路134Aに保持されたデータ電圧に応じて、画素電極104と電源線18Aとの接続状態を切り替えるスイッチング回路を構成している。メモリー回路134Bは、対応する走査線11が選択されているときにデータ線12Bに印加されたデータ電圧を保持する。駆動トランジスター132Bは、メモリー回路134Bに保持されたデータ電圧に応じて、画素電極104と電源線18Bとの接続状態を切り替えるスイッチング回路を構成している。

この例では、駆動トランジスター132A、132Bのいずれか一方がオン状態、他方がオフ状態となる。したがって、画素電極104は、電源線18Aまたは電源線18Bのいずれかに接続された状態となる。

【0070】

以下の説明では、データ電圧DATA(A)は画素トランジスター131Aのデータ線12Aに接続されるソース・ドレイン端子に印加される電圧である。データ電圧DATA(B)は画素トランジスター131Bのデータ線12Bに接続されるソース・ドレイン端子に印加される電圧である。駆動トランジスターのゲート電圧GT(A)は駆動トランジスター132Aのゲート端子に印加される電圧である。駆動トランジスターのゲート電圧GT(B)は駆動トランジスター132Bのゲート端子に印加される電圧である。電源線への供給電圧VEP(A)は駆動トランジスター132Aの電源線18Aに接続されるソース・ドレイン端子に印加される電圧である。電源線への供給電圧VEP(B)は駆動トランジスター132Bの電源線18Bに接続されるソース・ドレイン端子に印加される電圧である。

【0071】

続いて、一の走査線11に接続された画素13Aに注目して、黒書込画素、白書込画素および維持画素について、画素13Aの等価回路の各部における電圧の変化を順に説明する。

【0072】

[黒書込画素での電圧変化]

図19は、第5実施形態における黒書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。黒書込画素では、まずBフレームにおいて駆動トランジスターのゲート電圧GT(A)がVdhとなり、駆動トランジスター132Aがオン状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdlとなり、駆動トランジスター132Bがオフ状態となる。Bフレームの書込期間Twにおいて、電源線への供給電圧VEP(A)は+Vepとなり、画素電極の電圧PXもこれに追従して+Vepに変化する。画素電極の電圧PXが+Vepとなっているときに、画素13Aの階調が白から黒に変化していく。その後、電源線への供給電圧VEP(A)はNt電圧となり、画素電極の電圧PXもこれに追従してNt電圧に変化する。

【0073】

続いてWフレームにおいて駆動トランジスターのゲート電圧GT(A)がVdlとなり、駆動トランジスター132Aがオフ状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdhとなり、駆動トランジスター132Bがオン状態となる。Wフレームの書込期間Twにおいて、電源線への供給電圧VEP(A)は−Vepとなる。一方で、駆動トランジスター132Aはオフ状態、駆動トランジスター132Bはオン状態であるから、画素電極104は電源線18Bに接続される。したがって、画素電極の電圧PXは電源線への供給電圧VEP(B)、すなわちNt電圧に維持される。そして続くNフレームでも、画素電極の電圧PXはWフレームと同様にNt電圧に維持される。

なお、Nフレームでは電源線への供給電圧VEP(A)をNt電圧にすることで、駆動トランジスター132Aがオン状態、駆動トランジスター132Bがオフ状態となるようにしてもよいし、双方がオン状態となるようにしてもよい。以上が黒書込画素の電圧変化の説明である。

【0074】

[白書込画素での電圧変化]

図20は、第5実施形態における白書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。白書込画素ではBフレームにおいて駆動トランジスターのゲート電圧GT(A)がVdlとなり、駆動トランジスター132Aがオフ状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdhとなり、駆動トランジスター132Bがオン状態となる。Bフレームの書込期間Twにおいて、電源線への供給電圧VEP(A)は+Vepとなる。一方で、駆動トランジスター132Aはオフ状態、駆動トランジスター132Bはオン状態であるから、画素電極104は電源線18Bに接続される。したがって、画素電極の電圧PXは電源線への供給電圧VEP(B)、すなわちNt電圧に維持される。

【0075】

続いてWフレームにおいて駆動トランジスターのゲート電圧GT(A)がVdhとなり、駆動トランジスター132Aがオン状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdlとなり、駆動トランジスター132Bがオフ状態となる。Wフレームの書込期間Twにおいて、電源線への供給電圧VEP(A)は−Vepとなり、画素電極の電圧PXもこれに追従して−Vepに変化する。画素電極の電圧PXが−Vepとなっているときに、画素13Aの階調が黒から白に変化していく。その後、電源線への供給電圧VEP(A)はNt電圧となり、画素電極の電圧PXもこれに追従してNt電圧に変化する。

続くNフレームでは、画素電極の電圧PXはBフレームと同様にNt電圧に維持される。なお、Nフレームでは電源線への供給電圧VEP(A)をNt電圧にすることで、駆動トランジスター132Aがオン状態、駆動トランジスター132Bがオフ状態となるようにしてもよいし、双方がオン状態となるようにしてもよい。以上が白書込画素の電圧変化の説明である。

【0076】

[維持画素での電圧変化]

図21は、第5実施形態における維持画素の画素13の等価回路の各部における電圧の変化を示す図である。維持画素ではBフレーム、WフレームおよびNフレームのすべてにおいて駆動トランジスターのゲート電圧GT(A)がVdlとなり、駆動トランジスター132Aがオフ状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdhとなり、駆動トランジスター132Bがオン状態となる。駆動トランジスター132Aはオフ状態、駆動トランジスター132Bはオン状態であるから、画素電極104は、電源線18Bに接続される。したがって、画素電極の電圧PXは、電源線への供給電圧VEP(B)、すなわちNt電圧に維持される。以上が維持画素の電圧変化の説明である。

【0077】

[画素電極の電圧PXの変化例]

続いて、黒が書き込まれている画素13Aを維持画素、白書込画素とする場合、および白が書き込まれている画素13Aを維持画素、黒書込画素とする場合の4画素について、各画素電極の電圧PXの変化の例を説明する。

【0078】

図22は、第5実施形態における画素電極104に印加される電圧の変化の例を説明する図である。図22(a)は、図12(a)と同じであるため説明を省略する。

図22(b)についても図12(b)と符号については同じであるため説明を省略する。ただし、図12(b)における場合と異なり、「F」が存在しない。

【0079】

Bフレーム(BF)では、左下の画素が「+」となり、その他の画素が「0」となる。「+」の画素はBフレームの期間に黒が書き込まれる。「0」の画素は画素電極の電圧PXがNt電圧に固定されているため、「+」の画素の横電界の影響による電圧変動がない。続いて、Wフレーム(WF)では、右上の画素が「−」となり、その他の画素が「0」となる。「−」の画素はWフレームの期間に白が書き込まれる。「0」の画素は画素電極の電圧PXがNt電圧に固定されているため、「−」の画素の横電界の影響による電圧変動がない。

【0080】

この例では、BフレームとWフレームとが予め決められた回数繰り返されて、白書込画素に対応する画素13Aには白が書き込まれ、黒書込画素に対応する画素13Aには黒が書き込まれることになる。また、最後のフレームでは全体の画素13Aにおいて、画素電極の電圧PXがNt電圧に固定されるように、Nフレームが用いられている。このように、第5実施形態では、第1実施形態で存在した「F」となる画素13が存在せず、各画素13Aは書き込まれている状態か「0」となるように構成されているため、黒および白の書き込みが完了するまでの時間を短くすることができるとともに、電気泳動層110の光学状態の変化による表示の滲みが抑制される。

【0081】

<第6実施形態>

第6実施形態では第5実施形態と同様に「4T2C方式」を用いるが、電源線駆動回路17から電源線18Bに出力される素子電源信号がNt電圧以外を取り得る構成になっている。この例では、電源線18Aに出力される素子電源信号は、+VepまたはNt電圧のいずれかであり、電源線18Bに出力される素子電源信号は、−VepまたはNt電圧のいずれかである。また、駆動トランジスター132A、132Bのいずれか一方がオン状態、他方がオフ状態となる場合に限らず、双方がオフ状態となる場合を含む。したがって、画素電極104は、電源線18Aに接続された状態、電源線18Bに接続された状態、およびハイインピーダンスの状態のいずれかとなる。

【0082】

続いて、一の走査線11に接続された画素13Aに注目して、第6実施形態での黒書込画素、白書込画素および維持画素について、画素13Aの等価回路の各部における電圧の変化を順に説明する。なお、第6実施形態では、黒書込画素と白書込画素とは同じフレームで書き込まれるため、以下の説明ではこれまでのBフレームとWフレームとが同時に存在する意味から、BWフレーム(BWF)という表記をする。

【0083】

[黒書込画素での電圧変化]

図23は、第6実施形態における黒書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。黒書込画素では、まずBWフレームにおいて駆動トランジスターのゲート電圧GT(A)がVdhとなり、駆動トランジスター132Aがオン状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdlとなり、駆動トランジスター132Bがオフ状態となる。BWフレームの書込期間Twにおいて、電源線への供給電圧VEP(A)は+Vepとなり、画素電極の電圧PXもこれに追従して+Vepに変化する。このとき、電源線への供給電圧VEP(B)は−Vepとなっている。

画素電極の電圧PXが+Vepとなっているときに、画素13Aの階調が白から黒に変化していく。その後、電源線への供給電圧VEP(A)、VEP(B)はNt電圧となり、画素電極の電圧PXもこれに追従してNt電圧に変化する。

【0084】

続いてNフレームにおいても駆動トランジスターのゲート電圧GT(A)がVdhとなり、駆動トランジスター132Aがオン状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdlとなり、駆動トランジスター132Bがオフ状態となる。なお、オン状態とオフ状態が互いに入れ替わっていてもよいし、双方がオン状態であってもよい。

このとき、電源線への供給電圧VEP(A)、VEP(B)はともにNt電圧であり、画素電極の電圧PXもNt電圧に維持される。以上が黒書込画素の電圧変化の説明である。

【0085】

[白書込画素での電圧変化]

図24は、第6実施形態における白書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。白書込画素では、まずBWフレームにおいて駆動トランジスターのゲート電圧GT(A)がVdlとなり、駆動トランジスター132Aがオフ状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdhとなり、駆動トランジスター132Bがオン状態となる。これにより、画素電極の電圧PXが−Vepとなり、画素13Aの階調が黒から白に変化していく。

【0086】

続いてNフレームにおいても駆動トランジスターのゲート電圧GT(A)がVdlとなり、駆動トランジスター132Aがオフ状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdhとなり、駆動トランジスター132Bがオン状態となる。なお、オン状態とオフ状態が互いに入れ替わっていてもよいし、双方がオン状態であってもよい。

このとき、電源線への供給電圧VEP(A)、VEP(B)はともにNt電圧であり、画素電極の電圧PXもNt電圧に維持される。以上が白書込画素の電圧変化の説明である。

【0087】

[維持画素での電圧変化]

図25は、第6実施形態における維持画素の画素13Aの等価回路の各部における電圧の変化を示す図である。維持画素では、まずBWフレームにおいて駆動トランジスターのゲート電圧GT(A)、GT(B)は共にVdlとなり、駆動トランジスター132A、132Bは共にオフ状態となる。これにより、画素電極104がハイインピーダンスの状態となり、画素電極の電圧PXの電圧値が安定しない状態となる。

続いてNフレームでは、駆動トランジスターのゲート電圧GT(A)がVdhとなり、駆動トランジスター132Aがオン状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdlとなり、駆動トランジスター132Bがオフ状態となる。なお、オン状態とオフ状態が互いに入れ替わっていてもよいし、双方がオン状態であってもよい。

このとき、電源線への供給電圧VEP(A)、VEP(B)はともにNt電圧であり、Nフレームでは画素電極の電圧PXがNt電圧となり安定した状態に戻る。以上が維持画素の電圧変化の説明である。

【0088】

[画素電極の電圧PXの変化例]

続いて、黒が書き込まれている画素13Aを維持画素、白書込画素とする場合、および白が書き込まれている画素13Aを維持画素、黒書込画素とする場合の4画素について、各画素電極の電圧PXの変化の例を説明する。

【0089】

図26は、第6実施形態における画素電極104に印加される電圧の変化の例を説明する図である。図26(a)は、図12(a)と同じであるため説明を省略する。

図26(b)についても図12(b)と符号については同じであるため説明を省略する。

【0090】

BWフレーム(BWF)では、左下の画素が「+」となり、右上の画素が「−」となり、その他の画素が「F」となる。BWフレームの期間に応じて「+」の画素は黒が書き込まれ、「−」の画素は白が書き込まれる。。一方、「F」の画素は「+」の画素および「−」の画素の横電界の影響を受け、画素電極の電圧PXが変化する。続くNフレーム(NF)で総ての画素が「0」となるため、BWフレームにおいて電圧が変化した画素についてもNt電圧に安定することになる。そのため、Nフレームでは、電気泳動層110の光学状態がBWフレーム終了時で維持される。

その後は、BWフレーム、Nフレームが予め決められた回数繰り返されて、白書込画素に対応する画素13Aには白が書き込まれ、黒書込画素に対応する画素13Aには黒が書き込まれることになる。また、BWフレームにおいて「F」となった画素は、画素電極の電圧PXが不安定な状態となるが、NフレームにおいてNt電圧に安定した状態となるため、電気泳動層110の光学状態が変化しない、または変化したとしてもわずかな変化に抑えられる。したがって、Nフレームが存在しない場合に比べて、この電気泳動層110の光学状態の変化による表示の滲みが抑制される。また、黒および白の書き込みを同じフレームで行うため、黒および白の書き込みが完了するまでの時間を短くすることができる。

【0091】

<変形例>

以上、本発明の実施形態について説明したが、本発明は以下のようにさまざまな態様で実施可能である。

【0092】

[変形例1]

上述した第1実施形態では、BフレームとWフレームとの間にNフレームが挿入されていたが、BフレームとWフレームとの間のすべてにNフレームが挿入されていなくてもよい。例えば、BフレームとWフレームとをn回(nは1以上の整数)繰り返した後Nフレームが挿入されるようにしてもよい。また、画像の書き込みにおいて、BフレームとWフレームとが終了した後の最後にNフレームを設けてもよい。これらはすべて隣り合う画素13の横電界の影響の程度、フレーム長、および表示の滲みとして許容される程度に応じて設定されればよい。

【0093】

表示の滲みとして許容される程度としては、表示部1に表示される内容に応じて異なる場合がある。このような場合には、表示の滲みの許容度に応じた駆動モード(設定値)をユーザーが操作部8を操作するなどして適宜設定するようにすればよい。駆動モードとしては、例えば画像表示モード、文字表示モード、ペン入力モードなどとすればよい。画像表示モードでは、表示の滲みをなるべく低減するため、表示部1は第1実施形態のようにBフレームとWフレームとの間すべてにNフレームが存在するように動作する。文字表示モードでは、画像表示モードよりも表示の滲みを許容するものとする。またペン入力モードでは、さらに表示の滲みを許容するものとする。なお、ペン入力モードとは、表示部1の表面に設けられたタッチセンサー上をペンでなぞると、なぞった軌跡が黒色で表示部1に表示されるモードである。

【0094】

図27は、変形例1における表示部1の動作を説明する図である。図27(a)は文字表示モードの場合、図27(b)はペン入力モードの場合を示している。文字表示モードの場合には、この例ではBフレームとWフレームとを2回繰り返す度にNフレームが挿入されるモードである。一方、ペン入力モードの場合には、白書込画素は存在しないため、Bフレームのみが連続し、最後にNフレームが挿入される。なお、最後とは、ユーザによるペン入力が一定期間行われなかった場合としてもよい。なお、ペン入力ではなく消しゴムのようなものでの入力を想定し、なぞった軌跡が白色で表示部1に表示されるモードがあってもよい。この場合にはペン入力モードにおけるBフレームをWフレームとすればよい。

このように、表示の滲みを許容すると、Nフレームを少なくすることができるため、表示の切り替えを早くすることができる。以上、第1実施形態の変形例として説明したが、他の実施形態でも同様である。

【0095】

なお、これらの駆動モードの切り替えはユーザーによって設定されたが、取得部22によって取得される画像データの属性に応じて切り替えられるようにしてもよい。画像データの属性とは画像データがどのような画像を示すかの指標であればよい。例えば、コントローラー2が取得部22によって取得された画像データを解析して属性を決定するようにしてもよい。属性を示す属性情報が画像データに付加されていてもよく、その場合にはコントローラー2は付加された属性情報に基づいて属性を決定し、駆動モードを設定すればよい。

【0096】

[変形例2]

上述した各実施形態および各変形例では、Nフレームを除いた場合、BフレームとWフレームとは1フレームずつ交互に繰り返される構成であったが、別の構成であってもよい。例えば、BフレームとWフレームとが2フレームずつ繰り返されてもよい。また、BフレームとWフレームとが同じ回数ずつ繰り返されなくてもよい。

さらに、BフレームとWフレームとの長さは同じでなくてもよい。例えば、BフレームとWフレームとの書込期間Twの長さが異なっていてもよい。

なお、第6実施形態ではBWフレームを用いているため、上記内容はそのまま適用できないが、BWフレームとNフレームとは別に、第5実施形態におけるBフレームまたはWフレームをさらに加えるようにしてもよい。

【0097】

[変形例3]

上述した各実施形態および各変形例では、スイッチング素子を構成するトランジスターがnチャネル型のトランジスターであったが、pチャネル型のトランジスターにより構成してもよい。

また、スイッチング素子を構成するトランジスターがアモルファスSiを用いたものとしていたが、低温ポリシリコン(LTPS)、高温ポリシリコン(HTPS)、単結晶Si、酸化物半導体、有機半導体など他の半導体を用いてもよい。

【0098】

[変形例4]

上述した各実施形態および各変形例では、例として電気泳動層110が2階調表示を行う説明をしたが、3階調以上の多階調表示を行うものであってもよい。この場合、VRAM4の画像データは3階調以上の階調値を示す。多階調とする場合、例えば各画素への書き込み回数が階調に応じて変化するようにコントローラー2によって制御されればよい。

また、表示部1に用いられる電気光学素子は電気泳動素子以外であってもよく、例えば、エレクトロクロミック素子、エレクトロウェッティング素子、粉体トナー、液体トナー、強誘電液晶、OCB液晶、構造を機械的に変えることで反射率や透過率を変調させる素子など、電圧または電流が印加されることにより光学状態を異ならせる素子であればよい。

【0099】

[変形例5]

上述した各実施形態および各変形例において、表示部1は画素電極104と共通電極122との間に挟まれた電気泳動層110の光学状態を変化させて画像を表示していた。本変形例では、この構造以外により画像を表示するものであってもよい。例えば、表示部1は並置された2つ以上の電極の上に荷電粒子層が形成されたものであってもよい。この場合、各電極に電圧を印加することで荷電粒子を電極の配置面の任意の方向に移動させたり、凝集または拡散させたり、局所的に移動させたりして、荷電粒子層の光学状態を変えられる。

また、上述した各実施形態および各変形例において、表示部1は白黒表示をする例を説明したが、電気泳動層110または表示部1としてカラー表示ができるものであってもよい。例えば、白黒以外の色がついた電気泳動粒子を用いてもよいし、白黒粒子であっても電気泳動層の着色料を添加したり、カラーフィルタ等の層を別途設けてもよい。

また、表示部1は電源線駆動回路17を有していなくてもよい。この場合、コントローラー2が電源線18に素子駆動電圧を供給すればよい。

【0100】

[変形例6]

上述した各実施形態および各変形例において、電子機器1000は、電子ブックリーダーとしたが、パーソナルコンピューター、PDA(Personal Digital Assistant)、携帯電話、スマートフォン、タブレット端末、携帯ゲーム機、電子棚札、電子IDカードなどであってもよい。これらの電子機器において、コントローラー2が実現する各機能(図6参照)はCPU3がプログラムを実行することにより実現されてもよい。このプログラムは磁気記録媒体(磁気テープ、磁気ディスク(HDD(Hard Disk Drive)、FD(Flexible Disk))など)、光記録媒体(光ディスク(CD(Compact Disc)、DVD(Digital Versatile Disk))など)、光磁気記録媒体、半導体メモリーなどのコンピューター読取り可能な記録媒体に記憶した状態で提供されてもよい。また、このプログラムは通信回線を介して電子機器1000にダウンロードされてもよい。このようにして取得されたプログラムは電子機器1000にインストールされて使用される。

また、表示部1およびコントローラー2を組み合わせて表示装置として提供してもよい。

【符号の説明】

【0101】

1,1A…表示部、2…コントローラー、3…CPU、4…VRAM、5…RAM、6…ROM、7…記憶部、8…操作部、11…走査線、12,12A,12B…データ線、13,13A…画素、14…表示領域、15…走査線駆動回路、16,16A…データ線駆動回路、17,17A…電源線駆動回路、18,18A,18B…電源線、21…出力部、22…取得部、23…制御部、100…第1基板、101…基板、102…接着層、103…回路層、104…画素電極、110…電気泳動層、111…マイクロカプセル、112…バインダー、120…第2基板、121…フィルム、122…共通電極、131,131A,131B…画素トランジスター、132,132A,132B…駆動トランジスター、133,133A,133B…容量素子、134,134A,134B…メモリー回路

【技術分野】

【0001】

本発明は、電気光学装置を駆動する技術に関する。

【背景技術】

【0002】

電気光学装置の多くにおいて、1つの画素において1つのトランジスターと1つの容量素子とを有する方式(以下、この方式を「1T1C方式」という)が用いられている。電気泳動素子などの記憶性の電気光学素子を用いる場合、1T1C方式では、1枚の絵を出力するために1つの画素において複数回の書き込みを行う場合があった。一方、1つの画素において2つのトランジスターと1つの容量素子とを有する方式(以下、この方式を「2T1C方式」という)を用いると、1フレームにおける1つの画素に対する書き込み時間を長くすることができるため、書き込み回数を減じることができる。2T1C方式については、例えば、特許文献1に開示されている。また、1つの画素において4つのトランジスターと2つの容量素子とを有する方式(以下、この方式を「4T2C方式」という)を用いて低消費電力化を図る技術も開示されている(例えば、特許文献2)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−176330号公報

【特許文献2】特開2010−102299号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

2T1C方式では画素に白または黒の書き込みをするときには、画素電極に書き込みに必要な電圧が印加される。一方で、この書き込み中において書き込み対象外の画素の画素電極には0Vの電圧を書き込むことができないため、その画素電極はハイインピーダンスの状態になる。そのため、書き込み対象外の画素であっても書き込み対象の画素から横電界の影響を受けて、白または黒がわずかに書き込まれてしまい表示が滲んでしまうことがあった。

【0005】

本発明は、上述した事情に鑑みてなされたものであり、その目的の一つは、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することにある。

【課題を解決するための手段】

【0006】

上述の課題を解決するため、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持するメモリー回路と、前記メモリー回路に保持されたデータ電圧に応じて、素子駆動電源線に接続された状態またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路とを有する電気光学装置の駆動方法であって、前記画素毎に前記電気光学素子の光学状態を指定する画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる素子駆動電圧以上の第1の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第1ステップと、前記一の画素に対応する前記画素電極に、絶対値が前記素子駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第2ステップとを備えることを特徴とする電気光学装置の駆動方法を提供する。

この電気光学装置の駆動方法によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0007】

また、別の好ましい態様において、前記第1ステップは、前記素子駆動電源線に前記第2の電圧が印加された状態で、前記メモリー回路に前記データ電圧を保持させるステップと、前記メモリー回路に前記データ電圧が保持された状態で、前記素子駆動電源線に前記第1の電圧を印加するステップと、前記メモリー回路に前記データ電圧が保持された状態で、前記素子駆動電源線に前記第2の電圧を印加するステップとを有することを特徴とする。

この電気光学装置の駆動方法によれば、表示を滲みにくくしつつ書き込み時間を短縮することができる。

【0008】

また、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持する2つのメモリー回路と、前記2つのメモリー回路に保持されたデータ電圧に応じて、第1の素子駆動電源線に接続された状態または第2の素子駆動電源線に接続された状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路とを有する電気光学装置の駆動方法であって、前記画素毎に前記電気光学素子の光学状態を指定する画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第1ステップと、前記一の画素に対応する前記画素電極に前記第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第2ステップとを備えることを特徴とする電気光学装置の駆動方法を提供する。

この電気光学装置の駆動方法によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0009】

また、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持する2つのメモリー回路と、前記2つのメモリー回路に保持されたデータ電圧に応じて、第1の素子駆動電源線に接続された状態、第2の素子駆動電源線に接続された状態、またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路とを有する電気光学装置の駆動方法であって、前記画素毎に前記電気光学素子の光学状態を指定する画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、当該画素電極に前記第1の電圧の極性が反転した電圧であって、絶対値が前記最低駆動電圧以上の第3の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第1ステップと、前記一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第2ステップとを備えることを特徴とする電気光学装置の駆動方法を提供する。

この電気光学装置の駆動方法によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0010】

また、別の好ましい態様において、前記第1ステップは、n回(nは1以上の整数)のフレームで、前記一の画素に対応する前記画素電極に電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御することを特徴とする。

この電気光学装置の駆動方法によれば、書き込み時間を短縮することができる。

【0011】

また、別の好ましい態様において、前記第1ステップにおいて前記一の画素に対応する前記画素電極に電圧が印加された状態になる回数nは、前記画像データまたは設定値に基づいて設定可能であることを特徴とする。

この電気光学装置の駆動方法によれば、書き込む画像に応じて、表示の滲みの抑制を優先するか書き込み時間の短縮を優先するかを選択することができる。

【0012】

また、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持するメモリー回路と、前記メモリー回路に保持されたデータ電圧に応じて、素子駆動電源線に接続された状態またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路と、前記走査線を予め決められた順に選択する走査線駆動回路とを有する電気光学装置の駆動方法であって、前記走査線駆動回路により一の走査線が選択され、前記画素毎に前記電気光学素子の光学状態を指定する画像データに基づいて、当該一の走査線に接続された前記画素に対応する画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記信号線および前記素子駆動電源線に印加される電圧を制御する第1ステップと、前記走査線駆動回路により前記一の走査線とは異なる他の走査線が選択され、当該他の走査線に接続された一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第2ステップとを備え、前記走査線駆動回路は、前記他の走査線が次に選択されるまでの時間が、前記一の走査線が次に選択されるまでの時間よりも短くなるように、前記走査線を選択することを特徴とする電気光学装置の駆動方法を提供する。

この電気光学装置の駆動方法によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0013】

また、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持するメモリー回路と、前記メモリー回路に保持されたデータ電圧に応じて、素子駆動電源線に接続された状態またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路とを有する電気光学装置に制御信号を出力する出力手段と、前記複数の画素に対応する前記電気光学素子の光学状態を指定する画像データを取得する取得手段と、前記取得した画像データに基づいて前記電気光学装置を制御する前記制御信号を出力するように、前記出力手段を制御する制御手段とを具備し、前記制御手段は、前記取得した画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御し、前記一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御することを特徴とする制御装置を提供する。

この制御装置によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0014】

また、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持する2つのメモリー回路と、前記2つのメモリー回路に保持されたデータ電圧に応じて、第1の素子駆動電源線に接続された状態または第2の素子駆動電源線に接続された状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路とを有する電気光学装置に制御信号を出力する出力手段と、前記複数の画素に対応する前記電気光学素子の光学状態を指定する画像データを取得する取得手段と、前記取得した画像データに基づいて前記電気光学装置を制御する前記制御信号を出力するように、前記出力手段を制御する制御手段とを具備し、前記制御手段は、前記取得した画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御し、前記一の画素に対応する前記画素電極に前記第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御することを特徴とする制御装置を提供する。

この制御装置によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0015】

また、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持する2つのメモリー回路と、前記2つのメモリー回路に保持されたデータ電圧に応じて、第1の素子駆動電源線に接続された状態、第2の素子駆動電源線に接続された状態、またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路とを有する電気光学装置に制御信号を出力する出力手段と、前記複数の画素に対応する前記電気光学素子の光学状態を指定する画像データを取得する取得手段と、前記取得した画像データに基づいて前記電気光学装置を制御する前記制御信号を出力するように、前記出力手段を制御する制御手段とを具備し、前記制御手段は、前記取得した画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、当該画素電極に前記第1の電圧の極性が反転した電圧であって、絶対値が前記最低駆動電圧以上の第3の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御し、前記一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御することを特徴とする制御装置を提供する。

この制御装置によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0016】

また、本発明は、複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持するメモリー回路と、前記メモリー回路に保持されたデータ電圧に応じて、素子駆動電源線に接続された状態またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路と、前記走査線を予め決められた順に選択する走査線駆動回路とを有する電気光学装置に制御信号を出力する出力手段と、前記複数の画素に対応する前記電気光学素子の光学状態を指定する画像データを取得する取得手段と、前記取得した画像データに基づいて前記電気光学装置を制御する前記制御信号を出力するように、前記出力手段を制御する制御手段とを具備し、前記制御手段は、前記走査線駆動回路により一の走査線が選択され、前記画素毎に前記電気光学素子の光学状態を指定する画像データに基づいて、当該一の走査線に接続された前記画素に対応する画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記信号線および前記素子駆動電源線に印加される電圧を制御し、前記走査線駆動回路により前記一の走査線とは異なる他の走査線が選択され、当該他の走査線に接続された一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御し、前記他の走査線が次に選択されるまでの時間が、前記一の走査線が次に選択されるまでの時間よりも短くなるように、前記走査線駆動回路を制御することを特徴とする制御装置を提供する。

この制御装置によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0017】

また、本発明は、上記記載の制御装置と、前記制御装置から出力される前記制御信号により制御される前記電気光学装置とを具備することを特徴とする表示装置を提供する。

この表示装置によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【0018】

また、本発明は、上記記載の表示装置を具備することを特徴とする電子機器を提供する。

この電子機器によれば、隣り合う画素から横電界の影響を受けることによる表示の滲みを抑制することができる。

【図面の簡単な説明】

【0019】

【図1】電子機器1000の外観を示す図である。

【図2】電子機器1000のハードウエア構成を示すブロック図である。

【図3】表示部1の断面構造を示す模式図である。

【図4】第1実施形態における表示部1の回路構成を示す図である。

【図5】第1実施形態における画素13の等価回路を示す図である。

【図6】コントローラー2の機能構成を示すブロック図である。

【図7】第1実施形態における表示部1の動作を説明する図である。

【図8】第1実施形態における駆動信号を示すタイミングチャートである。

【図9】第1実施形態における黒書込画素の画素13の等価回路の各部における電圧の変化を示す図である。

【図10】第1実施形態における白書込画素の画素13の等価回路の各部における電圧の変化を示す図である。

【図11】第1実施形態における維持画素の画素13の等価回路の各部における電圧の変化を示す図である。

【図12】第1実施形態における画素電極104に印加される電圧の変化の例を説明する図である。

【図13】第2実施形態における駆動信号を示すタイミングチャートである。

【図14】第2実施形態における表示部1の動作を説明する図である。

【図15】第3実施形態における表示部1の動作を説明する図である。

【図16】第4実施形態における駆動信号を示すタイミングチャートである。

【図17】第5実施形態における表示部1Aの回路構成を示す図である。

【図18】第5実施形態における画素13Aの等価回路を示す図である。

【図19】第5実施形態における黒書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。

【図20】第5実施形態における白書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。

【図21】第5実施形態における維持画素の画素13Aの等価回路の各部における電圧の変化を示す図である。

【図22】第5実施形態における画素電極104に印加される電圧の変化の例を説明する図である。

【図23】第6実施形態における黒書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。

【図24】第6実施形態における白書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。

【図25】第6実施形態における維持画素の画素13Aの等価回路の各部における電圧の変化を示す図である。

【図26】第6実施形態における画素電極104に印加される電圧の変化の例を説明する図である。

【図27】変形例1における表示部1の動作を説明する図である。

【発明を実施するための形態】

【0020】

<第1実施形態>

[全体構成]

図1は、第1実施形態における電子機器1000の外観を示す図である。電子機器1000は画像を表示する表示装置である。この例においては、電子機器1000は電子書籍を閲覧するための装置、いわゆる電子ブックリーダーである。電子書籍は複数ページの画像を含むデータである。電子機器1000は電子書籍をある単位(例えば1ページずつ)で表示部1に表示する。電子書籍に含まれる複数ページのうち、表示の対象となる一のページを「選択ページ」という。選択ページはユーザーによるボタン8A〜8Fの操作に応じて変更される。ユーザーはボタン8A〜8Fの操作により電子書籍のページをめくること(ページ送りまたはページ戻し)ができる。

【0021】

図2は、電子機器1000のハードウェア構成を示すブロック図である。電子機器1000は、表示部1、コントローラー2、CPU(Central Processing Unit)3、VRAM(Video Random Access Memory)4、RAM(Random Access Memory)5、ROM(Read Only Memory)6、記憶部7、および操作部8を有する。これらの各構成はバスBUSを介して接続されている。

表示部1は、画像を表示する電気光学素子を含むディスプレイパネルを有する電気光学装置である。この例では、電圧の印加等によりエネルギーを与えなくても表示を保持するメモリー性の電気光学素子である、電気泳動粒子を用いている。この電気光学素子により、表示部1はモノクロ複数階調(この例では白黒2階調)の像を表示する。コントローラー2は表示部1を制御する制御装置である。CPU3は電子機器1000の各部を制御する処理装置(プロセッサー)である。

【0022】

CPU3は、RAM5をワークエリアとして、ROM6または記憶部7に記憶されたプログラムを実行する。VRAM4は表示部1に表示させる画像を示す画像データを記憶するメモリーである。画像データは表示部1に表示させる画像を示すデータであるから、以下に示すように、複数の画素13に対応する電気泳動層110における光学状態を指定するものとなる。

RAM5はデータを記憶するメモリーである。記憶部7は電子書籍のデータ(書籍データ)を記憶する不揮発性のメモリーである。記憶部7は複数の電子書籍のデータを記憶することができる。操作部8はユーザーの指示を入力するための入力装置であり、例えばタッチスクリーン、キーパッド、またはボタンを含む。図1に示したボタン8A〜8Fは、操作部8を構成する一部である。また、操作部8には、表示部1の表面に設けられたタッチセンサーなどを有していてもよい。バスBUSは構成要素間でデータまたは信号を伝送する伝送路である。

【0023】

図3は、表示部1の断面構造を示す模式図である。表示部1は、第1基板100、電気泳動層110、および第2基板120を有する。第1基板100および第2基板120は、電気泳動層110を挟持するための基板である。

【0024】

第1基板100は、基板101、接着層102、および回路層103を有する。基板101は絶縁性および可撓性を有する材料、例えばポリカーボネートで形成されている。なお基板101は軽量性、可撓性、弾性および絶縁性を有するものであれば、ポリカーボネート以外の樹脂材料により形成されてもよい。また、基板101は可撓性を有しないガラスにより形成されていてもよい。

接着層102は基板101と回路層103とを接着する層である。回路層103は電気泳動層110を駆動するための回路(後述する画素回路など)を有する層である。回路層103は画素電極104を有する。

【0025】

電気泳動層110はマイクロカプセル111およびバインダー112を有する。マイクロカプセル111はバインダー112によって固定されている。バインダー112としては、マイクロカプセル111との親和性が良好で電極との密着性が優れ、かつ高抵抗な材料が用いられる。マイクロカプセル111は内部に分散媒および電気泳動粒子が格納されたカプセルである。マイクロカプセル111は柔軟性を有する材料、例えばアラビアゴム・ゼラチン系の化合物またはウレタン系の化合物等が用いられる。なお、マイクロカプセル111と画素電極104との間には接着剤により形成された接着層が設けられてもよい。

【0026】

分散媒は、水、アルコール系溶媒(メタノール、エタノール、イソプロパノール、ブタノール、オクタノール、メチルセルソルブなど)、エステル類(酢酸エチル、酢酸ブチルなど)、ケトン類(アセトン、メチルエチルケトン、メチルイソブチルケトンなど)、脂肪族炭化水素(ぺンタン、ヘキサン、オクタンなど)、脂環式炭化水素(シクロへキサン、メチルシクロへキサンなど)、芳香族炭化水素(ベンゼン、トルエン、長鎖アルキル基を有するベンゼン類(キシレン、ヘキシルベンゼン、ヘブチルベンゼン、オクチルベンゼン、ノニルベンゼン、デシルベンゼン、ウンデシルベンゼン、ドデシルベンゼン、トリデシルベンゼン、テトラデシルベンゼンなど))、ハロゲン化炭化水素(塩化メチレン、クロロホルム、四塩化炭素、1,2−ジクロロエタンなど)、またはカルボン酸塩である。別の例で、分散媒はその他の油類であってもよい。また、分散媒はこれらの物質が混合されたものでもよい。さらに別の例で、分散媒には界面活性剤などが配合されてもよい。

【0027】

電気泳動粒子は分散媒中で電界によって移動する性質を有する粒子(高分子またはコロイド)である。この例においては白の電気泳動粒子と黒の電気泳動粒子がマイクロカプセル111内に格納されている。黒の電気泳動粒子は、例えば、アニリンブラックやカーボンブラック等の黒色顔料を含む粒子であり、この例においては正に帯電されている。白の電気泳動粒子は、例えば、二酸化チタンや酸化アルミニウム等の白色顔料を含む粒子であり、この例においては負に帯電されている。

【0028】

第2基板120はフィルム121および共通電極122を有する。フィルム121は電気泳動層110の封止および保護をするものである。フィルム121は透明で絶縁性を有する材料、例えばポリエチレンテレフタレートにより形成される。共通電極122は透明で導電性を有する材料、例えば酸化インジウムスズ(Indium Tin Oxide、ITO)により形成される。

マイクロカプセル111内の電気泳動粒子は画素電極104と共通電極122とに印加される電圧に応じてマイクロカプセル111内を移動することにより、電気泳動層110としての光学状態を異ならせる。電子機器1000のユーザーは電気泳動層110を第2基板120側から視認する。

【0029】

[表示部1の回路構成]

図4は、第1実施形態における表示部1の回路構成を示す図である。表示部1は、m本の走査線11、n本のデータ線12、m×n個の画素13、走査線駆動回路15、データ線駆動回路16、電源線駆動回路17、および電源線18を有する。表示領域14はm×n個の画素13を含む。以下、第j行第i列の画素を特に、画素13(i,j)という。画素13内の各要素についても同様である。

【0030】

走査線駆動回路15、データ線駆動回路16、および電源線駆動回路17は、コントローラー2により制御される。走査線11は行方向(X方向)に沿って配置され、走査線駆動回路15から出力される走査信号を伝達する。走査信号はm本の走査線11の中から一の走査線11を順次排他的に選択する信号である。データ線12(信号線)は列方向(Y方向)に沿って配置され、データ線駆動回路16から出力されるデータ信号を伝達する。データ信号は各画素13の階調に応じた信号である。

電源線18(素子駆動電源線)は行方向(X方向)に沿ってm本配置され、画素電極104に印加される素子駆動電圧を供給するための素子電源信号を伝達する配線である。電源線駆動回路17は、電源線18を介して画素13に素子駆動電圧を供給する。この例では、電源線駆動回路17はm本の電源線18にそれぞれ独立したタイミングで素子駆動電圧を供給する。

【0031】

画素13は走査線11およびデータ線12の交差に対応して設けられ、データ信号に応じた階調を示す。なお、複数の走査線11のうち第j行の走査線11を特に、第j行の走査線11という。データ線12についても同様である。

以下、データ信号、走査信号および素子電源信号など、画素13に伝達される各信号を駆動信号という。

【0032】

[画素13の回路構成]

図5は、第1実施形態における画素13(i,j)の等価回路(画素回路)を示す図である。この例においては、画素13は2T1C方式の回路構成になっている。画素13は、画素トランジスター131と、駆動トランジスター132と、容量素子133と、画素電極104とを有する。画素トランジスター131および駆動トランジスター132はスイッチング素子であり、この例ではアモルファスSiを用いたnチャネル型のTFT(Thin Film Transistor)である。

【0033】

画素トランジスター131のゲート端子は第j行の走査線11に接続されている。画素トランジスターのゲート電圧GATEは画素トランジスター131のゲート端子に印加される電圧である。画素トランジスター131のソース・ドレイン端子の一方は第i列のデータ線12に接続されている。データ電圧DATAは画素トランジスター131のデータ線12に接続されるソース・ドレイン端子に印加される電圧である。画素トランジスター131のソース・ドレイン端子の他方は駆動トランジスター132のゲート端子および容量素子133の一方の電極に接続されている。駆動トランジスターのゲート電圧GTは駆動トランジスター132のゲート端子に印加される電圧である。容量素子133の他方の電極は図示せぬ容量線に接続され、電圧VSTG(この例では接地電圧(基準電圧))に固定されている。以下の説明において、各電圧は基準電圧(0V)に対する値を示している。

なお、容量素子133は画素トランジスター131のソース・ドレイン端子と駆動トランジスター132のゲート端子とが接続された部分における寄生容量を含むものであり、必ずしも素子として存在していなくてもよい。

【0034】

駆動トランジスター132のソース・ドレイン端子の一方は電源線18に接続されている。電源線への供給電圧VEPは駆動トランジスター132の電源線18に接続されるソース・ドレイン端子に印加される電圧(素子駆動電圧)である。駆動トランジスター132のソース・ドレイン端子の他方は画素電極104に接続されている。画素電極の電圧PXは画素電極104に印加される電圧である。電気泳動層110は画素電極104および共通電極122に挟まれている。共通電極122は共通電圧COM(この例では接地電圧(基準電圧))に固定されている。

【0035】

ここで、画素トランジスター131および容量素子133は、メモリー回路134を構成している。メモリー回路134は、対応する走査線11が選択されているときにデータ線12に印加されたデータ電圧を保持する。駆動トランジスター132は、メモリー回路134に保持されたデータ電圧に応じて、画素電極104と電源線18との接続状態を切り替えるスイッチング回路を構成している。この例では、スイッチング回路はメモリー回路134に保持された電圧に応じて、画素電極104と電源線18とを電気的に接続した状態(駆動トランジスター132がオン状態)、または画素電極104がハイインピーダンスの状態(駆動トランジスター132がオフ状態)のいずれかに画素電極104の状態を切り替える。

【0036】

[コントローラー2の機能構成]

図6は、コントローラー2の機能構成を示すブロック図である。コントローラー2は、出力部21、取得部22、および制御部23を有する。出力部21は、表示部1に対して、走査線駆動回路15、データ線駆動回路16、および電源線駆動回路17を制御する制御信号を出力する。また、取得部22は、VRAM4に記憶されている画像データを取得し、制御部23に出力する。制御部23は、取得した画像データに基づいて各画素13に対応する電気泳動層110の光学状態を制御する制御信号を出力するように、出力部21を制御する。

【0037】

[動作]

CPU3は、OS(Operating System)またはアプリケーションプログラムに従って、コントローラー2の動作とは独立したタイミングでVRAM4のデータを書き替える。CPU3がVRAM4に記憶されている画像データを書き替えると、CPU3はVRAM4の書き替えを行った旨を示す書き替え通知をコントローラー2に出力する。コントローラー2は書き換え通知を受け取ると、VRAM4に記憶された画像データに基づいて、制御信号を表示部1に対して出力する。走査線駆動回路15、データ線駆動回路16、および電源線駆動回路17からこの制御信号に基づいて出力される駆動信号について説明する。

【0038】

図7は、第1実施形態における表示部1の動作を説明する図である。横軸は時刻の進行を示し、縦軸は走査線11のY方向の位置(Yj:jは1〜mの何れかの整数)を示している。「Scanning Line」とは、各フレームにおいて各走査線11が選択されたタイミングを示す線である。各走査線11が選択されるタイミングが異なるため、各画素13への書き込みが行われる期間は、接続される走査線11によって異なっている。各画素13への書き込みが行われる期間は、階調を白から黒へ変化させていくフレーム(以下、「Bフレーム」(黒フレーム、図では「BF」と記す))、階調を黒から白へ変化させていくフレーム(以下、「Wフレーム」(白フレーム、図では「WF」と記す))、および電気泳動層110の光学状態を異ならせない電圧(以下、Nt電圧といい、この例では基準電圧と同じ0V)を画素電極104に印加するフレーム(以下、「Nフレーム」(ニュートラルフレーム、図では「NF」と記す))に区別されている。この例では、Bフレーム、Nフレーム、Wフレーム、Nフレームが順に繰り返される。これらの各フレームを区別して説明する必要がない場合には、単に「フレーム」という。

【0039】

図8は、第1実施形態における駆動信号を示すタイミングチャートである。走査線駆動回路15は、図8のGATE(Yj:jは1〜mの何れかの整数)に示すように、複数の走査線11の中から一の走査線11を順次排他的に選択する走査信号を走査線11に供給する。選択された走査線11(電圧Gon)に接続された画素トランジスター131はオン状態となり、それ以外の走査線11(電圧Goff)に接続された画素トランジスター131はオフ状態となる。

【0040】

データ線駆動回路16は、夫々選択された走査線11に接続されている各画素13に対応して、表示させる階調に応じたデータ電圧のデータ信号をデータ線12に供給する。データ信号は、Bフレームにおいては、階調を白から黒へ変化させていく画素13(以下、「黒書込画素」という)に対してはデータ電圧をVdhとし、階調を黒から白へ変化させていく画素13(以下、「白書込画素」という)および階調を変化させない画素(以下、「維持画素」という)に対してはデータ電圧をVdlとする。Wフレームにおいては、データ信号は、白書込画素に対してはデータ電圧をVdh、黒書込画素および維持画素に対してはデータ電圧をVdlとする。また、Nフレームにおいては、黒書込画素、白書込画素および維持画素の総てに対してデータ電圧をVdhとする。

【0041】

電源線駆動回路17は、図8のVEP(Zj:jは1〜mの何れかの整数)に示すように、各フレームの選択期間Ts(図9参照)において、各行の電源線への供給電圧VEPがNt電圧となる素子電源信号を電源線18に出力する。選択期間Tsは各行に対応する走査線11が選択される期間であり、行毎に期間の開始タイミングが異なっている。

また、電源線駆動回路17は、各フレームの選択期間Ts以外の期間となる書込時間Tw(図9参照)において、電源線への供給電圧VEPがBフレームにおいては+Vepとなり、Wフレームにおいては−Vepとなり、NフレームにおいてはNt電圧となる素子電源信号を電源線18に供給する。Vepは、画素電極104に印加されると電気泳動層110の光学状態を異ならせることができる最低駆動電圧以上の電圧値である。書込期間Twも選択期間Tsと同様に、行毎に期間の開始タイミングが異なっている。

【0042】

続いて、一の走査線11に接続された画素13に注目して、黒書込画素、白書込画素および維持画素について、画素13の等価回路の各部における電圧の変化を順に説明する。

【0043】

[黒書込画素での電圧変化]

図9は、第1実施形態における黒書込画素の画素13の等価回路の各部における電圧の変化を示す図である。黒書込画素では、まずBフレームの選択期間Tsにおいて、画素トランジスターのゲート電圧GATEが電圧Gonとなることで、メモリー回路134にデータ電圧DATAが保持され、駆動トランジスターのゲート電圧GTはVdhとなる。Bフレームの書込期間Twにおいて、電源線への供給電圧VEPは+Vepとなり、画素電極の電圧PXもこれに追従して+Vepに変化する。画素電極の電圧PXが+Vepとなっているときに、画素13の階調が白から黒に変化していく。その後、電源線への供給電圧VEPはNt電圧となり、画素電極の電圧PXもこれに追従してNt電圧に変化する。

【0044】

続いてNフレームの選択期間Tsにおいて、画素トランジスターのゲート電圧GATEが電圧Gonとなることで、メモリー回路134にデータ電圧DATAが保持され、駆動トランジスターのゲート電圧GTはVdhとなる。Nフレームの書込期間Twにおいて、電源線への供給電圧VEPはNt電圧を維持し、画素電極の電圧PXもNt電圧を維持する。この状態では画素13の階調は変化しない。なお、この画素13と同じ走査線11に接続された他の総ての画素13についても、画素電極の電圧PXはNt電圧となる。

【0045】

続いてWフレームの選択期間Tsにおいて、画素トランジスターのゲート電圧GATEが電圧Gonとなることで、メモリー回路134にデータ電圧DATAが保持され、駆動トランジスターのゲート電圧GTはVdlとなる。Wフレームの書込期間Twにおいて、電源線への供給電圧VEPは−Vepとなる。一方で、駆動トランジスター132はオフ状態であるから、画素電極104がハイインピーダンスの状態となる。そのため、画素電極の電圧PXは、周囲の画素13における画素電極の電圧PXによる横電界の影響を受け電圧値が安定しない状態(Floating)となる。

【0046】

続くNフレームでは、上記のNフレームと同様に画素電極の電圧PXがNt電圧となり、画素電極の電圧PXの電圧値が安定した状態に戻る。

従来のようにNフレームが存在しない場合には、画素電極104がハイインピーダンスの状態となる期間、すなわち画素電極の電圧PXが不安定な状態が長い期間にわたって続くことになる。その場合、周囲の画素13からの横電界の影響により電気泳動層110の光学状態が変化してしまうため、ユーザーには表示の滲みが生じてきたように見えてしまう。一方、本発明のように画素電極の電圧PXの電圧値が不安定な状態となる期間が長く続かないようにすることで、表示の滲みを抑制することができる。以上が黒書込画素の電圧変化の説明である。

【0047】

[白書込画素での電圧変化]

図10は、第1実施形態における白書込画素の画素13の等価回路の各部における電圧の変化を示す図である。白書込画素では、まずBフレームにおいて駆動トランジスターのゲート電圧GTがVdlとなり、駆動トランジスター132がオフ状態となる。画素電極104がハイインピーダンスの状態となり、画素電極の電圧PXの電圧値が安定しない状態となる。続いてNフレームでは画素電極の電圧PXがNt電圧となり安定した状態に戻る。

続くWフレームでは駆動トランジスターのゲート電圧GTがVdhとなり、駆動トランジスター132がオン状態となる。Wフレームの書込期間Twにおいて、電源線への供給電圧VEPは−Vepとなり、画素電極の電圧PXもこれに追従して−Vepに変化する。画素電極の電圧PXが−Vepとなっているときに、画素13の階調が黒から白に変化していく。その後、電源線への供給電圧VEPはNt電圧となり、画素電極の電圧PXもこれに追従してNt電圧に変化する。続くNフレームでは画素電極の電圧PXはNt電圧となる。以上が白書込画素の電圧変化の説明である。

【0048】

[維持画素での電圧変化]

図11は、第1実施形態における維持画素の画素13の等価回路の各部における電圧の変化を示す図である。維持画素では、まずBフレームにおいて駆動トランジスターのゲート電圧GTがVdlとなり、駆動トランジスター132がオフ状態となる。画素電極104がハイインピーダンスの状態となり、画素電極の電圧PXの電圧値が安定しない状態となる。続いてNフレームでは画素電極の電圧PXがNt電圧となり安定した状態に戻る。

続くWフレームではBフレームと同様に駆動トランジスターのゲート電圧GTがVdlとなり、駆動トランジスター132がオフ状態となる。画素電極104がハイインピーダンスの状態となり、画素電極の電圧PXの電圧値が安定しない状態となる。続いてNフレームでは画素電極の電圧PXがNt電圧となり安定した状態に戻る。以上が維持画素の電圧変化の説明である。

【0049】

[画素電極の電圧PXの変化例]

続いて、黒が書き込まれている画素13を維持画素、白書込画素とする場合、および白が書き込まれている画素13を維持画素、黒書込画素とする場合の4画素について、各画素電極の電圧PXの変化の例を説明する。

【0050】

図12は、第1実施形態における画素電極104に印加される電圧の変化の例を説明する図である。図12(a)は、上記4画素に既に黒または白が書き込まれている初期状態(initial image)と、白または黒が書き込まれた書込み後の状態(writed image)とを示している。この図において「B」は黒、「W」は白を表す。図12(a)に示す例では、左上の画素および右下の画素は維持画素、右上の画素は白書込画素、左下の画素は黒書込画素となる。

図12(b)は、各フレームにおいて各画素に対応する画素電極の電圧PXがどのようになっているかを示している。図12(b)に示す例では、「F」はハイインピーダンスの状態により電圧値が不安定となっている状態、「+」は+Vepが印加されている状態、「−」は−Vepが印加されている状態、「0」はNt電圧(0V)が印加されている状態である。

【0051】

Bフレーム(BF)では、左下の画素が「+」となり、その他の画素が「F」となる。「+」の画素はBフレームの期間に黒が書き込まれる。一方、「F」の画素は「+」の画素の横電界の影響を受け、画素電極の電圧PXが+側に変化する。この期間が長く続くと電気泳動層110の光学状態が変化し始めることになるが、続くNフレーム(NF)で総ての画素が「0」となるため、Bフレームにおいて+側に電圧が変化した画素についてもNt電圧に安定することになる。そのため、Nフレームでは、電気泳動層110の光学状態がBフレーム終了時の状態で維持される。

【0052】

Wフレーム(WF)では、右上の画素が「−」となり、その他の画素が「F」となる。「−」の画素はWフレームの期間に白が書き込まれる。一方、「F」の画素は「−」の画素の横電界の影響を受け、画素電極の電圧PXが−側に変化する。この期間が長く続くと電気泳動層110の光学状態が変化し始めることになるが、続くNフレーム(NF)で総ての画素が「0」となるため、Wフレームにおいて−側に電圧が変化した画素についてもNt電圧に安定することになる。そのため、Nフレームでは、電気泳動層110の光学状態がWフレーム終了時の状態で維持される。

その後は、Bフレーム、Nフレーム、Wフレーム、Nフレームの順で予め決められた回数が繰り返されて、白書込画素に対応する画素13には白が書き込まれ、黒書込画素に対応する画素13には黒が書き込まれることになる。また、BフレームまたはWフレームにおいて「F」となった画素は、画素電極の電圧PXが不安定な状態となるが、NフレームにおいてNt電圧に安定した状態となるため、電気泳動層110の光学状態が変化しない、または変化したとしてもわずかな変化に抑えられる。したがって、Nフレームが存在しない場合に比べて、この電気泳動層110の光学状態の変化による表示の滲みが抑制される。

【0053】

<第2実施形態>

第1実施形態では電源線駆動回路17はm本の電源線18にそれぞれ独立したタイミングで素子駆動電圧を供給していたが、第2実施形態では総ての電源線18に共通の素子駆動電圧を供給する場合について説明する。

【0054】

図13は、第2実施形態における駆動信号を示すタイミングチャートである。この例においても第1実施形態の場合と同様にBフレーム、WフレームおよびNフレームが存在し、それぞれ選択期間Tsおよび書込期間Twが存在する。

走査線駆動回路15は、図13のGATE(Yj:jは1〜mの何れかの整数)に示すように、BフレームおよびWフレームの選択期間Tsにおいて、複数の走査線11の中から一の走査線11を順次排他的に選択する走査信号を走査線11に供給する。選択された走査線11に接続された画素トランジスター131はオン状態となり、それ以外の走査線11に接続された画素トランジスター131はオフ状態となる。一方、走査線駆動回路15は、Nフレームの選択期間Tsでは総ての走査線11をまとめて選択する走査信号を走査線11に供給する。そのため、Nフレームでは総ての画素トランジスター131がオン状態となる。Nフレームでは総ての走査線11がまとめて選択されるため、Nフレームの選択期間Tsは、BフレームおよびWフレームの選択期間Tsよりも短くなっている。

【0055】

データ線駆動回路16は、図13のDATAに示すように、各フレームの選択時間Tsにおいて、夫々選択された走査線11に接続されている各画素13に対応して、表示させる階調に応じたデータ電圧のデータ信号をデータ線12に供給する。Bフレームにおいてデータ信号は、黒書込画素に対してはデータ電圧をVdhとし、白書込画素および維持画素に対してはデータ電圧をVdlとする。Wフレームにおいてデータ信号は、白書込画素に対してはデータ電圧をVdh、黒書込画素および維持画素に対してはデータ電圧をVdlとする。Nフレームにおいてデータ信号は、総ての画素(黒書込画素、白書込画素および維持画素)に対してデータ電圧Vdhとする。

【0056】

電源線駆動回路17は、図13のVEPに示すように、各フレームの書込時間Twにおいて電源線への供給電圧VEPが、Bフレームでは+Vep、Wフレームでは−Vep、NフレームではNt電圧となる素子電源信号を電源線18に供給する。一方、選択期間Tsにおいて電源線駆動回路17は、電源線への供給電圧VEPがNt電圧となる素子電源信号を電源線18に供給する。

【0057】

図14は、第2実施形態における表示部1の動作を説明する図である。図7と同様に、横軸は時刻の進行を示し、縦軸は走査線11のY方向の位置(Yj:jは1〜mの何れかの整数)を示している。図14に示すようにNフレームは、BフレームおよびWフレームよりも選択期間Tsおよび書込期間Twが短くなっている。BフレームおよびWフレームの選択期間Tsでは、画素電極の電圧PXが、それぞれのフレームの直前のNフレームでの状態(Nt電圧)に維持されている。したがって、BフレームおよびWフレームの選択期間Tsは、実質的にはNフレームの状態と同様に画素電極の電圧PXがNt電圧に安定した状態であるため、図においては「(BF)」および「(WF)」として記載している。

このように総ての電源線18に共通の素子駆動電圧を供給する構成にしても、第1実施形態と同様に、Nフレームが存在しない場合に比べて、この電気泳動層110の光学状態の変化による表示の滲みを抑制することができる。

【0058】

<第3実施形態>

第1実施形態では走査線駆動回路15は、走査線11の並び順にしたがって順次排他的に選択する走査信号を走査線11に供給していたが、アドレス・デコーダ方式により飛び越し走査をするようにしてもよい。

【0059】

図15は、第3実施形態における表示部1の動作を説明する図である。図7と同様に、横軸は時刻の進行を示し、縦軸は走査線11のY方向の位置(Yj:jは1〜mの何れかの整数)を示している。飛び越し走査における走査線駆動回路15、データ線駆動回路16および電源線駆動回路17の動作例を説明する。

【0060】

(1)走査線駆動回路15が第Sb行の走査線11を選択するように走査信号を出力する。データ線駆動回路16および電源線駆動回路17がBフレームで画素13(i,Sb)に書き込むようにデータ信号および素子電源信号を出力する。具体的には、データ線駆動回路16は、第Sb行の走査線11が選択されているときに、画素13(i,Sb)のうち黒書込画素に対してはデータ電圧をVdhとし、白書込画素および維持画素に対してはデータ電圧をVdlとする。電源線駆動回路17は、電源線への供給電圧VEPが+Vepとなる素子電源信号を第Sb行の電源線18に出力する。

(2)走査線駆動回路15が第Sn1(=Sb+a)行の走査線11を選択するように走査信号を出力する。データ線駆動回路16および電源線駆動回路17がNフレームで画素13(i,Sn1)に書き込むようにデータ信号および素子電源信号を出力する。具体的には、データ線駆動回路16は、第Sn1行の走査線11が選択されているときに、画素13(i,Sn1)の総て(黒書込画素、白書込画素および維持画素)に対してデータ電圧をVdhとする。電源線駆動回路17は、電源線への供給電圧VEPがNt電圧となる素子電源信号を第Sn1行の電源線18に出力する。

(3)走査線駆動回路15が第Sw(=Sn1+b)行の走査線11を選択するように走査信号を出力する。データ線駆動回路16および電源線駆動回路17がWフレームで画素13(i,Sw)に書き込むようにデータ信号および素子電源信号を出力する。具体的には、データ線駆動回路16は、第Sw行の走査線11が選択されているときに、画素13(i,Sw)のうち白書込画素に対してはデータ電圧をVdhとし、黒書込画素および維持画素に対してはデータ電圧をVdlとする。電源線駆動回路17は、電源線への供給電圧VEPが−Vepとなる素子電源信号を第Sw行の電源線18に出力する。

(4)走査線駆動回路15が第Sn2(=Sw+a)行の走査線11を選択するように走査信号を出力する。データ線駆動回路16および電源線駆動回路17がNフレームで画素13(i,Sn2)に書き込むようにデータ信号および素子電源信号を出力する。具体的には、データ線駆動回路16は、第Sn2行の走査線11が選択されているときに、画素13(i,Sn2)の総て(黒書込画素、白書込画素および維持画素)に対してデータ電圧をVdhとする。電源線駆動回路17は、電源線への供給電圧VEPがNt電圧となる素子電源信号を第Sn2行の電源線18に出力する。

上記(1)から(4)の動作を繰り返し、動作を繰り返す度に、走査線駆動回路15は選択する走査線11を1行ずつずらしていく。また、Sb、Sw、Sn1、Sn2は、第m行を超えた場合には第1行に戻る。なお、Sb=Sn+cであるものとする。

【0061】

上述のように動作することで、一度選択された走査線11が次に選択されるまでの時間がa、b、cにより規定されるため、aはNフレームの時間、bはWフレームの時間、cはBフレームの時間に対応することになる。したがって、a、b、cを適宜設定することにより、各フレームの時間を設定することができる。例えば、bおよびcよりもaを小さくすれば、NフレームをWフレームおよびBフレームより短くすることができる。

このように飛び越し走査によってもNフレームを導入することができ、第1実施形態と同様に、Nフレームが存在しない場合に比べて、この電気泳動層110の光学状態の変化による表示の滲みを抑制することができる。また、飛び越し走査を用いることにより、各フレームの長さを適宜設定することができるため、短い時間のNフレームを挿入することもできる。

【0062】

<第4実施形態>

第1実施形態では電源線駆動回路17はm本の電源線18にそれぞれ独立したタイミングで素子駆動電圧を供給し、第2実施形態では総ての電源線18に共通の素子駆動電圧を供給していた。第4実施形態では電源線駆動回路17は、共通の素子駆動電圧が供給される複数本の電源線18を単位として、その単位毎に独立したタイミングで素子駆動電圧を供給する場合について説明する。

【0063】

図16は、第4実施形態における駆動信号を示すタイミングチャートである。この図に示す例では、共通の素子駆動電圧が供給される電源線18の単位は3本である。また、この図においては、2単位分(Y1〜Y3およびY4〜Y6の走査線11)に対応する部分のタイミングチャートとして示している。VEP1はY1〜Y3に対応する電源線への供給電圧、VEP2はY4〜Y6に対応する電源線への供給電圧を示している。タイミングチャートの上下に記載したフレーム(BF、WF、NF)、選択期間Tsおよび書込期間Twについては、Y1〜Y3に対応したものである。

図に示すように、Y1〜Y3でのNフレーム、Bフレーム(またはWフレーム)の選択期間Tsが終了した後、Y4〜Y6でのNフレーム、Bフレーム(またはWフレーム)の選択期間Tsが開始される。したがって、Y1〜Y3とY4〜Y6とはNフレーム+Bフレーム(またはWフレーム)の選択期間Tsだけ、各フレームのタイミングがずれている。

【0064】

このように電源線駆動回路17が複数本の電源線18を単位として素子駆動電圧を供給してもNフレームを導入することができ、第1実施形態と同様に、Nフレームが存在しない場合に比べて、この電気泳動層110の光学状態の変化による表示の滲みを抑制することができる。また、全フレームに占めるNフレームの割合を、第1実施形態と第2実施形態との中間にすることができる。また、電源線駆動回路17が素子駆動電圧を個別に制御する電源線18の数を、第1実施形態よりも少なくすることができる。

【0065】

<第5実施形態>

第1実施形態では「2T1C方式」を用いていたが、第5実施形態では「4T2C方式」を用いた場合について説明する。

【0066】

[表示部1Aの回路構成]

図17は、第5実施形態における表示部1Aの回路構成を示す図である。第1実施形態ではm×n個の画素13に対応してn本のデータ線12が設けられていたが、第5実施形態ではm×n個の画素13Aに対応してn本のデータ線12Aおよびn本のデータ線12Bが設けられている。また、第1実施形態ではm本の電源線18が設けられていたが、第5実施形態ではm本の電源線18Aおよびm本の電源線18Bが設けられている。このように、第5実施形態では各画素13Aに対して2本のデータ線(12A、12B)および2本の電源線(18A、18B)が設けられている。

【0067】

この例では、電源線18Aに出力される素子電源信号は第1実施形態と同様に+Vep、−Vep、Nt電圧のいずれかの電圧となる一方、電源線18Bに出力される素子電源信号はNt電圧となっている。

【0068】

[画素13Aの回路構成]

図18は、第5実施形態における画素13Aの等価回路を示す図である。この例では画素13Aは4T2C方式の回路構成になっている。そのため第1実施形態では各画素13にはメモリー回路134が1つ設けられていたが、第5実施形態では各画素13Aにはメモリー回路134Aおよびメモリー回路134Bの2つが設けられている。

【0069】

メモリー回路134Aは、対応する走査線11が選択されているときにデータ線12Aに印加されたデータ電圧を保持する。駆動トランジスター132Aは、メモリー回路134Aに保持されたデータ電圧に応じて、画素電極104と電源線18Aとの接続状態を切り替えるスイッチング回路を構成している。メモリー回路134Bは、対応する走査線11が選択されているときにデータ線12Bに印加されたデータ電圧を保持する。駆動トランジスター132Bは、メモリー回路134Bに保持されたデータ電圧に応じて、画素電極104と電源線18Bとの接続状態を切り替えるスイッチング回路を構成している。

この例では、駆動トランジスター132A、132Bのいずれか一方がオン状態、他方がオフ状態となる。したがって、画素電極104は、電源線18Aまたは電源線18Bのいずれかに接続された状態となる。

【0070】

以下の説明では、データ電圧DATA(A)は画素トランジスター131Aのデータ線12Aに接続されるソース・ドレイン端子に印加される電圧である。データ電圧DATA(B)は画素トランジスター131Bのデータ線12Bに接続されるソース・ドレイン端子に印加される電圧である。駆動トランジスターのゲート電圧GT(A)は駆動トランジスター132Aのゲート端子に印加される電圧である。駆動トランジスターのゲート電圧GT(B)は駆動トランジスター132Bのゲート端子に印加される電圧である。電源線への供給電圧VEP(A)は駆動トランジスター132Aの電源線18Aに接続されるソース・ドレイン端子に印加される電圧である。電源線への供給電圧VEP(B)は駆動トランジスター132Bの電源線18Bに接続されるソース・ドレイン端子に印加される電圧である。

【0071】

続いて、一の走査線11に接続された画素13Aに注目して、黒書込画素、白書込画素および維持画素について、画素13Aの等価回路の各部における電圧の変化を順に説明する。

【0072】

[黒書込画素での電圧変化]

図19は、第5実施形態における黒書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。黒書込画素では、まずBフレームにおいて駆動トランジスターのゲート電圧GT(A)がVdhとなり、駆動トランジスター132Aがオン状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdlとなり、駆動トランジスター132Bがオフ状態となる。Bフレームの書込期間Twにおいて、電源線への供給電圧VEP(A)は+Vepとなり、画素電極の電圧PXもこれに追従して+Vepに変化する。画素電極の電圧PXが+Vepとなっているときに、画素13Aの階調が白から黒に変化していく。その後、電源線への供給電圧VEP(A)はNt電圧となり、画素電極の電圧PXもこれに追従してNt電圧に変化する。

【0073】

続いてWフレームにおいて駆動トランジスターのゲート電圧GT(A)がVdlとなり、駆動トランジスター132Aがオフ状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdhとなり、駆動トランジスター132Bがオン状態となる。Wフレームの書込期間Twにおいて、電源線への供給電圧VEP(A)は−Vepとなる。一方で、駆動トランジスター132Aはオフ状態、駆動トランジスター132Bはオン状態であるから、画素電極104は電源線18Bに接続される。したがって、画素電極の電圧PXは電源線への供給電圧VEP(B)、すなわちNt電圧に維持される。そして続くNフレームでも、画素電極の電圧PXはWフレームと同様にNt電圧に維持される。

なお、Nフレームでは電源線への供給電圧VEP(A)をNt電圧にすることで、駆動トランジスター132Aがオン状態、駆動トランジスター132Bがオフ状態となるようにしてもよいし、双方がオン状態となるようにしてもよい。以上が黒書込画素の電圧変化の説明である。

【0074】

[白書込画素での電圧変化]

図20は、第5実施形態における白書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。白書込画素ではBフレームにおいて駆動トランジスターのゲート電圧GT(A)がVdlとなり、駆動トランジスター132Aがオフ状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdhとなり、駆動トランジスター132Bがオン状態となる。Bフレームの書込期間Twにおいて、電源線への供給電圧VEP(A)は+Vepとなる。一方で、駆動トランジスター132Aはオフ状態、駆動トランジスター132Bはオン状態であるから、画素電極104は電源線18Bに接続される。したがって、画素電極の電圧PXは電源線への供給電圧VEP(B)、すなわちNt電圧に維持される。

【0075】

続いてWフレームにおいて駆動トランジスターのゲート電圧GT(A)がVdhとなり、駆動トランジスター132Aがオン状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdlとなり、駆動トランジスター132Bがオフ状態となる。Wフレームの書込期間Twにおいて、電源線への供給電圧VEP(A)は−Vepとなり、画素電極の電圧PXもこれに追従して−Vepに変化する。画素電極の電圧PXが−Vepとなっているときに、画素13Aの階調が黒から白に変化していく。その後、電源線への供給電圧VEP(A)はNt電圧となり、画素電極の電圧PXもこれに追従してNt電圧に変化する。

続くNフレームでは、画素電極の電圧PXはBフレームと同様にNt電圧に維持される。なお、Nフレームでは電源線への供給電圧VEP(A)をNt電圧にすることで、駆動トランジスター132Aがオン状態、駆動トランジスター132Bがオフ状態となるようにしてもよいし、双方がオン状態となるようにしてもよい。以上が白書込画素の電圧変化の説明である。

【0076】

[維持画素での電圧変化]

図21は、第5実施形態における維持画素の画素13の等価回路の各部における電圧の変化を示す図である。維持画素ではBフレーム、WフレームおよびNフレームのすべてにおいて駆動トランジスターのゲート電圧GT(A)がVdlとなり、駆動トランジスター132Aがオフ状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdhとなり、駆動トランジスター132Bがオン状態となる。駆動トランジスター132Aはオフ状態、駆動トランジスター132Bはオン状態であるから、画素電極104は、電源線18Bに接続される。したがって、画素電極の電圧PXは、電源線への供給電圧VEP(B)、すなわちNt電圧に維持される。以上が維持画素の電圧変化の説明である。

【0077】

[画素電極の電圧PXの変化例]

続いて、黒が書き込まれている画素13Aを維持画素、白書込画素とする場合、および白が書き込まれている画素13Aを維持画素、黒書込画素とする場合の4画素について、各画素電極の電圧PXの変化の例を説明する。

【0078】

図22は、第5実施形態における画素電極104に印加される電圧の変化の例を説明する図である。図22(a)は、図12(a)と同じであるため説明を省略する。

図22(b)についても図12(b)と符号については同じであるため説明を省略する。ただし、図12(b)における場合と異なり、「F」が存在しない。

【0079】

Bフレーム(BF)では、左下の画素が「+」となり、その他の画素が「0」となる。「+」の画素はBフレームの期間に黒が書き込まれる。「0」の画素は画素電極の電圧PXがNt電圧に固定されているため、「+」の画素の横電界の影響による電圧変動がない。続いて、Wフレーム(WF)では、右上の画素が「−」となり、その他の画素が「0」となる。「−」の画素はWフレームの期間に白が書き込まれる。「0」の画素は画素電極の電圧PXがNt電圧に固定されているため、「−」の画素の横電界の影響による電圧変動がない。

【0080】

この例では、BフレームとWフレームとが予め決められた回数繰り返されて、白書込画素に対応する画素13Aには白が書き込まれ、黒書込画素に対応する画素13Aには黒が書き込まれることになる。また、最後のフレームでは全体の画素13Aにおいて、画素電極の電圧PXがNt電圧に固定されるように、Nフレームが用いられている。このように、第5実施形態では、第1実施形態で存在した「F」となる画素13が存在せず、各画素13Aは書き込まれている状態か「0」となるように構成されているため、黒および白の書き込みが完了するまでの時間を短くすることができるとともに、電気泳動層110の光学状態の変化による表示の滲みが抑制される。

【0081】

<第6実施形態>

第6実施形態では第5実施形態と同様に「4T2C方式」を用いるが、電源線駆動回路17から電源線18Bに出力される素子電源信号がNt電圧以外を取り得る構成になっている。この例では、電源線18Aに出力される素子電源信号は、+VepまたはNt電圧のいずれかであり、電源線18Bに出力される素子電源信号は、−VepまたはNt電圧のいずれかである。また、駆動トランジスター132A、132Bのいずれか一方がオン状態、他方がオフ状態となる場合に限らず、双方がオフ状態となる場合を含む。したがって、画素電極104は、電源線18Aに接続された状態、電源線18Bに接続された状態、およびハイインピーダンスの状態のいずれかとなる。

【0082】

続いて、一の走査線11に接続された画素13Aに注目して、第6実施形態での黒書込画素、白書込画素および維持画素について、画素13Aの等価回路の各部における電圧の変化を順に説明する。なお、第6実施形態では、黒書込画素と白書込画素とは同じフレームで書き込まれるため、以下の説明ではこれまでのBフレームとWフレームとが同時に存在する意味から、BWフレーム(BWF)という表記をする。

【0083】

[黒書込画素での電圧変化]

図23は、第6実施形態における黒書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。黒書込画素では、まずBWフレームにおいて駆動トランジスターのゲート電圧GT(A)がVdhとなり、駆動トランジスター132Aがオン状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdlとなり、駆動トランジスター132Bがオフ状態となる。BWフレームの書込期間Twにおいて、電源線への供給電圧VEP(A)は+Vepとなり、画素電極の電圧PXもこれに追従して+Vepに変化する。このとき、電源線への供給電圧VEP(B)は−Vepとなっている。

画素電極の電圧PXが+Vepとなっているときに、画素13Aの階調が白から黒に変化していく。その後、電源線への供給電圧VEP(A)、VEP(B)はNt電圧となり、画素電極の電圧PXもこれに追従してNt電圧に変化する。

【0084】

続いてNフレームにおいても駆動トランジスターのゲート電圧GT(A)がVdhとなり、駆動トランジスター132Aがオン状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdlとなり、駆動トランジスター132Bがオフ状態となる。なお、オン状態とオフ状態が互いに入れ替わっていてもよいし、双方がオン状態であってもよい。

このとき、電源線への供給電圧VEP(A)、VEP(B)はともにNt電圧であり、画素電極の電圧PXもNt電圧に維持される。以上が黒書込画素の電圧変化の説明である。

【0085】

[白書込画素での電圧変化]

図24は、第6実施形態における白書込画素の画素13Aの等価回路の各部における電圧の変化を示す図である。白書込画素では、まずBWフレームにおいて駆動トランジスターのゲート電圧GT(A)がVdlとなり、駆動トランジスター132Aがオフ状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdhとなり、駆動トランジスター132Bがオン状態となる。これにより、画素電極の電圧PXが−Vepとなり、画素13Aの階調が黒から白に変化していく。

【0086】

続いてNフレームにおいても駆動トランジスターのゲート電圧GT(A)がVdlとなり、駆動トランジスター132Aがオフ状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdhとなり、駆動トランジスター132Bがオン状態となる。なお、オン状態とオフ状態が互いに入れ替わっていてもよいし、双方がオン状態であってもよい。

このとき、電源線への供給電圧VEP(A)、VEP(B)はともにNt電圧であり、画素電極の電圧PXもNt電圧に維持される。以上が白書込画素の電圧変化の説明である。

【0087】

[維持画素での電圧変化]

図25は、第6実施形態における維持画素の画素13Aの等価回路の各部における電圧の変化を示す図である。維持画素では、まずBWフレームにおいて駆動トランジスターのゲート電圧GT(A)、GT(B)は共にVdlとなり、駆動トランジスター132A、132Bは共にオフ状態となる。これにより、画素電極104がハイインピーダンスの状態となり、画素電極の電圧PXの電圧値が安定しない状態となる。

続いてNフレームでは、駆動トランジスターのゲート電圧GT(A)がVdhとなり、駆動トランジスター132Aがオン状態となる。一方、駆動トランジスターのゲート電圧GT(B)がVdlとなり、駆動トランジスター132Bがオフ状態となる。なお、オン状態とオフ状態が互いに入れ替わっていてもよいし、双方がオン状態であってもよい。

このとき、電源線への供給電圧VEP(A)、VEP(B)はともにNt電圧であり、Nフレームでは画素電極の電圧PXがNt電圧となり安定した状態に戻る。以上が維持画素の電圧変化の説明である。

【0088】

[画素電極の電圧PXの変化例]

続いて、黒が書き込まれている画素13Aを維持画素、白書込画素とする場合、および白が書き込まれている画素13Aを維持画素、黒書込画素とする場合の4画素について、各画素電極の電圧PXの変化の例を説明する。

【0089】

図26は、第6実施形態における画素電極104に印加される電圧の変化の例を説明する図である。図26(a)は、図12(a)と同じであるため説明を省略する。

図26(b)についても図12(b)と符号については同じであるため説明を省略する。

【0090】

BWフレーム(BWF)では、左下の画素が「+」となり、右上の画素が「−」となり、その他の画素が「F」となる。BWフレームの期間に応じて「+」の画素は黒が書き込まれ、「−」の画素は白が書き込まれる。。一方、「F」の画素は「+」の画素および「−」の画素の横電界の影響を受け、画素電極の電圧PXが変化する。続くNフレーム(NF)で総ての画素が「0」となるため、BWフレームにおいて電圧が変化した画素についてもNt電圧に安定することになる。そのため、Nフレームでは、電気泳動層110の光学状態がBWフレーム終了時で維持される。

その後は、BWフレーム、Nフレームが予め決められた回数繰り返されて、白書込画素に対応する画素13Aには白が書き込まれ、黒書込画素に対応する画素13Aには黒が書き込まれることになる。また、BWフレームにおいて「F」となった画素は、画素電極の電圧PXが不安定な状態となるが、NフレームにおいてNt電圧に安定した状態となるため、電気泳動層110の光学状態が変化しない、または変化したとしてもわずかな変化に抑えられる。したがって、Nフレームが存在しない場合に比べて、この電気泳動層110の光学状態の変化による表示の滲みが抑制される。また、黒および白の書き込みを同じフレームで行うため、黒および白の書き込みが完了するまでの時間を短くすることができる。

【0091】

<変形例>

以上、本発明の実施形態について説明したが、本発明は以下のようにさまざまな態様で実施可能である。

【0092】

[変形例1]

上述した第1実施形態では、BフレームとWフレームとの間にNフレームが挿入されていたが、BフレームとWフレームとの間のすべてにNフレームが挿入されていなくてもよい。例えば、BフレームとWフレームとをn回(nは1以上の整数)繰り返した後Nフレームが挿入されるようにしてもよい。また、画像の書き込みにおいて、BフレームとWフレームとが終了した後の最後にNフレームを設けてもよい。これらはすべて隣り合う画素13の横電界の影響の程度、フレーム長、および表示の滲みとして許容される程度に応じて設定されればよい。

【0093】

表示の滲みとして許容される程度としては、表示部1に表示される内容に応じて異なる場合がある。このような場合には、表示の滲みの許容度に応じた駆動モード(設定値)をユーザーが操作部8を操作するなどして適宜設定するようにすればよい。駆動モードとしては、例えば画像表示モード、文字表示モード、ペン入力モードなどとすればよい。画像表示モードでは、表示の滲みをなるべく低減するため、表示部1は第1実施形態のようにBフレームとWフレームとの間すべてにNフレームが存在するように動作する。文字表示モードでは、画像表示モードよりも表示の滲みを許容するものとする。またペン入力モードでは、さらに表示の滲みを許容するものとする。なお、ペン入力モードとは、表示部1の表面に設けられたタッチセンサー上をペンでなぞると、なぞった軌跡が黒色で表示部1に表示されるモードである。

【0094】

図27は、変形例1における表示部1の動作を説明する図である。図27(a)は文字表示モードの場合、図27(b)はペン入力モードの場合を示している。文字表示モードの場合には、この例ではBフレームとWフレームとを2回繰り返す度にNフレームが挿入されるモードである。一方、ペン入力モードの場合には、白書込画素は存在しないため、Bフレームのみが連続し、最後にNフレームが挿入される。なお、最後とは、ユーザによるペン入力が一定期間行われなかった場合としてもよい。なお、ペン入力ではなく消しゴムのようなものでの入力を想定し、なぞった軌跡が白色で表示部1に表示されるモードがあってもよい。この場合にはペン入力モードにおけるBフレームをWフレームとすればよい。

このように、表示の滲みを許容すると、Nフレームを少なくすることができるため、表示の切り替えを早くすることができる。以上、第1実施形態の変形例として説明したが、他の実施形態でも同様である。

【0095】

なお、これらの駆動モードの切り替えはユーザーによって設定されたが、取得部22によって取得される画像データの属性に応じて切り替えられるようにしてもよい。画像データの属性とは画像データがどのような画像を示すかの指標であればよい。例えば、コントローラー2が取得部22によって取得された画像データを解析して属性を決定するようにしてもよい。属性を示す属性情報が画像データに付加されていてもよく、その場合にはコントローラー2は付加された属性情報に基づいて属性を決定し、駆動モードを設定すればよい。

【0096】

[変形例2]

上述した各実施形態および各変形例では、Nフレームを除いた場合、BフレームとWフレームとは1フレームずつ交互に繰り返される構成であったが、別の構成であってもよい。例えば、BフレームとWフレームとが2フレームずつ繰り返されてもよい。また、BフレームとWフレームとが同じ回数ずつ繰り返されなくてもよい。

さらに、BフレームとWフレームとの長さは同じでなくてもよい。例えば、BフレームとWフレームとの書込期間Twの長さが異なっていてもよい。

なお、第6実施形態ではBWフレームを用いているため、上記内容はそのまま適用できないが、BWフレームとNフレームとは別に、第5実施形態におけるBフレームまたはWフレームをさらに加えるようにしてもよい。

【0097】

[変形例3]

上述した各実施形態および各変形例では、スイッチング素子を構成するトランジスターがnチャネル型のトランジスターであったが、pチャネル型のトランジスターにより構成してもよい。

また、スイッチング素子を構成するトランジスターがアモルファスSiを用いたものとしていたが、低温ポリシリコン(LTPS)、高温ポリシリコン(HTPS)、単結晶Si、酸化物半導体、有機半導体など他の半導体を用いてもよい。

【0098】

[変形例4]

上述した各実施形態および各変形例では、例として電気泳動層110が2階調表示を行う説明をしたが、3階調以上の多階調表示を行うものであってもよい。この場合、VRAM4の画像データは3階調以上の階調値を示す。多階調とする場合、例えば各画素への書き込み回数が階調に応じて変化するようにコントローラー2によって制御されればよい。

また、表示部1に用いられる電気光学素子は電気泳動素子以外であってもよく、例えば、エレクトロクロミック素子、エレクトロウェッティング素子、粉体トナー、液体トナー、強誘電液晶、OCB液晶、構造を機械的に変えることで反射率や透過率を変調させる素子など、電圧または電流が印加されることにより光学状態を異ならせる素子であればよい。

【0099】

[変形例5]

上述した各実施形態および各変形例において、表示部1は画素電極104と共通電極122との間に挟まれた電気泳動層110の光学状態を変化させて画像を表示していた。本変形例では、この構造以外により画像を表示するものであってもよい。例えば、表示部1は並置された2つ以上の電極の上に荷電粒子層が形成されたものであってもよい。この場合、各電極に電圧を印加することで荷電粒子を電極の配置面の任意の方向に移動させたり、凝集または拡散させたり、局所的に移動させたりして、荷電粒子層の光学状態を変えられる。

また、上述した各実施形態および各変形例において、表示部1は白黒表示をする例を説明したが、電気泳動層110または表示部1としてカラー表示ができるものであってもよい。例えば、白黒以外の色がついた電気泳動粒子を用いてもよいし、白黒粒子であっても電気泳動層の着色料を添加したり、カラーフィルタ等の層を別途設けてもよい。

また、表示部1は電源線駆動回路17を有していなくてもよい。この場合、コントローラー2が電源線18に素子駆動電圧を供給すればよい。

【0100】

[変形例6]

上述した各実施形態および各変形例において、電子機器1000は、電子ブックリーダーとしたが、パーソナルコンピューター、PDA(Personal Digital Assistant)、携帯電話、スマートフォン、タブレット端末、携帯ゲーム機、電子棚札、電子IDカードなどであってもよい。これらの電子機器において、コントローラー2が実現する各機能(図6参照)はCPU3がプログラムを実行することにより実現されてもよい。このプログラムは磁気記録媒体(磁気テープ、磁気ディスク(HDD(Hard Disk Drive)、FD(Flexible Disk))など)、光記録媒体(光ディスク(CD(Compact Disc)、DVD(Digital Versatile Disk))など)、光磁気記録媒体、半導体メモリーなどのコンピューター読取り可能な記録媒体に記憶した状態で提供されてもよい。また、このプログラムは通信回線を介して電子機器1000にダウンロードされてもよい。このようにして取得されたプログラムは電子機器1000にインストールされて使用される。

また、表示部1およびコントローラー2を組み合わせて表示装置として提供してもよい。

【符号の説明】

【0101】

1,1A…表示部、2…コントローラー、3…CPU、4…VRAM、5…RAM、6…ROM、7…記憶部、8…操作部、11…走査線、12,12A,12B…データ線、13,13A…画素、14…表示領域、15…走査線駆動回路、16,16A…データ線駆動回路、17,17A…電源線駆動回路、18,18A,18B…電源線、21…出力部、22…取得部、23…制御部、100…第1基板、101…基板、102…接着層、103…回路層、104…画素電極、110…電気泳動層、111…マイクロカプセル、112…バインダー、120…第2基板、121…フィルム、122…共通電極、131,131A,131B…画素トランジスター、132,132A,132B…駆動トランジスター、133,133A,133B…容量素子、134,134A,134B…メモリー回路

【特許請求の範囲】

【請求項1】

複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、

前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、

前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持するメモリー回路と、前記メモリー回路に保持されたデータ電圧に応じて、素子駆動電源線に接続された状態またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路と

を有する電気光学装置の駆動方法であって、

前記画素毎に前記電気光学素子の光学状態を指定する画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第1ステップと、

前記一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第2ステップと

を備えることを特徴とする電気光学装置の駆動方法。

【請求項2】

前記第1ステップは、

前記素子駆動電源線に前記第2の電圧が印加された状態で、前記メモリー回路に前記データ電圧を保持させるステップと、

前記メモリー回路に前記データ電圧が保持された状態で、前記素子駆動電源線に前記第1の電圧を印加するステップと、

前記メモリー回路に前記データ電圧が保持された状態で、前記素子駆動電源線に前記第2の電圧を印加するステップと

を有する

ことを特徴とする請求項1に記載の電気光学装置の駆動方法。

【請求項3】

複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、

前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、

前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持する2つのメモリー回路と、前記2つのメモリー回路に保持されたデータ電圧に応じて、第1の素子駆動電源線に接続された状態または第2の素子駆動電源線に接続された状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路と

を有する電気光学装置の駆動方法であって、

前記画素毎に前記電気光学素子の光学状態を指定する画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第1ステップと、

前記一の画素に対応する前記画素電極に前記第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第2ステップと

を備えることを特徴とする電気光学装置の駆動方法。

【請求項4】

複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、

前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、

前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持する2つのメモリー回路と、前記2つのメモリー回路に保持されたデータ電圧に応じて、第1の素子駆動電源線に接続された状態、第2の素子駆動電源線に接続された状態、またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路と

を有する電気光学装置の駆動方法であって、

前記画素毎に前記電気光学素子の光学状態を指定する画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、当該画素電極に前記第1の電圧の極性が反転した電圧であって、絶対値が前記最低駆動電圧以上の第3の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第1ステップと、

前記一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第2ステップと

を備えることを特徴とする電気光学装置の駆動方法。

【請求項5】

前記第1ステップは、n回(nは1以上の整数)のフレームで、前記一の画素に対応する前記画素電極に電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する

ことを特徴とする請求項1乃至請求項4のいずれかに記載の電気光学装置の駆動方法。

【請求項6】

前記第1ステップにおいて前記一の画素に対応する前記画素電極に電圧が印加された状態になる回数nは、前記画像データまたは設定値に基づいて設定可能である

ことを特徴とする請求項5に記載の電気光学装置の駆動方法。

【請求項7】

複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、

前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、

前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持するメモリー回路と、前記メモリー回路に保持されたデータ電圧に応じて、素子駆動電源線に接続された状態またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路と、

前記走査線を予め決められた順に選択する走査線駆動回路と

を有する電気光学装置の駆動方法であって、

前記走査線駆動回路により一の走査線が選択され、前記画素毎に前記電気光学素子の光学状態を指定する画像データに基づいて、当該一の走査線に接続された前記画素に対応する画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記信号線および前記素子駆動電源線に印加される電圧を制御する第1ステップと、

前記走査線駆動回路により前記一の走査線とは異なる他の走査線が選択され、当該他の走査線に接続された一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する第2ステップと

を備え、

前記走査線駆動回路は、前記他の走査線が次に選択されるまでの時間が、前記一の走査線が次に選択されるまでの時間よりも短くなるように、前記走査線を選択する

ことを特徴とする電気光学装置の駆動方法。

【請求項8】

複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、

前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、

前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持するメモリー回路と、前記メモリー回路に保持されたデータ電圧に応じて、素子駆動電源線に接続された状態またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路と

を有する電気光学装置に制御信号を出力する出力手段と、

前記複数の画素に対応する前記電気光学素子の光学状態を指定する画像データを取得する取得手段と、

前記取得した画像データに基づいて前記電気光学装置を制御する前記制御信号を出力するように、前記出力手段を制御する制御手段と

を具備し、

前記制御手段は、

前記取得した画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御し、

前記一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する

ことを特徴とする制御装置。

【請求項9】

複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、

前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、

前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持する2つのメモリー回路と、前記2つのメモリー回路に保持されたデータ電圧に応じて、第1の素子駆動電源線に接続された状態または第2の素子駆動電源線に接続された状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路と

を有する電気光学装置に制御信号を出力する出力手段と、

前記複数の画素に対応する前記電気光学素子の光学状態を指定する画像データを取得する取得手段と、

前記取得した画像データに基づいて前記電気光学装置を制御する前記制御信号を出力するように、前記出力手段を制御する制御手段と

を具備し、

前記制御手段は、

前記取得した画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、または当該画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御し、

前記一の画素に対応する前記画素電極に前記第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する

ことを特徴とする制御装置。

【請求項10】

複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、

前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、

前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持する2つのメモリー回路と、前記2つのメモリー回路に保持されたデータ電圧に応じて、第1の素子駆動電源線に接続された状態、第2の素子駆動電源線に接続された状態、またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路と

を有する電気光学装置に制御信号を出力する出力手段と、

前記複数の画素に対応する前記電気光学素子の光学状態を指定する画像データを取得する取得手段と、

前記取得した画像データに基づいて前記電気光学装置を制御する前記制御信号を出力するように、前記出力手段を制御する制御手段と

を具備し、

前記制御手段は、

前記取得した画像データに基づいて、少なくとも一の画素に対応する前記画素電極に、絶対値が前記電気光学素子の光学状態を異ならせる最低駆動電圧以上の第1の電圧が印加された状態、当該画素電極に前記第1の電圧の極性が反転した電圧であって、絶対値が前記最低駆動電圧以上の第3の電圧が印加された状態、または当該画素電極がハイインピーダンスの状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御し、

前記一の画素に対応する前記画素電極に、絶対値が前記最低駆動電圧未満の第2の電圧が印加された状態になるように、前記走査線、前記信号線および前記素子駆動電源線に印加される電圧を制御する

ことを特徴とする制御装置。

【請求項11】

複数の走査線と複数の信号線との交差に対応して設けられた画素電極を有する複数の画素と、

前記画素電極と対向電極とに挟まれ、当該画素電極に印加される電圧に応じて光学状態を異ならせる電気光学素子と、

前記複数の画素の各々に設けられた画素回路であって、前記走査線および前記信号線が接続され、当該走査線が選択されているときに当該信号線に印加されたデータ電圧を保持するメモリー回路と、前記メモリー回路に保持されたデータ電圧に応じて、素子駆動電源線に接続された状態またはハイインピーダンスの状態のいずれかに前記画素電極の状態を切り替えるスイッチング回路とを有する画素回路と、

前記走査線を予め決められた順に選択する走査線駆動回路と

を有する電気光学装置に制御信号を出力する出力手段と、