電気回路およびノイズ抑制方法

【課題】

電磁放射ノイズを抑制することにより発振子による安定した発振動作を実現できるようにした電気回路およびノイズ抑制方法を提供する。

【解決手段】

発振回路に用いる全ての配線のパターン幅を集積回路102の端子幅(ピン幅)よりも同等以下のサイズとし、このパターン幅を有する配線でループ面積を小さくなるように最短長でグランド端子(ピン)と接続する。さらにグランド配線104をグランド端子106まで接続する間は一切の接続を行わないように配線する。

電磁放射ノイズを抑制することにより発振子による安定した発振動作を実現できるようにした電気回路およびノイズ抑制方法を提供する。

【解決手段】

発振回路に用いる全ての配線のパターン幅を集積回路102の端子幅(ピン幅)よりも同等以下のサイズとし、このパターン幅を有する配線でループ面積を小さくなるように最短長でグランド端子(ピン)と接続する。さらにグランド配線104をグランド端子106まで接続する間は一切の接続を行わないように配線する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、プリント配線基板上に搭載される電子部品が構成する電気回路およびノイズ抑制方法に関し、特に、電子部品同士を接続する配線から発生する高周波ノイズを抑制できるようにした電子回路およびノイズ抑制方法に関する。

【背景技術】

【0002】

近年、技術のめざましい発展により装置に搭載される機能の多機能化が進み、同時に装置が小型化する傾向にある。これは電子機器を構成している各部品それぞれを小型化することにより、あるいは、複数の部品を連結させて1つの部品とすることで部品数を少なくしたりすることなどにより実現している。このため部品同士の実装密度が濃くなり複雑化するため、部品を搭載する基板を増やして複数の階層から構成するようにしている。

【0003】

電子機器を動作させるのに必要な電子部品が搭載された信号基板上には、圧電効果などを用いて高い周波数精度の発振を起こす受動素子である発振子が搭載されており、図2に示すような発振回路を形成している。発振回路によってデジタル回路上で一定の周波数(クロックパルス)を発生させることができ、接続された電子部品に電気信号を伝送することができる。

【0004】

このような発振回路は、図2にも示すように発振子から発生したクロックパルスがコンデンサを跨いで配線されたグランド配線に複数のアースを接続することにより安定した発振動作を提供している。

【0005】

しかしながら、電圧の急激な変化などが生じることにより発振動作が不安定になり、発振子の動作が停止してしまうということがある。

【0006】

このため、安定したクロックパルスを発生させることができなくなり、プリント配線基板全体の故障に繋がってしまうという問題があった。

【0007】

先行技 術である特許文献1に開示された従来技術においては、発振子やコンデンサを接続する配線やグランド配線間で生じる静電容量の均一を行うほか、その周辺伝送路のグランドや電源を延在配線することによりクロックパルスを安定させるようにしている。

【0008】

また、一般に、技術の向上により発振子の精度も向上し、安定した発振動作を備えるようになってきた。例えば、発振子として従来ある水晶発振子に加えてセラミック発振子が開発され、不安定動作が解消されつつあり、安定した発振動作が可能となっている。

【特許文献1】特開平06−204356

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかしながら、特許文献1に示された従来技術においては、めざましい技術革新により、高い周波電流が発生し、プリント配線基板内部のグランドベタや電源ベタパターンが高周波的に誘起されることがある。そのため、各特性を有するそれぞれの配線基板間で共振現象を引き起こしてしまうという問題がある。

【0010】

また、一般的に用いられるセラミック発振子などを用いた場合であっても、発振回路を搭載する配線基板を有する装置の高性能化、多機能化に伴いより高い周波数の電流が必要となるため、発振子から周辺のグランド部に高周波電流が流れ込むことによるノイズの発生が生じてしまうという問題がある。

【0011】

さらに、このノイズの発生により共振現象が発生し、強い電磁ノイズ放射が発生してしまうという問題がある。

【0012】

そこで、本発明は、電磁放射ノイズを抑制することにより発振子による安定した発振動作を実現できるようにした電気回路およびノイズ抑制方法を提供することを目的とする。

【課題を解決するための手段】

【0013】

上記目的を達成するため、請求項1の発明は、集積回路が配置されたプリント配線基板上に搭載され、発振子とコンデンサの各素子を前記集積回路と接続する電気回路において、前記集積回路に設けられたグランド端子の幅以下のサイズのパターン幅で各素子同士および素子と集積回路を配線する配線手段とを具備することを特徴とする。

【0014】

また、請求項2の発明は、請求項1の発明において、前記配線手段は、前記集積回路のグランド端子への配線を最短長で配線することを特徴とする。

【0015】

また、請求項3の発明は、前記配線手段は、前記集積回路のグランド端子への配線上に一切の接続を行わず配線することを特徴とする。

【0016】

また、請求項4の発明は、集積回路が配置されたプリント配線基板上に搭載され、発振子とコンデンサの各素子を前記集積回路と接続する電気回路のノイズ抑制方法において、前記集積回路に設けられた発振端子の幅以下のサイズのパターン幅で各素子同士および素子と集積回路のグランド端子を配線し、その際、一切の接続を行うことなく最短長で配線することを特徴とする。

【発明の効果】

【0017】

本発明によれば、発振回路に用いる全ての配線のパターン幅を集積回路の端子幅(ピン幅)よりも同等以下のサイズとし、このパターン幅を有する配線でループ面積を小さくなるように最短長でグランド端子(ピン)と接続するような構成にして、このグランド端子までは一切のグランド接続を行わないように配線するような構成にしたので、EMI特性を向上させることが可能になるという効果を奏する。

【0018】

また、各ループが小さくなるため周辺部の配線効率が向上し、配線基板の縮小化に伴う装置の小型化が実現できる。

【発明を実施するための最良の形態】

【0019】

以下、本発明に係わる電気回路およびノイズ抑制方法の一実施例を添付図面を参照して詳細に説明する。

【実施例】

【0020】

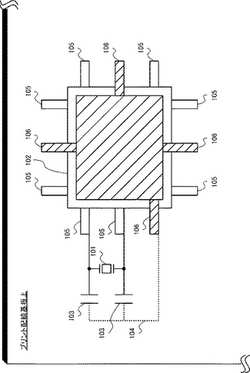

図1は、この発明に係わる電気回路およびノイズ抑制方法を適用して構成した構成図である。

【0021】

図1において、圧電効果を用いて高い周波数精度の発振を起こす受動素子である発振子101、トランジスタ、抵抗、コンデンサ、ダイオードなどの素子からなる集積回路102、発振子101との組み合わせにより発振回路を提供するために抵抗の役割を担うコンデンサ103、グランド端子106との配線パターンとして用いられるグランド配線104、集積回路102のピンである発振端子105、グランド接続を行うピンであるグランド端子106を含んで構成される。

【0022】

発振子101と2つのコンデンサ103により発振を行う発振回路を形成し、発振端子105との配線パターンから電流が入力される。すなわち、電流(特に、高周波電流)が流れ込む発振回路とグランド配線104を集積回路102と分離することになる。

【0023】

発振子101により発振された電荷を2つの発振端子105との配線パターンにより集積回路102に入力し、このときに用いられる配線を含む全ての配線パターンのパターン幅は、集積回路102の発振端子105の幅(ピン幅)と同等かまたは小さいパターン幅を用いる。

【0024】

また、各コンデンサ103から配線されるグランド配線104は途中、一切の接続地点を有することなくグランド端子106と接続される。これは、グランド配線104を基板上のグランドと接続することなく配線することを示している。このときの接続するグランド端子106は、発振端子105に最も近い位置にあるグランド端子106と接続する。

【0025】

さらにグランド端子106との接続を行うグランド配線104は、コンデンサ103から距離が最も短くなるように配線し、グランド配線104や電子部品によりループ上に形成される回路構成のループ面積を最小限のサイズにする。このとき、ループ内には配線パターンにより発生した信号同士の共振現象を他の電子部品に影響しないようにしている。

【0026】

そして、グランド配線104は、発振端子105の近傍に配線させ、集積回路102のグランド端子106と接続した後に、別に設けられた配線基板(例えば、グランド基板)と接続してもよい。また、同一基板上に存在する他の集積回路のグランドと接続する構成としてもよい。

【0027】

これにより、発生した高周波数電流やリターン電流をグランド配線104を介して集積回路102のグランド端子106にのみ流し込まれるのでEMI(EMI(Electro Magnetic Interference:電磁放射ノイズ)特性を向上させることができるようになる。

【0028】

図2は、この発明に係わる電気回路の従来の構成例を示す図である。

【0029】

図2は、共振を発生される受動素子である発振子201、複数の電荷素子から構成される電子部品202、コンデンサ203、配線204、アース接地205−A、205−B、205−C、205−D(以下、総称して「アース接地205」と示す)、抵抗206から構成されている。

【0030】

発振子201とコンデンサ203で構成される発振回路から電子部品202に接続される配線204には、複数のアース接地205が行われた状態を示している。もちろん、一点のみのアース接地205の場合もある。

【0031】

この場合、配線204で発生したノイズ信号を電子部品に直接伝えてしまうことがあり、正常な動作を阻害することになる。これにより、電子部品の動作が不安定となり障害の発生が高まるという問題がある。電子部品を破損させ、基板全体の動作を停止させてしまう。

【0032】

特に、100MHz帯域を超えるような周波数を取り扱う場合には、強いノイズが発生し、より破損の危険性を高めてしまう。高周波電流によるリターン電流の発生や基板上に存在する他の電子部品、さらには配線に電流が流れ込んでしまうという問題もある。

【0033】

本願発明により、他の電子部品への不要な電流の流れ込みを防止できるとともにEMI特性を向上させることができる。

【0034】

従って、本発明を適用することにより、発振子の安定動作が可能となり、さらに基板全体の配線効率が向上するという効果を奏する。

【0035】

さらには、配線効率の向上に伴って、基板サイズを縮小することができるため装置全体を小型化することができるようになる。

【0036】

本発明は、上記し、且つ図面に示す実施例に限定することなく、その要旨を変更しない範囲内で適宜変形して実施できるものである。

【産業上の利用可能性】

【0037】

本発明は、電子情報機器などに実装されるプリント配線基板上に搭載される電子回路およびノイズ抑制方法に適用可能であり、特に、100MHz帯域を超えるような高周波電流を取り扱うプリント配線基板で生じるノイズの抑制を行うことに有用である。

【図面の簡単な説明】

【0038】

【図1】この発明に係わる電気回路およびノイズ抑制方法を適用して構成した構成図。

【図2】この発明に係わる電気回路の従来の構成例を示す図。

【符号の説明】

【0039】

101 発振子

102 集積回路

103 コンデンサ

104 グランド配線

105 発振端子

106 グランド端子

201 発振子

202 電子部品

203 コンデンサ

204 配線

205 アース接地

206 抵抗

【技術分野】

【0001】

本発明は、プリント配線基板上に搭載される電子部品が構成する電気回路およびノイズ抑制方法に関し、特に、電子部品同士を接続する配線から発生する高周波ノイズを抑制できるようにした電子回路およびノイズ抑制方法に関する。

【背景技術】

【0002】

近年、技術のめざましい発展により装置に搭載される機能の多機能化が進み、同時に装置が小型化する傾向にある。これは電子機器を構成している各部品それぞれを小型化することにより、あるいは、複数の部品を連結させて1つの部品とすることで部品数を少なくしたりすることなどにより実現している。このため部品同士の実装密度が濃くなり複雑化するため、部品を搭載する基板を増やして複数の階層から構成するようにしている。

【0003】

電子機器を動作させるのに必要な電子部品が搭載された信号基板上には、圧電効果などを用いて高い周波数精度の発振を起こす受動素子である発振子が搭載されており、図2に示すような発振回路を形成している。発振回路によってデジタル回路上で一定の周波数(クロックパルス)を発生させることができ、接続された電子部品に電気信号を伝送することができる。

【0004】

このような発振回路は、図2にも示すように発振子から発生したクロックパルスがコンデンサを跨いで配線されたグランド配線に複数のアースを接続することにより安定した発振動作を提供している。

【0005】

しかしながら、電圧の急激な変化などが生じることにより発振動作が不安定になり、発振子の動作が停止してしまうということがある。

【0006】

このため、安定したクロックパルスを発生させることができなくなり、プリント配線基板全体の故障に繋がってしまうという問題があった。

【0007】

先行技 術である特許文献1に開示された従来技術においては、発振子やコンデンサを接続する配線やグランド配線間で生じる静電容量の均一を行うほか、その周辺伝送路のグランドや電源を延在配線することによりクロックパルスを安定させるようにしている。

【0008】

また、一般に、技術の向上により発振子の精度も向上し、安定した発振動作を備えるようになってきた。例えば、発振子として従来ある水晶発振子に加えてセラミック発振子が開発され、不安定動作が解消されつつあり、安定した発振動作が可能となっている。

【特許文献1】特開平06−204356

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかしながら、特許文献1に示された従来技術においては、めざましい技術革新により、高い周波電流が発生し、プリント配線基板内部のグランドベタや電源ベタパターンが高周波的に誘起されることがある。そのため、各特性を有するそれぞれの配線基板間で共振現象を引き起こしてしまうという問題がある。

【0010】

また、一般的に用いられるセラミック発振子などを用いた場合であっても、発振回路を搭載する配線基板を有する装置の高性能化、多機能化に伴いより高い周波数の電流が必要となるため、発振子から周辺のグランド部に高周波電流が流れ込むことによるノイズの発生が生じてしまうという問題がある。

【0011】

さらに、このノイズの発生により共振現象が発生し、強い電磁ノイズ放射が発生してしまうという問題がある。

【0012】

そこで、本発明は、電磁放射ノイズを抑制することにより発振子による安定した発振動作を実現できるようにした電気回路およびノイズ抑制方法を提供することを目的とする。

【課題を解決するための手段】

【0013】

上記目的を達成するため、請求項1の発明は、集積回路が配置されたプリント配線基板上に搭載され、発振子とコンデンサの各素子を前記集積回路と接続する電気回路において、前記集積回路に設けられたグランド端子の幅以下のサイズのパターン幅で各素子同士および素子と集積回路を配線する配線手段とを具備することを特徴とする。

【0014】

また、請求項2の発明は、請求項1の発明において、前記配線手段は、前記集積回路のグランド端子への配線を最短長で配線することを特徴とする。

【0015】

また、請求項3の発明は、前記配線手段は、前記集積回路のグランド端子への配線上に一切の接続を行わず配線することを特徴とする。

【0016】

また、請求項4の発明は、集積回路が配置されたプリント配線基板上に搭載され、発振子とコンデンサの各素子を前記集積回路と接続する電気回路のノイズ抑制方法において、前記集積回路に設けられた発振端子の幅以下のサイズのパターン幅で各素子同士および素子と集積回路のグランド端子を配線し、その際、一切の接続を行うことなく最短長で配線することを特徴とする。

【発明の効果】

【0017】

本発明によれば、発振回路に用いる全ての配線のパターン幅を集積回路の端子幅(ピン幅)よりも同等以下のサイズとし、このパターン幅を有する配線でループ面積を小さくなるように最短長でグランド端子(ピン)と接続するような構成にして、このグランド端子までは一切のグランド接続を行わないように配線するような構成にしたので、EMI特性を向上させることが可能になるという効果を奏する。

【0018】

また、各ループが小さくなるため周辺部の配線効率が向上し、配線基板の縮小化に伴う装置の小型化が実現できる。

【発明を実施するための最良の形態】

【0019】

以下、本発明に係わる電気回路およびノイズ抑制方法の一実施例を添付図面を参照して詳細に説明する。

【実施例】

【0020】

図1は、この発明に係わる電気回路およびノイズ抑制方法を適用して構成した構成図である。

【0021】

図1において、圧電効果を用いて高い周波数精度の発振を起こす受動素子である発振子101、トランジスタ、抵抗、コンデンサ、ダイオードなどの素子からなる集積回路102、発振子101との組み合わせにより発振回路を提供するために抵抗の役割を担うコンデンサ103、グランド端子106との配線パターンとして用いられるグランド配線104、集積回路102のピンである発振端子105、グランド接続を行うピンであるグランド端子106を含んで構成される。

【0022】

発振子101と2つのコンデンサ103により発振を行う発振回路を形成し、発振端子105との配線パターンから電流が入力される。すなわち、電流(特に、高周波電流)が流れ込む発振回路とグランド配線104を集積回路102と分離することになる。

【0023】

発振子101により発振された電荷を2つの発振端子105との配線パターンにより集積回路102に入力し、このときに用いられる配線を含む全ての配線パターンのパターン幅は、集積回路102の発振端子105の幅(ピン幅)と同等かまたは小さいパターン幅を用いる。

【0024】

また、各コンデンサ103から配線されるグランド配線104は途中、一切の接続地点を有することなくグランド端子106と接続される。これは、グランド配線104を基板上のグランドと接続することなく配線することを示している。このときの接続するグランド端子106は、発振端子105に最も近い位置にあるグランド端子106と接続する。

【0025】

さらにグランド端子106との接続を行うグランド配線104は、コンデンサ103から距離が最も短くなるように配線し、グランド配線104や電子部品によりループ上に形成される回路構成のループ面積を最小限のサイズにする。このとき、ループ内には配線パターンにより発生した信号同士の共振現象を他の電子部品に影響しないようにしている。

【0026】

そして、グランド配線104は、発振端子105の近傍に配線させ、集積回路102のグランド端子106と接続した後に、別に設けられた配線基板(例えば、グランド基板)と接続してもよい。また、同一基板上に存在する他の集積回路のグランドと接続する構成としてもよい。

【0027】

これにより、発生した高周波数電流やリターン電流をグランド配線104を介して集積回路102のグランド端子106にのみ流し込まれるのでEMI(EMI(Electro Magnetic Interference:電磁放射ノイズ)特性を向上させることができるようになる。

【0028】

図2は、この発明に係わる電気回路の従来の構成例を示す図である。

【0029】

図2は、共振を発生される受動素子である発振子201、複数の電荷素子から構成される電子部品202、コンデンサ203、配線204、アース接地205−A、205−B、205−C、205−D(以下、総称して「アース接地205」と示す)、抵抗206から構成されている。

【0030】

発振子201とコンデンサ203で構成される発振回路から電子部品202に接続される配線204には、複数のアース接地205が行われた状態を示している。もちろん、一点のみのアース接地205の場合もある。

【0031】

この場合、配線204で発生したノイズ信号を電子部品に直接伝えてしまうことがあり、正常な動作を阻害することになる。これにより、電子部品の動作が不安定となり障害の発生が高まるという問題がある。電子部品を破損させ、基板全体の動作を停止させてしまう。

【0032】

特に、100MHz帯域を超えるような周波数を取り扱う場合には、強いノイズが発生し、より破損の危険性を高めてしまう。高周波電流によるリターン電流の発生や基板上に存在する他の電子部品、さらには配線に電流が流れ込んでしまうという問題もある。

【0033】

本願発明により、他の電子部品への不要な電流の流れ込みを防止できるとともにEMI特性を向上させることができる。

【0034】

従って、本発明を適用することにより、発振子の安定動作が可能となり、さらに基板全体の配線効率が向上するという効果を奏する。

【0035】

さらには、配線効率の向上に伴って、基板サイズを縮小することができるため装置全体を小型化することができるようになる。

【0036】

本発明は、上記し、且つ図面に示す実施例に限定することなく、その要旨を変更しない範囲内で適宜変形して実施できるものである。

【産業上の利用可能性】

【0037】

本発明は、電子情報機器などに実装されるプリント配線基板上に搭載される電子回路およびノイズ抑制方法に適用可能であり、特に、100MHz帯域を超えるような高周波電流を取り扱うプリント配線基板で生じるノイズの抑制を行うことに有用である。

【図面の簡単な説明】

【0038】

【図1】この発明に係わる電気回路およびノイズ抑制方法を適用して構成した構成図。

【図2】この発明に係わる電気回路の従来の構成例を示す図。

【符号の説明】

【0039】

101 発振子

102 集積回路

103 コンデンサ

104 グランド配線

105 発振端子

106 グランド端子

201 発振子

202 電子部品

203 コンデンサ

204 配線

205 アース接地

206 抵抗

【特許請求の範囲】

【請求項1】

集積回路が配置されたプリント配線基板上に搭載され、前記集積回路と接続され、発振子とコンデンサを含む外付け回路を有するの各素子を前記集積回路と接続する電気回路において、

前記外付け回路のグランドラインと前記集積回路のグランド端子との間を接続する配線パターンは、途中にグラウンドとの接続を一切有しない

ことを特徴とする電気回路。

【請求項2】

前記配線パターンは、

前記集積回路のグランド端子の幅以下のパターン幅に形成される

ことを特徴とする請求項1記載の電気回路。

【請求項3】

前記配線パターンの長さは最短に設定される

ことを特徴とする請求項1または2記載の電気回路。

【請求項4】

集積回路が配置されたプリント配線基板上に搭載され、前記集積回路と接続され、発振子とコンデンサを含む外付け回路を有するの各素子を前記集積回路と接続する電気回路のノイズ抑制方法において、

前記外付け回路のグランドラインと前記集積回路のグランド端子との間を該集積回路のグランド端子の幅以下のパターン幅の配線パターンで接続し、

前記配線パターンの長さは、最短に設定され、かつ、途中にグラウンドとの接続を一切有しない

ことを特徴とする電気回路のノイズ抑制方法。

【請求項1】

集積回路が配置されたプリント配線基板上に搭載され、前記集積回路と接続され、発振子とコンデンサを含む外付け回路を有するの各素子を前記集積回路と接続する電気回路において、

前記外付け回路のグランドラインと前記集積回路のグランド端子との間を接続する配線パターンは、途中にグラウンドとの接続を一切有しない

ことを特徴とする電気回路。

【請求項2】

前記配線パターンは、

前記集積回路のグランド端子の幅以下のパターン幅に形成される

ことを特徴とする請求項1記載の電気回路。

【請求項3】

前記配線パターンの長さは最短に設定される

ことを特徴とする請求項1または2記載の電気回路。

【請求項4】

集積回路が配置されたプリント配線基板上に搭載され、前記集積回路と接続され、発振子とコンデンサを含む外付け回路を有するの各素子を前記集積回路と接続する電気回路のノイズ抑制方法において、

前記外付け回路のグランドラインと前記集積回路のグランド端子との間を該集積回路のグランド端子の幅以下のパターン幅の配線パターンで接続し、

前記配線パターンの長さは、最短に設定され、かつ、途中にグラウンドとの接続を一切有しない

ことを特徴とする電気回路のノイズ抑制方法。

【図1】

【図2】

【図2】

【公開番号】特開2006−270598(P2006−270598A)

【公開日】平成18年10月5日(2006.10.5)

【国際特許分類】

【出願番号】特願2005−86618(P2005−86618)

【出願日】平成17年3月24日(2005.3.24)

【出願人】(000005496)富士ゼロックス株式会社 (21,908)

【Fターム(参考)】

【公開日】平成18年10月5日(2006.10.5)

【国際特許分類】

【出願日】平成17年3月24日(2005.3.24)

【出願人】(000005496)富士ゼロックス株式会社 (21,908)

【Fターム(参考)】

[ Back to top ]