電流−モード利得分割デュアル−パスVCO

【課題】大きな電圧制御オシレータ(VCO)利得を効率的に取り扱うための技術の提供。

【解決手段】VCOの中心周波数を調節する平均制御電流を供給するための低速高利得パス、及び通常動作の間VCO周波数を調節する瞬間的な制御電流を供給するための高速低利得パス、を利用する。1つのデザインでは、VCOは、電圧−電流コンバータ252、電流増幅器254、総和器256、及び電流制御オシレータ(ICO)260を含む。電圧−電流コンバータは、制御電圧VCTRLを受け取り、そして第1電流I1と第2電流I2とを発生する。電流増幅器は、第1電流を増幅しそしてフィルタし、そして第3電流I3を発生する。総和器は、第2電流と第3電流を合算し、そして制御電流を発生する。ICOは、制御電流CTRLを受け取り、そして制御電流により決定される周波数を有するオシレータ信号を発生する。

【解決手段】VCOの中心周波数を調節する平均制御電流を供給するための低速高利得パス、及び通常動作の間VCO周波数を調節する瞬間的な制御電流を供給するための高速低利得パス、を利用する。1つのデザインでは、VCOは、電圧−電流コンバータ252、電流増幅器254、総和器256、及び電流制御オシレータ(ICO)260を含む。電圧−電流コンバータは、制御電圧VCTRLを受け取り、そして第1電流I1と第2電流I2とを発生する。電流増幅器は、第1電流を増幅しそしてフィルタし、そして第3電流I3を発生する。総和器は、第2電流と第3電流を合算し、そして制御電流を発生する。ICOは、制御電流CTRLを受け取り、そして制御電流により決定される周波数を有するオシレータ信号を発生する。

【発明の詳細な説明】

【技術分野】

【0001】

本明細書は、電子回路に係わり、そしてより具体的には、オシレータ及び位相固定ループ(PLL:phase-locked loop)に関する。

【0002】

[米国特許法35§119による優先権の主張]

特許に関する本出願は、米国特許仮出願番号第60/758,468号、名称“超低供給電圧位相固定ループ・アプリケーションのための電圧制御オシレータ(VCO)周波数を中心に合わせつつVCO利得Kvcoを削減するデュアル−パス方法(A dual-path method of reducing Voltage Controlled Oscillator(VCO) gain Kvco while centering VCO frequency for ultra low supply voltage Phase Locked Loop application)”、2006年1月11日出願、に優先権を主張し、本出願の譲受人に譲渡され、そして本明細書中に引用によってその全体が取り込まれている。

【背景技術】

【0003】

オシレータ及び位相固定ループは、多くの電子回路の不可欠な部品であり、そして通信回路において特に重要である。例えば、ディジタル・システムは、同期回路(例えば、フリップ−フロップ)をトリガするためにクロック信号を使用する。送信機及び受信機システムは、それぞれ周波数アップコンバージョン及びダウンコンバージョンのためにローカル・オシレータ(LO:local oscillator)信号を使用する。無線通信システム中の無線デバイス(例えば、セルラ電話機)は、ディジタル回路のためのクロック信号と送信機及び受信機システムのためのLO信号を一般的に使用する。クロック信号とLO信号は、オシレータを用いて発生され、そしてそれらの周波数は、多くの場合位相固定ループを用いて制御される。

【0004】

電圧制御オシレータ(VCO:voltage-controlled oscillator)は、制御電圧を用いて変化させることができる発信周波数を有するオシレータである。VCOは、広い範囲にわたり自身の発信周波数を変化させる能力を有するように設計されることができる。この広い同調範囲は、(1)VCOが要求される周波数で又は周波数の要求される範囲で動作することが可能であることを保証するために、そして(2)構成要素の許容誤差、集積回路(IC:integrated circuit)のプロセス変動、温度、電圧供給変動、及びその他に起因する発信周波数の変化を補償するために、要求されることがある。

【0005】

大きなVCO利得は、広い同調範囲を実現するために一般的に必要とされる。VCO利得は、VCOの同調範囲をそのVCOに対する制御電圧範囲により割り算したものにおおよそ等しい。大きなVCO利得は、様々な有害な効果を引き起こすことがある。第1に、VCOがPLLにおいて使用される場合に、大きなVCO利得は、一般的に広いループ・フィルタ帯域幅を結果としてもたらし、それはループ安定性を危うくする。一定のループ・フィルタ帯域幅を維持し、そして不安定性を回避するために、小さなチャージ・ポンプ電流及び/又は大きなループ・フィルタ・キャパシタのいずれかが、PLLにおいて使用されることができる。これは、結果としてチャージ・ポンプに対する信号対ノイズ比の低減と大きなオン−チップ・キャパシタのための面積ペナルティをもたらす。第2に大きなVCO利得は、大きな利得により増幅されようとしているPLL内の回路ブロック(例えば、チャージ・ポンプ及びループ・フィルタ)からのノイズを結果としてもたらし、それは結果としてVCO出力におけるより多くのジターをもたらす。これらの全ての有害な効果は、望ましくない。大きなVCO利得に関連する問題は、制御電圧範囲がさらに制限されるため低電圧アプリケーションにおいてさらに明らかである。

【0006】

それゆえ、大きなVCO利得を効率的に取り扱うためのそして良い性能を実現するための技術に対するこの分野における必要性がある。

【発明の概要】

【0007】

電流モード・デュアル・パスを使用して大きなVCO利得を効率的に取り扱うための技術が、本明細書中に記載される。本技術は、(1)VCOの中心周波数を調節する平均制御電流を供給するための低速高利得パス、及び(2)通常動作の間VCO周波数を調節する瞬間的なすなわち高速制御電流を供給するための高速低利得パス、を利用する。高利得パスは、大きなVCO利得に関係するが、遅くそしてこれゆえにPLLループ・ダイナミックスに影響を及ぼさない。低利得パスは、より小さなVCO利得に関係し、通常動作のあいだ係わり、そしてPLLループ・ダイナミックスに影響を及ぼす。VCOは、そのように本質的に2つのVCO利得からなるデュアル−パスVCO利得を有し、それらは低周波数及び高周波数において適用可能である。

【0008】

ある実施形態では、VCOは、電圧−電流コンバータ、電流増幅器、総和器、及び電流制御オシレータ(ICO)を含む。電圧−電流コンバータは、制御電圧を受け取り、そして第1電流と第2電流とを発生する。電流増幅器は、該第1電流を増幅しそしてフィルタし、そして第3電流を発生する。総和器は、該第2電流と該第3電流とを合算し、そして制御電流を発生する。ICOは、該制御電流を受け取り、そして該制御電流により決定される周波数を有するオシレータ信号を発生する。該電圧−電流コンバータ、該電流増幅器、及び該総和器は、例えば、電界効果型トランジスタ(FET)を用いて、効果的に与えられることができる。

【0009】

ある実施形態では、PLLは、上に説明されたVCO、分周器、位相−周波数検出器、及びループ・フィルタを含む。分周器は、該オシレータ信号を分周し、そしてフィードバック信号を供給する。位相−周波数検出器は、該フィードバック信号と基準信号との位相を比較し、そして検出器信号を供給する。該ループ・フィルタは、検出器信号をフィルタし、そして該制御電圧を供給する。PLLループ特性は、高速低利得パスにより与えられるより小さなVCO利得に基づいて設計されることができる。

【0010】

本発明の様々な態様及び実施形態は、下記にさらに詳細に記述される。

【図面の簡単な説明】

【0011】

【図1】古典的なPLLを示す図である。

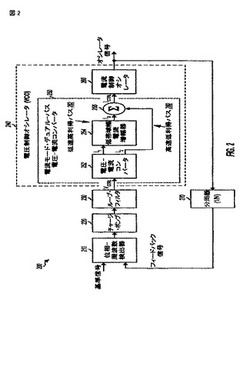

【図2】大きなVCO利得を効率的に取り扱うことが可能な新規なPLLを示す図である。

【図3】電流モード・デュアル−パス電圧−電流コンバータを示す図である。

【図4A】図3のコンバータのs−ドメイン・モデルを示す図である。

【図4B】デュアル−パスVCO利得のプロットを示す図である。

【図5】デュアル−パスVCO利得を持つVCOを有するPLLの動作を示す図である。

【図6】無線デバイスのブロック図を示す図である。

【発明を実施するための形態】

【0012】

本発明の特徴及び本質は、図面を使用して以下に述べる詳細な説明から、さらに明確になるであろう。図面では、同じ参照符号は一貫して対応するものを識別する。

【0013】

用語“具体例の”は、“例、事例、又は実例として働くこと”を意味するように本明細書中では使用される。“具体例の”として本明細書中で記載されたどの実施形態又はデザインも、その他の実施形態又はデザインに対して好ましい又は優位であるとして解釈される必要はない。

【0014】

図1は、古典的なPLL100を示す図であり、それは位相−周波数検出器(PFD:phase-frequency detector)110、チャージ・ポンプ(CP:charge pump)120、ループ・フィルタ(LF:loop filter)130、電圧制御オシレータ(VCO:voltage-controlled oscillator)140、及び分周器170を含む。VCO140は、電圧−電流コンバータ(V2I)150及び電流制御オシレータ(ICO:current-controlled oscillator)160を含む。

【0015】

ICO160は、コンバータ150からの制御電流によって決定される周波数を有するオシレータ信号を発生する。分周器170は、オシレータ信号を係数Nで分周し、そしてフィードバック信号を供給する、ここで、N≧1である。位相−周波数検出器110は、基準信号とフィードバック信号とを受け取り、2つの信号の位相を比較し、そして2つの信号間の位相差/誤差を指示する検出器信号を供給する。チャージ・ポンプ120は、検出された位相誤差に比例する誤差信号を発生する。ループ・フィルタ130は、誤差信号をフィルタし、そしてVCO140に対する制御電圧を供給する。ループ・フィルタ130は、フィードバック信号の位相又は周波数が、基準信号の位相又は周波数に固定されるように制御電圧を調整する。コンバータ150は、制御電圧をICO160に対する制御電流に変換する。

【0016】

VCO140は、広い同調範囲を有することができ、そしてVCO利得は大きいことがある。様々なデザインが、大きなVCO利得を取り扱うために使用されることができる。1つの従来のデザインでは、ディジタル・キャリブレーションは、VCO周波数を中心に合わせるために実行されることができる。このデザインでは、基準電圧は、VCOに与えられ、そして基準電流に変換される。キャリブレーション電流は、ディジタル−アナログ・コンバータで発生され、そしてICOに対する制御電流を発生させるために基準電流と合算される。基準電圧は、VCOに対する公称(すなわち、中心)制御電圧を表す。キャリブレーション電流は、基準電圧の印加でICOが所望の周波数の近くで動作するように選択される。実際に、キャリブレーション電流は、ICOの周波数を中心に合わせるオフセットを与える。これは、次に小さな利得が電圧−電流コンバータに対して使用されることを可能にし、それは、通常動作の間のVCO利得を低減する。このデザインは、追加の回路、例えば、正確な(例えば、バンドギャップ)電圧基準、DAC、及びディジタル・キャリブレーション回路、を使用する。その上、キャリブレーションが電源投入時に1回だけ実行される場合には、キャリブレートされた周波数は、温度及び供給電圧変動のような動作環境の変化のためにドリフトすることがある。

【0017】

別の1つの従来のデザインでは、2つの制御電圧がVCOに対して発生される。このデザインでは、ループ・フィルタからの低利得制御電圧は、基準電圧に対して比較され、そして結果の誤差電圧は、高利得制御電圧を得るために統合される。基準電圧は、VCOに対する公称制御電圧を表す。高利得制御電圧は、ICOを所望の周波数に移動させるために使用される。実際に、高利得制御電圧は、VCOの周波数を中心に合わせるオフセットを与える。これは次に、より小さな利得が低利得制御電圧に使用されることを可能にし、それは通常動作の間のVCO利得を低減する。このデザインは、同様に追加の回路、例えば、正確な(例えば、バンドギャップ)電圧基準及び統合器を与えるための演算増幅器、を使用する。その上、低利得制御電圧に対するパスの帯域幅は、ループ安定性を確実にするためにそしてPLLループ・ダイナミックスを混乱させることを回避するために注意深く設計される必要がある。

【0018】

大きなVCO利得を効率的に取り扱うための新規な技術が本明細書中に説明される。その技術は、上に説明された従来デザインの欠点を回避しつつ良い性能を提供することが可能である。その技術は、2つのパス:高速低利得パスと並行して低速高利得パス:を利用することにより大きなVCO利得を取り扱う。高利得パスは、平均制御電流を与え、それはVCOの中心周波数を調節する。低利得パスは、瞬間的な制御電流すなわち高速制御電流を与え、それは通常動作の間VCO周波数を調節する。高利得パスは、大きなVCO利得に関係するが、遅く、そしてこのためにPLLループ・ダイナミックスに影響を及ぼさない。低利得パスは、より小さなVCO利得に関係し、通常動作の間に必然的に含まれ、そしてPLLループ・ダイナミックスに影響を及ぼす。

【0019】

図2は、大きなVCO利得を効率的に取り扱うことが可能な新規なPLL200の1実施形態のブロック図を示す。PLL200は、位相−周波数検出器210、チャージ・ポンプ220、ループ・フィルタ230、電圧制御オシレータ240、及び分周器270を含む。VCO240は、電流モード・デュアル−パス電圧−電流コンバータ250及び電流制御オシレータ260を含む。

【0020】

位相−周波数検出器210、チャージ・ポンプ220、ループ・フィルタ230及びICO260は、図1中のそれぞれ、位相−周波数検出器110、チャージ・ポンプ120、ループ・フィルタ130、及びICO160に対して上に記述されたように動作する。位相−周波数検出器210、チャージ・ポンプ220、及びループ・フィルタ230は、本技術において公知のいずれかのデザインを用いて与えられることができる。例えば、位相−周波数検出器210は、アーリー−レイト(early-late)検出器であり得て、それはフィードバック信号が基準信号に対して早いか遅れているかどうかを判断する。ループ・フィルタ230は、1次のループ・フィルタ又はある別のループ・フィルタであり得る。ICO260は、様々なオシレータ・デザイン(例えば、コルピッツ・オシレータ、リング・オシレータ、遅延ライン・オシレータ、及びその他)を用いて与えられることができ、そしてディジタル回路系、又はアナログ回路系、又は両方のタイプの回路系で与えられることができる。ICO260は、しかも高周波数(RF:radio frequency)、中間周波数(IF:intermediate frequency)及びその他のような任意の周波数で動作するように設計されることができる。ICO260のデザインは、ICOがそこで使用されるアプリケーションに依存することがある。例えば、ICO260は、ディジタル回路系のためのクロック信号を発生するオシレータであり得る。ICO260は、同様に周波数ダウンコンバージョン及び/又はアップコンバージョンのために使用されるLO信号を発生するRFオシレータであり得る。

【0021】

図2に示された実施形態では、コンバータ250は、電圧−電流コンバータ252、低帯域幅電流増幅器254、及び総和器256を含む。電圧−電流コンバータ252は、ループ・フィルタ230から制御電圧VCTRLを受け取り、そして第1電流I1と第2電流I2を発生する。一般に、第1電流I1は、第2電流I2に等しいか、それよりも大きいか、それよりも小さい。電流増幅器254は、mの利得で第1電流I1を増幅し、増幅された電流をフィルタし、そして第3電流I3を供給する。電流増幅器254は、低帯域幅を有し、そして通常動作の間PLLループ・ダイナミックスに影響を及ぼさない。総和器256は、第2電流I2と第3電流I3とを合算し、そしてICO260に対して制御電流ICTRLを供給する。

【0022】

図2に示された実施形態では、コンバータ250は、2つのパス:高速低利得パス280と低速高利得パス282を有する。この実施形態では、高速低利得パス280は、1の利得を有しそしてフィルタしない、そして低速高利得パス282は、mの利得そして低帯域幅電流増幅器254により与えられるフィルタリングを有する。VCO利得は、そのように2つのパスへと分割される。パス280は、低VCO利得パスに対応し、それは通常動作の間のVCOの瞬間的な周波数を調節する。パス282は、高VCO利得パスに対応し、それはVCOの中心周波数をゆっくりと調節する。VCO利得分割は、電圧−電流変換の後で行われる。これは、コンバータ250の効率的な実行を可能にし、そして下記に記述されるように、他の利点を提供することができる。

【0023】

図3は、電流モード・デュアル−パス電圧−電流コンバータ250aの概略図を示し、それは図2のコンバータ250の1実施形態である。この実施形態では、コンバータ250aは、電圧−電流コンバータ310、高速低利得電流ミラー320、及び低速高利得電流ミラー330を含む。コンバータ250aは、N−チャネル電界効果トランジスタ(N−FET)とP−チャネルFET(P−FET)の両者を有する相補型金属酸化膜半導体(CMOS:complementary metal oxide semiconductor)で与えられる。

【0024】

電圧−電流コンバータ310は、N−FET312と314を含み、それは並列に接続されそして回路のグランドに接続された自身のソースを有する。N−FET312と314のゲートは、一緒に接続され、そして図2のループ・フィルタ230から制御電圧VCTRLを受け取る。

【0025】

高速低利得電流ミラー320は、P−FET322と324を含み、それらは電流ミラーとして接続される。P−FET322は、電源供給電圧VDDに接続されたソース、自身のドレインに接続されたゲート、及びN−FET312のドレインに接続されたドレインを有する。P−FET324は、供給電圧に接続されたソース、P−FET322のゲートに接続されたゲート、及び電流合算ノードに接続されたドレインを有する。

【0026】

低速高利得電流ミラー330は、P−FET332と334を含み、それらは電流ミラーとして接続される。P−FET332は、供給電圧に接続されたソース、自身のドレインに接続されたゲート、及びN−FET314のドレインに接続されたドレインを有する。P−FET334は、供給電圧に接続されたソース、P−FET332のゲートに接続されたゲート、及び電流合算ノードに接続されたドレインを有する。キャパシタ326は、P−FET332と334のゲートに接続された1端子と、供給電圧に接続された別の端子を有する。電流合算ノードは、ICOのための制御電流ICTRLを供給する。

【0027】

電圧−電流コンバータ310に関して、N−FET312と314は、制御電圧VCTRLを受け取り、それぞれI1とI2のドレイン電流を発生する。ドレイン電流と制御電圧との間の変換関数は、N−FET312と314の特性により決定される。図3に示されたように、N−FET312と314とが1Xの同じ大きさでありそして同じゲート−ソース電圧VGSを有する場合には、I1はI2に等しい。

【0028】

電流ミラー320に関して、P−FET322のドレイン電流は、N−FET312のドレイン電流に等しい。P−FET324のドレイン電流は、P−FET322のドレイン電流に等しい、というのはP−FET322と324が1Xの同じ大きさと同じVGS電圧を有するからである。これゆえ、P−FET324は、電流合算ノードにI1のドレイン電流を供給する。電流ミラー320は、いかなる無効の素子(寄生素子を除く)をも含まず、そしてそれゆえ高速である。

【0029】

電流ミラー330に関して、P−FET332のドレイン電流は、N−FET314のドレイン電流に等しい。P−FET334のドレイン電流は、P−FET332のドレイン電流のm倍である、というのは2つのP−FETが同じVGS電圧を有し、そしてP−FET334がm・Xの大きさを有するのに対して、P−FET332は1Xの大きさを有するからである。P−FET334は、電流合算ノードにI3=m・I1のドレイン電流を供給する。電流ミラー330は、キャパシタ326を含み、それはP−FET332と334のゲートにおける電圧の速い変化を防止する。そのように、ドレイン電流I3は、キャパシタ326のサイズと他の因子により決定される遅いレートで変化する。

【0030】

図3は、少数のFETと1つのキャパシタを使用する電流モード・デュアル−パス電圧−電流コンバータ250aの有効な実施形態を示す。電圧−電流変換は、2つのN−FET312と314を用いて実行される。高速低利得パスは、2つのP−FET322と324とからなる第1電流ミラーを用いて与えられる。低速高利得パスは、2つのP−FET332と334及び1つのキャパシタ326からなる第2電流ミラーを用いて与えられる。第2電流ミラーは、mの一定利得での電流増倍を提供する。電流合算ノードは、P−FET324と334のドレイン電流を上手く合算し、そして制御電流を供給する。

【0031】

図3は、CMOSで実装される、電流モード・デュアル−パス電圧−電流コンバータ250の1つの実施形態を示す。一般に、コンバータ250は、様々なデザインで与えられることができる。電圧−電流変換、増幅、フィルタリング、及び合算機能は、複数の回路を用いて明示的に実行されることができる、又は非明示的に実行されることができる。例えば、電流合算は、複数の回路出力を一緒に接続することにより達成されることができる。複数の機能は、しかも所定の回路内に統合されることができる。例えば、2つの電流ミラーは、統合されることができ、そして第1電流と第2電流とが、明確に発生されることはない。

【0032】

図4Aは、電流モード・デュアル−パス電圧−電流コンバータ250のs−ドメイン・モデル400のブロック図を示す。モデル400では、図2の低速高利得パス282は、図4Aに示される変換関数を有するブロック410により表わされる。高速低利得パス280は、線412により表わされる。総和器256は、総和器414により表わされる。

【0033】

電流モード・デュアル−パス電圧−電流コンバータ250に対するデュアル−パスVCO利得は、次式のように表わされることができる:

【数1】

【0034】

ここで、ω0は図2の電流増幅器254の帯域幅であり、

Kvcoは高速低利得パスだけのVCO利得であり、そして

K’vcoは低速高利得パスと高速低利得パスの両方でのVCO利得である。

【0035】

K’vcoは、全ての周波数にわたり適用可能であるデュアル−パスVCO利得である。Kvcoは、より高い周波数において適用可能なVCO利得であり、そしてPLLループ・ダイナミックスに影響を及ぼす。

【0036】

電流増幅器254の帯域幅ω0は、図3のキャパシタ336のサイズとP−FET332の相互コンダクタンスにより決定される。好適な容量値は、所望の帯域幅を実現するために選択されることができる。利得mは、様々な要因に基づいて選択されることができ、例えば、所望の性能、回路実施態様、及びその他である。もしmが小さ過ぎる場合には、デュアル−パスVCO利得の利点は、最小であり得る。逆に、もしmが大き過ぎる場合には、(m+1)・ω0のところのゼロ位置は、高過ぎることがあり、それはPLL安定性に悪影響を与えることがある。ある実施形態では、8の値がmに対して使用される。その他の値も、mに対して同様に使用されることができる。

【0037】

図4Bは、式(1)のデュアル−パスVCO利得のプロットを示す。図4Bと式(1)に示されるように、電流増幅器254の加算は、PLLループ利得に1つのポールと1つのゼロを加算する、それはPLLの周りの総利得である。ポールは、ω0のところに位置し、そしてゼロは、(m+1)・ω0のところ位置する。低周波数において(例えば、s→0)、VCO利得は、(m+1)・Kvcoとして近似されることができる。この大きなVCO利得は、ICOに対する平均制御電流を発生するために使用される。高周波数において、VCO利得は、Kvcoとして近似されることができる。この小さい方のVCO利得は、ロック条件の近くで使用され、そしてジターを低減することを助ける。PLLループ安定性は、(m+1)・ω0がPLLループ利得帯域幅よりもはるかに小さくなるようにそして好ましくはループ・フィルタ230の前記ゼロよりも低くなるように設計することにより保証されることができる。

【0038】

図5は、デュアル−パスVCO利得を持つVCOを有するPLLを動作させるためのプロセス500の1つの実施形態を示す。ブロック510は、VCOの動作を示し、そしてブロック520は、残りのPLLの動作を示す。

【0039】

ブロック510のVCOに関して、第1電流と第2電流は、制御電圧に基づいて発生される(ブロック512)。第1電流は、増幅されそしてフィルタされて、第3電流を発生する(ブロック514)。第2電流と第3電流は、合算されて、制御電流を発生する(ブロック516)。オシレータ信号は、制御電流によって決定される周波数を有するように発生される(ブロック518)。ブロック512,514と516は、図2のコンバータ250により実行されることができる。ブロック518は、ICO260により実行されることができる。

【0040】

ブロック520の残りのPLLに関して、オシレータ信号は、フィードバック信号を発生するために分周される(ブロック522)。フィードバック信号と基準信号の位相は、検出器信号を発生するために比較される(ブロック524)。検出器信号は、制御電圧を発生させるためにループ・フィルタを用いてフィルタされる(ブロック526)。ブロック522,524と526は、図2のそれぞれ、分周器270、位相−周波数検出器210、そしてループ・フィルタ230により実行されることができる。チャージ・ポンプ220は、位相−周波数検出器210の一部として考えられることができる。

【0041】

本明細書中に記述される技術は、制御電圧を電圧−電流変換した後でVCO利得を低速高利得パスと高速低利得パスへと分けることによって広い同調範囲と大きなVCO利得の問題に対処する。広い同調範囲は、VCOに対する平均制御電流を供給する低速高利得パスでサポートされる。高速低利得パスは、ロック条件の近くで使用されるより小さなVCO利得を供給する。より小さなVCO利得は、より小さなループ・フィルタ帯域幅の使用を可能にし、それはPLLループ安定性を改善する。より小さなVCO利得は、しかもオシレータ信号におけるより小さなジターを結果としてもたらす。低速高利得パスと高速低利得パスとの間の利得比mは、固定でありそして満足のいくように決められる。この公知の関係は、他のPLLループ・パラメータを決めることを容易にする。それに加えて、外部電圧基準は、この新規な技術で必要とされない。

【0042】

本明細書中に記述された技術は、各種の低電圧アプリケーションに対して有利に使用されることができる。低電源電圧は、電力消費量削減を助けるために多くの電子回路に対して一般的に使用される。低電力消費は、バッテリーで電源を供給される携帯デバイスに対して特に好ましい。しかしながら、低供給電圧は、制御電圧範囲を同様に制限し、それは大きなVCO利得問題をさらにはっきりとさせる。本明細書中に記述される技術は、大きなVCO利得を取り扱うことが可能であり、それは低電圧アプリケーションにおいてより過酷になり得る。

【0043】

本明細書中に記述された技術は、様々な電子回路に対して使用されることができる。無線通信デバイスに対する本技術の使用が、下記に述べられる。

【0044】

図6は、無線通信システムにおける無線デバイス600の1つの実施形態のブロック図を示す。無線デバイス600は、セルラ電話機、端末、PDA、ハンドセット、又はある他のデバイス又はデザインであり得る。無線通信システムは、符号分割多元接続(CDMA:Code Division Multiple Access)システム、時分割多元接続(TDMA:Time Division Multiple Access)システム、周波数分割多元接続(FDMA:Frequency Division Multiple Access)システム、移動通信のためのグローバル・システム(GMS:Global System for Mobile Communications)システム、直交周波数分割多元接続(OFDMA:Orthogonal Frequency Division Multiple Access)システム、等であり得る。

【0045】

無線デバイス600は、ディジタル・プロセッサ610とトランシーバ630を含み、それは双方向通信をサポートする。ディジタル・プロセッサ610は、1又はそれより多くの用途特定集積回路(ASIC:application specific integrated circuit)を用いて与えられることができ、そしてトランシーバ630は、1又はそれより多くのRF集積回路(RFIC:RF integrated circuit)を用いて与えられることができる。

【0046】

ディジタル・プロセッサ610の内部で、エンコーダ612は、送信されるデータを処理し(例えば、フォーマット化し、エンコードし、そしてインターリーブし)、そして変調器(Mod)614は、コード化されたデータをさらに処理して(例えば、変調し、そしてスクランブルして)データ・チップを生成する。トランシーバ630の内部で、送信(TX)ベースバンド・ユニット632は、ベースバンド処理、例えば、ディジタル−アナログ変換、フィルタリング、増幅、及びその他、を実行する。ミキサ634は、ベースバンド信号をRFへアップコンバートする。TX RFユニット636は、信号調整、例えば、フィルタリング及び強度増幅、を実行して、RF変調された信号を発生する、その信号はアンテナ640を介して送信される。データ受信に関して、受信(RX)RFユニット642は、アンテナ640から入力RF信号を受信し、そして信号調整、例えば、低雑音増幅及びフィルタリングを実行する。ミキサ644は、調整されたRF信号をRFからベースバンドにダウンコンバートする。RFベースバンド・ユニット646は、ベースバンド処理、例えば、フィルタリング、増幅、アナログ−ディジタル変換、等、を実行する。復調器(Dmod)616は、ユニット646からの入力サンプルを処理し(例えば、逆スクランブルし、そして復調し)そしてシンボル推定値を与える。デコーダ618は、シンボル推定値を処理し(例えば、逆インターリーブし、そしてデコードし)そしてデコードされたデータを与える。一般に、データ・プロセッサ610とトランシーバ630による処理は、無線システムのデザインに依存する。

【0047】

プロセッサ620は、様々なアプリケーション、例えば、ビデオ、オーディオ、グラフィックス、等、をサポートすることができる。コントローラ/プロセッサ660は、無線デバイス600内の様々な処理ユニットの動作を管理する。メモリ662は、無線デバイス600のためのプログラム・コードとデータを記憶する。

【0048】

VCO/PLL622は、ディジタル・プロセッサ610内の処理ユニットに対するクロック信号を発生する。VCO/PLL650は、周波数アップコンバージョンのためにミキサ634によって使用される送信LO信号と周波数ダウンコンバージョンのためにミキサ644によって使用される受信LO信号とを発生する。VCO622及び/又はVCO650は、大きなVCO利得を有することがあり、そして本明細書中に記述された技術を利用することができる。電流モード・デュアル−パス電圧−電流コンバータは、VCO622に対して使用されることができ、VCO利得を2つのパスへと分け、その結果、平均VCO周波数は低速高利得パスを用いて制御されることができ、そして瞬間的なVCO周波数は高速低利得パスを用いて調節されることができる。電流モード・デュアル−パス電圧−電流コンバータは、VCO650に対しても同様に使用されることができる。基準オシレータ664は、VCO/PLL622及び/又はVCO/PLL650に対する基準信号を発生する。基準オシレータ644は、水晶発振器(XO:crystal oscillator)、電圧制御XO(VCXO)、温度補償XO(TCXO)、又はある別のタイプのオシレータであり得る。

【0049】

本明細書中に記述されたVCOとPLLは、アナログIC、RFIC、ASIC、ディジタル信号プロセッサ(DSP)、ディジタル信号処理デバイス(DSPD)、プログラマブル論理デバイス(PLD)、フィールド・プログラマブル・ゲート・アレイ(FPGA)、プロセッサ、コントローラ、マイクロ−コントローラ、マイクロプロセッサ、及び他の電子ユニット、で与えられることができる。VCOとPLLは、例えば、N−MOS,P−MOS,CMOS,BJT,GaAs,及びその他のような、様々なICプロセスで与えられることができる。VCOとPLLは、単体構成素子を用いて同様に与えられることができる。

【0050】

開示された実施形態のこれまでの説明は、当業者が、本発明を作成する又は使用することを可能にするために提供される。これらの実施形態への様々な変形は、当業者に容易に明白にされるであろう、そして、ここで規定された一般的な原理は、本発明の精神又は範囲から逸脱することなく他の実施形態に適用されることができる。それゆえ、本発明は、本明細書中に示された実施形態に制限することを意図したものではなく、本明細書中に開示した原理及び新奇な機能と整合する最も広い範囲に適用されるものである。

【技術分野】

【0001】

本明細書は、電子回路に係わり、そしてより具体的には、オシレータ及び位相固定ループ(PLL:phase-locked loop)に関する。

【0002】

[米国特許法35§119による優先権の主張]

特許に関する本出願は、米国特許仮出願番号第60/758,468号、名称“超低供給電圧位相固定ループ・アプリケーションのための電圧制御オシレータ(VCO)周波数を中心に合わせつつVCO利得Kvcoを削減するデュアル−パス方法(A dual-path method of reducing Voltage Controlled Oscillator(VCO) gain Kvco while centering VCO frequency for ultra low supply voltage Phase Locked Loop application)”、2006年1月11日出願、に優先権を主張し、本出願の譲受人に譲渡され、そして本明細書中に引用によってその全体が取り込まれている。

【背景技術】

【0003】

オシレータ及び位相固定ループは、多くの電子回路の不可欠な部品であり、そして通信回路において特に重要である。例えば、ディジタル・システムは、同期回路(例えば、フリップ−フロップ)をトリガするためにクロック信号を使用する。送信機及び受信機システムは、それぞれ周波数アップコンバージョン及びダウンコンバージョンのためにローカル・オシレータ(LO:local oscillator)信号を使用する。無線通信システム中の無線デバイス(例えば、セルラ電話機)は、ディジタル回路のためのクロック信号と送信機及び受信機システムのためのLO信号を一般的に使用する。クロック信号とLO信号は、オシレータを用いて発生され、そしてそれらの周波数は、多くの場合位相固定ループを用いて制御される。

【0004】

電圧制御オシレータ(VCO:voltage-controlled oscillator)は、制御電圧を用いて変化させることができる発信周波数を有するオシレータである。VCOは、広い範囲にわたり自身の発信周波数を変化させる能力を有するように設計されることができる。この広い同調範囲は、(1)VCOが要求される周波数で又は周波数の要求される範囲で動作することが可能であることを保証するために、そして(2)構成要素の許容誤差、集積回路(IC:integrated circuit)のプロセス変動、温度、電圧供給変動、及びその他に起因する発信周波数の変化を補償するために、要求されることがある。

【0005】

大きなVCO利得は、広い同調範囲を実現するために一般的に必要とされる。VCO利得は、VCOの同調範囲をそのVCOに対する制御電圧範囲により割り算したものにおおよそ等しい。大きなVCO利得は、様々な有害な効果を引き起こすことがある。第1に、VCOがPLLにおいて使用される場合に、大きなVCO利得は、一般的に広いループ・フィルタ帯域幅を結果としてもたらし、それはループ安定性を危うくする。一定のループ・フィルタ帯域幅を維持し、そして不安定性を回避するために、小さなチャージ・ポンプ電流及び/又は大きなループ・フィルタ・キャパシタのいずれかが、PLLにおいて使用されることができる。これは、結果としてチャージ・ポンプに対する信号対ノイズ比の低減と大きなオン−チップ・キャパシタのための面積ペナルティをもたらす。第2に大きなVCO利得は、大きな利得により増幅されようとしているPLL内の回路ブロック(例えば、チャージ・ポンプ及びループ・フィルタ)からのノイズを結果としてもたらし、それは結果としてVCO出力におけるより多くのジターをもたらす。これらの全ての有害な効果は、望ましくない。大きなVCO利得に関連する問題は、制御電圧範囲がさらに制限されるため低電圧アプリケーションにおいてさらに明らかである。

【0006】

それゆえ、大きなVCO利得を効率的に取り扱うためのそして良い性能を実現するための技術に対するこの分野における必要性がある。

【発明の概要】

【0007】

電流モード・デュアル・パスを使用して大きなVCO利得を効率的に取り扱うための技術が、本明細書中に記載される。本技術は、(1)VCOの中心周波数を調節する平均制御電流を供給するための低速高利得パス、及び(2)通常動作の間VCO周波数を調節する瞬間的なすなわち高速制御電流を供給するための高速低利得パス、を利用する。高利得パスは、大きなVCO利得に関係するが、遅くそしてこれゆえにPLLループ・ダイナミックスに影響を及ぼさない。低利得パスは、より小さなVCO利得に関係し、通常動作のあいだ係わり、そしてPLLループ・ダイナミックスに影響を及ぼす。VCOは、そのように本質的に2つのVCO利得からなるデュアル−パスVCO利得を有し、それらは低周波数及び高周波数において適用可能である。

【0008】

ある実施形態では、VCOは、電圧−電流コンバータ、電流増幅器、総和器、及び電流制御オシレータ(ICO)を含む。電圧−電流コンバータは、制御電圧を受け取り、そして第1電流と第2電流とを発生する。電流増幅器は、該第1電流を増幅しそしてフィルタし、そして第3電流を発生する。総和器は、該第2電流と該第3電流とを合算し、そして制御電流を発生する。ICOは、該制御電流を受け取り、そして該制御電流により決定される周波数を有するオシレータ信号を発生する。該電圧−電流コンバータ、該電流増幅器、及び該総和器は、例えば、電界効果型トランジスタ(FET)を用いて、効果的に与えられることができる。

【0009】

ある実施形態では、PLLは、上に説明されたVCO、分周器、位相−周波数検出器、及びループ・フィルタを含む。分周器は、該オシレータ信号を分周し、そしてフィードバック信号を供給する。位相−周波数検出器は、該フィードバック信号と基準信号との位相を比較し、そして検出器信号を供給する。該ループ・フィルタは、検出器信号をフィルタし、そして該制御電圧を供給する。PLLループ特性は、高速低利得パスにより与えられるより小さなVCO利得に基づいて設計されることができる。

【0010】

本発明の様々な態様及び実施形態は、下記にさらに詳細に記述される。

【図面の簡単な説明】

【0011】

【図1】古典的なPLLを示す図である。

【図2】大きなVCO利得を効率的に取り扱うことが可能な新規なPLLを示す図である。

【図3】電流モード・デュアル−パス電圧−電流コンバータを示す図である。

【図4A】図3のコンバータのs−ドメイン・モデルを示す図である。

【図4B】デュアル−パスVCO利得のプロットを示す図である。

【図5】デュアル−パスVCO利得を持つVCOを有するPLLの動作を示す図である。

【図6】無線デバイスのブロック図を示す図である。

【発明を実施するための形態】

【0012】

本発明の特徴及び本質は、図面を使用して以下に述べる詳細な説明から、さらに明確になるであろう。図面では、同じ参照符号は一貫して対応するものを識別する。

【0013】

用語“具体例の”は、“例、事例、又は実例として働くこと”を意味するように本明細書中では使用される。“具体例の”として本明細書中で記載されたどの実施形態又はデザインも、その他の実施形態又はデザインに対して好ましい又は優位であるとして解釈される必要はない。

【0014】

図1は、古典的なPLL100を示す図であり、それは位相−周波数検出器(PFD:phase-frequency detector)110、チャージ・ポンプ(CP:charge pump)120、ループ・フィルタ(LF:loop filter)130、電圧制御オシレータ(VCO:voltage-controlled oscillator)140、及び分周器170を含む。VCO140は、電圧−電流コンバータ(V2I)150及び電流制御オシレータ(ICO:current-controlled oscillator)160を含む。

【0015】

ICO160は、コンバータ150からの制御電流によって決定される周波数を有するオシレータ信号を発生する。分周器170は、オシレータ信号を係数Nで分周し、そしてフィードバック信号を供給する、ここで、N≧1である。位相−周波数検出器110は、基準信号とフィードバック信号とを受け取り、2つの信号の位相を比較し、そして2つの信号間の位相差/誤差を指示する検出器信号を供給する。チャージ・ポンプ120は、検出された位相誤差に比例する誤差信号を発生する。ループ・フィルタ130は、誤差信号をフィルタし、そしてVCO140に対する制御電圧を供給する。ループ・フィルタ130は、フィードバック信号の位相又は周波数が、基準信号の位相又は周波数に固定されるように制御電圧を調整する。コンバータ150は、制御電圧をICO160に対する制御電流に変換する。

【0016】

VCO140は、広い同調範囲を有することができ、そしてVCO利得は大きいことがある。様々なデザインが、大きなVCO利得を取り扱うために使用されることができる。1つの従来のデザインでは、ディジタル・キャリブレーションは、VCO周波数を中心に合わせるために実行されることができる。このデザインでは、基準電圧は、VCOに与えられ、そして基準電流に変換される。キャリブレーション電流は、ディジタル−アナログ・コンバータで発生され、そしてICOに対する制御電流を発生させるために基準電流と合算される。基準電圧は、VCOに対する公称(すなわち、中心)制御電圧を表す。キャリブレーション電流は、基準電圧の印加でICOが所望の周波数の近くで動作するように選択される。実際に、キャリブレーション電流は、ICOの周波数を中心に合わせるオフセットを与える。これは、次に小さな利得が電圧−電流コンバータに対して使用されることを可能にし、それは、通常動作の間のVCO利得を低減する。このデザインは、追加の回路、例えば、正確な(例えば、バンドギャップ)電圧基準、DAC、及びディジタル・キャリブレーション回路、を使用する。その上、キャリブレーションが電源投入時に1回だけ実行される場合には、キャリブレートされた周波数は、温度及び供給電圧変動のような動作環境の変化のためにドリフトすることがある。

【0017】

別の1つの従来のデザインでは、2つの制御電圧がVCOに対して発生される。このデザインでは、ループ・フィルタからの低利得制御電圧は、基準電圧に対して比較され、そして結果の誤差電圧は、高利得制御電圧を得るために統合される。基準電圧は、VCOに対する公称制御電圧を表す。高利得制御電圧は、ICOを所望の周波数に移動させるために使用される。実際に、高利得制御電圧は、VCOの周波数を中心に合わせるオフセットを与える。これは次に、より小さな利得が低利得制御電圧に使用されることを可能にし、それは通常動作の間のVCO利得を低減する。このデザインは、同様に追加の回路、例えば、正確な(例えば、バンドギャップ)電圧基準及び統合器を与えるための演算増幅器、を使用する。その上、低利得制御電圧に対するパスの帯域幅は、ループ安定性を確実にするためにそしてPLLループ・ダイナミックスを混乱させることを回避するために注意深く設計される必要がある。

【0018】

大きなVCO利得を効率的に取り扱うための新規な技術が本明細書中に説明される。その技術は、上に説明された従来デザインの欠点を回避しつつ良い性能を提供することが可能である。その技術は、2つのパス:高速低利得パスと並行して低速高利得パス:を利用することにより大きなVCO利得を取り扱う。高利得パスは、平均制御電流を与え、それはVCOの中心周波数を調節する。低利得パスは、瞬間的な制御電流すなわち高速制御電流を与え、それは通常動作の間VCO周波数を調節する。高利得パスは、大きなVCO利得に関係するが、遅く、そしてこのためにPLLループ・ダイナミックスに影響を及ぼさない。低利得パスは、より小さなVCO利得に関係し、通常動作の間に必然的に含まれ、そしてPLLループ・ダイナミックスに影響を及ぼす。

【0019】

図2は、大きなVCO利得を効率的に取り扱うことが可能な新規なPLL200の1実施形態のブロック図を示す。PLL200は、位相−周波数検出器210、チャージ・ポンプ220、ループ・フィルタ230、電圧制御オシレータ240、及び分周器270を含む。VCO240は、電流モード・デュアル−パス電圧−電流コンバータ250及び電流制御オシレータ260を含む。

【0020】

位相−周波数検出器210、チャージ・ポンプ220、ループ・フィルタ230及びICO260は、図1中のそれぞれ、位相−周波数検出器110、チャージ・ポンプ120、ループ・フィルタ130、及びICO160に対して上に記述されたように動作する。位相−周波数検出器210、チャージ・ポンプ220、及びループ・フィルタ230は、本技術において公知のいずれかのデザインを用いて与えられることができる。例えば、位相−周波数検出器210は、アーリー−レイト(early-late)検出器であり得て、それはフィードバック信号が基準信号に対して早いか遅れているかどうかを判断する。ループ・フィルタ230は、1次のループ・フィルタ又はある別のループ・フィルタであり得る。ICO260は、様々なオシレータ・デザイン(例えば、コルピッツ・オシレータ、リング・オシレータ、遅延ライン・オシレータ、及びその他)を用いて与えられることができ、そしてディジタル回路系、又はアナログ回路系、又は両方のタイプの回路系で与えられることができる。ICO260は、しかも高周波数(RF:radio frequency)、中間周波数(IF:intermediate frequency)及びその他のような任意の周波数で動作するように設計されることができる。ICO260のデザインは、ICOがそこで使用されるアプリケーションに依存することがある。例えば、ICO260は、ディジタル回路系のためのクロック信号を発生するオシレータであり得る。ICO260は、同様に周波数ダウンコンバージョン及び/又はアップコンバージョンのために使用されるLO信号を発生するRFオシレータであり得る。

【0021】

図2に示された実施形態では、コンバータ250は、電圧−電流コンバータ252、低帯域幅電流増幅器254、及び総和器256を含む。電圧−電流コンバータ252は、ループ・フィルタ230から制御電圧VCTRLを受け取り、そして第1電流I1と第2電流I2を発生する。一般に、第1電流I1は、第2電流I2に等しいか、それよりも大きいか、それよりも小さい。電流増幅器254は、mの利得で第1電流I1を増幅し、増幅された電流をフィルタし、そして第3電流I3を供給する。電流増幅器254は、低帯域幅を有し、そして通常動作の間PLLループ・ダイナミックスに影響を及ぼさない。総和器256は、第2電流I2と第3電流I3とを合算し、そしてICO260に対して制御電流ICTRLを供給する。

【0022】

図2に示された実施形態では、コンバータ250は、2つのパス:高速低利得パス280と低速高利得パス282を有する。この実施形態では、高速低利得パス280は、1の利得を有しそしてフィルタしない、そして低速高利得パス282は、mの利得そして低帯域幅電流増幅器254により与えられるフィルタリングを有する。VCO利得は、そのように2つのパスへと分割される。パス280は、低VCO利得パスに対応し、それは通常動作の間のVCOの瞬間的な周波数を調節する。パス282は、高VCO利得パスに対応し、それはVCOの中心周波数をゆっくりと調節する。VCO利得分割は、電圧−電流変換の後で行われる。これは、コンバータ250の効率的な実行を可能にし、そして下記に記述されるように、他の利点を提供することができる。

【0023】

図3は、電流モード・デュアル−パス電圧−電流コンバータ250aの概略図を示し、それは図2のコンバータ250の1実施形態である。この実施形態では、コンバータ250aは、電圧−電流コンバータ310、高速低利得電流ミラー320、及び低速高利得電流ミラー330を含む。コンバータ250aは、N−チャネル電界効果トランジスタ(N−FET)とP−チャネルFET(P−FET)の両者を有する相補型金属酸化膜半導体(CMOS:complementary metal oxide semiconductor)で与えられる。

【0024】

電圧−電流コンバータ310は、N−FET312と314を含み、それは並列に接続されそして回路のグランドに接続された自身のソースを有する。N−FET312と314のゲートは、一緒に接続され、そして図2のループ・フィルタ230から制御電圧VCTRLを受け取る。

【0025】

高速低利得電流ミラー320は、P−FET322と324を含み、それらは電流ミラーとして接続される。P−FET322は、電源供給電圧VDDに接続されたソース、自身のドレインに接続されたゲート、及びN−FET312のドレインに接続されたドレインを有する。P−FET324は、供給電圧に接続されたソース、P−FET322のゲートに接続されたゲート、及び電流合算ノードに接続されたドレインを有する。

【0026】

低速高利得電流ミラー330は、P−FET332と334を含み、それらは電流ミラーとして接続される。P−FET332は、供給電圧に接続されたソース、自身のドレインに接続されたゲート、及びN−FET314のドレインに接続されたドレインを有する。P−FET334は、供給電圧に接続されたソース、P−FET332のゲートに接続されたゲート、及び電流合算ノードに接続されたドレインを有する。キャパシタ326は、P−FET332と334のゲートに接続された1端子と、供給電圧に接続された別の端子を有する。電流合算ノードは、ICOのための制御電流ICTRLを供給する。

【0027】

電圧−電流コンバータ310に関して、N−FET312と314は、制御電圧VCTRLを受け取り、それぞれI1とI2のドレイン電流を発生する。ドレイン電流と制御電圧との間の変換関数は、N−FET312と314の特性により決定される。図3に示されたように、N−FET312と314とが1Xの同じ大きさでありそして同じゲート−ソース電圧VGSを有する場合には、I1はI2に等しい。

【0028】

電流ミラー320に関して、P−FET322のドレイン電流は、N−FET312のドレイン電流に等しい。P−FET324のドレイン電流は、P−FET322のドレイン電流に等しい、というのはP−FET322と324が1Xの同じ大きさと同じVGS電圧を有するからである。これゆえ、P−FET324は、電流合算ノードにI1のドレイン電流を供給する。電流ミラー320は、いかなる無効の素子(寄生素子を除く)をも含まず、そしてそれゆえ高速である。

【0029】

電流ミラー330に関して、P−FET332のドレイン電流は、N−FET314のドレイン電流に等しい。P−FET334のドレイン電流は、P−FET332のドレイン電流のm倍である、というのは2つのP−FETが同じVGS電圧を有し、そしてP−FET334がm・Xの大きさを有するのに対して、P−FET332は1Xの大きさを有するからである。P−FET334は、電流合算ノードにI3=m・I1のドレイン電流を供給する。電流ミラー330は、キャパシタ326を含み、それはP−FET332と334のゲートにおける電圧の速い変化を防止する。そのように、ドレイン電流I3は、キャパシタ326のサイズと他の因子により決定される遅いレートで変化する。

【0030】

図3は、少数のFETと1つのキャパシタを使用する電流モード・デュアル−パス電圧−電流コンバータ250aの有効な実施形態を示す。電圧−電流変換は、2つのN−FET312と314を用いて実行される。高速低利得パスは、2つのP−FET322と324とからなる第1電流ミラーを用いて与えられる。低速高利得パスは、2つのP−FET332と334及び1つのキャパシタ326からなる第2電流ミラーを用いて与えられる。第2電流ミラーは、mの一定利得での電流増倍を提供する。電流合算ノードは、P−FET324と334のドレイン電流を上手く合算し、そして制御電流を供給する。

【0031】

図3は、CMOSで実装される、電流モード・デュアル−パス電圧−電流コンバータ250の1つの実施形態を示す。一般に、コンバータ250は、様々なデザインで与えられることができる。電圧−電流変換、増幅、フィルタリング、及び合算機能は、複数の回路を用いて明示的に実行されることができる、又は非明示的に実行されることができる。例えば、電流合算は、複数の回路出力を一緒に接続することにより達成されることができる。複数の機能は、しかも所定の回路内に統合されることができる。例えば、2つの電流ミラーは、統合されることができ、そして第1電流と第2電流とが、明確に発生されることはない。

【0032】

図4Aは、電流モード・デュアル−パス電圧−電流コンバータ250のs−ドメイン・モデル400のブロック図を示す。モデル400では、図2の低速高利得パス282は、図4Aに示される変換関数を有するブロック410により表わされる。高速低利得パス280は、線412により表わされる。総和器256は、総和器414により表わされる。

【0033】

電流モード・デュアル−パス電圧−電流コンバータ250に対するデュアル−パスVCO利得は、次式のように表わされることができる:

【数1】

【0034】

ここで、ω0は図2の電流増幅器254の帯域幅であり、

Kvcoは高速低利得パスだけのVCO利得であり、そして

K’vcoは低速高利得パスと高速低利得パスの両方でのVCO利得である。

【0035】

K’vcoは、全ての周波数にわたり適用可能であるデュアル−パスVCO利得である。Kvcoは、より高い周波数において適用可能なVCO利得であり、そしてPLLループ・ダイナミックスに影響を及ぼす。

【0036】

電流増幅器254の帯域幅ω0は、図3のキャパシタ336のサイズとP−FET332の相互コンダクタンスにより決定される。好適な容量値は、所望の帯域幅を実現するために選択されることができる。利得mは、様々な要因に基づいて選択されることができ、例えば、所望の性能、回路実施態様、及びその他である。もしmが小さ過ぎる場合には、デュアル−パスVCO利得の利点は、最小であり得る。逆に、もしmが大き過ぎる場合には、(m+1)・ω0のところのゼロ位置は、高過ぎることがあり、それはPLL安定性に悪影響を与えることがある。ある実施形態では、8の値がmに対して使用される。その他の値も、mに対して同様に使用されることができる。

【0037】

図4Bは、式(1)のデュアル−パスVCO利得のプロットを示す。図4Bと式(1)に示されるように、電流増幅器254の加算は、PLLループ利得に1つのポールと1つのゼロを加算する、それはPLLの周りの総利得である。ポールは、ω0のところに位置し、そしてゼロは、(m+1)・ω0のところ位置する。低周波数において(例えば、s→0)、VCO利得は、(m+1)・Kvcoとして近似されることができる。この大きなVCO利得は、ICOに対する平均制御電流を発生するために使用される。高周波数において、VCO利得は、Kvcoとして近似されることができる。この小さい方のVCO利得は、ロック条件の近くで使用され、そしてジターを低減することを助ける。PLLループ安定性は、(m+1)・ω0がPLLループ利得帯域幅よりもはるかに小さくなるようにそして好ましくはループ・フィルタ230の前記ゼロよりも低くなるように設計することにより保証されることができる。

【0038】

図5は、デュアル−パスVCO利得を持つVCOを有するPLLを動作させるためのプロセス500の1つの実施形態を示す。ブロック510は、VCOの動作を示し、そしてブロック520は、残りのPLLの動作を示す。

【0039】

ブロック510のVCOに関して、第1電流と第2電流は、制御電圧に基づいて発生される(ブロック512)。第1電流は、増幅されそしてフィルタされて、第3電流を発生する(ブロック514)。第2電流と第3電流は、合算されて、制御電流を発生する(ブロック516)。オシレータ信号は、制御電流によって決定される周波数を有するように発生される(ブロック518)。ブロック512,514と516は、図2のコンバータ250により実行されることができる。ブロック518は、ICO260により実行されることができる。

【0040】

ブロック520の残りのPLLに関して、オシレータ信号は、フィードバック信号を発生するために分周される(ブロック522)。フィードバック信号と基準信号の位相は、検出器信号を発生するために比較される(ブロック524)。検出器信号は、制御電圧を発生させるためにループ・フィルタを用いてフィルタされる(ブロック526)。ブロック522,524と526は、図2のそれぞれ、分周器270、位相−周波数検出器210、そしてループ・フィルタ230により実行されることができる。チャージ・ポンプ220は、位相−周波数検出器210の一部として考えられることができる。

【0041】

本明細書中に記述される技術は、制御電圧を電圧−電流変換した後でVCO利得を低速高利得パスと高速低利得パスへと分けることによって広い同調範囲と大きなVCO利得の問題に対処する。広い同調範囲は、VCOに対する平均制御電流を供給する低速高利得パスでサポートされる。高速低利得パスは、ロック条件の近くで使用されるより小さなVCO利得を供給する。より小さなVCO利得は、より小さなループ・フィルタ帯域幅の使用を可能にし、それはPLLループ安定性を改善する。より小さなVCO利得は、しかもオシレータ信号におけるより小さなジターを結果としてもたらす。低速高利得パスと高速低利得パスとの間の利得比mは、固定でありそして満足のいくように決められる。この公知の関係は、他のPLLループ・パラメータを決めることを容易にする。それに加えて、外部電圧基準は、この新規な技術で必要とされない。

【0042】

本明細書中に記述された技術は、各種の低電圧アプリケーションに対して有利に使用されることができる。低電源電圧は、電力消費量削減を助けるために多くの電子回路に対して一般的に使用される。低電力消費は、バッテリーで電源を供給される携帯デバイスに対して特に好ましい。しかしながら、低供給電圧は、制御電圧範囲を同様に制限し、それは大きなVCO利得問題をさらにはっきりとさせる。本明細書中に記述される技術は、大きなVCO利得を取り扱うことが可能であり、それは低電圧アプリケーションにおいてより過酷になり得る。

【0043】

本明細書中に記述された技術は、様々な電子回路に対して使用されることができる。無線通信デバイスに対する本技術の使用が、下記に述べられる。

【0044】

図6は、無線通信システムにおける無線デバイス600の1つの実施形態のブロック図を示す。無線デバイス600は、セルラ電話機、端末、PDA、ハンドセット、又はある他のデバイス又はデザインであり得る。無線通信システムは、符号分割多元接続(CDMA:Code Division Multiple Access)システム、時分割多元接続(TDMA:Time Division Multiple Access)システム、周波数分割多元接続(FDMA:Frequency Division Multiple Access)システム、移動通信のためのグローバル・システム(GMS:Global System for Mobile Communications)システム、直交周波数分割多元接続(OFDMA:Orthogonal Frequency Division Multiple Access)システム、等であり得る。

【0045】

無線デバイス600は、ディジタル・プロセッサ610とトランシーバ630を含み、それは双方向通信をサポートする。ディジタル・プロセッサ610は、1又はそれより多くの用途特定集積回路(ASIC:application specific integrated circuit)を用いて与えられることができ、そしてトランシーバ630は、1又はそれより多くのRF集積回路(RFIC:RF integrated circuit)を用いて与えられることができる。

【0046】

ディジタル・プロセッサ610の内部で、エンコーダ612は、送信されるデータを処理し(例えば、フォーマット化し、エンコードし、そしてインターリーブし)、そして変調器(Mod)614は、コード化されたデータをさらに処理して(例えば、変調し、そしてスクランブルして)データ・チップを生成する。トランシーバ630の内部で、送信(TX)ベースバンド・ユニット632は、ベースバンド処理、例えば、ディジタル−アナログ変換、フィルタリング、増幅、及びその他、を実行する。ミキサ634は、ベースバンド信号をRFへアップコンバートする。TX RFユニット636は、信号調整、例えば、フィルタリング及び強度増幅、を実行して、RF変調された信号を発生する、その信号はアンテナ640を介して送信される。データ受信に関して、受信(RX)RFユニット642は、アンテナ640から入力RF信号を受信し、そして信号調整、例えば、低雑音増幅及びフィルタリングを実行する。ミキサ644は、調整されたRF信号をRFからベースバンドにダウンコンバートする。RFベースバンド・ユニット646は、ベースバンド処理、例えば、フィルタリング、増幅、アナログ−ディジタル変換、等、を実行する。復調器(Dmod)616は、ユニット646からの入力サンプルを処理し(例えば、逆スクランブルし、そして復調し)そしてシンボル推定値を与える。デコーダ618は、シンボル推定値を処理し(例えば、逆インターリーブし、そしてデコードし)そしてデコードされたデータを与える。一般に、データ・プロセッサ610とトランシーバ630による処理は、無線システムのデザインに依存する。

【0047】

プロセッサ620は、様々なアプリケーション、例えば、ビデオ、オーディオ、グラフィックス、等、をサポートすることができる。コントローラ/プロセッサ660は、無線デバイス600内の様々な処理ユニットの動作を管理する。メモリ662は、無線デバイス600のためのプログラム・コードとデータを記憶する。

【0048】

VCO/PLL622は、ディジタル・プロセッサ610内の処理ユニットに対するクロック信号を発生する。VCO/PLL650は、周波数アップコンバージョンのためにミキサ634によって使用される送信LO信号と周波数ダウンコンバージョンのためにミキサ644によって使用される受信LO信号とを発生する。VCO622及び/又はVCO650は、大きなVCO利得を有することがあり、そして本明細書中に記述された技術を利用することができる。電流モード・デュアル−パス電圧−電流コンバータは、VCO622に対して使用されることができ、VCO利得を2つのパスへと分け、その結果、平均VCO周波数は低速高利得パスを用いて制御されることができ、そして瞬間的なVCO周波数は高速低利得パスを用いて調節されることができる。電流モード・デュアル−パス電圧−電流コンバータは、VCO650に対しても同様に使用されることができる。基準オシレータ664は、VCO/PLL622及び/又はVCO/PLL650に対する基準信号を発生する。基準オシレータ644は、水晶発振器(XO:crystal oscillator)、電圧制御XO(VCXO)、温度補償XO(TCXO)、又はある別のタイプのオシレータであり得る。

【0049】

本明細書中に記述されたVCOとPLLは、アナログIC、RFIC、ASIC、ディジタル信号プロセッサ(DSP)、ディジタル信号処理デバイス(DSPD)、プログラマブル論理デバイス(PLD)、フィールド・プログラマブル・ゲート・アレイ(FPGA)、プロセッサ、コントローラ、マイクロ−コントローラ、マイクロプロセッサ、及び他の電子ユニット、で与えられることができる。VCOとPLLは、例えば、N−MOS,P−MOS,CMOS,BJT,GaAs,及びその他のような、様々なICプロセスで与えられることができる。VCOとPLLは、単体構成素子を用いて同様に与えられることができる。

【0050】

開示された実施形態のこれまでの説明は、当業者が、本発明を作成する又は使用することを可能にするために提供される。これらの実施形態への様々な変形は、当業者に容易に明白にされるであろう、そして、ここで規定された一般的な原理は、本発明の精神又は範囲から逸脱することなく他の実施形態に適用されることができる。それゆえ、本発明は、本明細書中に示された実施形態に制限することを意図したものではなく、本明細書中に開示した原理及び新奇な機能と整合する最も広い範囲に適用されるものである。

【特許請求の範囲】

【請求項1】

制御電圧を受け取るため、そして第1電流と第2電流とを発生させるために構成された電圧−電流コンバータと、

該第1電流を増幅しフィルタするため、そして第3電流を発生させるために構成された電流増幅器と、

該第2電流と該第3電流とを合算して、制御電流を発生させるために構成された総和器と、及び

該制御電流を受け取り、そして該制御電流により決定される周波数を有するオシレータ信号を発生させるために構成された電流制御オシレータ(ICO)と、

を具備する集積回路。

【請求項2】

該電流増幅器は、一定の係数mだけ該第1電流を増幅するために構成される、ここで、mは1より大きい、請求項1の集積回路。

【請求項3】

該電流増幅器は、

該第2電流を受け取るため、そして該第3電流を供給するために構成された電流ミラーを具備する、請求項1の集積回路。

【請求項4】

該電流増幅器は、該第1電流に対するフィルタリングを提供するために構成されたキャパシタをさらに具備する、請求項3の集積回路。

【請求項5】

該総和器は、該電圧−電流コンバータと該電流増幅器との出力に対する合算ノードにより形成される、請求項1の集積回路。

【請求項6】

該電圧−電流コンバータと該電流増幅器は、電界効果型トランジスタ(FET)を用いて与えられる、請求項1の集積回路。

【請求項7】

該オシレータ信号を分周するため、そしてフィードバック信号を供給するために構成された分周器と、

該フィードバック信号と基準信号との位相を比較するため、そして検出器信号を供給するために構成された位相−周波数検出器と、及び

該検出器信号をフィルタするため、そして該制御電圧を供給するために構成されたループ・フィルタと、

をさらに具備する、請求項1の集積回路。

【請求項8】

該ループ・フィルタは、第1帯域幅を有し、そして該電流増幅器は、該第1帯域幅よりも狭い第2帯域幅を有する、請求項7の集積回路。

【請求項9】

制御電圧に基づいて第1電流と第2電流とを発生させること、

第3電流を発生させるために該第1電流を増幅することそしてフィルタすること、

制御電流を発生させるために該第2電流と該第3電流とを合算することと、及び

該制御電流により決定される周波数を有するオシレータ信号を発生させることと、

を具備する方法。

【請求項10】

フィードバック信号を発生させるために該オシレータ信号を分周することと、

検出器信号を発生させるために該フィードバック信号と基準信号との位相を比較することと、及び

該制御電圧を発生させるために該検出器信号をフィルタすることと、

をさらに具備する、請求項9の方法。

【請求項11】

制御電圧に基づいて第1電流と第2電流とを発生させるための手段と、

第3電流を発生させるために該第1電流を増幅するためそしてフィルタするための手段と、

制御電流を発生させるために該第2電流と該第3電流とを合算するための手段と、及び

該制御電流により決定される周波数を有するオシレータ信号を発生させるための手段と、

を具備する装置。

【請求項12】

フィードバック信号を発生させるために該オシレータ信号を分周するための手段と、

検出器信号を発生させるために該フィードバック信号と基準信号との位相を比較するための手段と、及び

該制御電圧を発生させるために該検出器信号をフィルタするための手段と、

をさらに具備する、請求項11の装置。

【請求項13】

制御電圧を受け取るため、低速高利得パスを介して第1電流を発生させるため、高速低利得パスを介して第2電流を発生させるため、そして制御電流を発生させるために該第1電流と該第2電流とを合算するため、に構成されたコンバータと及び

該制御電流を受け取るため、そして該制御電流により決定される周波数を有するオシレータ信号を発生させるために構成された電流制御オシレータ(ICO)と、

を具備する集積回路。

【請求項14】

該低速高利得パスは、該高速低利得パスに対して相対的に一定の利得係数mを有する、ここで、mは1より大きい、請求項13の集積回路。

【請求項15】

基準信号と該オシレータ信号を受け取るため、そして該オシレータ信号の該周波数が該基準信号の周波数に固定されるように該制御信号を発生させるため、に構成された位相固定ループ、

をさらに具備する、請求項13の集積回路。

【請求項16】

制御電圧を受け取るため、低速高利得パスを介して第1電流を発生させるため、高速低利得パスを介して第2電流を発生させるため、そして制御電流を発生させるために該第1電流と該第2電流とを合算するため、に構成されたコンバータ;及び

該制御電流を受け取るため、そして該制御電流により決定される周波数を有するオシレータ信号を発生させるために構成された電流制御オシレータ(ICO)、

を具備する無線デバイス。

【請求項17】

該低速高利得パスは、該高速低利得パスに対して相対的に一定の利得係数mを有する、ここで、mは1より大きい、請求項16の無線デバイス。

【請求項18】

基準信号と該オシレータ信号を受け取るため、そして該オシレータ信号の該周波数が該基準信号の周波数に固定されるように該制御信号を発生させるため、に構成された位相固定ループをさらに具備する、請求項16の無線デバイス。

【請求項19】

該オシレータ信号は、ディジタル回路系に対するクロック信号を発生させるために使用される、請求項16の無線デバイス。

【請求項20】

該オシレータ信号は、送信機において周波数アップコンバージョンのため又は受信機において周波数ダウンコンバージョンのために使用される、請求項16の無線デバイス。

【請求項1】

制御電圧を受け取るため、そして第1電流と第2電流とを発生させるために構成された電圧−電流コンバータと、

該第1電流を増幅しフィルタするため、そして第3電流を発生させるために構成された電流増幅器と、

該第2電流と該第3電流とを合算して、制御電流を発生させるために構成された総和器と、及び

該制御電流を受け取り、そして該制御電流により決定される周波数を有するオシレータ信号を発生させるために構成された電流制御オシレータ(ICO)と、

を具備する集積回路。

【請求項2】

該電流増幅器は、一定の係数mだけ該第1電流を増幅するために構成される、ここで、mは1より大きい、請求項1の集積回路。

【請求項3】

該電流増幅器は、

該第2電流を受け取るため、そして該第3電流を供給するために構成された電流ミラーを具備する、請求項1の集積回路。

【請求項4】

該電流増幅器は、該第1電流に対するフィルタリングを提供するために構成されたキャパシタをさらに具備する、請求項3の集積回路。

【請求項5】

該総和器は、該電圧−電流コンバータと該電流増幅器との出力に対する合算ノードにより形成される、請求項1の集積回路。

【請求項6】

該電圧−電流コンバータと該電流増幅器は、電界効果型トランジスタ(FET)を用いて与えられる、請求項1の集積回路。

【請求項7】

該オシレータ信号を分周するため、そしてフィードバック信号を供給するために構成された分周器と、

該フィードバック信号と基準信号との位相を比較するため、そして検出器信号を供給するために構成された位相−周波数検出器と、及び

該検出器信号をフィルタするため、そして該制御電圧を供給するために構成されたループ・フィルタと、

をさらに具備する、請求項1の集積回路。

【請求項8】

該ループ・フィルタは、第1帯域幅を有し、そして該電流増幅器は、該第1帯域幅よりも狭い第2帯域幅を有する、請求項7の集積回路。

【請求項9】

制御電圧に基づいて第1電流と第2電流とを発生させること、

第3電流を発生させるために該第1電流を増幅することそしてフィルタすること、

制御電流を発生させるために該第2電流と該第3電流とを合算することと、及び

該制御電流により決定される周波数を有するオシレータ信号を発生させることと、

を具備する方法。

【請求項10】

フィードバック信号を発生させるために該オシレータ信号を分周することと、

検出器信号を発生させるために該フィードバック信号と基準信号との位相を比較することと、及び

該制御電圧を発生させるために該検出器信号をフィルタすることと、

をさらに具備する、請求項9の方法。

【請求項11】

制御電圧に基づいて第1電流と第2電流とを発生させるための手段と、

第3電流を発生させるために該第1電流を増幅するためそしてフィルタするための手段と、

制御電流を発生させるために該第2電流と該第3電流とを合算するための手段と、及び

該制御電流により決定される周波数を有するオシレータ信号を発生させるための手段と、

を具備する装置。

【請求項12】

フィードバック信号を発生させるために該オシレータ信号を分周するための手段と、

検出器信号を発生させるために該フィードバック信号と基準信号との位相を比較するための手段と、及び

該制御電圧を発生させるために該検出器信号をフィルタするための手段と、

をさらに具備する、請求項11の装置。

【請求項13】

制御電圧を受け取るため、低速高利得パスを介して第1電流を発生させるため、高速低利得パスを介して第2電流を発生させるため、そして制御電流を発生させるために該第1電流と該第2電流とを合算するため、に構成されたコンバータと及び

該制御電流を受け取るため、そして該制御電流により決定される周波数を有するオシレータ信号を発生させるために構成された電流制御オシレータ(ICO)と、

を具備する集積回路。

【請求項14】

該低速高利得パスは、該高速低利得パスに対して相対的に一定の利得係数mを有する、ここで、mは1より大きい、請求項13の集積回路。

【請求項15】

基準信号と該オシレータ信号を受け取るため、そして該オシレータ信号の該周波数が該基準信号の周波数に固定されるように該制御信号を発生させるため、に構成された位相固定ループ、

をさらに具備する、請求項13の集積回路。

【請求項16】

制御電圧を受け取るため、低速高利得パスを介して第1電流を発生させるため、高速低利得パスを介して第2電流を発生させるため、そして制御電流を発生させるために該第1電流と該第2電流とを合算するため、に構成されたコンバータ;及び

該制御電流を受け取るため、そして該制御電流により決定される周波数を有するオシレータ信号を発生させるために構成された電流制御オシレータ(ICO)、

を具備する無線デバイス。

【請求項17】

該低速高利得パスは、該高速低利得パスに対して相対的に一定の利得係数mを有する、ここで、mは1より大きい、請求項16の無線デバイス。

【請求項18】

基準信号と該オシレータ信号を受け取るため、そして該オシレータ信号の該周波数が該基準信号の周波数に固定されるように該制御信号を発生させるため、に構成された位相固定ループをさらに具備する、請求項16の無線デバイス。

【請求項19】

該オシレータ信号は、ディジタル回路系に対するクロック信号を発生させるために使用される、請求項16の無線デバイス。

【請求項20】

該オシレータ信号は、送信機において周波数アップコンバージョンのため又は受信機において周波数ダウンコンバージョンのために使用される、請求項16の無線デバイス。

【図1】

【図2】

【図3】

【図4A】

【図4B】

【図5】

【図6】

【図2】

【図3】

【図4A】

【図4B】

【図5】

【図6】

【公開番号】特開2012−186813(P2012−186813A)

【公開日】平成24年9月27日(2012.9.27)

【国際特許分類】

【外国語出願】

【出願番号】特願2012−65310(P2012−65310)

【出願日】平成24年3月22日(2012.3.22)

【分割の表示】特願2008−550527(P2008−550527)の分割

【原出願日】平成19年1月11日(2007.1.11)

【出願人】(595020643)クゥアルコム・インコーポレイテッド (7,166)

【氏名又は名称原語表記】QUALCOMM INCORPORATED

【Fターム(参考)】

【公開日】平成24年9月27日(2012.9.27)

【国際特許分類】

【出願番号】特願2012−65310(P2012−65310)

【出願日】平成24年3月22日(2012.3.22)

【分割の表示】特願2008−550527(P2008−550527)の分割

【原出願日】平成19年1月11日(2007.1.11)

【出願人】(595020643)クゥアルコム・インコーポレイテッド (7,166)

【氏名又は名称原語表記】QUALCOMM INCORPORATED

【Fターム(参考)】

[ Back to top ]