電流センサ

【課題】ダストコアを用いても精度良く測定できる電流センサを提供する。

【解決手段】ダストコア(圧粉磁心)によって形成された磁気ヨーク2を使用する電流センサ1において、磁気ヨーク2は、バスバー4に流れる電流によって生じる磁路上にギャップ長を含みつつ、バスバー4を取り囲み、当該ギャップ長を構成するギャップにホール素子3が設けられている。そして、磁路の磁束密度がB−H曲線の直線領域内に制限されるように全磁路長(Ly+Lg)に対するギャップ長(Lg)の割合が設定されている。

【解決手段】ダストコア(圧粉磁心)によって形成された磁気ヨーク2を使用する電流センサ1において、磁気ヨーク2は、バスバー4に流れる電流によって生じる磁路上にギャップ長を含みつつ、バスバー4を取り囲み、当該ギャップ長を構成するギャップにホール素子3が設けられている。そして、磁路の磁束密度がB−H曲線の直線領域内に制限されるように全磁路長(Ly+Lg)に対するギャップ長(Lg)の割合が設定されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ホール素子を用いた電流センサに関する。

【背景技術】

【0002】

ホール素子を用いた電流センサは、電流が流れる導体を取り囲むように、鋼板(電磁鋼板)で形成された磁気ヨークが設けられ、その磁路上のギャップにホール素子が介挿された構成となっている(例えば、特許文献1参照。)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−58451号公報(図1)

【発明の概要】

【発明が解決しようとする課題】

【0004】

上記のような従来の電流センサに使用される磁気ヨーク用の鋼板は、比較的高価であり、コストダウンのためにダストコア(圧粉磁心)の採用が検討されている。ところが、鋼板に比べてダストコアは飽和磁束密度が低く、そのため、ダストコアを用いた電流センサで電流(特に大電流)を測定しようとすると精度が悪くなる。

【0005】

かかる従来の問題点に鑑み、本発明は、ダストコアを用いても電流を精度良く測定できる電流センサを提供することを目的とする。

【課題を解決するための手段】

【0006】

(1)本発明の電流センサは、ダストコアによって形成され、導体に流れる電流によって生じる磁路上にギャップ長を含みつつ、当該導体を取り囲む磁気ヨークと、前記ギャップ長を構成するギャップに設けられるホール素子と、を備え、前記磁路の磁束密度がB−H曲線の直線領域内に制限されるように全磁路長に対する前記ギャップ長の割合を設定した。

上記のように構成された電流センサでは、ホール素子が、B−H曲線の直線領域すなわち、直線性に優れた領域で使用されるので、安価なダストコアを用いても精度を損なわずに電流検出を行うことができる。

【0007】

(2)また、上記(1)の電流センサにおいて、割合は10%〜30%の範囲内であることが好ましい。

この場合、ホール素子を、直線性に優れた領域で、かつ、出力が低下し過ぎない範囲で使用することができる。

【0008】

(3)また、上記(1)又は(2)の電流センサにおいて、割合は、磁路上の複数個所に設けられたギャップの長さの総和として確保することもできる。

この場合、全磁路長に対するギャップ長の割合を複数個所のギャップで確保することができるので、磁気ヨークの形態に関して、ギャップを確保するための種々の設計が可能となる。

【0009】

(4)また、上記(1)〜(3)のいずれかの電流センサにおいて、割合は、鋼板コアによって形成された磁気ヨークの場合より大きく設定され、それにより生じ得るホール素子の相対的な出力低下を、駆動電流増大によって抑制するようにしてもよい。

ホール素子の出力が低下した場合は、例えば増幅回路の利得を高めて低下を補う必要があるが、そうすると、ノイズも増幅される。しかし、ホール素子の駆動電流を増大すれば、増幅回路の利得を高めなくてもホール素子自身で、出力低下を抑制することができる。

【発明の効果】

【0010】

本発明の電流センサによれば、ダストコアを用いても電流を精度良く測定することができる。

【図面の簡単な説明】

【0011】

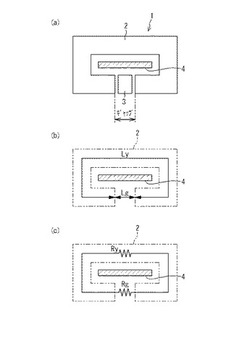

【図1】(a)は、本発明の一実施形態に係る電流センサの概略図であり、(b)は磁路長を示す図、(c)は磁気抵抗を示す図である。

【図2】磁気回路におけるB−H曲線の一例である。

【図3】ホール素子の付属回路を示す図である。

【図4】B−H曲線のヒステリシスを示すグラフであり、(a)は比較例として直線性の良くない領域まで使用する場合のヒステリシス特性を示し、(b)は本実施形態の如く直線性の良い領域のみを使用する場合のヒステリシス特性を示している。

【図5】所定の磁気ヨークについて、ギャップ長を種々変化させ、電流検出の精度を決める直線性について調べた結果を示すグラフである。

【図6】複数個所にギャップを設けた磁気ヨークの一例を示す図である。

【発明を実施するための形態】

【0012】

図1の(a)は、本発明の一実施形態に係る電流センサの概略図である。また、(b)は磁路長を示す図、(c)は磁気抵抗を示す図である。

図1において、この電流センサ1は、例えば、PWM変調された交流の大電流(例えば数十〜数百アンペア)が流れるバスバー4の電流測定用に設けられるものである。バスバー4は、例えば、電気自動車のインバータとモータとを繋ぐ導体のうちの1本である。

【0013】

電流センサ1は、磁気ヨーク2と、ホール素子3とを備えている。磁気ヨーク2はダストコア(圧粉磁心)によって形成されている。

(b)に示すように、導体であるバスバー4に流れる電流によって磁路が形成される。全磁路長は、磁気ヨーク2内の磁路長Lyと、ギャップ長(=ギャップの磁路長)Lgとの和である。すなわち、磁気ヨーク2は、磁路(Ly+Lg)上にギャップ長Lgを含みつつ、バスバー4を図示のように取り囲んでいる。ギャップとなる空間には、ホール素子3が装着される。なお、磁気ヨーク2内の磁路長Lyは、厚み(内周−外周)の中間を通る長さとして定義されるものとする。

【0014】

ここで、磁気ヨーク2の比透磁率をμy、断面積をSとする。また、ギャップの比透磁率を1とする。なお、ギャップとなる空間領域の、磁路に直交する面積も同様にSである。真空の透磁率をμ0とすると、磁気ヨーク2のみの磁気抵抗Ryは、

Ry=Ly/(μy・μ0・S) ・・・(1)

と表される。一方、ギャップの磁気抵抗Rgは、

Rg=Lg/(μ0・S) ・・・(2)

と表される。

【0015】

従って、式(1)、(2)より、磁気回路の総磁気抵抗Rは、

R=Ry+Rg

=Ly/(μy・μ0・S)+Lg/(μ0・S)

=(Ly/μy+Lg)/(μ0・S) ・・・(3)

となる。バスバー4を流れる電流によって生じる起磁力をFとすると、磁気回路内の磁束Φは、

Φ=F/R ・・・(4)

である。また、磁束密度Bは、式(3)、(4)より、

B=Φ/S=μ0・F/(Ly/μy+Lg) ・・・(5)

となる。

【0016】

上記の式(5)より、磁束密度Bは、ギャップの磁路長Lgに概ね反比例する。従って、ギャップの磁路長Lgを、鋼板の場合よりも相対的に大きく取ることで、B−H曲線における非飽和領域(直線性の良い領域)を使用することができる。具体的には、鋼板の磁気ヨークの場合は通常、Lg/(Ly+Lg)が約5%と、比較的小さい値であるのに対して、上記実施形態の場合はLg/(Ly+Lg)が10%以上で30%以下の、比較的大きい値とする。

【0017】

図2は、磁気回路におけるB−H曲線の一例である。電流増大に伴って磁界Hが強くなるほど磁束密度Bも増大する。このとき、領域A1では、B−H曲線はほぼ直線で、B−Hは比例関係にある。しかし、磁束密度Bは、値B1を超えると勾配が鈍化し、値B2で飽和する。従って、領域A2では直線性が損なわれる。ギャップが小さい(例えば5%)場合、磁束密度Bが領域A2にまで達するので、直線性が良くない領域A2でもホール素子3は電流検出を行うことになり、結果的に検出の精度が悪くなる。一方、ギャップが大きい(10%以上)場合、測定対象が同じ電流範囲であっても磁束密度Bは領域A2に到達せず、領域A1にとどまる。従って、ホール素子3は、直線性の良い領域A1でのみ電流検出を行うことになり、検出の精度が良い。

【0018】

ダストコアの場合、Lg/(Ly+Lg)が10%以上であれば、確実に、直線性の良い領域でホール素子3を使用することができる。10%に満たない場合は、磁束密度BがB1を超えて領域A2に入る可能性がある。5%では確実に領域A2に入り、最大電流に対しては磁気飽和に至る。なお、ギャップの割合が全磁路長の30%を超える場合には、ホール素子3の出力が低下し過ぎて好ましくない。

【0019】

図3は、ホール素子3の付属回路(又は周辺回路)を示す図である。ホール素子3では、磁束密度B、駆動回路31による駆動電流IC、出力電圧VHが、方向性において互いに直交する関係にある。出力電圧VHは、増幅回路32によって増幅される。磁束密度Bの方向へのホール素子3の厚さをd、電子の電荷をe、ホール素子3を構成する半導体のキャリア密度をn、ホール係数をRHとすると、

RH=1/(e・n) ・・・(6)

VH=(RH/d)・IC・B ・・・(7)

となる。

【0020】

上記の式(7)において、ホール係数RH及び厚さdは共に定数となるので、出力電圧VHは、駆動電流ICと磁束密度Bとの積に比例する。駆動電流ICが一定で、ギャップを大きくすることによって磁束密度Bが低下すると出力電圧VHが低下するが、ギャップを大きく取っても、駆動電流ICを増大させることによって、出力電圧VHの低下を抑制することができる。

【0021】

なお、ギャップを大きく取った場合に、駆動電流ICを増大させることなく、増幅回路32の利得を大きくすることによっても所要の出力を得ることは可能であるが、この場合、増幅回路32への入力に混入するノイズも増幅することになるので、その点でも、駆動電流ICを増大させることが好ましい。

また、ホール素子3の半導体の種類としては、例えば、InSb、InAs、Si、GaAsがある。温度に対する出力電圧VHの安定性の観点では、GaAsが好適である。

【0022】

図4は、B−H曲線のヒステリシスを示すグラフであり、(a)は比較例として直線性の良くない領域まで使用する場合のヒステリシス特性を示し、(b)は本実施形態の如く直線性の良い領域のみを使用する場合のヒステリシス特性を示している。(a)の場合、磁気飽和の影響により、ヒステリシスループは大きくなる。これに対して、(b)の場合、磁気飽和しないので、ヒステリシスループは小さくなる。(a)のヒステリシス[%]を(Br1/Bm1)、(b)のヒステリシス[%]を(Br2/Bm2)とすると、

(Br1/Bm1)>(Br2/Bm2)

であり、ギャップを大きく取ることによりヒステリシスは改善される。

【0023】

ここで、所定の磁気ヨークについて、ギャップ長を種々変化させ、電流検出の精度を決める直線性と、ヒステリシスとについて調べた結果を、図5のグラフ及び表1に示す。ギャップ長は、3mmから8mmまで1mmずつ変化させた。これらのギャップ長の、全磁路長に対する割合は、以下の通りである。

【0024】

3mm →4.66%

4mm →6.21%

5mm →7.76%

6mm →9.32%

7mm →10.87%

8mm →12.42%

【0025】

図5において、横軸は電流を示し、縦軸はホール素子3による電流検出のフルスケールに対する誤差すなわち、直線性に対する誤差[%]を示している。グラフにより明らかなように、直線性は、3mmの場合が最も悪く、ギャップ長が増大するほど直線性が良くなり、3〜8mmの範囲では、8mmの場合が最も良い、という結果となっている。

【0026】

【表1】

【0027】

また、上記の表1より、ヒステリシスに関しても、3〜8mmの範囲では、8mmの場合が最も良い結果となっている。磁束密度Bはギャップ長が長いほど小さくなるので、前述のように、ホール素子3の駆動電流ICを増大して出力電圧VHを確保することが必要である。

【0028】

以上のように、本実施形態に係る電流センサ1では、ホール素子3が、B−H曲線の直線領域すなわち、直線性に優れた領域で使用されるので、安価なダストコアを用いても精度を損なわずに電流検出を行うことができる。従って、ダストコアを用いても精度良く測定できる電流センサ1を提供することができる。

【0029】

なお、ギャップ長は、必ずしも一個所で確保しなくてもよい。図6は、複数個所にギャップを設けた磁気ヨーク2の一例を示す図である。この場合、ギャップ長は、(Lg1+Lg2)となる。すなわち、全磁路長に対するギャップ長の割合は、磁路上の複数個所に設けられたギャップの長さの総和として確保することができる。これにより、磁気ヨーク2の形態に関して、ギャップを確保するための種々の設計が可能となる。

【0030】

なお、今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は特許請求の範囲によって示され、特許請求の範囲と均等の意味及び範囲内での全ての変更が含まれることが意図される。

【符号の説明】

【0031】

1 電流センサ

2 磁気ヨーク

3 ホール素子

4 バスバー(導体)

(Ly+Lg) 全磁路長

Lg ギャップ長

【技術分野】

【0001】

本発明は、ホール素子を用いた電流センサに関する。

【背景技術】

【0002】

ホール素子を用いた電流センサは、電流が流れる導体を取り囲むように、鋼板(電磁鋼板)で形成された磁気ヨークが設けられ、その磁路上のギャップにホール素子が介挿された構成となっている(例えば、特許文献1参照。)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−58451号公報(図1)

【発明の概要】

【発明が解決しようとする課題】

【0004】

上記のような従来の電流センサに使用される磁気ヨーク用の鋼板は、比較的高価であり、コストダウンのためにダストコア(圧粉磁心)の採用が検討されている。ところが、鋼板に比べてダストコアは飽和磁束密度が低く、そのため、ダストコアを用いた電流センサで電流(特に大電流)を測定しようとすると精度が悪くなる。

【0005】

かかる従来の問題点に鑑み、本発明は、ダストコアを用いても電流を精度良く測定できる電流センサを提供することを目的とする。

【課題を解決するための手段】

【0006】

(1)本発明の電流センサは、ダストコアによって形成され、導体に流れる電流によって生じる磁路上にギャップ長を含みつつ、当該導体を取り囲む磁気ヨークと、前記ギャップ長を構成するギャップに設けられるホール素子と、を備え、前記磁路の磁束密度がB−H曲線の直線領域内に制限されるように全磁路長に対する前記ギャップ長の割合を設定した。

上記のように構成された電流センサでは、ホール素子が、B−H曲線の直線領域すなわち、直線性に優れた領域で使用されるので、安価なダストコアを用いても精度を損なわずに電流検出を行うことができる。

【0007】

(2)また、上記(1)の電流センサにおいて、割合は10%〜30%の範囲内であることが好ましい。

この場合、ホール素子を、直線性に優れた領域で、かつ、出力が低下し過ぎない範囲で使用することができる。

【0008】

(3)また、上記(1)又は(2)の電流センサにおいて、割合は、磁路上の複数個所に設けられたギャップの長さの総和として確保することもできる。

この場合、全磁路長に対するギャップ長の割合を複数個所のギャップで確保することができるので、磁気ヨークの形態に関して、ギャップを確保するための種々の設計が可能となる。

【0009】

(4)また、上記(1)〜(3)のいずれかの電流センサにおいて、割合は、鋼板コアによって形成された磁気ヨークの場合より大きく設定され、それにより生じ得るホール素子の相対的な出力低下を、駆動電流増大によって抑制するようにしてもよい。

ホール素子の出力が低下した場合は、例えば増幅回路の利得を高めて低下を補う必要があるが、そうすると、ノイズも増幅される。しかし、ホール素子の駆動電流を増大すれば、増幅回路の利得を高めなくてもホール素子自身で、出力低下を抑制することができる。

【発明の効果】

【0010】

本発明の電流センサによれば、ダストコアを用いても電流を精度良く測定することができる。

【図面の簡単な説明】

【0011】

【図1】(a)は、本発明の一実施形態に係る電流センサの概略図であり、(b)は磁路長を示す図、(c)は磁気抵抗を示す図である。

【図2】磁気回路におけるB−H曲線の一例である。

【図3】ホール素子の付属回路を示す図である。

【図4】B−H曲線のヒステリシスを示すグラフであり、(a)は比較例として直線性の良くない領域まで使用する場合のヒステリシス特性を示し、(b)は本実施形態の如く直線性の良い領域のみを使用する場合のヒステリシス特性を示している。

【図5】所定の磁気ヨークについて、ギャップ長を種々変化させ、電流検出の精度を決める直線性について調べた結果を示すグラフである。

【図6】複数個所にギャップを設けた磁気ヨークの一例を示す図である。

【発明を実施するための形態】

【0012】

図1の(a)は、本発明の一実施形態に係る電流センサの概略図である。また、(b)は磁路長を示す図、(c)は磁気抵抗を示す図である。

図1において、この電流センサ1は、例えば、PWM変調された交流の大電流(例えば数十〜数百アンペア)が流れるバスバー4の電流測定用に設けられるものである。バスバー4は、例えば、電気自動車のインバータとモータとを繋ぐ導体のうちの1本である。

【0013】

電流センサ1は、磁気ヨーク2と、ホール素子3とを備えている。磁気ヨーク2はダストコア(圧粉磁心)によって形成されている。

(b)に示すように、導体であるバスバー4に流れる電流によって磁路が形成される。全磁路長は、磁気ヨーク2内の磁路長Lyと、ギャップ長(=ギャップの磁路長)Lgとの和である。すなわち、磁気ヨーク2は、磁路(Ly+Lg)上にギャップ長Lgを含みつつ、バスバー4を図示のように取り囲んでいる。ギャップとなる空間には、ホール素子3が装着される。なお、磁気ヨーク2内の磁路長Lyは、厚み(内周−外周)の中間を通る長さとして定義されるものとする。

【0014】

ここで、磁気ヨーク2の比透磁率をμy、断面積をSとする。また、ギャップの比透磁率を1とする。なお、ギャップとなる空間領域の、磁路に直交する面積も同様にSである。真空の透磁率をμ0とすると、磁気ヨーク2のみの磁気抵抗Ryは、

Ry=Ly/(μy・μ0・S) ・・・(1)

と表される。一方、ギャップの磁気抵抗Rgは、

Rg=Lg/(μ0・S) ・・・(2)

と表される。

【0015】

従って、式(1)、(2)より、磁気回路の総磁気抵抗Rは、

R=Ry+Rg

=Ly/(μy・μ0・S)+Lg/(μ0・S)

=(Ly/μy+Lg)/(μ0・S) ・・・(3)

となる。バスバー4を流れる電流によって生じる起磁力をFとすると、磁気回路内の磁束Φは、

Φ=F/R ・・・(4)

である。また、磁束密度Bは、式(3)、(4)より、

B=Φ/S=μ0・F/(Ly/μy+Lg) ・・・(5)

となる。

【0016】

上記の式(5)より、磁束密度Bは、ギャップの磁路長Lgに概ね反比例する。従って、ギャップの磁路長Lgを、鋼板の場合よりも相対的に大きく取ることで、B−H曲線における非飽和領域(直線性の良い領域)を使用することができる。具体的には、鋼板の磁気ヨークの場合は通常、Lg/(Ly+Lg)が約5%と、比較的小さい値であるのに対して、上記実施形態の場合はLg/(Ly+Lg)が10%以上で30%以下の、比較的大きい値とする。

【0017】

図2は、磁気回路におけるB−H曲線の一例である。電流増大に伴って磁界Hが強くなるほど磁束密度Bも増大する。このとき、領域A1では、B−H曲線はほぼ直線で、B−Hは比例関係にある。しかし、磁束密度Bは、値B1を超えると勾配が鈍化し、値B2で飽和する。従って、領域A2では直線性が損なわれる。ギャップが小さい(例えば5%)場合、磁束密度Bが領域A2にまで達するので、直線性が良くない領域A2でもホール素子3は電流検出を行うことになり、結果的に検出の精度が悪くなる。一方、ギャップが大きい(10%以上)場合、測定対象が同じ電流範囲であっても磁束密度Bは領域A2に到達せず、領域A1にとどまる。従って、ホール素子3は、直線性の良い領域A1でのみ電流検出を行うことになり、検出の精度が良い。

【0018】

ダストコアの場合、Lg/(Ly+Lg)が10%以上であれば、確実に、直線性の良い領域でホール素子3を使用することができる。10%に満たない場合は、磁束密度BがB1を超えて領域A2に入る可能性がある。5%では確実に領域A2に入り、最大電流に対しては磁気飽和に至る。なお、ギャップの割合が全磁路長の30%を超える場合には、ホール素子3の出力が低下し過ぎて好ましくない。

【0019】

図3は、ホール素子3の付属回路(又は周辺回路)を示す図である。ホール素子3では、磁束密度B、駆動回路31による駆動電流IC、出力電圧VHが、方向性において互いに直交する関係にある。出力電圧VHは、増幅回路32によって増幅される。磁束密度Bの方向へのホール素子3の厚さをd、電子の電荷をe、ホール素子3を構成する半導体のキャリア密度をn、ホール係数をRHとすると、

RH=1/(e・n) ・・・(6)

VH=(RH/d)・IC・B ・・・(7)

となる。

【0020】

上記の式(7)において、ホール係数RH及び厚さdは共に定数となるので、出力電圧VHは、駆動電流ICと磁束密度Bとの積に比例する。駆動電流ICが一定で、ギャップを大きくすることによって磁束密度Bが低下すると出力電圧VHが低下するが、ギャップを大きく取っても、駆動電流ICを増大させることによって、出力電圧VHの低下を抑制することができる。

【0021】

なお、ギャップを大きく取った場合に、駆動電流ICを増大させることなく、増幅回路32の利得を大きくすることによっても所要の出力を得ることは可能であるが、この場合、増幅回路32への入力に混入するノイズも増幅することになるので、その点でも、駆動電流ICを増大させることが好ましい。

また、ホール素子3の半導体の種類としては、例えば、InSb、InAs、Si、GaAsがある。温度に対する出力電圧VHの安定性の観点では、GaAsが好適である。

【0022】

図4は、B−H曲線のヒステリシスを示すグラフであり、(a)は比較例として直線性の良くない領域まで使用する場合のヒステリシス特性を示し、(b)は本実施形態の如く直線性の良い領域のみを使用する場合のヒステリシス特性を示している。(a)の場合、磁気飽和の影響により、ヒステリシスループは大きくなる。これに対して、(b)の場合、磁気飽和しないので、ヒステリシスループは小さくなる。(a)のヒステリシス[%]を(Br1/Bm1)、(b)のヒステリシス[%]を(Br2/Bm2)とすると、

(Br1/Bm1)>(Br2/Bm2)

であり、ギャップを大きく取ることによりヒステリシスは改善される。

【0023】

ここで、所定の磁気ヨークについて、ギャップ長を種々変化させ、電流検出の精度を決める直線性と、ヒステリシスとについて調べた結果を、図5のグラフ及び表1に示す。ギャップ長は、3mmから8mmまで1mmずつ変化させた。これらのギャップ長の、全磁路長に対する割合は、以下の通りである。

【0024】

3mm →4.66%

4mm →6.21%

5mm →7.76%

6mm →9.32%

7mm →10.87%

8mm →12.42%

【0025】

図5において、横軸は電流を示し、縦軸はホール素子3による電流検出のフルスケールに対する誤差すなわち、直線性に対する誤差[%]を示している。グラフにより明らかなように、直線性は、3mmの場合が最も悪く、ギャップ長が増大するほど直線性が良くなり、3〜8mmの範囲では、8mmの場合が最も良い、という結果となっている。

【0026】

【表1】

【0027】

また、上記の表1より、ヒステリシスに関しても、3〜8mmの範囲では、8mmの場合が最も良い結果となっている。磁束密度Bはギャップ長が長いほど小さくなるので、前述のように、ホール素子3の駆動電流ICを増大して出力電圧VHを確保することが必要である。

【0028】

以上のように、本実施形態に係る電流センサ1では、ホール素子3が、B−H曲線の直線領域すなわち、直線性に優れた領域で使用されるので、安価なダストコアを用いても精度を損なわずに電流検出を行うことができる。従って、ダストコアを用いても精度良く測定できる電流センサ1を提供することができる。

【0029】

なお、ギャップ長は、必ずしも一個所で確保しなくてもよい。図6は、複数個所にギャップを設けた磁気ヨーク2の一例を示す図である。この場合、ギャップ長は、(Lg1+Lg2)となる。すなわち、全磁路長に対するギャップ長の割合は、磁路上の複数個所に設けられたギャップの長さの総和として確保することができる。これにより、磁気ヨーク2の形態に関して、ギャップを確保するための種々の設計が可能となる。

【0030】

なお、今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は特許請求の範囲によって示され、特許請求の範囲と均等の意味及び範囲内での全ての変更が含まれることが意図される。

【符号の説明】

【0031】

1 電流センサ

2 磁気ヨーク

3 ホール素子

4 バスバー(導体)

(Ly+Lg) 全磁路長

Lg ギャップ長

【特許請求の範囲】

【請求項1】

ダストコアによって形成され、導体に流れる電流によって生じる磁路上にギャップ長を含みつつ、当該導体を取り囲む磁気ヨークと、

前記ギャップ長を構成するギャップに設けられるホール素子と、を備え、

前記磁路の磁束密度がB−H曲線の直線領域内に制限されるように全磁路長に対する前記ギャップ長の割合を設定したことを特徴とする電流センサ。

【請求項2】

前記割合は10%〜30%の範囲内である請求項1記載の電流センサ。

【請求項3】

前記割合は、前記磁路上の複数個所に設けられたギャップの長さの総和として確保する請求項1又は2に記載の電流センサ。

【請求項4】

前記割合は、鋼板コアによって形成された磁気ヨークの場合より大きく設定され、それにより生じ得る前記ホール素子の相対的な出力低下を、駆動電流増大によって抑制する請求項1〜3のいずれか1項に記載の電流センサ。

【請求項1】

ダストコアによって形成され、導体に流れる電流によって生じる磁路上にギャップ長を含みつつ、当該導体を取り囲む磁気ヨークと、

前記ギャップ長を構成するギャップに設けられるホール素子と、を備え、

前記磁路の磁束密度がB−H曲線の直線領域内に制限されるように全磁路長に対する前記ギャップ長の割合を設定したことを特徴とする電流センサ。

【請求項2】

前記割合は10%〜30%の範囲内である請求項1記載の電流センサ。

【請求項3】

前記割合は、前記磁路上の複数個所に設けられたギャップの長さの総和として確保する請求項1又は2に記載の電流センサ。

【請求項4】

前記割合は、鋼板コアによって形成された磁気ヨークの場合より大きく設定され、それにより生じ得る前記ホール素子の相対的な出力低下を、駆動電流増大によって抑制する請求項1〜3のいずれか1項に記載の電流センサ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−79862(P2013−79862A)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願番号】特願2011−219971(P2011−219971)

【出願日】平成23年10月4日(2011.10.4)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【出願人】(000183406)住友電装株式会社 (6,135)

【出願人】(395011665)株式会社オートネットワーク技術研究所 (2,668)

【Fターム(参考)】

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願日】平成23年10月4日(2011.10.4)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【出願人】(000183406)住友電装株式会社 (6,135)

【出願人】(395011665)株式会社オートネットワーク技術研究所 (2,668)

【Fターム(参考)】

[ Back to top ]